## TEXAS INSTRUMENTS

Improving Man's Effectiveness Through Electronics

# Model 980 Computer Maintenance Manual Arithmetic Unit And Control Console

MANUAL NO . 960699 - 9702 ORIGINAL ISSUE 15 JULY 1972 REVISED AND REISSUED 1 SEPTEMBER 1975

#### C Texas Instruments Incorporated 1975 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

### LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 980 Computer Maintenance Manual, Arithmetic Unit and Control Console (960699-9702)

Total number of pages in this publication is 128 consisting of the following:

| PAGE<br>NO.       | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|-------------------|---------------|-------------|---------------|-------------|---------------|

| Cover             | 0             |             |               |             |               |

| Eff. Pages        | 0             |             |               |             |               |

| iii - iv          | _             | •           |               |             |               |

| 1-1 - 1-10        | 0             |             |               |             |               |

| 2-1 - 2-2         | 0             |             |               |             |               |

| 3-1 - 3-6         | 0             |             |               |             |               |

| 4-1 - 4-86        | 0             |             |               |             |               |

| 5-1 - 5-4         | 0             |             |               |             |               |

| Alphabetical      |               |             |               |             |               |

| Index Div         | 0             |             |               |             |               |

| Index-1 - Index-8 | 0             |             |               |             |               |

| User's Response.  | 0             |             |               |             |               |

| Bus. Reply        | 0             |             |               |             |               |

| Cover Blank       |               |             |               |             |               |

| Cover             | 0             |             |               |             |               |

#### **PREFACE**

This manual contains maintenance instructions for the Arithmetic Unit and the Control Console of either the Texas Instruments Model 980A or Model 980B Computer. Maintenance information is distributed within the remaining four sections of this manual as follows:

- Section I describes the general functions and characteristics of the Arithmetic Unit and Control Console.

- Section II describes the installation of the Arithmetic Unit and Control Console.

- Section III describes the operation and programming for the Arithmetic Unit.

- Section IV provides theory of operation for the Airthmetic Unit and the Control Console.

- Section V describes maintenance and trouble analysis procedures for the units.

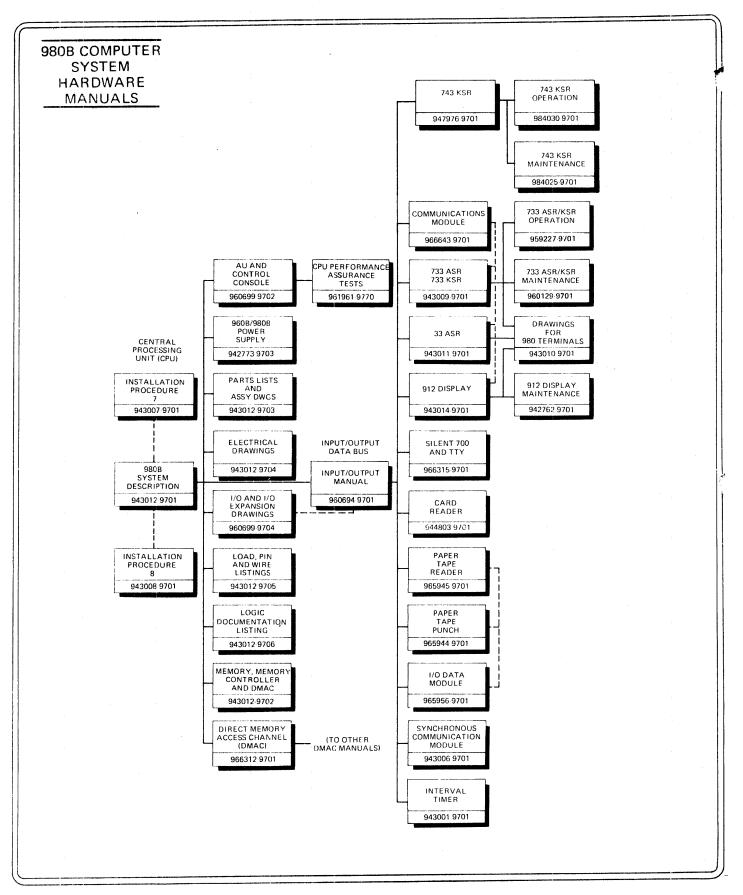

Before using this manual for maintenance, review the System Description manual for the computer to gain a better understanding of the system interrelations. Maintenance documentation for the circuit boards is contained in the Parts List and Assembly Drawings manual, the Electrical Drawings manual, the Load, Pin and Wire List manual, and the Logic Documentation manual for the computer system. These manuals are described in the System Description manual listed below that applies to the particular computer:

- Model 980A Computer Maintenance Manual, System Description, TI Part Number 960699-9701

- Model 980A Computer Maintenance Manual Electrical Drawings, TI Part Number 960699-9707

- Model 980A Computer Maintenance Manual Memory, Memory Controller and Direct Memory Access Channel, TI Part Number 960699-9703

- Model 980A Computer Maintenance Manual Load and Pin List, TI Part Number 960699-9708

- Model 960A/980A Computer Maintenance Manual Power Supply, TI Part Number 226750-9705

- Model 980B Computer Maintenance Manual, System Description, TI Part Number 943012-9701

- Model 980B Computer Maintenance Manual Electrical Drawings, TI Part Number 943012-9708

- Model 980B Computer Maintenance Manual Memory, Memory Controller and Direct Memory Access Channel, TI Part Number 943012-9702

- Model 980B Computer Maintenance Manual Load and Pin List, TI Part Number 943012-9705

- Model 960B/980B Computer Maintenance Manual Power Supply, TI Part Number 942773-9703

- Program Descriptions, listings and operating procedures for the Performance Assurance Tests TI Part Number 961961-9770.

#### SECTION I

#### GENERAL DESCRIPTION

#### 1.1 GENERAL

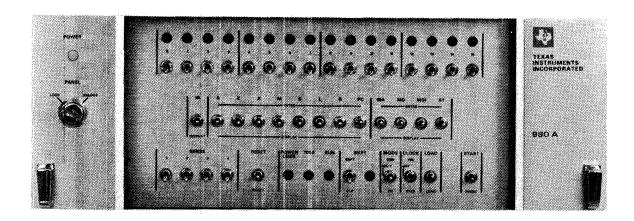

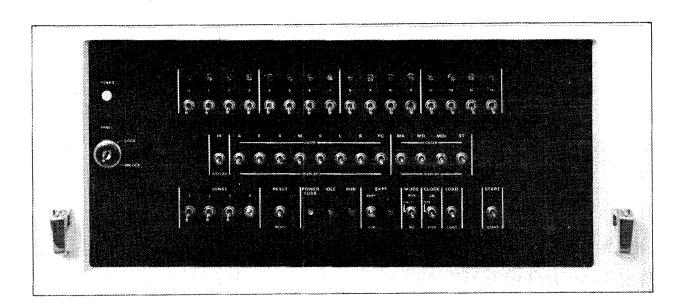

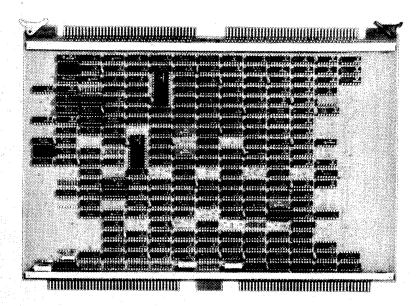

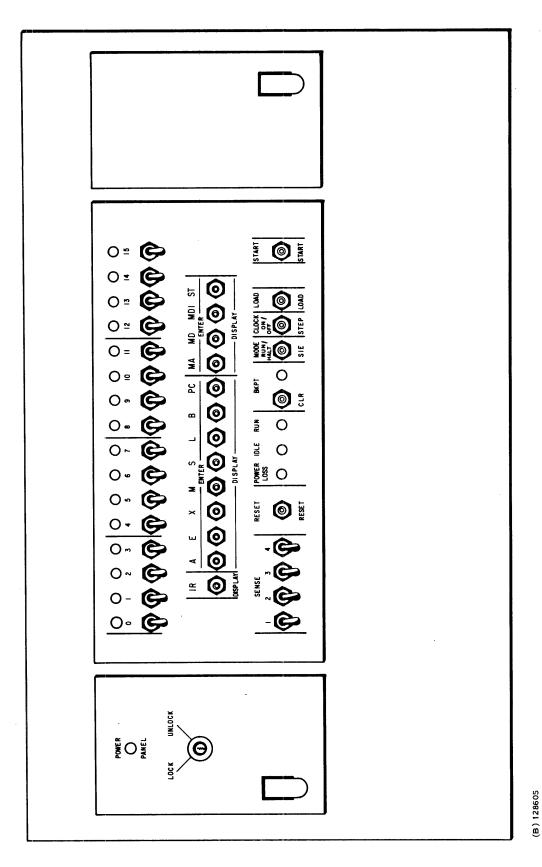

Figure 1-1 shows both the 980A and 980B control consoles and figure 1-2 shows the Arithmetic Unit printed circuit boards.

#### 1.2 ARITHMETIC UNIT FUNCTIONS

The Arithmetic Unit (AU) contains logic for four major system functions:

- Instruction Execution

- System Interrupt Control

- Input/Output Bus Control

- Console Function Control.

- 1.2.1 INSTRUCTION EXECUTION. Execution of the basic instruction set is the primary function of the AU. Machine instructions can be 16, 32, or 48 bits in length. The basic memory word contains 16 bits of binary data; therefore, 32 and 48 bit instructions must be accessed from 2 and 3 successive memory locations, respectively. The instruction formats are described in the *Model 980 Computer Assembly Language Programmer's Reference Manual* (TI Part Number 943013-9701).

After the AU has accessed the first instruction word, a legal instruction operation test is performed. All operand and address calculations are performed and the operation is executed. For the AU to perform this function, a 16-bit random access memory is required to store the program data and instructions.

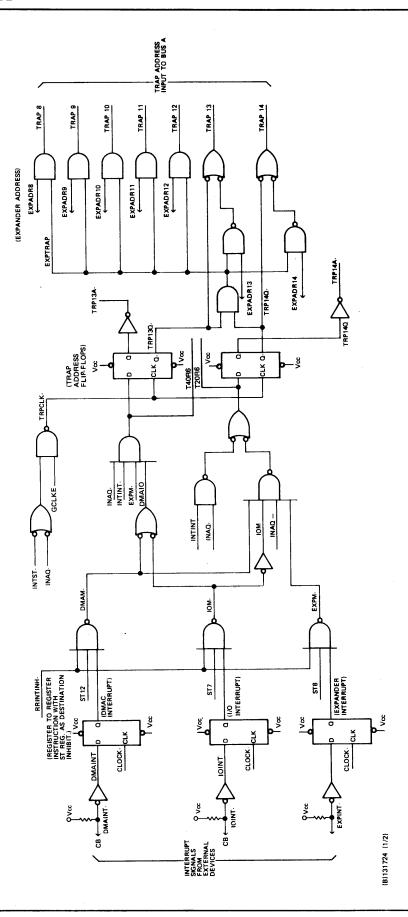

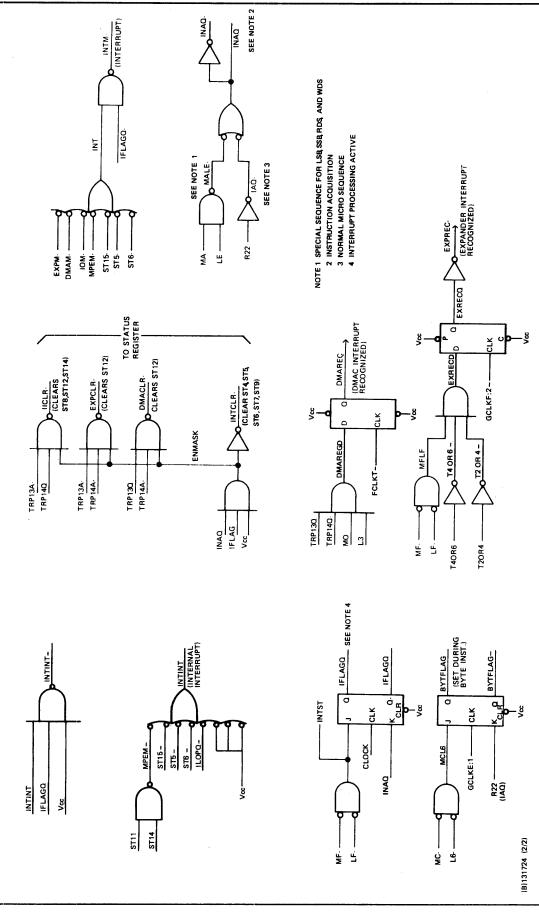

- 1.2.2 SYSTEM INTERRUPT CONTROL. The interrupt feature provides a method of switching from one routine to another due to an internal or external condition. During program execution, the AU monitors the system for three standard types of interrupt and one optional interrupt type. The standard interrupt types are: internal, Direct Memory Access Channel (DMAC), and Input/Output bus interrupts. The optional interrupt feature adds up to 32 priority vectored interrupt lines. When any interrupt occurs, the AU detects the condition and, assuming interrupts are enabled, initiates appropriate action on a priority basis.

- 1.2.3 INPUT/OUTPUT BUS CONTROL. The 16-bit Input/Output (I/O) bus is used for single-word transfers between memory and a slow-speed I/O device. Each transfer requires the execution of an AU instruction. All timing and control for direct I/O data transfers is provided by the AU.

- 1.2.4 CONSOLE FUNCTION CONTROL. The AU also functions as controller for the control console. All console functions are sequenced by logic contained within the AU.

980A CONTROL CONSOLE

131705 (980-773-18-2)

129829 (980-374-13-7)

Figure 1-1. 980A and 980B Control Consoles

AU1

131706

AU2

131707

Figure 1-2. Arithmetic Unit Printed Circuit Boards No. 1 and No. 2

#### 1.3 ARITHMETIC UNIT CHARACTERISTICS

All circuitry in the Arithmetic Unit consists of small and medium scale integrated circuits of transistor-transistor logic (TTL). The plastic dual-in-line packages are mounted on two multilayer printed circuit boards (TI Part Number 960754(AU1) and 960751(AU2)). All AU logic is designed to function synchronously with a single 4.0-MHz clock signal which is obtained from the memory controller board.

1.3.1 ARITHMETIC UNIT LOCATION AND CONNECTIONS. The two AU boards (AU1 and AU2) have dual 80-pin connectors on the bottom-edge that plug into the computer connector plate slots as shown in the mechanical configuration that is illustrated in Section II—Installation.

The +5 Volts and ground signals on the connector plate printed circuit board are bussed on etched paths to the AU board connectors.

All bottom edge connector signals between the AU connector pins and other system units are carried through wire-wrapped connections. Partition signals, required between the two AU boards, are brought to the top-edge connector pins and are carried through the one-to-one printed circuit connector boards (TI Part Number 960961).

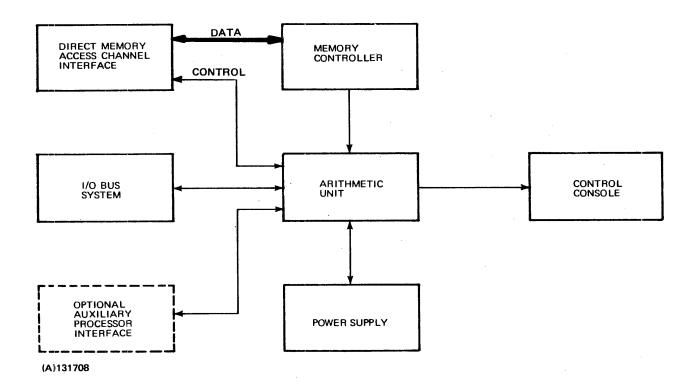

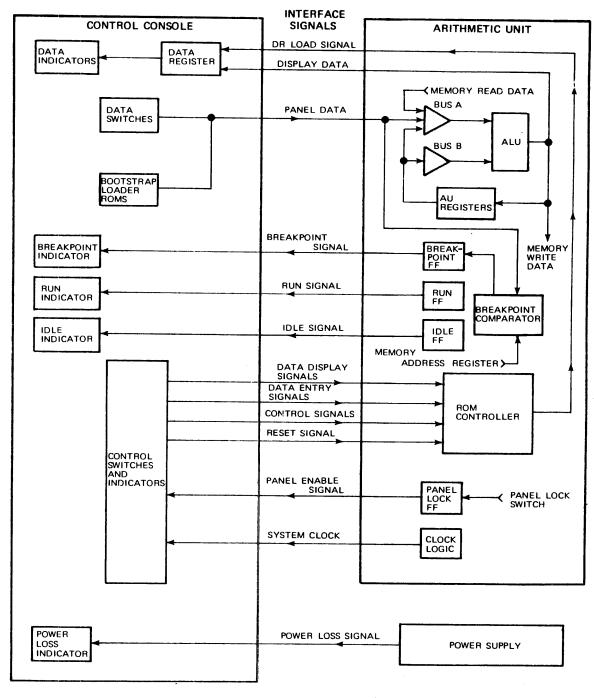

A basic functional diagram of the AU and related units that interconnect to the AU through the connector plate wiring is illustrated in figure 1-3.

Figure 1-3. Arithmetic Unit System Interface, Functional Diagram

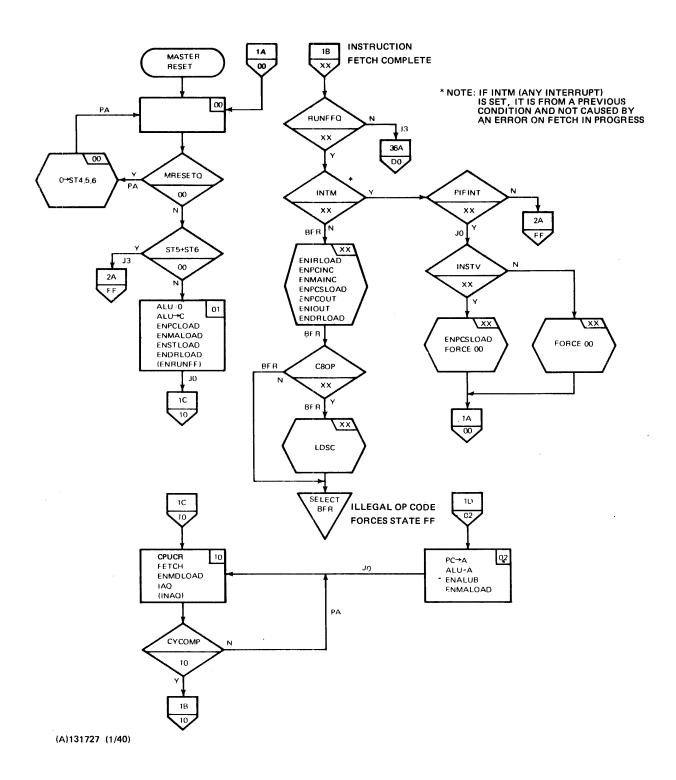

1.3.2 ARITHMETIC UNIT CONTROL. Logic control functions in the AU are performed with a TTL Read-Only Memory (ROM). The control ROM consists of 256 words with 72 bits-per-word. A logic state in the AU is identified by the present address of the ROM controller. Major control signals that are required for state functions are taken from the contents of the 72-bit ROM word being addressed as a given state. Micro sequencing is performed by changing the ROM address as determined by the state transfer logic. State transfers or ROM address changes occur on the negative edge of the True system clock pulse to maintain synchronization.

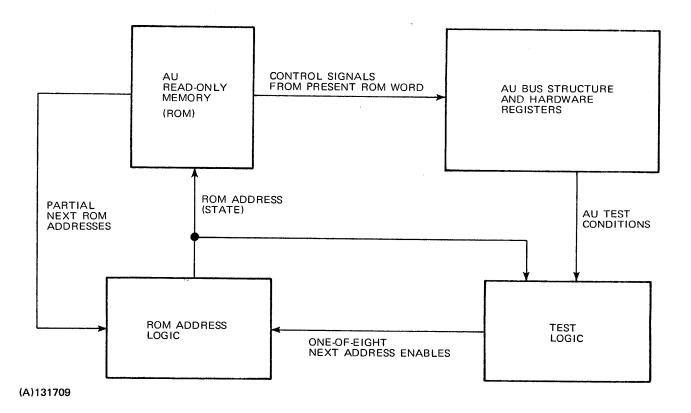

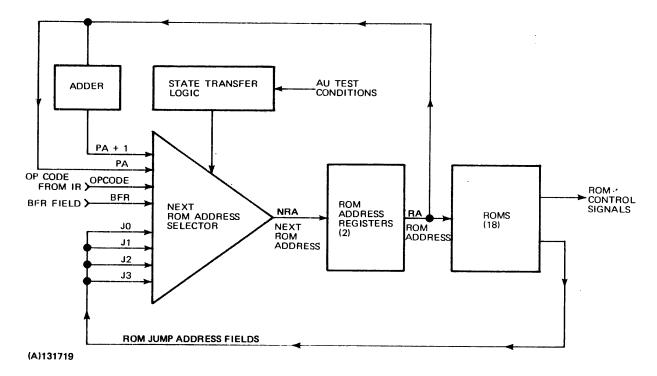

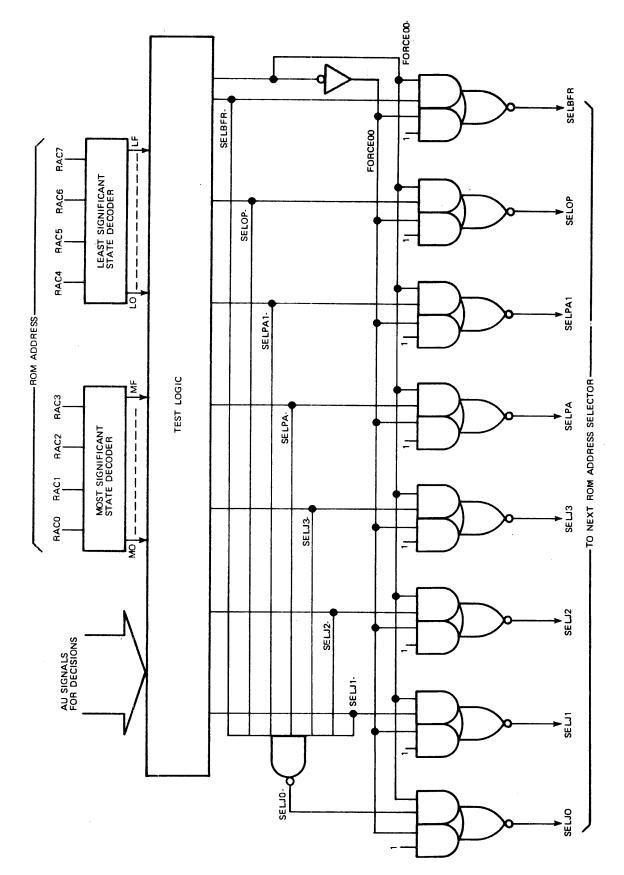

A functional diagram of the AU control configuration is illustrated in figure 1-4. In a given logic state, the present ROM address is required by the AU test logic to enable appropriate decisions resulting from AU test conditions. With this information, the test logic generates an enable signal for the next ROM address selection. The ROM address logic uses the next address enable signal to select one of eight possible next ROM addresses, or a default address. Once selected, the next ROM address is loaded into the ROM address register on the negative-edge of the true system clock pulse and a state transfer occurs.

Of the nine possible next addresses that are generated by the ROM address logic, four are obtained from ROM outputs of the present state. The remaining five are generated with logic.

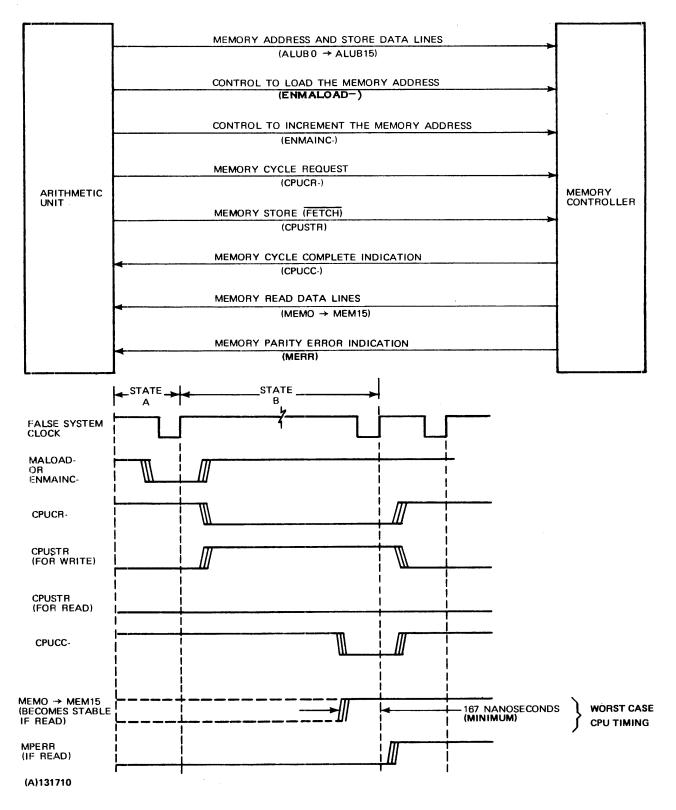

1.3.3 ARITHMETIC UNIT MEMORY ACCESS. The 16-bit data structure of the Arithmetic Unit has the capability of addressing 65, 536 words of random access memory. The AU requests memory cycles from the semiconductor memory system; however, the memory controller performs all memory cycle priority and control functions. Interface signals between the AU and memory controller and the generalized timing information are shown in figure 1-5.

Figure 1-4. Arithmetic Unit Control Configuration, Functional Diagram

Figure 1-5. Memory Controller Interface Connections, Signals, and Timing

A 16-bit memory address register is duplicated on both the arithmetic unit and memory controller. This allows the same sixteen lines (ALUBO→ALUB15) to carry both memory addresses and write data to the memory controller board. Both registers may be parallel loaded or incremented by one in the logic state that precedes the memory cycle. Any time the AU memory address register is loaded or incremented, the register on the memory controller receives the same controls; however, the converse is not true.

Arithmetic memory cycles require two logic states. These states are illustrated in figure 1-5 as state A and state B. In state A, the memory address register is conditioned to be loaded. The ENMALOAD— signal can load the memory address register with the address which appears on the ALUB lines, or the ENMAINC— signal can increment the present address by one. Once the memory address is conditioned to be loaded, an AU memory cycle may be requested.

A typical memory cycle state occurs during state B. During state B, the AU generates CPUCR—as a cycle request to the memory controller. If a store cycle is requested, CPUSTR is generated along with CPUCR—. A fetch cycle is requested if only CPUCR— is generated. As shown in figure 1-5, an AU cycle request disables the AU system clock. This condition remains until the memory controller finishes the cycle and returns a cycle complete signal (CPUCC—) to the AU. Then the clock starts and state transfer occurs. Since the clock stops during memory cycles, AU control signals which require clocks do not effect the AU until the end of the memory cycle state.

The minimum time duration of a cycle state is 750 nanoseconds. Two system factors can extend this time. The Direct Memory Access Channel (DMAC) can be in operation, making it impossible for the AU to gain immediate access to memory. Also, the memory controller must refresh the MOS memory. This requires a 750-nanosecond cycle every 31 microseconds (every 62 microseconds on the 980A) during normal operating conditions. If either of these conditions occur, the AU remains in its cycle state until the memory controller provides access to the AU and issues a CPUCC— signal.

During a store cycle, data stored in memory is taken from the ALUB lines. If data is fetched from memory, the AU takes data from the MEM lines. Read data must be stable for 167 nanoseconds before the edge of the clock pulse occurs to meet worst case propagation delays through the AU data path. If a memory parity error is detected by the memory controller, the MERR signal indicates this condition in the state immediately following the memory cycle.

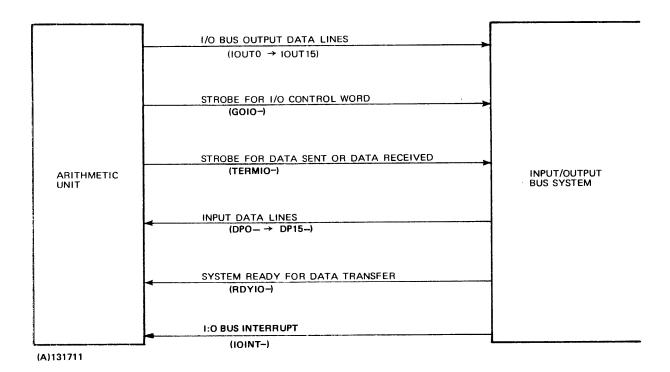

1.3.4 DIRECT INPUT/OUTPUT. The AU provides control and timing for the direct I/O bus by the execution of two I/O bus instructions. The basic interface signals between the AU and I/O bus system are shown in figure 1-6. Data transferred out to the I/O bus system is transferred on the IOUT lines. Input data to the AU is transferred on the DP lines.

During the execution of both the Write Direct Signal (WDS) or Read Direct Single (RDS) instructions the first word of the instruction is sent to the I/O bus as the control word along with the strobe signal GOIO—. This control word contains the coded external I/O register number which is unique to each I/O controller used. This word also contains a code bit to identify the difference between WDS and RDS instructions.

After the control word is sent, the WDS instruction sends an operand word out on the IOUT lines. It also strobes the data with TERMIO—. An RDS instruction controls the AU to accept data on the DP lines. After the data has been received, a TERMIO— strobe is sent to indicate data transfer has occurred.

Figure 1-6. Input/Output Bus System Interface Signal Connections

If the BUSY option is used with either the RDS or WDS instructions, the AU transfers the control word and GOIO— as in all cases; however, the AU delays the transfer of data for a maximum of 750 nanoseconds. The AU must receive the RDYIO— signal during the 750 nanosecond period to initiate a data transfer. For detailed I/O bus timing, refer to the *Model 980 Computer Input/Output Manual* (TI Part Number 960694-9701).

- 1.3.5 DIRECT MEMORY ACCESS CONTROL. By executing the Automatic Transfer Instruction (ATI), the AU allows direct memory access by high speed device controllers. The AU continues program execution; however, the DMAC has a higher priority on memory cycles. Under these conditions, cycle times for the AU increase, because the AU must wait for the DMAC device to finish its cycles. The memory controller provides complete memory cycle priority control.

- 1.3.6 AUXILIARY PROCESSOR PORT ACTIVATION. The Auxiliary Processor Port (APP) is similar to the DMAC port in that the AU allows devices on both ports to have memory access. However, when the AU executes the Auxiliary Processor Instruction (API), the AU does not execute subsequent instructions until the APP device has completed its process. Auxiliary processes are treated as optional CPU instructions. When the process is complete, the AU executes the next program instruction. Also, if the APP device is not in the system, the AU takes illegal instruction operation code action as with any other illegal instruction. With respect to DMAC and refresh cycles, the APP requested memory cycles have the same access priority as AU instructions.

Because auxiliary processes can require long execution times, these processes can be aborted by the occurrence of system interrupts. However, it is a function of the APP controller to relinquish access to the system and return system control to the AU in the event of an interrupt. It is only possible for the APP device to lose control immediately if the Privileged Instruction Feature (PIF) is enabled and the APP controller attempts a memory address violation.

- 1.3.7 INTERRUPT CONTROL. There are three standard types of interrupts and a fourth optional interrupt which the AU can control. These interrupts are recognized by the AU in the following order of priority:

- Internal

- Expanded Priority Interrupt System (optional)

- Direct Memory Access Channel

- I/O Bus System.

The internal interrupt can be generated from several sources of equal priority. These sources include:

- Illegal Operation Codes

- Power Failures

- Memory Parity Errors

- Privileged Instruction Feature Memory Address Violations

- Privileged Instruction Feature Instruction Violations.

STATUS REGISTER BIT

The occurrence of any or all of these conditions causes the AU to execute the next instruction from memory address  $0000_{16}$ . To determine which condition caused the internal interrupt, status register bits are set to identify each. These status bits are as follows:

CALISE

| STITUS RESISTER BIT | CAUSE                     |

|---------------------|---------------------------|

| 5                   | PIF Address Violation     |

| 6                   | PIF Instruction Violation |

| 14                  | Memory Parity Error       |

| 15                  | Power Failure             |

| (NONE OF ABOVE)     | Illegal Operation code    |

The PIF violations and memory parity errors can be disabled, by other status bits, to prevent these violations and errors from causing internal interrupts. These status bits (enable = ONE, disable = ZERO) are shown in table 1-1.

The optional expanded interrupt is generated by priority logic in the expanded interrupt system. When the AU recognizes this type of interrupt, it executes the next instruction from the location specified by the address read in from the expanded interrupt system. This type of an interrupt can occur only if status bit 8 is set.

#### Table 1-1. Status Register Bits

| Bit | Function                                                     |

|-----|--------------------------------------------------------------|

| 0   | Comparison Indicator                                         |

| 1   | Comparison Indicator                                         |

| 2   | Overflow Indicator                                           |

| 3   | Carry Indicator                                              |

| 4   | PIF Address & Instruction Violation Interrupt Enable/Disable |

| 5   | PIF Address Violation Indicator                              |

| 6   | PIF Instruction Violation Indicator                          |

| 7   | I/O Interrupt Enable/Disable                                 |

| 8   | Optional Expanded I/O Interrupt Enable/Disable               |

| 9   | PIF Lower Limit Address Bias Enable                          |

| 10  | Index Indicator                                              |

| 11  | Memory Parity Error Interrupt Enable/Disable                 |

| 12  | DMAC Interrupt Enable/Disable                                |

| 13  | -                                                            |

| 14  | Memory Parity Error Indicator                                |

| 15  | Power Failure Indicator                                      |

The DMAC can cause an interrupt if status bit 12 is set. This interrupt causes the AU to initiate the transfer of the next instruction out of memory location  $0004_{16}$ .

The I/O bus system interrupts are enabled if status bit 7 is set. The AU initiates the transfer of the next instruction out of memory location  $0006_{16}$  if this type of an interrupt is recognized.

The AU checks for interrupt requests after the execution of each instruction in a program. Exceptions to this rule include WDS, RDS, LSB, SSB, and register-to-register instructions which have the status register as the destination register. If any or all of the interrupts occur, the AU responds to the interrupt with the highest priority. The AU also disables all other interrupt types of the same priority level and lower.

#### **SECTION II**

#### INSTALLATION

#### 2.1 GENERAL

This section describes the installation of the Arithmetic Unit (AU) and Control Console. The installation of the series 980 Computers is covered in the Model 980 (A or B) Computer Maintenance Manual, System Description referenced in the Preface to this manual.

#### **CAUTION**

Removal or replacement of the AU or Control Console logic boards require that ac power and battery power must be turned off.

An air baffle (dust cover) mounts over the CPU logic card cage. This baffle must be removed in order to gain access to the AU and Control Console modules. Generally, the CPU should not be operated prior to replacing the baffle to ensure proper cooling air flow.

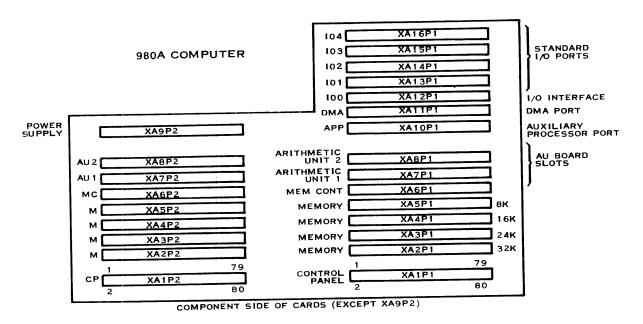

#### 2.2 ARITHMETIC UNIT INSTALLATION

The AU logic multilayer circuit boards plug into a connector plate mounted in the CPU chassis. Each logic board has two bottom-edge connectors that mate with captive connectors on the connector plate. The slot location for each board is labeled on the card cage frame (A1 or A2). The A1 board is marked with an A1 on the ejector tab and is located in slot A1. Similarly, the A2 board is located in slot A2. The connector numbers associated with slots A1 and A2 differ between the 980A and 980B models. This is shown in figure 2-1. Modules are installed with components facing the front of the machine.

- 2.2.1 980A CONNECTOR PLATE. Slots A1 and A2 are designated XA7 and XA8, respectively, on the 980A Computer connector plate. Connectors XA7P1 and XA7P2 receive the A1 logic board edge connectors. Slot A2 connectors XA8P1 and XA8P2 receive the A2 logic board edge connectors.

- 2.2.2 980B CONNECTOR PLATE. Slots A1 and A2 are designated XA6 and XA7, respectively, on the 980B computer connector plate. Connectors XA6P1 and XA6P2 receive the A1 logic board edge connector. Slot A2 connectors XA7P1 and XA7P2 receive the A2 logic board edge connectors.

#### 2.3 AU OPERATION VERIFICATION

After performance of the AU installation procedure the operation of the AU should be verified by executing the applicable CPU Performance Assurance Test (PAT).

#### 2.4 CONTROL CONSOLE INSTALLATION

The Control Console assembly plugs into the slot labeled CP (stamped on the card cage frame). The symbolized panel, with LED displays and switches, faces the front of the computer. The trim frame is aligned to a cutout in the chassis front panel when the console is properly installed.

#### FRONT TOP VIEW

COMPONENT SIDE OF CARDS (EXCEPT XA8P2)

FRONT TOP VIEW

(A)131712

Figure 2-1. Arithmetic Unit Printed-Circuit Card Locations

#### **SECTION III**

#### **OPERATION AND PROGRAMMING**

#### 3.1 GENERAL

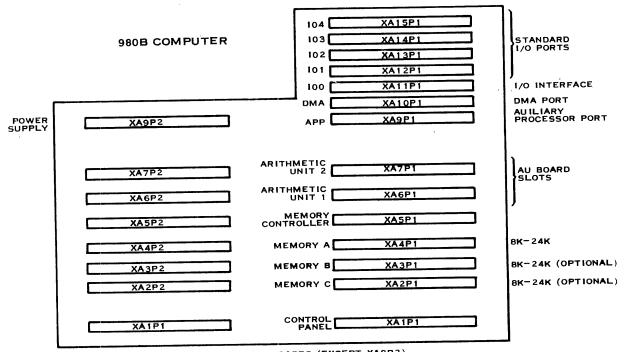

The Control Console provides mlnual control of AU operations, display of system data, and monitoring of machine status. This section describes the functions of the switches and indicators.

#### 3.2 CONSOLE SWITCHES

The Control Console contains logic, switches, and indicators for manual control of the AU. The toggle switches, on the control panel, are arranged in three rows. The top row contains 16 data entry switches; the center row provides control of data display and entry; the lower row provides control of system operation. Figure 3-1 shows the Control Console switches and indicators.

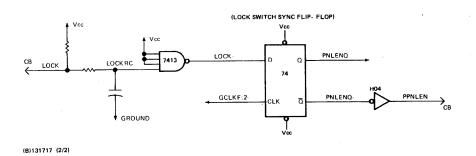

- 3.2.1 CONSOLE KEY LOCK SWITCH (LOCK/UNLOCK). The Console Key Lock Switch enables operation of the Control Console in the UNLOCK position. When the switch is in the LOCK position, all controls are disabled except the 16 data switches, the 4 sense switches, and the Breakpoint/Clear (BKPT/CLR) switch. The contents of the DATA switches cannot be entered when the Key Lock Switch is in the LOCK position, but the breakpoint logic continues to monitor the memory address specified by the data switches. The BKPT/CLR resets the BKPT indicator; however, the system cannot be forced to halt. The key can be removed in either position.

- 3.2.2 DATA SWITCHES. The Data Switches are numbered 0 through 15, left to right. When a switch is up, the corresponding bit position is a logic one; it is a logic zero when the switch is down. These Data Switches allow the selection of data that can be placed in the following locations: the program address register (PC), the machine status register (ST), the memory address register (MA), directly into memory (MD), and registers A, E, X, M, S, L, or B. Data loading occurs in the specified location when the corresponding Enter Switch is actuated to the ENTER position, providing that the AU is in the Halt mode. When the AU is running the Data Switches contain the address being monitored by the breakpoint logic.

- 3.2.3 IR SWITCH. The IR switch is used to display instruction register data on the indicators. The switch has a normal center position, a momentary up position, and a momentary down position. When pushed to the DISPLAY (down) position, the contents of the instruction register are displayed. The up position of the switch is nonfunctional. The display function is only active when the computer is in the Halt Mode.

- 3.2.4 PC, A, B, E, L, M, S, X, ST, MA AND MD DISPLAY AND ENTER SWITCHES. These switches control the following data DISPLAY and ENTER functions, respectively: Program Counter; Registers A, B, E, L, M, S, X and ST; Memory Address register; and Memory Data. Each switch has a normal center position, a momentary up position, and a momentary down position. When any of these switches is pushed to the ENTER (up) position, the current setting of the 16 DATA switches is loaded into the associated register or memory location. The entered value is displayed by the display indicators. The Memory Data (MD) is entered into the address specified by the contents of the Memory Address (MA) register. If the switch is pushed to the DISPLAY (down) position, the contents of the associated register or memory are displayed. All switches in this group only function when the computer is in the Halt Mode.

Figure 3-1. Control Console Panel Switches and Indicators

3.2.5 MDI SWITCH. The Memory Data and Increment Address (MDI) switch functions as the MD switch that is described in the preceding paragraph for entering or displaying memory data except each time MDI is actuated to either ENTER or DISPLAY, the Memory Address Register is incremented. It is used for loading or displaying consecutive memory locations.

#### **NOTE**

If the MDI switch is activated to read location MEM the MA register contains address MEM+1 while the Data Indicators display the contents of MEM.

- 3.2.6 SENSE SWITCHES. The four SENSE switches are two-position toggle switches used by the two sense switch instructions (SSE and SSN). Each SENSE switch is placed in the up position for a logic one or down for a logic zero.

- 3.2.7 **RESET SWITCH**. The system RESET switch is used to reset major system registers. This switch has a normal center position and a momentary down position. When the switch is pushed to the RESET (down) position, the program counter, status register, memory address register, and display register are cleared. This function can occur if the computer is in the Halt or Run mode, but it is disabled when the panel is locked.

- 3.2.8 BKPT SWITCH. The Breakpoint (BKPT) switch is a three-position toggle switch. If the computer is in the Run or SIE mode and the BKPT switch is in the center position, the BKPT indicator is lighted when the data switch setting is contained in the memory address register. The indicator can be extinguished by pushing the BKPT switch to the CLR (down) position (computer in any mode) without affecting system operation. When the BKPT switch is in the BKPT (up) position and the computer is in the Run mode, the computer Halts and the BKPT indicator lights if the DATA switch setting is contained in the memory address register. The instruction which uses the breakpoint address is completed before the computer Halts. When the panel is locked the Halt cannot occur.

- 3.2.9 MODE SWITCH. The MODE control switch is a three position toggle switch. To start program execution, the MODE switch is placed in the up (RUN) position and the START switch is actuated (placed in momentary down position). The Run mode is entered and the RUN indicator is lighted when the START switch is actuated. When the MODE switch is placed in the center (HALT) position, the system halts when the instruction in progress is completed. To execute a single instruction, the MODE switch is placed in the down (SIE) position and the START switch is actuated.

- 3.2.10 CLOCK SWITCH. The Clock switch is a three-position toggle switch with a normal center position (OFF) an up position (ON) and a momentary down position (STEP). For normal system operation, this switch is in the up (ON) position and the system clock is free running. When the Clock switch is placed in the center (OFF) position, the arithmetic unit clock is stopped. Each time the Clock switch is pushed to the momentary down (STEP) position, a single system clock pulse is generated for the arithmetic unit. The operation of this switch is normally disabled. Refer to the maintenance section for instructions on enabling the Clock Switch using a jumper on the Console printed circuit board.

- 3.2.11 LOAD SWITCH. The LOAD (store bootstrap loaders in memory) switch is a two-position toggle switch with a normal center position and momentary up position. If the system is halted and this switch is pushed to the up position, 256 words of optional firmware program are loaded into memory. The memory location of the first word is always zero.

If the MODE switch is in the RUN position, the computer begins execution at the address in the program counter. If the MODE switch is in the HALT position the computer does not begin execution until the MODE switch is placed in the RUN position and the START switch is actuated (momentary down position).

3.2.12 START SWITCH. The Start switch is a two-position toggle switch with a normal center position and momentary down position. If the system is in the Halt mode and this switch is pushed to the down (START) position, the RUN or SIE setting of the MODE switch is enabled.

#### 3.3 CONSOLE DISPLAY INDICATORS

Console indicators display data and machine status. The top row of indicators (DATA) display 16 data bits, 0 through 15, left to right. The remaining four indicators display machine status (e.g., PWR LOSS, IDLE, RUN, and BKPT).

- 3.3.1 DATA INDICATORS. Sixteen Data indicators at the top of the console display machine data. The contents of a memory location or of any one of eleven machine registers can be displayed when the system is in the Halt mode. Data can be entered manually into memory or into any of ten machine registers. When a manual entry is executed, the value is displayed. When the system is in the Run or SIE (Single Instruction Execution) mode, the present instruction address is continually displayed.

- 3.3.2 POWER LOSS INDICATOR. The Power Loss (memory power failure) indicator is on when memory power is lost and ac power is restored. The Power Loss indicator is turned off by activating the System RESET switch.

- 3.3.3 IDLE INDICATOR. The Idle indicator is lighted, and the Run indicator is extinguished, when an Idle instruction causes the computer to halt. The Idle indicator is then extinguished when the computer enters the Run or SIE mode or by system RESET.

- 3.3.4 RUN INDICATOR. The Run indicator is lighted when the system is placed in the Run mode and the START switch is activated. When the system is removed from the Run mode, the Run Indicator is extinguished.

- 3.3.5 BKPT INDICATOR. The BKPT (Breakpoint) Indicator is lighted when the memory address register contents are the same as the data switches and the computer is in the Run or SIE mode. The BKPT indicator is extinguished by setting the BKPT switch to the CLR position.

#### 3.4 MEMORY INITIALIZATION

Memory initialization is performed following power turn on if memory refresh has been lost. Memory loss is signified when the PWR LOSS indicator is lighted. The memory initialization routine writes into every memory location to eliminate parity errors caused by the power loss. Interrupts are masked during initialization to prevent internal interrupt traps.

The routine to initialize memory is loaded into memory by the ROM bootstrap logic from the Control Panel ROM. The following procedure loads and executes the initialize routine.

- Depress RESET switch

- Set PC =  $000F_{16}$ , the entry point for the initialization routine

- Set the Mode switch to the RUN position (upward)

- Activate the LOAD switch to the momentary up position

- Initialization is now complete. An idle instruction is placed in each location by the routine (CE00<sub>16</sub>).

#### 3.5 ROM BOOTSTRAP OPERATION

**Memory Location**

The ROM bootstrap loader moves 256 words of Read-Only memory (ROM) into CPU memory starting at memory location  $0000_{16}$ . The bootstrap library contains basic routines used to initiate data input operations from the standard input peripherals. The input data from the peripherals usually is a relocating loader for control of system or diagnostic entry.

3.5.1 BOOTSTRAP INDEX. The first 16 locations of memory, following the bootstrap library, contain a jump for each standard peripheral device. The selected jump instruction transfers program control to the desired bootstrap program. The list below associates the memory locations with their device routines.

Device

| nory Eccution | Device                                                          |

|---------------|-----------------------------------------------------------------|

| 0             | Model 31, 33, or 44 Diablo Moving-head disc                     |

| 1             | DDC Fixed-head disc                                             |

| 2             | 800/1600 Magnetic tape                                          |

| 3             | Card Reader                                                     |

| 4             | High-speed paper-tape reader                                    |

| 5             | Teletype reader                                                 |

| 6             | ASR 733 and Teletype reader with communication module interface |

| 7             | DS330 Disc system*                                              |

| 8 to E        | Left for further expansion                                      |

| F             | Store idles to all of memory                                    |

| *DG220 :      |                                                                 |

<sup>\*</sup>DS330 is present only in the special ROM shipped with systems shipped with a DS330 Disc System.

The selected bootstrap program is relocated by the program to end at location  $87_{16}$  and it enters data from the device beginning at location  $88_{16}$ . The program expects the length to be the 12th input word that is read into location  $93_{16}$ .

- 3.5.2 BOOTSTRAP OPERATING PROCEDURE. The following procedure enters the bootstrap, starts bootstrap execution and initiates the data input from the selected peripheral device.

- Ready the (loader) program media in the desired I/O device

- Reset the computer

- Select the Run mode

- Put the memory location assigned to the desired bootstrap in the PC (e.g., PC=0005<sub>16</sub> for teletypewriter)

- Toggle the Load switch (up)

- After the program media is loaded, the machine enters the idle mode.

#### 3.6 CONTROL CONSOLE CHARACTERISTICS

The Control Console assembly consists of a printed-circuit board assembly, a panel symbolized with control and indicator identification and a trim frame. All console electrical components, switches, and indicators are mounted on the printed circuit board which has two 80-pin, bottom-edge, connectors. The entire console assembly is installed in card connectors XA1P1 and XA1P2. Except for +5 volts and ground, all system interconnections are completed using wire wrap connections on the back panel. The trim frame is aligned to a cutout in the chassis front panel when the control console assembly is properly installed.

#### **SECTION IV**

#### THEORY OF OPERATION

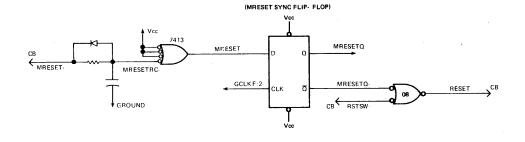

#### 4.1 POWER SUPPLY MASTER RESET AND POWER OFF

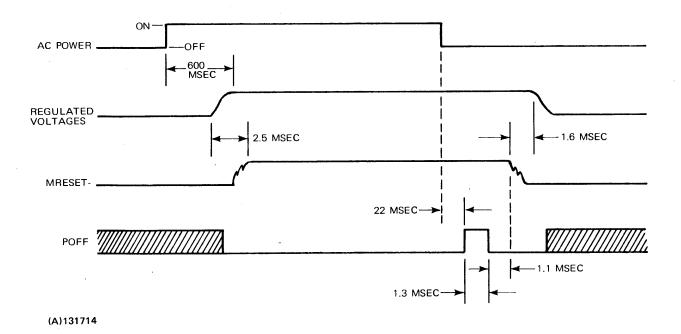

The Central Processor Unit (CPU) power supply outputs two signals to the system to indicate the condition of system power.

Signal timing is shown in figure 4-1. The times that are listed in this figure are approximate; because, times are affected by factors such as ac line voltage and power supply loading. However, the sequence of signal transitions always occurs as shown in the diagram.

The master reset signal (MRESET—) is switched to ground when any regulated supply voltage is below tolerance. When system ac power is turned on, the supply voltages reach the regulated level in approximately 600 milliseconds. The MRESET— circuit opens 2 to 3 milliseconds after the +5 Volt supply starts to rise from zero volt. When the circuit opens, all voltages reach regulated levels. When high, the MRESET— signal is connected through a 100 ohm resistor to +5 Volts.

Figure 4-1. MRESET- and POFF Signal Timing

#### NOTE

The transitions in MRESET— contain noise caused by relay contact bounce in the 980A computer power supply. This noise is removed by filters in the AU where MRESET— is used. A transistor switch replaces the relay in the 980B power supply.

When ac power is turned OFF, MRESET remains high until approximately 16 milliseconds before the regulated supply voltages begin to fall.

The second status signal from the power supply is power off (POFF). The POFF signal is generated when ac power is turned OFF, or when an ac power interruption of sufficient duration occurs to cause loss of regulation. The POFF signal is generated by logic circuits; therefore, the state of POFF is undefined until the supply voltages approach regulated levels. At ac power turn on, POFF settles to a logic ZERO level before MRESET— goes high. When ac power is interrupted, POFF goes to a logic ONE level within 20 to 24 milliseconds after the interruption occurs. The POFF signal remains at a logic ONE level for approximately 1.3 milliseconds and returns to a ZERO level approximately 1.1 milliseconds before MRESET— goes low. The leading edge of the POFF signal causes an internal interrupt in the AU and the trailing edge halts program execution by clearing the run flip-flop. The 1.3 millisecond duration of POFF provides sufficient time to execute an interrupt service routine that is designed to prepare the system for the imminent power failure.

#### 4.2 AU CLOCK SOURCE AND DISTRIBUTION

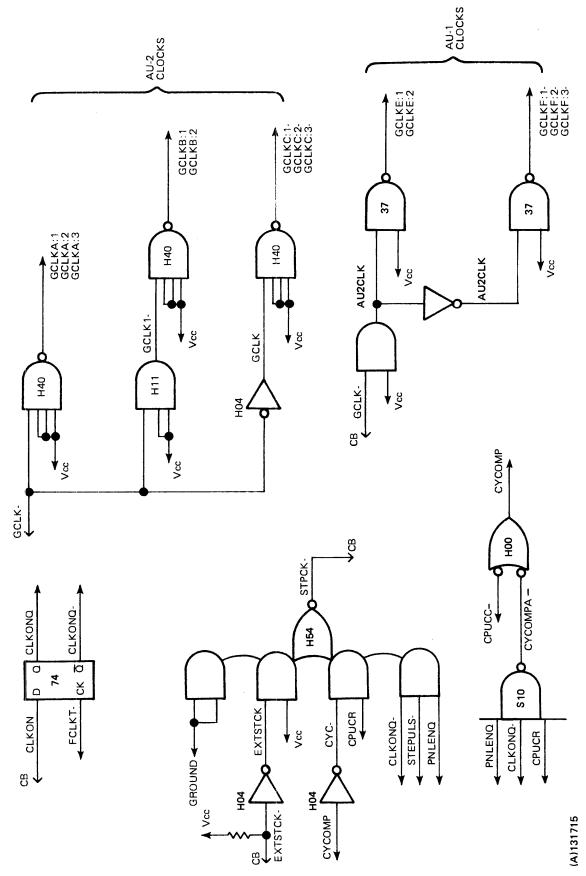

4.2.1 CLOCK SOURCE SIGNALS. The memory controller board in the CPU generates two separate clock signals for use by the computer system. (Figure 4-2 shows the clock control and clock distribution logic.) The first and most widely used clock signal by the AU is called GCLK—. The GCLK— signal is high for 167 nanoseconds and low for 83 nanoseconds to consume a total period of 250 nanoseconds. This GCLK— clock signal can be interrupted by several conditions. When interrupted, GCLK— remains in a high state as long as these conditions exist.

A STPCK— signal is generated by the AU and is sent to the memory controller as an indication that GCLK— must be stopped. The STPCK— signal stops GCLK— if any one of three conditions exist. The first condition exists when the AU or API has requested a memory cycle with CPUCR— and the memory controller has not sent back the cycle complete signal, CPUCC—. The second condition exists when the AU is in the Step clock mode. When the console signal CLKON is low and the panel is unlocked, GCLK— is stopped. In this state, a single clock pulse is enabled when the momentary STEP position of the CLOCK switch is activated on the console. The signal STEPULS—, which is a synchronous 250-nanosecond pulse, is generated by the control console enabling this clock pulse. A third input signal is available to permit special user conditions to stop GCLK—. The signal EXTSTCK— is available at the bottom edge connector of AU-1 for special use.

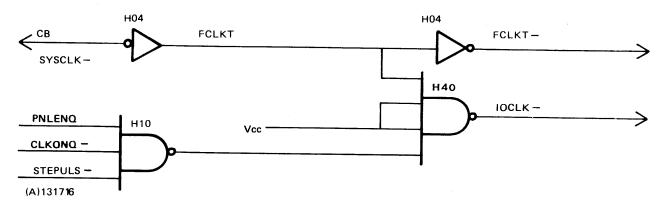

The second system clock source signal is SYSCLK—. This clock signal has the same waveform as GCLK—; however, SYSCLK— is used for system logic which cannot have clock interruptions for the same conditions which interrupt GCLK—.

The clock distribution logic minimizes skew by assuring that the clock pulse presented to each flip-flop is delayed by the same number of gate propagations from the primary system clock GCLK—.

4.2.2 BUFFERED AU CLOCK SIGNALS. As shown in figure 4-2, there are three types of buffered clock signals used on AU-2. All three of these clock signals are derived from GCLK—. The first type (GCLKA:1, 2, and 3) is generated for use with NAND gates which enable False clocks to trigger positive edge triggered devices. The second type (GCLKB:1 and 2.) is a True clock that is used to trigger negative-edge triggered devices which do not have enable gates. The third type (GCLKC:1-2- and 3-) is a False clock that is used to trigger, positive edge, triggered devices which also do not have enable gates.

The AU-1 logic board uses two types of buffered clocks that are derived from GCLK—. The first type (GCLKE:1 and 2) is used for the same functions as GCLKA:1 and GCLKB:1. The second type is used for the same functions as GCLKC:1. The SYSCLK— signal has limited use on AU-1. The SYSCLK— signal buffering is shown in figure 4-3 as FCLKT and FCLKT—. Signal IOCLK— is buffered SYSCLK— conditioned by STPIOCLR— and distribution to the I/O bus system.

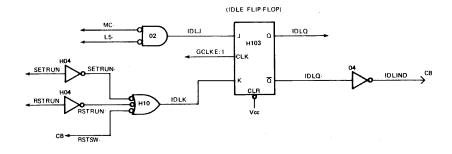

#### 4.3 RUN FLIP-FLOP

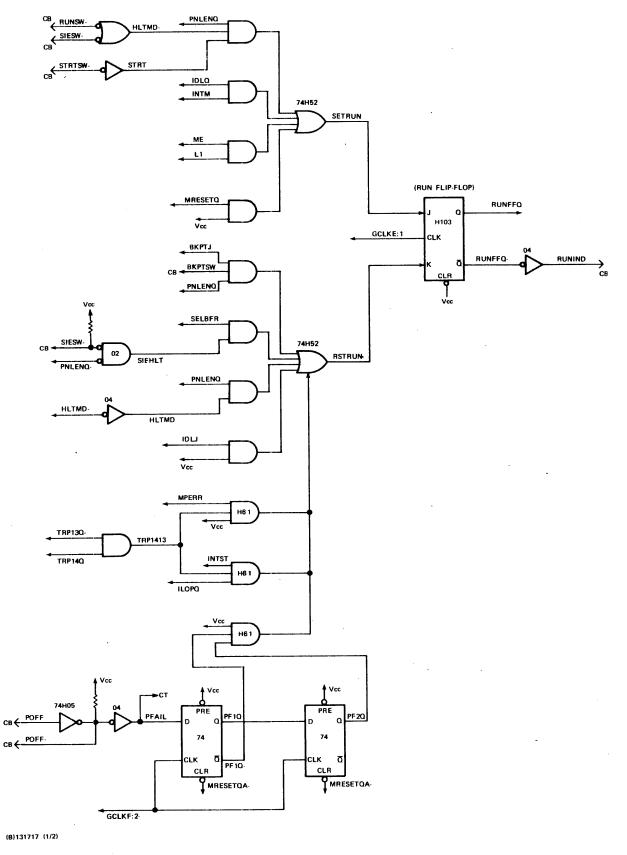

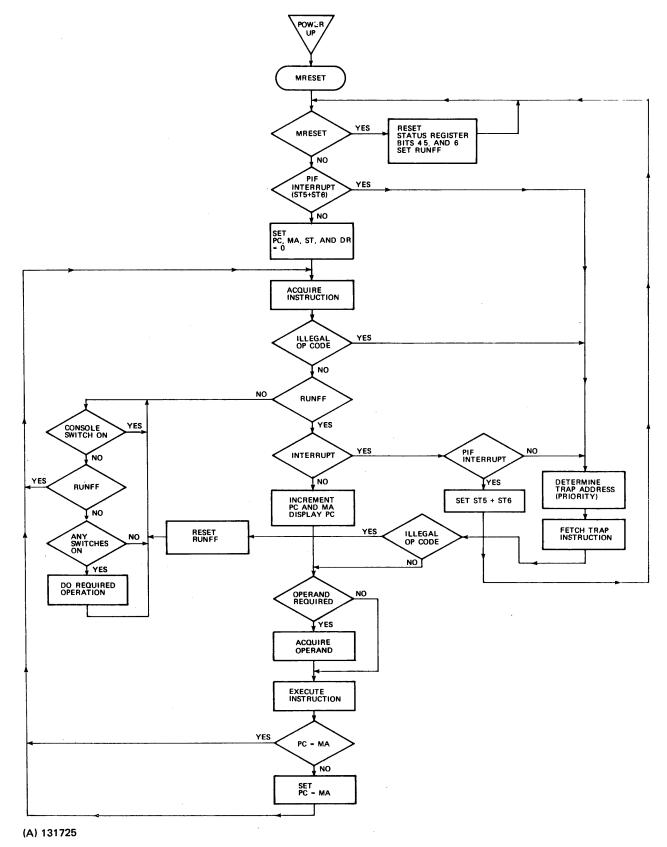

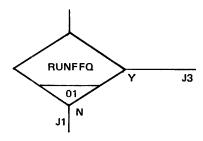

- 4.3.1 FUNCTION. The RUN flip-flop acts as a flag that indicates to the AU control logic whether to execute the next instruction in a program or to halt the computer. While the AU is executing instructions, the control logic checks the RUN flip-flop (RUNFFQ) before each instruction is executed. If the RUN flip-flop is set, the AU continues execution. If the RUN flip-flop is reset during an instruction, the AU finishes executing that instruction and then halts. If the AU is in the Halt mode, the control logic also checks the RUN flip-flop. If the RUN flip-flop is set, the AU enters the Run mode and initiates instruction execution. The state of the RUN flip-flop is also used to generate the RUN indicator signal (RUNIND) for the control console. A logic drawing of the RUN flip-flop with associated set and reset logic is shown in figure 4-4.

- 4.3.2 **SET CONDITIONS.** There are five system conditions which set the RUN flip-flop. The first set condition occurs each time system ac power is turned on, and the power supply master reset signal (MRESET—) goes to a logic Zero. The MRESET— is synchronized and sensed by the RUN flip-flop steering logic as MRESETQ. This condition causes the AU to initially come up in the Run mode when ac power is applied. However, if the MODE switch on the front panel is in the HALT position, the run condition is not maintained.

The second set condition occurs when the front panel bootstrap loader function is activated. State El<sub>16</sub> is used in the microsequence to transfer the ROM loader programs into memory. This state is decoded as ME and Ll to set the RUN flip-flop. This function is accomplished to permit the AU to enter the Run mode and execute the loader programs after these programs have been entered into memory.

The third set condition exists when the AU is in the halt mode due to IDL instruction execution and an enabled interrupt is requested. When these conditions exist, the AU can be removed from the idle condition (Halt mode) because of an interrupt.

The fourth and fifth set conditions are accomplished by use of the control console. If the AU is in the halt mode (either idle or normal halt) and the PANEL switch is in the UNLOCK position, the run mode may be entered by use of the front panel MODE and START switches. If either the RUN or SIE (single instruction execution) position of the MODE switch is selected and the momentary START switch is activated, the RUN flip-flop is set.

Figure 4-2. Clock Control and Distribution Logic

Figure 4-3. SYSCLK- Distribution

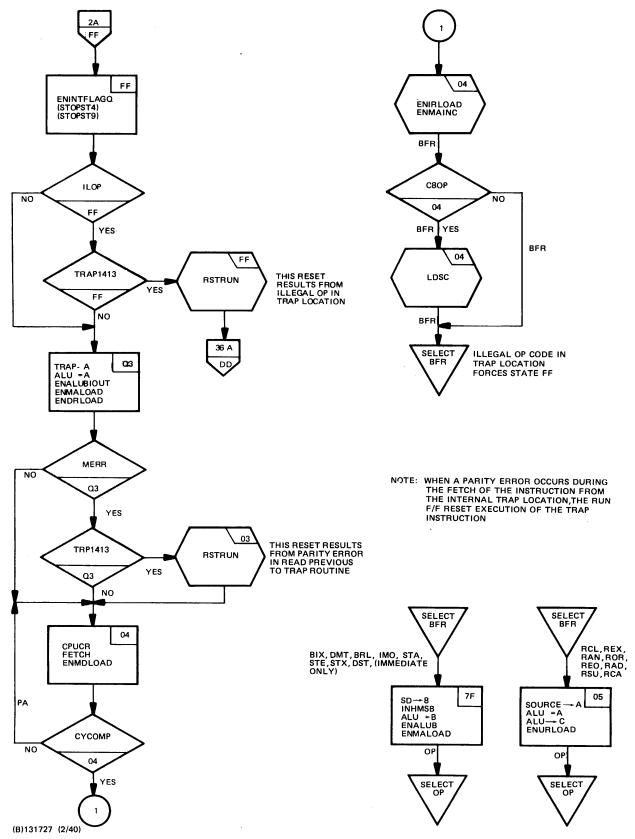

4.3.3 RESET CONDITIONS. There are seven system conditions which reset the RUN flip-flop. The first reset condition occurs each time power is turned off. A power supply power failure signal (POFF) interrupts the AU when power is about to be lost. The trailing edge of this power failure signal is sensed to reset the RUN flip-flop. This action halts the computer. All power failure interrupts must be processed before this action occurs.

The second reset condition occurs when an illegal instruction is detected in the internal interrupt trap location.

The third reset condition occurs when a parity error is detected in the internal interrupt trap location. Also, if an interrupt trap occurs (i.e., because of an address violation or instruction violation) and the previous memory read detected a memory parity error, then the RUN flip-flop is reset.

For the second and third reset conditions, when the AU has sequenced through the interrupt trap state ( $FF_{16}$ ), the trap address is for internal interrupts ( $0002_{16}$ ), and an illegal instruction or memory parity error is detected, the RUN flip-flop is reset.

The fourth reset condition occurs when an IDL instruction is executed by the AU. The RUN flip-flop is reset when the AU sequences through the IDL state.

The fifth reset condition occurs when the control console MODE switch is in the HALT (center) position and the PANEL switch is in the UNLOCK position.

The sixth reset condition occurs when the AU is in the SIE mode and instruction execution starts. If the SIE position of the MODE switch is selected with the panel enabled, the RUN flip-flop is reset when the SELBFR signal is generated at the beginning of instruction execution. The machine halts after executing the single instruction.

The seventh reset condition occurs when the breakpoint switch is in the BKPT position. When the BKPT switch is set and the memory address register content is equal to the panel switch settings during an instruction memory cycle, the RUN flip-flop is reset and the machine halts if the panel is unlocked.

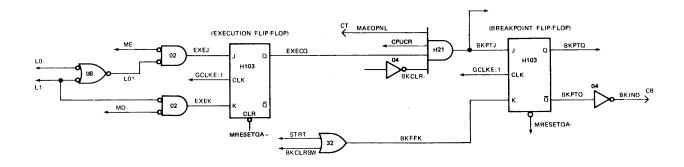

4.3.4 ASSOCIATED LOGIC. The breakpoint flip-flop is controlled by control console and AU breakpoint conditions. The panel switch settings (PNL0 $\rightarrow$ 15) and AU memory address contents (MAR0-15) are compared by four 4-bit comparators (SN7485's) on the AU-2 board. When these data words are equal, the signal MAEQPNL is generated and sent to the breakpoint logic on AU-1.

Figure 4-4. Run Flip-Flop Logic Diagram (Sheet 1 of 2)

Figure 4-4. Run Flip-Flop Logic Diagram (Sheet 2 of 2)

#### 4.4 BUS STRUCTURE AND REGISTERS

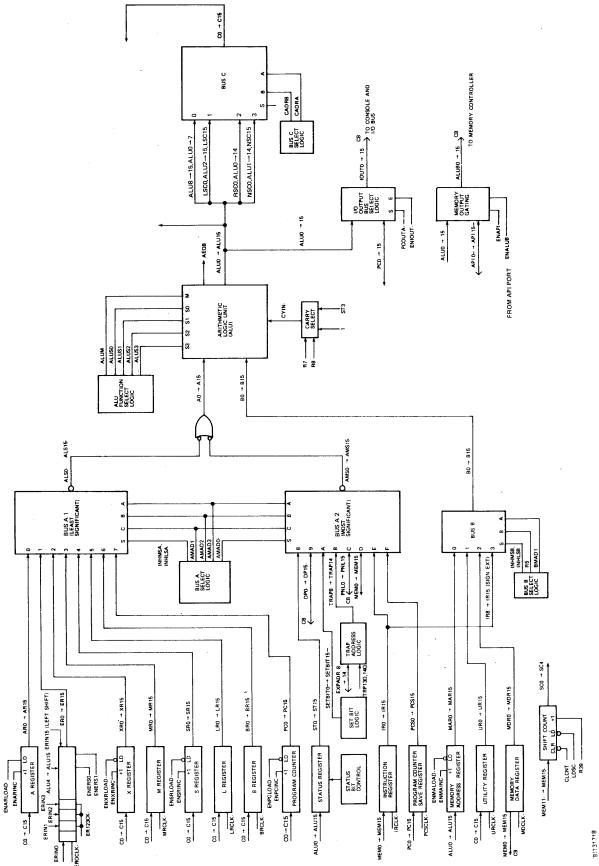

The Arithmetic Unit (AU) functional diagram with data paths and registers is illustrated in figure 4-5. The data path and registers are primarily implemented on the AU-2 board. The AU has three major data selectors or data buses. Two of the buses (data bus A and data bus B) supply 16-bit data to the Arithmetic Logic Unit (ALU). The ALU performs arithmetic or logical processing of data on data bus A and data bus B. The third bus (data bus C) allows the output bits of the ALU to be shifted or interchanged when processing shift, rotate, or byte instructions. The data bus C lines are returned to the necessary registers as illustrated in figure 4-5.

4.4.1 DATA BUS A. Data bus A is a 16 to 1 data bus that is implemented with two sets of 8 to 1 selectors (SN74151). The respective bit outputs of each pair of 8 to 1 selectors (A1 and A2), are OR'd as illustrated in figure 4-5. The selectors are controlled by bus A select logic that supplies select address lines to the selectors using ROM output bits. Table 4-1 lists the selector output for each select address. The A1 selectors permit portions of the inputs to be enabled to the bus (i.e., A1 output can be the most significant half (MSH) of selected input (bits 0-7) or least significant half (LSH) of selected input (bits 8-15). The A1 selectors can also be all enabled or inhibited.

Several data bus A selector inputs do not originate at the registers. The bus A selector input to pin number 9 (DP0-DP15-) is the input data to the CPU from the I/O Bus. The bus A selector input A (SETBIT0-SETBIT15-) originates in the set bit logic and is utilized during the set bit instruction. Trap address logic provides a trap address for interrupts to bus A selector input B. Bus A selector input C (PNLO-PNL15) originates at the control console data switches and is used to manually enter data into the CPU. Bus A selector input D (MEMO-MEM15) is the memory data output lines from the memory controller.

- 4.4.2 DATA BUS B. Data bus B is a 4 to 1 data bus that is implemented with 4 to 1 selectors (SN74153). Bus B select logic derives select addresses from ROM output bits. Table 4-2 lists the data selected for each bus B select address.

- 4.4.3 DATA BUS C. Data bus C is a 4 to 1 data bus that is implemented with 4 to 1 selectors (SN74153). Bus C select logic derives select addresses from ROM output bits. Table 4-3 lists the data selected for each bus C select address. The bus C logic allows the ALU outputs to be bit shifted or byte exchanged.

- 4.4.4 OTHER SELECTORS. Two remaining selectors are also shown in figure 4-5. An I/O output data bus selector allows the Program Counter (PC) or the ALU output to be selected to the console and I/O bus. The control console and I/O device controllers receive data from the CPU on this bus.

A second selector allows the memory controller to receive memory input data from the CPU or Auxiliary Processor Port (APP).

4.4.5 ARITHMETIC LOGIC UNIT. The Arithmetic Logic Unit (ALU) performs arithmetic and logic processing of data from bus A and bus B. The ALU consists of 4-bit arithmetic units (SN74S181) and look-ahead carry generators (SN74182). The ALU control signals in figure 4-5 are ROM generated. Functions for various ALU control signal combinations are listed in table 4-4. The ALU outputs are bus C selector inputs and shift signals which allow bit shifts.

Digital Systems Division

Figure 4-5. AU Functional Block Diagram

Table 4-1. Data Bus A Selection

|                     | Function                                                                    | Select                                                          |                                 |           |                |                         |       | ıput Sig  | mals Selo | Input Signals Selected as Outputs (AO→A15)                                                                                                            | ıtputs (A               | 0→A15                                       |                           |                                 |                                |                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|-----------|----------------|-------------------------|-------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------|---------------------------|---------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus                 | Selected                                                                    | S <sub>X</sub> C B A                                            | Α0                              | <b>A1</b> | A2             | A3 A                    | A4 A5 | <b>46</b> | A7        | <b>A8</b>                                                                                                                                             | A9                      | A10 A                                       | A11 /                     | A12 A13                         | 3 A14                          | A15                                                                                                                                                                                                             |

|                     | $AR \rightarrow A$ $ER \rightarrow A$ $XR \rightarrow A$ $MP \rightarrow A$ | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         | ARO<br>ERO<br>XRO               |           |                |                         |       |           |           |                                                                                                                                                       |                         |                                             |                           |                                 |                                | AR15<br>ER15<br>XR15                                                                                                                                                                                            |

| A1                  | SR-A<br>LR-A<br>BR-A<br>PC-A                                                | 0 1 0 0 0 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1                         | MRO<br>SRO<br>LRO<br>BRO<br>PCO |           |                |                         |       |           |           |                                                                                                                                                       |                         |                                             |                           |                                 |                                | MR15<br>SR15<br>LR15<br>BR15<br>PC15                                                                                                                                                                            |

|                     | ST→A<br>DP→A<br>SETBIT→A                                                    | S <sub>y</sub> C B A 0 0 0 0 0 0 0 1 0 0 1 0                    | ST0<br>DP0-<br>SETBIT0-         |           |                |                         |       |           |           |                                                                                                                                                       |                         |                                             | ž                         | ST12 0                          | ST14                           | ST15<br>DP15-<br>SETBIT15-                                                                                                                                                                                      |

| A2                  | TRAP→A<br>PNL→A<br>MEM→A<br>IR→A<br>PCS→A                                   | 0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0<br>0 1 1 1             | 0 PNL0 MEM0 IR0 PCS0            |           |                |                         |       |           | 0         | TRAP8                                                                                                                                                 |                         |                                             |                           |                                 | TRAP14                         |                                                                                                                                                                                                                 |

|                     | BUS A1 E                                                                    | BUS A1 ENABLES A1 SELECT ENABLE                                 | SNABLE                          | BUS<br>Sy | BUS A2 ENABLES | NABLES<br>ACTION        |       | NO        | NOTES:    | 1. SELEC                                                                                                                                              | CT ADDI<br>S I<br>C I   | RESS DI<br>R1 (I<br>R2-                     | ERIVE                     | D FROM<br>o tables              | l FOLLOV<br>shown for          | <ol> <li>SELECT ADDRESS DERIVED FROM FOLLOWING ROM BITS</li> <li>R1 (Refers to tables shown for logical values of R1)</li> <li>R2-</li> </ol>                                                                   |

| SMSH<br>0<br>0<br>1 | SLSH<br>0<br>1<br>1                                                         | ENABLE A1<br>ENABLE MSH OF A1<br>ENABLE LSH OF A1<br>INHIBIT A1 | H OF A1<br>I OF A1              | 0 1       | EN             | ENABLE A2<br>INHIBIT A2 | 2 0   |           |           | B R3– A R4– 2. SELECT ADDRESS SIGNAL "SX" IS II MOST SIGNIFICANT HALF, LEAST SIGN HALVES OF FIRST 8 REGISTERS TO BE Sy IS EITHER ENABLED OR DISABLED. | B 1 A 1 CT ADDE GNIFICA | R3-<br>R4-<br>RESS SI<br>ANT HA<br>&ST 8 RI | GNAL<br>ALF, LI<br>EGISTE | "SX" IS<br>EAST SIG<br>RRS TO I | IMPLEM<br>GNIFICAI<br>BE SELEC | B R3- A R4- 2. SELECT ADDRESS SIGNAL "SX" IS IMPLEMENTED TO ALLOW MOST SIGNIFICANT HALF, LEAST SIGNIFICANT HALF, OR BOTH HALVES OF FIRST 8 REGISTERS TO BE SELECTED TO BUS A. Sy IS EITHER ENABLED OR DISABLED. |

Table 4-2. Data Bus B Selection

| FUNCTION      | _ | LECT |        |             |          |    | INP   | UT SI | GNAL | S SEI  | ECTI     | ED AS | OUT | PUTS (I |     |     |     |     |               |

|---------------|---|------|--------|-------------|----------|----|-------|-------|------|--------|----------|-------|-----|---------|-----|-----|-----|-----|---------------|

| SELECTED      | S | В    | Α      | В0          | B1       | В2 | В3    | В4    | В5   | В6     | В7       | В8    | В9  | B10     | B11 | B12 | B13 | B14 | B15           |

| MAR→B<br>UR→B | 0 | 0    | 0      | MAR0<br>UR0 | <b>+</b> |    |       |       |      |        |          |       |     |         |     |     |     | -   | MAR15<br>UR15 |

| MRD→B<br>IR→B | 0 | 1    | 0<br>1 | MDR0<br>IR0 | -        | IR | 8 SIG | N EXT | ENDE | D<br>I | <b>-</b> | IR8   | 4   |         |     |     |     | 1   | MDR15<br>IR15 |

NOTE: SELECT ADDRESS DERIVED FROM ROM BITS R5 AND R6.

S = INHLSB

$A = BMA01 = RGT (IR5 \cdot IR6 \cdot IR7 \cdot R51)$

B = R5

4.4.6 PROGRAM COUNTER AND SAVE REGISTERS. The Program Counter (PC) is a 16-bit register that normally contains the address of the next instruction. The PC consists of 4-bit synchronous counters (SN74163). These counters can be parallel loaded with ALU output data or can be incremented. The load function is controlled by ROM control (ROM bit 42) or by logic that detects selection of the PC as a source or destination in a register to register instruction.

The output of the PC is one of the bus A selector inputs and is also an input to the Program Counter Save Register (PCS).

The PCS is an internal register that cannot be accessed by the programmer. The CPU utilizes the PCS for temporary storage during a store status block instruction. The PCS consists of D type flip-flops (SN74174). The control ROM generates the PCS clock and the PCS output is an input to the bus A selector.

- 4.4.7 INSTRUCTION REGISTER. The Instruction Register (IR) is a 16-bit register that retains the current instruction the CPU is executing. The IR consists of four registers (SN74175) that are loaded by the ROM generated IR clock with data from the memory output lines. Bus A selector and bus B selector inputs are supplied by the IR.

- 4.4.8 ARITHMETIC REGISTER. The primary arithmetic register or A Register (AR) is a 16-bit register that uses program control for add, subtract, AND, OR, and other functions. The AR consists of 4-bit counters (SN74163) which can be incremented, or parallel loaded with bus C data. Load and increment signals are generated by the control ROM. The AR output is connected to the bus A selector.

- 4.4.9 SECONDARY ARITHMETIC REGISTER. The secondary arithmetic register or E Register (ER) is a 16-bit register that utilizes program control to extend the A register for multiply, divide, and other functions. The ER consists of 4-bit shift registers (SN74194) for ER bits 4 through 15. Bits 0 through 4 are implemented with D type flip-flops and logic gates to handle register shift and arithmetic instructions that utilize ER and other registers. The ER has several clocks which are used for different parts of the ER. The ROM bits 28 through 34 control the operation of the ER.

Table 4-3. Data Bus C Selection

|                     |          | C15      | ALU<br>7          | LSC<br>15      | ALU<br>14      | NSC<br>15  |

|---------------------|----------|----------|-------------------|----------------|----------------|------------|

|                     |          | C14      | ALU<br>6          | ALU<br>15      | ALU<br>13      | ALU<br>14  |

|                     |          | C13      | ALU<br>5          | ALU<br>14      | ALU<br>12      | ALU<br>13  |

|                     |          | C12      | ALU<br>4          | ALU<br>13      | ALU<br>12      | ALU<br>12  |

|                     |          | CIII     | ALU<br>3          | ALU<br>12      | ALU<br>10      | ALU<br>11  |

| (C0-C15)            |          | C10      | ALU<br>2          | ALU<br>11      | ALU<br>9       | ALU<br>10  |

| Bus C               |          | හ        | ALU<br>1          | ALU<br>10      | ALU<br>8       | ALU<br>9   |

| Selected As Outputs |          | జ        | ALU<br>0          | ALU<br>9       | ALU<br>7       | ALU<br>8   |

| Selected A          |          | C2       | ALU<br>15         | ALU 8          | ALU<br>6       | ALU<br>7   |

| Signals             | •        | <b>9</b> | ALU<br>14         | ALU<br>7       | ALU<br>5       | ALU<br>6   |

| Input               | •        | ೮        | ALU<br>13         | ALU<br>6       | ALU<br>4       | ALU<br>5   |

|                     |          | 2        | <b>AL</b> U<br>12 | ALU<br>\$      | ALU<br>3       | ALU<br>4   |

|                     |          | ខ        | ALU<br>11         | ALU<br>4       | ALU<br>2       | ALU<br>3   |

|                     |          | S        | ALU<br>10         | ALU<br>3       | ALU<br>1       | ALU<br>2   |

|                     |          | C1 C2    | ALU ALU<br>9 10   | ALU ALU<br>2 3 | ALU ALU<br>0 1 | ALU ALU    |

|                     |          | 2        | ALU8              | LSC0           | RSC0           | NSC0       |

| Select<br>Address   |          | S B A    | 0 0 0             | 0 0 1 LSC0     | 0 1 0 RSC0     | 0 1 1 NSC0 |

|                     | Function | Selected | CIR8-C            | LSHIFT-C       | RSHIFT-C       | ALU-C      |

Notes:

Select address derived from the following:

S Logic 0

B CADRB = R16-\*DIVIT-\*BYTESHFTA CADRA = R17-\*MPYIT-\*BYTESHFT-

Table 4-4. Arithmetic Logic Functions

|          |       |       |       |                                      | AT IT DINOTION                   |                                         |

|----------|-------|-------|-------|--------------------------------------|----------------------------------|-----------------------------------------|

|          |       |       |       | - ,, ,, T                            | ALU FUNCTION                     | ODED ACTIONS                            |

|          | SELEC | CTION |       | M = H<br>LOGIC                       | M=L; ARITHMETIC (                | PERATIONS                               |

| $ s_3 $  | $s_2$ | $s_1$ | $s_0$ | FUNCTIONS                            | CYIN = 0                         | CYIN = 1                                |

| <u> </u> |       |       |       |                                      |                                  |                                         |

| L        | L     | L     | L     | $\mathbf{F} = \overline{\mathbf{A}}$ | F = A                            | F = A PLUS 1                            |

| L        | L     | L     | Н     | $F = \overline{A + B}$               | F = A + B                        | F = (A + B) PLUS 1                      |

| L        | L     | Н     | L     | $F = \overline{A}B$                  | $F = A + \overline{B}$           | $F = (A + \overline{B}) PLUS 1$         |

| L        | L     | Н     | Н     | F = 0                                | F = MINUS 1 (2's COMPL)          | F = ZERO                                |

| L        | Н     | L     | L     | $F = \overline{AB}$                  | $F = A PLUS A\overline{B}$       | F = A PLUS AB PLUS 1                    |

| L        | Н     | L     | Н     | $\mathbf{F} = \overline{\mathbf{B}}$ | $F = (A + B) PLUS A\overline{B}$ | $F = (A + B) PLUS A\overline{B} PLUS 1$ |

| L        | Н     | Н     | L     | $F = A \oplus B$                     | F = A MINUS B MINUS 1            | F = A MINUS B                           |

| L        | Н     | Н     | Н     | $F = A\overline{B}$                  | $F = A\overline{B} MINUS 1$      | $F = A\overline{B}$                     |

| Н        | L     | L     | L     | $F = \overline{A} + B$               | F = A PLUS AB                    | F = A PLUS AB PLUS 1                    |

| Н        | L     | L     | Н     | $F = \overline{A \oplus B}$          | F = A PLUS B                     | F = A PLUS B PLUS 1                     |

| Н        | L     | Н     | L     | F = B                                | $F = (A + \overline{B}) PLUS AB$ | $F = (A + \overline{B}) PLUS AB PLUS 1$ |

| Н        | L     | Н     | Н     | F = AB                               | F = AB MINUS 1                   | F = AB                                  |

| Н        | Н     | L     | L     | F = 1                                | F = A PLUS A*                    | F = A PLUS A PLUS 1                     |

| Н        | Н     | L     | Н     | $F = A + \overline{B}$               | F = (A + B) PLUS A               | F = (A + B) PLUS A PLUS 1               |

| Н        | Н     | Н     | L     | F = A + B                            | $F = (A + \overline{B}) PLUS A$  | $F = (A + \overline{B})$ PLUS A PLUS 1  |

| Н        | Н     | Н     | Н     | F = A                                | F = A MINUS 1                    | F = A                                   |

<sup>\*</sup>Each bit is shifted to the next more significant position.

- 4.4.10 BASE, LINK, AND MAINTENANCE REGISTERS. The Base Register (BR), Link Register (LR), and Maintenance Register (MR) are 16-bit registers under program control that are implemented with SN74174 registers. The MR is used for temporary storage. The LR is used to hold return address for subroutine linkage. The BR is used to hold base addresses for BR related instructions. These three registers are loaded utilizing ROM control.

- 4.4.11 STORAGE REGISTER. The Storage Register (SR) is also used for temporary data storage under program control. The SR is implemented with SN74163 counters. This register can be parallel loaded with bus C data or incremented during byte instructions. Load and increment signals for the SR are ROM generated.

- 4.4.12 INDEX REGISTER. The Index Register (XR) is a 16-bit register under program control that is used during indexed instructions. The XR uses ROM generated control signals and is also implemented with SN74163 counters.

4.4.13 STATUS REGISTER. The Status Register (ST) is a 15-bit register that consists of individual flip-flops. The contents of the ST are used to indicate program and machine status. Five ROM outputs (R23 through R27) control the ST. Outputs R23, R24, and R25 are decoded into seven clock enable signals by an SN7442 4 to 10 line decoder. The remaining two ROM outputs are used for separate clock enable signals. Parallel loading of the ST with ALU data is accomplished with load status instructions or by console operation. Individual bits are set or reset by program or machine condition changes. Status Register bits 0 (ST0) and 1 (ST1) function as comparison indicators to indicate the result of the last compare operation as listed in table 4-5.

Additionally the Auxiliary Processor Port (APP) has access to these bits and can set the state of these bits if the APP external controller requires such action.

The STO and ST1 bits are implemented with D type flip-flops with appropriate steering logic for the D input and clock. The compare condition is gated to the D input by an enable signal from the decoder that is described in previous paragraphs. The ROM control is used to enable clock signals to the flip-flop.

Status register bit 2 is the overflow indicator that is turned on or off by instructions which cause overflow. The ST2 bit is implemented with a D type flip-flop and steering logic for the D input and clock. The ST2 bit is set during certain arithmetic shift, two's-complement, left shift, multiply, and divide instructions. The APP also has access to the ST2 bit.

Status Register bit 3 (ST3) is the carry indicator. This bit is also implemented with a D type flip-flop. The ST3 is turned on by any add, subtract, or complement instruction that results in a carry into the sign bit (bit 0) of a register. If these instructions do not result in a carry into the sign bit, the carry indicator is turned off. The carry condition is determined by logic that monitors bit 0 of the bus A and bus B and bit 0 of the sum of bus A data and bus B data at the output of the ALU. The logic equation for carry appears below utilizing bus A bit 0 (A0) and bus B bit 0 (B0), and the ALU bit 0 (ALU0) output:

Carry =

$$\overline{ALUO}(A0\overline{B0} + \overline{A0}B0) + ALUO (\overline{A0\overline{B0} + \overline{A0}B0})$$

The carry bit can also be set by an external controller utilizing the auxiliary processor port during an Auxiliary Processor Initiate (API) instruction.

Status Register bit 4 (ST4) is the Privileged Instruction and Memory Protect (PIF) control bit. If ST4 is set, any attempt to address protected memory or execute privileged instructions will cause an internal interrupt and the CPU to trap to location 2. The ST4 bit is implemented using a D type flip-flop with ROM enables on the D input and clock that allow ST4 to be loaded with ALU4. The output of ST4 is gated to the memory controller. The gate is disabled during interrupts or when an instruction is being acquired in the Single Instruct mode (SIE).

Table 4-5. ST0 and ST1 Comparison

| ST0 | ST1 | RESULTS      |

|-----|-----|--------------|

| 0   | 0   | Less than    |

| 0   | 1   | Equal to     |

| 1   | 0   | Greater than |

| 11  | 1   | Not allowed  |

Status Register bit 5 (ST5) is the PIF address violation indicator. When a program attempts to address protected memory while ST4 is set, ST5 is set and an internal interrupt occurs. The ST5 bit is implemented using a J-K flip-flop with an address violation (ADRV—) from the memory controller on the J input and status register clear (STLDCLR) on the K input.

Status Register bit 6 (ST6) is the PIF instruction violation indicator. If a program attempts to execute a privileged instruction while ST4 is set, an internal interrupt occurs. The ST6 bit is also implemented using a J-K flip-flop with the instruction violation line from the memory controller on the J-input and status register clear on the K-input. The J-input indicates an instruction violation (INSTV) without an address violation (ADRV—).

Status Register bits 7, 8, 11, and 12 (ST7, ST8, ST11, and ST12) are interrupt enables for the I/O interrupt (ST7), the external interrupt (ST8), the memory parity error interrupt (ST11) and the DMAC interrupt (ST12). These ST bits are implemented using D type flip-flops with ROM control logic.

Status Register bit 9 (ST9) is the PIF lower limit address bias enable. If this bit is set, the contents of the PIF lower limit register plus one is added to all CPU memory access addresses. The ST9 bit is implemented with a D type flip-flop and is gated before being routed to the memory controller. As with the ST4 bit, the gated control is disabled by IFLAG— during interrupt processing.

Status Register bit 10 (ST10) is the index indicator and is implemented with a D type flip-flop. When bit ST10 is set, indexing precedes indirect addressing if used. If ST10 is not set, indexing follows indirect addressing. Unless indirect addressing is used, this bit is ignored.

Status Register bit 14 (ST14) is the memory parity error indicator implemented with a J-K flip-flop. The memory parity error signal (MPERR) from the memory controller sets ST14.

Status Register bit 15 (ST15) is the power fail indicator set by the power supply approximately 1.0 millisecond before power failure occurs causing an internal interrupt. The ST15 bit is implemented with a J-K flip-flop and so is another flip-flop, PFMSKQ, associated with ST15 operation. The power fail signal (POFF) from the power supply is buffered to produce PFAIL and is applied to ST15 and another double flip-flop that supplies a one clock time reset pulse concurrent with the trailing edge of the POFF signal. This reset pulse resets the RUN flip-flop (RUNFFQ). In this buffer, a wired-OR (POFF—) allows other external power supplies (such as an external I/O chassis) to cause a power fail trap. When POFF goes high, to indicate an imminent power failure, ST15 is set which sets PFMSKQ. With PFMSKQ set, the power fail signal is inhibited from ST15 to prevent subsequent power fail traps that could occur since POFF goes low resetting RUNFFQ and halting the CPU. Approximately 1.0 millisecond, POFF goes low to reset the CPU including PFMSKQ. Now the CPU is in a reset state and loss of power can occur without harm.

4.4.14 MEMORY ADDRESS REGISTER. The Memory Address Register (MAR) is a 16-bit register that holds the address for any CPU memory accesses. The MAR is implemented both in the arithmetic unit and the memory controller since there is only one 16-line data bus (ALUB0-ALUB15) to the memory controller. This data bus must carry both the memory access addresses and memory write data.

The MAR in the AU is implemented with four SN74163 counters to permit parallel loading of ALU data and incrementing by a factor of one. The MAR control signals are also ROM generated.

- 4.4.15 UTILITY REGISTER. The Utility Register (UR) is a 16-bit register which is not program accessible. The UR, is implemented with SN74174 hex registers and is used as a temporary internal storage register during certain instructions such as some register-to-register (RR) instructions. The UR can be parallel loaded with bus C data and the UR output is a bus B selector input.

- 4.4.16 MEMORY DATA REGISTER. The Memory Data Register (MDR) is a 16-bit register that holds the memory read data (MEM0-MEM15) from the memory controller.

The MDR is implemented with SN74174 registers which are parallel loaded by the ROM control. The MDR output is one of the bus B selector inputs.

4.4.17 SHIFT COUNTER. The Shift Counter (SC) is a 5-bit counter that counts the number of shifts performed during shift, multiply, and divide instructions, to enable the various registers during the Load Register File (LRF) instruction, and to provide the proper timing sequence during Read and Write Direct Single (RDS and WDS) instructions. The SC is implemented with SN74163 counters. During multiply and divide instructions, the SC is cleared and incremented to times. This factor is arrived at by decoding  $0F_{16}$  on the counter outputs, then allowing one more count. During the LRF instructions, the SC is cleared and incremented to  $06_{16}$  (7 times). During shift instructions, the SC is loaded with one's-complement of the desired shift count. After the one's-complement is loaded, the SC is incremented to 1F to produce the correct number of shifts.

### 4.5 READ ONLY MEMORY CONTROLLER.

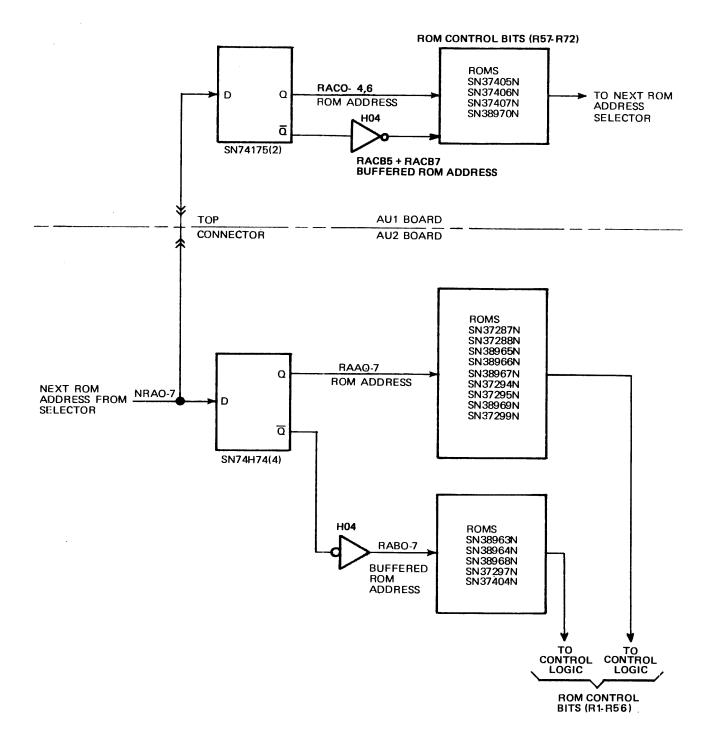

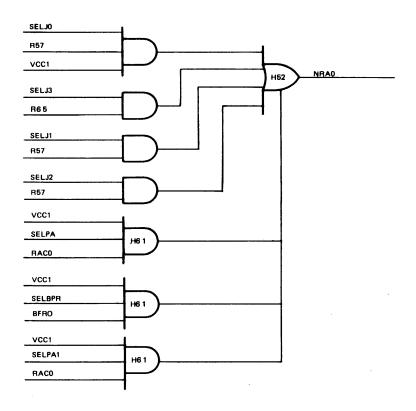

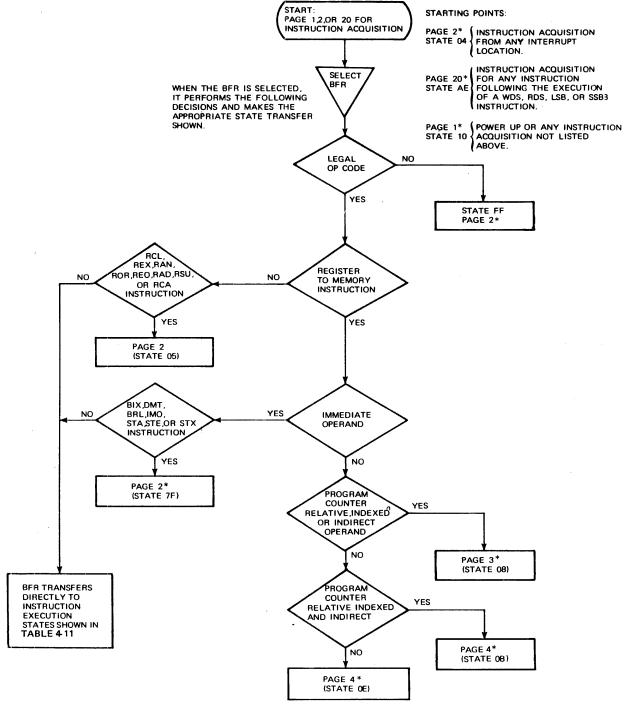

The Read-Only-Memory (ROM) controller generates basic control signals to enable data flow and logic functions in each state of the arithmetic unit microsequence. A functional block diagram of the ROM controller is illustrated in figure 4-6. Another ROM controller is the Basic Function ROM (BFR) which is discussed in Section 4.6.4.

Figure 4-6. ROM Controller Functional Diagram

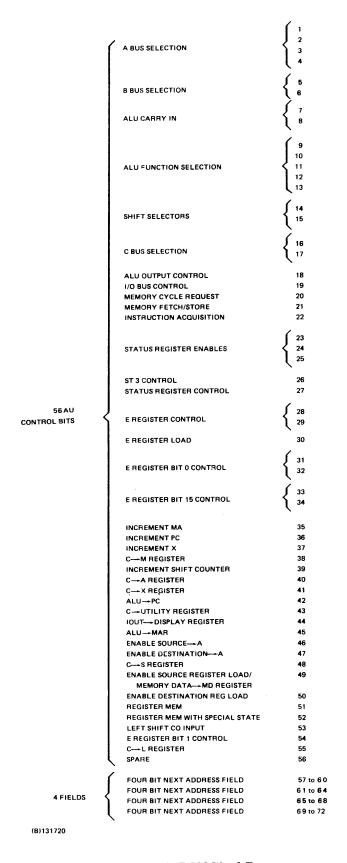

4.5.1 READ ONLY MEMORY. Read-Only-Memory (ROM) is implemented with eighteen 1024-bit Transistor-Transistor Logic (TTL) ROM's (SN74187). Each network is organized as 256 words with 4 bits in each word. The contents of each word is designed to produce the correct control signals for each AU microsequence state. The words are permanently coded in the ROM during manufacturing. The individual networks are operated in parallel to provide the ROM with 256 72-bit words. The basic ROM word format is illustrated in figure 4-7.