# Texas Instruments Model 980A Computer

## **System Characteristics**

## Copyright 1972

By

## Texas Instruments Incorporated

### All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

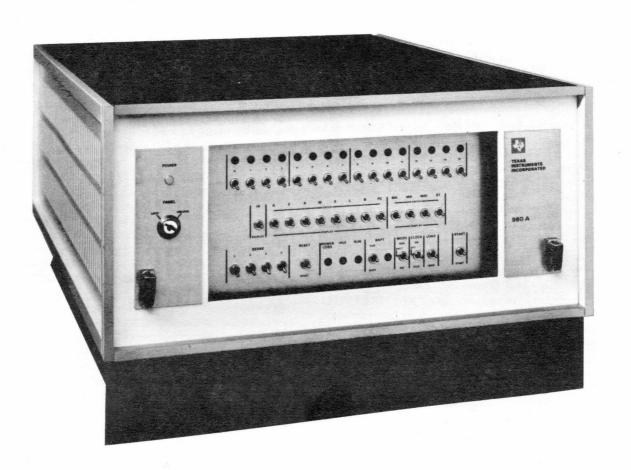

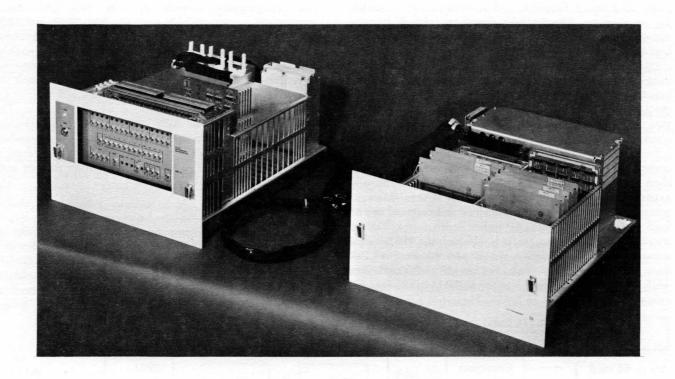

980A Processor (Extended memory chassis front panel removed for viewing)

#### **OVERVIEW**

The latest in the 900 series of digital processors from Texas Instruments is the 980A general purpose computer. The 980A is designed not only to meet today's systems needs but the future's increased operating speeds and requirements. With performance characteristics exceeding those of many larger and higher-priced computers, the 980A is a fast and powerful 16-bit computer at a low unit price which includes an extensive list of hardware and software features, built-in and standard. By optimizing the use of hardware components common with the 960A industrial control computer, TI is able to provide the 980A general purpose computer at the cost of most stripped-down competitive models. Both computers are backed by TI's worldwide sales and service organizations.

The 980A is a general purpose arithmetic machine with many of the features incorporated as standard items which are usually considered as options or accessories to this class of computer. Bootstrap loader, multiply and divide, programmable memory protection, and power fail detection and auto restart are some of the hardware features included in the basic selling price. Combining these characteristics with an effective, I/O oriented executive-type monitor, establishes the 980A as a dramatically low-cost, high-performance general purpose processor.

The 980A uses MOS semiconductor memory elements. Up to 65K words can be directly addressed by the CPU. Sockets are provided and fully wired so that memory is field expandable in modules of 4K or 8K words up to 32K words directly within the CPU. Standard with the CPU is a power supply designed to support up to 65K

words of memory. An additional 32K words of memory can be easily added to the system, external to the 32K basic CPU. Basic memory cycle time is 750 nanoseconds while instruction decode and control microsequencing executes in 250 nanoseconds. As the technology of manufacturing faster semiconductor memories is developed, these new products will be incorporated in the computer reducing the obsolesence factor and increasing its potential usefulness to the end user.

An optional, plug-in battery pack is available for the 980A which makes the semiconductor memory non-volatile. When a primary ac power failure occurs, it is detected immediately and the battery supply is switched to the memory, sustaining the memory's data contents. During power-down conditions, the battery is capable of maintaining 8K words of memory for four weeks at room temperature.

Although the 980A is a general purpose, I/O Bus structured computer, it shares many characteristics of the Model 960A computer. Where the 960A is designed primarily for interfacing with the control of external devices by efficient bit manipulation, the 980A incorporates hardware features and software support to allow bit/byte/word/or byte string manipulation. The difference between the two computers is established by the problems each is intended to solve. The 960A provides a cost-effective mechanism by virtue of its dual processor architecture and the Communications Register Unit (CRU) for interfacing and operating other machinery as a system. The 980A combines the arithmetic features, speed, and flexibility to provide a profitable solution to the class of jobs involving data processing and manipulation. TI supports both computers in a hierarchial and distributive multiprocessor configuration where this problem/solution differentiation is required. Provisions have been made in the 980A to extend this interface to special function hardware such as floating point arithmetic or special transforms by including an Auxiliary Processor Port in the CPU and implementing it with its own activation instruction.

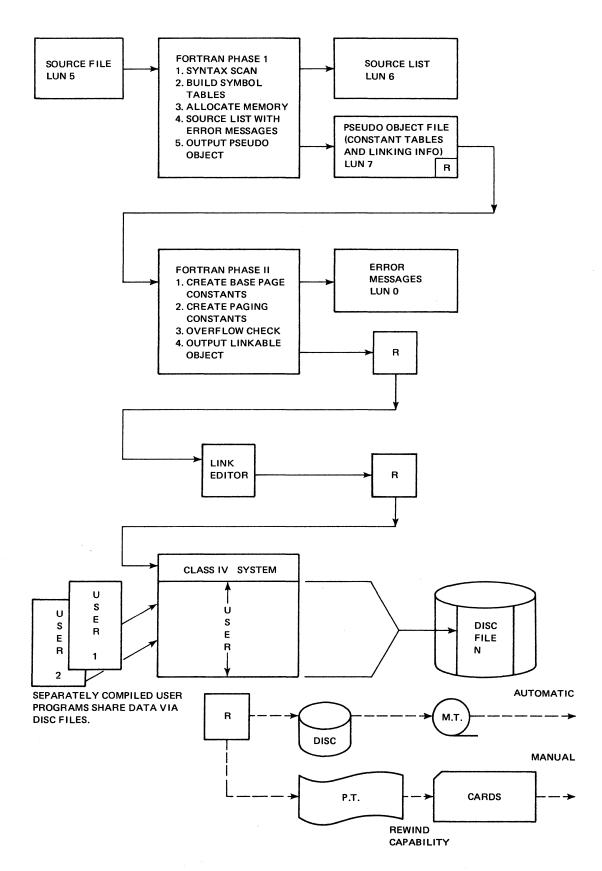

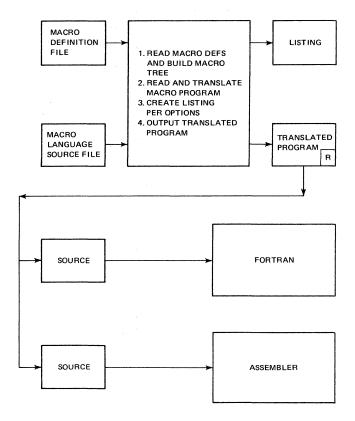

To minimize the general user's programming costs, FORTRAN IV and a macro processor are fully implemented in the 980A. System Executives, available in both disc-resident and non-disc versions, allow rapid program generation as well as compile and execute capabilities. Programmable memory protect, used in conjunction with a privileged class of instructions accessible only to the System Executive, provides an operating environment which is unaffected by programmer errors.

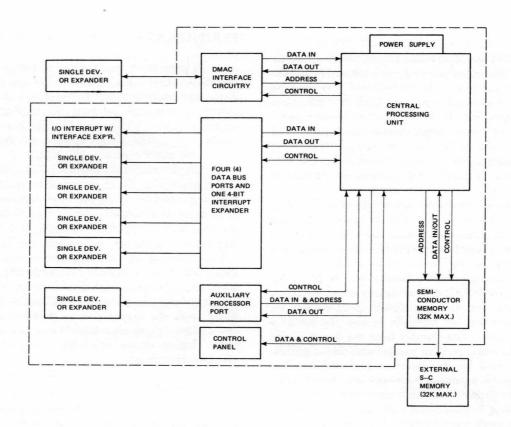

#### Configuration Guide

The 980A is modular and can be configured in minimum form as a processor with 4K words of memory, a teletype for input/output, and three additional I/O ports for additional device controllers. A single 980A will support 65K words of random access semiconductor memory, up to

eight high-speed device controllers such as discs, magnetic tape units, and line printers on a direct memory access channel (DMAC), and up to 256 I/O Bus devices.

Both serial and parallel universal type interfaces are available for special or custom devices communicating via the I/O Bus. Four I/O ports with decoded interrupt, one DMAC port and one Auxiliary Processor port are implemented in the basic CPU. Any port may be expanded into multiple ports within the mainframe or in an external chassis. For example, the I/O Bus may be expanded internally to accommodate 13 device controllers with the addition of a connector plate and three special bus expander logic printed circuit boards. The same expander cards are used each time the I/O Bus is extended. The mainframe power supply is designed to provide all required operating voltages and currents for the CPU with the full 65K memory, any desired internal expansion feature, and also provide the user with regulated +5 Vdc power source for external use.

When external expansion of either DMAC or the I/O Bus is required, an independent chassis is available complete with power supplies. Each chassis may be factory wired to accommodate combinations of different device controllers, or unwired allowing custom wire-wrap interconnects. A maximum of 56 80-pin sockets can be mounted in each chassis.

#### Compatibility

The earlier generation, general purpose Model 980 is upward program-compatible with the new, Model 980A. The 980A has some instructions not in the 980's instruction set, thus software developed for the 980 will run on the 980A. The 980A is not program compatible with the 960A, but they are data compatible and use many of the same peripheral devices. A disc or magnetic tape may be recorded on one computer and read on another. DMAC controllers as well as devices are physically interchangeable. Both the 980A and 960A use some common hardware in the mainframe to the extent that power supplies and semiconductor memory modules may be interchanged.

A Cross-Assembler for the 960A is available for use on the 980A as well as a 360 Cross-Assembler for off-line assembly of 980A programs.

#### **MAINFRAME**

#### Architecture

The 980A is basically a 16-bit word oriented computer. The instruction set, however, allows direct manipulation of data in the form of bits, words or strings of bytes or words. Arithmetic operations can be performed in single-word or double-word precision.

Hardware multiply and divide has been incorporated as a standard feature in the 980A central processor.

The 980A is designed for general purpose computer applications. Programmable memory protect has been incorporated allowing upper and lower limit boundaries to be established by the operating system. Privileged instructions have been implemented in the 980A so that the system supervisor is protected from interference by user programs and user programs are protected from each other. Attempts by users to access protected memory or change status are flagged as system violations and generate an internal interrupt.

#### Central Processor

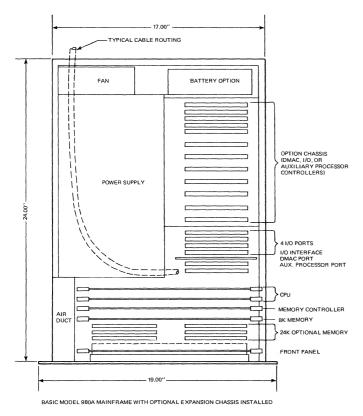

The basic 980A processor is available from 4K to 65K of semiconductor memory in increments of 4K. Memory modules are available in either 4K or 8K configurations. The CPU can directly address memory to a maximum of 65K words. The CPU mainframe is wired to house 32K words internally with the remaining portion of incorporated memory housed in an external chassis; power for the external memory chassis is derived from the basic CPU.

All processors include memory parity, programmable memory protect, privileged instructions, hardware program relocation, failure interrupt (auto restart with battery option), ROM bootstrap loader, multiply and divide, a control panel with key lock, one Auxiliary Processor (AP) port, one DMAC port, four I/O Bus ports with expanded interrupt, power supply, and rackmount chassis with slides.

A rear-mounted fan provides air circulation through the power supply and internal printed circuit boards. External cabling to the CPU is routed via cableways mounted over the fan assembly. Power and ground interconnections throughout the chassis are made via mother boards; signal interconnections are wire-wrap terminations. Space is available in the mainframe to mount an optional battery pack and a 12-connector internal expansion backplate. The battery provides refresh power to the semiconductor memory in the event of primary power failure. The internal expansion chassis is supplied unwired, wired for I/O Bus expansion, or wired for the inclusion of particular DMAC controllers or DMAC port expansion.

Table 1 lists the general characteristics of the 980A central processor, and Table 2 defines the operating and environmental specifications. Table 3 lists the physical characteristics.

### Data Structure

Both data and instruction words in the 980A are 16 bits. Negative numbers are represented in the TWO's complement form with the most significant bit indicating the word sign. The range of integers represented in one

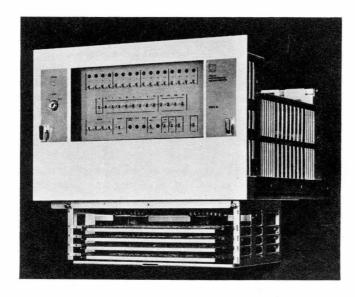

980A Mechanical Configurations

16-bit word is from  $-2^{15}$  to  $+2^{15}$  -1. Basic arithmetic instructions use one-word operands; however, the extended instruction set provides some double-precision (2-word) arithmetic operations. Basic machine instructions may be one, two, or three words long. The operands for floating-point arithmetic subroutines consist of two words, 8-bit exponent and 24-bit mantissa, or three words with an 8-bit exponent and 32-bit mantissa.

#### Registers

The 980A incorporates eight directly addressable 16-bit registers. These registers with their normal functions and designations are as follows:

| Register<br>Number | Designation | Function                    |

|--------------------|-------------|-----------------------------|

| 0                  | Α           | Primary Arithmetic Register |

| 1                  | E           | Secondary (extension)       |

|                    |             | Arithmetic Register         |

| 2                  | X           | Index Register              |

| 3                  | M           | Maintenance Register        |

| 4                  | S           | Storage Register            |

| 5                  | L           | Link Register               |

| 6                  | В           | Base Register               |

| 7                  | P           | Program Counter             |

The processor status is contained in an additional 16-bit register identified as the Status Register. The Status Register is directly addressable under program control and together with the program counter constitutes the status block. The following status or control bits are indicated by the Status Register:

#### Bit Function

- 0-1 Comparison indicators showing result of last magnitude comparison

- 2 Overflow indicator

- 3 Carry indicator showing arithmetic operation which resulted in overflow into sign bit

- 4 Enable/Disable Memory Protect

- 5 Memory Protect address violation

- 6 Privileged Instruction violation

- 7 Enable/disable I/O Bus interrupt

- 8 Enable/disable expanded interrupt

- 9 Enable/disable privileged instruction lower limit address bias

- 10 Pre/post index control

- 11 Enable/disable memory parity error interrupt

- 12 Enable/disable DMAC interrupt

- 14 Memory parity error indicator flag

- 15 Power failure indicator showing primary ac power failure is imminent.

#### Addressing

The 980A computer incorporates a Memory Protect/Privileged Instruction Feature (MP/PIF) for systems programming which prevents a user program from:

Changing the memory protection boundary address Bring the computer to an idle Branching into or accessing data in protected memory Changing Status Register Interfacing with system I/O operations.

The MP/PIF is controlled by two Status Register bits. When bit 4 is set (MP/PIF enabled), any attempt to address protected memory or use privileged instructions causes a system interrupt. Protected memory is defined by two Hardware Limit Registers implemented in the memory controller. Both upper and lower limit address registers are loaded under program control with the standard I/O instruction.

When Status Register bit 9 is set, the lower limit address bias is enabled and all subsequent memory accesses are dynamically biased by the current value in the lower limit address register. User programs are relocated automatically and executed as though they had never been moved. The two modes of MP/PIF operation can be used together or independently providing a powerful tool for the systems programmer.

| Characteristic                            | Description                                                 |

|-------------------------------------------|-------------------------------------------------------------|

| Memory                                    |                                                             |

| Type                                      | MOS semiconductor                                           |

| Word length                               | 16 bits + parity                                            |

| Cycle time/word                           | 750 nanoseconds                                             |

| Refresh rate                              | Every 67 microseconds (maximum memory speed                 |

|                                           | reduced 1.2%)                                               |

| Capacity (words)                          |                                                             |

| Minimum                                   | 4,096                                                       |

| Maximum                                   | 65,537                                                      |

| Increment size                            | 4,096                                                       |

| Memory Protect                            | High and low address boundary protect alterable by          |

|                                           | System Executive.                                           |

| ROM                                       | Bootstrap loaders for 8 devices standard, switch initiated  |

|                                           | 2000014p 1044011 101 0 4011000 Standard, Switten initiated  |

| Central Processor                         |                                                             |

| Number of working registers               | 8                                                           |

| Special register                          | Status - establishes working environment in CPU             |

| Number of instructions                    | 98                                                          |

| Fixed point arithmetic (TWO's complement) | Hardware                                                    |

| Add time (µsec)                           | 1.75 (register to memory)                                   |

| τιασ τιπο (μισος)                         | 0.75 (immediate)                                            |

| Multiply time (µsec)                      | 6.25 (register to memory)                                   |

| νιατείριγ είπιο (μοσο)                    | 5.25 (immediate)                                            |

| Divide time (µsec)                        | 7.75 (register to memory)                                   |

| Divide time (psec)                        | 6.75 (immediate)                                            |

| Floating point arithmetic                 | Subroutine (hardware available 4th quarter 1972)            |

| Addressing                                | 15 modes including Immediate, Absolute, Index, Indirect,    |

|                                           | Displacement, and PC and Base Relative.                     |

| Special features                          | Direct address to bit level                                 |

|                                           | Privileged Instructions preventing branching into           |

|                                           | protected memory, halting CPU, changing status, or          |

|                                           | performing I/O.                                             |

| Maximum number of I/O device controllers  | 256                                                         |

| Maximum number of DMAC device controllers | 8 std. (64 max.)                                            |

| Priority Interrupt System                 |                                                             |

| Levels                                    | 4, hardware, expandable to 64                               |

| I/O Channels                              | · · · · · · · · · · · · · · · · · · ·                       |

| Auxiliary Processor                       | 1 port implemented                                          |

| DMAC                                      | 1 port implemented, expandable to 8                         |

| I/O Bus                                   | 4 ports with interrupt bits implemented, expandable to 256. |

| Transfer rate (words/sec)                 | - · · · · · · · · · · · · · · · · · · ·                     |

| DMAC                                      | 1M (device limited)                                         |

| I/O Bus                                   | 130K                                                        |

| Microsequenced CPU control (ROM)          | 250-nanosecond cycle time                                   |

Table 2. 980A Operational And Environmental Specifications

| Specification                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating                                               | 0°C to 50°C at sea level (derate upper limit 4°C for 50-Hz operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Storage                                                 | -40°C to 70°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Shock                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating                                               | 1G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Shipping                                                | 15G's to shipping container                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Humidity                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating                                               | 0 to 95% RH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Storage                                                 | 0 to 95% RH (non-condensing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Altitude                                                | 0 to 10,000 feet (derate upper operating temperature limit 2°C/2500 ft)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Reliability                                             | The calculated mean time between failure (MTBF) for the 980A with 4K words memory is 4000 hours. Calculations are based on MIL-HB-217A and represent a worst case number. Neither the confidence level or individual component failure rates have been adjusted to comprehend reduced interconnection failures due to multilayer PC board utilization, or the increased component reliability achieved by total system burn-in at maximum operation temperature for one week. These two mechanisms significantly increase the actual reliability. |

|                                                         | The established design goal for mean time to repair (MTTR) at the PC board replacement level is less than 10 minues.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AC line noise immunity                                  | Dual, computer grade L-C line filters incorporated in each CPU power supply. Provides broad band noise suppression. Rejection specification dependent on noise characteristics.                                                                                                                                                                                                                                                                                                                                                                   |

| Power failure detection<br>Auto restart from power down | Standard power supply feature Incorporated in CPU but requires memory protect battery option to function                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## The following addressing modes are also available:

|                                       | Instruction     |                                       | Instruction     |

|---------------------------------------|-----------------|---------------------------------------|-----------------|

| Hardware Addressing Modes             | Length In Words | Hardware Addressing Modes             | Length In Words |

| Immediate 8-bit                       | 1               | (Program counter ±7-bit displacement  |                 |

| Immediate 16-bit                      | 2               | ±15-bit index) indirect               | 1               |

| Immediate 32-bit                      | 3               | (Program counter ±7-bit displacement) |                 |

| 16-bit absolute address               | 2               | indirect ±15-bit index                | 1               |

| 16-bit absolute address ±15-bit index | 2               | Base register + 8-bit displacement    | 1               |

| Program counter ±7-bit displacement   | 1               | (Base register + 8-bit displacement)  |                 |

| Program counter ±15-bit index         | 1               | indirect                              | 1               |

| Program counter ±7-bit displacement   | •               | Base register + 8-bit displacement    |                 |

| ±15-bit index                         | 1               | ±15-bit index                         | 1               |

| (Program counter ±7-bit displacement) |                 | Each memory bit is directly           |                 |

| indirect                              | 1               | addressable                           |                 |

Table 3. 980A Physical Characteristics

| Component                              | Part Number | Input Power                                 | Power<br>Available | Weight<br>(lbs) | Shipping<br>Weight<br>(lbs) | Physical Size<br>(inches)                             |

|----------------------------------------|-------------|---------------------------------------------|--------------------|-----------------|-----------------------------|-------------------------------------------------------|

| 980A CPU (8K memory)                   | 960705-2    | 115 Vac±10%,47-63Hz,450<br>watts max. (32K) | ı                  | 80              | 120                         | 12-1/4Hx19Wx24D<br>Shipping Container:<br>23Hx31Wx36D |

| External I/O or DMAC expansion chassis | 216150-1    | 115Vac±10%,47-63Hz, 300 watts max.          |                    | 70              | 100                         | 10-1/4x19Wx24D                                        |

| External memory expansion chassis      | 960707-2    |                                             |                    | 15              | 25                          | 5-1/4Hx19Wx10D<br>(mechanically coupled<br>to CPU)    |

| Control panel*                         | 960740      |                                             |                    |                 |                             | ,                                                     |

| CPU control (AU1)*                     | 960754      | +5V, 14A                                    |                    |                 | 8 (typ.)                    | Full size CPU PC boards                               |

| CPU control (AU2)*                     | 960751      |                                             |                    |                 | 8 (typ.)                    | Full size CPU PC boards                               |

| Memory Controller*                     | 960748      | +5V, 4A                                     |                    |                 | 8 (typ.)                    | Full size CPU PC boards                               |

| 8K-word Memory Module                  | 226844-4    | +5V, 1.5A                                   |                    |                 | 8 (typ.)                    | Full size CPU PC boards                               |

| I/O Interface card                     | 960759      | +5V, 0.5A                                   |                    |                 | 5 (typ.)                    | Single/Dbl Ended I/O<br>PC boards                     |

| EIA Communication<br>Module (half-dup) | 217539      |                                             | RS-232B            |                 | 5 (typ.)                    | Single/Dbl Ended I/O<br>PC boards                     |

| Digital I/O Module<br>(16 In/Out)      | 961648-1    |                                             | +5Vdc, 1A          |                 | 5 (typ.)                    | Single/Dbl Ended I/O<br>PC boards                     |

| DMAC Interface card                    | 226772-1    |                                             |                    |                 | 5 (typ.)                    | Single/Dbl Ended I/O<br>PC boards                     |

| Fixed Head Disc DMAC<br>Controller     | 961751-17   | +5V, 5A                                     |                    |                 | 12 (typ.)                   |                                                       |

| Moving Head Disc DMAC<br>Controller    | 961752-1    | +5V, 8A                                     |                    |                 | 12 (typ.)                   |                                                       |

| Line Printer DMAC<br>Controller        | 217065-2    | +5V, 1A                                     |                    |                 | 10 (typ.)                   |                                                       |

| Mag Tape DMAC<br>Controller            | 217536-2    | +5V, 6A                                     |                    |                 | 12 (typ.)                   |                                                       |

Note: All weights are approximate and are dependent on PC board compliment.

Base relative addressing does not increase instruction execution time. Indexing increases execution time 250 nanoseconds, and indirect addressing adds 750 nanoseconds to the basic cycle time.

#### Machine Instructions.

Table 4 describes standard machine instructions grouped by instruction class as opposed to instruction

function. Within any group, the descriptions are given in alphabetical order according to the mnemonic used by the programmer when coding in assembly language. These condensed instruction descriptions do not include conditions of overflow and carry indicators or format details. Machine execution times (in microseconds) are associated with each instruction.

<sup>\*</sup>Included in basic CPU

Table 4. 980A Instruction Set

| Register-Me | emory Instructions                                                                                                                       | Memory<br>Referencing | Immediate<br>Addressing |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|

| ADD         | Add effective operand to contents of A register and leave sum in A register.                                                             | 1.75                  | 0.75                    |

| AND         | Logically AND effective operand with contents of A register and leave result in A register.                                              | 1.75                  | 0.75                    |

| BIX         | Add one to X register and leave result in X register. BRANCH IF INCREMENTED INDEX is non-zero to effective address; otherwise, continue. | 1.25                  | 1.25                    |

| BRL         | Load Link Register with contents of program counter, branch to effective address, and continue.                                          | 1.50                  | 1.50                    |

| BRU         | Branch unconditionally to effective address and continue.                                                                                | 1.25                  | 1.00                    |

| CPA         | Compare algebraically effective operand with A register.                                                                                 | 1.75                  | 0.75                    |

| CPL         | Compare logically (16-bit unsigned number) effective operand with A register.                                                            | 1.75                  | 0.75                    |

| DAD         | Add double-length operand in effective address and effective address plus one to the combined A and E registers.                         | 2.75                  | 1.0                     |

| DIV         | Divide combined A and E registers by effective operand and leave quotient in A and remainder in E.                                       | 2.75 → 7.75           | 1.50 → 6.75             |

| DLD         | Load combined A and E registers with contents of effective address and effective address plus one.                                       | 2.75                  | 1.0                     |

| DMT         | Decrement operand by one; if zero, skip next instruction.                                                                                | 2.75                  | 1.0                     |

| DSB         | Subtract double-length effective operand from combined A and E registers.                                                                | 2.75                  | 1.0                     |

| DST         | Store combined A and E registers in effective address and effective address plus one.                                                    | 2.75                  | 2.75                    |

| IMO         | Increment effective operand by one.                                                                                                      | 2.75                  | 2.75                    |

| IOR         | Logically inclusive OR effective operand with A register, and leave results in A register.                                               | 1.75                  | 0.75                    |

| LDA         | Load register A with effective operand.                                                                                                  | 1.75                  | 0.75                    |

| LDE         | Load register E with effective operand.                                                                                                  | 1.75                  | 0.75                    |

| LDM         | Load register M with effective operand.                                                                                                  | 1.75                  | 0.75                    |

|             |                                                                                                                                          |                       |                         |

Table 4. 980A Instruction Set (Continued)

| Register-Me                 | mory Instructions                                                                                                                                                                                                                  | Memory<br>Referencing | Immediate<br>Addressing |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|

| LDX                         | Load register X with effective operand.                                                                                                                                                                                            | 1.75                  | 0.75                    |

| MPY                         | Multiply effective operand by A register, and leave result in combined A and E registers.                                                                                                                                          | 2.25 → 6.25           | 1.25 → 5.25             |

| STA                         | Store register A in effective address.                                                                                                                                                                                             | 2.00                  | 2.0                     |

| STE                         | Store register E in effective address.                                                                                                                                                                                             | 2.00                  | 2.0                     |

| STX                         | Store register X in effective address.                                                                                                                                                                                             | 2.00                  | 2.0                     |

| SUB                         | Subtract effective operand from A register and leave result in A register.                                                                                                                                                         | 1.75                  | 0.75                    |

| Register Shi                | ft Instructions                                                                                                                                                                                                                    | Executio              | n Time                  |

| ALA                         | Shift A register left the number of bit positions indicated by immediate operand, and fill vacated bits with zeros.                                                                                                                | All shift 0.75+       | shift count<br>4        |

| ALD                         | Shift combined A and E registers left the number of bits indicated by immediate operand, and fill vacated bits with zeros. (Omit register E bit 0 from the shift, and force the bit to agree with register A bit 0.)               |                       |                         |

| ARA                         | Shift A register right the number of bit positions indicated by immediate operand, and fill vacated bits with the sign bit.                                                                                                        |                       |                         |

| ARD                         | Shift combined A and E registers right the number of bits indicated by immoperand, and fill vacated bits with the register A sign bit. (Omit register E bit 0 from the shift, and force it to agree with bit 0 of the A register.) | nediate               |                         |

| CLD                         | Circularly left shift combined A and E registers the number of bits specified by immediate operand.                                                                                                                                | i                     |                         |

| CRA CRB CRE CRL CRM CRS CRX | <ul> <li>Circularly right shift contents of the A,B,E,L,M,S, or X register by the num of bits specified by immediate operand.</li> </ul>                                                                                           | ber                   |                         |

| CRD                         | Circularly right shift combined A and E registers the number of bits specific by immediate operand.                                                                                                                                | ed                    |                         |

| LLA                         | Logically left shift A register the number of bits specified by immediate operand, and fill vacated bits with zeros. (Differs from ALA by indicators s                                                                             | et.)                  |                         |

| LLD                         | Logically left shift combined A and E registers the number of bits specified by immediate operand, and fill vacated bits with zeros.                                                                                               |                       |                         |

| LRA                         | Logically right shift A register the number of bits specified by immediate operand, and fill vacated bits with zeros.                                                                                                              |                       |                         |

|                             |                                                                                                                                                                                                                                    |                       |                         |

Table 4. 980A Instruction Set (Continued)

| Register Sh | ift Instructions                                                                                                | Execution Time                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| LTO         | Logically left shift A register per operand. If bit 0=1 during shift, store number shifted in X register.       | All shift $1.0 + \frac{\text{shift count}}{4}$ |

| LTZ         | Logically left shift A register per operand. If bit 0=0 during shift, store number shifted in X register.       |                                                |

| RTO         | Logically right shift A register per operand. If bit 15=1, set bit to 0 and store number shifted in X register. |                                                |

| RTZ         | Logically right shift A register per operand. If bit 15=0, set to 1 and store number shifted in X register.     |                                                |

| egister to  | Register Instructions                                                                                           | Execution Time                                 |

| SR=Sou      | rce Register DR=Destination Register                                                                            | 1.25                                           |

| RAD         | Add the contents of SR to DR.                                                                                   | 1.25                                           |

| RAN         | Logically AND SR to DR.                                                                                         | 1.25                                           |

| RCA         | Algebraically compare SR to DR.                                                                                 | 1.25                                           |

| RCL         | Logically compare SR to DR.                                                                                     | 1.25                                           |

| RCO         | Replace DR with the TWO's complement of SR.                                                                     | 1.00                                           |

| RDE         | Subtract one from SR and place results in DR.                                                                   | 1.00                                           |

| REO         | Exclusive OR SR to DR.                                                                                          | 1.25                                           |

| REX         | Exchange SR and DR.                                                                                             | 1.50                                           |

| RIN         | Add one to SR and place result in DR.                                                                           | 1.00                                           |

| RIV         | Place ONE's complement of SR in DR.                                                                             | 1.00                                           |

| RMO         | Move SR to DR.                                                                                                  | 1.00                                           |

| ROR         | Logically inclusive OR SR to DR.                                                                                | 1.25                                           |

| RSU         | Subtract SR from DR                                                                                             | 1.25                                           |

| egister Ski | p Instructions                                                                                                  | All execute in 1.0 µ sec                       |

| SEV         | Skip the next instruction if register bit 15=0 (even).                                                          |                                                |

| SMI         | Skip the next instruction if register bit 0=1 (minus).                                                          |                                                |

| SNO         | Skip the next instruction if any bit in register=0.                                                             |                                                |

| SNZ         | Skip the next instruction if any bit in register=1.                                                             |                                                |

| SOD         | Skip the next instruction if register bit 15=1 (odd).                                                           |                                                |

| SOO         | Skip the next instruction if all register bits=1.                                                               |                                                |

Table 4. 980A Instruction Set (Continued)

| Register Sk            | rip Instructions                                                                                                                                                                                                                               | All execute in 1.0 p | ısec     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|

| SPL                    | Skip the next instruction if register bit 0=0 (plus).                                                                                                                                                                                          |                      |          |

| SZE                    | Skip the next instruction if all register bits=0.                                                                                                                                                                                              |                      |          |

| Status Indi            | cator Skip Instructions                                                                                                                                                                                                                        | All execute in 1.0   | Jsec     |

| SEQ                    | Skip the next instruction if the last compare (CPA, CPL, RCA, or RCL) was                                                                                                                                                                      | =,                   |          |

| SGE                    | Skip the next instruction if the last compare was.                                                                                                                                                                                             |                      |          |

| SGT                    | Skip the next instruction if the last compare was >.                                                                                                                                                                                           |                      |          |

| SLE                    | Skip the next instruction if the last compare was ≤.                                                                                                                                                                                           |                      |          |

| SLT                    | Skip the next instruction if the last compare was <.                                                                                                                                                                                           | -                    |          |

| SNC                    | Skip the next instruction if the carry indicator is not set.                                                                                                                                                                                   |                      |          |

| SNE                    | Skip the next instruction if the last compare was $\neq$ .                                                                                                                                                                                     |                      |          |

| SNV                    | Skip the next instruction if the overflow indicator is not set.                                                                                                                                                                                | 3                    |          |

| SOC                    | Skip the next instruction if the carry indicator is set.                                                                                                                                                                                       |                      |          |

| sov                    | Skip the next instruction if the overflow indicator is set.                                                                                                                                                                                    |                      |          |

| Sense Swite            | ch Instructions                                                                                                                                                                                                                                | All execute in 1.0   | <br>usec |

| SSE                    | Skip the next instruction if the indicated sense switches are set.                                                                                                                                                                             |                      |          |

| SSN                    | Skip the next instruction if any indicated sense switch is not set.                                                                                                                                                                            |                      |          |

| Multi-regis            | ter Instructions                                                                                                                                                                                                                               |                      |          |

| LRF                    | Load registers A,E,X,M,S,L, and B from sequential memory locations starting at specified address.                                                                                                                                              |                      |          |

| LSB                    | Load program counter with specified address and Status Register with specified address plus one, and branch.                                                                                                                                   |                      |          |

| LSR                    | Same as LSB, with highest priority interrupt in priority interrupt option set to 0.                                                                                                                                                            |                      |          |

| SRF                    | Store registers A,E,X,M,S,L, and B into sequential memory locations starting at specified address.                                                                                                                                             |                      |          |

| SSB                    | Store program counter and Status Register at specified address and address plus one, and branch to address plus two.                                                                                                                           |                      |          |

| Byte Mani <sub>l</sub> | pulation Instructions                                                                                                                                                                                                                          | Execution Time       | ·        |

| CLC                    | Logically compare one consecutive, specified byte string in memory to a second byte string in memory. The first byte-comparison-not-equal terminates the instruction, and the number of bytes left to be compared is stored in the X register. | 5.0+2.25/byte        |          |

Table 4. 980A Instruction Set (Continued)

| Byte Manip                             | ulation Instructions                                                                                                                                                                                                                                                        | Execution Time          |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| MVC                                    | Move a consecutive, specified byte string from one place in memory to another.                                                                                                                                                                                              | 4.75+2.75/byte          |

| Memory/Re                              | gister Bit Manipulation Instructions                                                                                                                                                                                                                                        | Execution Time          |

| SABO                                   | Set a specified bit in register A to a one.                                                                                                                                                                                                                                 | 1.0                     |

| SABZ                                   | Set a specified bit in register A to a zero.                                                                                                                                                                                                                                | 1.0                     |

| SMBO                                   | Set a specified bit in memory to a one.                                                                                                                                                                                                                                     | 3.25                    |

| SMBZ                                   | Set a specified bit in memory to a zero.                                                                                                                                                                                                                                    | 3.25                    |

| TABO                                   | Skip the next instruction if a specified bit in register A=1.                                                                                                                                                                                                               | 1.25                    |

| TABZ                                   | Skip the next instruction if a specified bit in register A=0.                                                                                                                                                                                                               | 1.25                    |

| ТМВО                                   | Skip the next instruction if a specified bit in memory = 1.                                                                                                                                                                                                                 | 2.75                    |

| TMBZ                                   | Skip the next instruction if a specified bit in memory = 0.                                                                                                                                                                                                                 | 2.75                    |

| —————————————————————————————————————— | rocessor                                                                                                                                                                                                                                                                    |                         |

| API                                    | Automatically initiates transfer of information to device/<br>processor/CPU attached to auxiliary processor bus. (General<br>purpose of special function.) This instruction is used to<br>initiate execution of unique instruction sets implemented<br>in special hardware. | AP controller dependent |

| Data Bus In                            | put/Output Instructions                                                                                                                                                                                                                                                     | Execution Time          |

| RDS                                    | One word of data is moved from indicated external device into specified register or memory location.                                                                                                                                                                        | 3.00 → 4.75             |

| WDS                                    | One word of data is moved from a specified register or memory location to indicated peripheral device.                                                                                                                                                                      | 3.00 → 5.0              |

| Direct Mem                             | ory Access Channel Input/Output Instruction                                                                                                                                                                                                                                 | Execution Time          |

| ATI                                    | Automatically transfer a buffer of data to or from a specific peripheral device.                                                                                                                                                                                            | 2.5                     |

| Single Func                            | tion Instructions                                                                                                                                                                                                                                                           | Execution Time          |

| IDL                                    | The computer idles until external interrupt or START switch                                                                                                                                                                                                                 | 1.0                     |

| NRM                                    | Shift combined A and E registers left until bit 0 of A register is different from bit 1, and fill vacated bits with zeros. Store the number of places shifted in X register. (Omit register E bit 0 from the shift, and force that bit to agree with register A bit 0.)     | 1.0 → 8.75              |

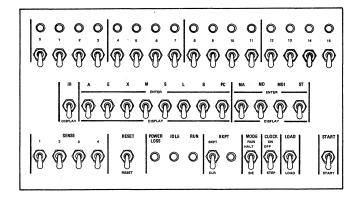

980A Console Control Panel

#### Console Control Panel

The operator's control panel is physically contained on a plug-in printed circuit board with operator access to switches and controls through a front panel cutout. Switch functions are performed by two or three position toggle switches and all control panel indicators are long-life (in excess of 10<sup>5</sup> hours) light emitting diodes (LED's). A key-operated LOCK/UNLOCK switch, located on the left of the control panel, disables switch control functions. An indicator lamp above the key switch indicates the application of primary ac power to the CPU. The power ON/OFF switch is located at the rear of the mainframe. Following is a brief description of the operating and control functions of the console.

| Control      | Function                                                                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------|

| DATA         | 16 switches and corresponding indicators used to enter or readout data                                            |

| IR/DISPLAY   | Initiates display of Instruction Register contents via the data display indicators                                |

| A through ST | Allows display or entry of data into selected working register. Note: MDI automatically increments memory address |

| SENSE 1-4<br>RESET<br>POWER LOSS | Four software accessed sense switches Performs system reset function Monitors battery level and indicates marginal battery power to maintain memory during ac power down condition |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDLE                             | Indicates the CPU has executed an idle instruction                                                                                                                                 |

| RUN                              | Indicates the CPU is operating in the run mode                                                                                                                                     |

| BKPT/CLR                         | Switch enable which compares data<br>switches to memory address. Indicator<br>lights up when comparison equal; if break<br>point enabled, CPU halts                                |

| MODE                             | CPU mode control allowing run, stop, or single instruction execution conditions                                                                                                    |

| CLOCK                            | Control allowing continuous, none, or single clock pulses to be generated                                                                                                          |

| LOAD                             | Initiates auto load of 256 word ROM bootstrap into memory                                                                                                                          |

| START                            | Initiates RUN and SIE.                                                                                                                                                             |

#### Interrupt Control

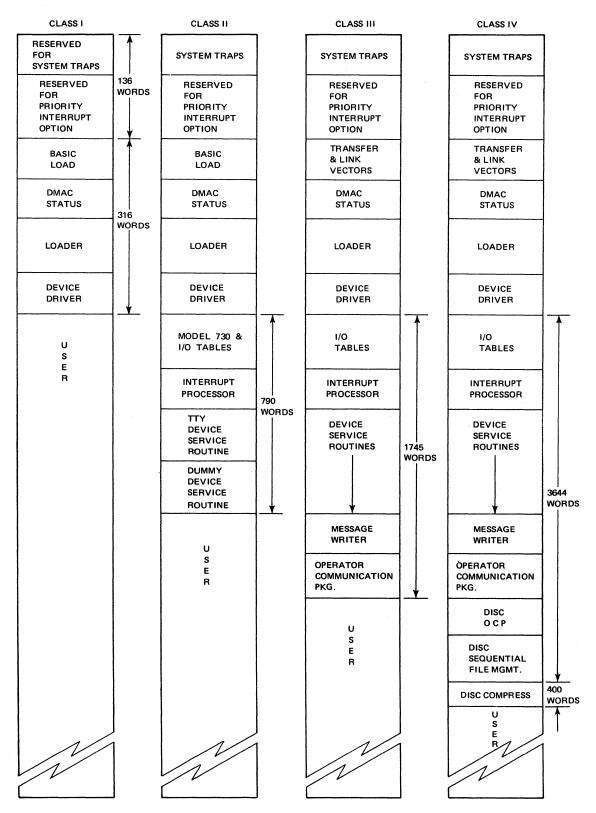

The 980A features a priority interrupt system that provides added program control of input/output operations, provides immediate response to abnormal conditions, and allows immediate recognition of special external conditions. The interrupt system has four levels of priority control as shown in Table 5.

When an interrupt is recognized by the processor, the instruction at the trap address is executed; however, the program counter remains unchanged unless the instruction executed specifies a program counter change. If the instruction does not modify the program counter, the following instruction is executed from the normal program sequence. Interrupts are not recognized during the execution of the trap instruction and the following instruction. The internal interrupt cannot be disabled; however, the other interrupts can be masked by the control bit in the Status Register.

Table 5. 980A Interrupts and Priorities

| Interrupt         | Priority | Trap Address<br>(Hexadecimal) | Remarks                                                                                    |

|-------------------|----------|-------------------------------|--------------------------------------------------------------------------------------------|

| Internal          | 1        | 0-2                           | Includes illegal op codes, PIF violation, memory parity error, power failure, and restart. |

| External priority | 2        | 8-87                          | Optional expansion to 64 levels                                                            |

| DMAC              | 3        | 4                             | DMA device interrupt                                                                       |

| I/O               | 4        | 6                             | I/O Bus interrupt                                                                          |

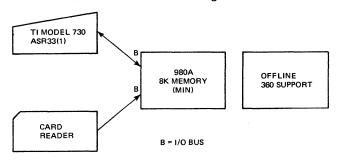

980A Basic I/O Contiguration

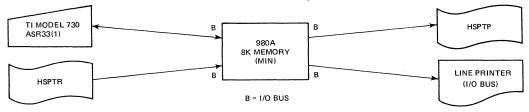

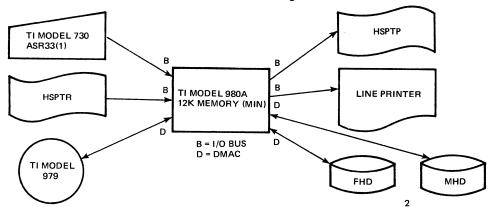

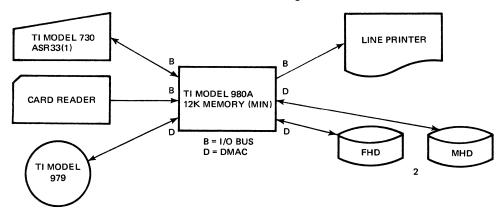

980A With Expanded I/O and DMAC

#### I/O Control

Input and output operations for the 980A use either the I/O Bus, Direct Memory Access Channel, or the Auxiliary Processor port. The DMAC and I/O may be expanded with associated interrupts until the maximum configuration specified in Table 1 is reached. Special instructions have been implemented to initiate and supervise the transfer of data by each method. The DMAC and AP can operate at memory speeds, the I/O Bus transfers 16 lines of parallel data at a maximum rate of 130K words/second.

Controllers are available for all peripheral devices offered for the 980A. In the case of devices requiring high-speed DMAC communications, controllers take the form of multiple special function printed circuit boards and require specially wired connectors. Internal chassis expansion can accommodate generally one such DMAC controller; multiple DMAC devices usually require external chassis expansion. Interfaces to slower speed devices are made via the I/O Bus and normally involve the use of a single interface card. Data transfer from the device to the interface may be either serial or parallel with device address decoding performed by the Interface card. All I/O Bus devices interrupt via a common interrupt line. The program must test status to determine the cause of the interrupt. Interrupt decoding is provided on the I/O Bus expansion module to allow rapid identification of each interrupt.

Block transfers via the DMA channel are initiated by the Automatic Transfer Instruction (ATI) which selects the device and device function, and addresses an initialization list in memory. The DMAC controls the block transfer thereafter and transfers data words directly between the high-speed device and memory. Any change in the status of a DMAC device causes an interrupt to be generated. All devices connected to DMAC initiate an interrupt via the common DMAC interrupt line. The interrupt status bits for the eight DMAC ports are merged into a DMAC status word that is stored in memory at interrupt time. This allows quick access to the port causing the interrupt.

The Auxiliary Processor (AP) initiates communication via the API instruction. Memory access is then available to any AP controller. An optionally expandable hardware interrupt scheme where interrupt priority has been previously established and vectored can be used with AP controllers. AP transfers differ from DMAC transfers in that once a transfer is initiated, the 980A enters a wait state until such time as the AP port releases the CPU. Free access to memory is allowed the AP port controllers while operation is suspended; however, DMAC transfers will proceed as normal.

#### **PERIPHERALS**

TI provides a broad range of peripheral devices for the 980A. These include standard low-speed devices such as paper tape equipment and teleprinters and high-speed bulk storage devices such as fixed and moving-head discs and magnetic tapes. Universal I/O Bus interfaces for both parallel and serial data transfers are also available for custom computer control applications.

All peripherals described in Table 6, either directly manufactured by TI or provided as an OEM device, are fully supported by TI for the 980A computer. If purchased as an optional peripheral, each device will be furnished with the required computer interface and documentation. Appropriate hardware controllers, all required cabling, software drivers and support subroutines, and the device itself are fully checked out with the accompanying interfaces. Hardware maintenance contracts are available for all peripherals. Some TI specifications for OEM devices differ from the manufacturer's standard specification for the device; e.g., changes have been made to accommodate either higher device reliability, serviceability, or more effective operation.

#### **Data Communications**

Data communication devices, such as data sets and EIA compatible devices, interface the 980A through communication modules operating on the I/O Bus. Both half and full-duplex operating modes are available; however, full-duplex module requires two I/O ports. Transmission rates available are 110, 300, 1200, and 2400 baud. The communication module provides asynchronous operation and includes character assembly/disassembly, insertion/deletion of start/stop bits and generates an interrupt when character transmission is received or completed. Bell Data Sets 103A or F and 202 C or D are directly interfaced and controlled by the module. The communication module fully complies with EIA Standard RS-232B or will interface devices requiring a standard 20-milliampere current loop. A ±15-volt regulator is required when operating the communication module with an EIA compatible device.

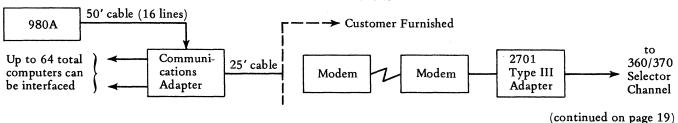

#### 360/370 Communications

A 360/370 Communications Adapter (C/A) is available for the 980A. The C/A operates full-duplex to a customer furnished, self-clocking, synchronous modem (such as the Milgo 4400) operating at 2400 baud. A simplified block diagram of the network is shown as follows:

Table 6. 980A Peripheral Devices

| TI Part No.  | Manufacturer                 | Description                                                                                                                                                                                                                                | Power<br>Requirements               | Size                                       | Ship<br>Weight |

|--------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|----------------|

| Teleprinters |                              |                                                                                                                                                                                                                                            |                                     |                                            |                |

| 966330       | TI Model 730                 | Virtually silent operation. Print rate-10, 15, or 30 cps switch selectable. MTBF < 2 failures/year any reason. Uses standard TTY DC interface (20 mA/60mA neutral). Full ASCII character set. Options- answerback memory and 5mA polar IF. | 115Vac±10%<br>50-60 Hz<br>100 watts | 18DX17WX16¼H                               | 40             |