# TEXAS INSTRUMENTS

Improving Man's Effectiveness Through Electronics

# Model 990/4 Computer

System Hardware Reference Manual

MANUAL NO. 945251-9701 ORIGINAL ISSUE 1 MAY 1976 REVISED AND REISSUED 1 DECEMBER 1976

# C Texas Instruments Incorporated 1976 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

# LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 990/4 Computer System Hardware Reference Manual (945251-9701)

Original Issue . . . . . . . . . . . . . 1 May 1976

Revised and Reissued . . . . . . . . . 1 December 1976 (ECN 415077)

Total number of pages in this publication is 172 consisting of the following:

| PAGE<br>NO.           | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|-----------------------|---------------|-------------|---------------|-------------|---------------|

| Cover                 | . 0           |             |               |             |               |

| Effective Pages       | . 0           |             |               |             |               |

| iii - vii             | . 0           |             |               |             |               |

| 1-0 - 1-6             | . 0           |             |               |             |               |

| 2-1 - 2-38            | . 0           |             |               |             |               |

| 3-1 - 3-110           | . 0           |             |               |             |               |

| Alphabetical Index Di | v. 0          |             |               |             |               |

| Index-1 - Index-4 .   | . 0           |             |               |             |               |

| User's Response       | . 0           |             |               |             |               |

| Business Reply        | . 0           |             |               |             |               |

| Cover Blank           | . 0           |             |               |             |               |

| Cover                 |               |             |               |             |               |

|                       |               |             |               |             |               |

# TABLE OF CONTENTS

| Paragraph | Title                                                |      |  |  |  |

|-----------|------------------------------------------------------|------|--|--|--|

|           | SECTION I. GENERAL DESCRIPTION                       |      |  |  |  |

| 1.1       | General                                              | 1-1  |  |  |  |

| 1.2       | Purpose of Equipment                                 |      |  |  |  |

| 1.3       | Hardware Description                                 |      |  |  |  |

| 1.3.1     | 990/4 Microcomputer                                  |      |  |  |  |

| 1.3.2     | Chassis Assembly                                     |      |  |  |  |

| 1.3.3     | 990/4 Memory Expansion Board                         |      |  |  |  |

| 1.3.4     | EPROM Memory Module                                  |      |  |  |  |

| 1.3.5     | CRU Interface Boards                                 |      |  |  |  |

| 1.3.6     | CRU Expansion Board                                  |      |  |  |  |

| 1.5.0     |                                                      | 1-3  |  |  |  |

|           | SECTION II. INSTALLATION AND OPERATION               |      |  |  |  |

| 2.1       | General                                              |      |  |  |  |

| 2.2       | Unpacking/Packing (6- and 13-Slot Chassis)           | 2-1  |  |  |  |

| 2.3       | Unpacking/Packing (OEM Chassis)                      |      |  |  |  |

| 2.4       | Installation (Tabletop Chassis)                      | 2-8  |  |  |  |

| 2.5       | Installation (Rackmount Chassis)                     | 2-10 |  |  |  |

| 2.6       | Installation (OEM Chassis)                           |      |  |  |  |

| 2.7       | Interrupt Installation                               |      |  |  |  |

| 2.7.1     | Preparation and Planning                             |      |  |  |  |

| 2.7.2     | Modification of Jumper Plug                          |      |  |  |  |

| 2.7.3     | Reinstallation of System                             |      |  |  |  |

| 2.8       | Circuit Board Jumper Modifications                   |      |  |  |  |

| 2.8.1     | 990/4 Microcomputer Board Jumper Options             |      |  |  |  |

| 2.8.2     | 990/4 Memory Expansion Board Options                 |      |  |  |  |

| 2.8.3     | EPROM Memory Module Jumper Options                   |      |  |  |  |

| 2.9       | CRU Expansion Installation Requirements              |      |  |  |  |

| 2.9.1     | CRU Expansion Board Jumper Options                   |      |  |  |  |

| 2.9.2     | CRU Buffer Board Jumper Options                      |      |  |  |  |

| 2.9.3     | Expansion Chassis Interrupt Wiring                   |      |  |  |  |

| 2.10      |                                                      |      |  |  |  |

| 2.10.1    | Logic Board Installation Procedures                  |      |  |  |  |

|           | Full-Sized Logic Board Installation                  |      |  |  |  |

| 2.10.2    | Half-Sized Logic Boards                              |      |  |  |  |

| 2.11      | System Checkout Procedure                            | 2-38 |  |  |  |

|           | SECTION III. PRINCIPLES OF OPERATION                 |      |  |  |  |

| 3.1       | General                                              |      |  |  |  |

| 3.2       | 990/4 Circuit Board                                  |      |  |  |  |

| 3.2.1     | TMS 9900 Microprocessor                              | 3-1  |  |  |  |

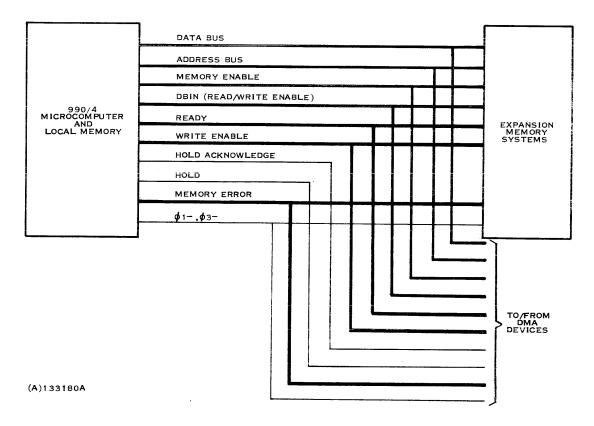

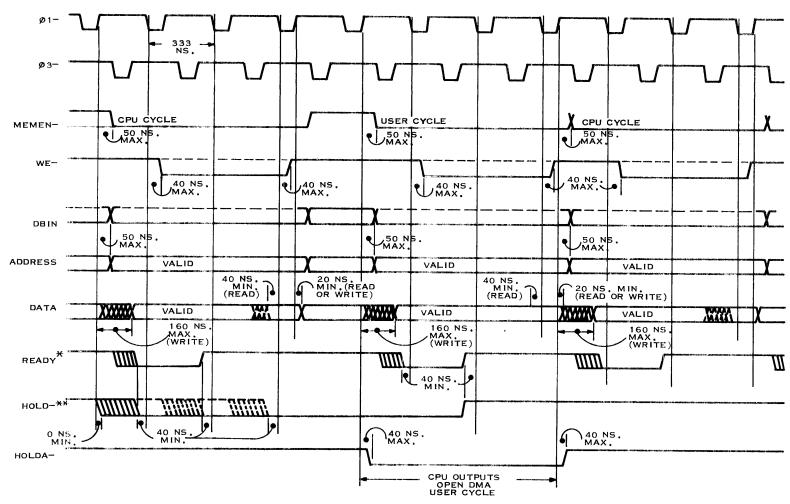

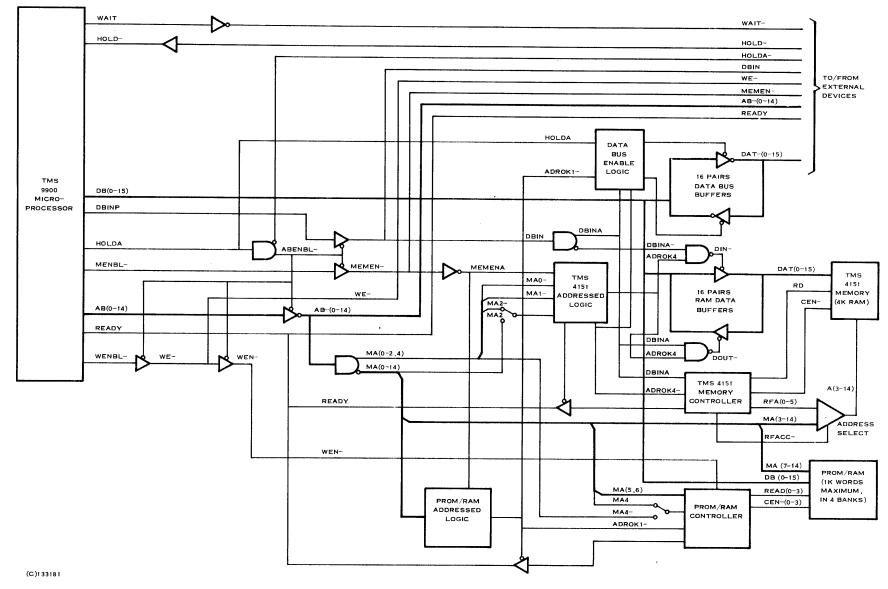

| 3.2.2     | 990/4 - 9900 Memory/DMA Bus                          | 3-17 |  |  |  |

| 3.2.3     | Programmable ROM/RAM                                 |      |  |  |  |

| 3.2.4     | Dynamic Random Access Memory (RAM)                   |      |  |  |  |

| 3.2.5     | Microprocessor Clock                                 |      |  |  |  |

| 3.2.6     | Interrupts                                           |      |  |  |  |

| 3.2.7     | External Instructions and Programmer Panel Functions | 3-36 |  |  |  |

|           |                                                      |      |  |  |  |

# **TABLE OF CONTENTS (Continued)**

| Paragraph | Title                                        | Page  |

|-----------|----------------------------------------------|-------|

| 3.2.8     | Programmer Panel Interface                   | .3-40 |

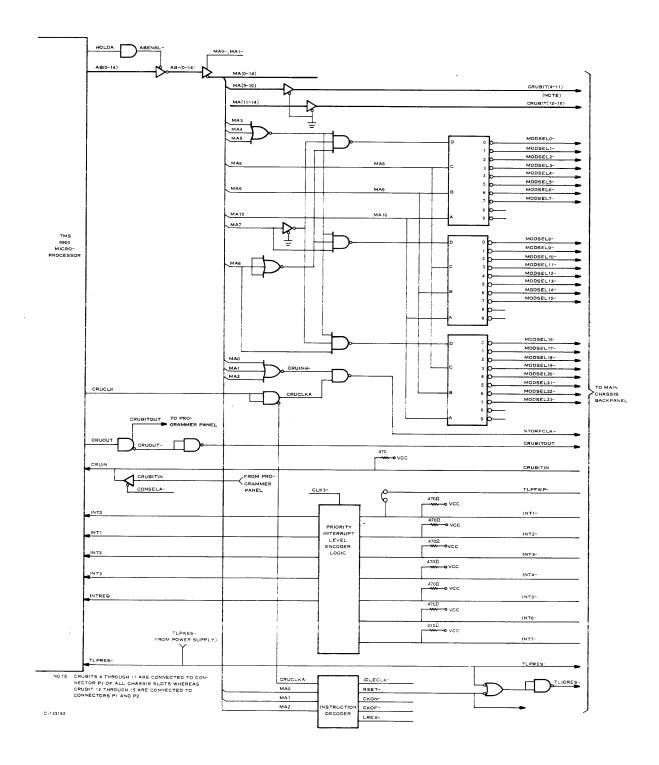

| 3.2.9     | Communications Register Unit (CRU) Interface |       |

| 3.2.10    | 990/4 Board Assembly Configurations          |       |

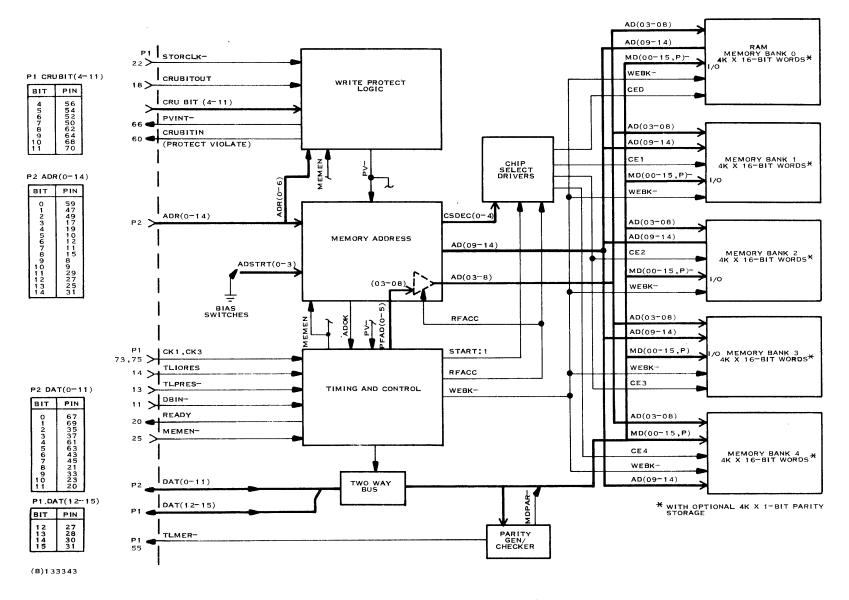

| 3.3       | 990/4 Memory Expansion Module                |       |

| 3.3.1     | Memory Controller                            |       |

| 3.3.2     | Memory Expansion Read/Write Operation        |       |

| 3.3.3     | Parity Generation/Parity Check Option        |       |

| 3.4       | EPROM Memory Module                          |       |

| 3.4.1     | EPROM Functional Theory                      |       |

| 3.4.2     | Memory Options                               |       |

| 3.5       | 990/4 Chassis                                | .3-72 |

| 3.5.1     | OEM Chassis                                  |       |

| 3.5.2     | 6-Slot Chassis                               | .3-74 |

| 3.5.3     | 13-Slot Chassis                              | .3-80 |

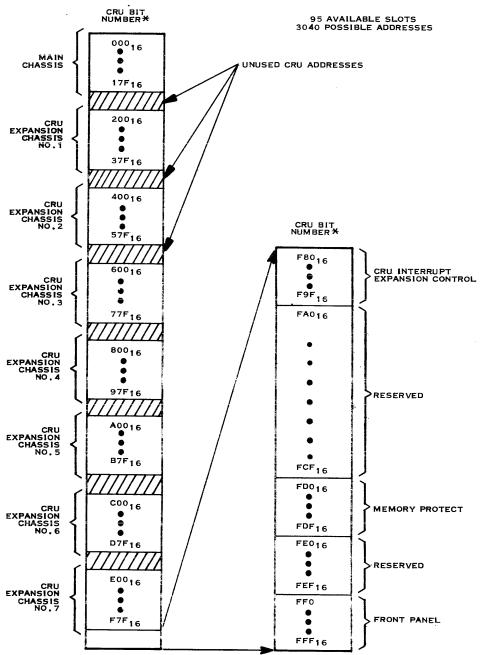

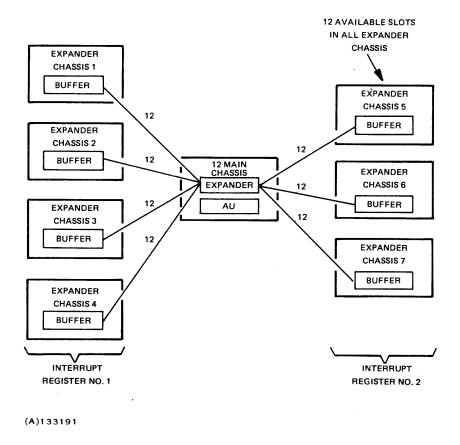

| 3.6       | CRU Expansion                                | .3-80 |

| 3.6.1     | Expansion Chassis Interrupt Scheme           |       |

| 3.6.2     | CRU Expansion Address Scheme                 |       |

| 3.6.3     | CRU Expansion Boards                         |       |

| 3.7       | Programmer Panel                             |       |

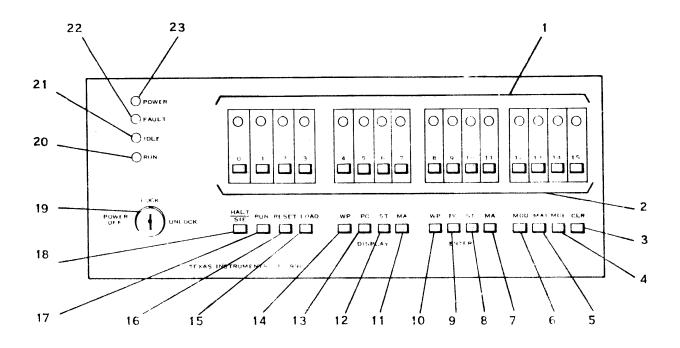

| 3.7.1     | Programmer Panel Controls and Indicators     |       |

| 3.7.2     | Programmer Panel Modes of Operation          | .3-95 |

| 3.7.3     | Interface Signals                            |       |

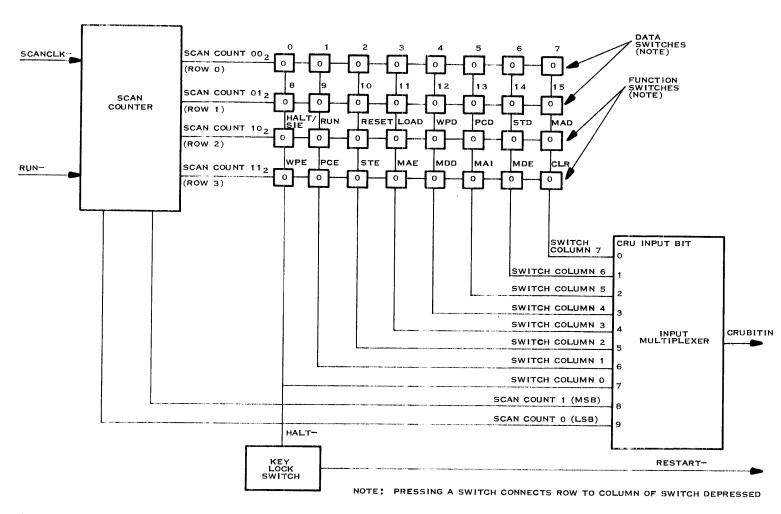

| 3.7.4     | Programmer Panel Addressing                  |       |

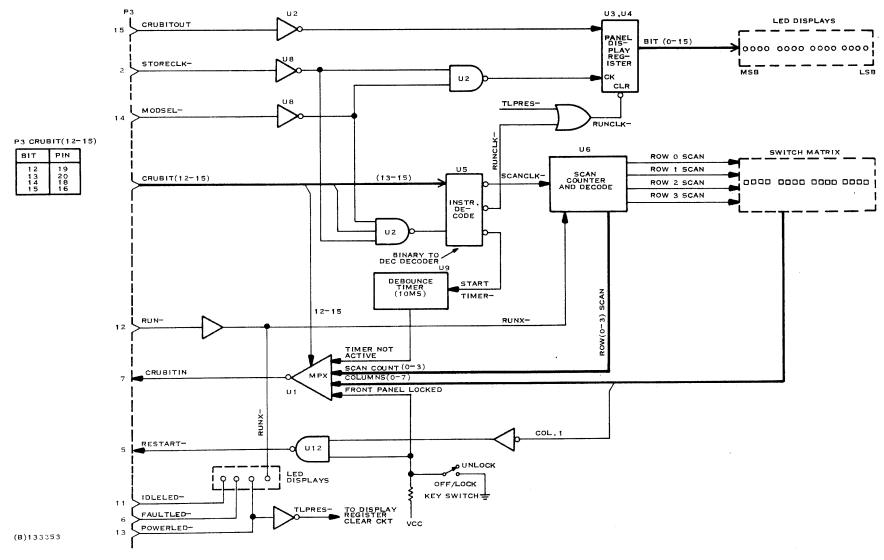

| 3.7.5     | Theory of Operation                          |       |

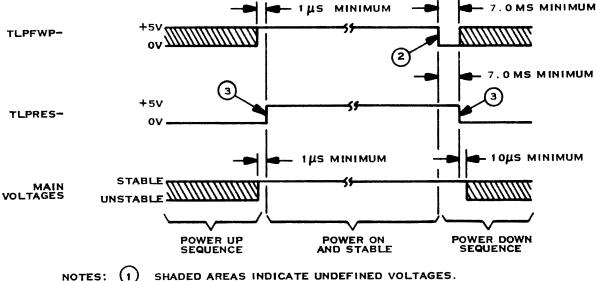

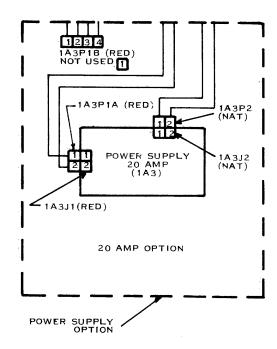

| 3.8       | 20-Ampere Power System                       |       |

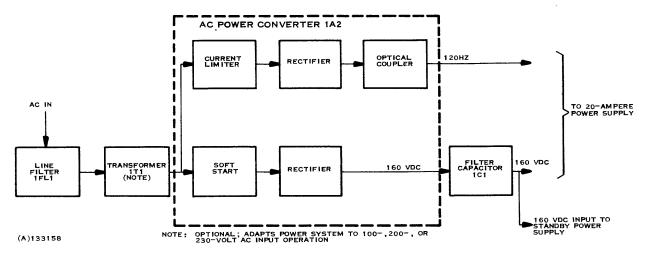

| 3.8.1     | Ac Power Converter and Filters               |       |

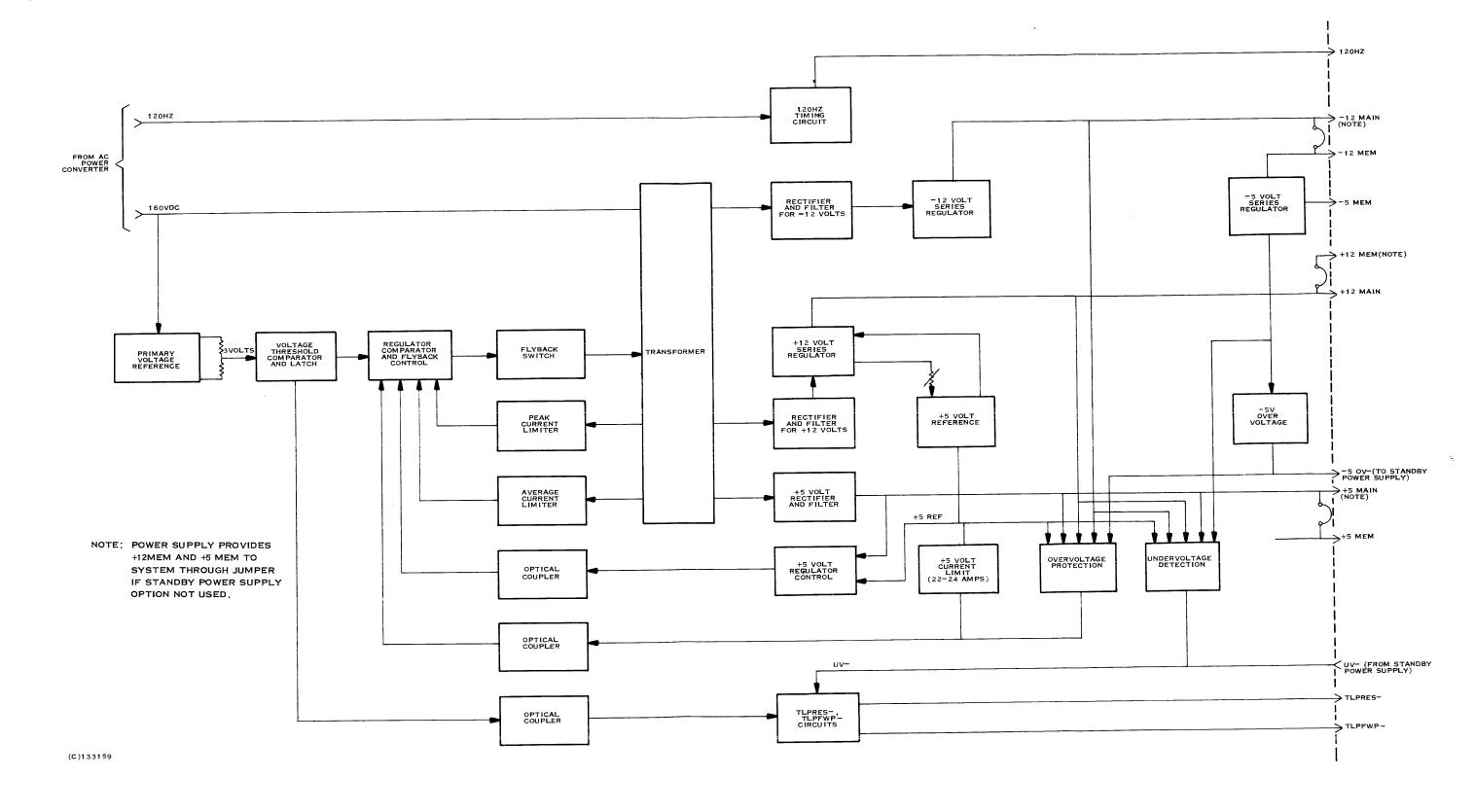

| 3.8.2     | 20-Ampere Power Supply                       |       |

| 3.8.3     | Standby Power Supply                         |       |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                                          | Page |

|--------|--------------------------------------------------------------------------------|------|

| 1-1    | Model 990/4 Microcomputer in Three Packaging Options                           | 1-0  |

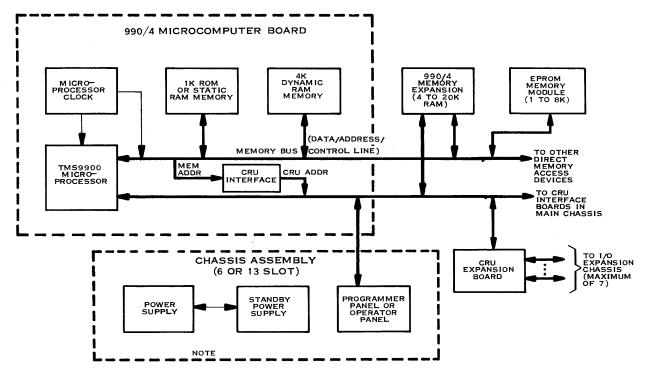

| 1-2    | Model 990/4 Microcomputer System Block Diagram                                 |      |

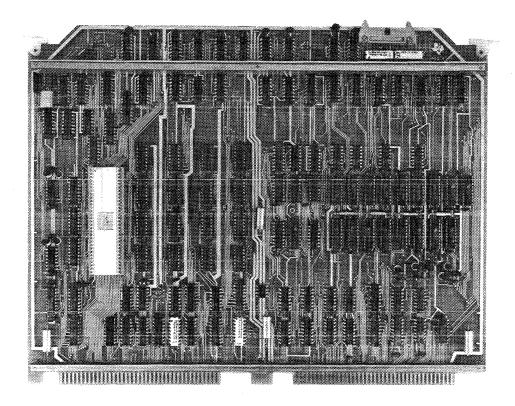

| 1-3    | 990/4 Microcomputer Board                                                      | 1-3  |

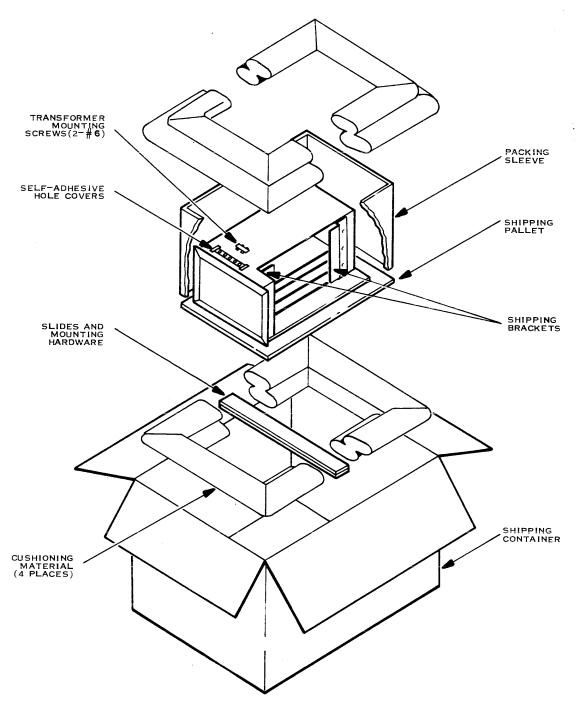

| 2-1    | Computer Shipping Packaging                                                    |      |

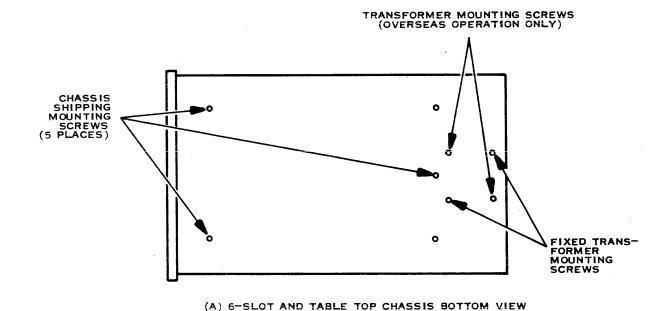

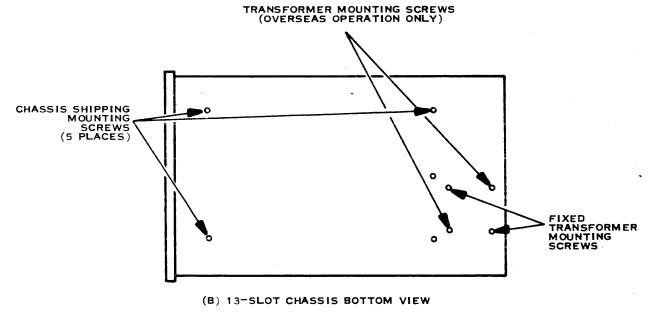

| 2-2    | Location of Chassis Shipping Pallet Mounting Screws                            |      |

| 2-3    | OEM Chassis Shipping Packaging                                                 |      |

| 2-4    | Location of Chassis Enclosure Screws                                           |      |

| 2-5    | 6-Slot Chassis Prewired Configuration                                          |      |

| 2-6    | Clip Nut Installation                                                          | 2-11 |

| 2-7    | Mounting Cabinet Depth Specification                                           |      |

| 2-8    | Mounting Hole Positioning                                                      |      |

| 2-9    | Mounting Screw Installation                                                    | 2-13 |

| 2-10   | Chassis Slide Positioning                                                      |      |

| 2-11   | Installation of Ball Stud and Stop Plate                                       |      |

| 2-12   | 13-Slot Chassis Prewired Configuration                                         | 2-16 |

| 2-13   | Mounting Bracket Installation                                                  | 2-17 |

| 2-14   | Positioning of OEM Chassis in 19-Inch Rack                                     | 2-18 |

| 2-15   | OEM Chassis External Connections                                               | 2-19 |

| 2-16   | Chassis Configuration Charts                                                   | 2-21 |

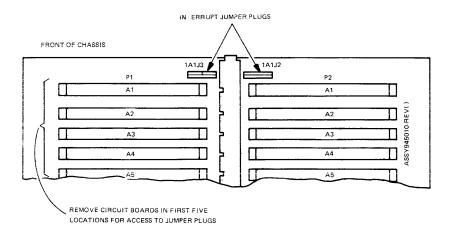

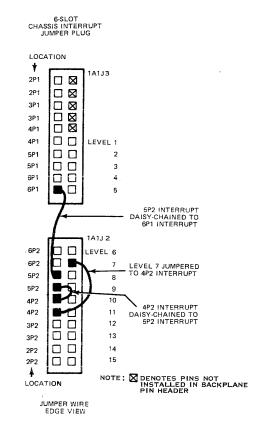

| 2-17   | Location of Interrupt Jumper Plugs (6- and 13-Slot Chassis)                    |      |

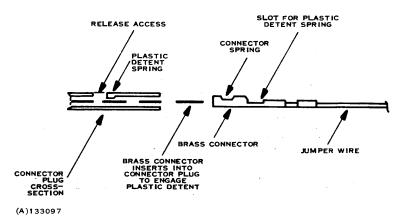

| 2-18   | Interrupt Jumper Wire Installation                                             | 2-24 |

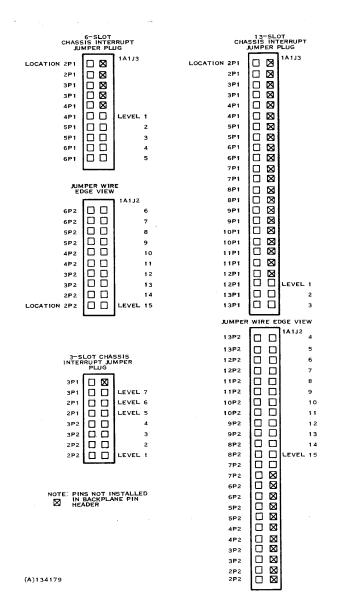

| 2-19   | 3-, 6- and 13-Slot Chassis Interrupt Jumper Plugs (Main and Expansion Chassis) | 2.24 |

| 2-20   | Jumper Plug Daisy-Chain Sample Connection                                      | 2 25 |

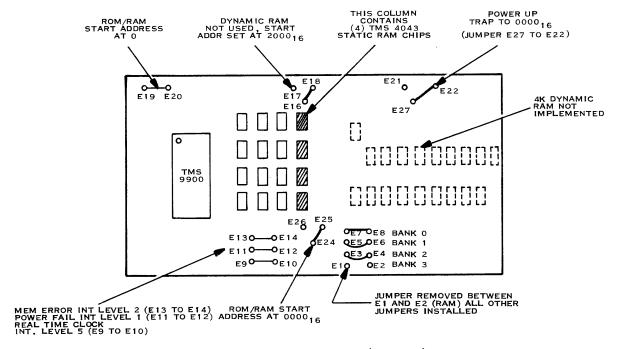

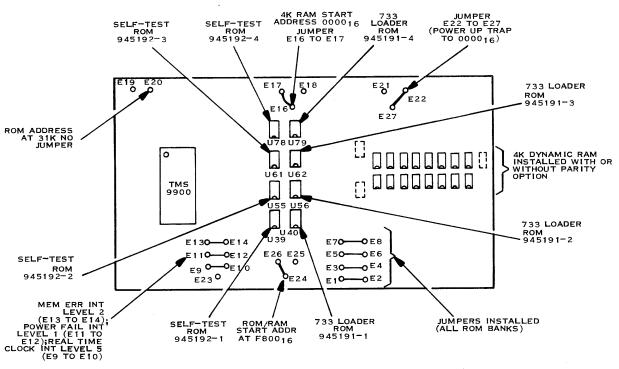

| 2-21   | 990/4 Microcomputer Board Options                                              |      |

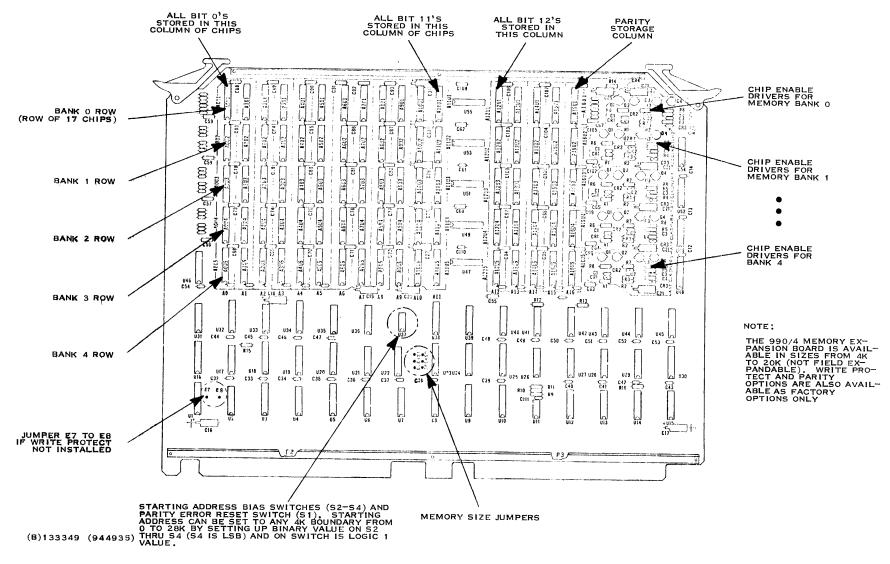

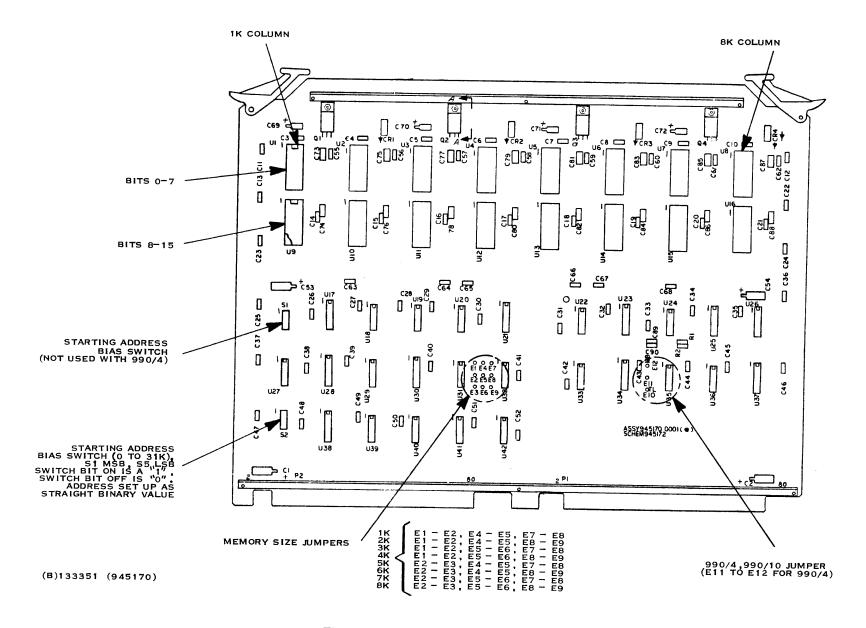

| 2-22   | 990/4 Memory Expansion Board Options                                           | 2-20 |

| 2-23   | EPROM Memory Module Options                                                    | 2-32 |

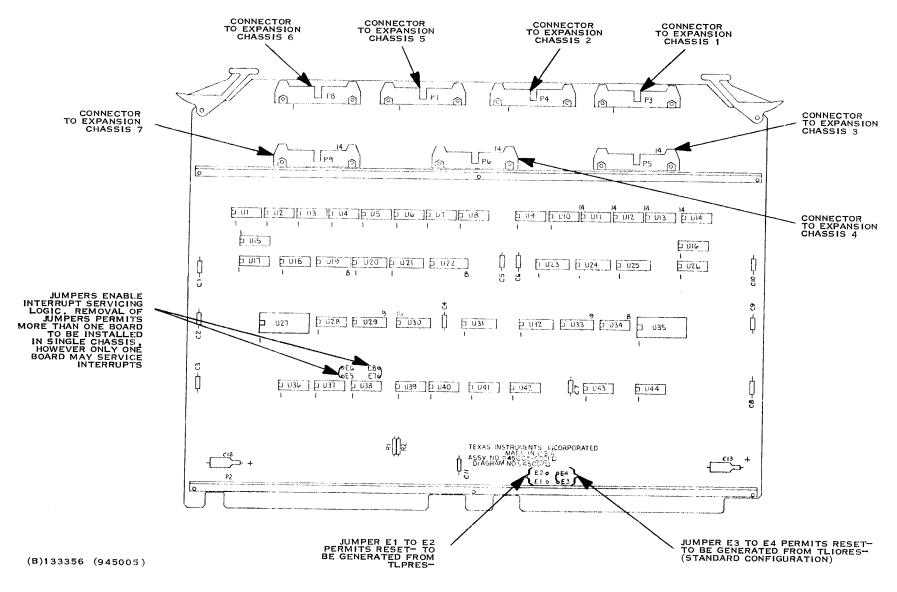

| 2-24   | CRU Expansion Board Options                                                    | 2-33 |

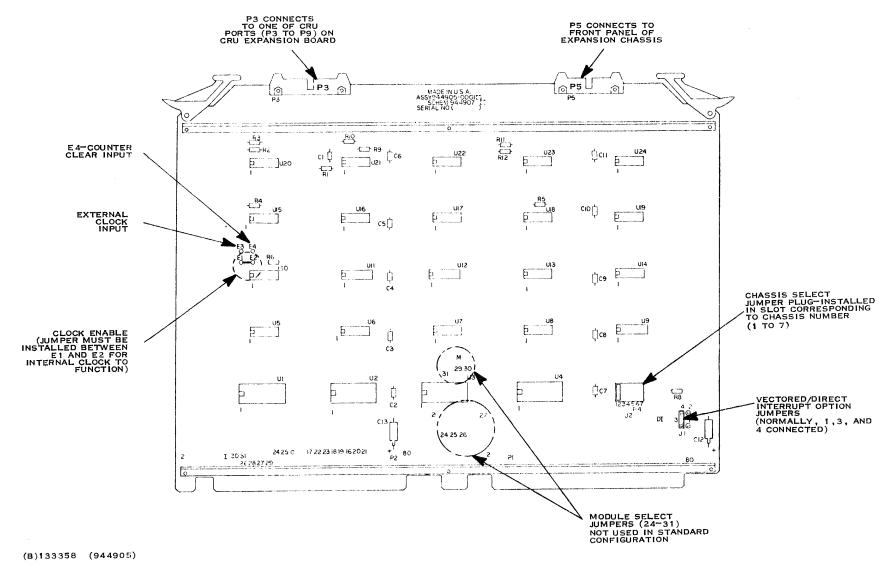

| 2-25   | CRU Buffer Board Options                                                       | 2-35 |

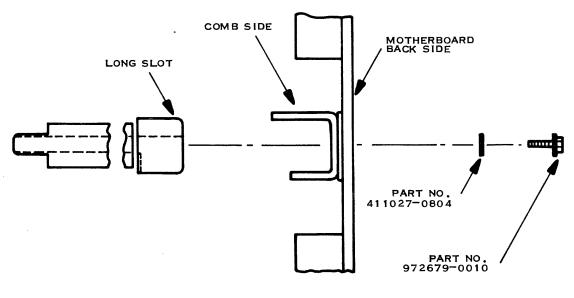

| 2-26   | Center Card Guide Installation Diagram                                         | 2.38 |

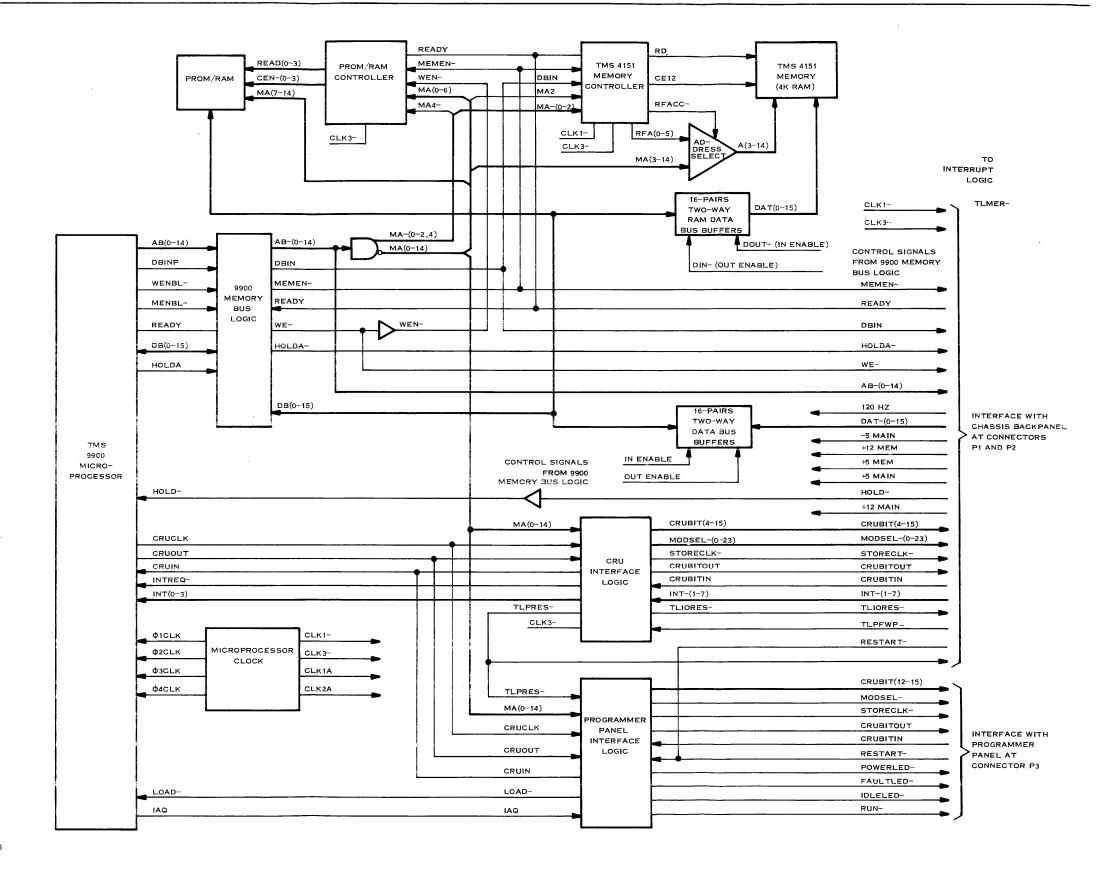

| 3-1    | 990/4 Circuit Board Block Diagram                                              |      |

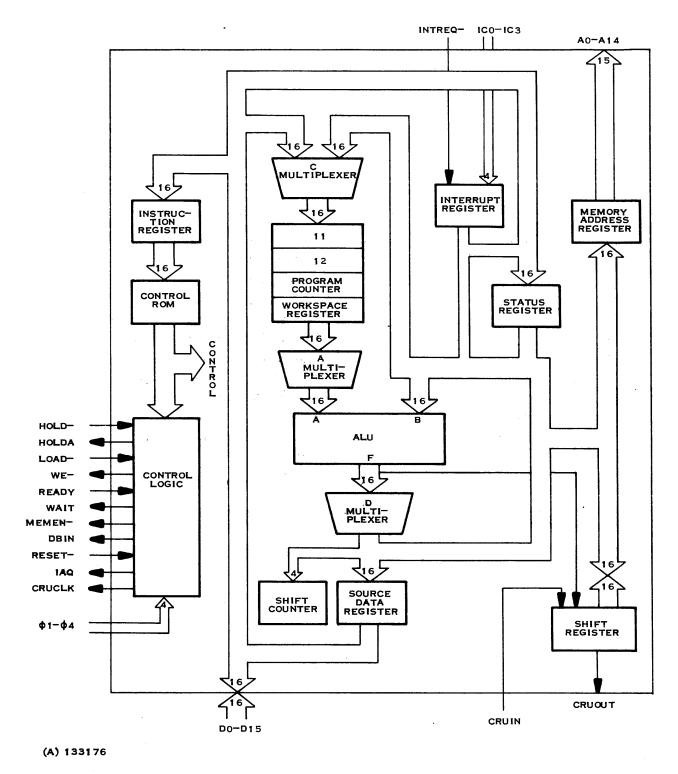

| 3-2    | TMS 9900 Microprocessor Architecture                                           |      |

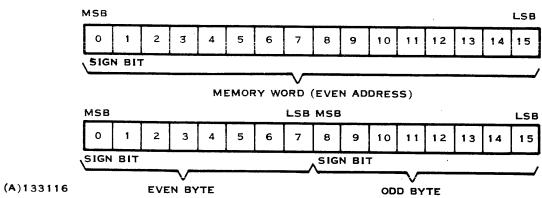

| 3-3    | Microprocessor Word and Byte Format                                            | 3-0  |

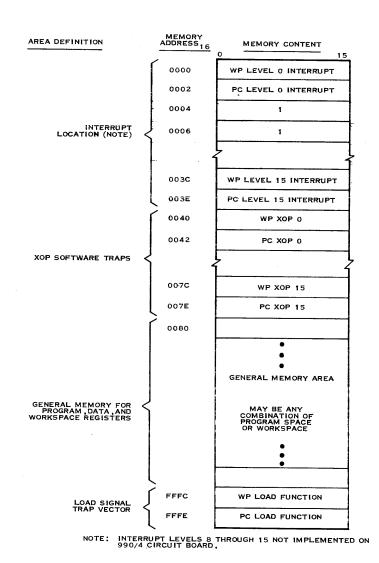

| 3-4    | TMS 9900 Memory Map                                                            | 3-1  |

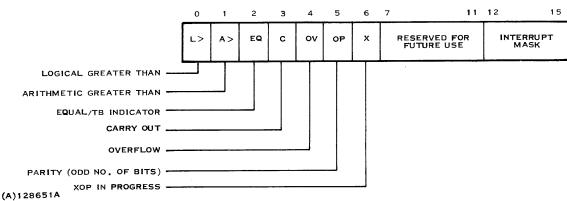

| 3-5    | Status Register Bit Assignments                                                | 3-/  |

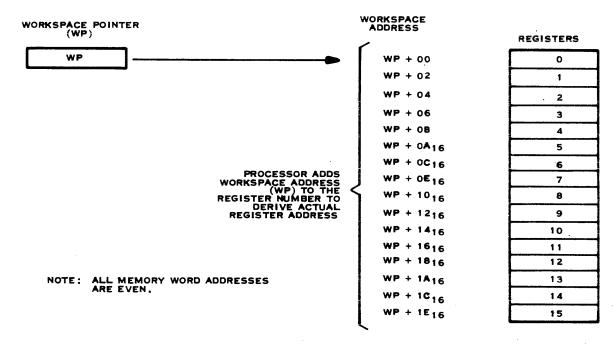

| 3-6    | Workspace Pointer and Registers                                                |      |

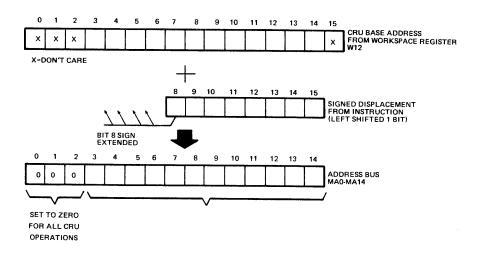

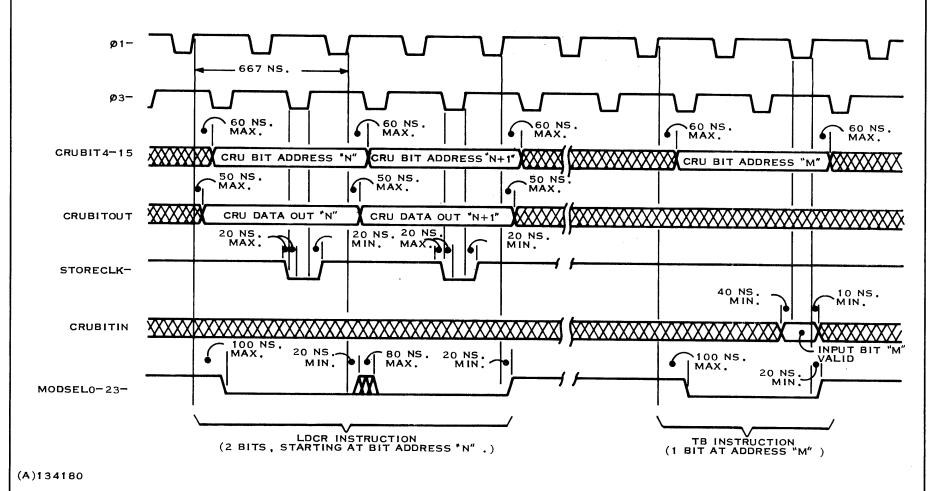

| 3-7    | TMS 9900 Single-Bit CRU Address Development                                    | 2.10 |

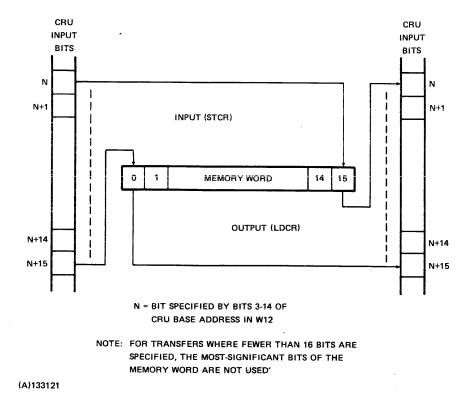

| 3-8    | TMS 9900 LDCR/STCR Data Transfer                                               | 3-10 |

| 3-9    |                                                                                |      |

| 3-10   |                                                                                | 3-16 |

| 3-10   | 990/4-9900 Bus Functional Diagram                                              | 3-17 |

| 3-11   | 990/4 Chassis Signal Assignments — P1 Connector Pins                           | 3-18 |

| J-12   | 990/4-9900 Bus Timing                                                          | 3-23 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                            | Page      |

|--------|------------------------------------------------------------------|-----------|

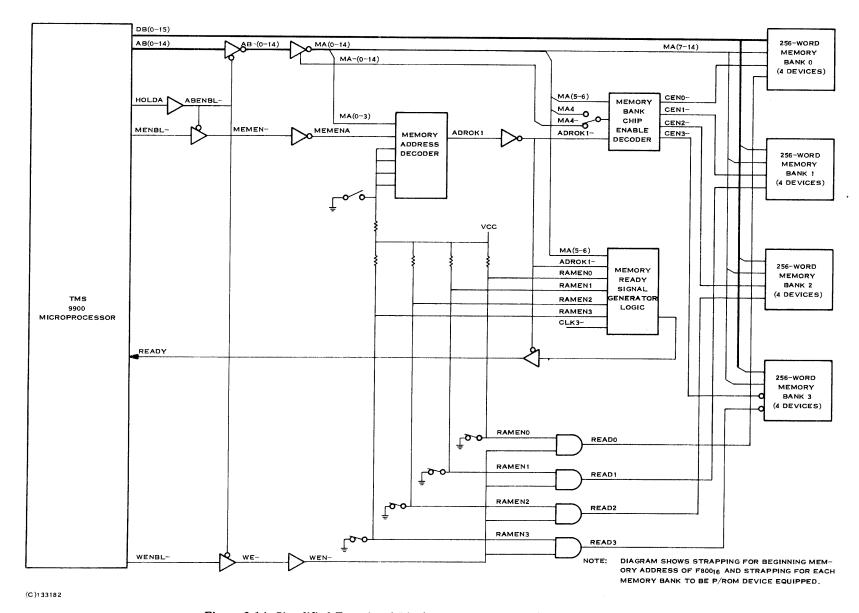

| 3-13   | Simplified Logic Diagram of 9900 Memory Bus                      | <br>.3-24 |

| 3-14   | Simplified Functional Block Diagram of PROM/RAM and Controller   | <br>.3-26 |

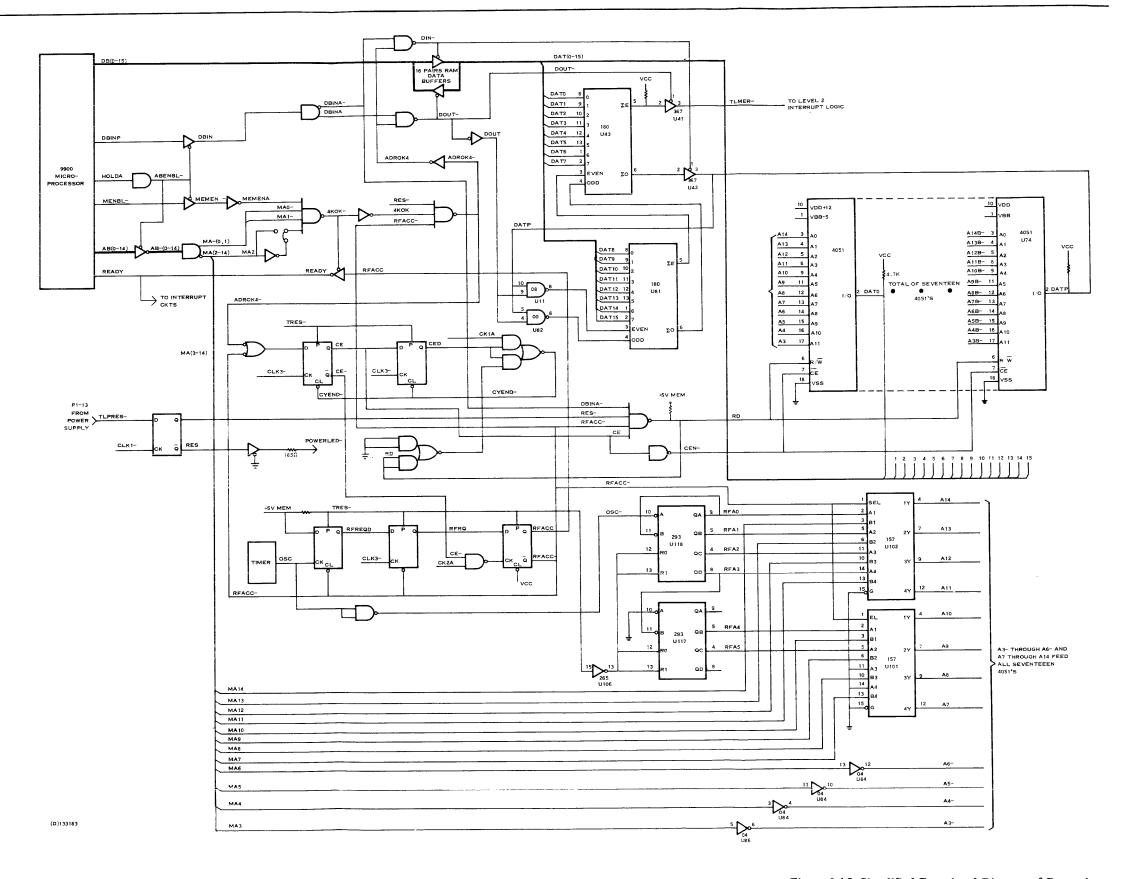

| 3-15   | Simplified Functional Diagram of Dynamic RAM and Controller      | <br>.3-29 |

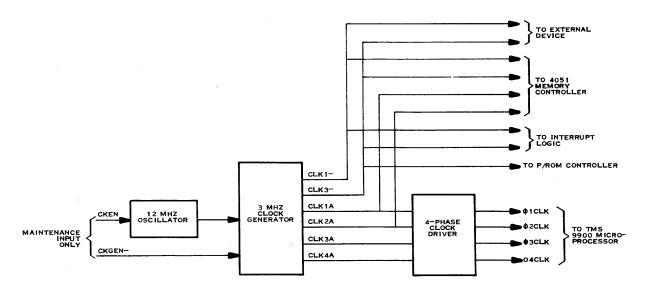

| 3-16   | Simplified Block Diagram of Microprocessor Clock                 | <br>.3-32 |

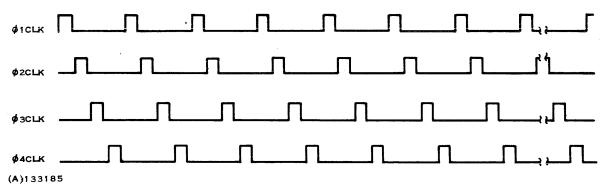

| 3-17   | Timing Diagram, 4-Phase Clock Input to Microprocessor            | <br>.3-33 |

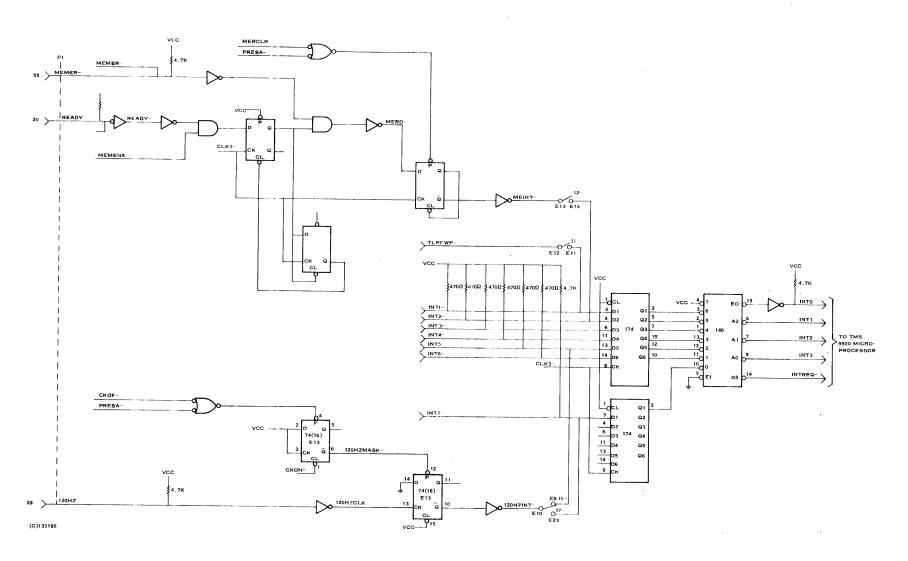

| 3-18   | 990/4 Circuit Board Interrupt Logic                              | <br>.3-35 |

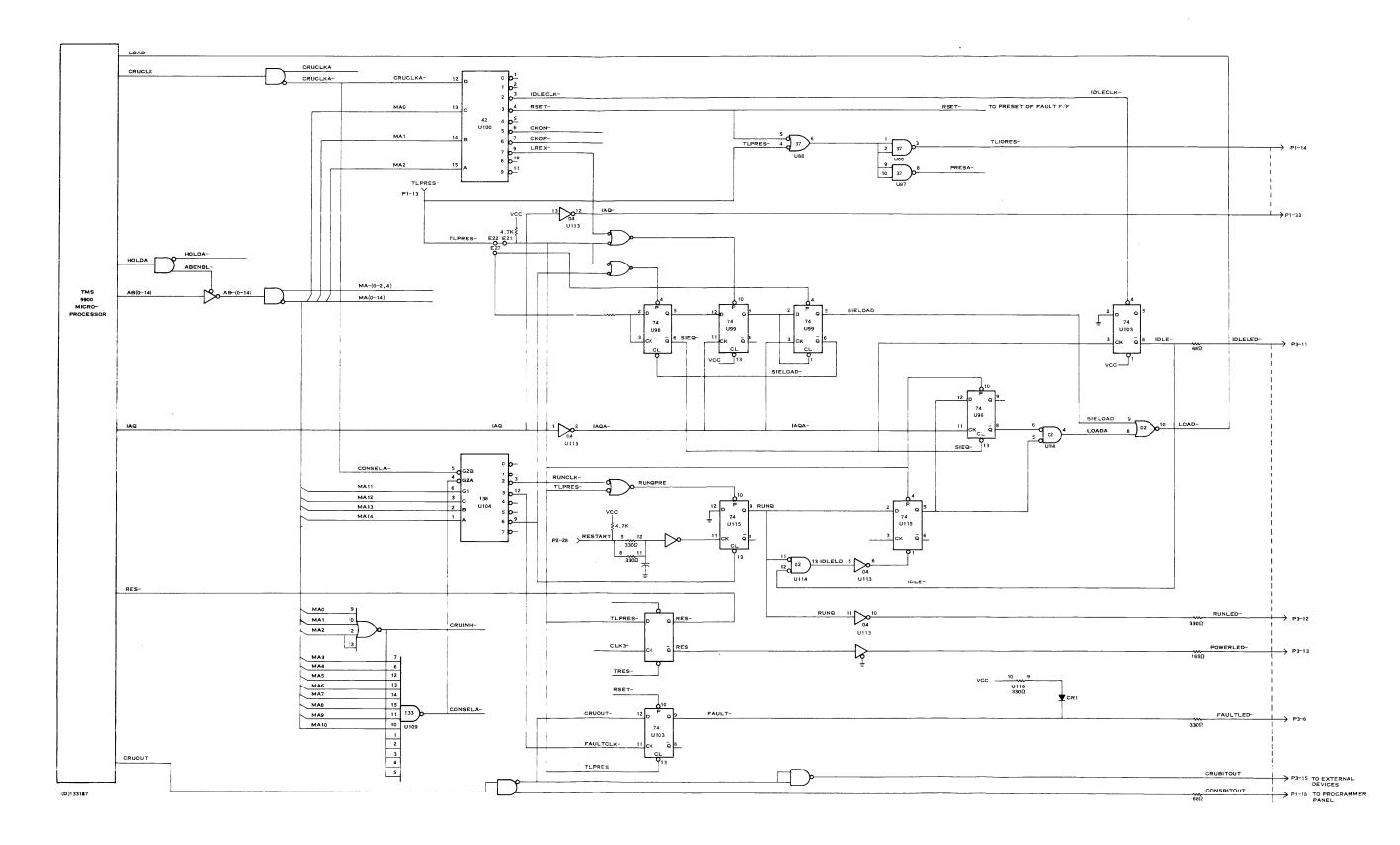

| 3-19   | Simplified Logic Diagram of External Instructions and Programmer |           |

|        | Panel Functions Implementation                                   | <br>.3-37 |

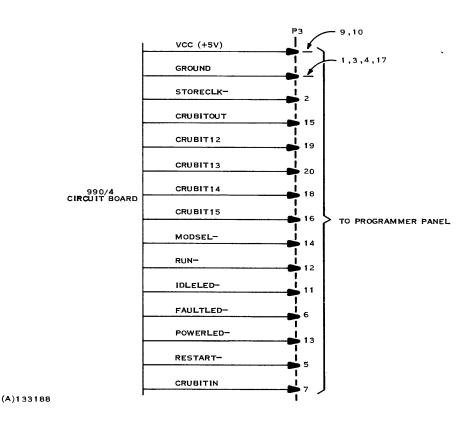

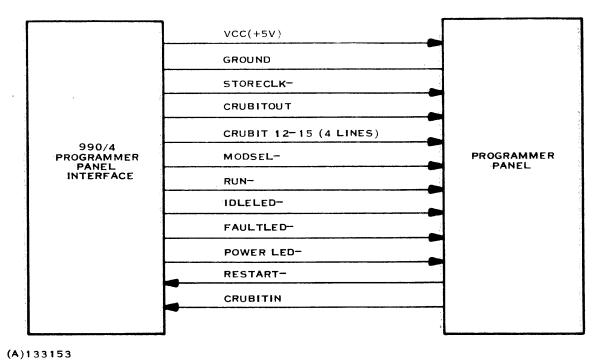

| 3-20   | Programmer Panel Interface Signals                               | <br>.3-40 |

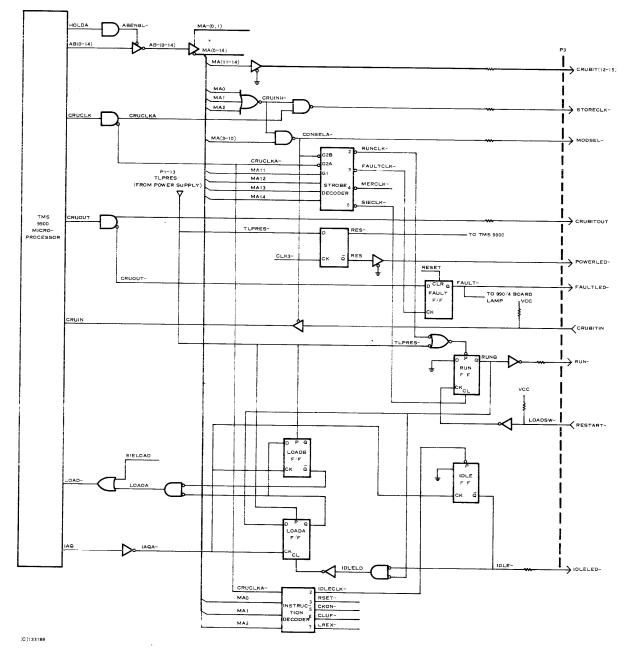

| 3-21   | Simplified Logic Diagram of Programmer Panel Interface           | <br>.3-41 |

| 3-22   | CRU Address Map for Standard Expansion Implementation Using      |           |

|        | 12-Inch Chassis                                                  | <br>.3-45 |

| 3-23   | Standard CRU Expansion Implementation Hardware                   | <br>.3-46 |

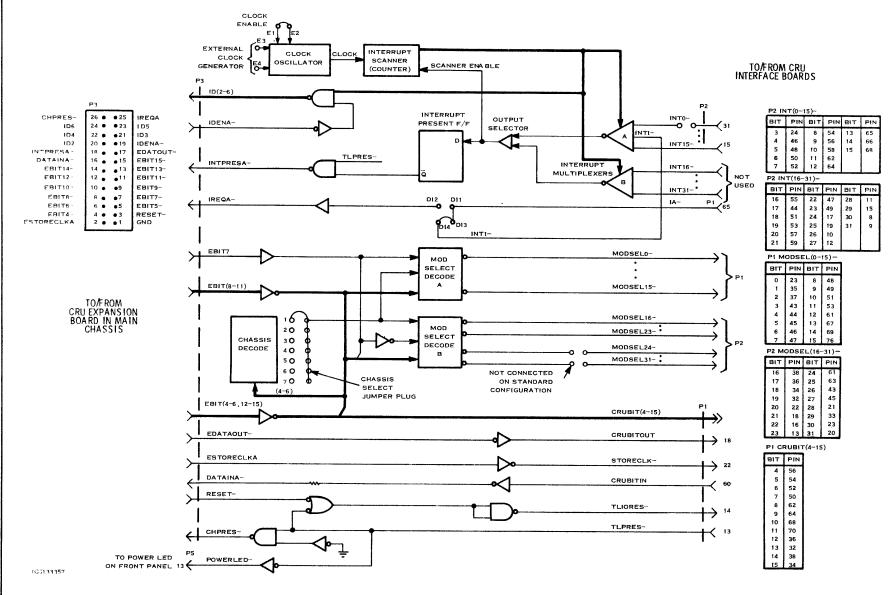

| 3-24   | Simplified Logic Diagram of 990/4 CRU Interface Implementation   | <br>.3-47 |

| 3-25   | Chassis Power Supply Timing                                      | <br>.3-50 |

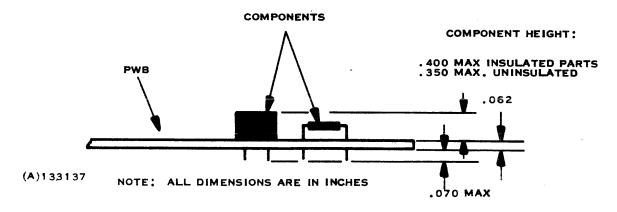

| 3-26   | CRU Circuit Board Dimensions Required                            | <br>.3-51 |

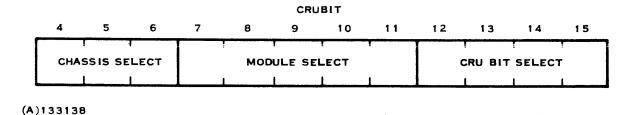

| 3-27   | CRU Address Field Assignments                                    |           |

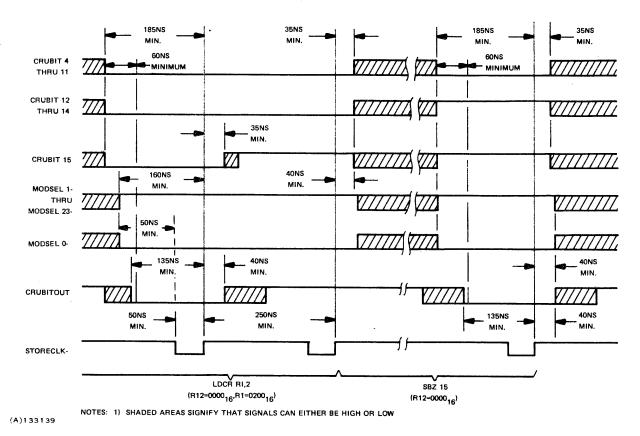

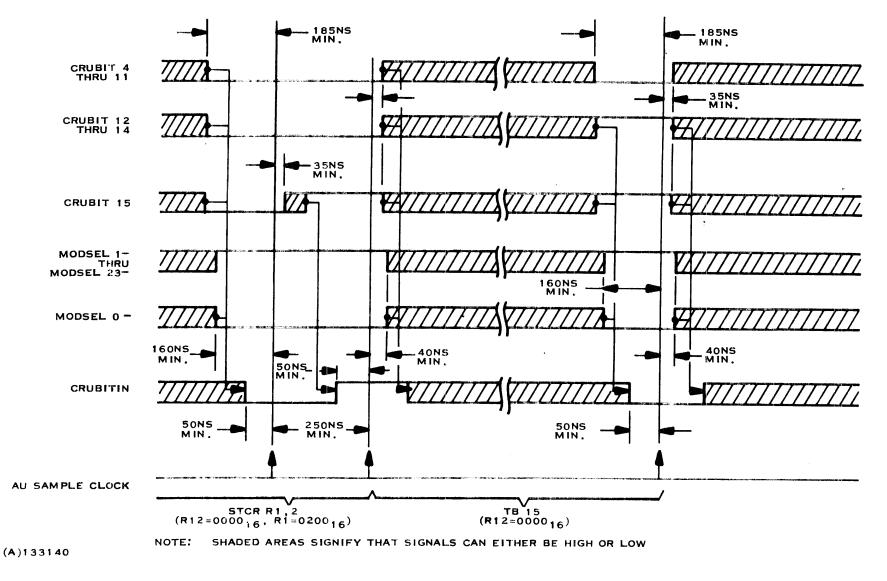

| 3-28   | CRU Output Timing Minimum Restrictions                           |           |

| 3-29   | CRU Input Timing Minimum Restrictions                            |           |

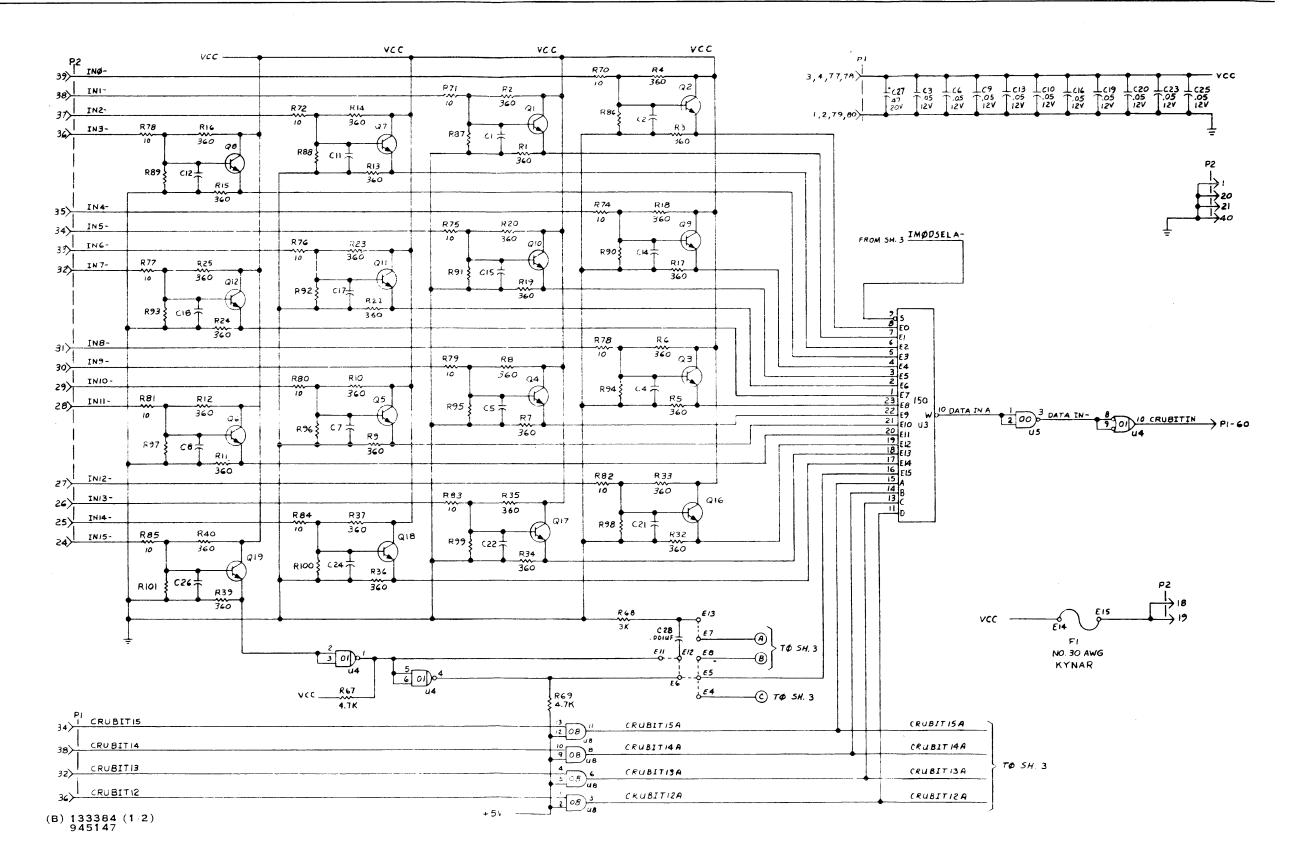

| 3-30   | Example CRU Module - Logic Diagram of 16 I/O TTL Data Module     | <br>.3-55 |

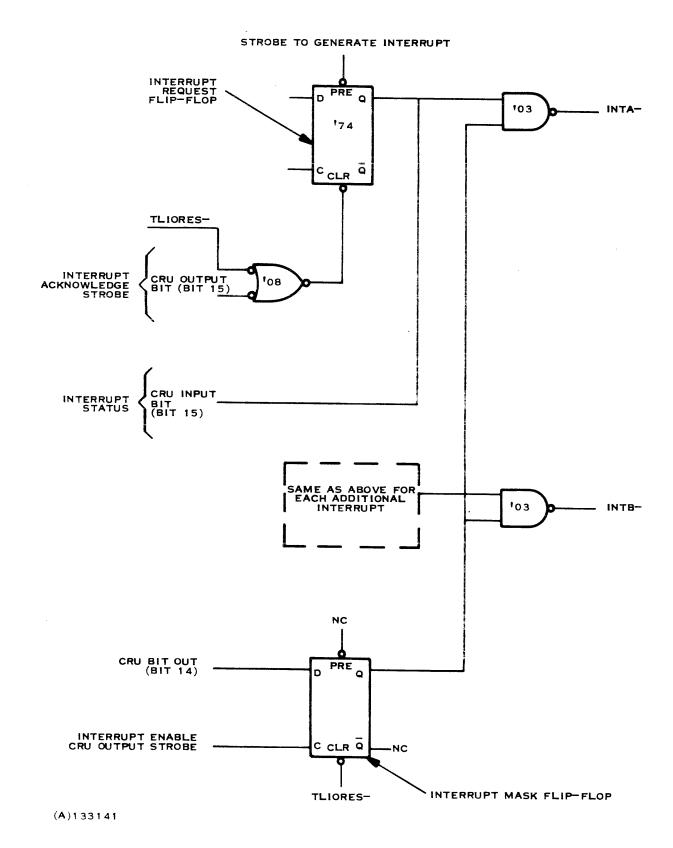

| 3-31   | CRU Interrupt Implementation                                     |           |

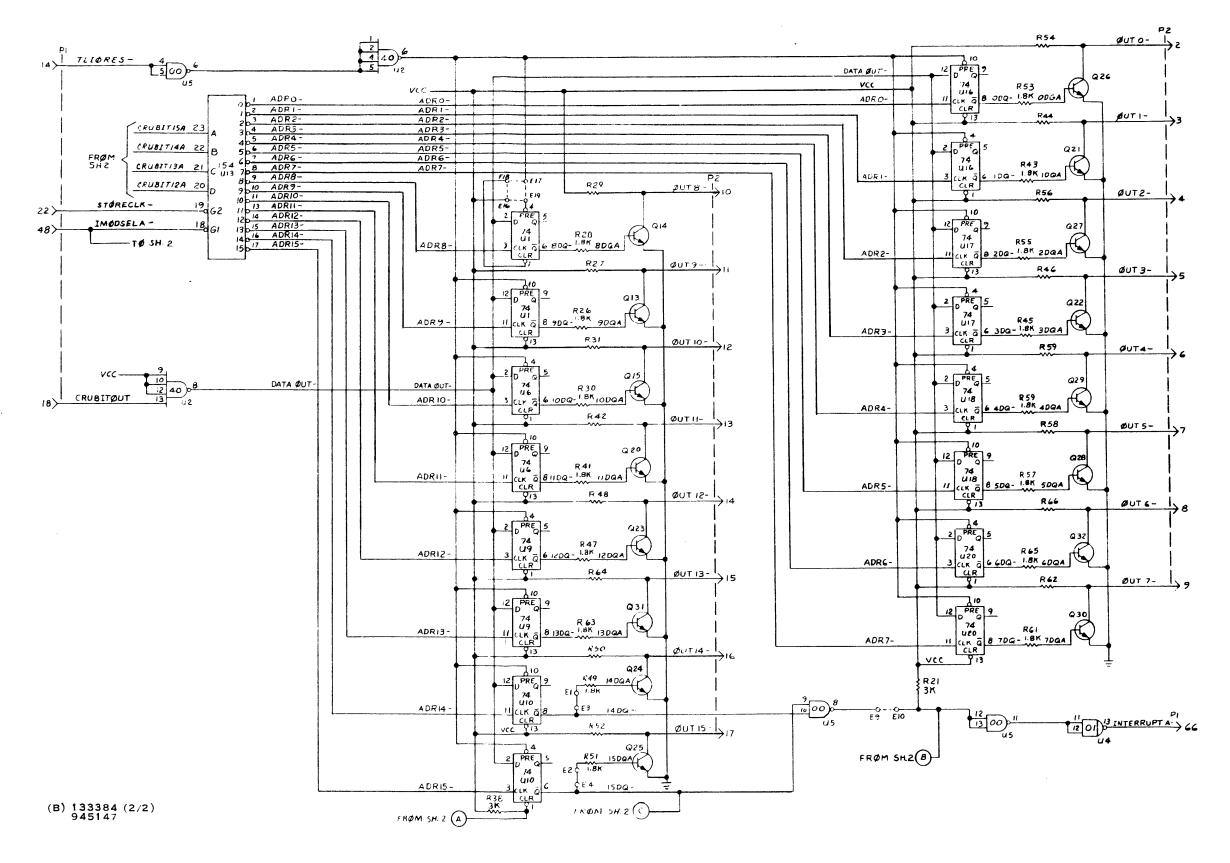

| 3-32   | 990/4 Memory Expansion Board Block Diagram                       | <br>.3-66 |

| 3-33   | EPROM Memory Module Block Diagram                                |           |

| 3-34   | OEM Chassis Physical Configuration                               |           |

| 3-35   | OEM Chassis Backpanel Schematic                                  | <br>.3-75 |

| 3-36   | Operator Front Panel, 6-Slot Chassis                             |           |

| 3-37   | 6-Slot Chassis Physical Configuration                            |           |

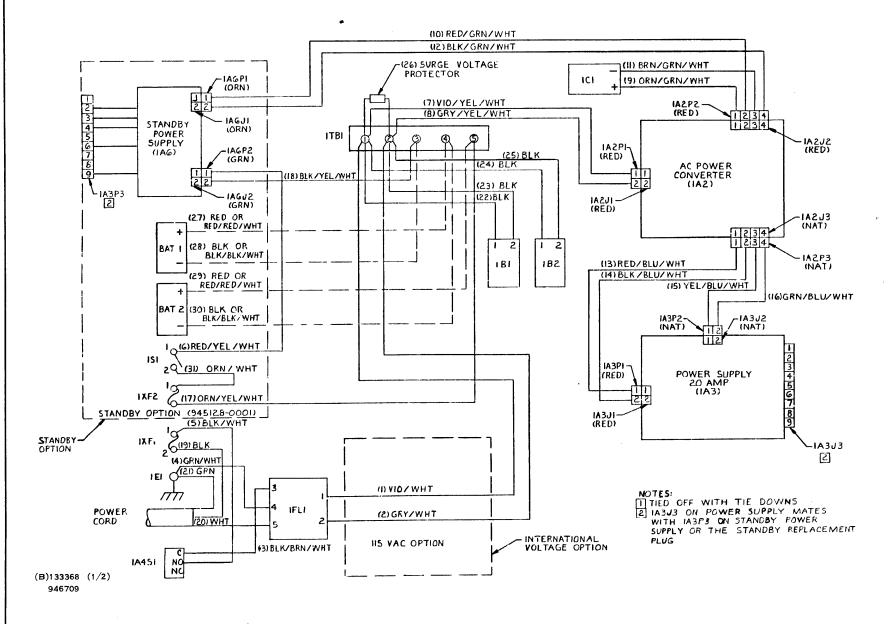

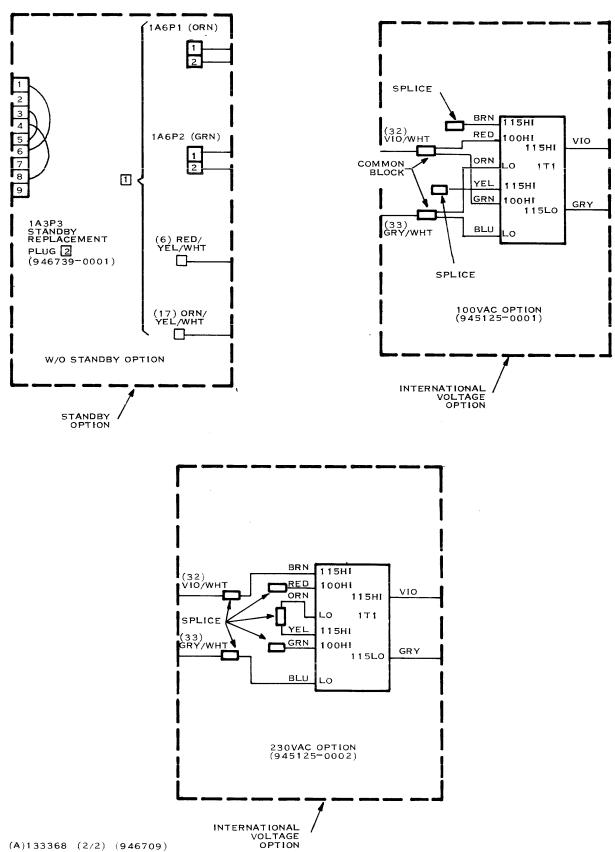

| 3-38   | 6-Slot Chassis Wiring Diagram                                    | <br>.3-78 |

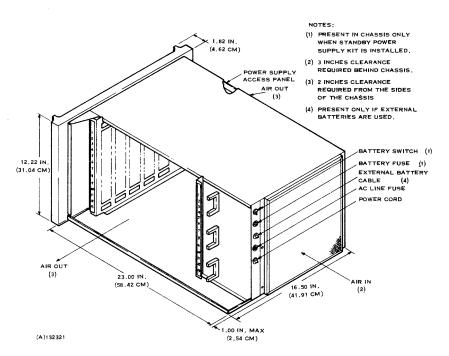

| 3-39   | 13-Slot Chassis Physical Configuration                           | <br>.3-80 |

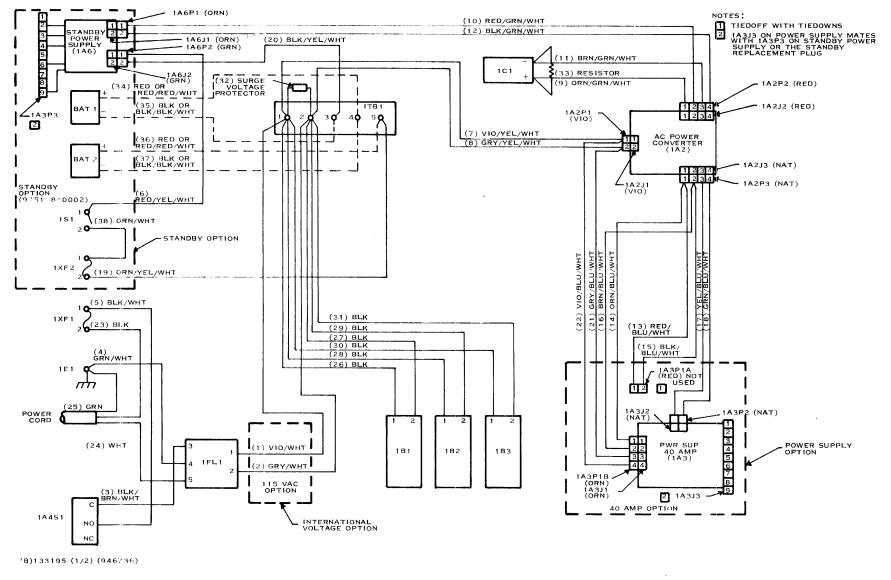

| 3-40   | 13-Slot Chassis Wiring Diagram                                   | <br>.3-81 |

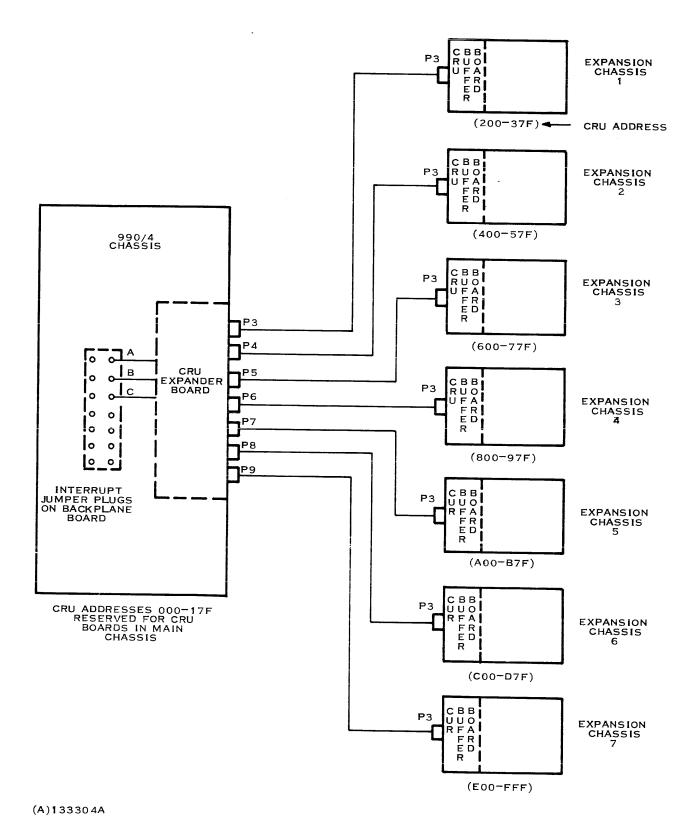

| 3-41   | CRU Expansion, Simplified Block Diagram                          | <br>.3-83 |

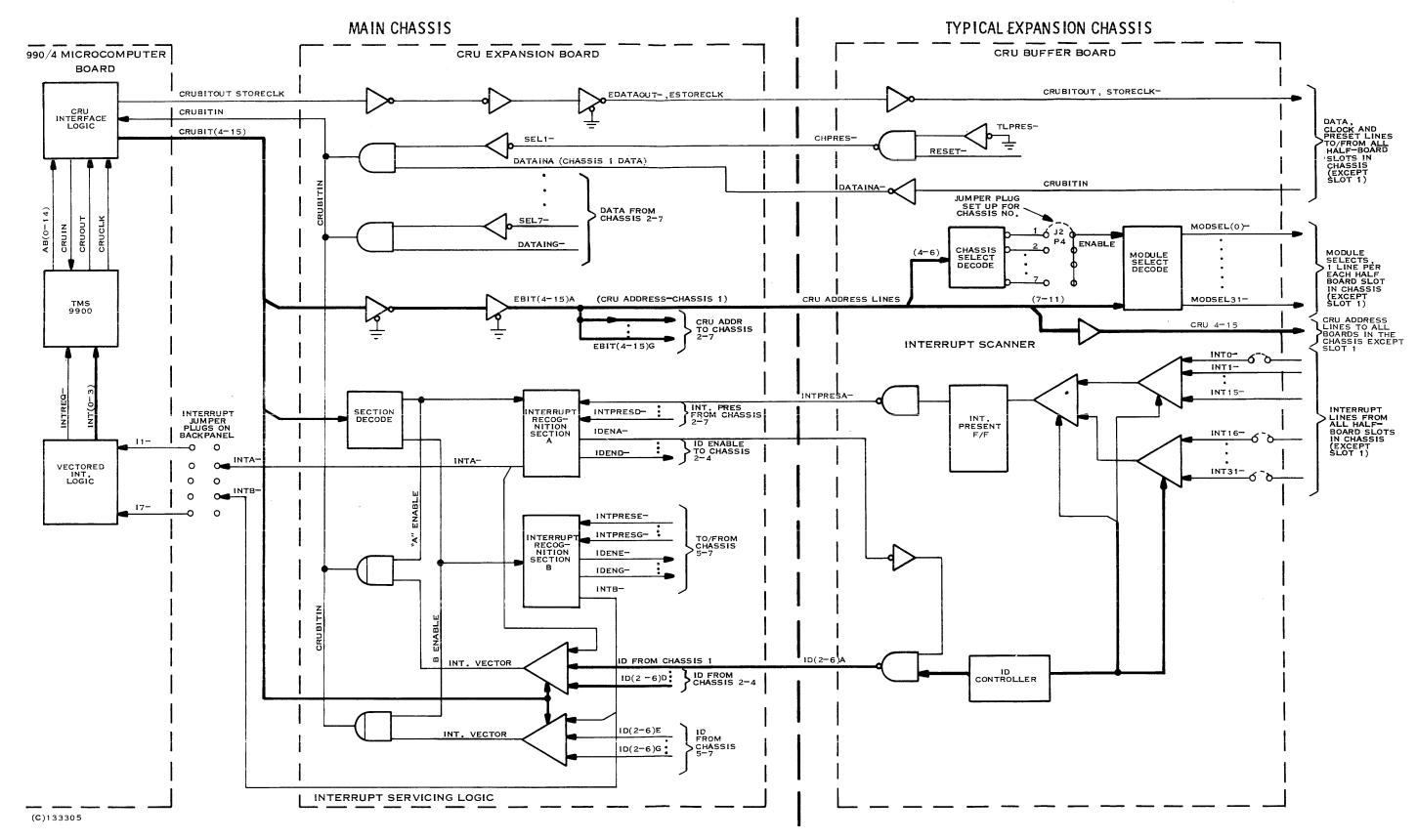

| 3-42   | CRU Expansion System, Functional Diagram                         | <br>.3-85 |

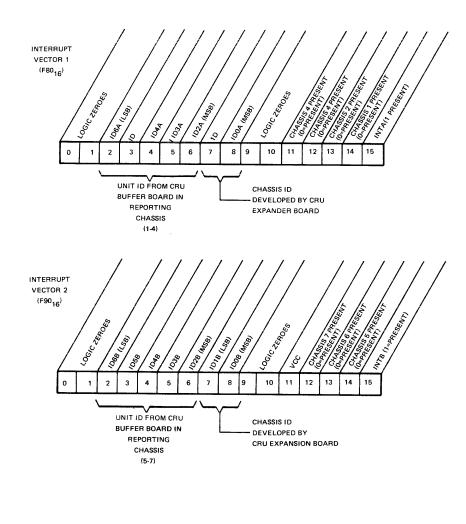

| 3-43   | Expansion Interrupt Vector Format                                | <br>.3-87 |

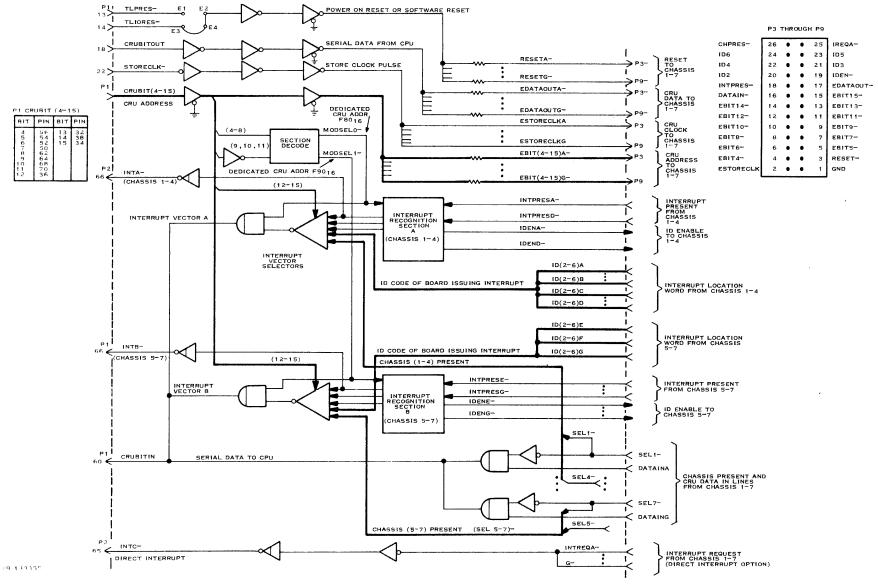

| 3-44   | CRU Expander Board Block Diagram                                 |           |

| 3-45   | CRU Buffer Board Block Diagram                                   | <br>.3-90 |

| 3-46   | 990 Programmer Panel Controls and Indicators                     |           |

| 3-47   | Programmer Panel Functional Block Diagram                        |           |

| 3-48   | Switch Scanner Block Diagram                                     |           |

| 3-49   | Programmer Panel Interface Diagram                               | <br>.3-98 |

| 3-50   | Block Diagram of Ac Power Converter and Filters                  | <br>3-104 |

| 3-51   | Block Diagram of 20-Ampere Power Supply                          |           |

| 3-52   | Standby Power Supply, Simplified Block Diagram                   | <br>3-109 |

# LIST OF TABLES

| Table | Title .                                            | Page |

|-------|----------------------------------------------------|------|

| 2-1   | Computer Chassis Specifications                    | 2-2  |

| 2-2   | 990/4 Circuit Board Jumper Options                 |      |

| 2-3   | 990/4 Memory Expansion Board Jumper Options        |      |

| 2-4   | EPROM Memory Module Jumper Options                 |      |

| 2-5   | CRU Expansion Board Jumper Options                 |      |

| 2-6   | CRU Buffer Board Jumper Options                    |      |

| 3-1   | TMS 9900 Microprocessor Characteristics            | 3-5  |

| 3-2   | Dedicated Workspace Registers                      | 3-8  |

| 3-3   | TMS 9900 Microprocessor External Instruction Codes | 3-12 |

| 3-4.  | TMS 9900 Pin Assignments and Functions             | 3-13 |

| 3-5   | Interrupt Level Data                               |      |

| 3-6   | CRU Interface Signals                              |      |

| 3-7   | CRU Circuit Board Signals                          | 3-54 |

| 3-8   | Programmer Panel Controls and Indicators           |      |

| 3-9   | Programmer Panel Interface Connections             |      |

| 3-10  | Programmer Panel CRU Input Bit Assignments         |      |

| 3-11  | Programmer Panel CRU Output Bit Assignments        |      |

| 3-12  | 20-Ampere Power Supply DC Power Output             |      |

| 3-13  | Standby Power Supply Specifications                |      |

| 3-14  | Standby Operations Specifications                  |      |

133171 (990-975-2-21)

133172 (990-875-7-5)

133174 (990-975-2-8)

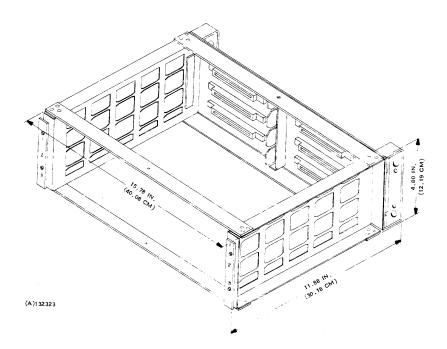

Figure 1-1. Model 990/4 Microcomputer in Three Packaging Options

#### SECTION I

#### GENERAL DESCRIPTION

#### 1.1 GENERAL

This manual provides operation and installation instructions for the Model 990/4 Microcomputer System manufactured by Texas Instruments Incorporated. The manual also provides sufficient hardware description to permit the user to modify existing logic boards or custom design new logic boards for special system applications.

This section provides a brief physical and functional description of the Model 990/4 Microcomputer System (figure 1-1) and describes the options available. For ease of reference, the Model 990/4 Microcomputer System is referred to as the 990/4 Microcomputer System or simply the 990/4.

### 1.2 PURPOSE OF EQUIPMENT

The 990/4 Microcomputer System is a low-cost, high-performance computer system constructed around the TMS 9900 16-bit microprocessor chip. The microcomputer system may be configured as a general-purpose computer with a wide range of supporting peripherals or it may be implemented as a special-purpose controller with a minimum configuration OEM chassis and limited set of peripherals.

#### 1.3 HARDWARE DESCRIPTION

The 990/4 Microcomputer System consists of a main chassis (one of three optional types) and up to seven optional I/O expansion chassis for adding peripherals to the system when configuring large systems.

The main chassis in the 990/4 System consists of the following hardware units:

- 990/4 Microcomputer Board

Chassis Assembly

minimum configuration

- 990/4 Memory Expansion Board (optional)

- EPROM Memory Module (optional)

- CRU Expansion Board (optional)

- CRU Interface Board(s) (optional)

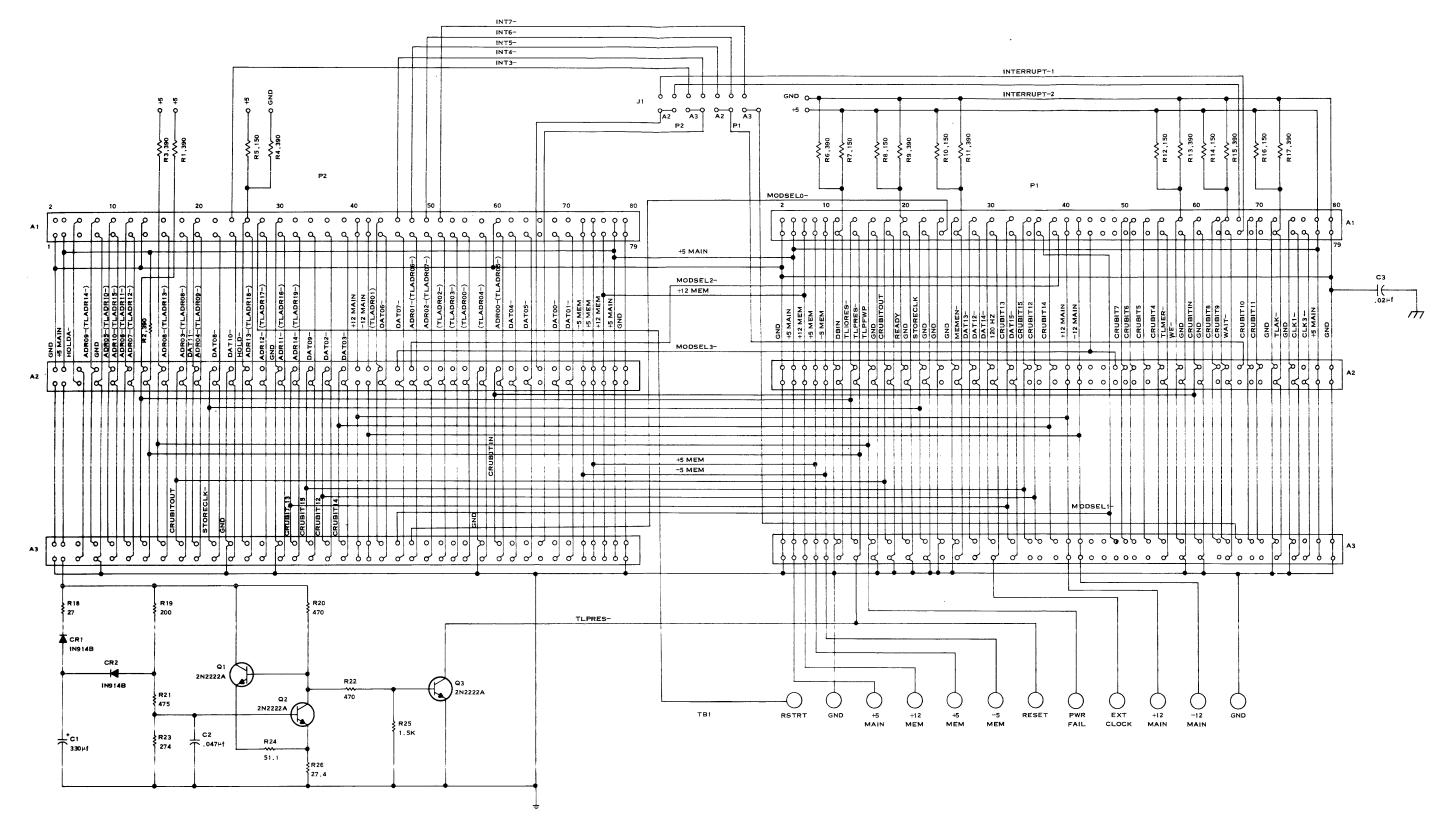

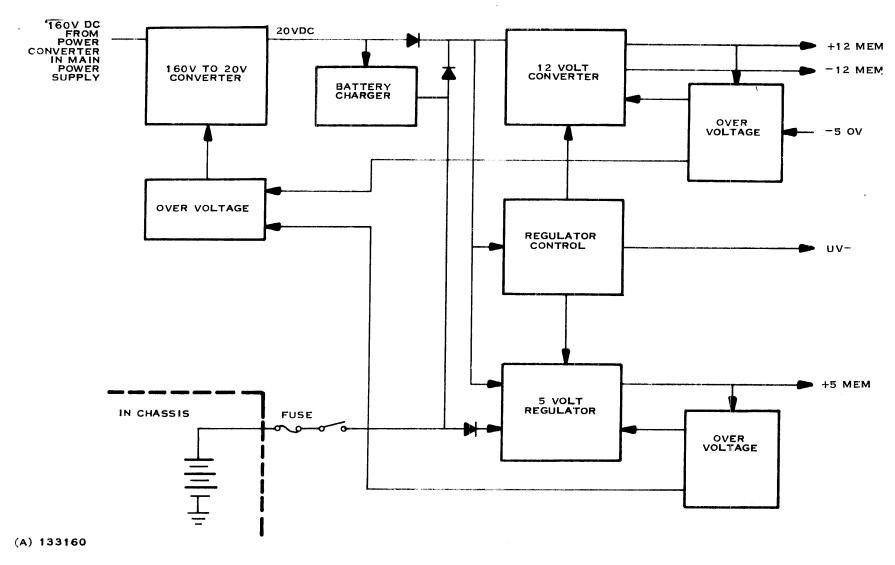

A simplified block diagram of the 990/4 System is shown in figure 1-2. The features and configurations of each unit in this figure are described in the following paragraphs.

NOTE: 3-SLOT OEM CHASSIS NOT EQUIPPED WITH POWER SUPPLIES OR PROGRAMMER/OPERATOR PANEL

(A)133173A

Figure 1-2. Model 990/4 Microcomputer System Block Diagram

- 1.3.1 990/4 MICROCOMPUTER. The 990/4 Microcomputer (figure 1-3) is a complete microcomputer on a single full-sized printed circuit board. The 990/4 Microcomputer includes the TMS 9900 microprocessor chip, supporting clock and interface logic plus two on-board memories. Some of the major features of the 990/4 Microcomputer board include:

- Up to 4K by 16-bit words of local on-board dynamic random access memory (RAM).

- Up to 1K by 16-bit words of local on-board read only memory (ROM) or static RAM.

- Microprocessor capability for direct accessibility of up to 32K by 16-bit words of memory.

- Communications register unit (CRU) serial I/O channel.

- Sixteen-Bit-Parallel I/O channel for communications with external memory or direct memory access controllers.

- Eight vectored interrupts plus provisions for real-time clock and power-up interrupts from power supply and memory interrupts from on-board and external RAM memories using optional error detect circuits.

- One CRU interface for the programmer panel (or operator panel).

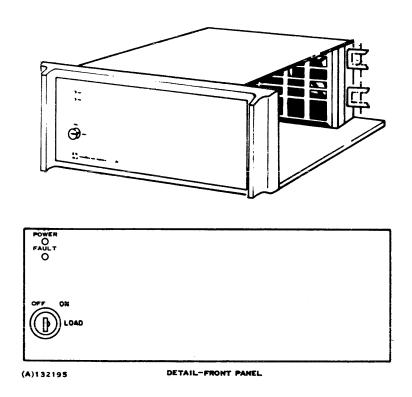

Figure 1-3. 990/4 Microcomputer Board

The special-purpose controller configuration of the 990/4 Microcomputer comes equipped with one bank of 256 by 16-bit words of static RAM. Four TMS 4043 (256 × 4) static RAM devices are mounted in four 16-pin sockets to form the 256-word bank of memory. Twelve additional 16-bit sockets are available to allow implementation of up to 768 words of either static RAM or PROM (programmable ROM) in 256-word increments. Each 256-word bank must be either all static RAM or all PROM. The PROM devices are SN74S287 256 by 4-bit programmable read only memory ICs.

The general-purpose computer configuration of the 990/4 Microcomputer is equipped with 4K by 16-bit words of MOS dynamic RAM. Sixteen TMS 4051 devices (4096 × 1) are required to provide the 4K words of memory. A seventeenth TMS 4051 is used in a factory-installed parity option for the dynamic RAM. This second configuration of the 990/4 Microcomputer board has sixteen 16-pin sockets for the addition of up to 1024 words of static RAM or ROM in 256-word increments. A third configuration of the microcomputer board is the same as the second configuration except that a set of eight ROMs are installed in eight of the memory sockets. These ROMs contain the on-board CPU basic diagnostics, bootstrap loader program and programmer panel software.

1.3.2 CHASSIS ASSEMBLY. The Model 990/4 Microcomputer System may be implemented in a 3-slot, 6-slot or 13-slot chassis assembly. The 6-slot and 13-slot chassis contain built-in power supplies, cooling fans, and either an operator panel or a programmer panel. The features and options available in each of the chassis assemblies are discussed in more detail in the following paragraphs.

- 1.3.2.1 3-Slot OEM Chassis. The low-cost 3-slot OEM chassis option consists of a 3-slot chassis assembly with a 3-slot chassis backpanel. In the 3-slot configuration, slot 1 of the backpanel is wired to accept the full-sized 990/4 Microcomputer printed circuit board and the other two slots are wired to accept two full-sized logic boards or four half-sized boards. However, the 3-slot OEM chassis is not equipped with built-in power supplies or cooling fans; the user must supply the computer with a source of regulated dc power and cooling air.

- 1.3.2.2 6-Slot Chassis. The 7-inch, 6-slot chassis consists of a chassis and backpanel which accommodates the 990/4 Microcomputer board in slot 1 (or CRU buffer board when used as an I/O expansion chassis), up to six full-sized logic boards, a built-in 20-ampere power supply, and either a programmer panel or an operator panel. The user may also select an optional standby power supply consisting of a standby power supply board (mounts on and connects to the 20-ampere power supply), a 12-volt battery and a chassis-mounted switch and fuse.

During normal operation, the standby power supply board maintains a trickle charge on the battery and develops the regulated dc voltages used in the semiconductor memory circuits. During a power-failure condition, the board automatically switches to battery operation to preserve data in the semiconductor memory.

The backpanel of the 6-slot chassis is wired to accept the 990/4 Microcomputer in slot 1; the other five slots are wired to accept five full-sized logic boards or as many as 10 half-sized logic boards. An air filter and fans provide filtered air cooling for the power supplies and circuit cards mounted in the chassis.

- 1.3.2.3 13-Slot Chassis. The 12-inch, 13-slot chassis is an enlarged version of the 6-slot chassis that accommodates a greater number of logic boards. The 13-slot chassis is used both as a main chassis for the microcomputer and as an I/O expansion chassis for CRU-type devices only (all DMA devices must be implemented in main chassis). The 13-slot chassis assembly consists of a chassis backpanel with slots for 13 full-sized logic boards, a 40-ampere power supply, and either a programmer panel or an operator panel. The standby power supply is also available with the 13-slot chassis. The backpanel is wired to accept the 990/4 Microcomputer board (or CRU buffer card when used as an expansion chassis) in slot 1 and the remaining 12 slots are wired to accept 12 full-sized logic boards or as many as 24 half-sized logic boards.

- 1.3.3 990/4 MEMORY EXPANSION BOARD. The optional memory expansion board (module) is a full-sized, double-sided, 160-pin printed circuit board that installs in one of the chassis slots of the main chassis other than slot 1. The interconnections between the expansion board and the memory and CRU buses on the 990/4 Microcomputer board are accomplished through etch wiring on the chassis backplane. When fully implemented, the memory expansion board provides 20K words of dynamic random access memory (RAM) storage. The board is also available in memory sizes ranging from 4K to 20K in 4K increments. However, the memory size is set up at the time of manufacture and is not alterable in the field. Each 4096-word increment uses 16 Texas Instruments TMS 4050 integrated circuit devices. Each of the 16 TMS 4050s is a high-speed dynamic 4096-bit MOS circuit organized as 4096 one-bit words. As another option, odd parity may be factory-implemented by installing a seventeenth TMS 4050 for each 4K words of memory storage and installing two parity generator/checker ICs on the board. Data is preserved in the dynamic MOS memory storage cells on the board by performing a memory refresh cycle at each of 64 row addresses every two milliseconds.

The expansion memory module is addressed in a block of consecutive addresses with the start address set for zero or any 4K work boundary in the memory address space. The start address is selected via switches on the board, and the upper limit address is indicated by module-sized jumper wires. The expansion memory is electrically connected to the memory bus in the main chassis and may be accessed for read and write operations by either the TMS 9900 Microprocessor or by a direct memory access controller (installed in the main chassis only). A memory protect option adds the capability to define a write protect zone in memory. The boundaries of the protected zone are programmable in 256-word increments. The protected zone is defined by two 7-bit registers that are addressed through a CRU interface with the 990/4 Microcomputer board. The protect function may be disabled under program control without altering contents of the boundary registers. An attempt to write to protected memory results in a setting of a software-readable Protect Violation flag that may be wired (optionally) to any unused interrupt level.

1.3.4 EPROM MEMORY MODULE. The EPROM (Erasable, Programmable Read Only Memory) module is an optional memory board equipped with IC sockets and associated addressing and control logic to accommodate from 1K to 8K of field expandable memory. The EPROM memory is currently implemented with INTEL 2708 1024 by 4-bit EPROM ICs. The EPROM board may be used in either a 990/4 or 990/10 System simply by connecting the correct set of jumper wires corresponding to the computer type.

The EPROM memory is also addressed in a block of consecutive addresses with the start address set to zero or any 1K boundary in the 990/4's 32K address space.

- 1.3.5 CRU INTERFACE BOARDS. The main chassis may optionally contain a number of CRU interface boards to provide an interface between the computer's serially oriented CRU bus and each of the parallel-data oriented peripherals in the system. CRU boards are available for all standard peripherals such as card readers, video display terminals, teleprinters and other similar devices. In addition, 16 I/O data modules are available which provide a general-purpose 16-bit input and output interface between the CRU and any device requiring EIA or TTL levels at its interface. Section III of this manual provides sufficient CRU interface card design data to permit a user to custom-build a new CRU interface card or modify any existing card to accommodate any specific requirements not met by the line of CRU interface cards presently being manufactured by Texas Instruments.

- 1.3.6 CRU EXPANSION BOARD. The CRU expansion board is an optional plug-in module used in the main chassis to expand the CRU interface signals present at the chassis backpanel to drive up to seven expansion chassis. Each of seven connectors on the CRU expansion board may be cabled to an associated connector on the CRU buffer board located in slot 1 of each expansion chassis.

The CRU expansion board also contains provisions for monitoring the interrupt lines from chassis 1 through 4 (designated Section A) and chassis 5 through 7 (Section B). The board then issues either an A or B interrupt to the computer indicating the chassis group in which the interrupt occurred. The CRU expansion board also develops and provides temporary storage for a 16-bit interrupt vector which may be read under software control to determine the source of the interrupt. In addition to the above described interrupt scheme, the CRU expansion board also fans in direct interrupt lines from all seven chassis and issues an interrupt to the microcomputer if a direct interrupt is detected from any board in any of the seven expansion chassis. The direct interrupt feature is used to permit more rapid interrupt recognition for those peripherals in the expansion chassis that require a faster interrupt response than is available through the scanner method.

#### **SECTION II**

#### INSTALLATION AND OPERATION

#### 2.1 GENERAL

This section provides information and procedures for unpacking the computer from its shipping container, installing it in either a tabletop or a rackmounted configuration, and checking the operation of the newly installed computer system. The section also includes a procedure for modifying the interrupt structure of the computer and verifying that the proper jumper wire options have been installed. The procedures assume that the user has a fundamental knowledge of basic handtools and cabling techniques, but they do not require a detailed understanding of computer hardware or software. This section does not cover installation of any of the peripheral devices that may accompany the computer shipment. Installation instructions for those devices are included in the Installation and Operation manual that is shipped with each peripheral device. To aid in planning to meet the installation requirements for the computer, table 2-1 summarizes the specifications and requirements of the available chassis for the computer.

## 2.2 UNPACKING/PACKING (6- AND 13-SLOT CHASSIS)

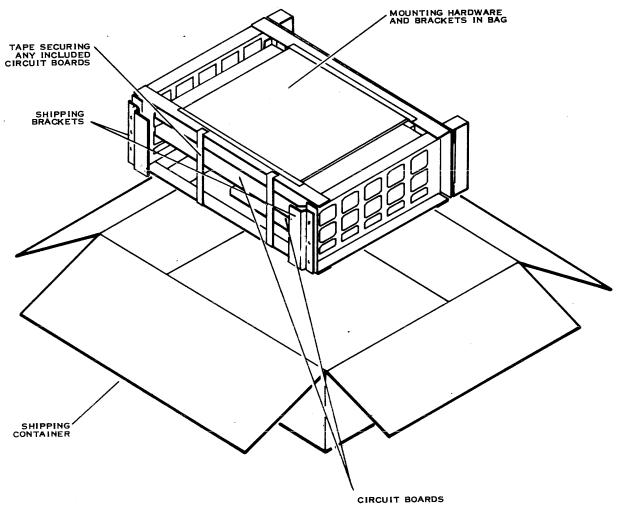

The computer is shipped in a corrugated cardboard container together with the circuit boards and interconnecting cables required to install the system. Upon receipt of the container, inspect to ensure that no signs of physical damage are present. After completion of the preliminary inspection, perform the following steps to remove the computer from its container and ready it for operation. Figure 2-1 illustrates the required steps.

### **NOTE**

Save shipping carton, shipping brackets and all packing materials for use in reshipment of the unit.

- 1. Position container so that the address label is right-side up.

- 2. Open top of container, and remove cushioning material from corners.

#### **NOTE**

If the computer has the tabletop enclosure (6-slot chassis only), no foam block is required to secure circuit boards in chassis.

3. Remove cardboard inner sleeve and foam block (rackmount configurations) from shipping container.

## **WARNING**

Use proper lifting techniques to avoid backstrain when lifting computer chassis.

4. Remove computer and attached shipping pallet from container. When lifting assembly, lift from under the assembly to avoid undue strain on the chassis assembly.

Table 2-1. Computer Chassis Specifications

| Characteristic                  | 6-Slot Chassis                                                        | 13-Slot Chassis                                                       | 3-Slot (OEM) Chassis                              |

|---------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------|

| Height                          | 7 inches<br>(17.8 cm)                                                 | 12-¼ inches (31.1 cm)                                                 | 4-13/16 inches (12.2 cm)                          |

| Width                           | 16-½ inches (41.9 cm)                                                 | 16-1/2 inches<br>(41.9 cm)                                            | 11-7/8 inches (30.2 cm)                           |

| Depth                           | 23 inches (58.4 cm)                                                   | 23 inches (58.4 cm)                                                   | 15-¾ inches (40.1 cm)                             |

| Ambient Temperature             |                                                                       |                                                                       |                                                   |

| Operating <sup>1</sup> with Low | 32° to 122° F<br>(0° to 50° C)                                        | 32° to 122° F<br>(0° to 50° C)                                        | 32° to 122° F<br>(0° to 50° C)                    |

| Speed Fan                       | 32° to 95° F<br>(0° to 35° C)                                         | 32° to 95° F<br>(0° to 35° C)                                         | Does not apply                                    |

| Storage                         | 40° to +158° F<br>(40° to +70° C)                                     | -40° to 158° F<br>(-40° to +70° C)                                    | 40° to +158°F<br>(40° to +70° C)                  |

| Humidity <sup>2</sup>           | 0% to 95%                                                             | 0% to 95%                                                             | 0% to 95%                                         |

| Altitude                        | 0 to 10,000 feet<br>(0 to 3.05 km)                                    | 0 to 10,000 feet (0 to 3.05 km)                                       | 0 to 10,000 feet (0 to 3.05 km)                   |

| Heat Load                       |                                                                       |                                                                       | •                                                 |

| Full Card Slot<br>Power Supply  | 50 watts<br>170 watts                                                 | 50 watts<br>170 watts                                                 | 50 watts <sup>3</sup><br>170 watts <sup>3</sup>   |

| Exhaust Temperature             | 149° F (maximum)<br>(65° C)                                           | 149° F (maximum)<br>(65° C)                                           | 149° F (maximum)<br>(65° C)                       |

| External Power Requirements     |                                                                       |                                                                       | , ,                                               |

| Standard                        | 115 Vac ± 10%<br>3-wire service<br>(hot, neutral, gnd)                | 115 Vac ± 10%<br>3-wire service<br>(hot, neutral, gnd)                | -5 Vdc ±6%<br>+5 Vdc ±3%<br>±12 Vdc ±3%<br>Ground |

| Optional                        | 100, 200 or<br>230 Vac ± 10%<br>3-wire service<br>(hot, neutral, gnd) | 100, 200 or<br>230 Vac ± 10%<br>3-wire service<br>(hot, neutral, gnd) | Does not apply                                    |

# Notes:

- 1. Lower the upper operating limit by 3.6° F (2° C) for every 2500 feet (762 meters) increase in altitude.

- 2. No condensation should be allowed.

- 3. Cooling capacity attainable only when externally supplied with a 600 feet/minute ambient air flow.

(A)133078

Figure 2-1. Computer Shipping Packaging

#### **CAUTION**

To prevent the mounting screws on the underside of the shipping pallet from scratching table surface, place a shielding material (the packing sleeve removed in step 3 makes an excellent shield) on the table before setting the assembly on the table.

5. Place the removed assembly on a convenient, protected work surface.

### **NOTE**

For rackmount configurations, the slides are packed in the bottom of the shipping container.

Remove rackmount slides (if present) and interface cables from bottom of shipping container.

#### **CAUTION**

In following steps, do not allow the unit to overhang the work surface so far that it will fall off the surface.

- 7. Position computer and shipping pallet assembly so that front edge of assembly overhangs edge of work surface to reveal two (2) #10 mounting screws that secure computer to shipping pallet. See figure 2-2 for location of all mounting screws.

- 8. Use a straight blade screwdriver to remove two screws and their associated washers and lock washers. Save screws and washers for reshipment.

- 9. Reposition computer and shipping pallet assembly so that rear edge of assembly overhangs the edge of work surface to reveal three (3) #10 mounting screws that secure computer to shipping pallet.

- 10. Remove the three screws, washers and lock washers and save for reshipment.

#### **NOTE**

If the computer was ordered for overseas operation, two (2) additional mounting screws are visible on the underside of shipping pallet. If these screws are not included on the unit being installed, skip step 11.

- 11. Remove two (2) #6 transformer mounting screws and their associated washers and lock washers, and save for reshipment.

- 12. Lift computer chassis from shipping pallet and place it on work surface such that the rear of unit overhangs work surface to reveal holes for previously removed mounting screws.

(A)133079

Figure 2-2. Location of Chassis Shipping Pallet Mounting Screws

#### **NOTE**

If unit being installed did not have the two #6 mounting screws (see step 11), skip step 13 and proceed to step 14.

- 13. Remove two (2) #6 screws taped to top of computer chassis and insert them in holes vacated by two #6 mounting screws removed in step 11. Tighten two new screws to secure transformer to chassis.

- 14. Remove strip of self-adhesive hole covers that are taped to top of computer chassis. Use three of the hole covers to cover three mounting screw holes along the rear of chassis.

- 15. Reposition computer chassis such that front edge overhangs work surface to reveal the mounting holes for front mounting screws.

- 16. Use remaining two (2) self-adhesive hole covers to cover front mounting screw holes.

- 17. Set computer chassis in a safe position on work surface to continue with remaining portions of installation procedure.

- 18. Pack all shipping materials into original shipping container and store container for use in reshipment of unit.

- 19. Inspect computer chassis (and included components) for signs of damage that may have occurred during shipment. If damage has occurred, notify the carrier immediately.

To repack the unit, reverse above procedure using original packing material.

#### 2.3 UNPACKING/PACKING (OEM CHASSIS)

The OEM chassis is shipped in a corrugated cardboard container together with the circuit boards and mounting hardware for the system. Upon receipt of the container, inspect to ensure that no signs of physical damage are present. After completion of the preliminary inspection, perform the following steps to remove the chassis from its container. Figure 2-3 illustrates the material included in the packing container.

#### **NOTE**

Save shipping carton and all packing materials for use in reshipment of the unit.

- 1. Position container so that address label is right-side up.

- 2. Open top of container and remove chassis assembly enclosed in cushion wrap.

- 3. Remove cushion wrap from chassis assembly.

- 4. Remove bag containing mounting hardware from chassis assembly.

(A)133080

Figure 2-3. OEM Chassis Shipping Packaging

## **NOTE**

If circuit boards are included in shipment, they are secured in place by shipping brackets. If no circuit boards are included, skip step 5.

- 5. Remove shipping brackets that secure circuit boards in chassis and save for use in reshipment of the unit.

- 6. Inspect the chassis and all included components for signs of damage that may have occurred during shipment. If damage has occurred, notify carrier immediately.

# 2.4 INSTALLATION (TABLETOP CHASSIS)

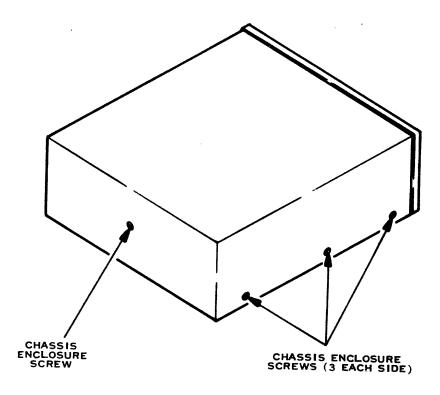

The tabletop chassis is a 6-slot chassis configuration contained in an attractive enclosure. The unit is shipped fully assembled to ensure that all components arrive safely. However, before operating the computer the enclosure must be removed to connect the computer to the system peripheral devices. The following procedure describes the steps required to completely integrate the new computer into its operating environment.

1. Set unpacked chassis assembly in the approximate installation position.

#### NOTE

The chassis enclosure is secured to the chassis by three (3) ovalhead screws on each side of the chassis and one (1) oval-head screw at the rear of the assembly as illustrated in figure 2-4.

- 2. Remove seven (7) oval-head screws and their associated finishing washers that secure the chassis enclosure to the chassis. Save screws and washers for reinstallation of enclosure.

- 3. Carefully lift enclosure up from the chassis and set enclosure in a safe place. Remove the shipping brackets that hold the logic boards in place and save for reuse at a later date.

(A)133299

Figure 2-4. Location of Chassis Enclosure Screws

#### NOTE

The chassis is shipped from the factory with interrupts installed in predetermined locations as illustrated in figure 2-5. CRU addresses are fixed and cannot be changed.

- 4. Determine chassis location and interrupt assignments for each peripheral interface in system. If interrupt assignments do not match the factory-installed interrupts, or if additional interrupt assignments are required, perform Interrupt Installation procedure in this section of manual.

- 5. Remove the interface modules, memory boards and processor boards from the chassis one at a time, and refer to the Circuit Board Jumper Modifications paragraph near the end of this section to verify that all jumper wires are properly installed. Return boards to original slots.

- 6. Install peripheral device interface cables on proper interface module in computer chassis as described in Installation and Operation manual included with peripheral device. All interface cables should be routed through cable clamps at rear of chassis and should exit at rear of chassis.

- 7. Connect ac power cord to a source of ac power with specifications applicable to equipment being installed.

- 8. Turn key switch on front panel to ON (or UNLOCK) position. Observe that POWER indicator (and the RUN indicator) on front panel light and that fans operate.

- 9. Perform System Checkout procedure specified later in this section of manual.

| SLOT<br>NO. | FIXED<br>CRU<br>BASE<br>ADDRESS | CIRCUIT BOARD                | INTER-<br>RUPT<br>LEVEL | FIXED<br>CRU<br>BASE<br>ADDRESS | CIRCUIT BOARD                | INTER-<br>RUPT<br>LEVEL |

|-------------|---------------------------------|------------------------------|-------------------------|---------------------------------|------------------------------|-------------------------|

| 1           | N/A                             | 990/4 AU                     | N/A                     | N/A                             | 990/4 AU                     | N/A                     |

| 2           | 0120                            | MEMORY EXPANSION<br>OR SPARE | N/A                     | 0100                            | MEMORY EXPANSION<br>OR SPARE | N/A                     |

| 3           | 00E0                            | 913A VDT NO. 1               | 3                       | 0000                            | 913A VDT NO. 1               | 3                       |

| 4           | 00 <b>A</b> 0                   | FLOPPY DISC<br>CONTROLLER    | 7                       | 0080                            | FLOPPY DISC<br>CONTROLLER    | 7                       |

| 5           | 0060                            | SPARE                        | N/A                     | 0040                            | CARD READER                  | 4                       |

| 6           | 0020                            | PROM PROGRAMMER              | NOT<br>USED             | 0000                            | 733 ASR/KSR                  | 6                       |

#### (A) 6-SLOT PREWIRED CHASSIS

(A)133082

Figure 2-5. 6-Slot Chassis Prewired Configuration

- 10. Slip chassis enclosure over chassis and align it so that it mates properly with front panel and mounting-screw holes.

- 11. Secure chassis enclosure to chassis using seven oval-head screws and finishing washers removed in step 2.

- 12. Position computer in final installation site.

- 13. Perform system software installation procedures for operating system to be used with computer. For Texas Instruments supplied software, this information is provided in System Operation Guide for specific software package.

#### 2.5 INSTALLATION (RACKMOUNT CHASSIS)

Either the 6-slot or the 13-slot chassis can be ordered for mounting in a 19-inch equipment rack. The chassis is shipped with all circuit boards installed in chassis; the rackmounting hardware is packed in same carton as chassis. After performing the unpacking procedure, perform following steps to install the computer in rack:

#### NOTE

The following procedure requires access to the rear of installation rack after computer chassis is mounted in rack.

1. Set unpacked chassis assembly on a convenient work surface near equipment rack in which computer will be installed.

#### WARNING

Ensure that the power cord is not connected to a source of ac power before continuing with procedure. Failure to observe this precaution could result in severe electrical shock.

- 2. Remove six (6) screws that secure air filter and rear access plate to rear of chassis. It is not necessary to remove air filter from access plate.

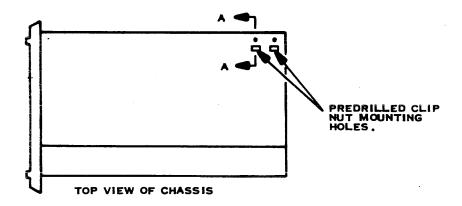

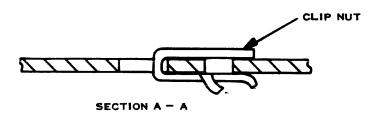

- 3. Install two clip nuts in predrilled holes in chassis as illustrated in figure 2-6.

- 4. Reinstall rear access cover/air filter assembly using the six mounting screws removed in step 2.

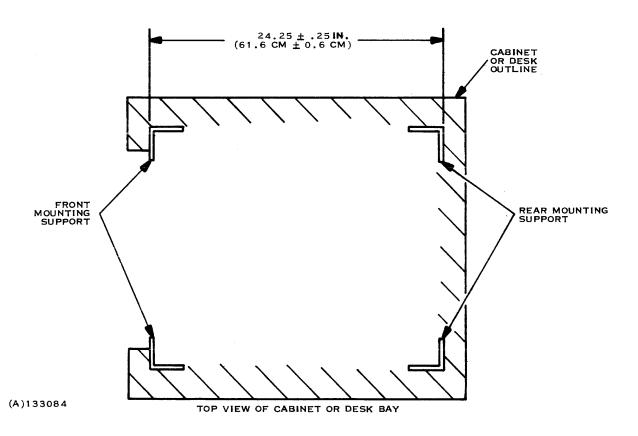

- 5. Inspect the front and rear mounting supports in the rack (or desk) to ensure that distance between front and rear supports is 24-1/4 inches ± 1/4 inch (61.6 cm ± 0.6 cm) as illustrated in figure 2-7.

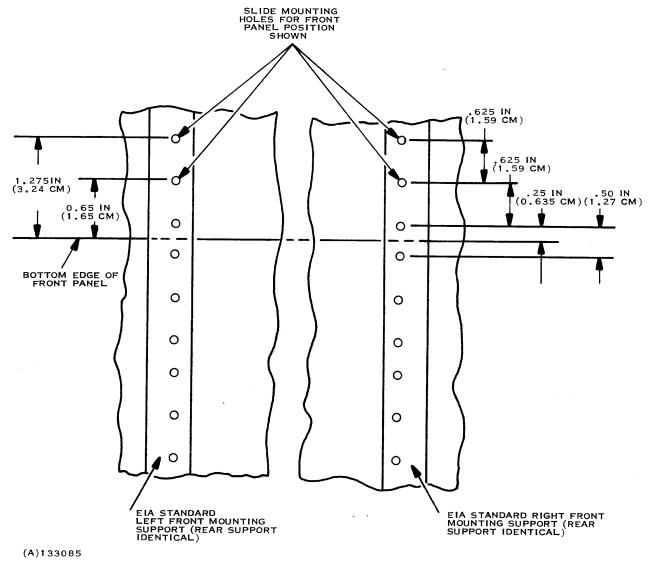

- 6. Determine desired vertical position of bottom edge of computer front panel. When using an EIA standard vertical support, the bottom edge of front panel must be centered between two holes that are 0.5 inch (1.27 cm) apart as illustrated in figure 2-8. Using that figure, locate position of two slide mounting holes on each of four mounting supports. These holes are 0.65 inch (1.65 cm) and 1.275 inches (3.24 cm) above the bottom edge of front panel.

(A)133083

Figure 2-6. Clip Nut Installation

Figure 2-7. Mounting Cabinet Depth Specification

Figure 2-8. Mounting Hole Positioning

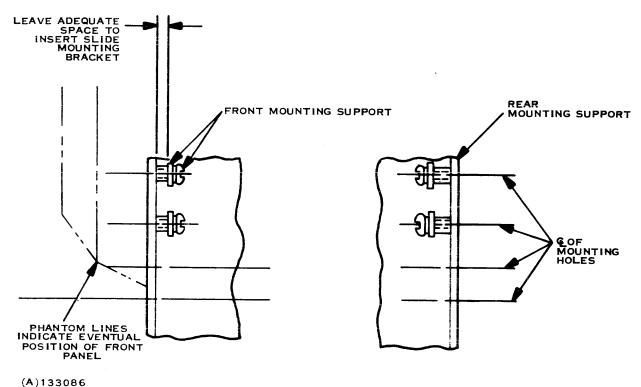

- 7. Loosely install eight (8) 10-32 × 1/4 mounting screws and their associated flat washers and lock washers in eight selected holes in mounting supports (front and rear). Screws are installed from inside of enclosure as illustrated in figure 2-9.

- 8. Loosely assemble rear mounting brackets to slides using hardware provided with slides. Finger tighten rear mounting bracket screws.

- 9. Position left side against front and rear mounting supports such that slide mounting brackets fit between washers of mounting screws and mounting supports. Finger tighten four mounting screws to hold slide in place.

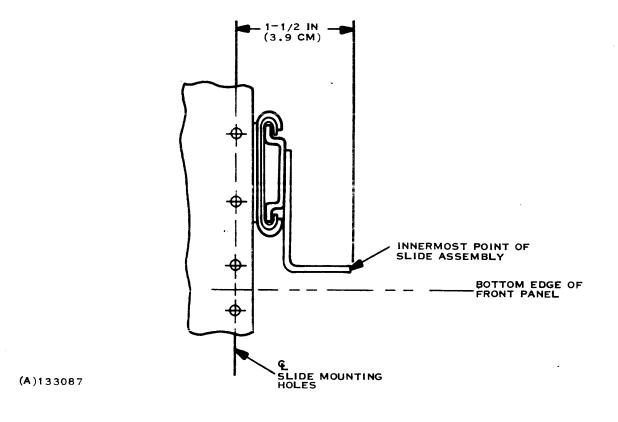

- 10. Adjust slide so that distance from center of cabinet mounting screws to innermost point of slide assembly is 1-1/2 inches (3.91 cm) as illustrated in figure 2-10.

Figure 2-9. Mounting Screw Installation

Figure 2-10. Chassis Slide Positioning

- 11. Ensure that slide assembly is square with cabinet mounting supports and tighten four (4) slide mounting screws and rear bracket mounting screws.

- 12. Repeat steps 9 through 11 with right slide.

- 13. Extend both slides and release disconnect mechanism to remove inner slide member from slide assemblies.

- 14. Attach inner slide members to left and right underside of computer chassis using 6-32 X 1/4 self-tapping screws. Do not overtighten screws.

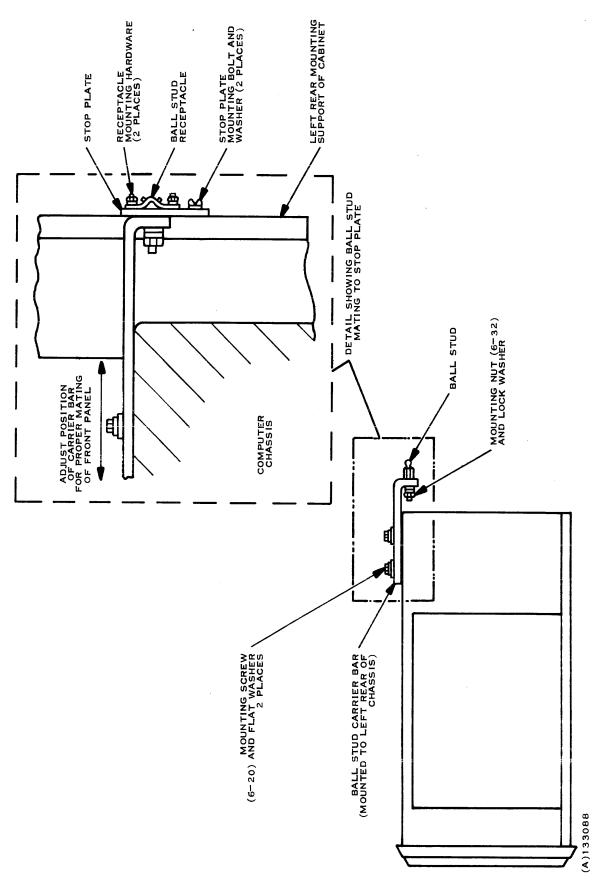

- 15. Mount ball stud to ball stud carrier bar using a 6-32 nut and lock washer as illustrated in figure 2-11.

- 16. Loosely install ball stud carrier bar to top of computer chassis using 6-20 screws and flat washers inserted into clip nuts installed in chassis in step 3.

- 17. Insert chassis into mounted slides and reseat the disconnect mechanism. Push chassis into rack. During last inch of travel, lift front of chassis to ensure correct slide mating.

- 18. Assemble ball stud receptacle to stop plate using mounting hardware provided.

- 19. Install stop plate assembly to back edge of left rear mounting support of cabinet at a height such that ball stud receptacle mates with ball stud of the computer chassis.

- 20. Adjust forward-backward position of ball stud carrier bar on computer chassis such that chassis stops and ball stud latches into receptacle when back of front panel is between 1/32 inch to 1/16 inch (0.8 cm to 0.16 cm) from front mounting support of cabinet.

- 21. Slide computer chassis in and out of cabinet several times to ensure smooth operation and good alignment of all parts. Readjust as required.

- 22. Connect power cord from back of computer chassis to ac power distribution system of cabinet. Do not apply power at this time.

- 23. Slide chassis out from the cabinet to expose circuit boards mounted within the computer chassis. Remove shipping brackets that hold logic boards in place.

#### **NOTE**

The chassis is shipped from factory with interrupts installed in predetermined locations. Figure 2-12 illustrates these assignments for the 13-slot chassis; 6-slot chassis assignments are identical to those previously described for tabletop chassis. CRU addresses shown in figure cannot be changed.

24. Determine chassis location and interrupt assignments for each peripheral interface in system. If interrupt assignments do not match the factory-installed interrupts, or if additional interrupt assignments are required, perform Interrupt Installation procedure in this section of manual. If board slot assignments are unknown or an expansion chassis is being used, refer to Preparation Planning procedure in this section.

Figure 2-11. Installation of Ball Stud and Stop Plate

SLOT NUMBER

1

8

11

12

13

P1 (CHASSIS FRONT)

P2 (CHASSIS REAR)

|                                 |                              |                         |                                 | 1 2 (CHASSIS REAR)           |                         |

|---------------------------------|------------------------------|-------------------------|---------------------------------|------------------------------|-------------------------|

| FIXED<br>CRU<br>BASE<br>ADDRESS | CIRCUIT BOARD                | INTER-<br>RUPT<br>LEVEL | FIXED<br>CRU<br>BASE<br>ADDRESS | ÇIRCUIT BOARD                | INTER-<br>RUPT<br>LEVEL |

| N/A                             | 990/4 AU                     | N/A                     | N/A                             | 990/4 AU                     | N/A                     |

| 02E0                            | MEMORY EXPANSION<br>OR SPARE |                         | 02 <b>C</b> 0                   | MEMORY EXPANSION<br>OR SPARE |                         |

| 02 <b>A</b> 0                   | MEMORY EXPANSION<br>OR SPARE |                         | 0280                            | MEMORY EXPANSION<br>OR SPARE |                         |

| 0260                            | SPARE                        |                         | 0240                            | SPARE                        |                         |

| 0220                            | SPARE                        |                         | 0200                            | SPARE                        |                         |

| 01E0                            | SPARE                        |                         | 0100                            | SPARE                        |                         |

| 0 <b>1A</b> 0                   | SPARE                        | (13)*                   | 0180                            | SPARE                        | (13)*                   |

| 0160                            | CRT 3                        | (9)*                    | 0140                            | CRT 3                        | (9) <b>*</b>            |

| 0120                            | CRT 2 OR CRU<br>EXPANDER     | (10)*                   | 0100                            | CRT 2 OR CRU<br>EXPANDER     | (10)*                   |

| 00E0                            | CRT 1                        | (11)*                   | 0000                            | CRT 1                        | (11)*                   |

| 0 <b>0A</b> 0                   | FLOPPY DISC<br>CONTROLLER    | 7                       | 0080                            | FLOPPY DISC<br>CONTROLLER    | 7                       |

| 0060                            | LINE PRINTER                 | (14)*                   | 0040                            | CARD READER                  | 4                       |

| 0020                            | PROM PROGRAMMER              | (15)*<br>NOT<br>USED    | 0000                            | 733 ASR/KSR                  | 6                       |

<sup>\*</sup>INTERRUPTS PREWIRED BUT NOT RECOGNIZED BY 990/4. MUST BE RECONFIGURED FOR USE WITH 990/4.

(A)133090

(B) 13-SLOT PREWIRED CHASSIS

Figure 2-12. 13-Slot Chassis Prewired Configuration

- 25. Verify that all boards are in their proper slots and are firmly seated in chassis.

- 26. Install peripheral device interface cables on proper interface module in computer chassis as described in Installation and Operation manual included with peripheral device. All interface cables should be routed through cable clamps at the rear of chassis and should exit at rear of chassis.

- 27. Turn key switch on front panel to ON (on programmer panel to the UNLOCK) position. Observe that the POWER and RUN indicators on front panel light and that fans operate.

- 28. Perform the System Checkout procedure specified later in this section of the manual.

- 29. Slide computer into cabinet to complete final installation of computer.

- 30. Install blank panels (if supplied) to fill open spaces in cabinet or rack.

- 31. Perform system software installation procedures for the operating system to be used with computer. For Texas Instruments supplied software, this information is provided in the System Operation Guide for the specific software package.

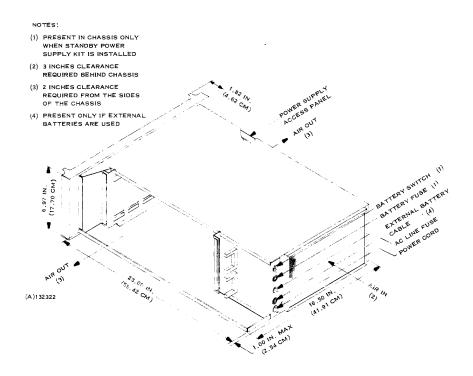

## 2.6 INSTALLATION (OEM CHASSIS)

The OEM (3-slot) chassis can be mounted in a customer-designed configuration, or it can be ordered for installation in a 19-inch equipment rack. The chassis is shipped with all circuit boards installed in the chassis; the rackmounting hardware (if ordered) is packed in the same carton as the chassis. The following procedure describes the steps required to mount the OEM chassis in a 19-inch rack. Other types of installation will require similar steps, but modified to suit the customer's site requirements.

- 1. Set unpacked chassis assembly on a convenient work surface near equipment rack in which chassis will be installed.

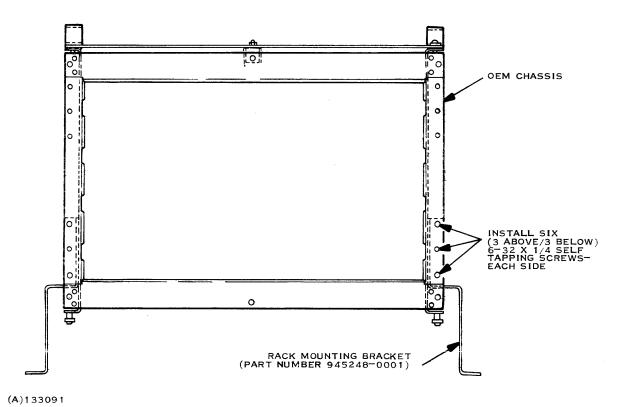

- 2. Attach one rackmounting bracket (Part Number 945248-0001) to each side of chassis using six (6) 6-32 × 1/4-inch, self-tapping screws for each bracket as illustrated in figure 2-13.

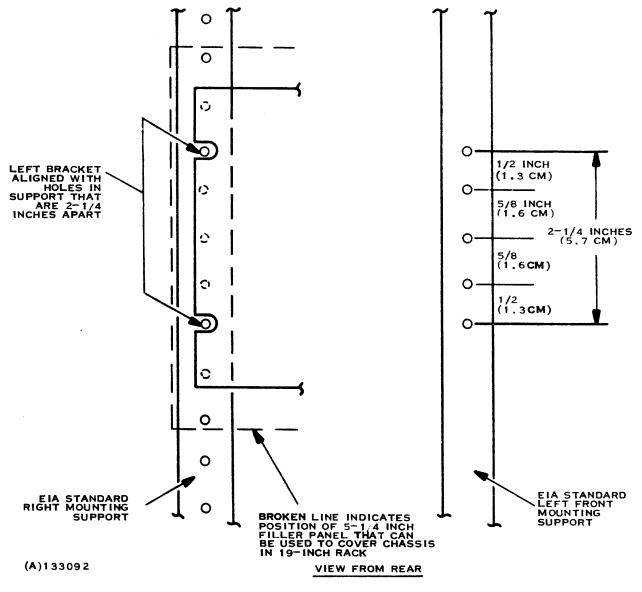

- 3. Determine desired vertical position of chassis in rack. The mounting bracket requires two holes, 2-1/4 inches apart, on each of front mounting supports of rack as illustrated in figure 2-14.

Figure 2-13. Mounting Bracket Installation

Figure 2-14. Positioning of OEM Chassis in 19-Inch Rack

- 4. Loosely install four (4) 10-32 × 1/4 mounting screws, and their associated flat washers and lock washers in the four selected holes in front mounting supports. Screws are installed from inside of enclosure.

- 5. Position slots in chassis mounting bracket on installed mounting screws such that bracket fits between cabinet mounting support and flat washer of mounting screws.

- 6. Ensure that chassis is square with cabinet mounting supports, and tighten all four mounting screws.

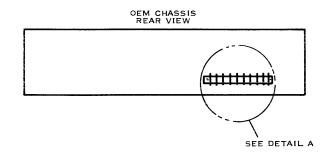

- 7. Connect external power and control lines to terminal strip at the rear of chassis as illustrated in figure 2-15.

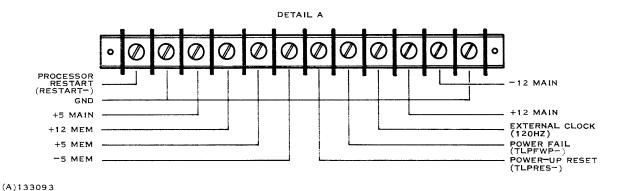

Figure 2-15. OEM Chassis External Connections

# **NOTE**

The chassis is shipped from the factory without any interrupt lines installed. These must be installed to enable operation of interface circuits.

- 8. Remove shipping brackets that hold logic boards in place, and save brackets for reuse. Perform Interrupt Installation procedure described later in this section of the manual.

- 9. Verify that interface modules, memory board (if installed) and the processor board are firmly seated in their correct positions in chassis.

- 10. Install peripheral device interface cables and any other external interface cables that lead to chassis. Peripheral device cabling for Texas Instruments supplied devices is described in the Installation and Operation manual included with each peripheral device.

- 11. Apply power and use the Model 990 Computer Maintenance Unit to perform the System Checkout procedure as described later in this section.

- 12. Install 5-1/4-inch blank panel to cover chassis in rack or cabinet.

#### 2.7 INTERRUPT INSTALLATION

The computer chassis (except the OEM chassis) is shipped from the factory with predetermined interrupts installed. These interrupt assignments are listed in the installation procedure for the particular chassis elsewhere in this section. If the interrupts do not meet the requirements of the system being installed, they may be easily modified. Wiring in the backplane of the chassis brings the interrupts from each connector to a pair of jumper plugs located on the backplane above the AU circuit board. Similarly, backplane connections bus the interrupt inputs to the processor to the jumper plug connections. Installing jumper wires in the jumper plugs connects the interrupts from the modules in the chassis to the appropriate interrupt level input to the processor. Modification of the predetermined interrupt configuration is a three-part procedure consisting of:

- Preparation and planning

- Modification of jumper plug

- Reinstallation of system

- 2.7.1 PREPARATION AND PLANNING. To ensure that the interrupt configuration is correctly installed and does not upset the operation of the software system that will control the system, proper planning of the chassis configuration is required. To aid in this planning, figure 2-16 provides a Chassis Configuration chart for each type of chassis that should be completed with the information for the system being installed. The following steps outline the procedure to prepare for modifying interrupts in either chassis:

- 1. Fill-in locations in Chassis Configuration chart with modules that comprise system to be installed. Observe following restrictions:

- a. In the main chassis, the 990/4 Microcomputer circuit board must occupy the topmost slot (slot 1). In an expansion chassis, the CRU buffer board must occupy slot 1.

- b. The memory circuit boards (if used) must occupy the slots immediately below the processor in the main chassis only. Memory boards or DMA devices cannot be installed in an expansion chassis.

- c. CRU addresses for interface modules that are assigned by the system software must correspond to the CRU address of the chassis slot in which the module is installed. Texas Instruments supplied software requires that the modules be located in the slots designated in the chassis installation procedures in this section. Before deciding on a chassis location for a new board, determine the address that system software has assigned to the board. If the CRU word address is less than or equal to  $01E0_{16}$  (byte address  $03C0_{16}$ ), the circuit board must be installed in the main chassis. If the CRU word address is greater than or equal to  $0200_{16}$  (byte address  $0400_{16}$ ), the board must be installed in one of the expansion chassis. The CRU address that must be added to a CRU

|                |                                 | P1 (CHASSIS FRONT)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | P2 (CHASSIS REAR)                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

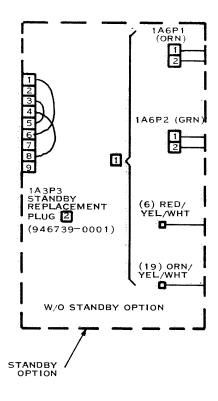

| SLOT<br>NUMBER | FIXED<br>CRU<br>BASE<br>ADDRESS | CIRCUIT BOARD                     | INTER-<br>RUPT<br>LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIXED<br>CRU<br>BASE<br>ADDRESS | CIRCUIT BOARD                             | INTER-<br>RUPT<br>LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |