# TEXAS INSTRUMENTS

Improving Man's Effectiveness Through Electronics

Model 990/5 Computer Hardware User's Manual

MANUAL NO. 946294-9701

ORIGINAL ISSUE 1 JANUARY 1979

# C Texas Instruments Incorporated 1979 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

# LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

CHANGE NO.

Model 990/5 Computer Hardware User's Manual (946294-9701)

Total number of pages in this publication is 154 consisting of the following:

| PAGE<br>NO.       | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. |

|-------------------|---------------|-------------|---------------|-------------|

| Cover             | 0             |             |               |             |

| Effective Pages   | 0             |             |               |             |

| iii - ix          | 0             |             |               |             |

| 1-0 - 1-22        | 0             |             |               |             |

| 2-1 - 2-42        | 0             |             |               |             |

| 3-1 - 3-12        | 0             |             |               |             |

| 4-1 - 4-38        | 0             |             |               |             |

| 5-1 - 5-22        | 0             |             |               |             |

| Alphabetical Inde | x Div 0       |             |               |             |

| Index-1 - Index-4 | 0             |             |               |             |

| User's Response.  | 0             |             |               |             |

| Business Reply    | 0             |             |               |             |

| Cover Blank       | 0             |             |               |             |

# **NOTE**

ALL REFERENCES TO TMS9903 SYNCHRONOUS COMMUNICATIONS CONTROLLER (SCC) OR COMMUNICATIONS PORT 3 ARE RESERVED FOR FUTURE ENHANCEMENTS.

#### **PREFACE**

The Texas Instruments Model 990/5 Microcomputer is a complete basic computer packaged on a single, full-size, printed circuit board. The Central Processing Unit (CPU) for the 990/5 is the Model TMS 9900 Microprocessor made by Texas Instruments.

This manual provides information on the 990/5 microcomputer and is directed to both the Original Equipment Manufacturer (OEM) equipment purchaser and the end-user.

Information in this manual is divided into the following sections:

- I General Description Provides an overview description of the Model 990/5 Microcomputer outlining hardware, firmware and software features.

- II Installation Outlines procedures for unpacking the microcomputer from its shipping container, installing it in various chassis configurations, and establishing the switch settings and jumper connections required for various configurations.

- Operation Describes controls and indicators for 990/5 front panels, general operating procedures for the front panel, and loading procedures.

- IV Programming Considerations Contains information on programming considerations relative to the TMS 9900 microprocessor instruction set, the communications ports address bit assignments, and the asynchronous clock rate selection.

- V Interface Requirements Assists users and OEM equipment purchasers in interfacing peripherals with the 990/5 microcomputer.

Additional information related to the 990/5 microcomputer may be found in the following documents:

| Title                                                               | Part Number |

|---------------------------------------------------------------------|-------------|

| Model 990 Computer Diagnostic Handbook                              | 945400-9701 |

| Model 990/5 Computer Field Maintenance Manual                       | 946295-9701 |

| Model 990/5 Computer Depot Maintenance Manual                       | 946296-9701 |

| Model 990 Computer Peripheral Equipment Field<br>Maintenance Manual | 945419-9701 |

| Model 990 Computer Family Maintenance Drawings:                     |             |

| Volume I, Processors                                                | 945421-9701 |

| Volume II, Peripherals                                              | 945421-9702 |

• Ó

## TABLE OF CONTENTS

| Paragraph | Title                                        | Page         |

|-----------|----------------------------------------------|--------------|

|           | SECTION I. GENERAL DESCRIPTION               |              |

| 1.1       | Introduction                                 | 1-1          |

| 1.2       | Equipment Description                        | 1-1          |

| 1.2.1     | Four-Phase Clock Generator/Driver            | 1-4          |

| 1.2.2     | TMS 9900 Microprocessor                      | 1-4          |

| 1.2.3     | TMS 4116 Dynamic Random-Access Memory        | 1-12         |

| 1.2.4     | TMS 4700 Read-Only Memory                    | 1-12         |

| 1.2.5     | Communications Register Unit Interface Logic | 1-13         |

| 1.2.6     | TILINE Interface Logic                       | 1-13         |

| 1.2.7     | Communications Ports                         | 1-16         |

| 1.2.8     | Interrupts                                   | 1-18         |

| 1.3       | 990/5 Characteristics and Specifications     | 1-19         |

| 1.4       | Multiprocessor Features                      | 1-19         |

|           | SECTION II. INSTALLATION                     |              |

| 2.1       | General                                      | 2.1          |

| 2.2       | Site Preparation                             |              |

| 2.2.2     | Space Requirements                           |              |

| 2.2.3     | Interconnect Cabling Requirements            |              |

| 2.2.4     | Unpacking/Packing (6- and 13-Slot Chassis)   |              |

| 2.3       | Installation (Tabletop Chassis)              |              |

| 2.4       | Installation (Rackmount Chassis)             |              |

| 2.5       | Preparing a Slot Location                    |              |

| 2.6       | Interrupt Connections                        |              |

| 2.7       | Memory Configuration                         |              |

| 2.8       | CRU Expansion Installation Requirements      |              |

| 2.8.1     | CRU Expansion Board Jumper Options           |              |

| 2.8.2     | CRU Buffer Board Jumper Options              |              |

| 2.8.3     | Expansion Chassis Interrupt Wiring           |              |

| 2.9       | TILINE Expansion                             |              |

| 2.9.1     | TILINE Coupler Address Options               |              |

| 2.9.2     | TILINE Coupler Interrupt Options             |              |

| 2.9.3     | IORESET Jumper Option                        |              |

| 2.9.4     | Writing to Remote Slave Option               |              |

| 2.9.5     | Peripheral Control Space Address Option      |              |

| 2.10      | Logic Board Installation Procedures          |              |

| 2.11      | Communications Port Connections              | 2_30         |

| 2.12      | System Checkout Procedures                   | 2_30         |

| 2.12.1    | Model 990/5 Self-Test                        | 2-39<br>2-30 |

| 2.12.2    | Model 990/5 Diagnostic Tests                 |              |

| 2.12.3    | Peripheral Diagnostic Tests                  | 2_42         |

|           | 1O                                           | 72           |

## TABLE OF CONTENTS (Continued)

| Paragraph                                                                                                                                                                            | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                      | SECTION III. OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                            | General  990/5 Microcomputer Front Panels Programmer Front Panel Operator Front Panel General Operating Procedures Workspace Register Display Current Instruction Display Masking Interrupts Program Loading Procedures with ROM Loader Load Procedures Using Operator Panel Load Procedures Using Programmer Panel Fault Indications in Loading Fault Indications in Self-Test Mode                                                                                                                                                                                            |      |

|                                                                                                                                                                                      | SECTION IV. PROGRAMMING CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.6<br>4.7 | General TMS 9900 Microprocessor TMS 9900 Instruction Set Definition Addressing Modes Terms and Definitions Status Register Instructions TMS 9900 Instruction Execution Times TMS 9902 Asynchronous Communication Controllers (Comm. Ports 1 and CPU Interface Communications Channel Interface Interrupt Output Clock Input Control and Data Output Status and Data Input TMS 9903 (Port 3) in the 990/5 CRU Output Data to Communications Channel (Port 3) CRU Input Data from Communications Channel (Port 3) Modem Communications, Port 3 Only Interprocessor Communications |      |

| 4.7                                                                                                                                                                                  | 990/5 Operation with Higher Level 990 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3/ |

|                                                                                                                                                                                      | SECTION V. INTERFACE REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.3<br>5.4                                                                                                                | General  CRU/TILINE Backpanel Connectors, P1 and P2  CRU Interface Interrupts  CRU Timing  TILINE Interface Miscellaneous Backpanel Signals  Operator or Programmer Front Panel Connector, P3  Communications Ports Interfaces, P4, P5, P6                                                                                                                                                                                                                                                                                                                                      |      |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                                          | Page |

|--------|--------------------------------------------------------------------------------|------|

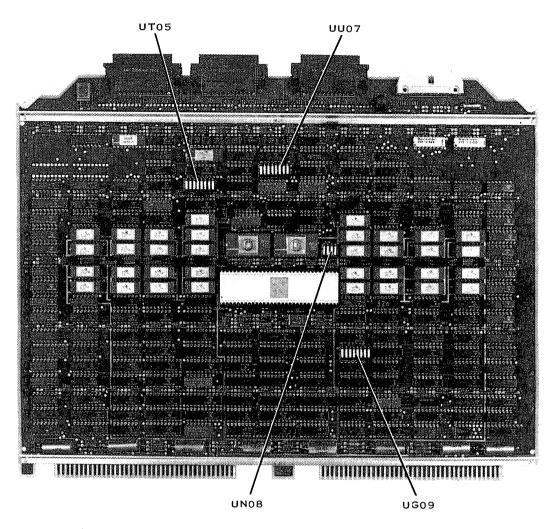

| 1-1    | 990/5 Microcomputer Printed Circuit Board                                      | 1-0  |

| 1-2    | 990/5 Chassis Assembly (6- and 13-Slot Chassis)                                |      |

| 1-3    | Model 990/5 Microcomputer Block Diagram                                        |      |

| 1-4    | Clock Generator Timing Diagram                                                 |      |

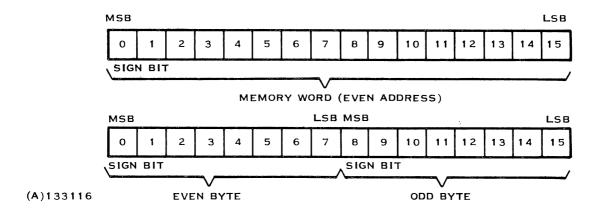

| 1-5    | Microprocessor Word and Byte Format                                            |      |

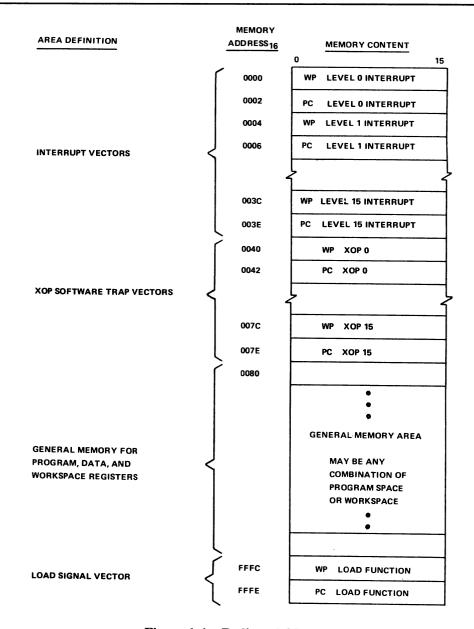

| 1-6    | Dedicated Memory Addresses                                                     |      |

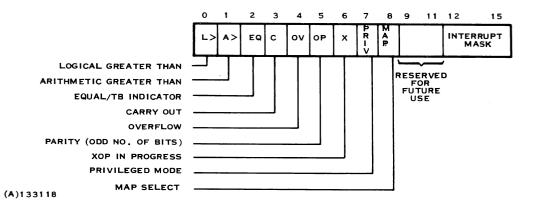

| 1-7    | Status Register Bit Assignments                                                | 1-7  |

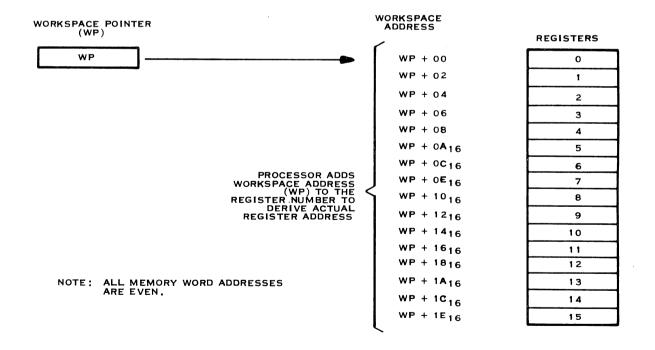

| 1-8    | Workspace Pointer and Registers                                                | 1-8  |

| 1-9    | TMS 9900 Single-Bit CRU Address Development                                    | 1-10 |

| 1-10   | TMS 9900 LDCR/STCR Data Transfer                                               | 1-11 |

| 1-11   | 32KB 990/5 and TILINE Addressing                                               | 1-14 |

| 1-12   | 64KB 990/5 and TILINE Addressing                                               | 1-15 |

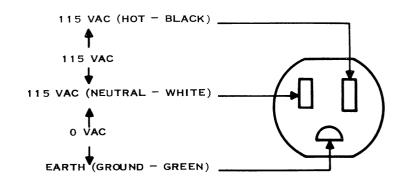

| 2-1    | Site AC Receptacle Wiring                                                      | 2-3  |

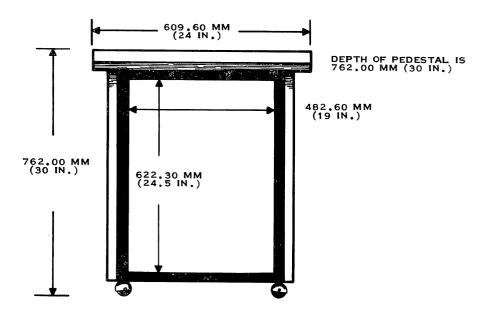

| 2-2    | Single-Bay Pedestal Dimensions                                                 | 2-3  |

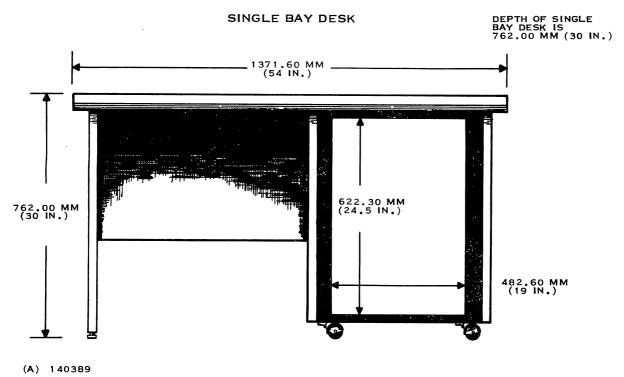

| 2-3    | Single-Bay Desk Dimensions                                                     | 2-4  |

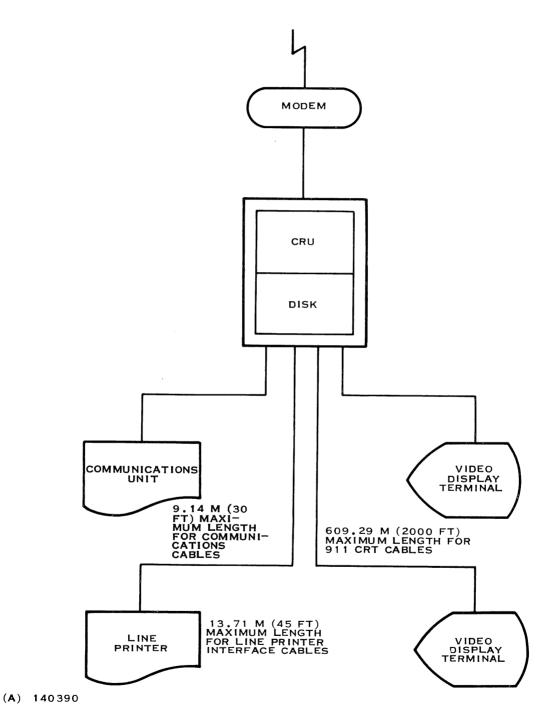

| 2-4    | Typical System Cabling                                                         |      |

| 2-5    | Typical Cable Marking for 911 VDU                                              | 2-6  |

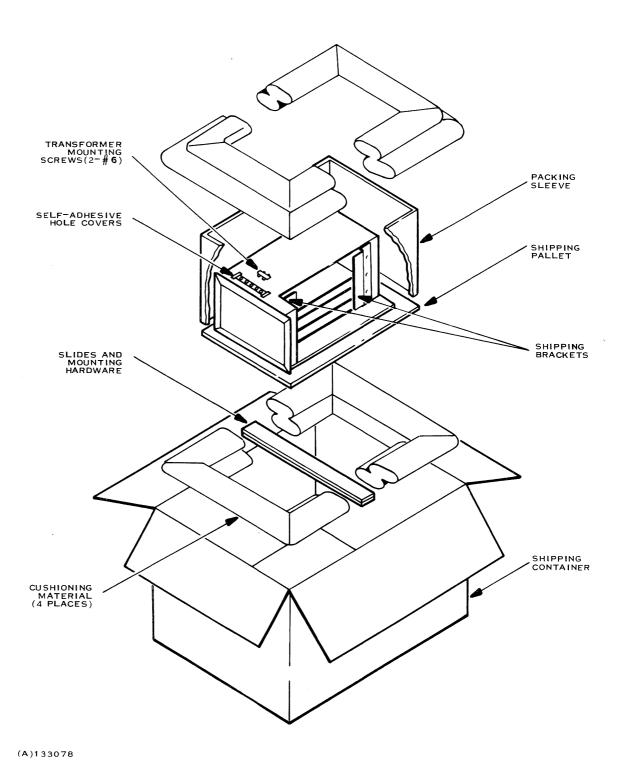

| 2-6    | Computer Shipping Packaging                                                    |      |

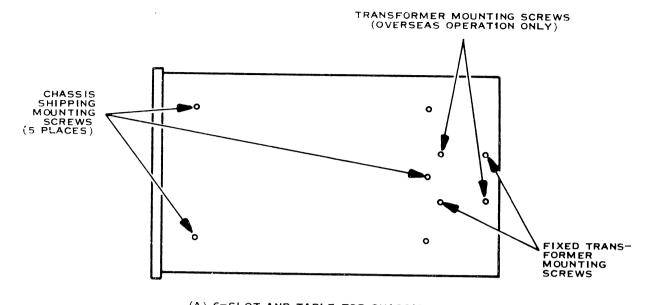

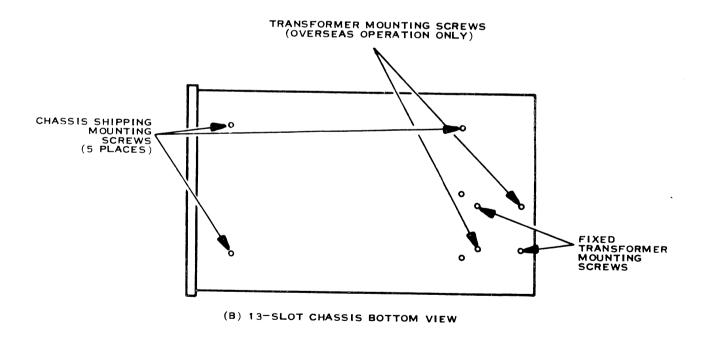

| 2-7    | Location of Chassis Shipping Pallet Mounting Screws                            | 2-9  |

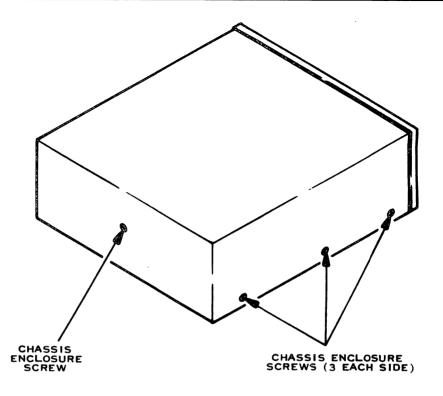

| 2-8    | Location of Chassis Enclosure Screws                                           | 2-11 |

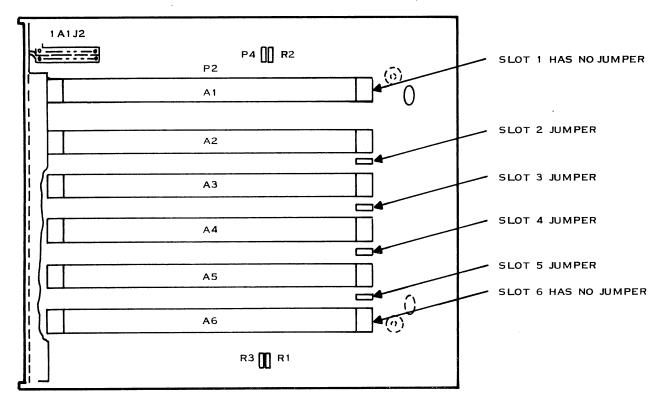

| 2-9    | 6-Slot Chassis Prewired Configuration                                          |      |

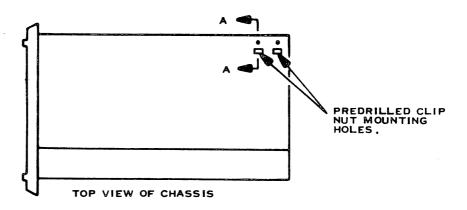

| 2-10   | Clip Nut Installation                                                          |      |

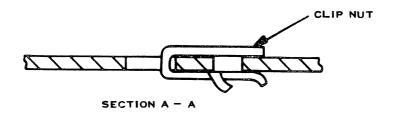

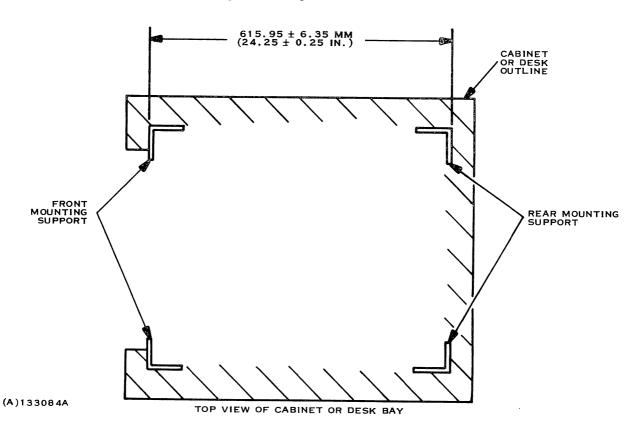

| 2-11   | Mounting Cabinet Depth Specification                                           |      |

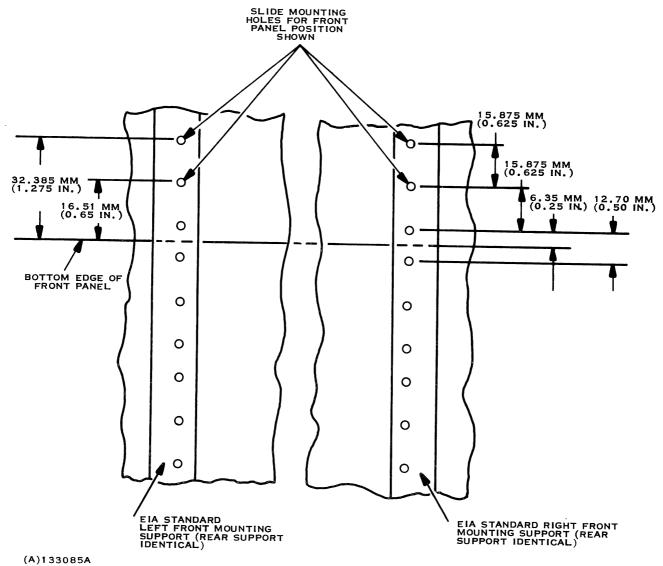

| 2-12   | Mounting Hole Positioning                                                      |      |

| 2-13   | Mounting Screw Installation                                                    | 2-15 |

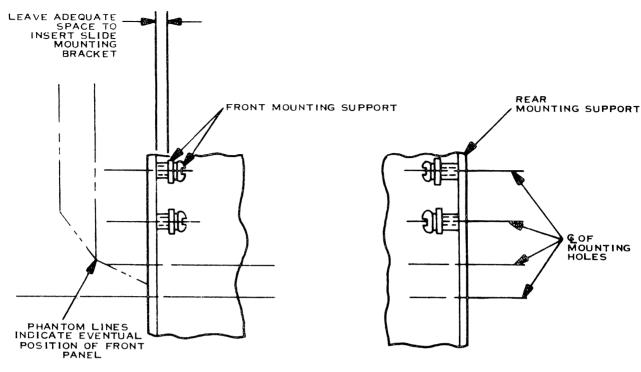

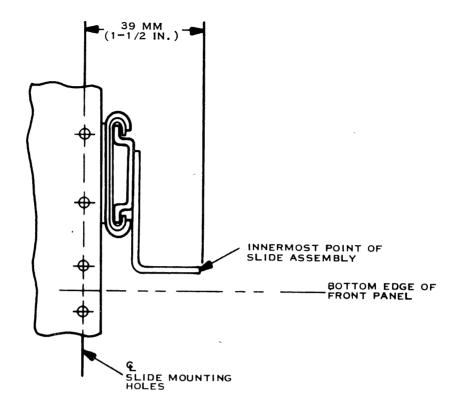

| 2-14   | Chassis Slide Mounting                                                         |      |

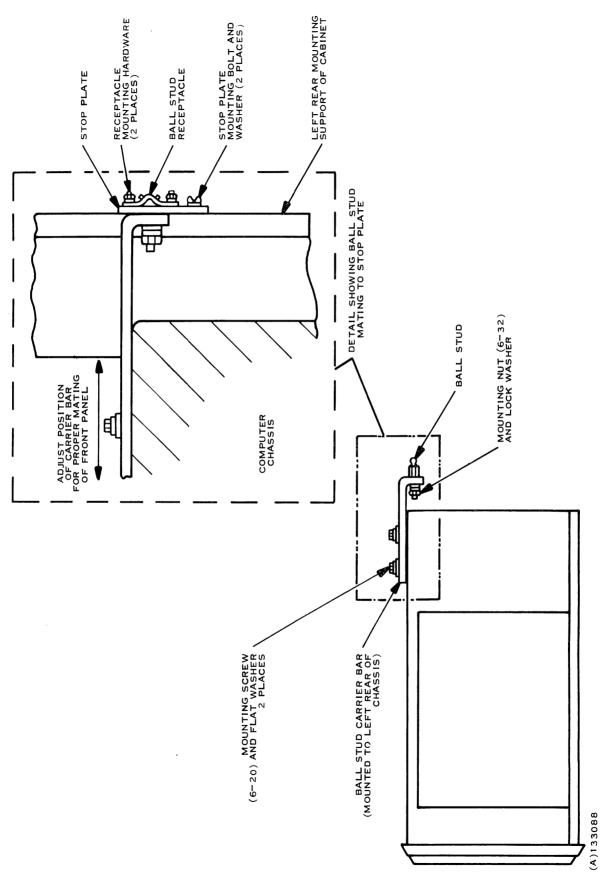

| 2-15   | Installation of Ball Stud and Stop Plate                                       |      |

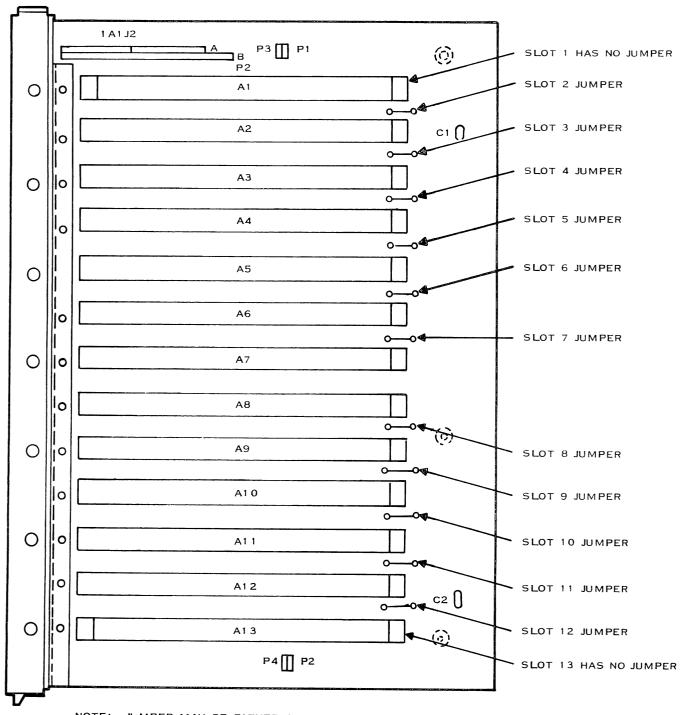

| 2-16   | 13-Slot Chassis Prewired Configuration                                         | 2-19 |

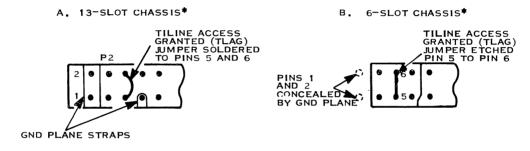

| 2-17   | TILINE Access Granted Jumper Locations for 6-Slot Chassis (Current Production) | 2_20 |

| 2-18   | TILINE Granted Jumper Locations for 13-Slot Chassis (Current Production)       |      |

| 2-19   | TILINE Access Granted Jumpers on the 990/5 Backpanel                           |      |

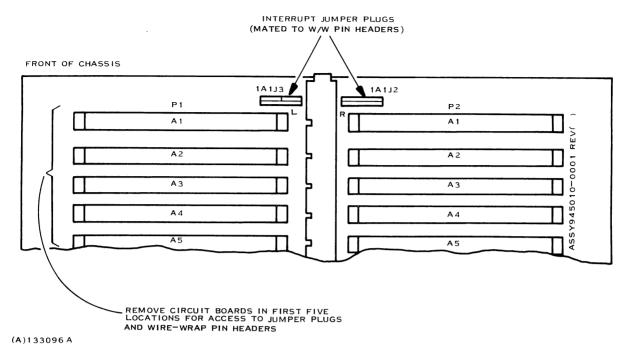

| 2-20   | Location of Interrupt Jumper (6- and 13-Slot Chassis)                          |      |

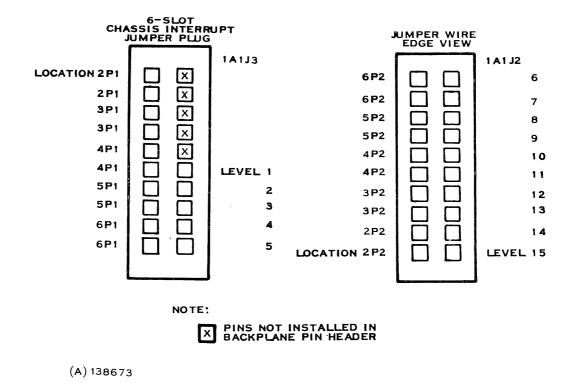

| 2-21   | 6-Slot Chassis Interrupt Jumper Plugs                                          |      |

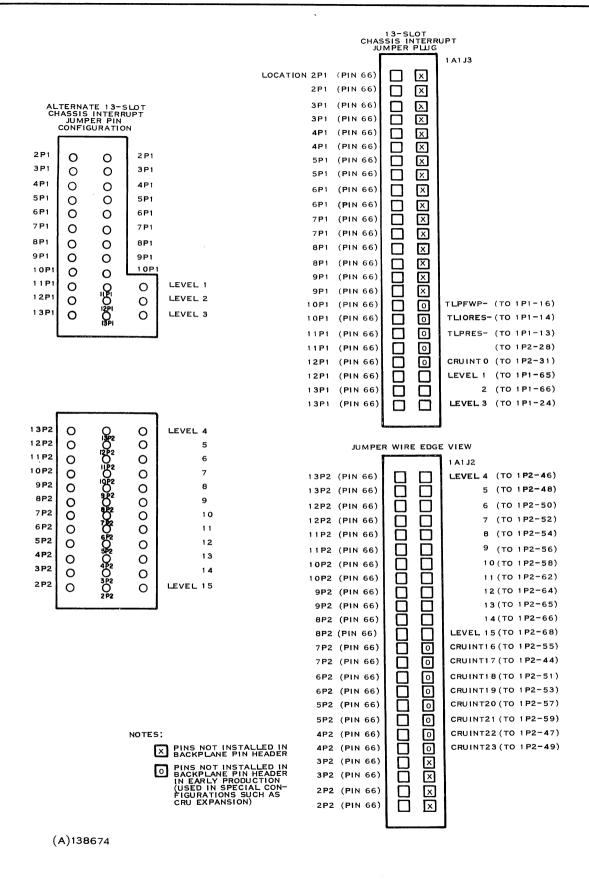

| 2-22   | 13-Slot Chassis Interrupt Jumper Plugs                                         |      |

| 2-23   | CRU Expansion Board Options                                                    |      |

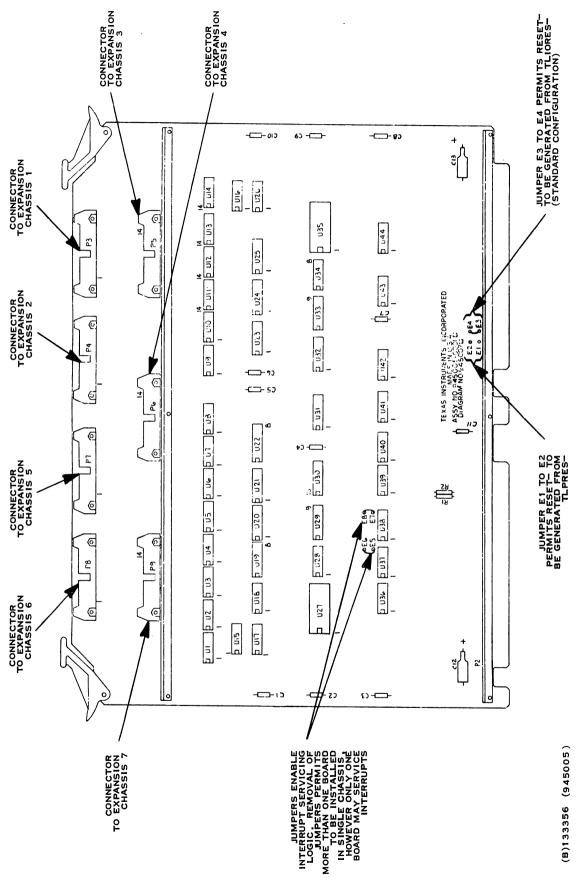

| 2-24   | CRU Buffer Board Options                                                       |      |

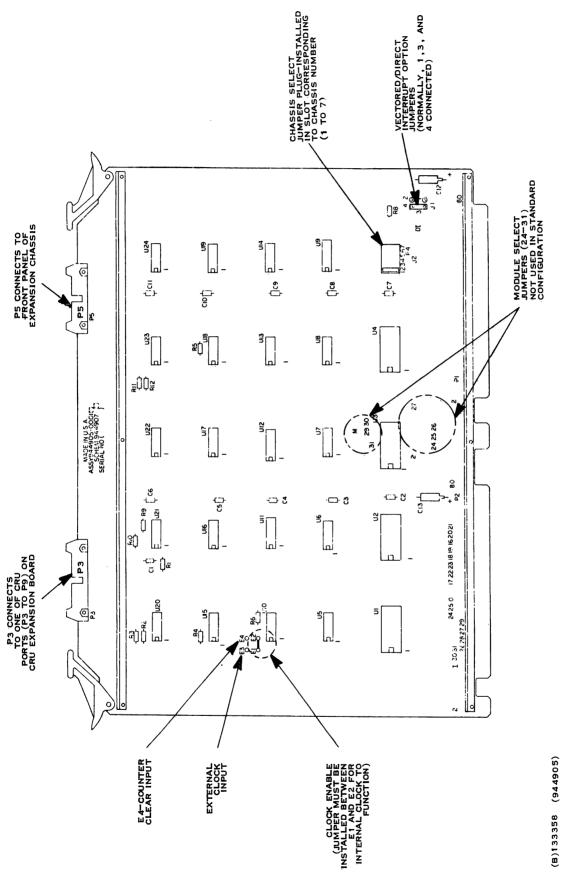

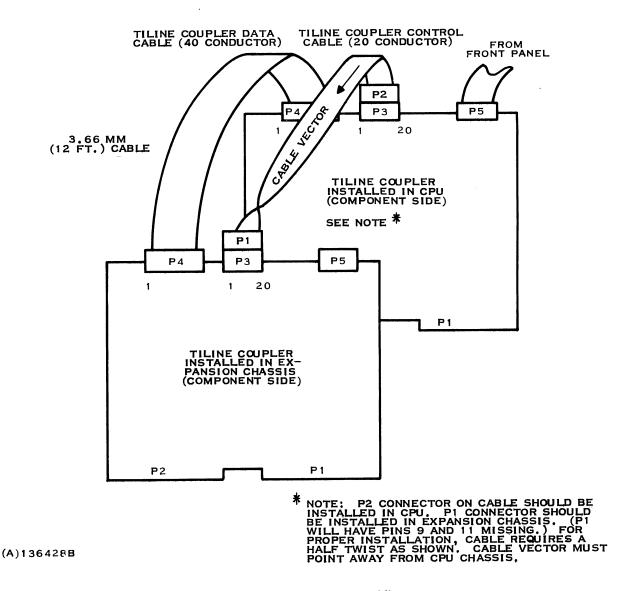

| 2-25   | TILINE Expansion Cabling                                                       |      |

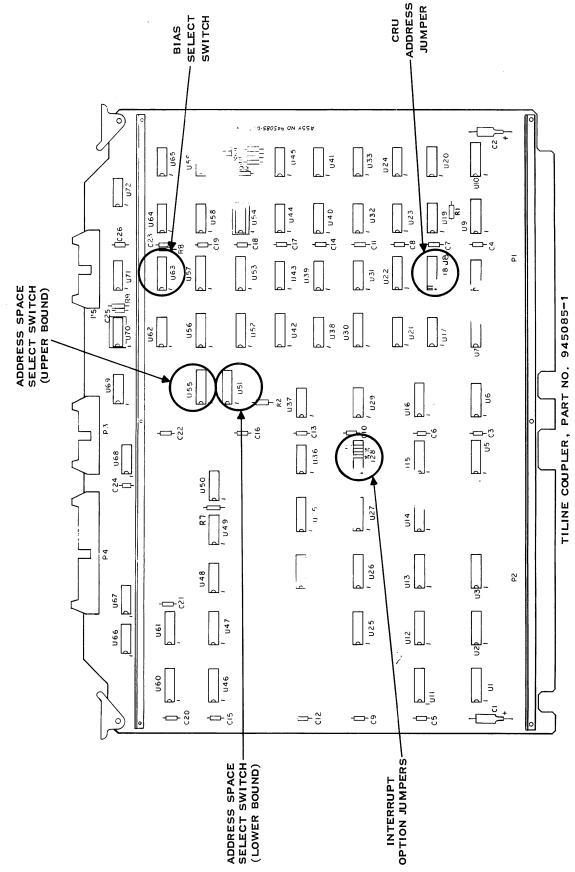

| 2-26   | TILINE Coupler Options                                                         |      |

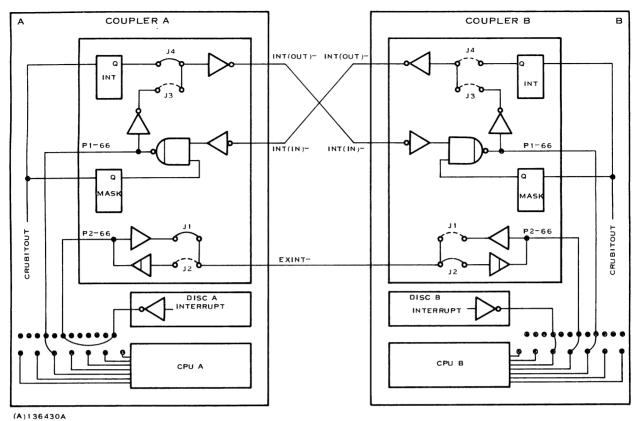

| 2-27   | TILINE Coupler Interrupt Circuitry, Functional Block Diagram                   |      |

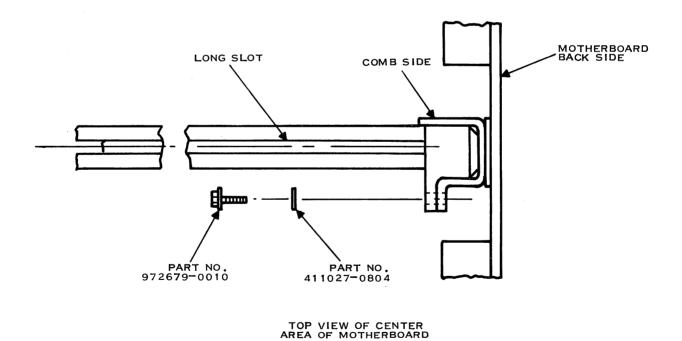

| 2-28   | Center Card Guide Installation Diagram                                         |      |

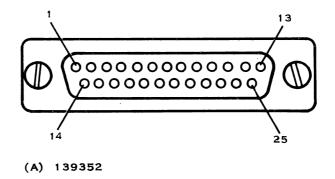

| 2-29   | Contact Orientation for Ports 1, 2, and 3 (P4, P5, and P6)                     |      |

| 2-30   | Option Switch Locations                                                        |      |

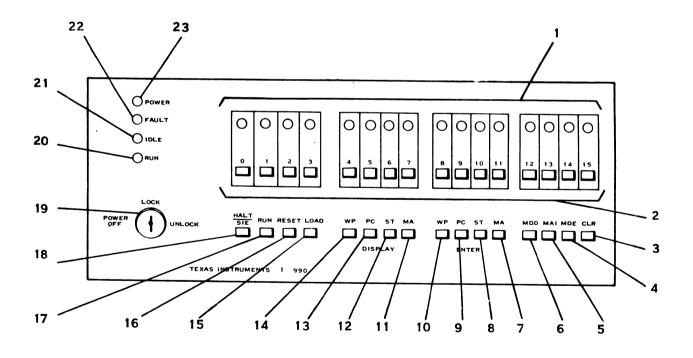

| 3-1    | 990 Programmer Panel, Controls and Indicators                                  | 3-1  |

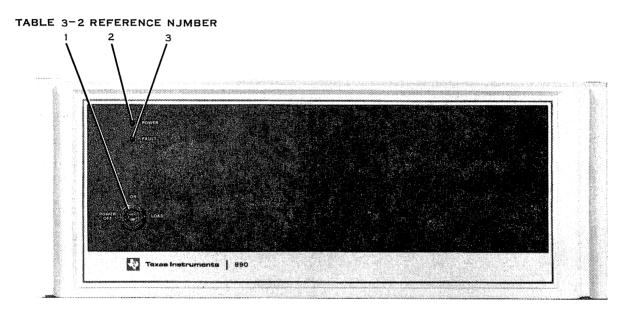

| 3-2    | 990 Operator Panel, Control and Indicators                                     |      |

| 4-1    | TMS 9902 (Ports 1 and 2)                                                       | 4-15 |

| 4-2    | ACC-CPU Interconnection                                                        |      |

| 5-1    | Chassis Power Supply Timing                                                    | 5-6  |

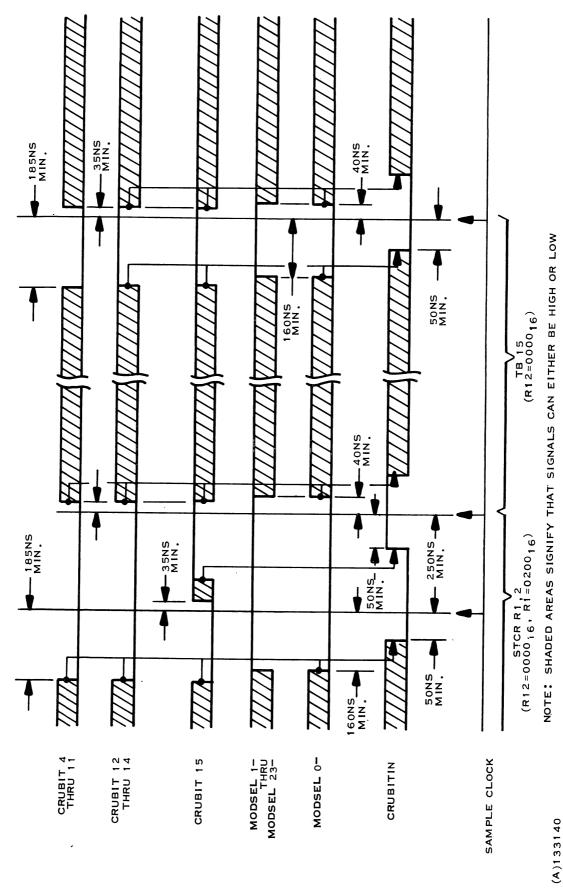

| 5-2    | CRU Output Timing, Minimum Restrictions                                        |      |

|        |                                                                                |      |

$(x_1,x_2,\dots,x_n) = (x_1,x_2,\dots,x_n) + (x_1,x_2,\dots,x_n) = (x_1,x_2,\dots,x_n)$

•

## LIST OF ILLUSTRATIONS (Continued)

| Figure .   | Title                                                                                          | Page   |

|------------|------------------------------------------------------------------------------------------------|--------|

| 5-3        | CRU Input Timing, Minimum Restrictions                                                         | .5-9   |

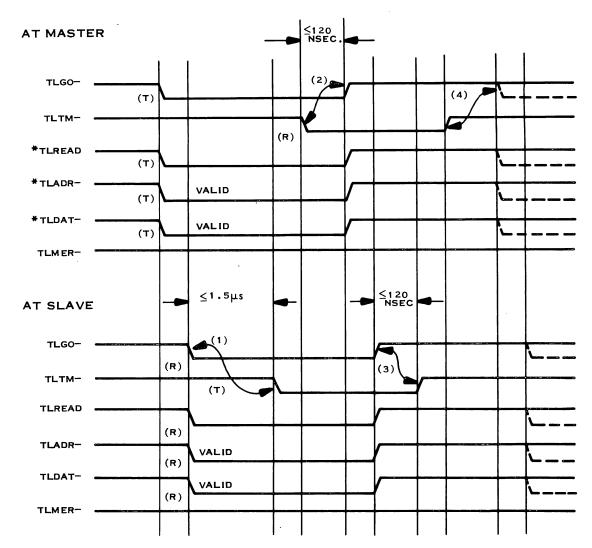

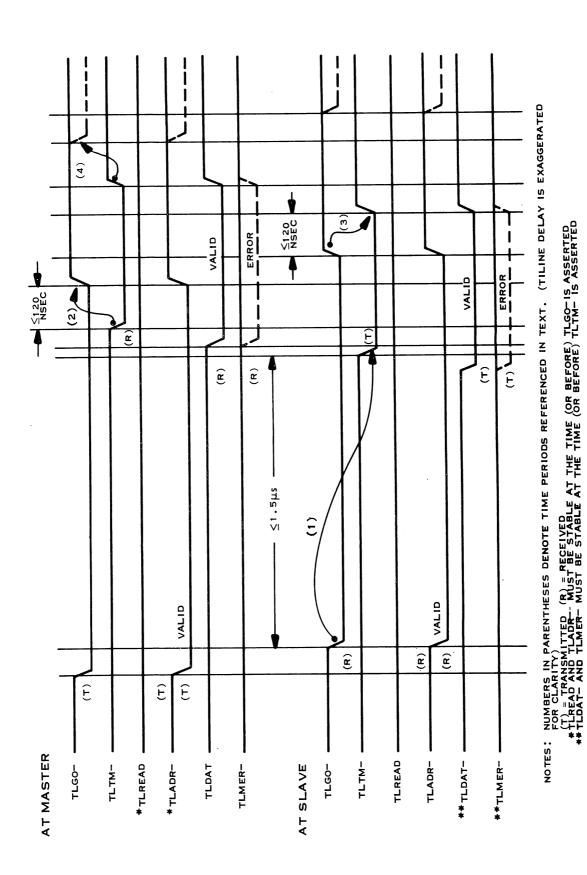

| 5-4        | TILINE Master to Slave Write Cycle Timing Diagram                                              |        |

| 5-5        | TILINE Master to Slave Read Cycle Timing Diagram                                               | 5-15   |

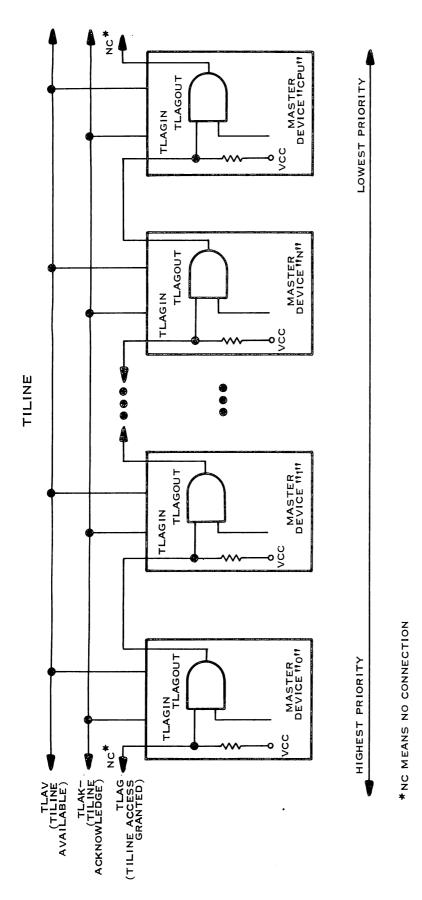

| 5-6        | TILINE Master Devices Priority Interconnections                                                | 5-16   |

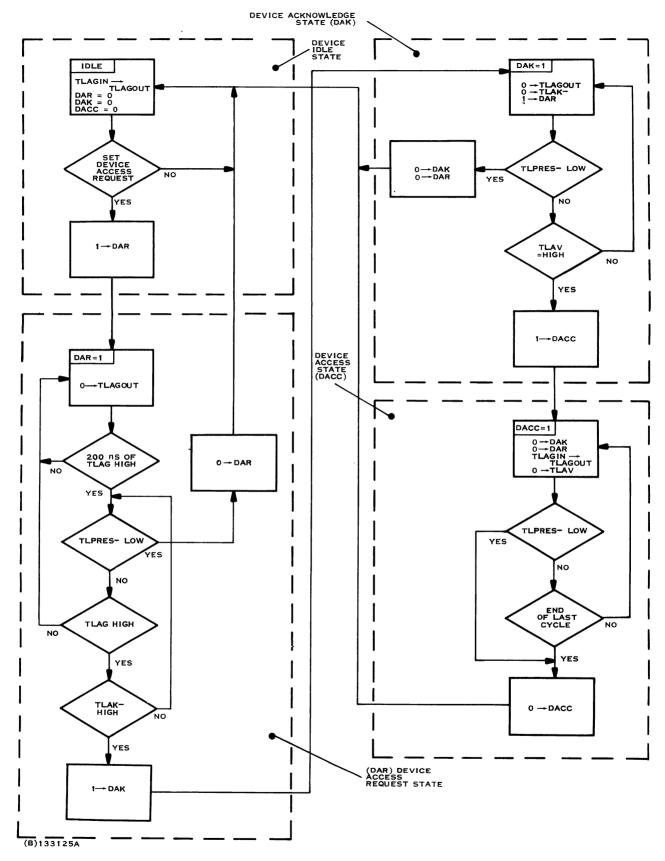

| 5-7        | TILINE Master Device                                                                           | 5-17   |

|            | LIST OF TABLES                                                                                 |        |

| Table      | Title                                                                                          | Page   |

| 1-1        | TMS 9900 Microprocessor Characteristics                                                        | 1-5    |

| 1-2        | Dedicated Workspace Registers                                                                  | 1-8    |

| 1-3        | TMS 9900 Microprocessor External Instruction Codes                                             |        |

| 1-4        | 990/5 Board Current Requirements in Amperes                                                    |        |

| 1-5        | Interprocessor Communications CRU Bit Assignments                                              | . 1-21 |

| 2-1        | Computer Chassis Specifications                                                                | 2-1    |

| 2-2        | CRU Expansion Board Jumper Options                                                             |        |

| 2-3        | CRU Buffer Board Jumper Options                                                                |        |

| 2-4        | Examples of TILINE Coupler Address Space Switch Settings                                       |        |

| 2-5        | Examples of TILINE Coupler Bias Switch Settings                                                |        |

| 2-6<br>2-7 | TILINE CRU Address Jumpers                                                                     |        |

| 2-1        | Location of Option Switches on the 990/5                                                       | . 2-41 |

| 3-1        | Programmer Panel, Controls and Indicators                                                      | 3-2    |

| 3-2        | Operator Panel, Control and Indicators                                                         | 3-5    |

| 4-1        | Instruction Execution Times                                                                    | . 4-12 |

| 4-2        | CRU Output Bits to Ports 1 or 2 (TMS 9902)                                                     |        |

| 4-3        | CRU Input Bits from Ports 1 or 2 (TMS 9902)                                                    | . 4-24 |

| 4-4        | CRU Output Bits to Port 3 (TMS 9903)                                                           | . 4-27 |

| 4-5        | CRC Polynomial Selection                                                                       | . 4-30 |

| 4-6        | Mode Selection                                                                                 |        |

| 4-7        | Configuration Selection                                                                        |        |

| 4-8<br>4-9 | Receive Character Length Select                                                                | . 4-31 |

| 4-10       | CRUOUT Addresses 0-11 — Data Output                                                            | . 4-31 |

| 4-11       | CRUIN Address 0-15 — Receiver Status and Interrupts, Port 3                                    | 4-32   |

| 4-12       | TMS 9903 CRU Input Bits 0 Through 15 Address Assignments,                                      | . 4-33 |

|            | Read Register Contents (Control Flag Set to 1), Port 3                                         | 4-35   |

| 4-13       | CRU Output and Input Bits 32 Through 47 Address Assignments                                    |        |

| 4 14       | (Modem Communications)                                                                         | . 4-35 |

| 4-14       | Communications Port 3 Selectable Transmit and Receive Clock Rates (Synchronous Communications) | . 4-36 |

| 5-1        | 990/5 System Interface Pin Out                                                                 | 5-2    |

| 5-2        | CRU Signals                                                                                    | 5-4    |

| 5-3        | 990/5 Interrupt Inputs                                                                         | 5-5    |

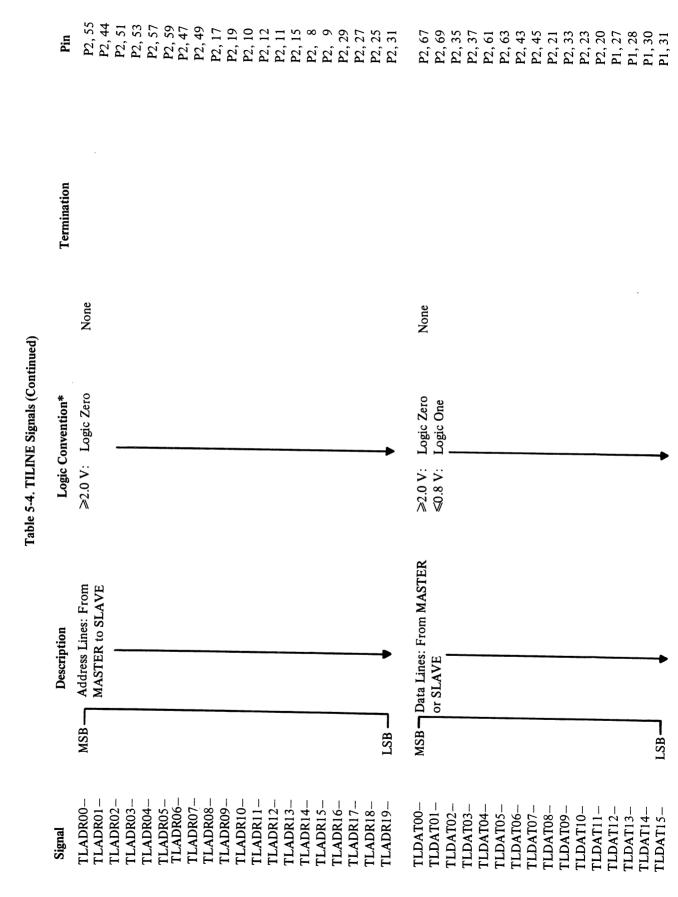

| 5-4        | TILINE Signals                                                                                 | . 5-10 |

| 5-5        | Miscellaneous Backpanel Signals                                                                | . 5-19 |

| 5-6<br>5-7 | Backpanel Power Pins                                                                           | . 5-20 |

| 5-7<br>5-8 | Front Panel Power/Signal Voltages                                                              | . 5-20 |

| 5-8        | Communications Interface Signals (P4, P5, and P6)                                              | . 5-21 |

(A) 140437

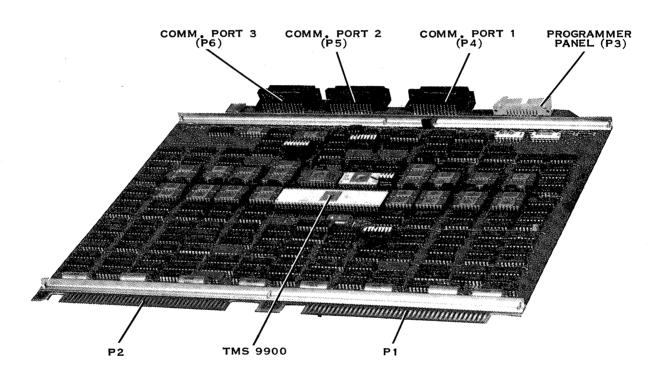

Figure 1-1. 990/5 Microcomputer Printed Circuit Board

#### SECTION I

#### **GENERAL DESCRIPTION**

#### 1.1 INTRODUCTION

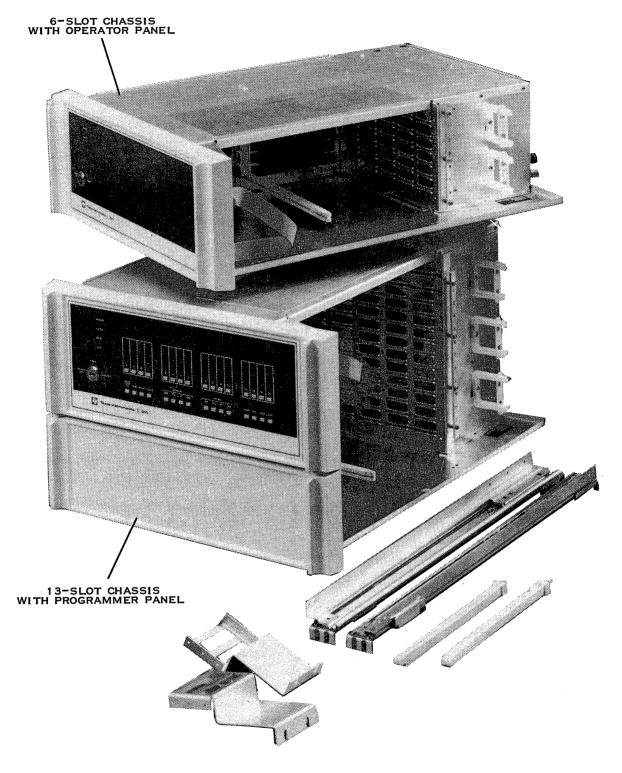

The Texas Instruments Model 990/5 Microcomputer is a complete basic computer packaged on a single, full-size ( $362 \times 274.3$  mm or  $14.25 \times 10.80$  in.) printed circuit board (see figures 1-1 and 1-2). The Central Processor Unit (CPU) for the 990/5 is the Model TMS 9900 Microprocessor made by Texas Instruments. In addition to the TMS 9900 microprocessor, the 990/5 microcomputer board provides the following standard features:

- TMS 4116 Dynamic Random-Access Memory (RAM) elements for a choice of 32 or 64K bytes of on-board memory.

- TMS 4700 Read-Only Memory (ROM) elements; the first 1K bytes of ROM are used for self-test and the other 1K bytes for loader programs.

- TMS 9902 Asynchronous Communications Controller (ACC) elements (two) provide interface between the 990/5 and serial, asynchronous communications channels.

- TMS 9903 Synchronous Communications Controller (SCC) element to provide interface between synchronous or asynchronous communications channels.

- Communications Register Unit (CRU) interface logic for serial I/O transfers with front panel and other CRU devices, e.g., 743 KSR, 810 Printer, single-density floppy disk, etc.

- TILINE\* interface logic for parallel data transfers to high speed devices such as magnetic tape units, moving head disk and dual-density floppy disk units, etc.

- Host-slave interface logic to transfer interrupts between host processor located in slot 1 and slave processor(s) in other card slots. (Host is always located in slot 1.)

- Clock elements to supply microprocessor and communications controllers with timing signals.

- Vectored interrupt logic to accommodate 16 levels of priority.

#### 1.2 EQUIPMENT DESCRIPTION

9

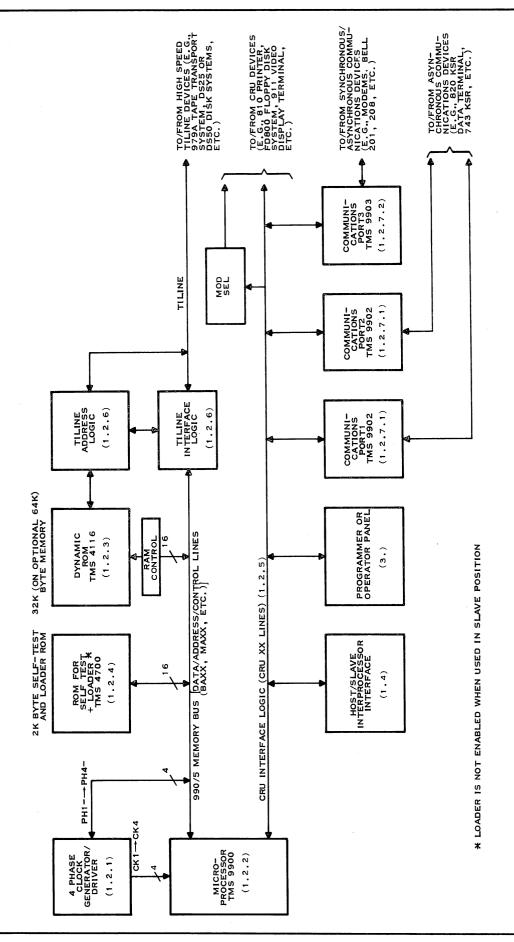

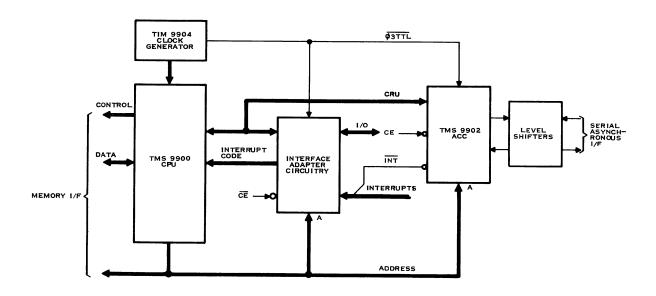

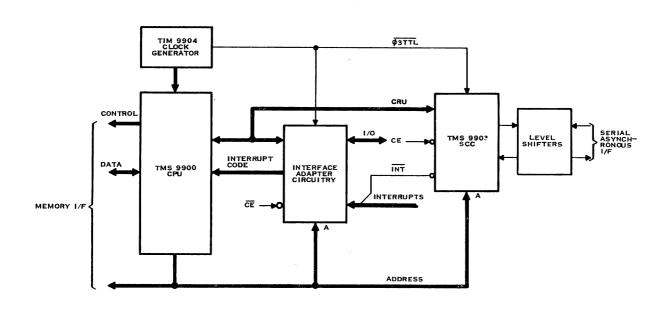

A simplified block diagram of the Model 990/5 microcomputer is shown in figure 1-3. Each of the blocks shown in this figure is described in the following paragraphs. The blocks shown in the diagram are described from left to right.

<sup>\*</sup> Trademark of Texas Instruments Incorporated

(A)140897

Figure 1-2. 990/5 Chassis Assembly (6- and 13-Slot Chassis)

ø

Figure 1-3. Model 990/5 Microcomputer Block Diagram

(B) 139348A

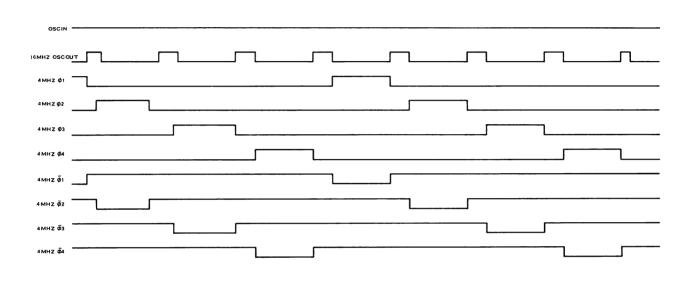

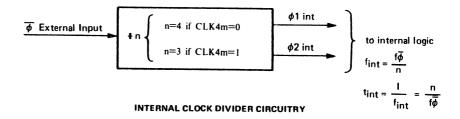

1.2.1 FOUR-PHASE CLOCK GENERATOR/DRIVER. The clock generator consists of an oscillator, a divide-by-four counter, and a second divide-by-four counter with gating to generate four clock phases. These clock phases provide clock inputs to the TMS 9900. The frequency of the internal oscillator is established by a 64 MHz quartz crystal and an LC circuit. The LC circuit connected to the tank inputs selects the desired crystal overtone. Crystal frequency (fundamental) is 64 MHz; output frequency to the TMS 9900 is 4 MHz. A timing diagram of the four-phase clock generator is shown in figure 1-4.

Figure 1-4. Clock Generator Timing Diagram

1.2.2 TMS 9900 MICROPROCESSOR. The TMS 9900 is a 16-bit microprocessor on an integrated circuit chip that functions as a full-scale, general purpose computer when combined with an external memory and a clock source. In addition to its compact size, the microprocessor offers features such as:

- Vectored interrupts and memory located register files for efficient context switching (a switch from one subprogram to another)

- Two I/O channels that include a command-driven (CRU) channel

- A 16-bit direct memory access channel (also buffered to form TILINE address lines external to the TMS 9900)

- Full 64K bytes of memory addressing space

- A flexible set of 69 instructions (five of which are implemented external to the chip and will be explained in paragraph 1.2.2.5).

A summary of TMS 9900 microprocessor characteristics is provided in table 1-1.

#### Table 1-1. TMS 9900 Microprocessor Characteristics

Item

Characteristic

Word size 16 bits

Maximum memory 64K bytes

Clock rate 4 MHz

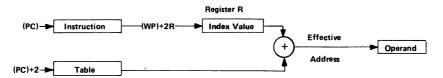

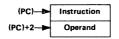

Addressing modes Immediate

Workspace register

Workspace register indirect Symbolic memory (direct)

Indexed memory

Workspace register indirect auto-

increment

Program Counter Relative

CRU Relative

Interrupts 16 interrupt levels

Working Registers 16 total

Input/Output Direct (CRU) and Direct Memory

Access (DMA)

Address bus 15 bits

Data bus 16 bits

Power +12 Vdc, ±5 Vdc

Package 64 pins, dual in-line package

Technology N-channel silicon gate

Instruction set 5 general address modes, set includes

multiply and divide

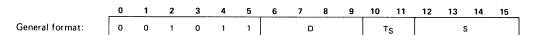

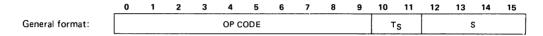

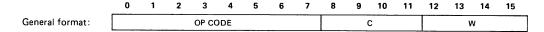

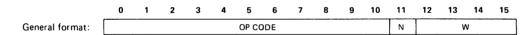

1.2.2.1 Microprocessor Architecture. The memory word of the TMS 9900 is 16 bits in length. Each word is also defined as 2 bytes of 8 bits each. The instruction set of the TMS 9900 allows both word and byte operands. Thus, all memory word locations are on even byte address boundaries. Byte instructions can address either the even or odd byte of a word. The memory space is 65536 bytes (or 32768 words). Word and byte formats are shown in figure 1-5.

1.2.2.2 Registers and Memory. The TMS 9900 employs an advanced memory-to-memory architecture. Blocks of memory designated as workspace replace internal hardware registers as program data registers. Dedicated TMS 9900 memory addresses are shown in figure 1-6. The first 32

words are used for interrupt trap vectors. The next contiguous block of 32 memory words is used by the extended operation (XOP) instruction for trap vectors. The last two memory words, FFFC<sub>16</sub> and FFFE<sub>16</sub>, are used for the trap vector of the LOAD signal. The remaining memory is then available for programs, data, and workspace registers. If desired, any of the special areas may also be used as general memory. Three internal registers are accessible to the user. The program counter (PC) contains the address of the instruction following the current instruction being executed. This address is referenced by the processor to fetch the next instruction from memory and is then automatically incremented. The status register (ST) contains the interrupt mask level and status information pertaining to the instruction operation. Each bit in the register signifies a particular function or condition that exists in the microprocessor. Figure 1-7 illustrates the bit position assignments. Some instructions use the status register to check for a prerequisite condition, others affect the values of the bits in the register, and others load the entire status register with a new set of parameters. The workspace pointer register (WP) contains the address of the first word in the currently active set of workspace registers. A workspace register file occupies 16 contiguous memory words in the general memory area (see figure 1-6). Each workspace register may hold data or addresses and function as operand registers, accumulators, address registers, or index registers. Some workspace registers take on special significance during execution of certain instructions. Table 1-2 lists each of these dedicated workspace registers and the instructions that use them. During instruction execution, the processor addresses any registers in the workspace by adding the register number to the contents of the workspace pointer as shown in figure 1-8.

Figure 1-5. Microprocessor Word and Byte Format

Figure 1-6. Dedicated Memory Addresses

Figure 1-7. Status Register Bit Assignments

(A)133119

Table 1-2. Dedicated Workspace Registers

| Register No. | Contents               | Used During                                                                         |

|--------------|------------------------|-------------------------------------------------------------------------------------|

| 0            | Shift count (optional) | Shift instructions (SLA, SRA, SRC and SRL)                                          |

| 11           | Return address         | Branch and Link Instruction (BL)                                                    |

|              | Effective address      | Software implemented Extended Operation (XOP)                                       |

| 12           | CRU base address       | CRU instructions (SBO, SBZ, TB, LDCR and STCR)                                      |

| 13           | Saved WP register      | Context switching (BLWP, RTWP, software XOP, recognized interrupt, LOAD, and RESET) |

| 14           | Saved PC register      | Context switching (BLWP, RTWP, software XOP, recognized interrupt, LOAD, and RESET) |

| 15           | Saved ST registers     | Context switching (BLWP, RTWP, software XOP, recognized interrupt, LOAD and RESET)  |

Figure 1-8. Workspace Pointer and Registers

The workspace concept is particularly valuable during operations that require a context switch (a change from one program to another or to a subroutine, as in the case of an interrupt). Such an operation using a conventional multiregister arrangement requires that at least part of the contents of the register file be stored and reloaded. A memory cycle is required to store or fetch each word. By exchanging the contents of the program counter, status register, and workspace pointer, the microprocessor accomplishes a complete context switch with only three store cycles and two fetch cycles. After the switch the workspace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine, and the contents of the WP, PC, and ST registers from the previous routine have been saved in new workspace registers 13, 14, and 15, respectively. A corresponding savings in time occurs when the original context is restored. Instructions in the microprocessor that result in a context switch include:

- Branch and Load Workspace Pointer (BLWP)

- Return from Subroutine (RTWP)

- Extended Operation (XOP)

Device interrupts, power-up RESET—, and LOAD— also cause a context switch by forcing the microprocessor to trap to a service routine.

1.2.2.3 Interrupts. The TMS 9900 microprocessor can accommodate 16 interrupt levels with the highest priority level 0 and the lowest level 15. Level 0 is reserved for the power-up RESET—function, and all other levels may be used for external devices. The external levels may also be shared by several device interrupts, depending upon system requirements.

The microprocessor continuously compares the interrupt code (ICO through IC3) with the interrupt mask contained in status register bits 12 through 15. When the level of the pending interrupt is less than or equal to the enabling mask level (higher or equal priority interrupt), the microprocessor recognizes the interrupt and initiates a context switch following completion of the currently executing instruction. The processor fetches the new context WP and PC from the interrupt vector locations. Then, the previous context WP, PC, and ST are stored in workspace registers 13, 14, and 15 of the new workspace. The microprocessor then forces the interrupt mask to a value that is one less than the level of the interrupt being serviced, except for the level 0 interrupt that loads zero into the mask. This allows only interrupts of higher priority to interrupt a service routine. The microprocessor also inhibits interrupts until the first instruction of the service routine has been executed so that program linkage is preserved should a higher priority interrupt occur. All interrupt requests should remain active until recognized by the microprocessor in the device service routine. The individual service routines must reset the interrupt requests before the routine is complete. If a higher priority interrupt occurs, a second context switch is made to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the first service routine parameters to the processor to complete processing of the lower priority interrupt. All interrupt subroutines should terminate with the return instruction to restore original program parameters.

1.2.2.4 Input/Output. The TMS 9900 microprocessor uses a versatile direct command-driven I/O interface designated as the Communications Register Unit (CRU). The CRU provides up to 4096 directly addressable input bits and 4096 directly addressable output bits. Both input and output bits can be addressed individually or in fields of from 1 to 16 bits. The microprocessor employs three dedicated I/O pins (CRUIN, CRUOUT, and CRUCLK) and 12 bits (A3 through A14) of the address bus at the interface to the CRU system. The microprocessor instructions that drive the CRU interface can set, reset, or test any bit in the CRU array or move data between memory and CRU data fields.

Because of its extremely flexible data format, the CRU interface can be used effectively for a wide range of control and data transaction operations. These applications can be divided into two broad categories: those involving a single control bit transfer, and those requiring input or output of several data or status bits.

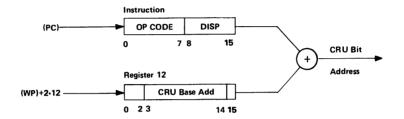

The microprocessor performs three single-bit CRU functions: test bit (TB), set bit to one (SBO), and set bit to zero (SBZ). To identify the bit to be operated upon, the microprocessor develops a CRU-bit address and places it on the address bus, A3 to A14.

For the two output operations (SBO and SBZ), the microprocessor generates a CRUCLK pulse that indicates to the CRU device that the operation is one of output and places bit 7 of the instruction word on the CRUOUT line to accomplish the specified operation (bit 7 is a logic 1 for SBO and a logic 0 for SBZ). The test bit instruction is an input operation that transfers the addressed CRU bit from the CRUIN input line to bit 2 (equal bit, see figure 1-7) of the status register.

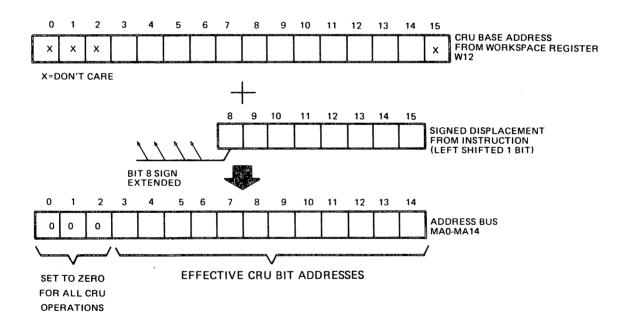

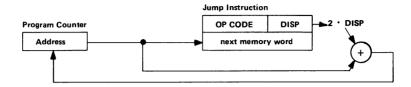

The microprocessor develops a CRU-bit address for the single-bit operations from the CRU base address contained in workspace register 12 (W12) and the signed displacement contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The base address from bits 3 through 14 in W12 is added to the signed displacement specified in the instruction and the result is loaded onto the address bus. Figure 1-9 illustrates the development of a single-bit CRU address.

NOTE: MEMORY ADDRESS LINES MA3 THROUGH MA14 ARE RENAMED CRUBIT4 THROUGH

CRUBIT15 AT THE OUTPUTS OF THE CRU ADDRESS DRIVERS

(A)133120

Figure 1-9. TMS 9900 Single-Bit CRU Address Development

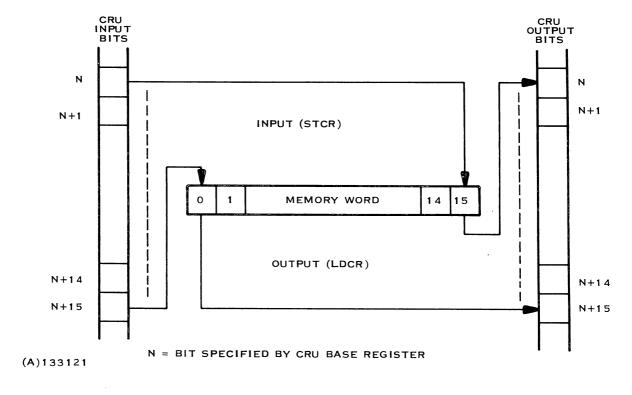

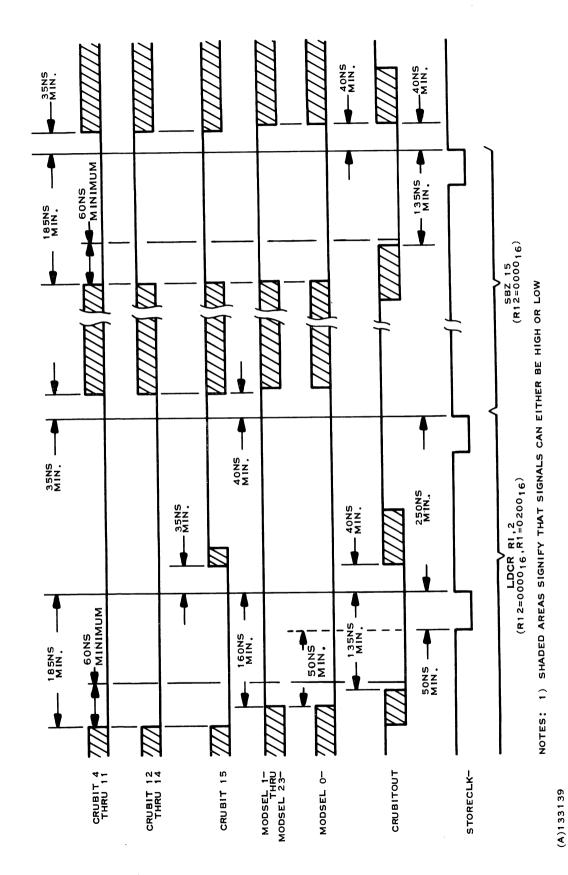

The microprocessor performs two multiple-bit CRU operations: store communications register (STCR) and load communications register (LDCR). Both operations perform a data transfer from CRU to memory or from memory to CRU as illustrated in figure 1-10. Although the figure shows a full 16-bit transfer operation, any number of bits from 1 to 16 may be involved. The LDCR instruction fetches a word from memory and right-shifts the word to serially transfer it to CRU output bits. If the LDCR involves 8 or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves 9 or more bits, those bits come from the right-justified field within the whole memory word. As the bits are transferred to the CRU interface, the CRU address is incremented for each successive bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest addressed bit in the CRU field.

An STCR instruction transfers data from the CRU to memory. If the operation involves a transfer of a byte or less, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves 9 to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero. When the input from the CRU device is complete, the first bit from the CRU is in the least significant bit position in the memory word or byte.

Figure 1-10. TMS 9900 LDCR/STCR Data Transfer

1.2.2.5 External Instructions. The TMS 9900 microprocessor has five external instructions that allow user-defined external functions to be initiated under program control. These instructions are Clock-On (CKON), Clock-Off (CKOF), Reset (RSET), Idle (IDLE), and Load and Restart Execution (LREX). Except for IDLE, these instructions relate to functions that have been implemented on the 990/5 circuit board but these functions do not restrict use of the instructions to initiate various user-defined functions in external devices. IDLE also causes the microprocessor to enter and remain in the idle state until an interrupt, RESET— or LOAD—, occurs. When any of these five instructions are executed by the microprocessor, a unique 3-bit code appears on the three most significant bits of the address bus (A0 through A2) along with the CRUCLK pulse. When the microprocessor is in an idle state, the 3-bit code and CRUCLK pulses occur repeatedly until the idle state is terminated. The external instructions codes are shown in table 1-3.

| Table 1-3. TMS 9900 Microprocessor External Instruction Cod |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| EXTERNAL INSTRUCTION | <b>A0</b> | A1 | A2 |

|----------------------|-----------|----|----|

| LREX                 | Н         | Н  | Н  |

| CKOF                 | Н         | Н  | L  |

| CKON                 | Н         | L  | Н  |

| RSET                 | L         | Н  | Н  |

| IDLE                 | L         | Н  | L  |

1.2.2.6 Load Function. The LOAD—signal permits cold-start ROM loaders and front panels to be implemented for the TMS 9900 microprocessor. When active, LOAD—causes the microprocessor to initiate a trap immediately following the instruction being executed.

Memory location FFFC<sub>16</sub> is used to obtain the trap vector (WP and PC). The old PC, WP, and ST are loaded into the new workspace, and the interrupt mask is set to 0000. Then, program execution resumes using the new PC and WP.

1.2.3 TMS 4116 DYNAMIC RANDOM-ACCESS MEMORY. The TMS 4116 is a 16,384 one-bit memory element. Each bit of the sixteen-bit word handled by the microprocessor is stored in its own element; a seventeenth element is available for parity. For a basic 990/5, this arrangement of elements allows for storage/retrieval of 32,768 bytes (32K bytes). The microcomputer may be expanded to an additional 32K bytes when 17 more TMS 4116 elements are included; one element for each bit of the 16-bit word and one element for the parity bit.

#### NOTE

Refresh operations are performed every 15.5  $\mu$ secs of one memory cycle duration.

1.2.4 TMS 4700 READ-ONLY MEMORY. The Read-Only Memory contains preprogrammed self-test and loader software. There are two elements; one for the lower order 8 bits, the other for the upper order 8 bits. Together, the two elements provide for storage of 1024 words of 16 bits each. One half of the storage capacity (512 sixteen-bit locations from address F800<sub>16</sub> to FBFE<sub>16</sub>) is used for computer self-test; the other half of ROM is used for loader programs (addresses FC00<sub>16</sub> through FFFE<sub>16</sub>).

The ROM can only be addressed by the TMS 9900 microprocessor; ROM cannot be addressed via the TILINE. Note that the lower half of this memory (addresses F800<sub>16</sub> through FBFE<sub>16</sub>) is addressed at the same address as that reserved for the TILINE peripheral control space (TPCS). Access to either the TPCS or ROM self-test is determined by the state of ENROMAF800 (Enable ROM at address F800). This signal is the result of a set-bit-to-one (SBO) instruction addressed to CRU output bit at location hexadecimal 17F8. When enabled, TMS 9900 microprocessor memory cycles in this address range go to ROM and exercise self-test. The lower half of ROM is disabled by resetting the CRU output bit with an SBZ (set-bit-to-zero) instruction at location 17F8<sub>16</sub>. With the lower half of ROM disabled, TMS 9900 microprocessor memory cycles in this address range are directed to the TILINE as accesses to the TPCS. The lower half of ROM is also disabled whenever the 990/5 microcomputer is in the RUN mode. The upper half of ROM, containing loader programs (addressed at FC00<sub>16</sub> through FFFE<sub>16</sub>), is always ready to accept addresses in this range. Additional information on the TMS 4700 ROM may be found in Section IV, entitled Programming Considerations.

1.2.5 COMMUNICATION REGISTER UNIT INTERFACE LOGIC. The direct command driven input/output interface for the 990/5 microcomputer is called the CRU. The CRU provides for up to 4096 directly addressable input bits and up to 4096 directly addressable output bits. Input and output operations can address each of the bits individually or in fields of from one to sixteen bits. The microprocessor instructions that drive the CRU can set, reset, or test any bit in the CRU array; or the microprocessor instructions can move data between memory and the CRU data fields.

Logic for the CRU is implemented on the 990/5 circuit board and this logic exerts control over the interface data and control lines that consist of a clock, data in, data out, CRU address lines, and decoded module select lines. The 990/5 circuit board logic implements the CRU interface to the 990 chassis backpanel, the programmer panel, the three on-board communications ports, and the host processor interface logic. The CRU interface to the chassis backpanel is disabled when the 990/5 circuit board is installed in a chassis slot other than slot 1. See figures 2-9 and 2-16, respectively, for the basic 6-slot and 13-slot chassis configurations.

- 1.2.5.1 Module Select Logic. Twenty-four module select signals are decoded by CRU interface logic and are distributed, two per chassis slot, to twelve chassis slots when a 13-slot chassis is in use. Similarly, ten module select signals are distributed to five chassis slots when the 6-slot chassis is used. In either case, no module select signal distribution is made to chassis slot 1. Each full-sized chassis slot has the capability to implement a maximum of 32 input/output bits. The main chassis CRU addresses begin at 000 and extend to a maximum of hexadecimal 09F for a 6-slot chassis and to a maximum of hexadecimal 17F for the 13-slot chassis. If a computer system requires more CRU slots than are available in a main chassis, then from one to seven additional 6- or 13-slot CRU expansion chassis can be added. The chassis and backpanels used in the expansion chassis are identical to those used for the main chassis.

- 1.2.5.2 Backpanel CRU Interface Signals. Logic on the 990/5 circuit board implements a dedicated CRU interface for the programmer panel and also the standard CRU interface for the main chassis. The interface signals to the main chassis are routed via connectors P1 and P2 on the 990/5 circuit board. The master 990/5 circuit board is installed in slot 1 in the main chassis. The remaining slots are designated slots 2 through 6 for a 6-slot chassis and slots 2 through 13 for a 13-slot chassis. Both connectors in each chassis slot are furnished with the CRU select bits (CRUBIT 12-15) and other CRU interface signals that permit each connector to pass signals to address 16 bits of the CRU. Connector P1 in a chassis slot receives one module select signal corresponding to one 16-bit register whereas connector P2 receives two module select signals and thus may address up to 32 bits of the CRU. Connector P1 also receives the eight most significant bits of the CRU address thus permitting the chassis slot to be used for a CRU expansion driver or for modules that ignore the module select signals and decode their own CRU addresses, i.e., CRUBIT04 through CRUBIT15.

- 1.2.6 TILINE INTERFACE LOGIC. The 990/5 CRU provides a TILINE bus interface. TILINE is a high-speed, parallel bus interconnecting 990 CPUs, memories, and autonomous high-speed devices such as disk controllers. TILINE permits implementation of tightly coupled multiprocessor systems with advanced features such as shared memory.

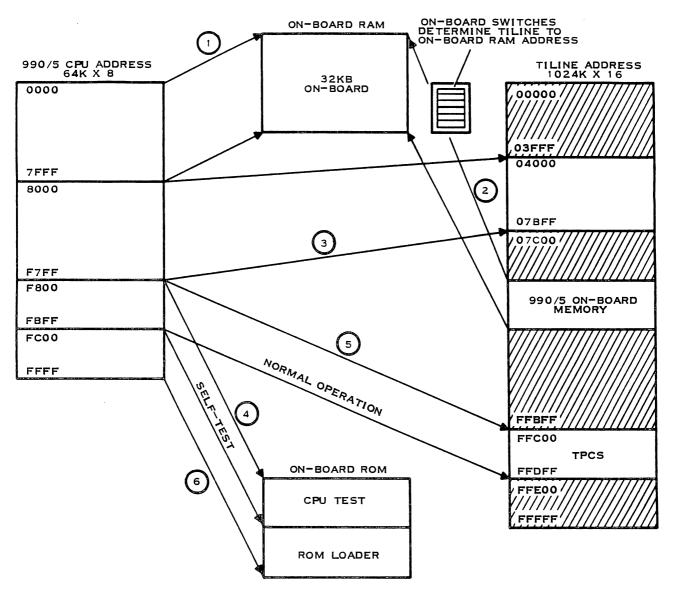

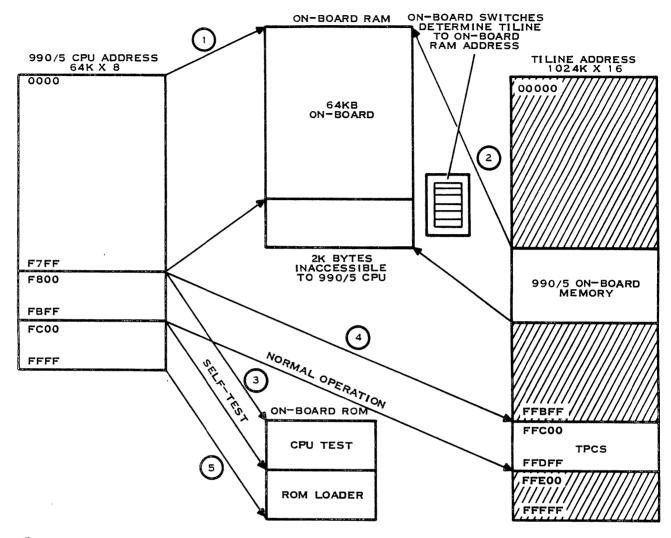

The TILINE bus address is 20 bits in length and describes a  $1024K \times 16$  bit address space. The 990/5 CPU generates a 16-bit address identifying locations in a  $64K \times 8$  bit address space. The relationship of these addresses for a 32K byte system and a 64K byte system are shown in figures 1-11 and 1-12, respectively.

- 1 CPU ADDRESSES 0000-7FFF ALWAYS ADDRESS ON-BOARD RAM

- TILINE CAN ADDRESS ON-BOARD RAM. TILINE ADDRESS IS SET BY ON-BOARD SWITCHES ANYWHERE IN TILINE ADDRESS SPACE ON 4K WORD BOUNDARIES.

- (3) CPU ADDRESSES 8000 F7FF REACH TILINE ADDRESSES 04000 07FFF

- (4) CPU ADDRESSES F800 FBFF DURING SELF-TEST ADDRESS ON-BOARD ROM

- 5 CPU ADDRESSES F800 FBFF AFTER SELF-TEST ADDRESS TILINE PERIPHERAL CONTROL SPACE

- 6 CPU ADDRESSES FC00 FFFF ADDRESS ON-BOARD ROM LOADER

(A) 1393518

Figure 1-11. 32KB 990/5 and TILINE Addressing

- 1 CPU ADDRESSES 0000 F7FF ALWAYS ADDRESS ON-BOARD RAM

- TILINE CAN ADDRESS ON-BOARD RAM. TILINE ADDRESS IS SET BY ON-BOARD SWITCHES ANYWHERE IN TILINE ADDRESS SPACE ON 4K WORD BOUNDARIES.

- 3 CPU ADDRESSES F800 FBFF DURING SELF-TEST ADDRESS ON-BOARD ROM

- CPU ADDRESSES F800 FBFF AFTER SELF-TEST ADDRESS TILINE PERIPHERAL CONTROL SPACE

- 5 CPU ADDRESSES FC00 FFFF ADDRESS ON-BOARD ROM LOADER

(A) 139350B

Figure 1-12. 64KB 990/5 and TILINE Addressing

1.2.6.1 Master-Slave Concept. There are two classes of devices that connect to the TILINE: TILINE master devices that control data transfers and TILINE slave devices that generate or accept data in response to some master device. (This discussion of TILINE master/slave relationships should not be confused with the CPU host and CPU slave relationship.) Data transfers in either direction always occur between one master and one slave. A processor is an example of a master device; a memory module is an example of a slave device. All slave devices recognize a specific address and are activated only when addressed. For example, a memory module is activated when some master device performs a read operation from an address within the bounds of its address. The configuration of the system must be such that only one slave device recognizes a particular address. For memory modules, pencil switches on the modules are set to provide the desired starting address and size of the module.

Peripheral device controllers are both master and slave devices. Special registers addressed at specific memory addresses near the high end of the memory address space (TILINE peripheral control space) constitute the slave part of the peripheral controller. The registers are loaded by the processor using memory-to-memory move instructions. The registers specify the parameters of a peripheral data transfer. In the case of a disk, they specify disk address, the number of words of data to be transferred, the memory address to which the data is to be transferred, and whether the data is to be read or written. One register in each peripheral controller is a status register for that controller. The bits in the register indicate information such as "operation complete", "read error", "rewind complete", and "illegal command". Other bits in the peripheral controller status register are set by the central processor to command the peripheral to start, stop, clear its interrupt, or reset. All of these registers are addressed by the central processor as consecutive words of memory at some specific address. Pencil switches are used to set the address of the registers for each peripheral controller. When a peripheral controller operation is started by the central processor, it transfers data between memory and the peripheral device by cycle-stealing with the central processor and any other master devices that may be active. When a peripheral controller needs to transfer a word of data over the TILINE, the master device part of the peripheral controller must gain access to the TILINE and then may address a slave (such as a memory module) and read from, or write to it.

1.2.6.2 990/5 TILINE Operation. The 990/5 CPU is both a TILINE slave and TILINE master device. As a TILINE slave device, the 990/5 CPU is seen as a contiguous 32K bytes or 64K bytes (as equipped) block of memory with its starting address selectable at 4K boundaries through the use of eight pencil switches. Switches 1 through 8 are set to the most significant eight bits of the desired starting TILINE address. Switch 1 is the most significant bit; switch 8 is the least significant of the eight bits mentioned above.

As a TILINE master device, the 990/5 microprocessor can access TILINE Peripheral Control Space (TPCS) by decoding accesses in the address range of hexadecimal F800 through FBFE and forcing the five most significant TILINE address bits to logic 1 when the decode is true. In addition, when the 990/5 microprocessor has only 32K bytes of memory, accesses above address hexadecimal 8000 but below address hexadecimal F800 are made to TILINE memory with the address unmapped. This permits more than one processor to share a common 30K bytes of TILINE memory.

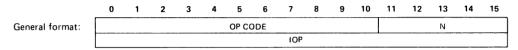

1.2.7 COMMUNICATIONS PORTS. Three communications ports are implemented on the 990/5 circuit board. Each port is a CRU device with a dedicated, hardwired CRU address. Ports 1 and 2 are each implemented with a TMS 9902 Asynchronous Communication Controller (ACC) and are addressed at CRU addresses hexadecimal 1700 and 1740, respectively. Port 3 is implemented with a TMS 9903 Synchronous Communication Controller (SCC) with additional external logic and is addressed at CRU address hexadecimal 1780. None of the three ports has a hardware reset. Therefore, a communications enable bit at CRU address hexadecimal 17CE enables all three communications ports. An SBO instruction to the bit should be executed after the software reset of the three ports. The interrupt from each port is enabled or inhibited by directing an SBO or SBZ to the appropriate CRU output bit. The CRU output bits are addressed as follows: port 1 interrupt at

hexadecimal 17C8, port 2 interrupt at hexadecimal 17CA, port 3 interrupt at hexadecimal 17CC. The two ACC ports are used for local asynchronous communications with peripheral devices such as an ASR or printer. The third port may be used in either the asynchronous or the synchronous mode to support either local or modem communications. When used in the synchronous mode, the baud rate for the third port is selectable. All three ports meet standards of EIA RS232-C as established by the Electronic Industries Association.

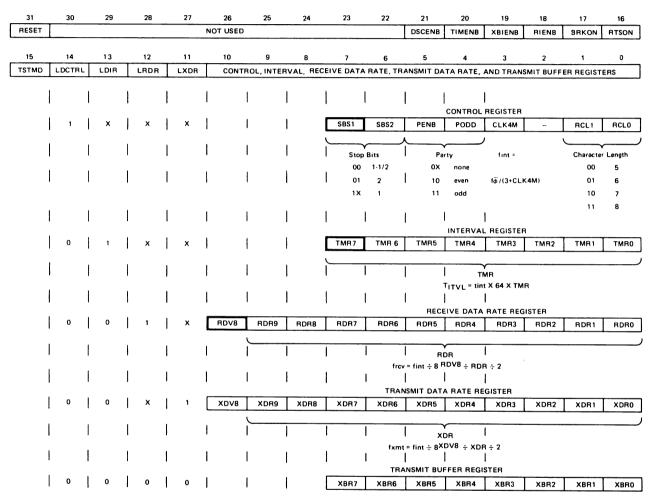

- 1.2.7.1 Asynchronous Communications Ports. The TMS 9902 ACC devices used to implement communications ports 1 and 2 provide an interface between the TMS 9900 microprocessor and serial asynchronous communications channels. They perform the timing and data serialization and deserialization, thus facilitating the control of the asynchronous channel by the microprocessor. Key features of the TMS 9902 ACC are as follows:

- 5- to 8-bit character length

- 1, 1.5, or 2 stop bits

- Even, odd, or no parity

- Fully programmable data rate generation

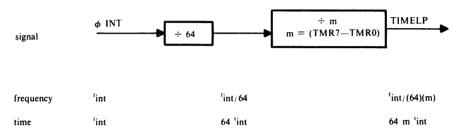

- Interval timer with resolution from 64 to 16,320 microseconds

- Fully TTL compatible, including single power supply

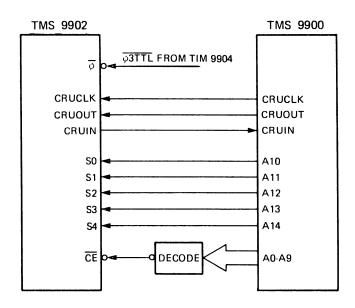

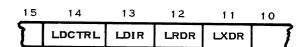

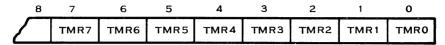

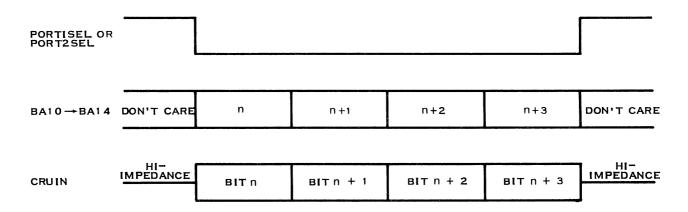

The TMS 9902 interface to the asynchronous channel is through level shifters which translate the TTL inputs and outputs to standard RS-232. The TMS 9902 interface to the TMS 9900 microprocessor through the CRU provides up to 32 directly addressable output bits and up to 32 directly addressable input bits. The CRU interface consists of 12 address lines and three dedicated input/output lines (CRUIN, CRUOUT, and CRUCLK). When the TMS 9902 is addressed by the TMS 9900 microprocessor, the seven most significant bit address lines (BA03 through BA09) generate a low port select signal that is applied to the chip enable pin (CE—) of the TMS 9902. With CE— active (low), the five least significant bit address lines (BA10 through BA14 that are connected to address pins S0 through S4 of the TMS 9902, respectively) address the CRU input or output bit being accessed. When data is being transferred from the TMS 9900 microprocessor to the TMS 9902, a CRUCLK pulse indicates that the operation is one of output, and valid data on the CRUOUT lines is transferred to the addressed CRU output bit of the TMS 9902. When data is to be transferred from the TMS 9902 to the microprocessor, data from the addressed CRU input bit is placed on the CRUIN line for transfer. More detailed information on the TMS 9902 may be found in Section IV, Programming Considerations.

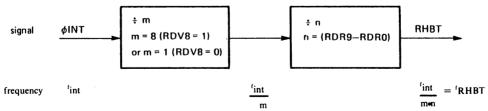

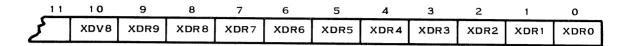

1.2.7.2 Synchronous Communications Port. The TMS 9903 used to implement communications port 3 provides the system designer with a wide range of capabilities in synchronous and asynchronous communications control. Communications port 3 can be used to support local synchronous or asynchronous communications or can be used with a modem. The TMS 9903 operates in a multi-mode configuration that allows a broad range in the degree of active participation required in the control of high-speed serial communications. Most synchronous datalink control protocols can be supported through software control of sync and fill characters, timing, CRC generation and detection, etc. Universal applicability is further assured through the dynamic character length selection from 5- to 9-bit data words plus parity.

Definition and operation of all communications control is under software control, which makes upgrading to another protocol simply a matter of changing software with no hardware changes required. Key features of the TMS 9903 SCC are as follows:

- DC to 250 KBPS data rate, half- or full-duplex

- Dynamic character length selection

- Line protocols, including BI-SYNC, SDLC, HDLC, and many others

- Programmable polynomial CRC generation and detection

- Interface to unclocked or NRZI data with 32X clocks

- Two programmable sync registers

- On-chip interval timer (64  $\mu$ s to 16.32 ms)

- Automatic zero insert and delete for SDLC and HDLC

- Single +5 V supply, 20-pin DIP, all inputs and outputs TTL compatible

- N-channel Silicon-Gate technology

- Replaces 100 SSI and MSI devices

The TMS 9903 interface to the synchronous or asynchronous channel is through level shifters which translate the TTL inputs and outputs to the appropriate level. The TMS 9903 interface to the microprocessor through the CRU provides 32 directly addressable output bits and 32 directly addressable input bits. The CRU interface consists of 12 address lines and three dedicated input/output lines (CRUIN, CRUOUT, and CRUCLK).

1.2.8 INTERRUPTS. Logic for 15 vectored interrupt levels (13 external) is contained on the 990/5 microcomputer circuit board. Each interrupt input is terminated with a 470-ohm pull-up resistor and a flip-flop to synchronize interrupts with the microprocessor clock. The highest priority interrupt level is reserved as a power-up trap. The interrupt levels are assigned priority rankings from level 0 (highest priority) to level 15 (lowest priority). All priority interrupt levels with the exception of the power-up interrupt (level 0) are maskable under software control. Interupt inputs are synchronized with the 990/5 clock, encoded, and presented to the TMS 9900 microprocessor along with an interrupt request. The interrupt levels are vectored for rapid reaction to recognized interrupts. That is, corresponding to each interrupt level is a two-word vector located in low-order memory (addresses 00 through 3E, hexadecimal). When the TMS 9900 microprocessor recognizes an interrupt, it loads the vector for that level into the Workspace Pointer (WP, first vector word) and the Program Counter (PC, second vector word) to defined the new workspace and program starting point for the interrupt servicing routine. A number of interrupt conditions are generated on the 990/5 circuit board and are wired directly to interrupt inputs. The interrupt conditions are discussed in the paragraphs that follow.

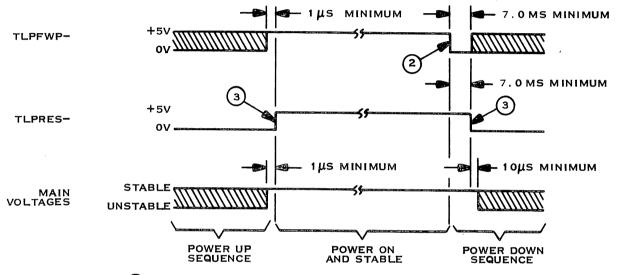

1.2.8.1 Power Failure Interrupt. When ac power begins to fail in a standard TI chassis, a sensor in the power supply generates a TLPFWP— pulse that is applied to the 990/5 circuit board as a level I interrupt. The microcomputer has 7.0 milliseconds of program time after receipt of the power failure warning before a power supply reset halts operation.

- 1.2.8.2 Error Interrupt. Logic to generate an error interrupt at priority level 2 is contained on the 990/5 circuit board. The error interrupt is a merging of memory parity error detect logic and the TILINE timeout condition. Each of these conditions is latched in an error register. The 990/5 microcomputer may access parity error status and timeout status by executing a CRU read instruction to CRU input bits 12 and 15, respectively, at CRU base address hexadecimal 1FC0. A CRU write instruction similarly addressed clears parity error and timeout conditions. Additionally, a write instruction addressed to CRU output bit 12 at CRU base address hexadecimal 1FE0 (front panel) also clears the parity error condition. Both conditions are cleared by execution of the reset instruction.

- 1.2.8.3 Real-Time-Clock Interrupt. The standard TI chassis power supply provides a line frequency synchronized clock input to the 990/5 circuit board that is used by logic on the board to implement a real-time-clock interrupt function. This function may be connected to interrupt level 5 (standard) or interrupt level 15, or it may be disconnected. External instructions CKON and CKOF are used to enable or disable the real-time-clock interrupt function.

- 1.2.8.4 Communications Ports Interrupts. An interrupt from each of the three communications ports may be connected to an external interrupt input by a switch. When activated, connections are as follows: communications port 1 to interrupt level 8, communications port 2 to interrupt level 14, and communications port 3 to interrupt level 6. These interrupts are masked until a CRU output instruction is issued to set output bits 36, 37, and 38, respectively, of CRU base address hexadecimal 1780.

- 1.2.8.5 Host Processor Interrupt. When a 990/5 microcomputer is installed in a chassis slot other than slot 1, it performs as a slave processor. A host processor (installed in chassis slot 1) may generate an interrupt to the slave processor through the host processor CRU. This interrupt is hardwired to interrupt level 3. The slave processor may mask the interrupt by setting bit 14 of CRU base address hexadecimal 17E0 (see paragraph 1.4).

#### 1.3 990/5 CHARACTERISTICS AND SPECIFICATIONS

The power requirements for the 990/5 circuit board are listed in table 1-4. The specifications for the 6- and 13-slot chassis are listed in table 2-1.

#### 1.4 MULTIPROCESSOR FEATURES

The 990/5 microcomputer features hardware which facilitate multiprocessor applications including multiple CPUs in a single chassis. It should be noted to prospective users that successful multiprocessor applications require careful planning at system and software levels. The most basic multiprocessor feature is the TILINE multi-user bus which permits shared memory modules and access from one CPU to another CPU's memory.

The 990/5 CPU identifies itself as host when plugged into slot 1 of the chassis. As the host, the 990/5 controls external CRU chassis wiring and has, in addition to 1K of ROM self-test, 1K of ROM for bootstrap loading.

A 990/5 CPU in any chassis slot other than slot 1 identifies itself as slave. Slave 990/5 drivers for external CRU chassis wiring are disabled, and the bootstrap loader is disabled. The slave 990/5 has 1K of self-test, controls on-board CRU, and may address TILINE devices in TILINE Peripheral Control Space (TPCS).

An interprocessor communications scheme provides CRU-driven maskable interrupts between processors. Any slave addresses the host at a single CRU address. The host addresses each slave independently. Differentation among multiple slaves is implemented by on-board pencil switches to provide a 4-bit identification code. This identification is independent of the station identification which is used by host 990/5 CPUs only.

Table 1-4. 990/5 Board Current Requirements in Amperes

| Voltage*    | With 32K<br>Bytes | With 64K<br>Bytes |

|-------------|-------------------|-------------------|

| Operating:  |                   |                   |

| +5V Main    | 2.25              | 2.50              |

| +12V Main   | .20               | .20               |

| -12V Main   | .04               | .04               |

| +5V Memory  | .30               | .30               |

| +12V Memory | .33               | .65               |

| -5V Memory  | .02               | .03               |

| Standby:    |                   |                   |

| +5V Memory  | .30               | .30               |

| +12V Memory | .025              | .050              |

| -5V Memory  | .02               | .03               |

<sup>\*</sup>Maximum tolerance for all voltages except -5V Memory is  $\pm 3$  percent. Tolerance for -5V Memory is  $\pm 6$  percent.

#### 990/5 Microcomputer Board Dimensions:

274.32 mm (10.8 inches) wide by 361.95 mm (14.25 inches) long by 1.5575 mm (.062 inch) thick. Component height on board is 8.89 mm (.350 inch), maximum.

In a single chassis, interprocessor communications are limited to slave-host and host-slave; i.e., no slave-slave direct communications can occur. The slave processor (not to be confused with a TILINE slave device) and the host processor may interrupt each other, mask interrupts from each other, acknowledge interrupts from each other, and enable interrupts from each other on interrupt acknowledge. The host processor uses 64 CRU bits, beginning at CRU address hexadecimal 1F40 (Register R12 = hexadecimal 1E80), to communicate with up to sixteen slave processors. The 990/5 microprocessor circuit board contains four switches that permit selection of one of sixteen groups of four bits each to which the slave processor responds. The 990/5 microprocessor uses four bits at CRU address hexadecimal 1BF0 (Register R12 = hexadecimal 17E0) to communicate with a host processor. Table 1-5 lists the CRU bit assignments and a description of each.

# Table 1-5. Interprocessor Communications CRU Bit Assignments

| Output Bit | Description                                                                      |  |

|------------|----------------------------------------------------------------------------------|--|

| 0          | Interrupt remote processor                                                       |  |

| 1          | Interrupt local processor on receipt of remote processor's interrupt acknowledge |  |

| 2          | Acknowledge interrupt from remote processor                                      |  |

| 3          | Interrupt from remote processor mask (1 = Enable; 0 = Disable)                   |  |

| Input Bit  |                                                                                  |  |

| 0          | Interrupt to remote processor active                                             |  |

| 1          | Slave fault (in 990/5) or logic 0 (in other CPUs)                                |  |

| 2          | Interrupt from remote processor active                                           |  |

| 3          | Slave idle (in 990/5) or logic 0 (in other CPUs)                                 |  |

.

#### **SECTION II**

#### INSTALLATION

#### 2.1 GENERAL

This section provides information and procedures for unpacking the microcomputer from its shipping container, installing it in either a tabletop or a rackmounted chassis, and checking the operation of the newly installed computer system. This section also includes a procedure for modifying the interrupt structure of the computer and verifying that the proper jumper wire options have been installed. The procedures assume that the user has a fundamental knowledge of basic handtools and cabling techniques, but they do not require a detailed understanding of computer hardware or software. This section does not cover installation of any of the peripheral devices that may accompany the computer shipment. Installation instructions for those devices are included in the Installation and Operation manual that is shipped with each peripheral device. To aid in planning to meet the installation requirements for the computer, table 2-1 summarizes the specifications and requirements of the available chassis for the computer.

Table 2-1. Computer Chassis Specifications

| Characteristic                   | 6-Slot Chassis                      | 13-Slot Chassis                     |

|----------------------------------|-------------------------------------|-------------------------------------|

| Height                           | 178 mm<br>(7 inches)                | 311 mm<br>(12-¼ inches)             |

| Width                            | 419 mm<br>(16-½ inches)             | 419 mm<br>(16-½ inches)             |

| Depth                            | 584 mm<br>(23 inches)               | 584 mm<br>(23 inches)               |

| Ambient Temperature <sup>1</sup> |                                     | •                                   |

| Operating <sup>2</sup>           | 0° to 50°C<br>(32° to 122°F)        | 0° to 40°C<br>(32° to 104°F)        |

| Storage                          | -40° to +70°C<br>(-40° to +158°F)   | 40° to +70°C<br>(40° to 158°F)      |

| Humidity <sup>3</sup>            | 0% to 95%                           | 0% to 95%                           |

| Altitude                         | 0 to 3.05 km<br>(0 to 10,000 feet)  | 0 to 3.05 km<br>(0 to 10,000 feet)  |

| Heat Load                        |                                     |                                     |

| Full Card Slot<br>Power Supply   | 30 watts<br>100 watts               | 30 watts<br>170 watts               |

| Exhaust Temperature              | 65°C (maximum)<br>(149°F (maximum)) | 65°C (maximum)<br>(149°F (maximum)) |

#### Notes:

- Lower the upper operating limit by 2°C (3.6°F) for every 762 metres (2500 feet) increase in altitude.

- 2. If the 990/5 board is to be installed in other than a standard TI chassis, the following environmental conditions are required:

Ambient air temperature at board<sup>1</sup>

5°C to 65°C

(41°F to 149°F)

Air flow at exhaust

100 ft/min

3. No condensation should be allowed.

Table 2-1. Computer Chassis Specifications (Continued)

| Characteristic              | 6-Slot Chassis                                                                                    | 13-Slot Chassis                                                                                  |

|-----------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| External Power Requirements |                                                                                                   | ,                                                                                                |

| Standard                    | 115 Vac +15%, -10%<br>3-wire service<br>(hot, neutral, gnd)                                       | 115 Vac +15%, -10%<br>3-wire service<br>(hot, neutral, gnd)                                      |

| Optional                    | 100, 200, or 230 Vac<br>+15%, -10%<br>or 220 + 10%, -15%<br>3-wire service<br>(hot, neutral, gnd) | 100, 200, or 230 Vac<br>+15%, -10%<br>or 220 +10%, -15%<br>3-wire service<br>(hot, neutral, gnd) |

There is considerable flexibility in the 990/5 Interrupt, CRU address, and TILINE address assignments. This flexibility is matched in the TI standard software packages by a capability in these software packages to define the I/O assignments. The software and hardware assignments must agree. A 990/5 user, who also intends to use the TI standard software packages, should read the programming considerations in paragraph 4.1 before selecting particular I/O assignments.

#### 2.2 SITE PREPARATION

Site preparation, which includes the power, space, environmental, special supply, and communications requirements for the Model 990/5 Minicomputer System, is covered in detail in the following paragraphs.

2.2.1 HARDWARE ENVIRONMENT CONSIDERATIONS. The customer is responsible for providing an environment that is free of excessive dust and foreign particles. This environment may be a typical office environment free from excessive airborne matter that may cause damage to the equipment. The requirements listed below are necessary for proper operation of the 990/5:

|                         | 990 Chassis   | Equip. Desk and Single-Bay Pedestal | Rackmount<br>Cabinet |

|-------------------------|---------------|-------------------------------------|----------------------|

| Input Power Frequency:1 | 60 Hz         | 60 Hz                               | 60 Hz                |

| Input Current:          | 7.5 amps      | 20.0 amps                           | 30.0 amps            |

| Watts:                  | 862.5         | N/A                                 | N/A                  |

| Btu/hr: <sup>2</sup>    | 2950          | N/A                                 | N/A                  |

| Power Cord Length:      | 1.8 m (6 ft.) | 3.6 m (12 ft.)                      | 3.6 m (12 ft.)       |

<sup>&</sup>lt;sup>1</sup> All units are powered by 115 Vac +15%, -10%.

Ac outlets must be located so that the power cords are not stretched or in danger of damage once the hardware is in place. The cord may not lay in traffic lanes and must be capable of carrying a minimum of 20 amps.

The ac input lines for all TI equipment will be dedicated; no non-TI device may share the same ac power lines.

No electrically noisy equipment may be plugged into the power to impair operation of the equipment. Examples of noisy equipment are: air conditioners, compressors, copy machines, electric fans, neon lights, and ac motors.

<sup>&</sup>lt;sup>2</sup> Calculations are based on 1 watt = 3.413 Btu/hr.

The 115 Vac wiring shall consist of a hot, a neutral, and an earth return. The earth return (ground) will be terminated properly and in such a manner that it makes a good connection to the earth (ground) return at the power source.

The user will ensure that the ac receptacle is wired as shown in figure 2-1.

#### NOTE

Rackmount cabinets require receptacles for 30 amp service.

2.2.2 SPACE REQUIREMENTS. All equipment will be positioned such that a three-foot clearance exists on all sides of the desk, cabinet, and disk drive. Figures 2-2 and 2-3 give dimensions for space requirements.

(A) 140387

Figure 2-1. Site AC Receptacle Wiring

#### SINGLE BAY PEDESTAL

(A) 140388

Figure 2-2. Single-Bay Pedestal Dimensions

Figure 2-3. Single-Bay Desk Dimensions

2.2.3 INTERCONNECT CABLING REQUIREMENTS. A typical system cabling configuration is given in figure 2-4. The preinstallation site inspection should be completed at least two weeks prior to installation. If the system is to use remote CRTs and line printers, the cables and connector kits should be installed and checked-out at least one week prior to system installation.

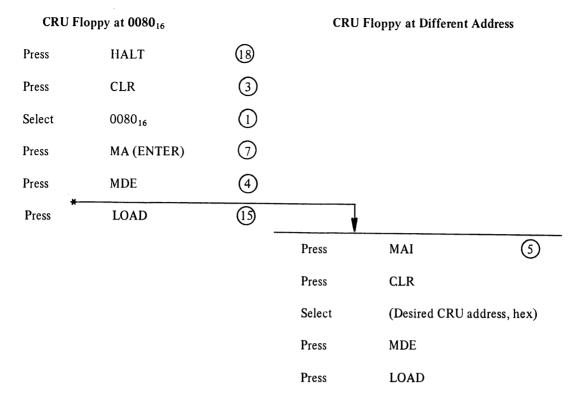

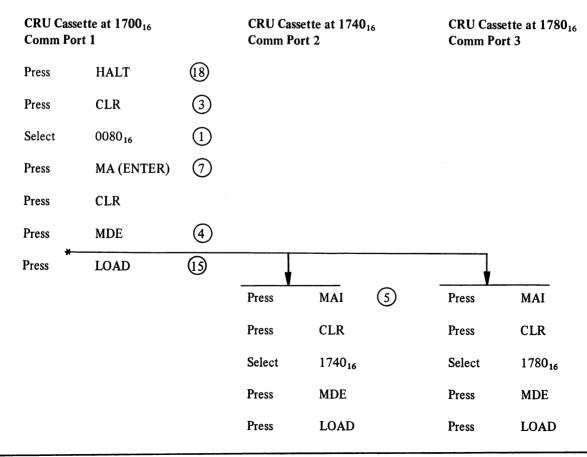

Route the peripheral cables in such a manner that there are no breaks or splices in the cables. Both ends of all cables will be clearly marked with a semi-permanent marking, such as good quality masking tape or gum labels. An example of this is shown in figure 2-5. If the user mounts a peripheral in a desk or other device, the desk must not bind any cables, and the control knobs should be easily accessible.