# OPERATION AND MAINTENANCE INSTRUCTIONS:

ASC-4X CENTRAL PROCESSOR (CP-4X)

VOLUME 1

Equipment Group P.O. Box 2909 Austin, Texas 78767

# TEXAS INSTRUMENTS

931443-2 January 1976

#### © Texas Instruments Incorporated 1976 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

# LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Operation and Maintenance Instructions: ASC-4X Central Processor (CP-4X), Vol. 1, P/N 931443-2

Total number of pages in this publication is 298 consisting of the following:

| PAGE<br>NO.       | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|-------------------|---------------|-------------|---------------|-------------|---------------|

| Title             | 0             |             |               |             |               |

| Effective Pages . | 0             |             |               |             |               |

| iii - x           | 0             |             |               |             |               |

| 1-1 - 1-32        | 0             |             |               |             |               |

| 2-1/2-2           | 0             |             |               |             |               |

| 3-1/3-2           | 0             |             |               |             |               |

| 4-1 - 4-252       | 0             |             |               |             |               |

### TABLE OF CONTENTS

| Paragraph                                                                                | Title                                                                                                                                                                                                                                                                                  | Page                                          |  |  |  |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|

|                                                                                          | SECTION I. GENERAL DESCRIPTION                                                                                                                                                                                                                                                         |                                               |  |  |  |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1                                                        | General                                                                                                                                                                                                                                                                                | 1-1<br>1-1<br>1-3<br>1-5                      |  |  |  |

| 1.4.2<br>1.4.3<br>1.4.4<br>1.4.5<br>1.4.6<br>1.4.7<br>1.4.8                              | Register File          Instruction Files          Instruction Registers          Address Modification          Address and Operand Registers          IMM/REG Registers          Memory Address Control                                                                                | 1-5<br>1-5<br>1-5<br>1-5                      |  |  |  |

| 1.4.9<br>1.4.10<br>1.4.11<br>1.4.12<br>1.4.13<br>1.4.14                                  | Memory Buffer File                                                                                                                                                                                                                                                                     | 1-6<br>1-6<br>1-6<br>1-6<br>1-6               |  |  |  |

| 1.4.15<br>1.4.16<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.9.1                             | Arithmetic Pipeline EF Output Register General Characteristics CP Instruction Set Instruction Format Data Formats Physical Description Cooling System Logic Circuits                                                                                                                   | 1-7<br>1-7<br>1-24<br>1-25<br>1-27            |  |  |  |

|                                                                                          | SECTION II. INSTALLATION                                                                                                                                                                                                                                                               |                                               |  |  |  |

| 2.1                                                                                      | General                                                                                                                                                                                                                                                                                | 2-1                                           |  |  |  |

|                                                                                          | SECTION III. OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                    |                                               |  |  |  |

| 3.1                                                                                      | General                                                                                                                                                                                                                                                                                | 3-1                                           |  |  |  |

|                                                                                          | SECTION IV. PRINCIPLES OF OPERATION                                                                                                                                                                                                                                                    |                                               |  |  |  |

| 4.1<br>4.2<br>4.2.1<br>4.2.1.1<br>4.2.1.2<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.4.1<br>4.2.5 | General       IPU Level 0         Look-Ahead Register (LA)          Cycle Interruptions          Output Compare          Load Look-Ahead Counter          Branch Address Register (BA)          Present Address Register (PA)          PA Inputs          Output Address Register (OA) | 4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-2<br>4-2 |  |  |  |

| Paragraph          | Title                                                  |       |       |       |     |     | Page   |

|--------------------|--------------------------------------------------------|-------|-------|-------|-----|-----|--------|

| 4251               | Da D                                                   |       |       |       |     |     | _      |

| 4.2.5.1<br>4.2.5.2 | P3 Register Output                                     |       |       |       |     |     | 4-13   |

|                    | LA Register Output                                     |       |       |       |     |     | 4-13   |

| 4.2.5.3            | AK Register Output                                     |       |       |       |     |     | 4-13   |

| 4.2.5.4            | Load/Store Details                                     |       |       |       |     |     | . 4-13 |

| 4.2.6              | New Memory Interface File                              |       |       |       |     |     | 4-13   |

| 4.2.6.1            | Instruction Processing                                 |       |       |       |     | •   | 4.13   |

| 4.2.6.2            | Load/Store Details                                     |       |       |       |     | • • | 4.13   |

| 4.2.6.3            | Store File                                             |       |       |       |     |     | 4 1 4  |

| 4.2.7              | KA/KB Current Instruction Files                        |       |       |       |     |     | 4 14   |

| 4.2.8              | The Select                                             |       |       |       | ٠.  | • • | 4 14   |

| 4.2.9              | Word Select                                            |       |       |       |     |     | 4 1 4  |

| 4.2.10             | Level 0 Controller                                     |       | •     |       |     | • • | 4 14   |

| 4.3                | II C Level 1                                           |       |       |       |     |     | 4 1 4  |

| 4.3.1              | P1 Register                                            | • • • | • •   |       | • • |     | 4-14   |

| 4.3.2              | Instruction Register (IR)                              |       |       |       | • • | • • | 4-15   |

| 4.3.3              | Level 1 Controller                                     |       | • •   | • • • | • • | • • | 4-15   |

| 4.4                | Register File                                          |       | • •   |       | • • | • • | 4-15   |

| 4.4.1              | Base Address File, A and B                             |       |       |       |     |     | 4-15   |

| 4.4.2              | General Storage File, C and D                          |       |       |       | ٠.  | • • | 4-15   |

| 4.4.3              | Index File. I                                          | • •   |       |       | • • |     | 4-15   |

| 4.4.4              | Vector Parameter File, V                               | • •   |       |       |     |     | 4-15   |

| 4.5                | IPU Level 2                                            | • •   | • •   |       |     |     | 4-15   |

| 4.5.1              | IPU Level 2  Level 2 Controller  Level 2 POM           |       |       |       |     |     | 4-16   |

| 4.5.2              | Level 2 ROM                                            |       | • •   |       |     |     | 4-16   |

| 4.5.3              | R2 Register                                            |       | • • • |       |     |     | 4-16   |

| 4.5.4              |                                                        | • •   | • •   |       |     | • • | 4-16   |

| 4.5.5              | Indexing Register (XR) Displacement Register (NR)      |       |       |       |     |     | 4-17   |

| 4.5.6              | Displacement Register (NR)                             |       |       |       | • • |     | 4-17   |

| 4.5.7              | P2 Register                                            |       |       |       |     |     | 4-18   |

| 4.6                | Base Address Register (BR)                             |       |       |       |     |     | 4-18   |

| 4.6.1              |                                                        |       |       |       |     |     | .4-18  |

| 4.6.2              | Modification Adder Adder Resultant (AR) Register       |       |       |       |     |     | .4-18  |

| 4.6.3              | Adder Resultant (AR) Register P3 Register              | • •   |       |       |     |     | .4-18  |

| 4.6.4              | P3 Register                                            |       |       |       |     |     | .4-18  |

| 4.6.5              | Level 3 ROM ROM Supplement Register (C3)               | ٠.    |       |       |     |     | .4-19  |

| 4.6.6              | ROM Supplement Register (C3)                           |       |       |       |     |     | .4-19  |

| 4.6.7              |                                                        |       |       |       |     |     | .4-19  |

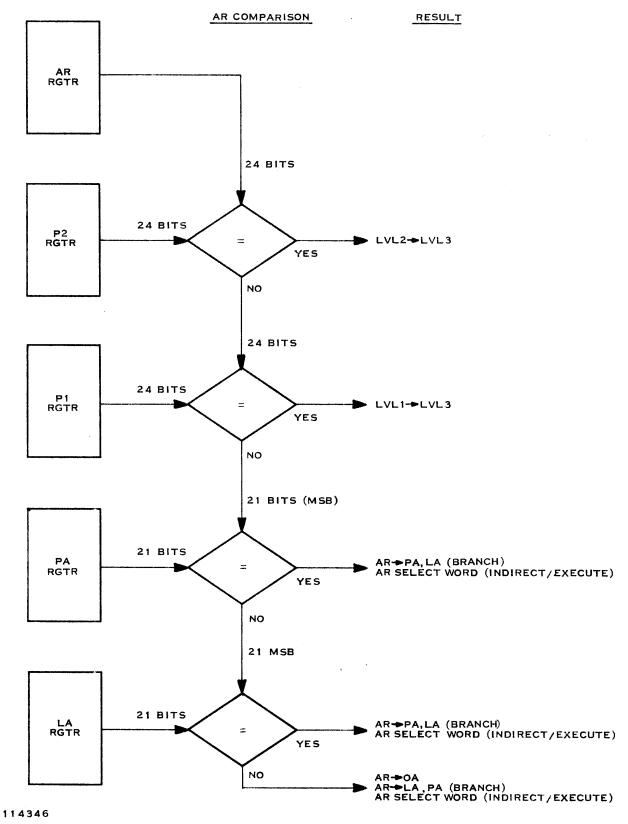

| 4.6.8              | Level 3 Controller  Branch Indirect Execute Comparison |       |       |       |     |     | .4-19  |

| 4.7                | Branch, Indirect, Execute Comparison IPU Level 4       |       |       |       |     |     | .4-19  |

| 4.7.1              |                                                        |       |       |       |     |     | .4-21  |

| 4.7.2              | Level 4 Controller                                     |       |       | • •   |     |     | .4-21  |

| 4.7.3              |                                                        |       |       |       |     | ٠.  | .4-21  |

| 4.7.4              | Register Hazard Comparison  AO Register                |       |       |       |     |     | .4-21  |

| 4.7.5              |                                                        |       |       |       |     |     | .4-23  |

| 4.7.6              |                                                        |       |       |       |     |     | .4-23  |

| 4.7.7              | a Operand Hazard Companson                             |       |       |       |     |     | 4 2 2  |

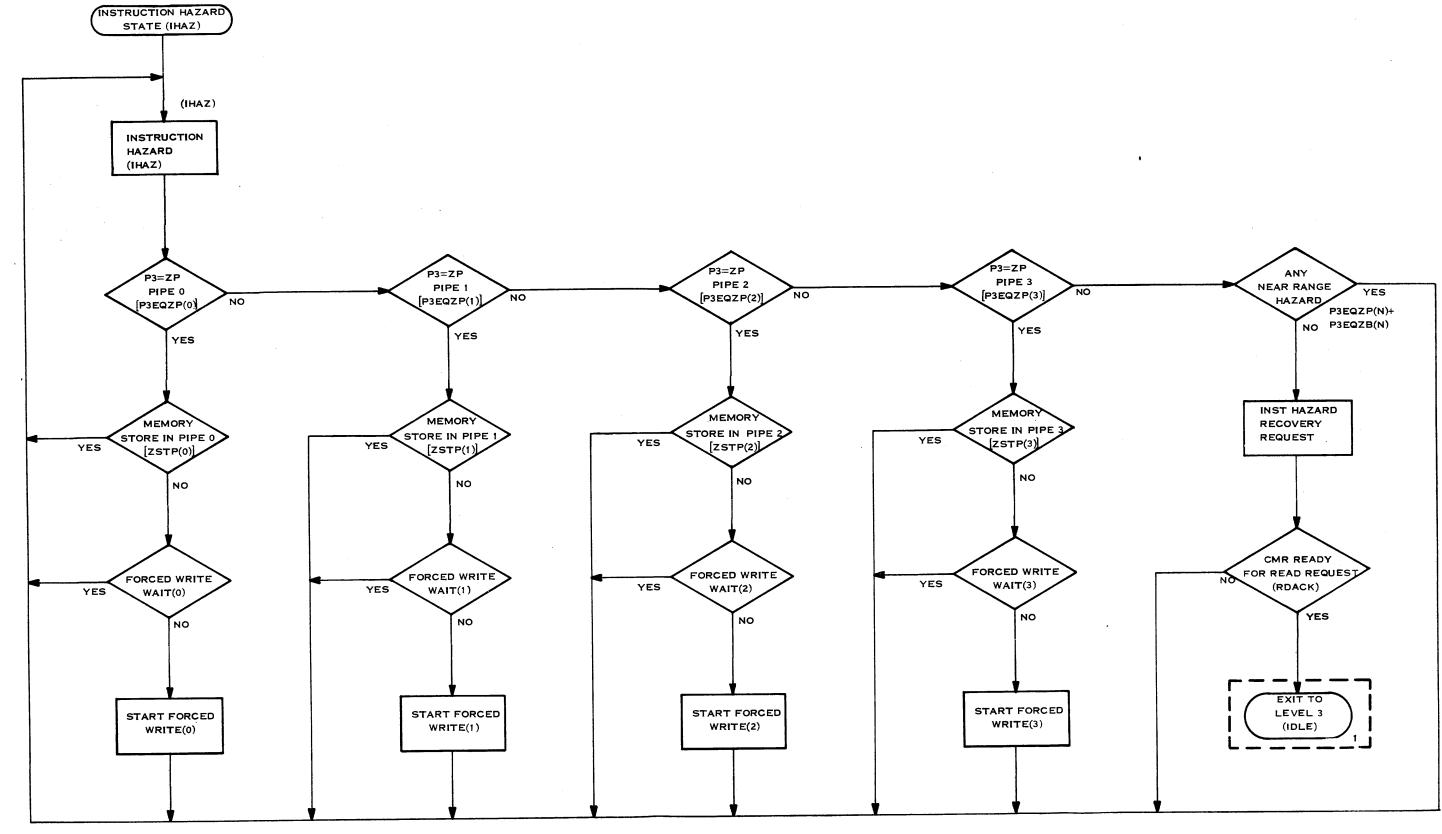

| 4.7.8              | real Range histraction hazard Comparison               |       |       |       |     |     | 4 2 5  |

| 4.7.9              | range instruction hazard comparison                    |       |       |       |     |     | 1 25   |

| 4.8                | RO Register                                            |       |       |       |     |     | 100    |

|                    | Master Hard Core (I4MHCA)                              |       |       |       |     |     | .4-26  |

| Paragraph | Title                                                         | Page             |

|-----------|---------------------------------------------------------------|------------------|

| 4.8.1     | Capture Common Command Register (Capture CCR)                 | 4-2              |

| 4.8.2     | MCW, MCP and Error Monitor                                    | 4-2'             |

| 4.8.2.1   | CP Control Register ,                                         | 4-2              |

| 4.8.2.2   | CP Switches                                                   | 4-27             |

| 4.8.2.3   | MHC Response                                                  |                  |

| 4.8.3     | Sequence Control                                              | 4-28             |

| 4.8.4     | CCR Output Register                                           | 4-28             |

| 4.8.5     | Unit Register Read                                            | 4-30             |

| 4.9       | Memory Buffer Units (MBUS)                                    | 4-30             |

| 4.9.1     | Memory Interface File (SC)                                    | 4-30             |

| 4.9.2     | Vector Buffer File (XB, XH, YB, YH)                           | 4-30             |

| 4.9.3     | Operand Buffer Files (X, Y)                                   | 4-30             |

| 4.9.4     | X and Y Word Select                                           | 4.33             |

| 4.9.5     | MAB/MCD Output Registers                                      | 4.33             |

| 4.9.5.1   | Scalar Data Paths                                             | A_33             |

| 4.9.5.2   | Vector Data Paths                                             | 4_37             |

| 4.9.6     | REG Register                                                  | 4.33             |

| 4.9.7     | IMM Register                                                  | <del>4-</del> 33 |

| 4.9.8     | Z Register Select                                             | 4 22             |

| 4.9.9     | Z Resultant Storage File                                      | 4 22             |

| 4.9.10    | ZH Half Phase Holding File                                    | 4-33             |

| 4.9.11    | ZB Memory Storage File                                        | 4 24             |

| 4.9.12    | ROM Address Register                                          | 4-34             |

| 4.9.13    | ROM Address Select                                            | 4-34             |

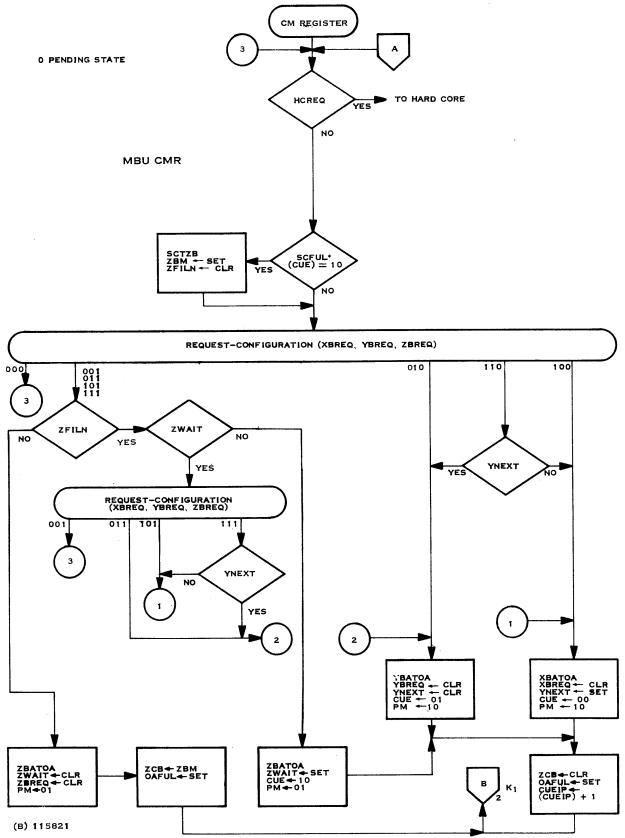

| 4.9.14    | MBU ROM                                                       | 4-35             |

| 4.9.15    | ROM Output Register                                           | 4-35             |

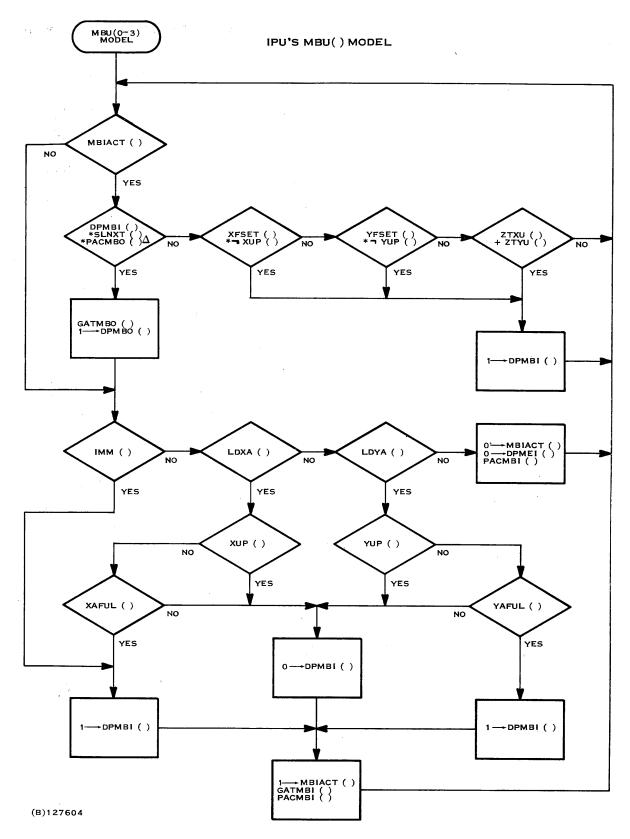

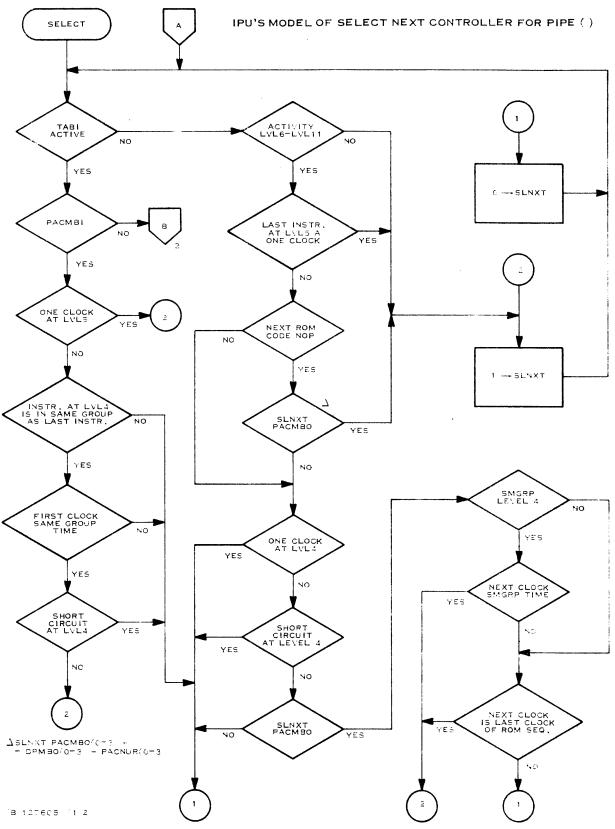

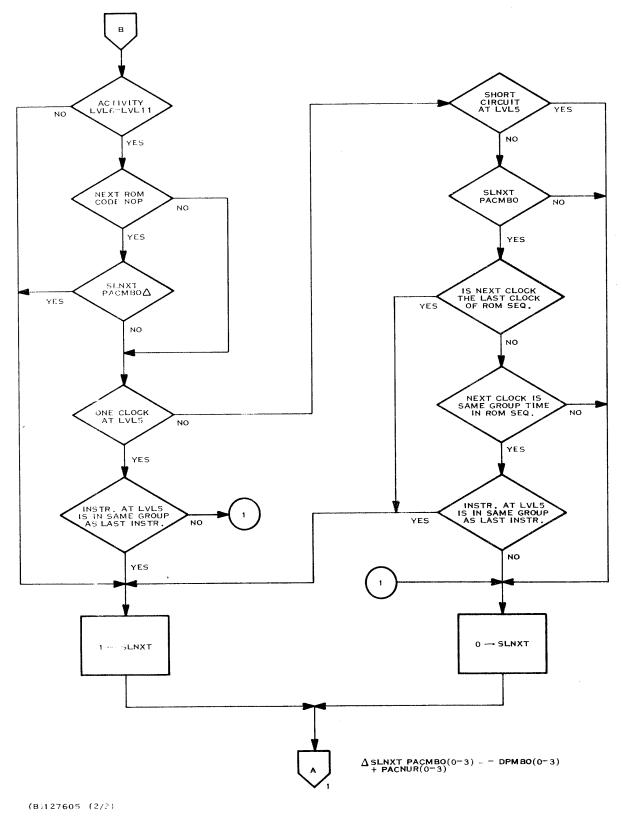

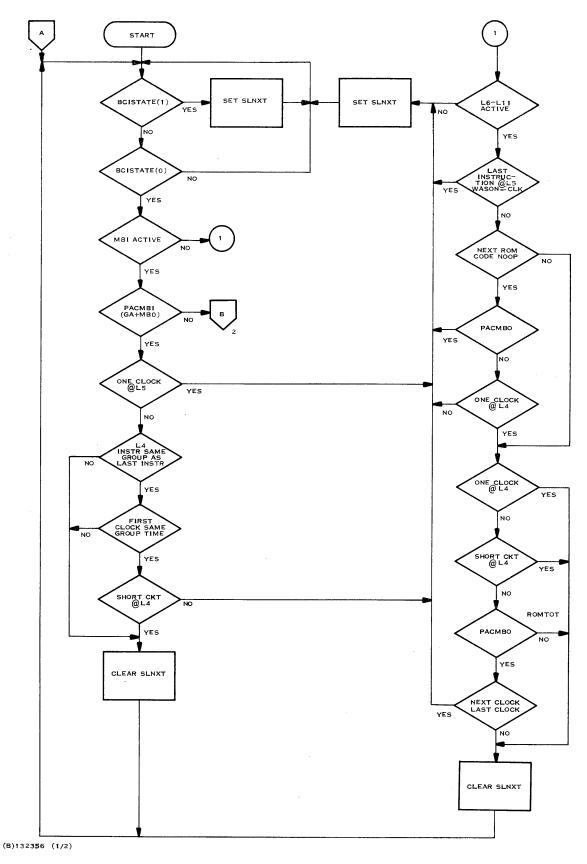

| 4.9.16    | Select Next Controller                                        | 4-35             |

| 4.9.17    | AU Control                                                    | 4-35             |

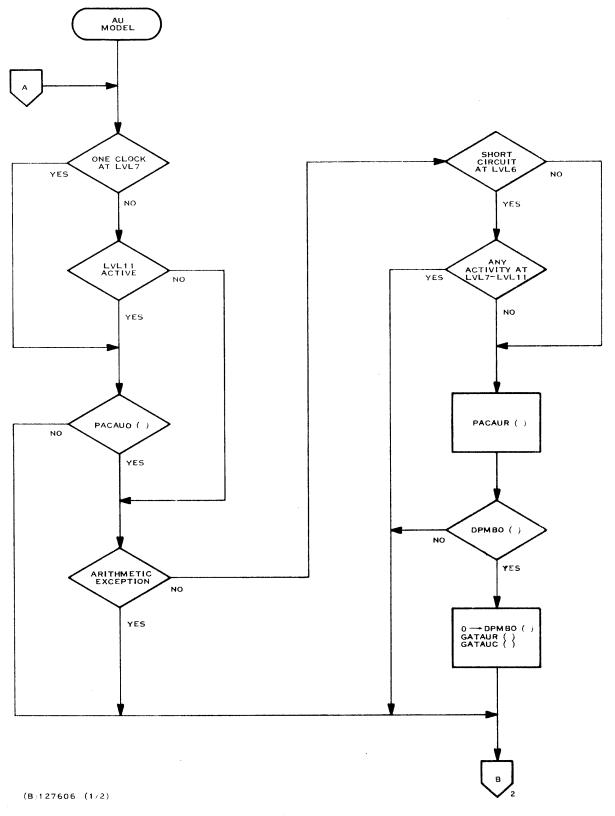

| 4.9.18    | AU Model                                                      | 4-35             |

| 4.9.19    | Z Data and Address Control                                    | 4-35             |

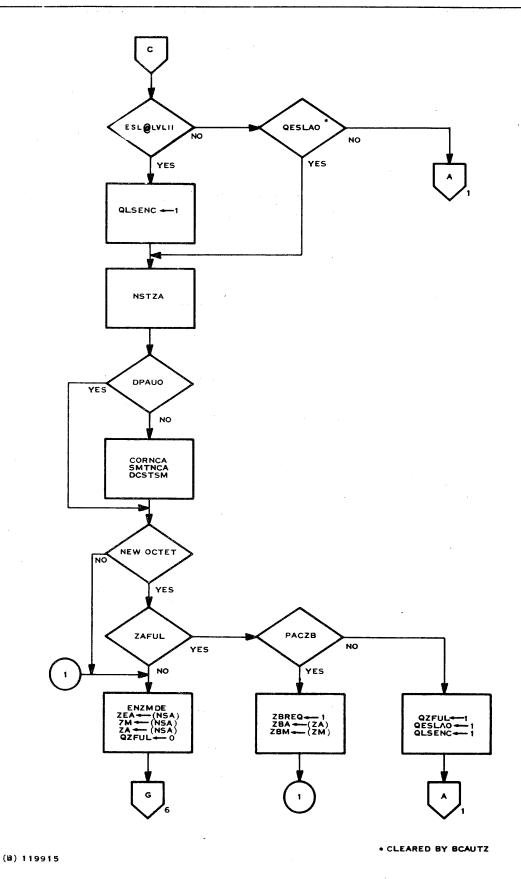

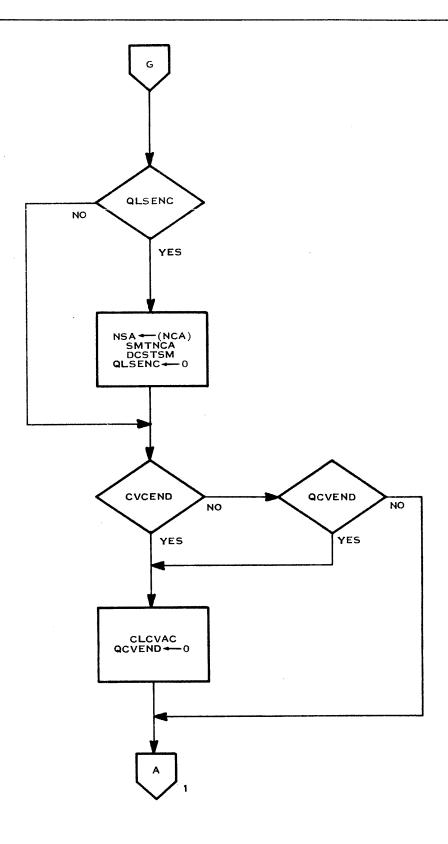

| 4.9.20    | Z Data and Address Control  Level 5 Controller                | 4-35             |

| 4.9.21    | Level 6 Controller                                            | 4-36             |

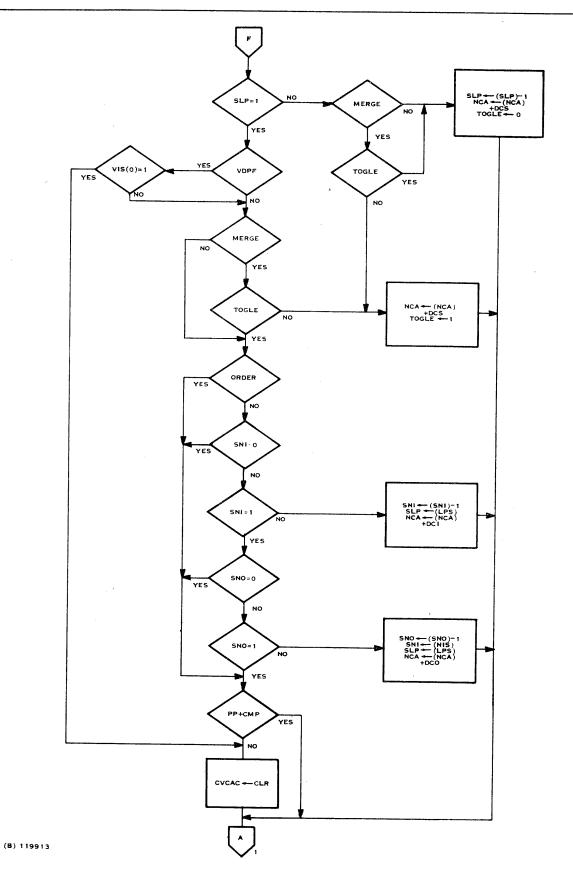

| 4.9.22    | Inner Loop Storage Pagister (NIS)                             | 4-36             |

| 4.9.23    | Inner Loop Storage Register (NIS)                             | 4-36             |

| 4.9.24    |                                                               | 4-36             |

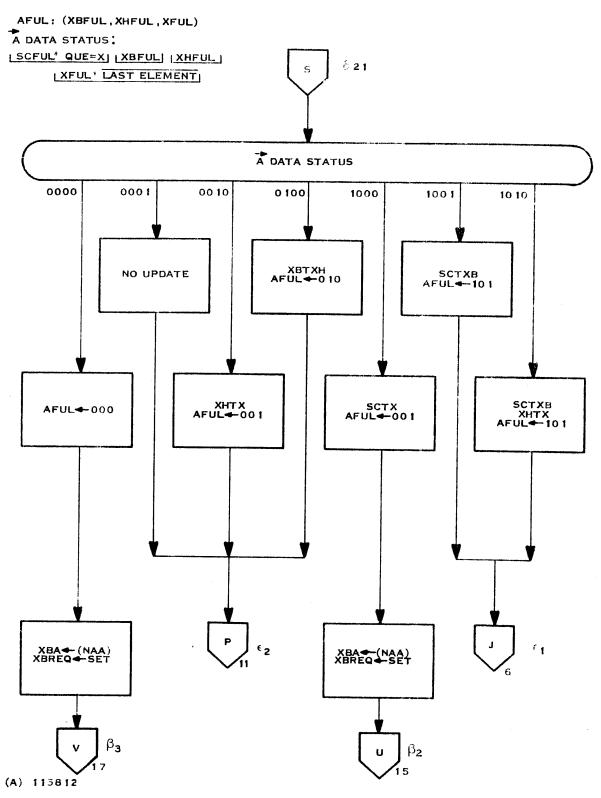

| 4.9.25    | Vector Initialization Control                                 |                  |

| 4.9.25.1  |                                                               | 4-36             |

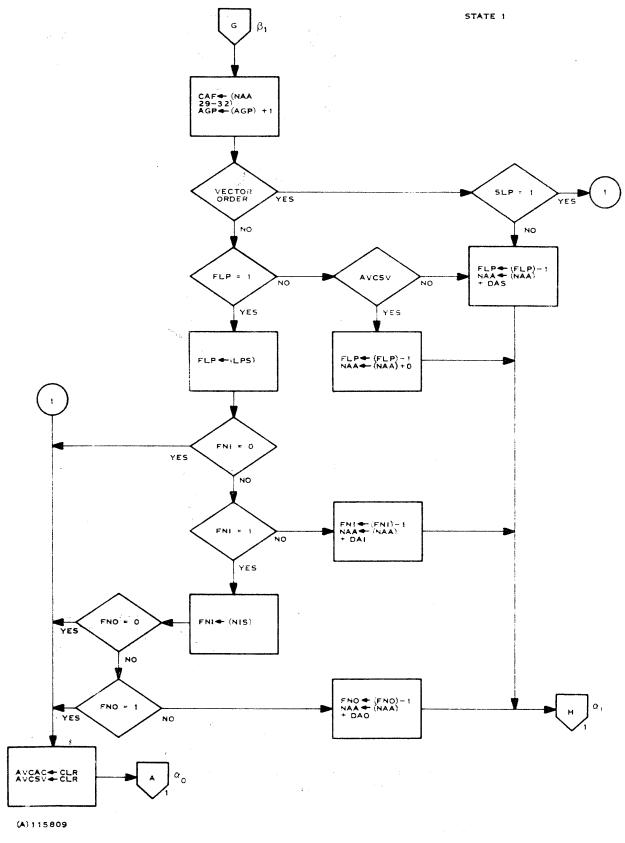

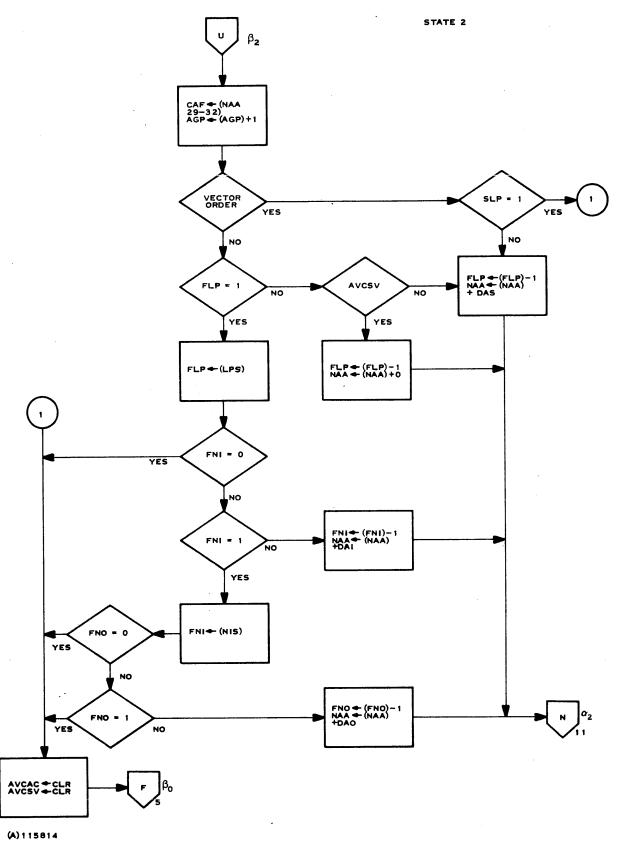

| 4.9.25.2  | Self Loop Counter (FLP)                                       | 4-36             |

| 4.9.25.3  | Inner Loop Counter (FNI)                                      | 4-37             |

| 4.9.25.4  | Outer Loop Counter (FNO)                                      | 4-37             |

| 4.9.26    |                                                               | 4-37             |

| 4.9.27    | MBU Unit Hard Core                                            | 4-38             |

| 4.9.27.1  | Vector Address Register (NAA/MRA)                             | 4-38             |

| 4.9.27.2  | Vector Address Register (NAA/NBA)                             | 4-38             |

| 4.9.27.3  |                                                               | 4-38             |

| 4.9.27.4  | Octet Request Register (SBA/YBA)  Circular Address File (CAF) | 4-38             |

| 4.9.28    |                                                               | 4-39             |

| 4.9.29    | Buffer Operand Address Register (XA/YA)                       | 4-39             |

| 4.9.29.1  | C Vector Address Register (NCA)                               | 4-39             |

| 1.7.47.1  | C Vector Address Register (NCA)                               | 4-40             |

| Paragraph | Title                                            | Page            |

|-----------|--------------------------------------------------|-----------------|

| 4.9.29.2  | Address Adder                                    | 4-40            |

| 4.9.29.3  | Scalar Storage Address Register (NSA)            | 4-40            |

| 4.9.29.4  | Resultant Storage Address Register (ZA)          | 4-40            |

| 4.9.29.5  | Half Phase Holding Register (ZAH)                |                 |

| 4.9.29.6  | Memory Storage Address Register (ZBA)            |                 |

| 4.9.29.7  | Halfword Modified Indicator Register (ZM)        |                 |

| 4.9.29.8  | Half Phase Holding Register (ZMH)                |                 |

| 4.9.29.9  | Memory Storage Modified Halfwords Register (ZBM) |                 |

| 4.9.29.10 | Storage Word Address Register (ZEA)              | 4-41            |

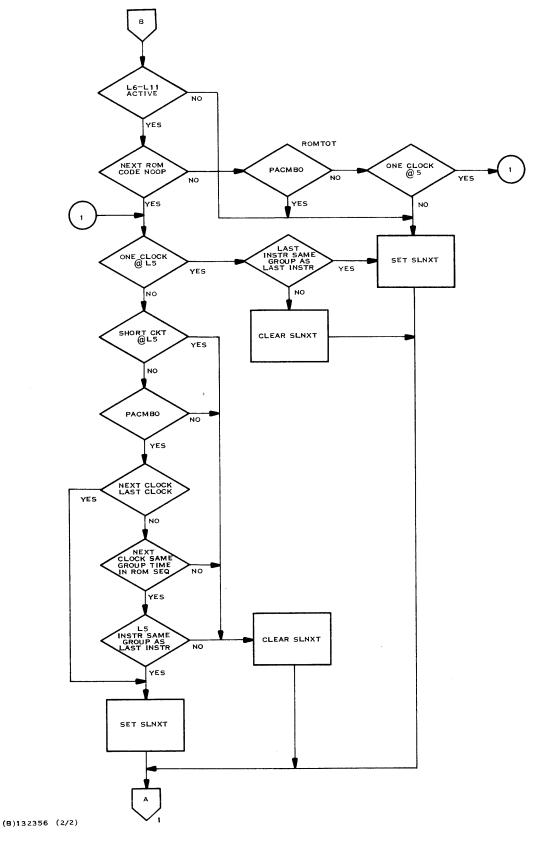

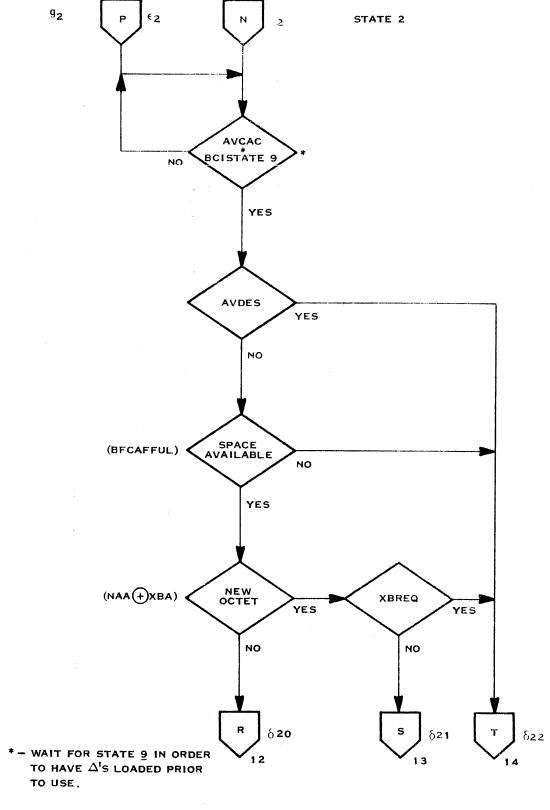

| 4.9.30    | Central Memory Requester (CMR)                   |                 |

| 4.9.30.1  | CMR Priority Gate                                | 4-41            |

| 4.9.30.2  | Memory Octet Address Register (OA)               |                 |

| 4.9.30.3  | Asynchronous Address Register (AA)               | 4-41            |

| 4.9.30.4  | Halfword Bits Check and Merge                    | 4-42            |

| 4.9.30.5  | Zone Control Bit Registers (ZCB/AZC)             |                 |

| 4.9.30.6  | CMR Control                                      | 4-42            |

| 4.9.30.7  | Cue File                                         | 4-42            |

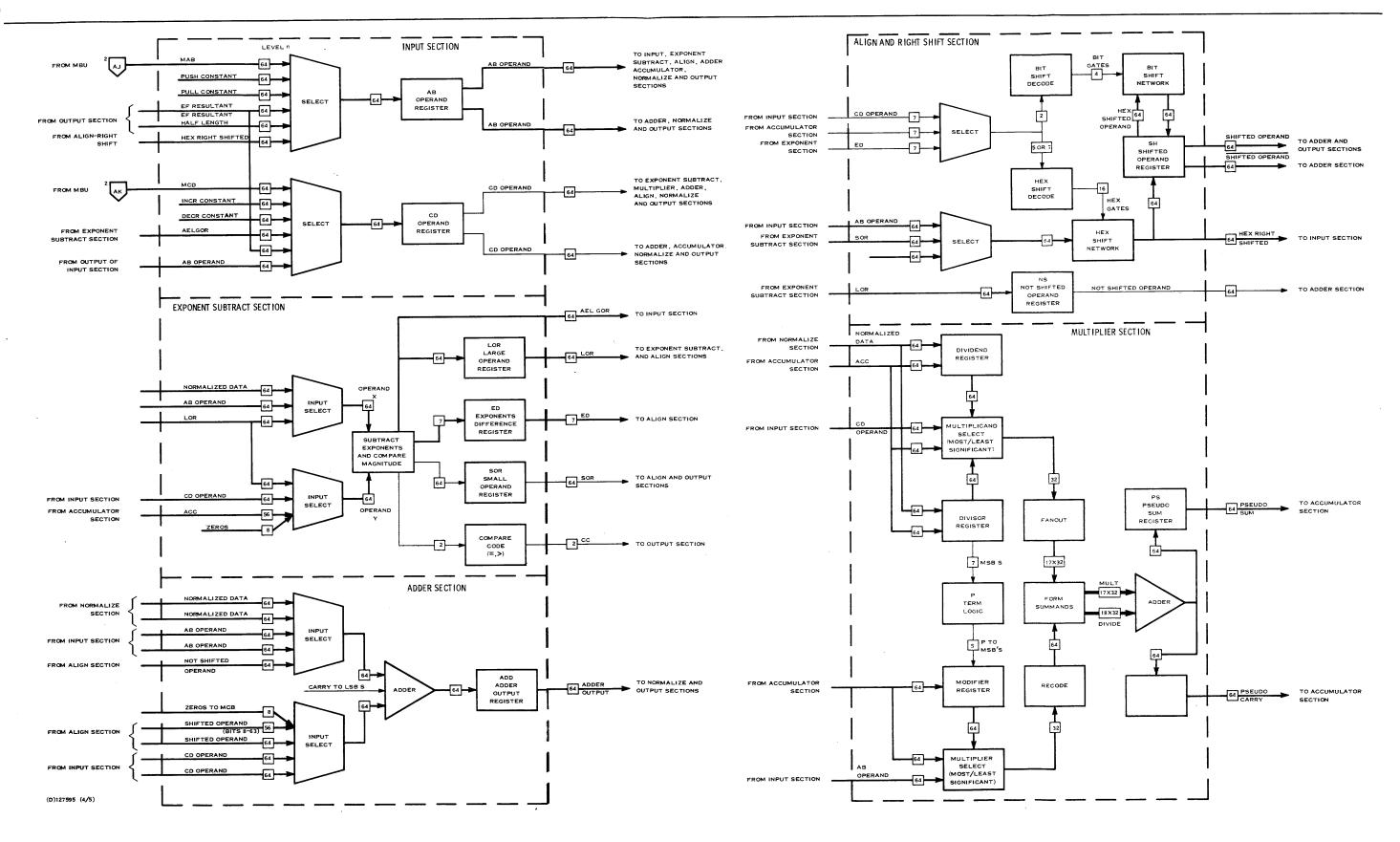

| 4.10      | AU Input                                         | 4-43            |

| 4.11      | Exponent Subtract                                | , <b>.</b> 4-43 |

| 4.11.1    | Input Select                                     | 4-43            |

| 4.11.2    | Subtract Exponents and Compare Magnitude         |                 |

| 4.11.3    | LOR Register                                     | 4-45            |

| 4.11.4    | SOR Register                                     |                 |

| 4.11.5    | ED Register                                      | 4-45            |

| 4.11.6    | Compare Code                                     | 4-45            |

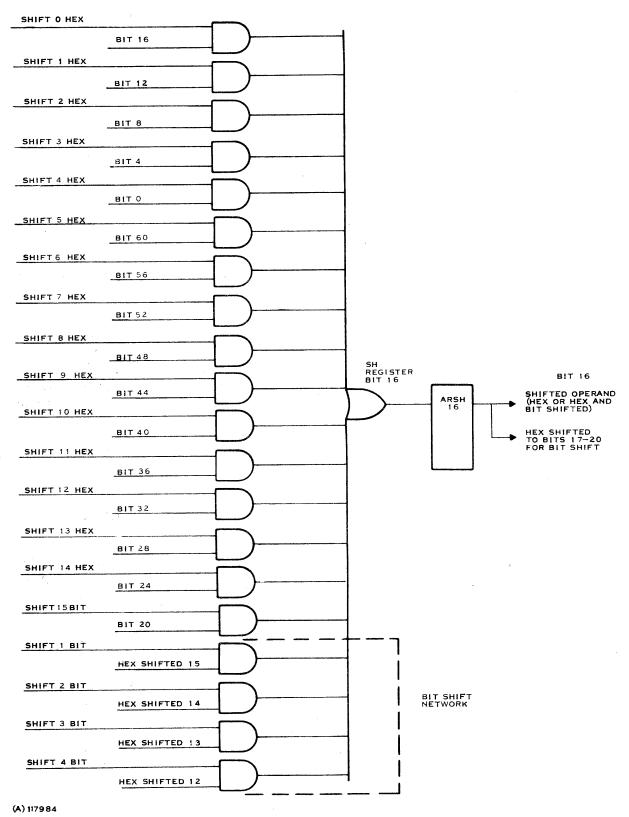

| 4.12      | Align and Right Shift                            | 4-45            |

| 4.12.1    | Select                                           | 4-45            |

| 4.12.2    | Hex Shift Decode                                 | 4-45            |

| 4.12.3    | Bit Shift Decode                                 | 4-45            |

| 4.12.4    | Shift Sequence                                   | 4-46            |

| 4.12.5    | Not Shifted Register (NS)                        | 4-46            |

| 4.13      | Adder Section                                    | 4-46            |

| 4.13.1    | Input Select                                     | 4-46            |

| 4.13.2    | Adder                                            | 4-46            |

| 4.13.3    | Adder Output Register (ADD)                      | 4-46            |

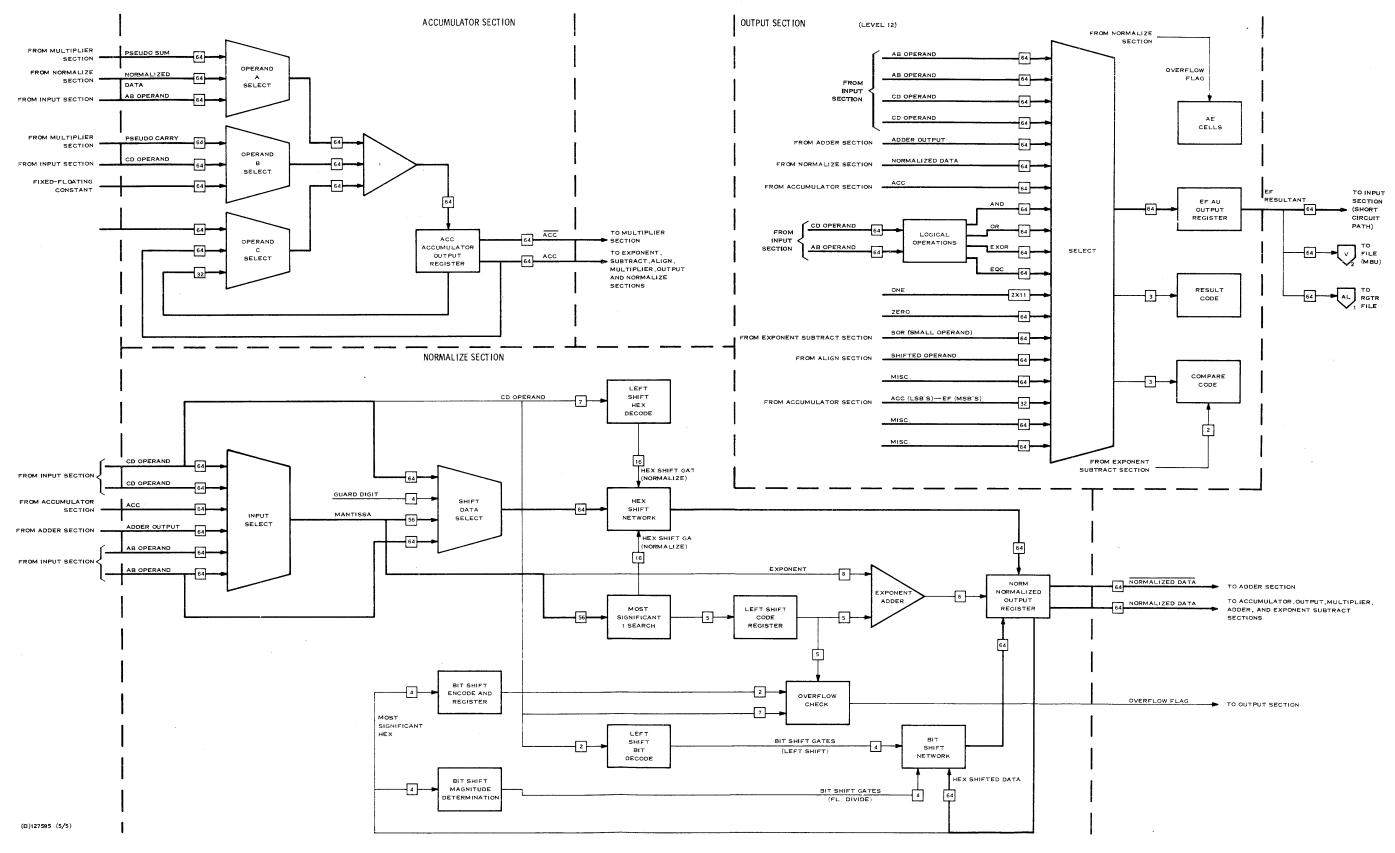

| 4.14      | Accumulator                                      | 4-46            |

| 4.14.1    | Operand Select                                   | 4-48            |

| 4.14.2    | Adder                                            | 448             |

| 4.14.3    | Accumulator Output Register (ACC)                | 4-48            |

| 4.15      | Output                                           | 4-48            |

| 4.15.1    | Logical Operations                               | 4-48            |

| 4.15.2    | Output Select                                    | 4-48            |

| 4.15.3    | EF Register                                      | 4-48            |

| 4.15.5    | Result Code                                      |                 |

| 4.15.6    | Arithmetic Exception Cells (AE)                  |                 |

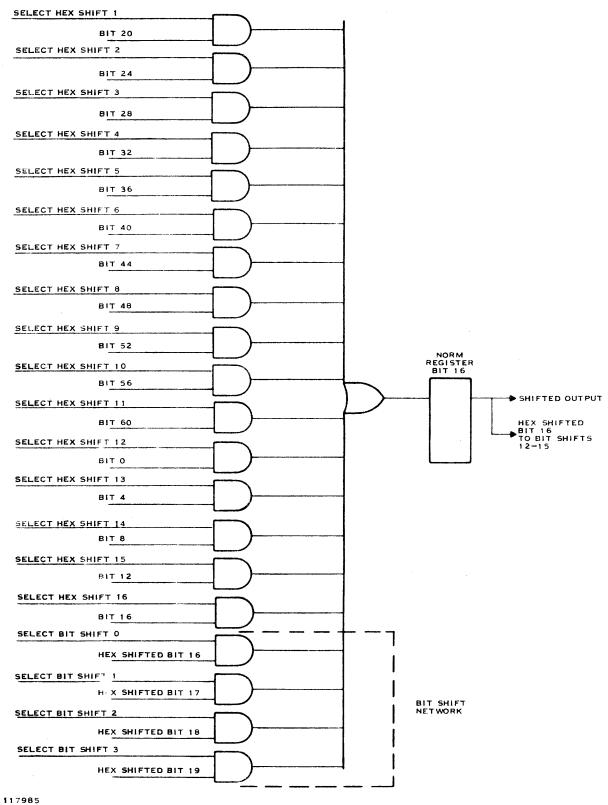

| 4.16      | Normalize Section                                |                 |

| 4.16.1    | Input Select                                     |                 |

| 4.16.2    | Most Significant 1 Search                        |                 |

| 4.16.3    | Left Shift Code Register                         |                 |

| 4.16.4    | Exponent Adder                                   | 4-50            |

| Paragraph | Title                                  |     |         |     |   | F     | Page |

|-----------|----------------------------------------|-----|---------|-----|---|-------|------|

| 4.16.5    | Left Shift Hex Decode                  |     | <br>    |     |   | 4     | -50  |

| 4.16.6    | Hex Shift Network/Bit Shift Network    |     | <br>    |     |   | 4     | -50  |

| 4.16.7    | Normalized Output Register (NORM)      |     | <br>    |     |   | 4     | -50  |

| 4.16.8    | Left Shift Bit Decode                  |     | <br>    |     |   | 4     | -52  |

| 4.16.9    | Bit Shift Magnitude Determination      |     | <br>    |     |   | 4     | -52  |

| 4.16.10   | Bit Shift Encode and Register          |     | <br>    |     |   | 4     | -52  |

| 4.16.11   | Overflow Check                         |     | <br>    |     |   | 4     | -52  |

| 4.17      | Multiplier Section                     |     | <br>    |     |   | 4     | -52  |

| 4.17.1    | Dividend Register                      |     | <br>    |     |   | 4     | -52  |

| 4.17.2    | Divisor Register                       |     | <br>    |     |   | 4     | -53  |

| 4.17.3    | P-Term Logic                           |     | <br>    |     |   | 4     | -53  |

| 4.17.5    | Multiplicand/Multiplier Select         |     | <br>    |     |   | 4     | -53  |

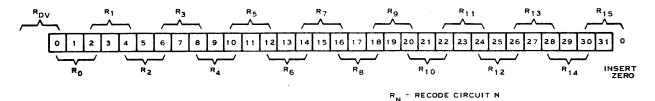

| 4.17.6    | Recode                                 |     | <br>    |     |   | 4-    | -53  |

| 4.17.7    | Fanout                                 |     | <br>    |     |   | 4-    | -54  |

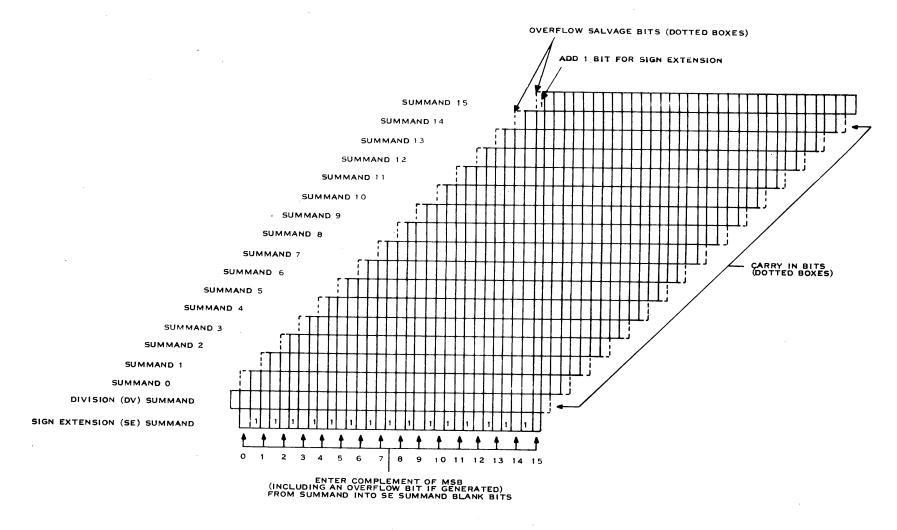

| 4.17.8    | Form Summands                          |     | <br>    |     |   | 4     | -54  |

| 4.17.8.1  | Overflow Salvage                       |     | <br>    |     |   | 4-    | -54  |

| 4.17.8.2  | Sign Extension Summand                 |     |         |     |   |       |      |

| 4.17.8.3  | Division Summand                       |     |         |     |   |       |      |

| 4.17.8.4  | Two's Complement                       |     |         |     |   |       |      |

| 4.17.9    | Adder Tree                             |     |         |     |   |       |      |

| 4.17.10   | Pseudo-Sum (PS) Register               |     |         |     |   |       |      |

| 4.17.11   | Pseudo-Carry (PC) Register             |     |         |     |   |       |      |

| 4.18      | Multiplication Theory                  |     |         |     |   |       |      |

| 4.18.1    | Algorithm Derivation                   |     |         |     |   |       |      |

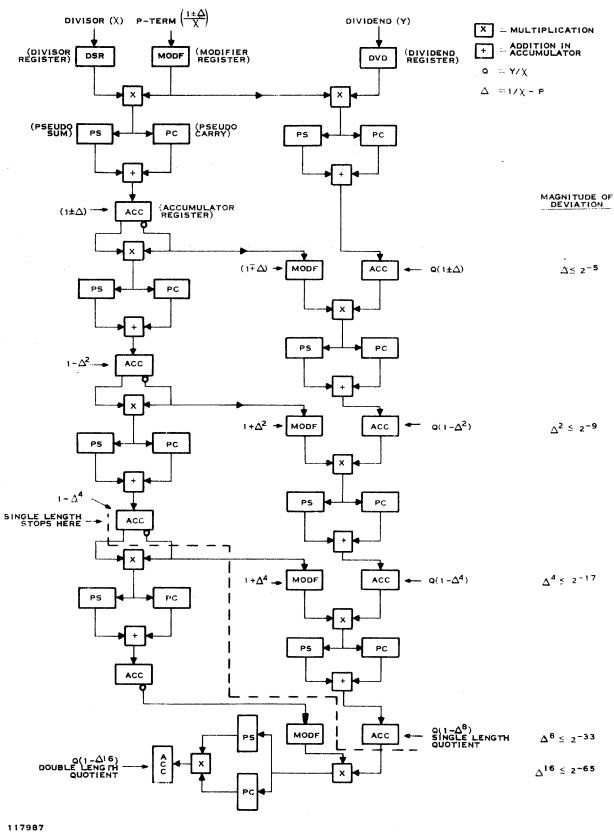

| 4.19      | AU Division Theory                     |     |         |     |   |       |      |

| 4.20      | Sign Extension Algorithm               |     |         |     |   |       |      |

| 4.20.1    | Two's Complement Formation             |     |         |     |   |       |      |

| 4.20.2    | Algorithm Derivation                   |     |         |     |   |       |      |

| 4.21      | AU Unit Hard Core                      |     |         |     |   |       |      |

| 4.22      | Controller Descriptions and Flowcharts |     |         |     |   |       |      |

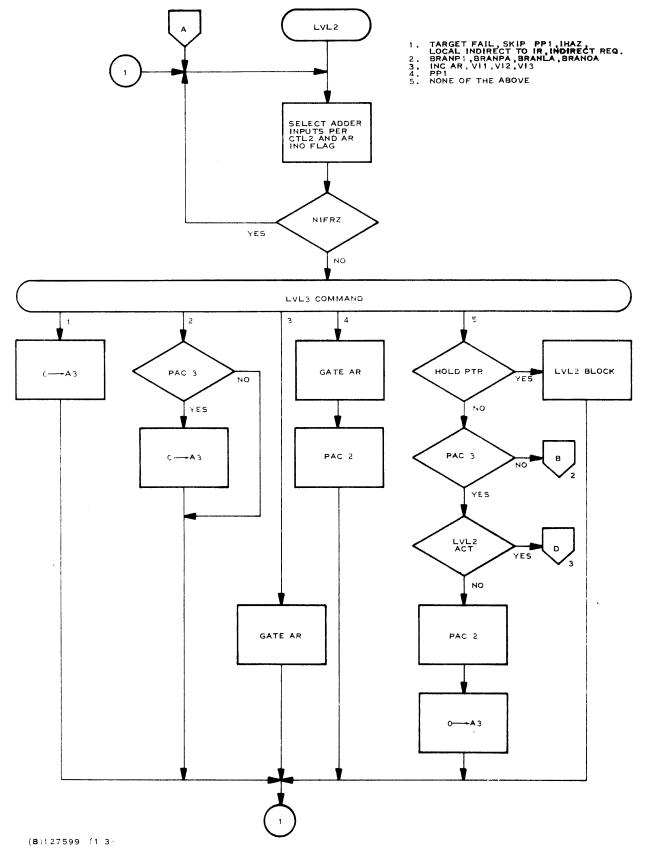

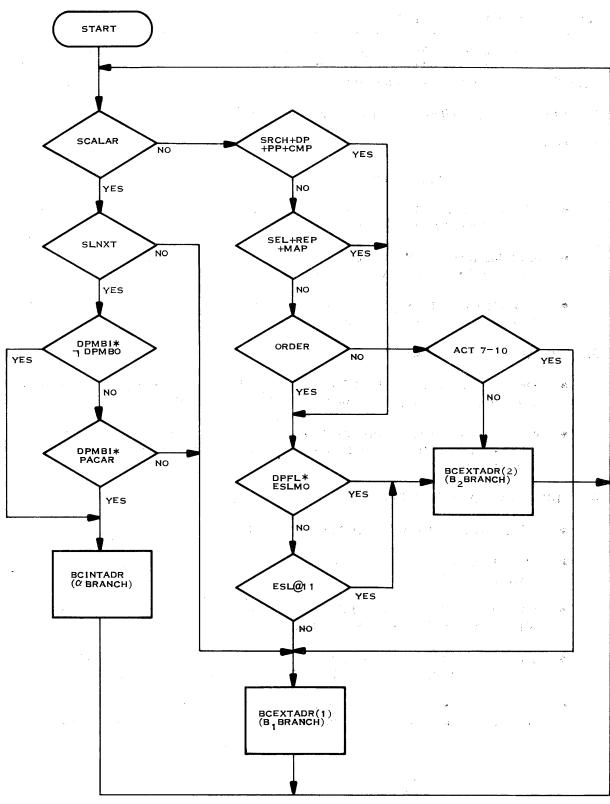

| 4.22.1    | Instruction Flow                       |     |         |     |   |       |      |

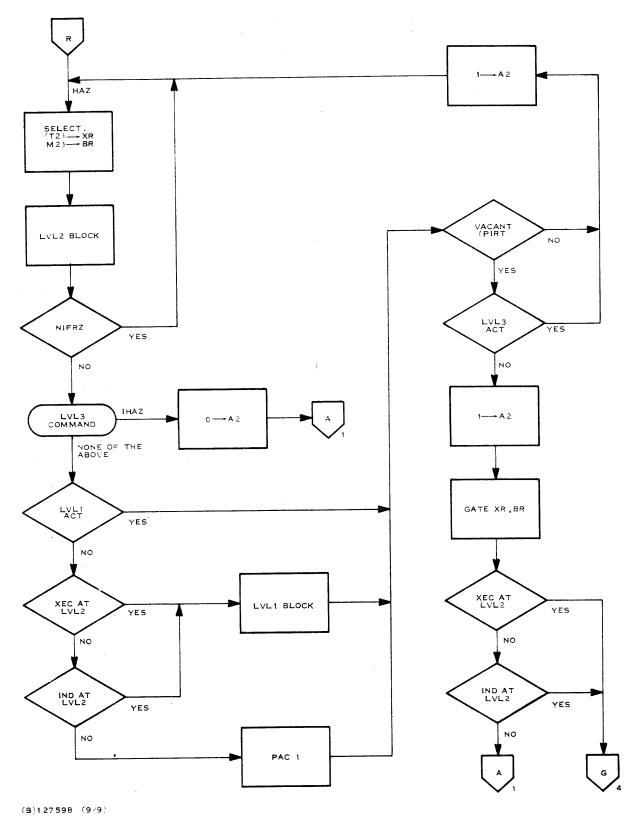

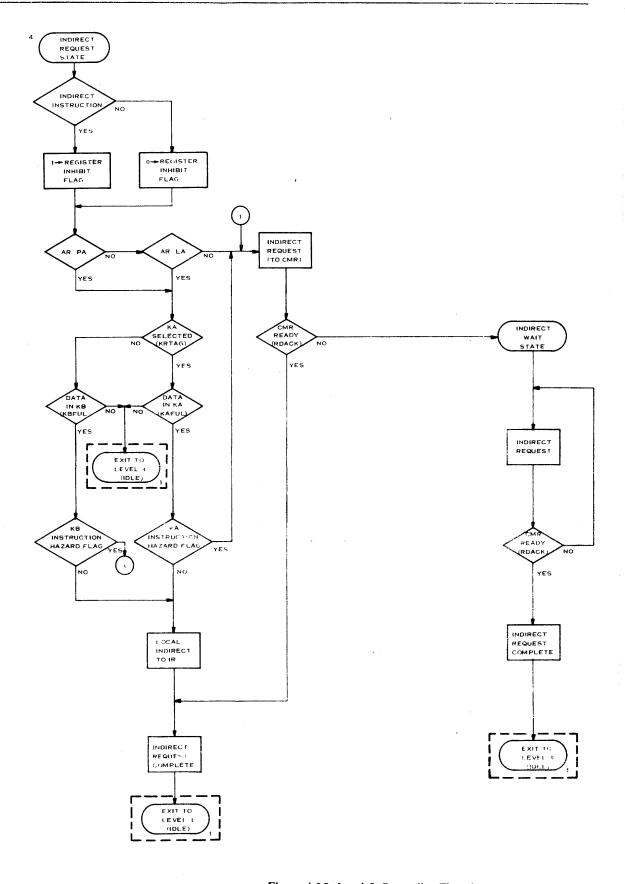

| 4.22.1.1  | Indirect Addressing                    |     |         |     |   |       |      |

| 4.22.1.2  | Execute Instruction                    |     |         |     |   |       |      |

| 4.22.1.3  | Skips                                  |     |         |     |   |       |      |

| 4.22.1.4  | Branches                               |     |         |     |   |       |      |

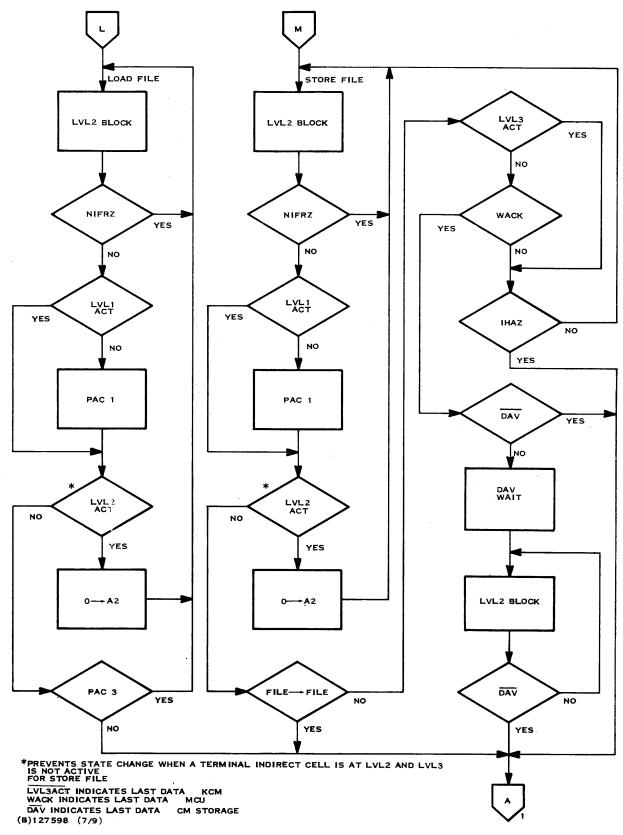

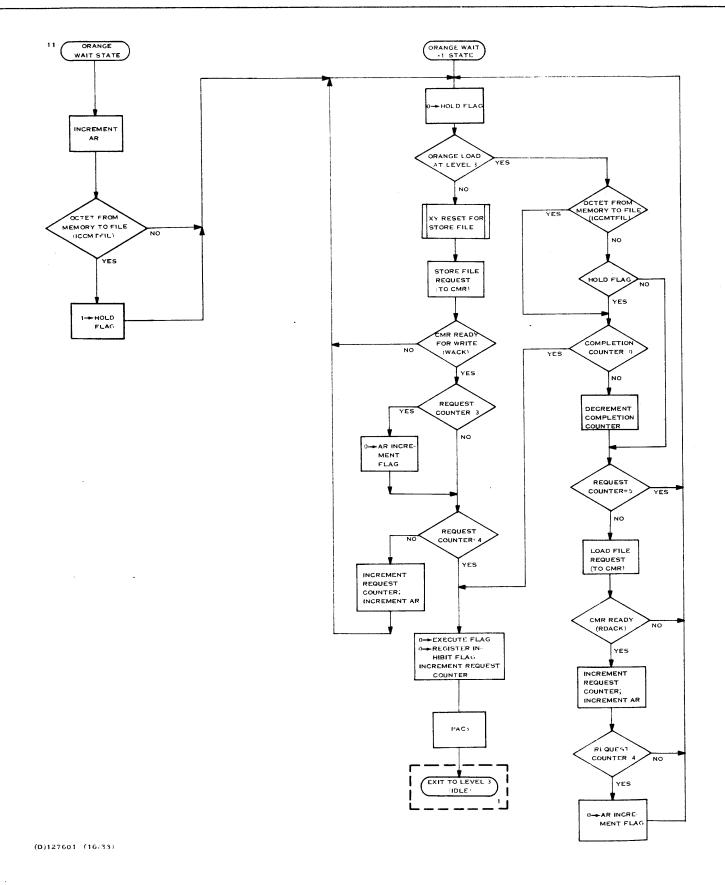

| 4.22.1.5  | Store File and Load File Instructions  |     |         |     |   |       |      |

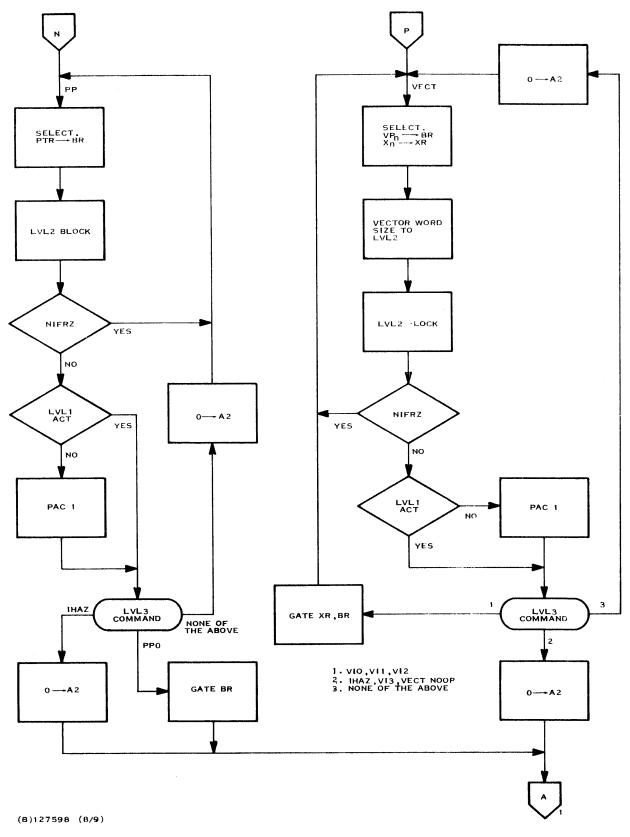

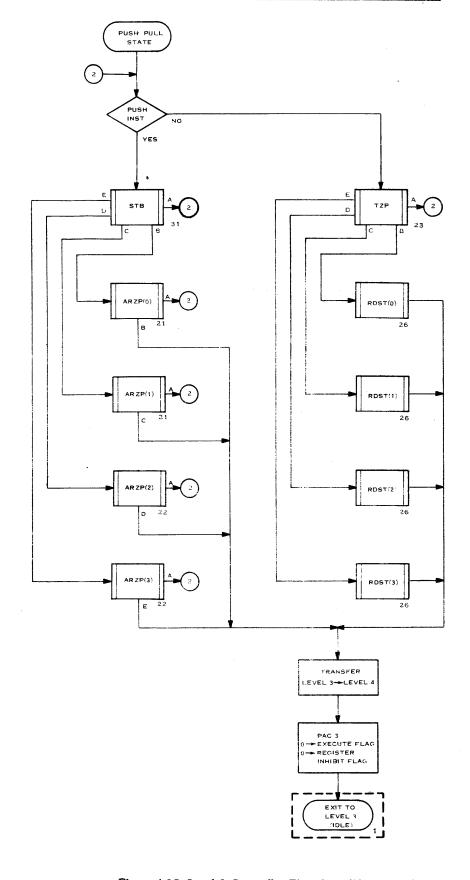

| 4.22.1.6  | Push, Pull Instructions                |     |         |     |   |       |      |

| 4.23      | Level 5 Scalar Input Controller        |     |         |     |   |       |      |

| 4.23.1    | Input Stage Not Active (NOT MBIAC)     |     |         |     |   |       |      |

| 4.23.1.1  | Load Immediate Operand                 |     |         |     |   |       |      |

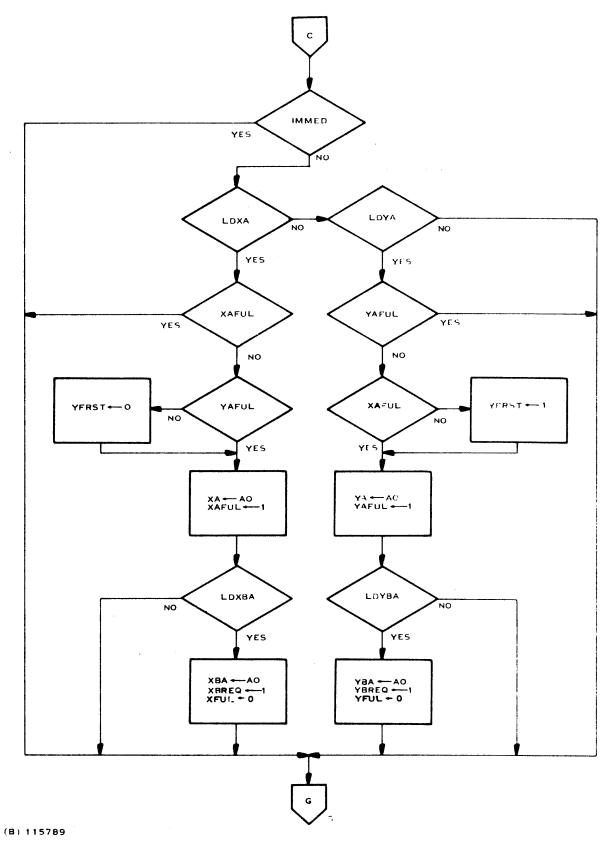

| 4.23.1.2  | Load From X Buffer (LDXA)              |     |         |     |   |       |      |

| 4.23.1.3  | Load From Y Buffer (LDYA)              |     |         |     |   |       |      |

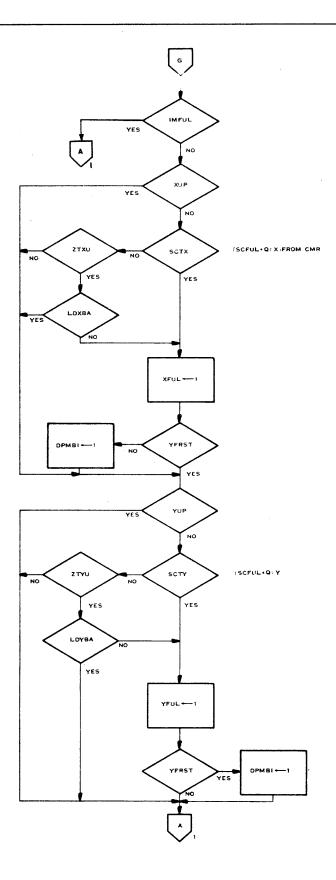

| 4.23.2    | Input Stage Active (MBIAC)             |     | <br>    |     |   | . 4-1 | 80   |

| 4.23.2.1  | Transfer OK                            |     |         |     |   |       |      |

| 4.23.2.2  | Transfer Not OK                        |     |         |     |   |       |      |

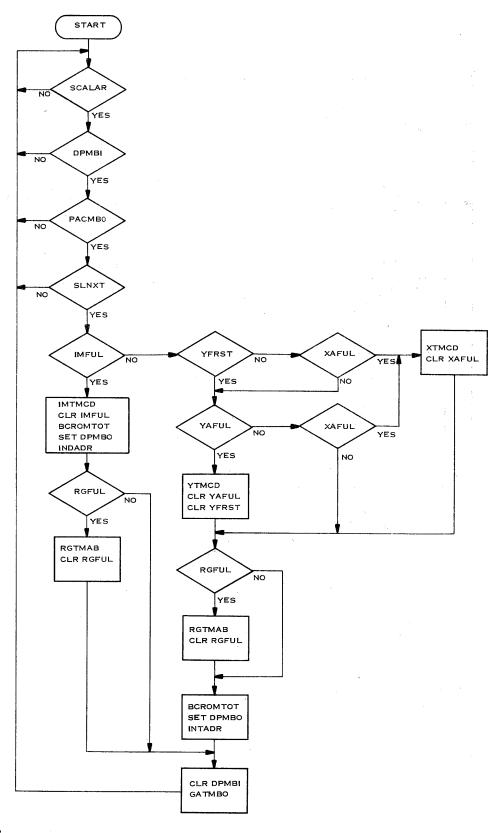

| 4.24      | Level 6 Controller - Scalar Mode       |     |         |     |   |       |      |

| 4.25      | Level 6 Controller - Vector Mode       |     |         |     |   |       |      |

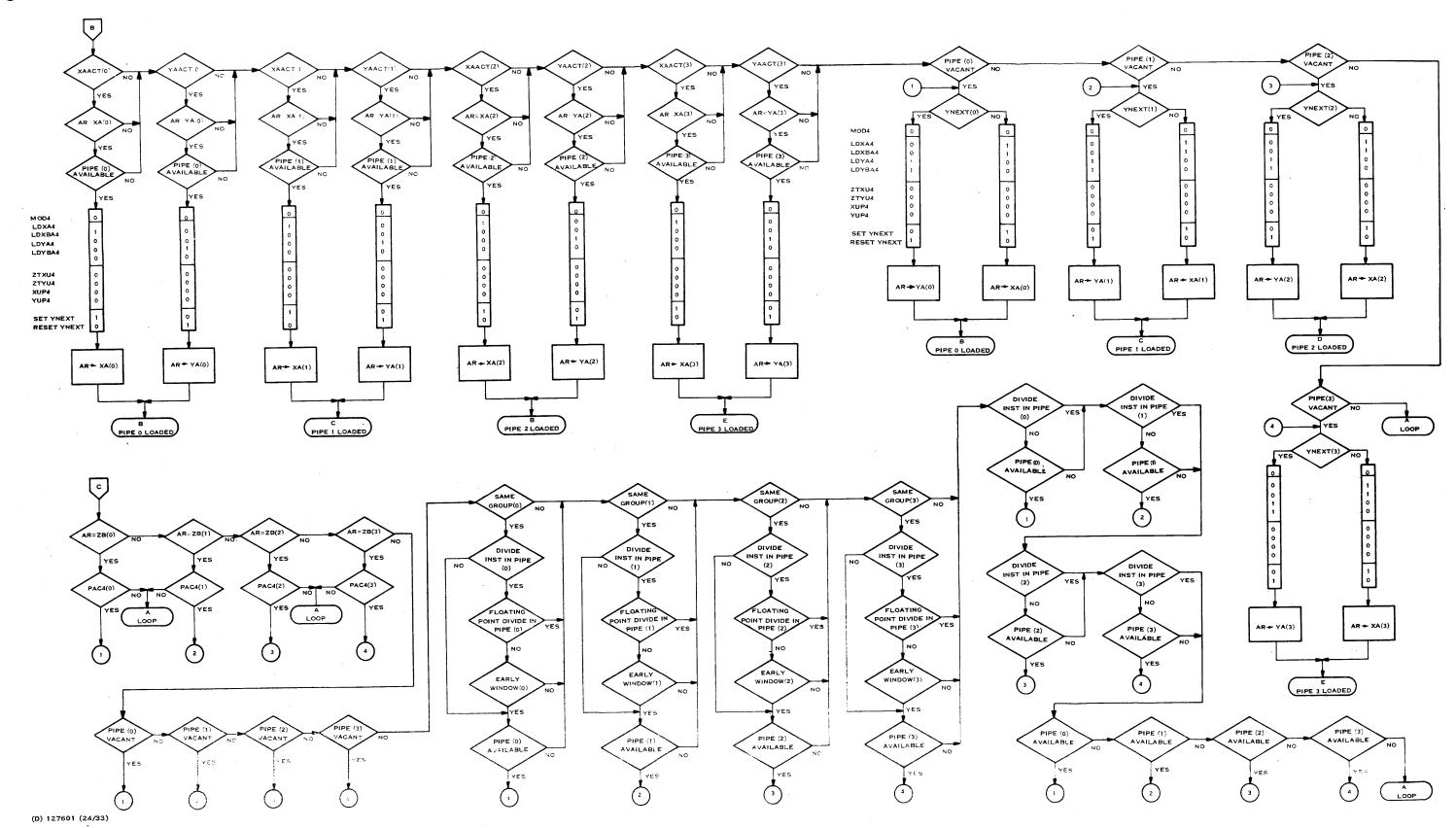

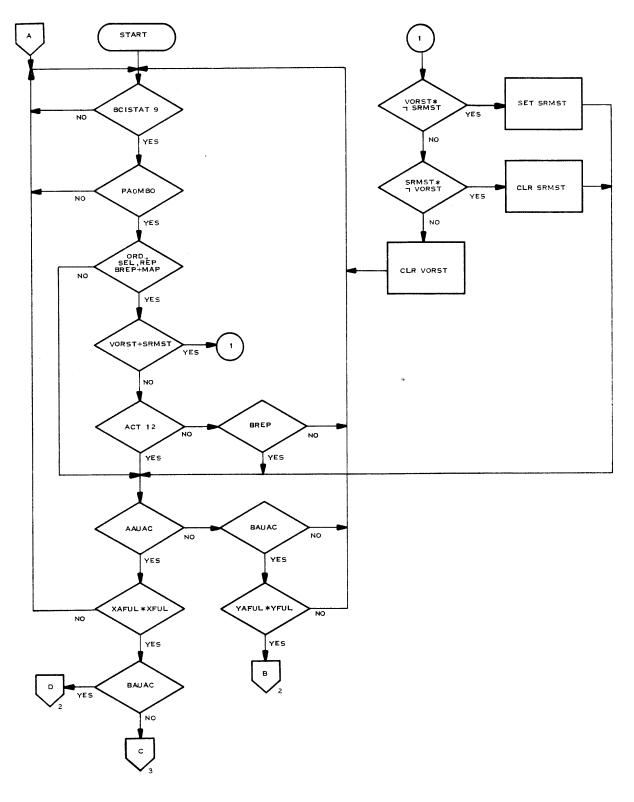

| 4.26      | Select Next Controller                 |     |         |     |   |       |      |

| 4.27      | Central Memory Requester (CMR)         |     |         |     |   |       |      |

| 4.28      | Other Control Circuits                 | - • | <br>. • | . • | - | 4-2   |      |

## LIST OF ILLUSTRATIONS

| Figure                    | Title                                                         | Page  |

|---------------------------|---------------------------------------------------------------|-------|

| 1-1                       | ASC Simplified Block Diagram                                  | 1-2   |

| 1-2                       | 4XCP Unit Structure                                           |       |

| 1-3                       | Central Processor Block Diagram                               |       |

| 1-4                       | Scalar Op Code Map                                            |       |

| 1-5                       | Vector Op Code Map                                            |       |

| 1-6                       | ASC Instruction Word Format                                   |       |

| 1-7                       | T-Field Subdivision                                           |       |

| 1-8                       | 32-Bit, Fixed Point Data Word Format                          |       |

| 1-10                      | 32-Bit, Floating Point Data Word Format                       |       |

| 1-10                      | 64-Bit, Floating Point Data Word Format                       |       |

| 1-11                      | Typical ASC Central Processor Four-Pipe Configuration         |       |

| 1-12                      |                                                               |       |

|                           | Schematic Representation of CP Cooling System                 |       |

| 1-14                      | ECL Circuits                                                  |       |

| 4-1                       | Central Processor Block Diagram                               |       |

| 4-2                       | Vector Parameter File Format                                  | 4-16  |

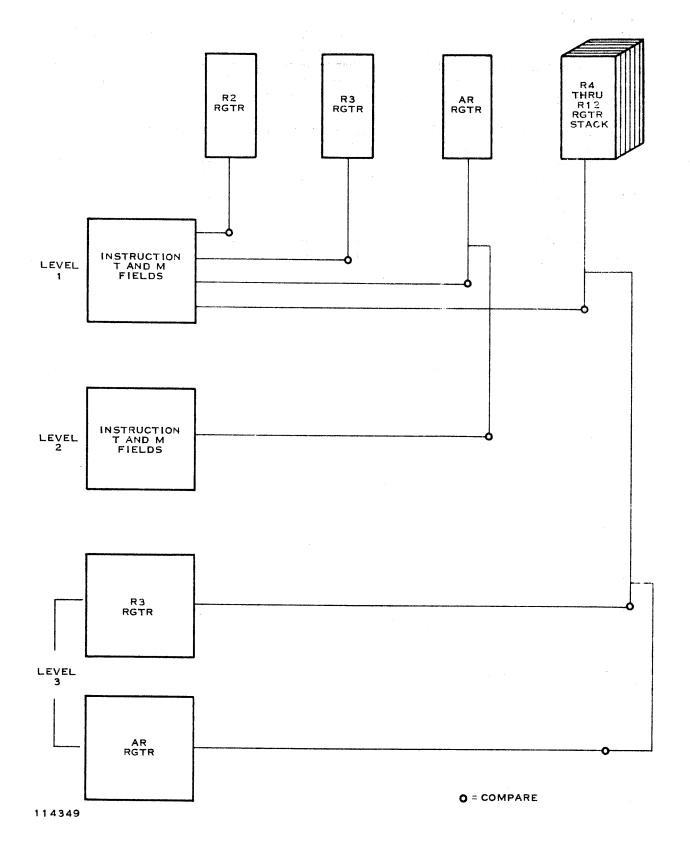

| 4-3                       | Branch, Indirect, Execute Comparisons                         | 4-20  |

| 4-4                       | Register Hazard Comparisons                                   | 4-22  |

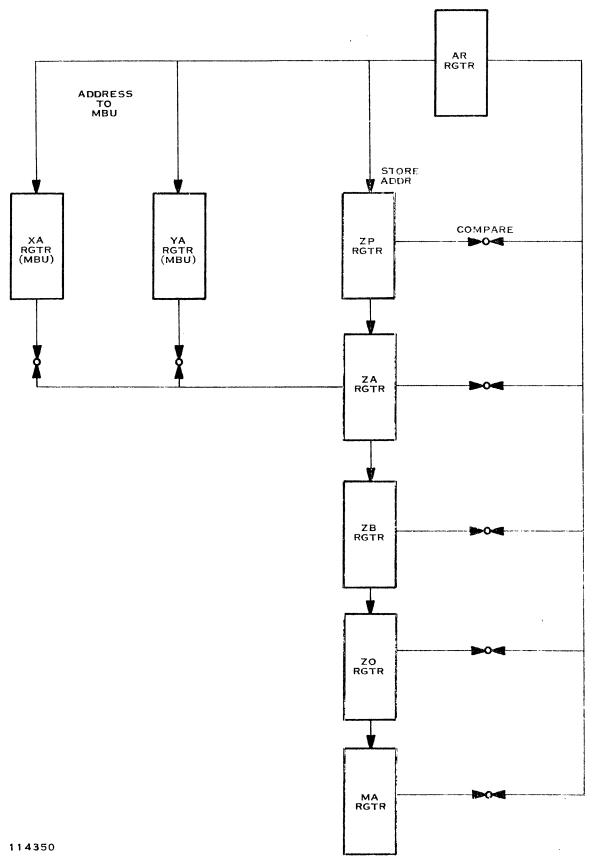

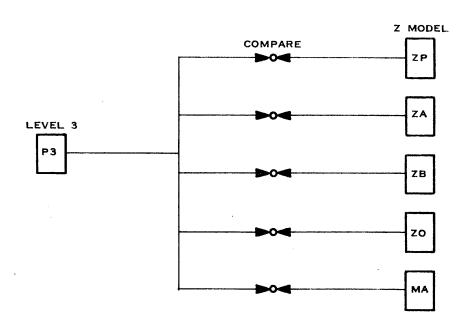

| 4-5                       | Operand Hazard Comparisons                                    |       |

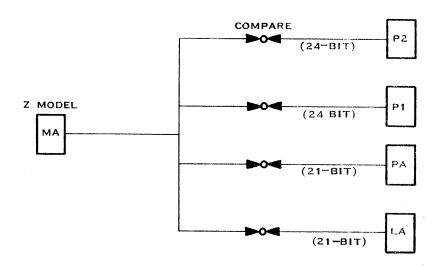

| 4-6                       | Near Range Instruction Hazard Comparisons                     |       |

| 4-7                       | Far Range Instruction Hazard Comparisons                      |       |

| 4-8                       | Common Command Register and Transfer Bit                      |       |

| 4-9                       | CP Control Register                                           |       |

| 4-10                      | CP Response Byte                                              |       |

| 4-11                      | CP Condition Byte                                             |       |

| 4-12                      | Typical CAF Word                                              |       |

| 4-13                      | Exponent Subtract and Compare Logic Flowchart                 |       |

| 4-14                      | Simplified Right Shift Netowrk (Bit 16 of Operand)            |       |

| 4-15                      | Simplified Left Shift (Normalize) Network (Bit 16 of Operand) |       |

| 4-16                      | Multiplier Word Recode Bit Assignments                        |       |

| 4-17                      | Summand Array                                                 |       |

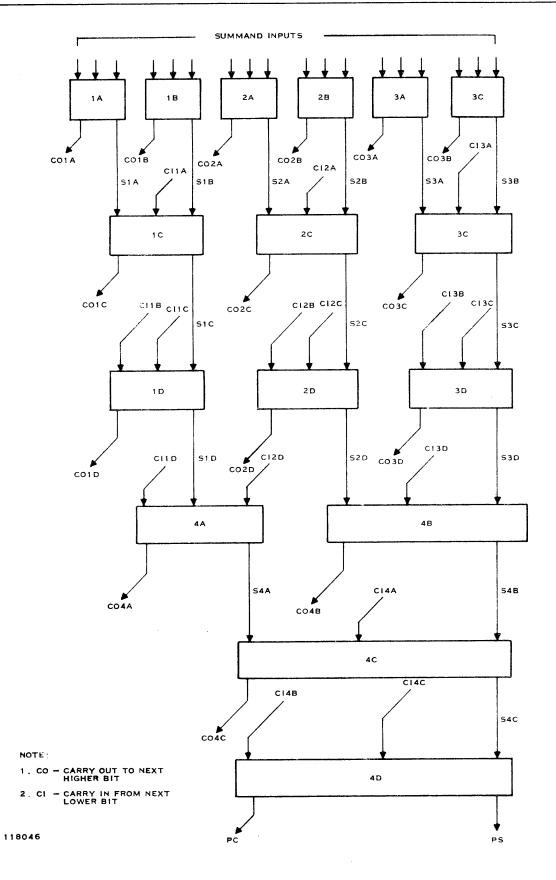

| 4-18                      | Simplified Adder Tree Block Diagram                           |       |

| <b>4-</b> 10 <b>4-</b> 19 | CP Hardware Utilization-Division Process                      |       |

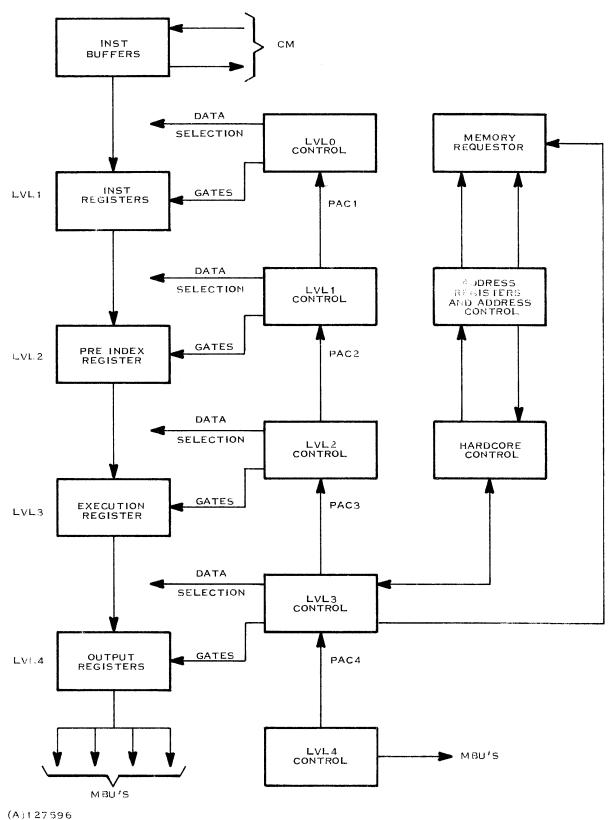

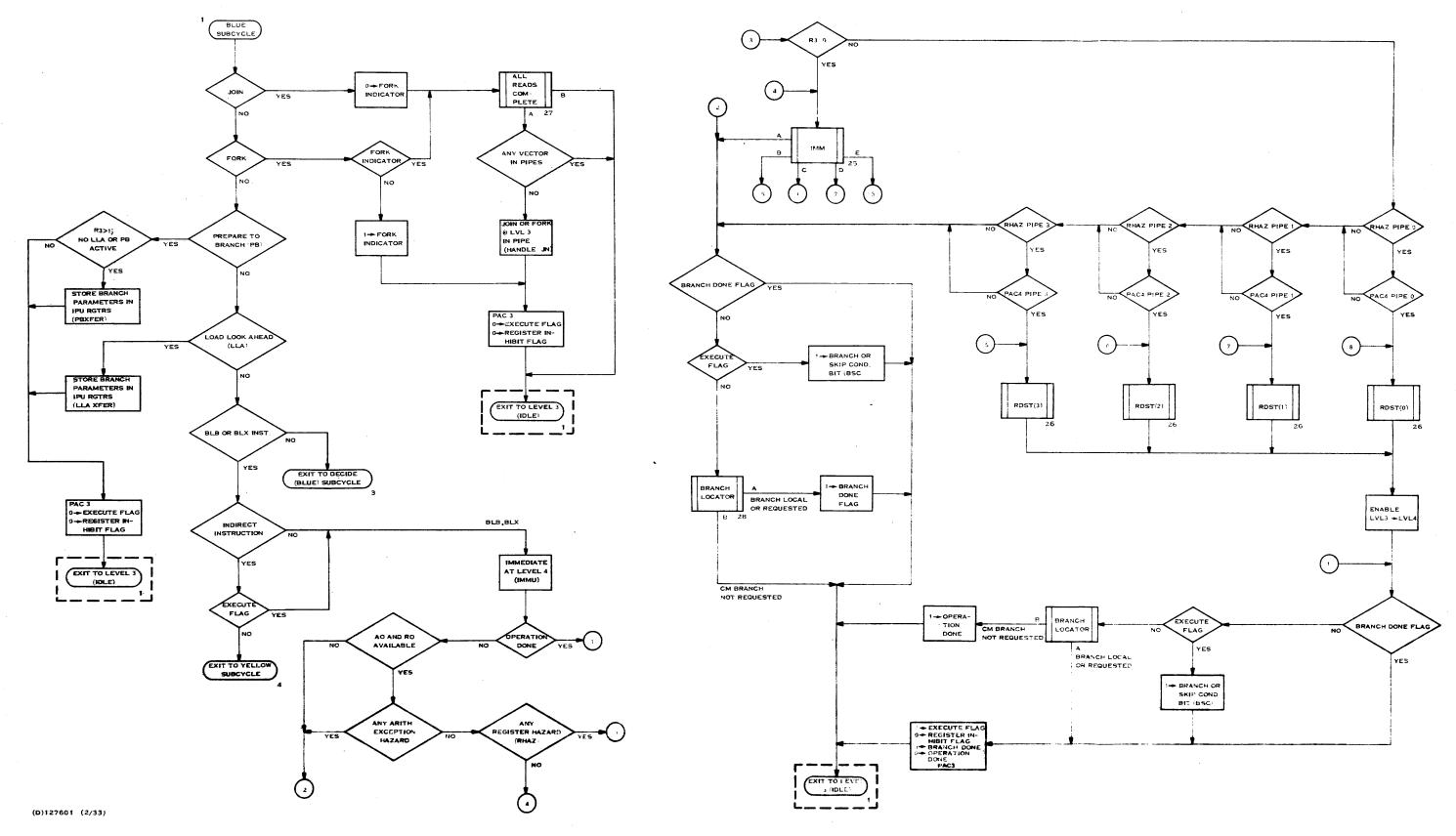

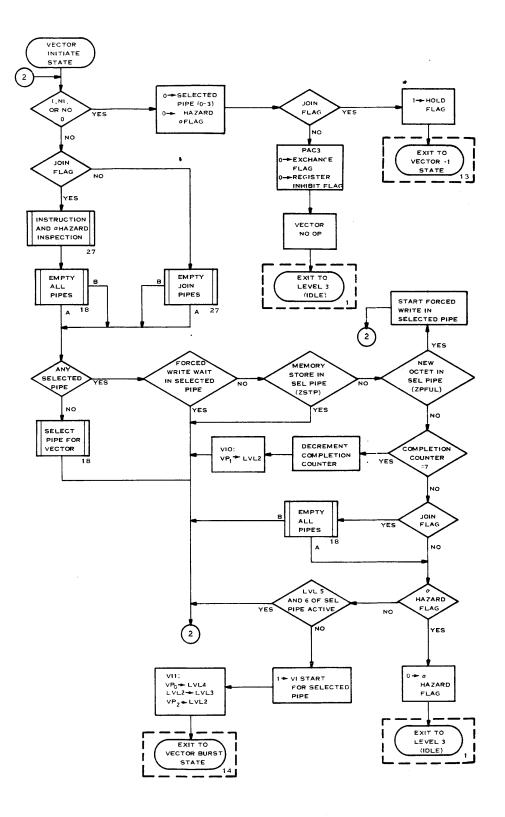

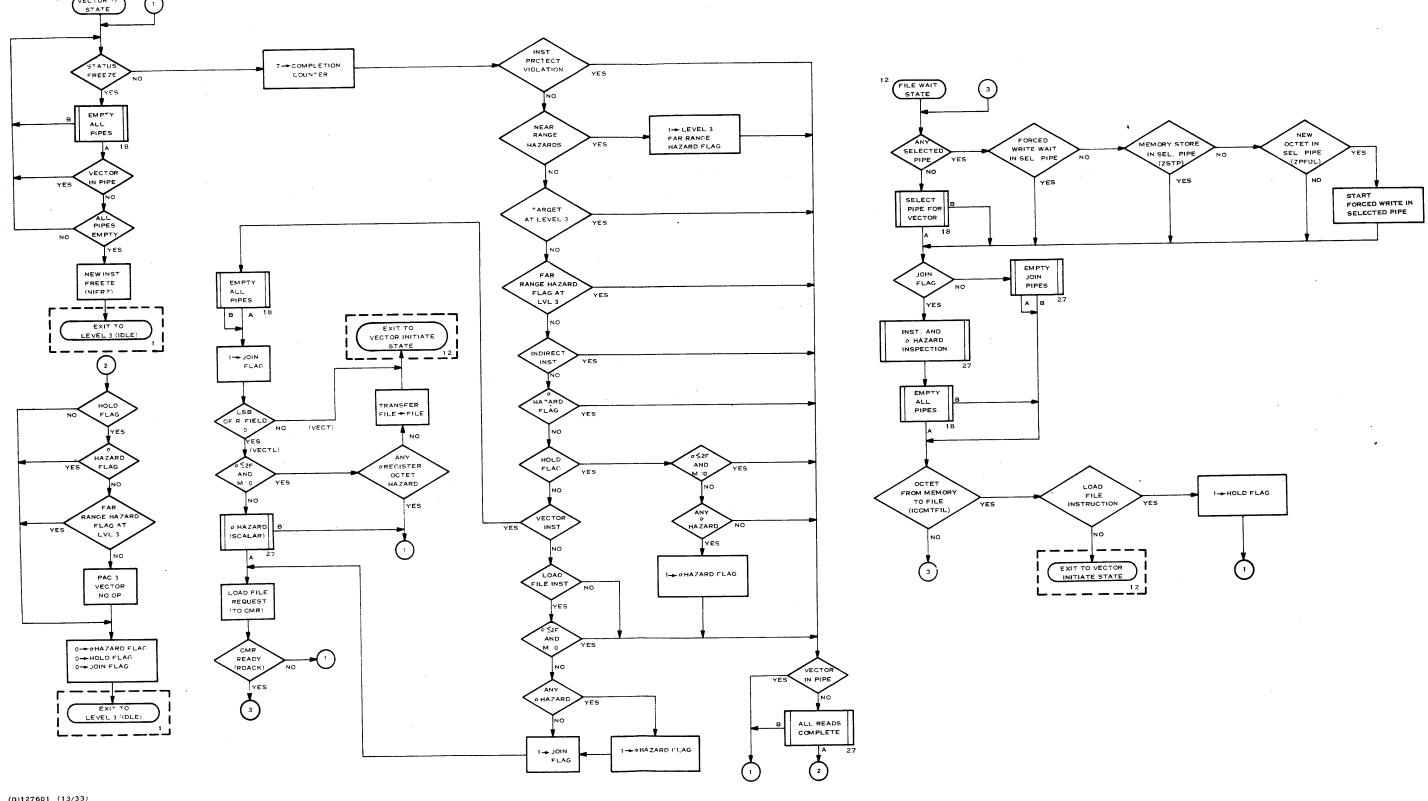

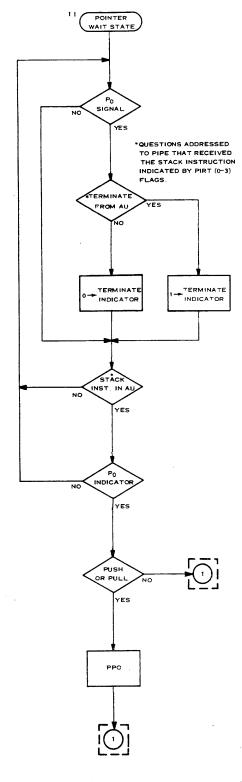

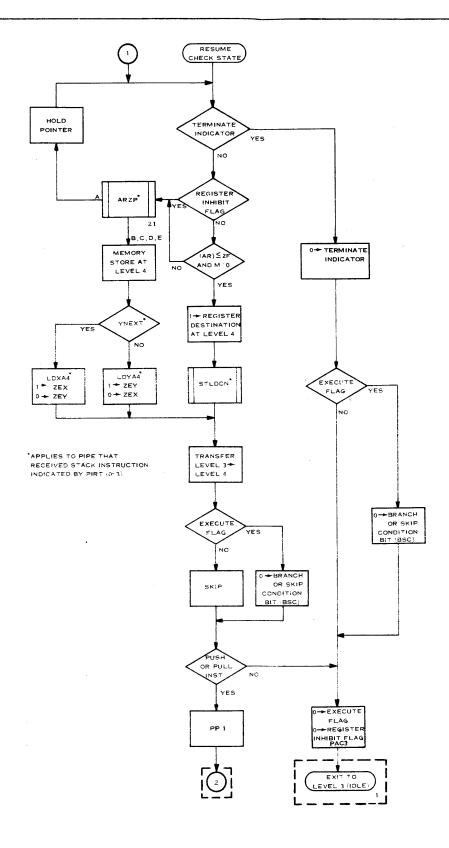

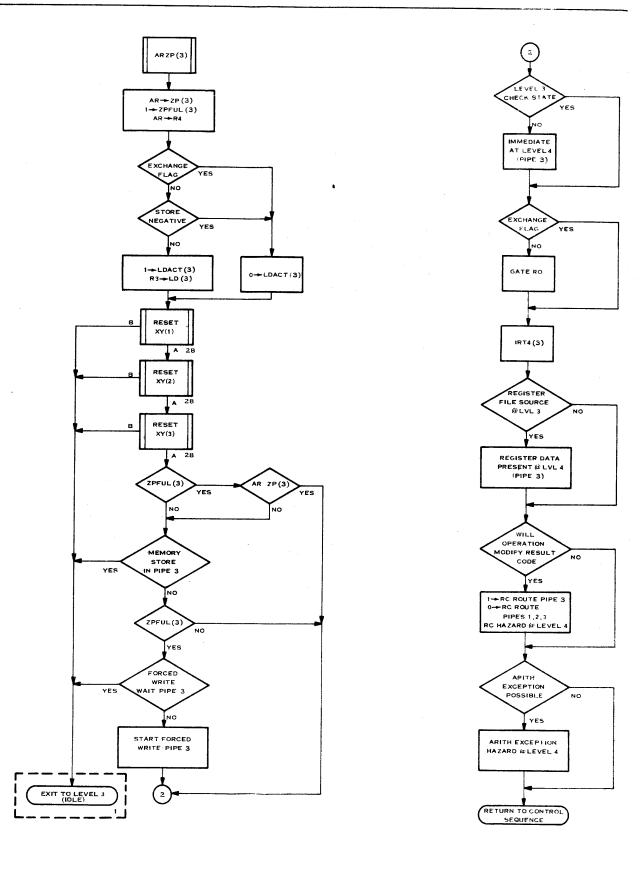

| 4-19                      | IPU Control                                                   |       |

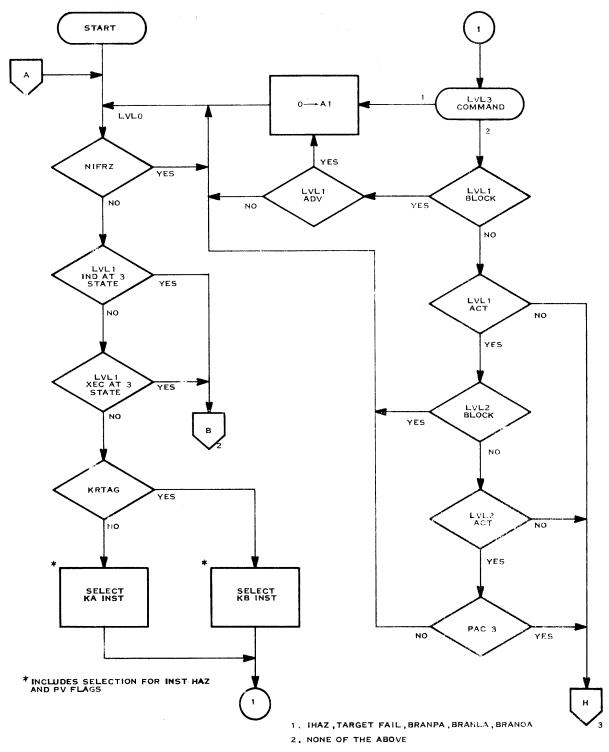

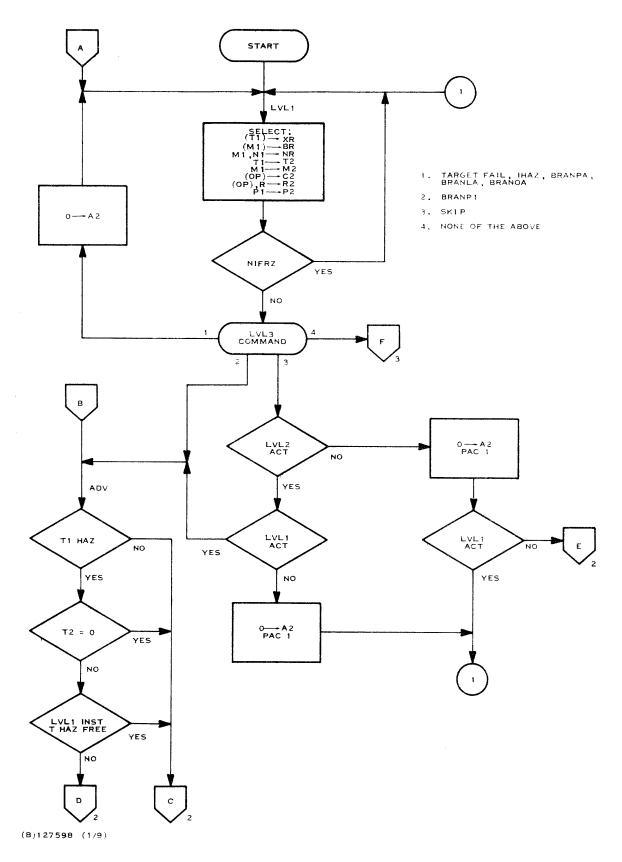

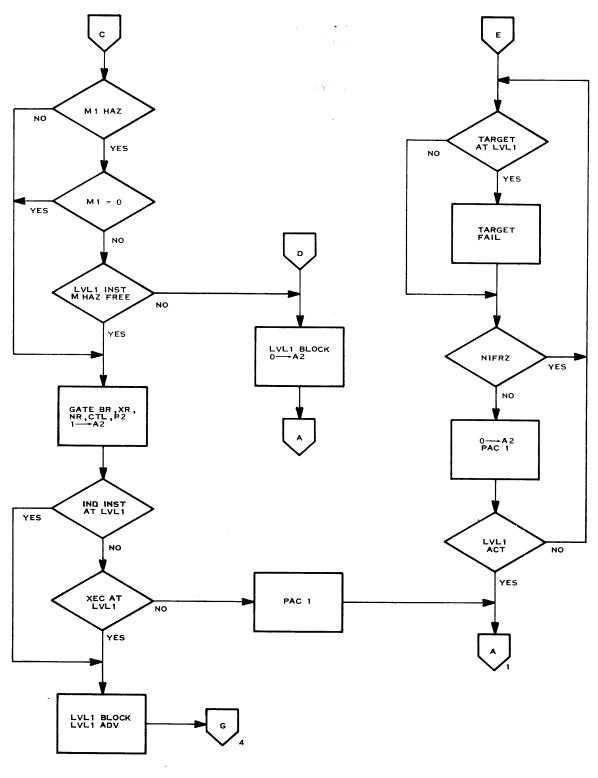

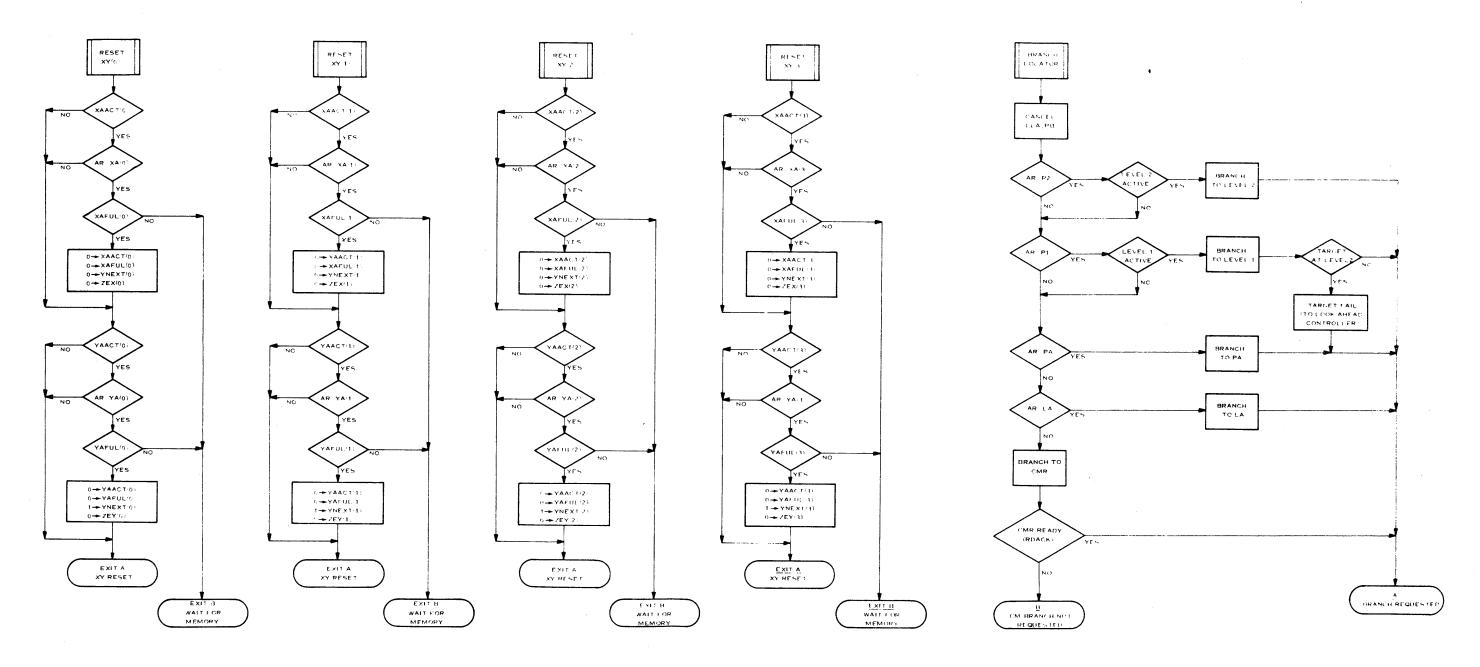

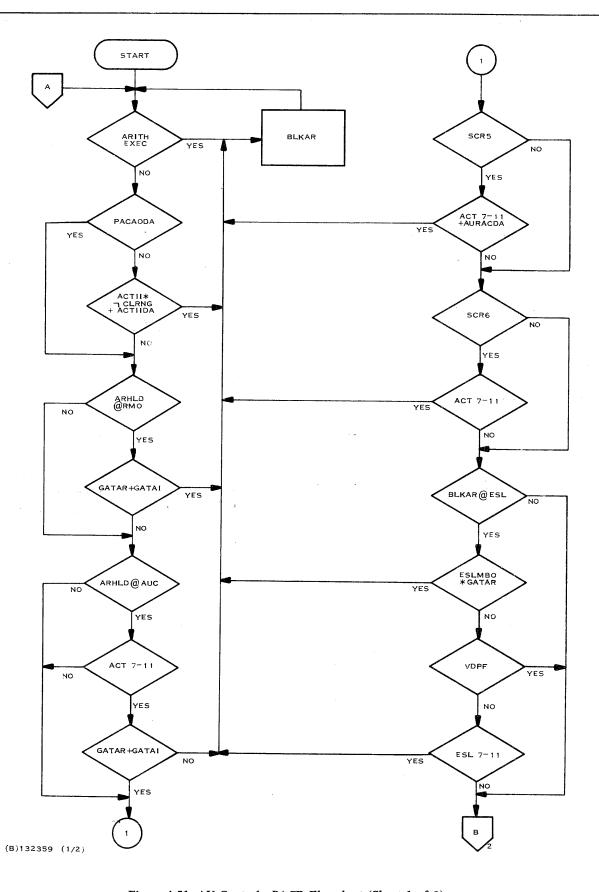

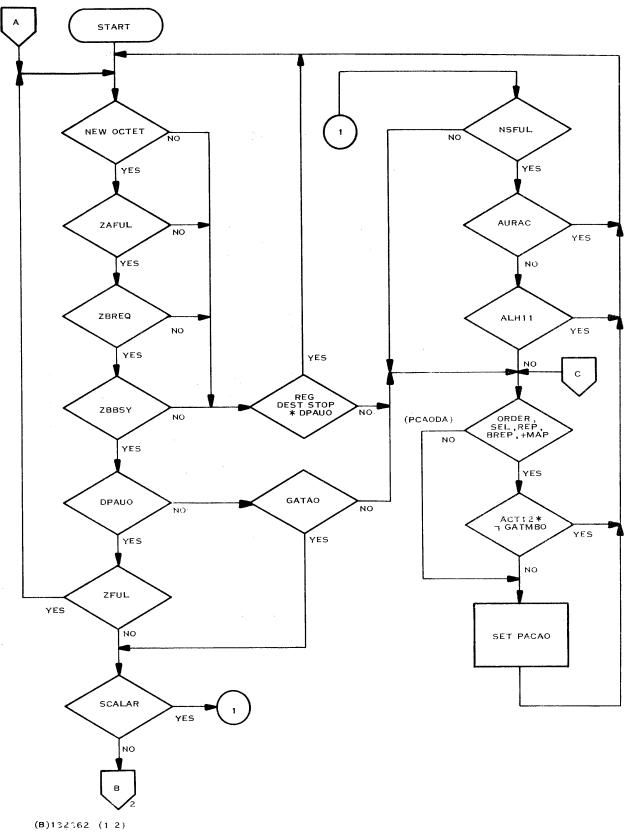

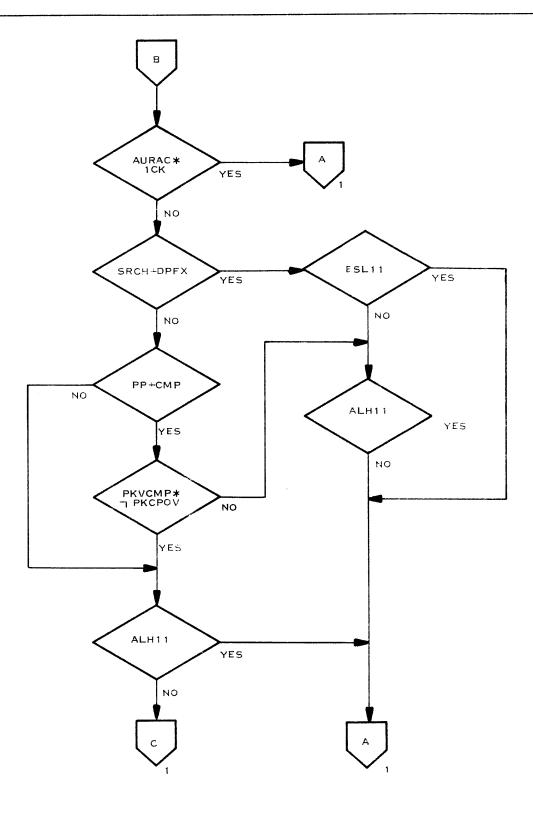

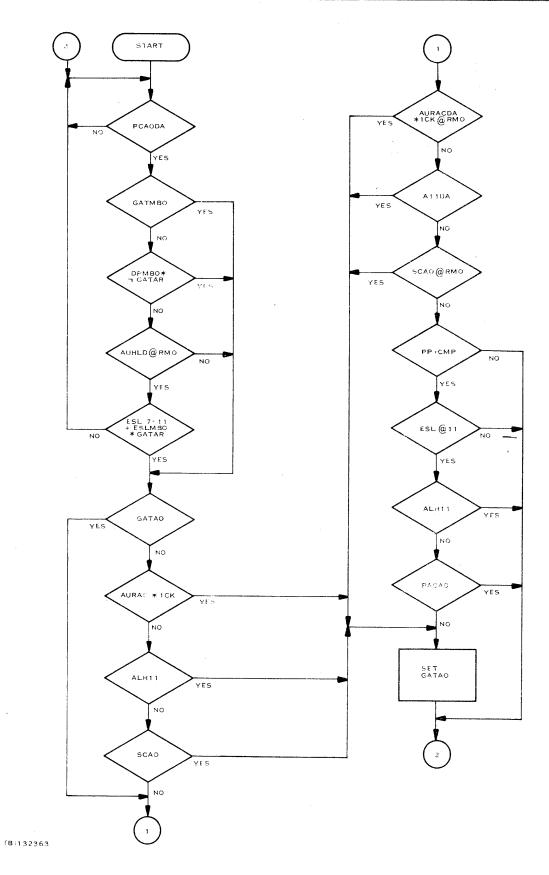

| 4-20<br>4-21              | Level 0 Controller Flowchart                                  |       |

| 4-21                      |                                                               |       |

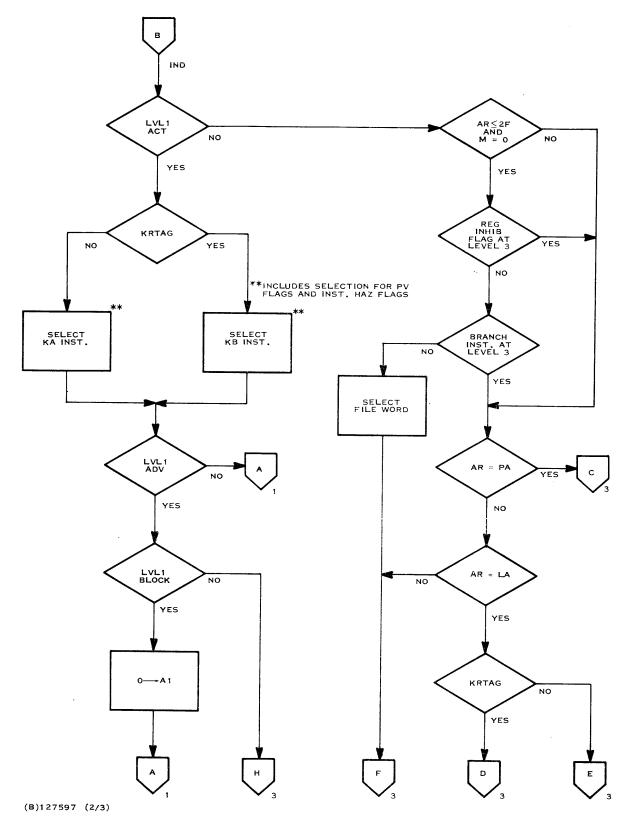

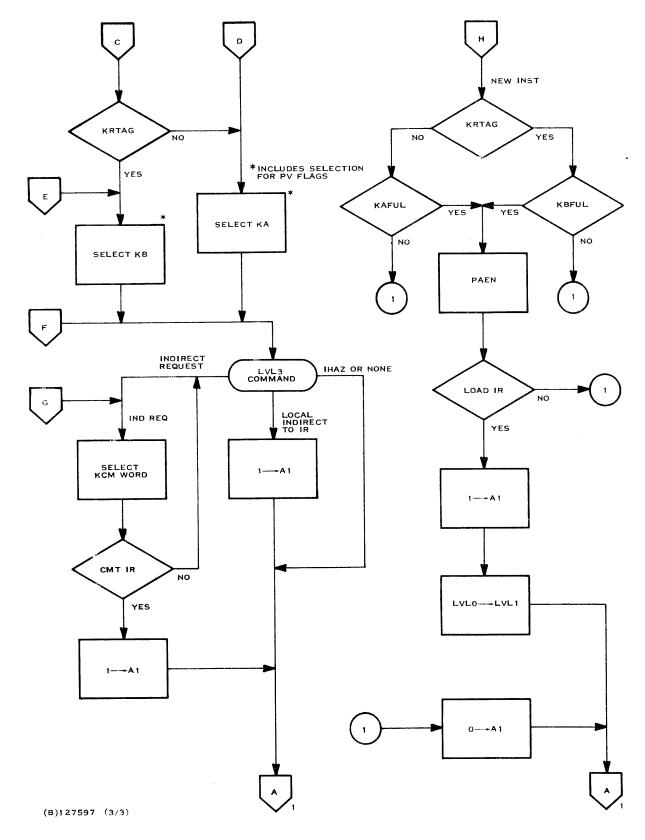

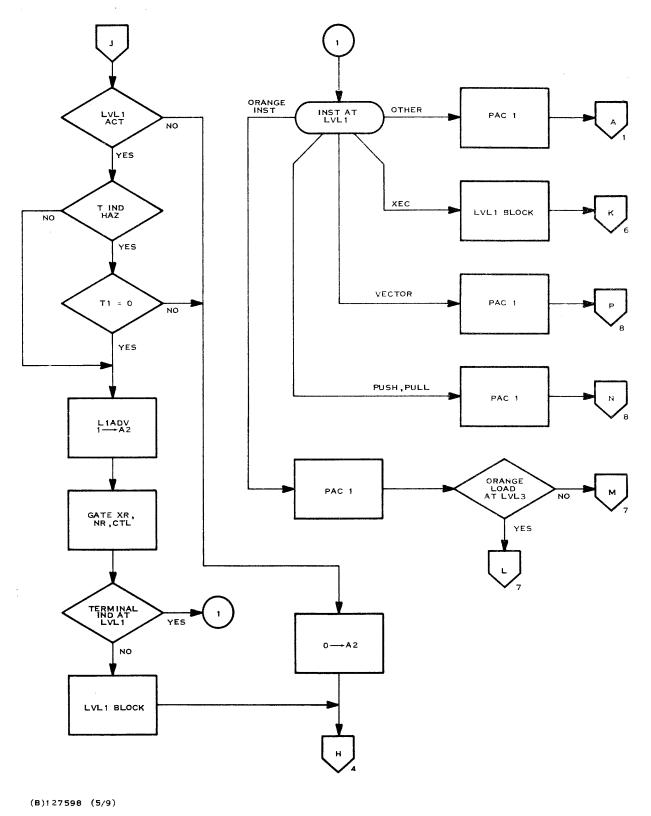

|                           | Level 1 Controller Flowchart                                  |       |

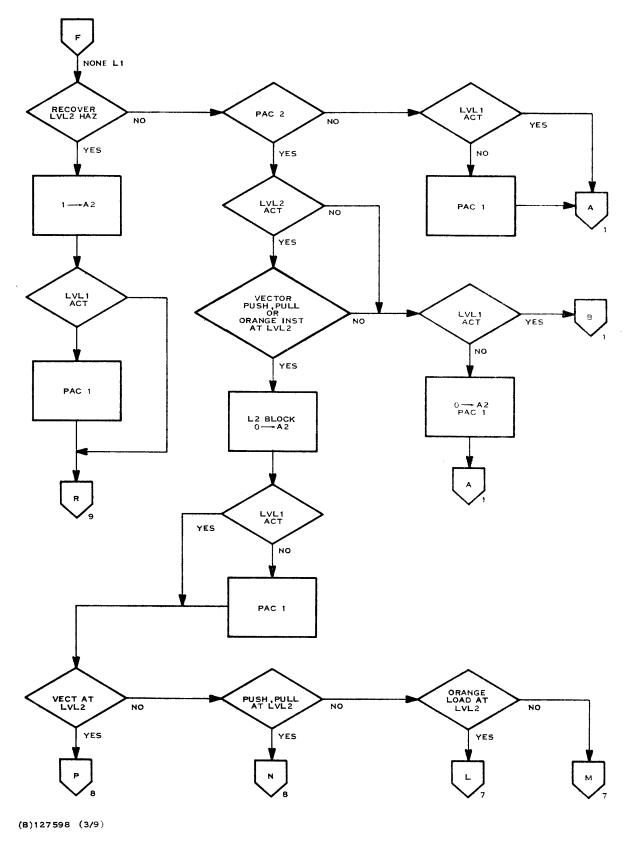

| 4-23                      | Level 2 Controller Flowchart                                  |       |

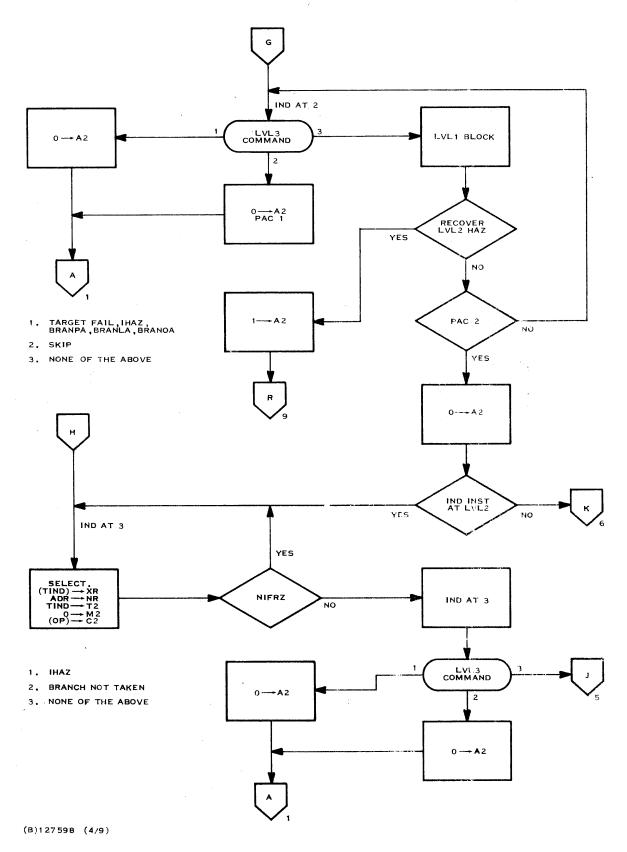

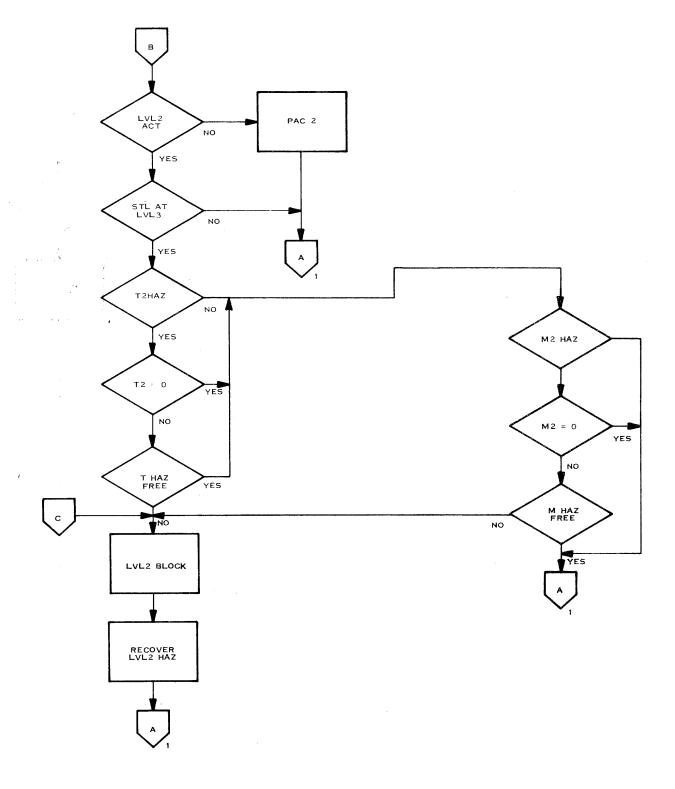

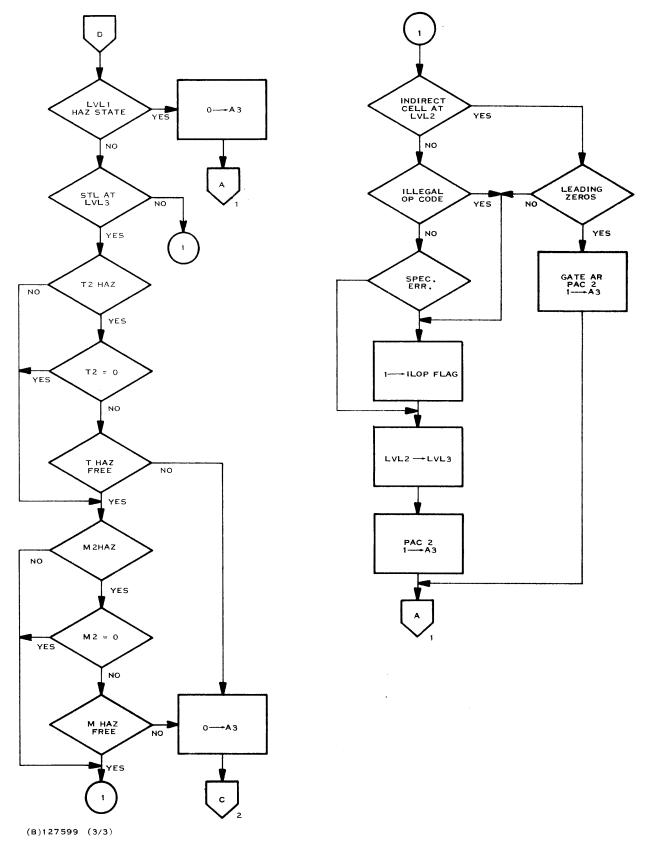

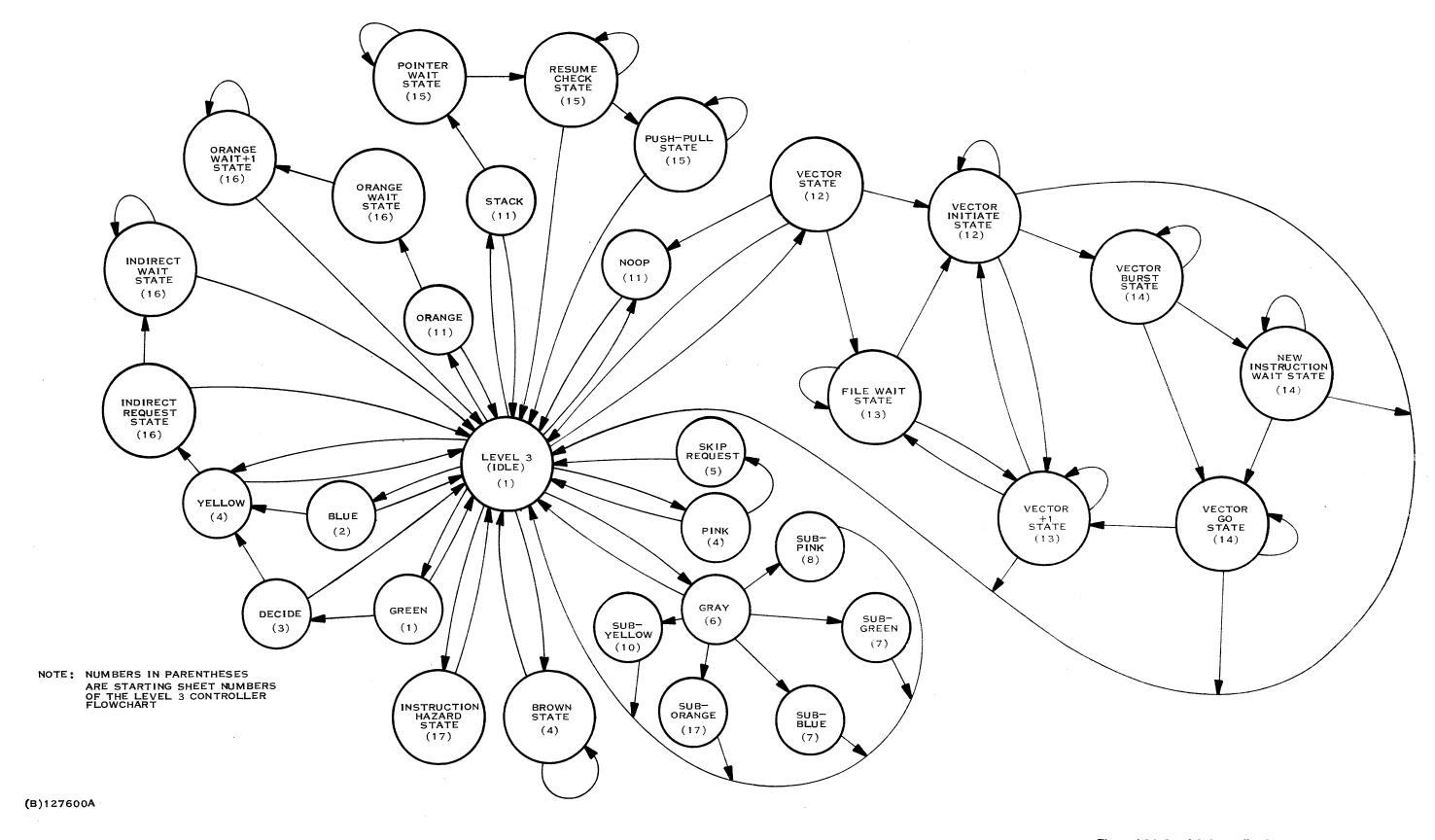

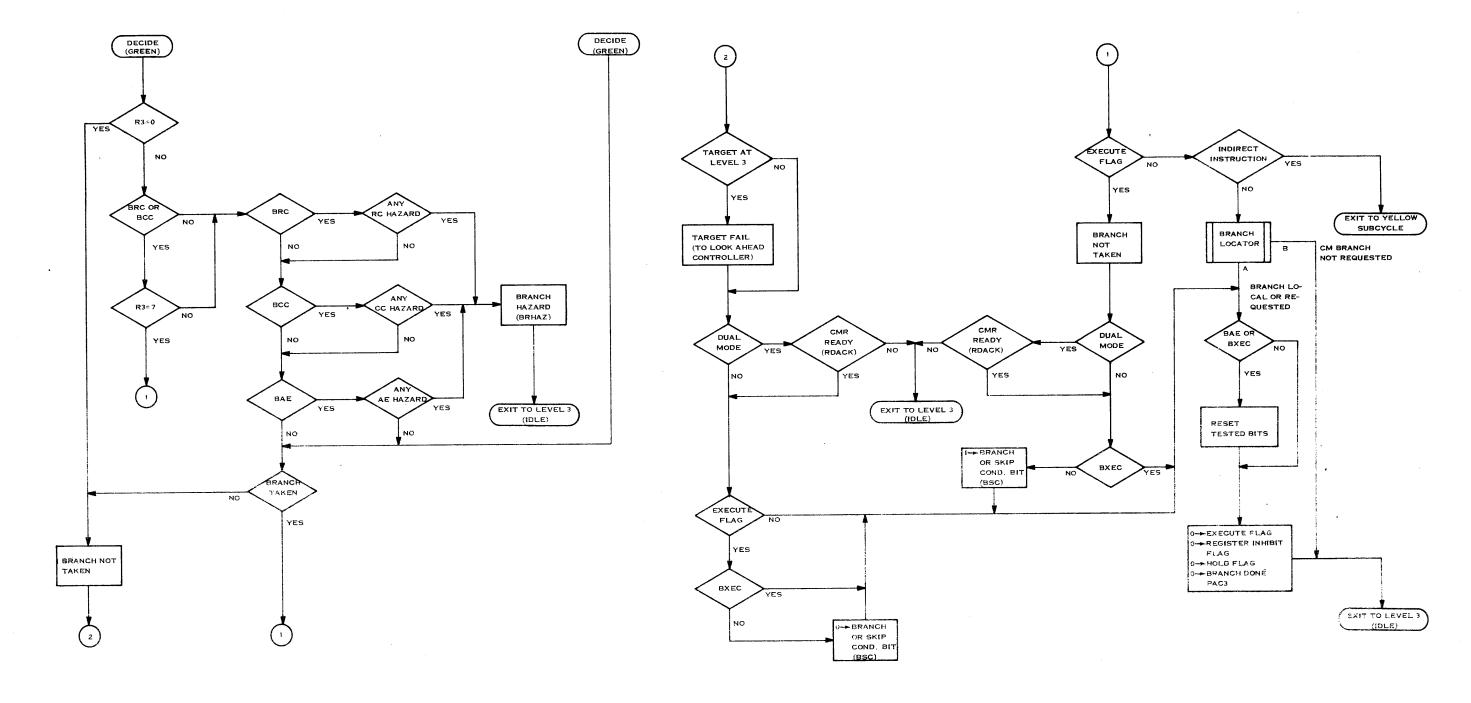

| 4-24                      | Level 3 Controller State Diagram                              |       |

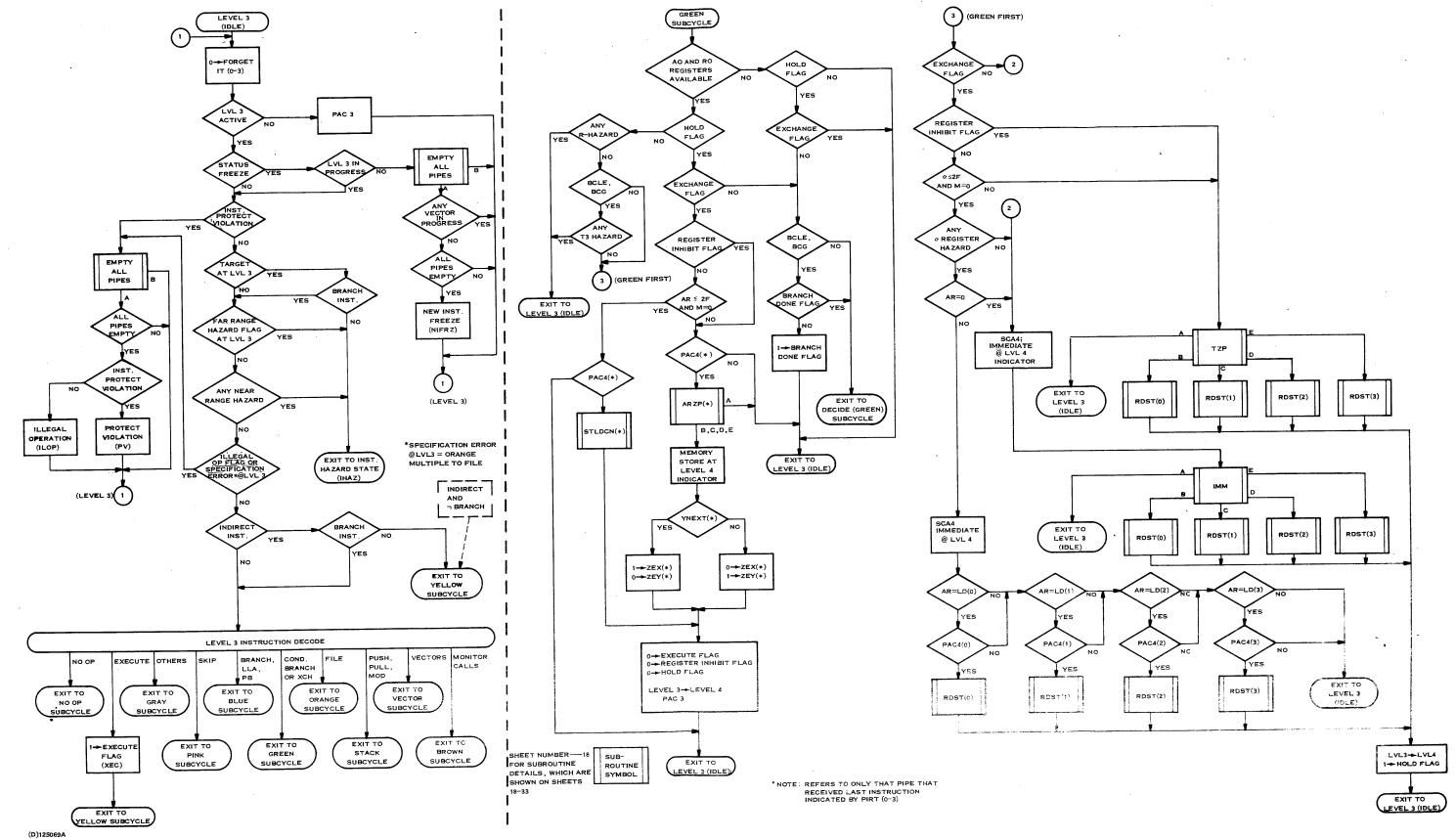

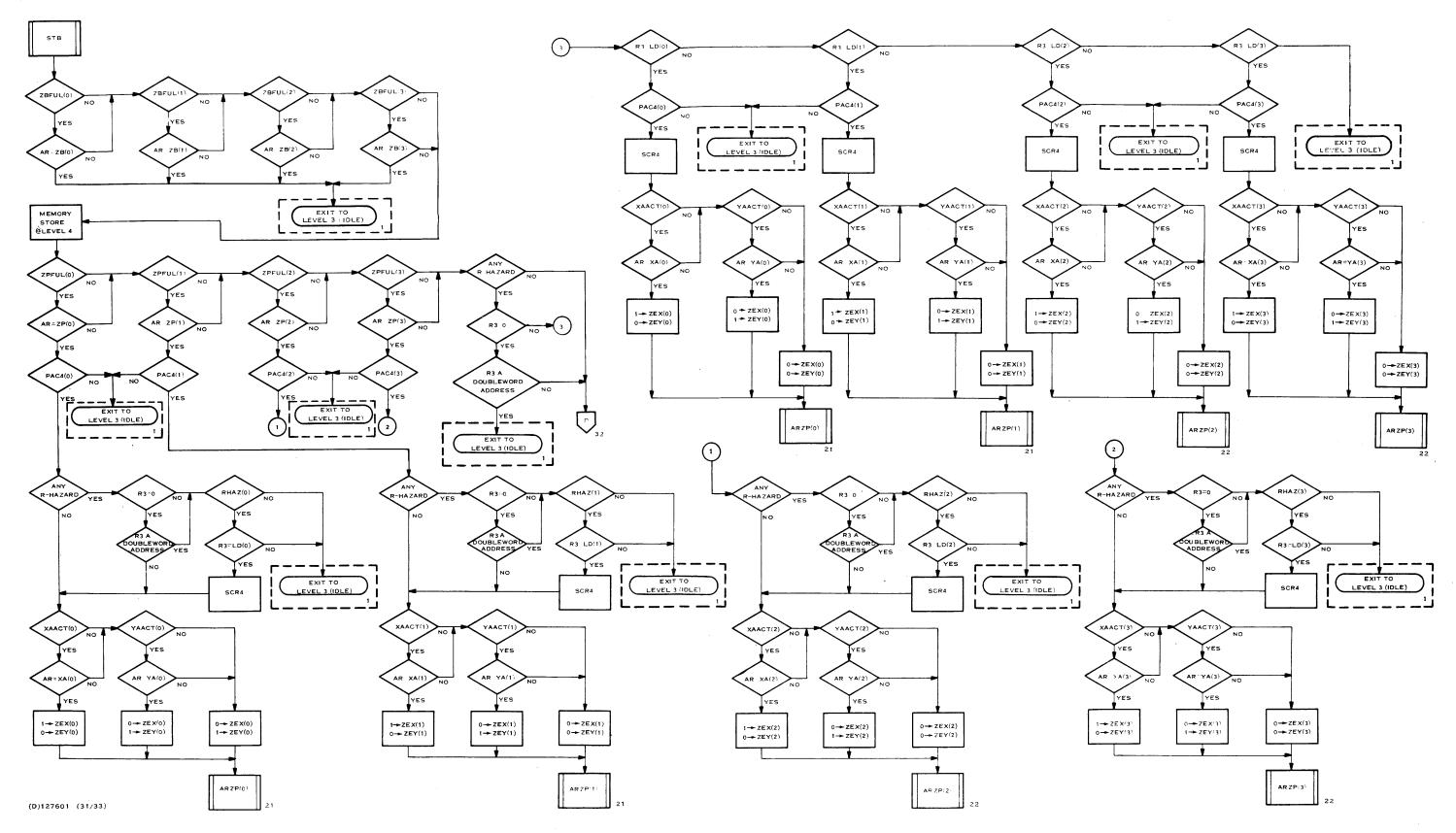

| 4-25                      | Level 3 Controller Flowchart                                  |       |

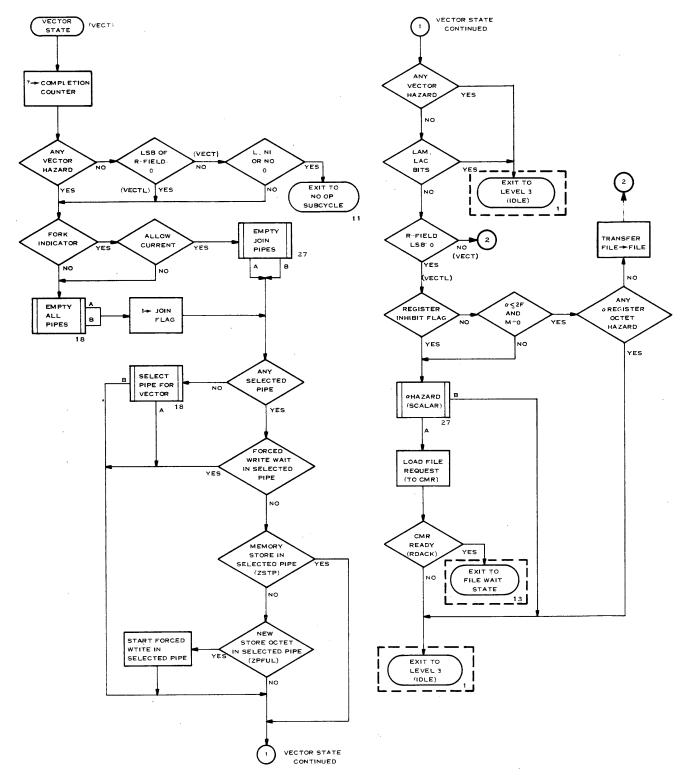

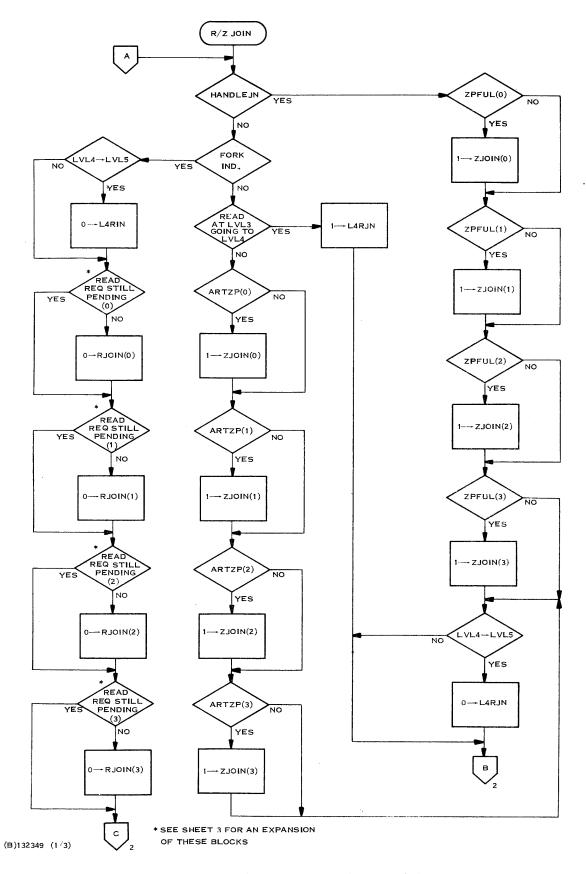

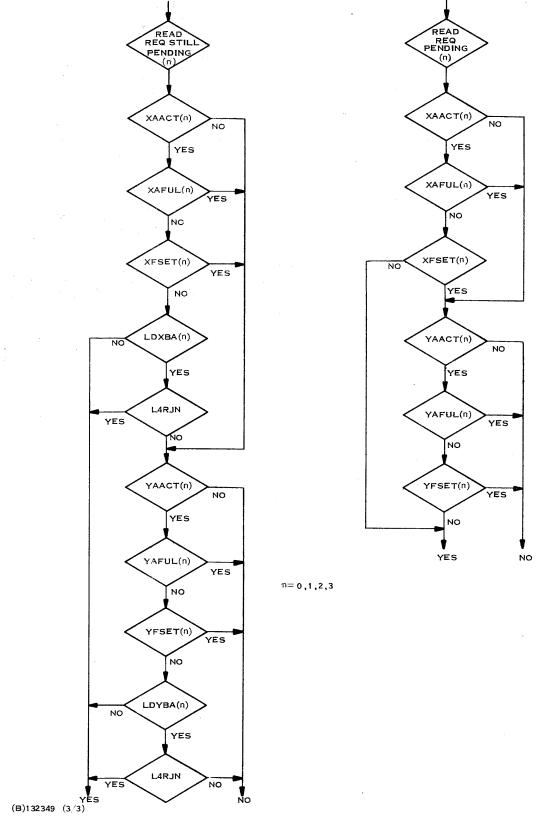

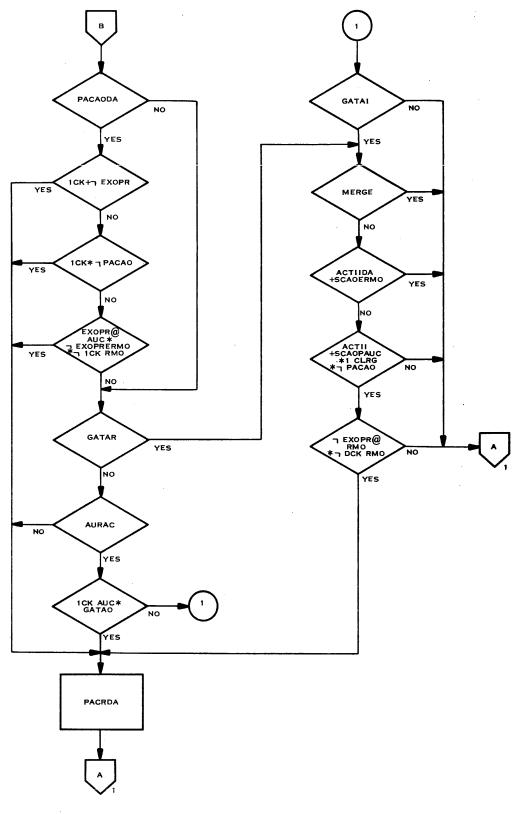

| 4-26                      | R/Z Join Flowchart                                            |       |

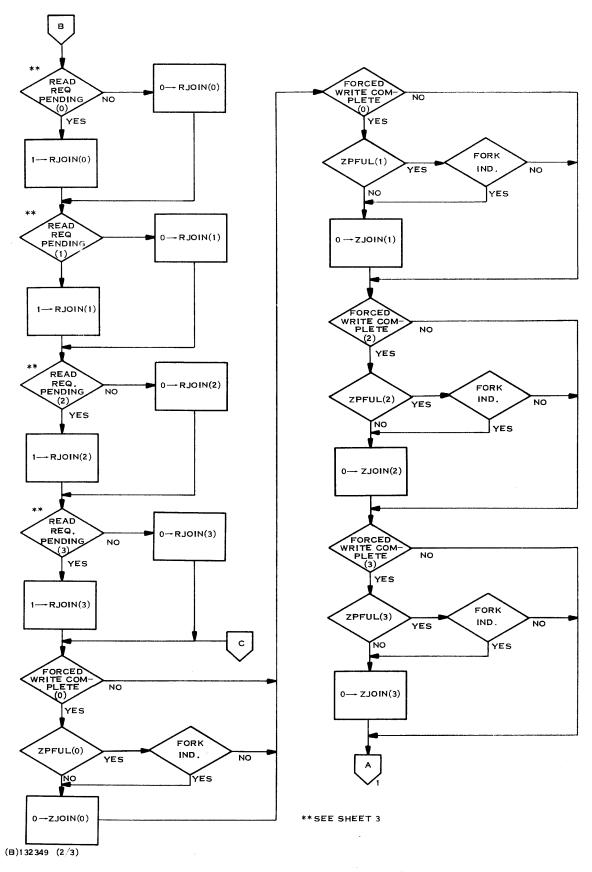

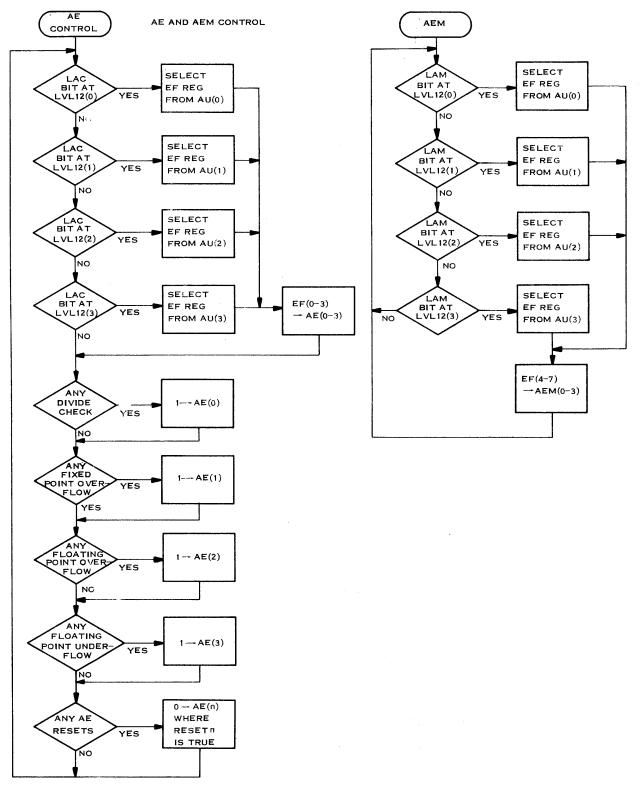

| 4-27                      | Arithmetic Exception and Arithmetic Exception Mask Control    |       |

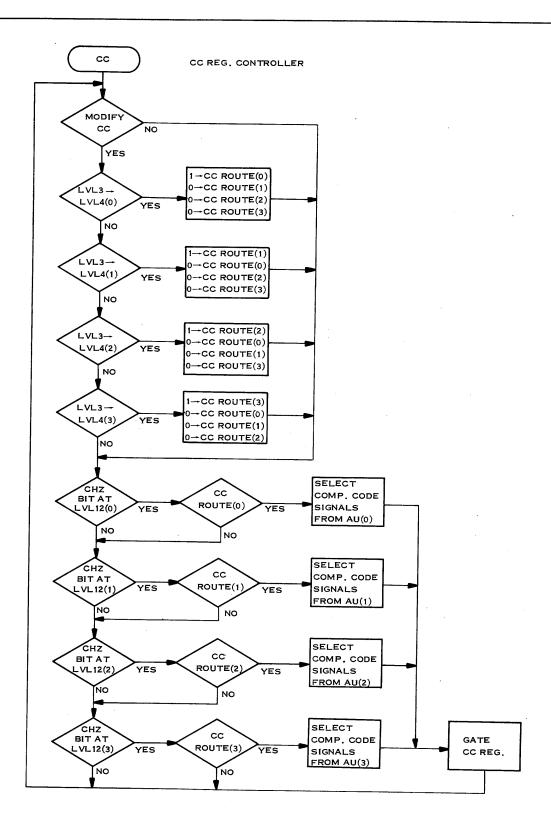

| 4-28                      | Compare Code Register Controller Flowchart                    |       |

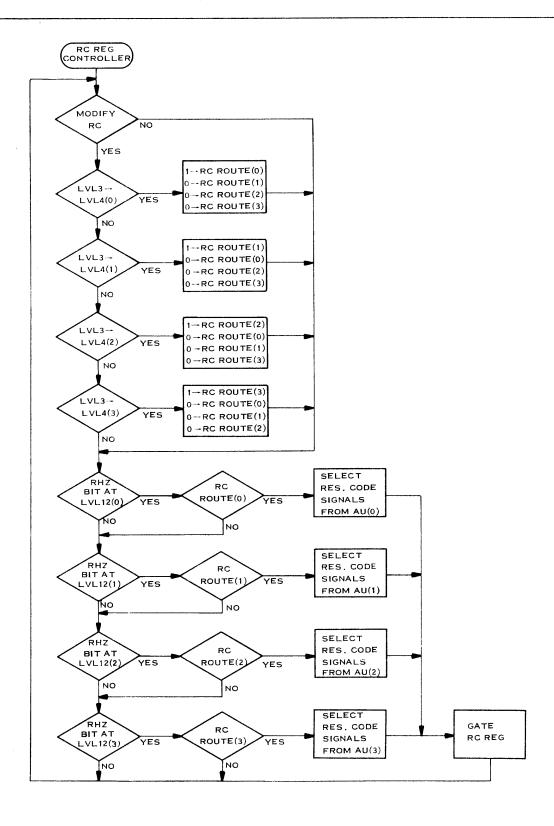

| 4-29                      | Result Code Register Controller Flowchart                     |       |

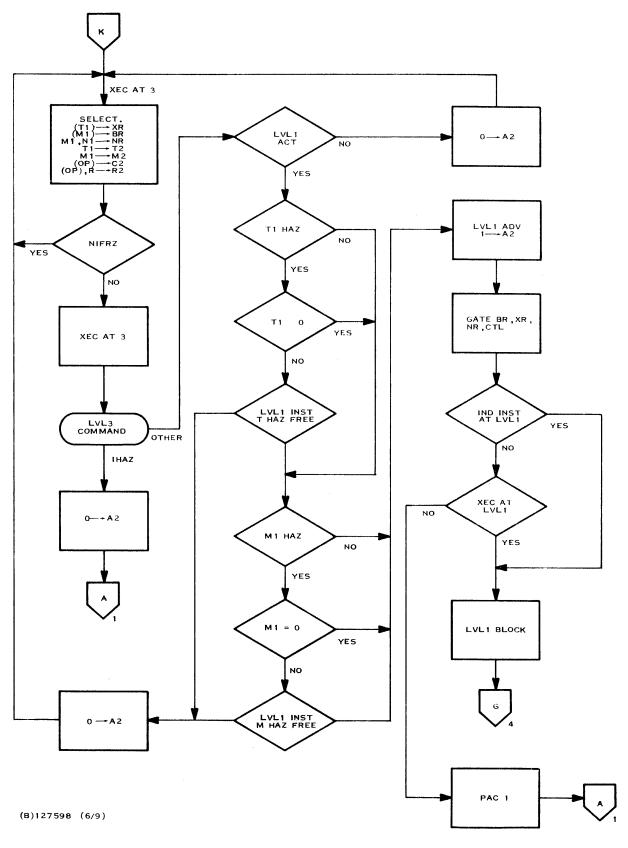

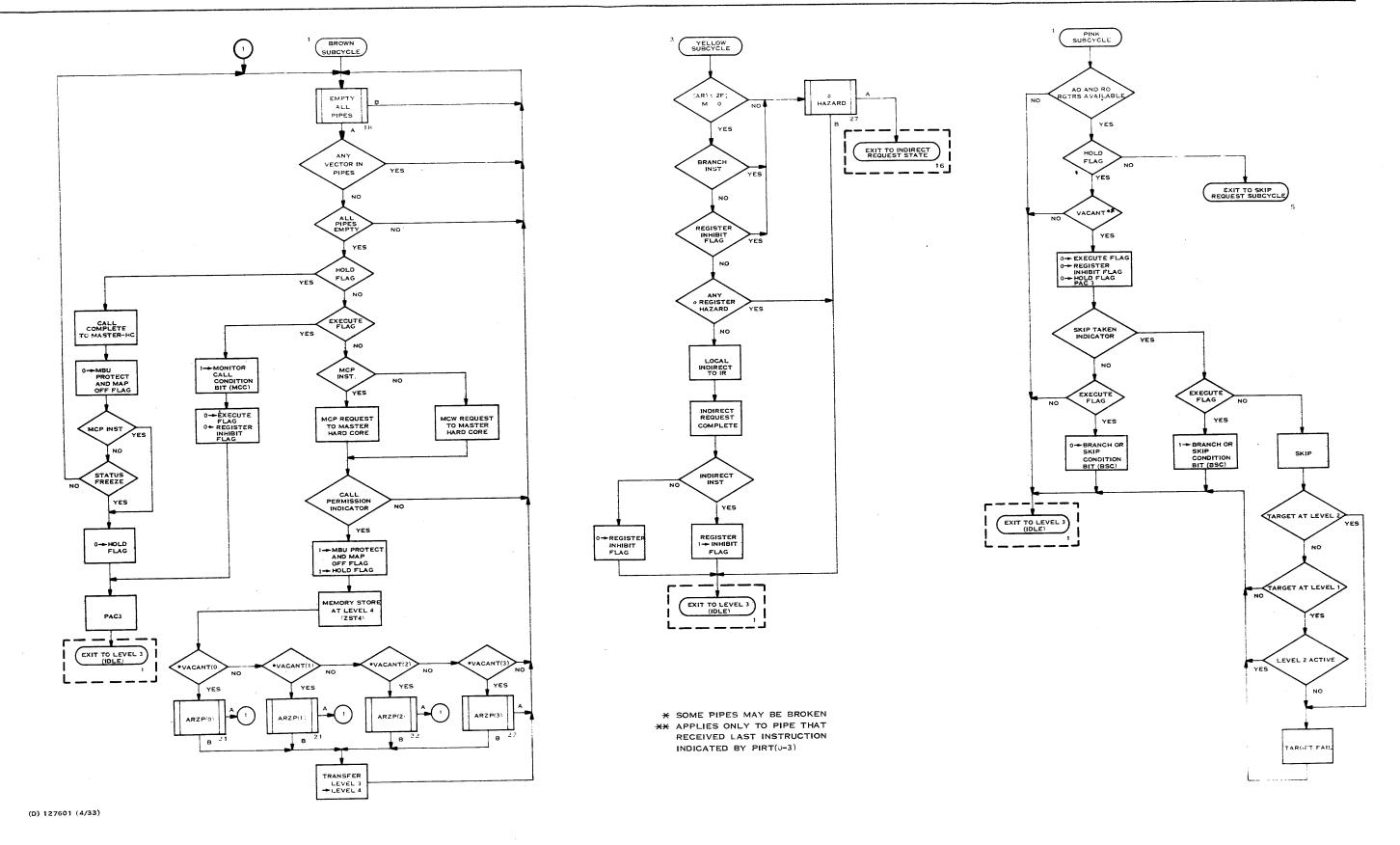

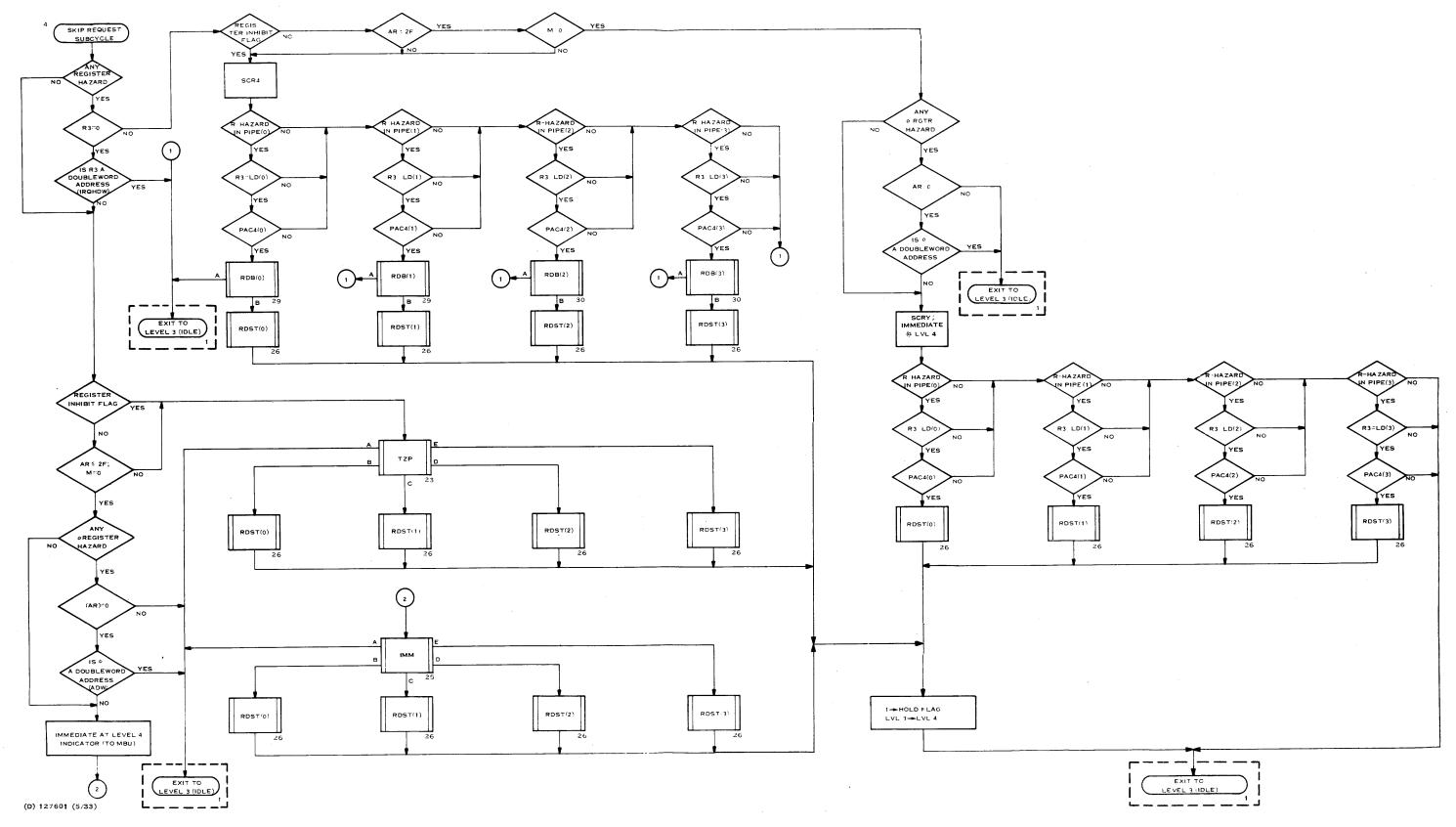

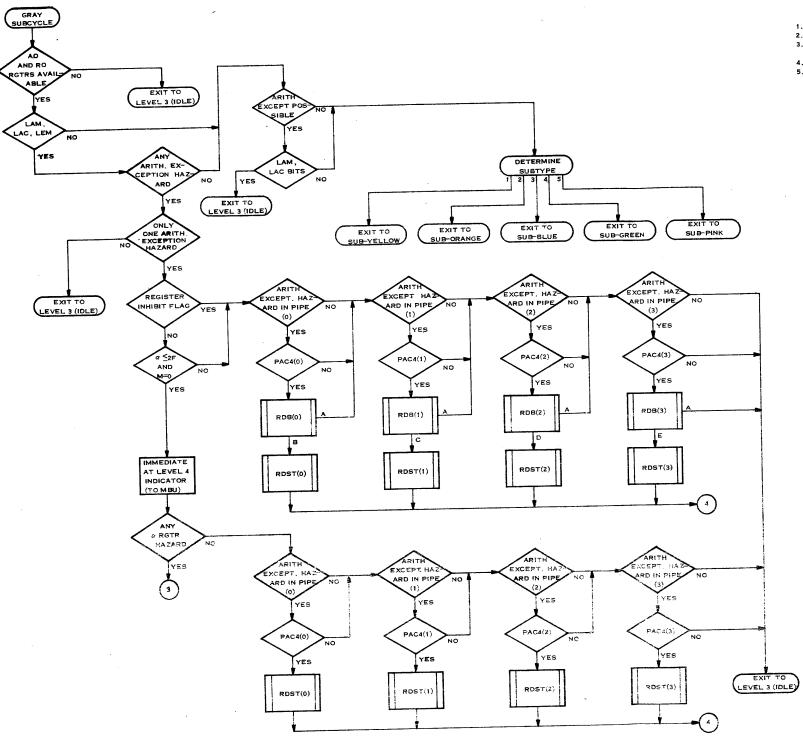

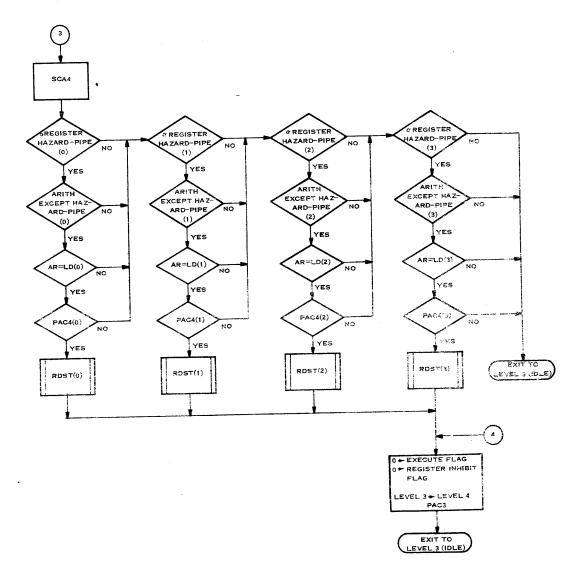

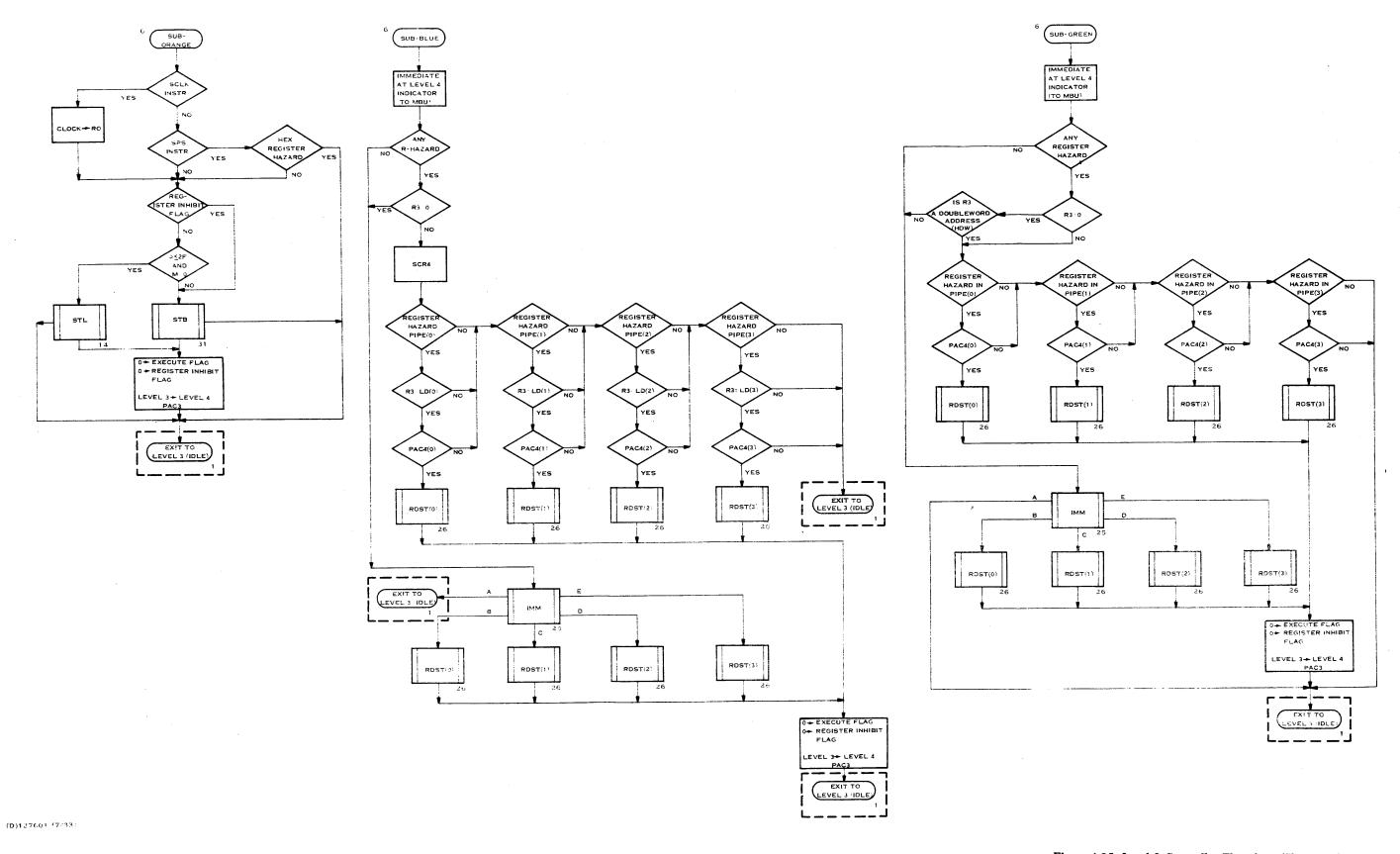

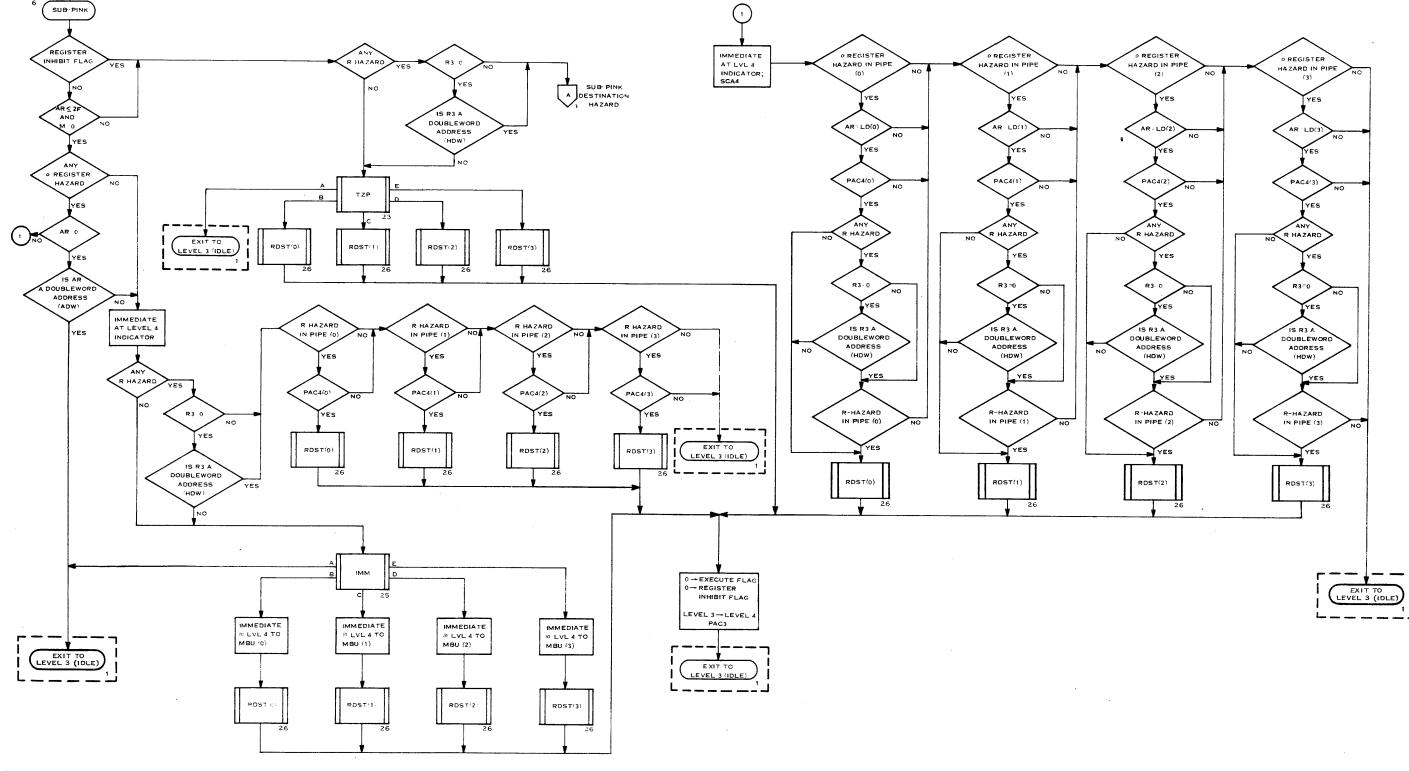

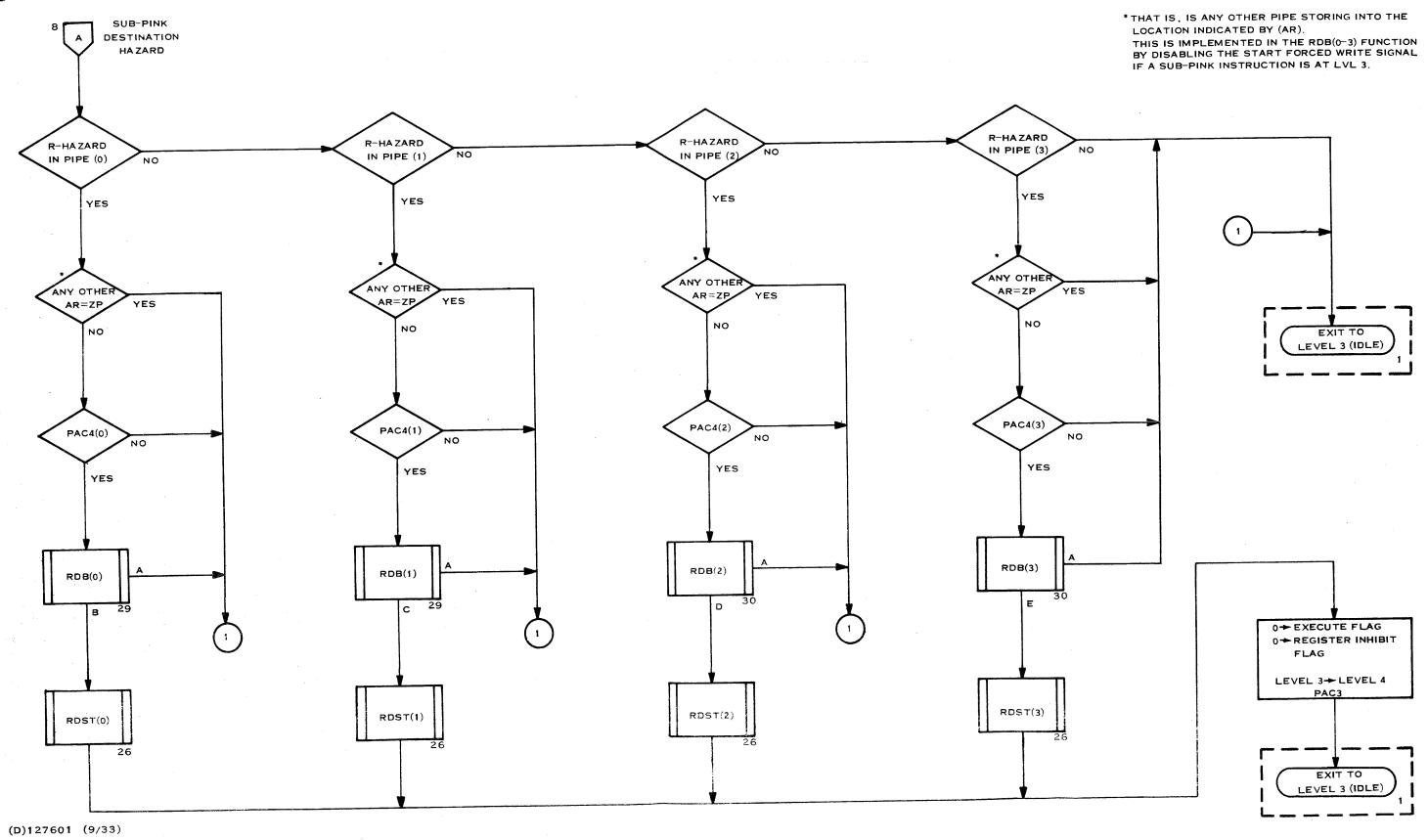

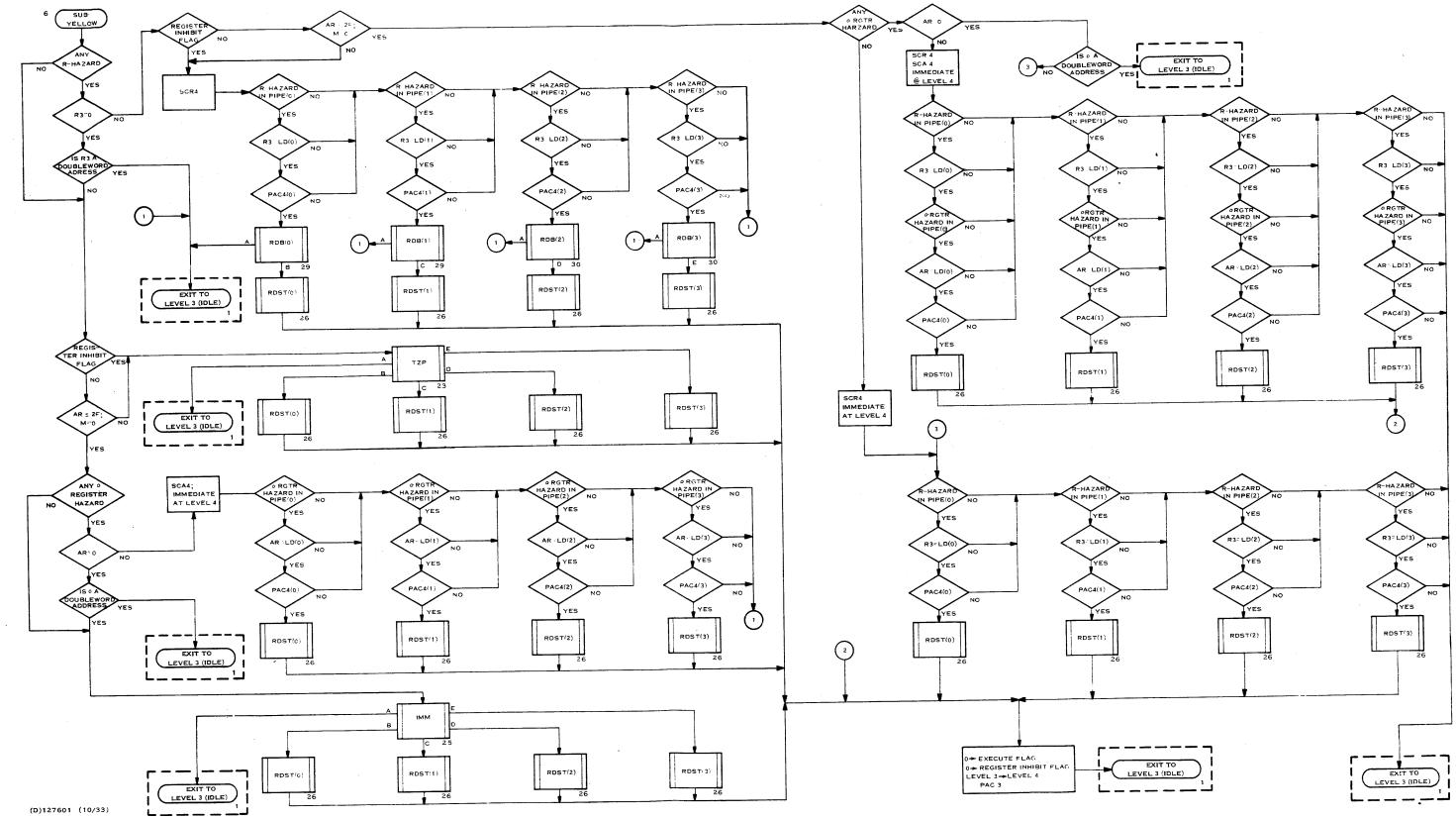

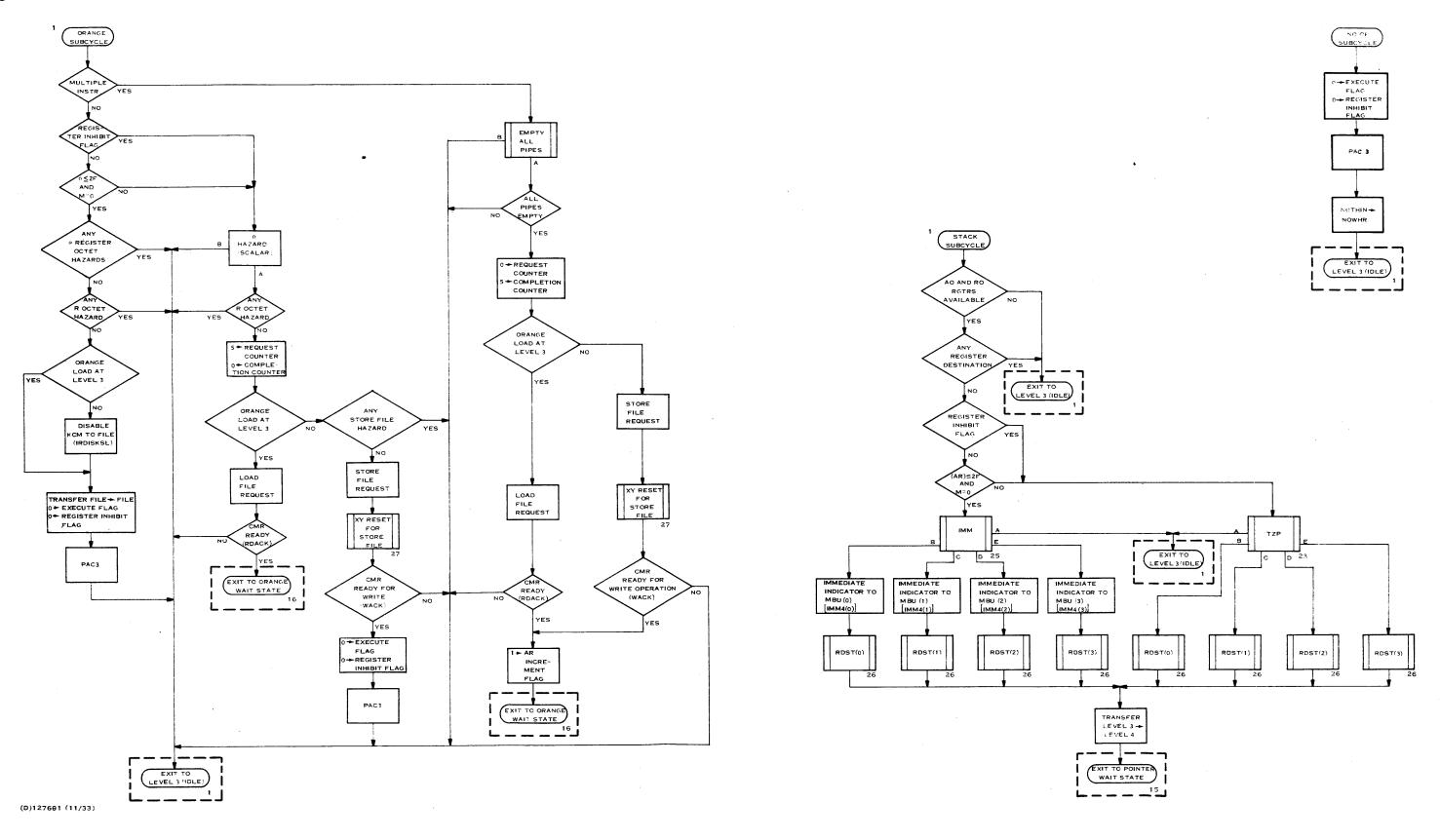

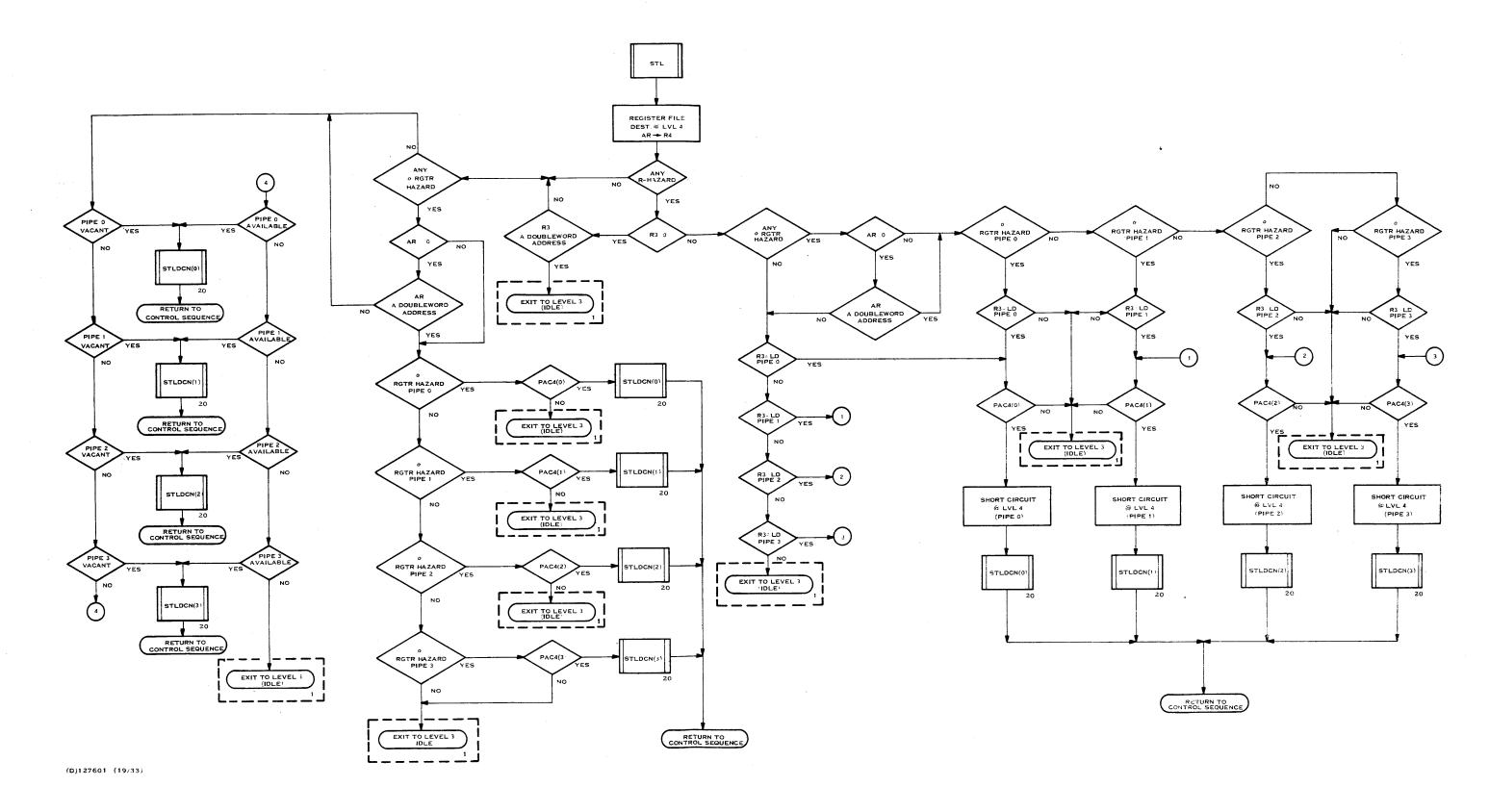

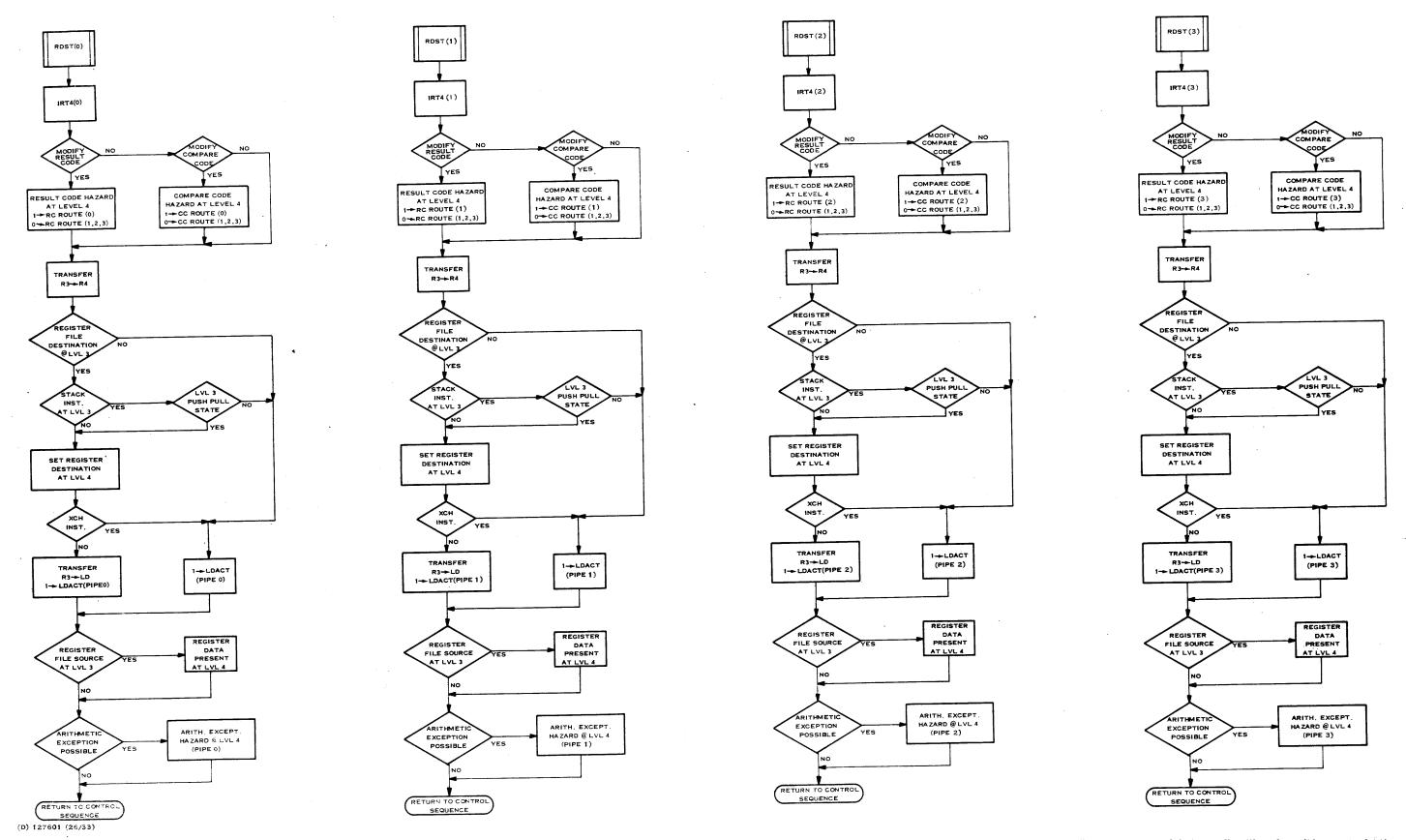

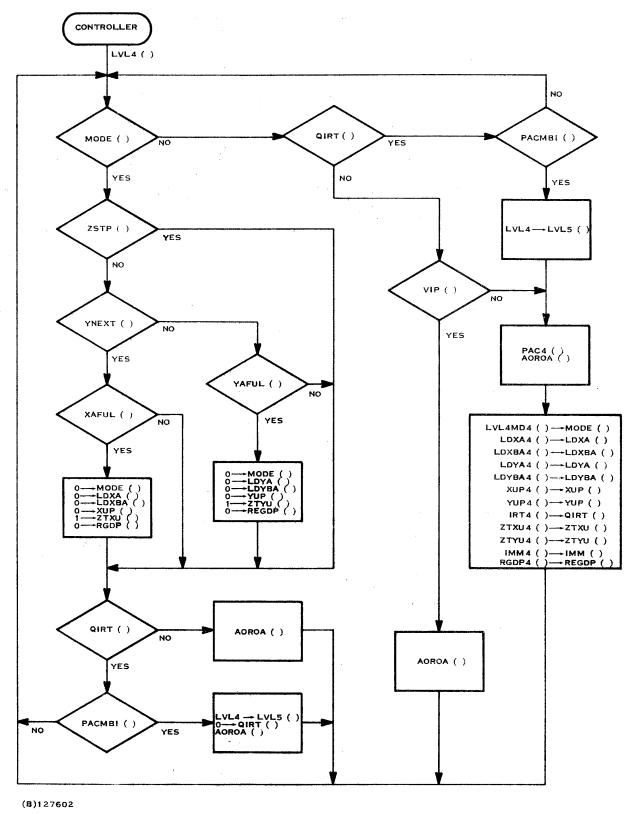

| 4-30                      | Level 4 Controller Flowchart                                  |       |

| 4-31                      | Level 4 IPU Models                                            |       |

| 4-32                      | Leve 1 4 MBU Model                                            |       |

| 4-33                      | Level 4 Select Next Controller Model                          |       |

| 4-34                      | Level 4 IPU's AU Model                                        | 4-164 |

| 4-35                      | Level 4 PACAUO = 1                                            | 4-166 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                       | Page  |

|--------|-------------------------------------------------------------|-------|

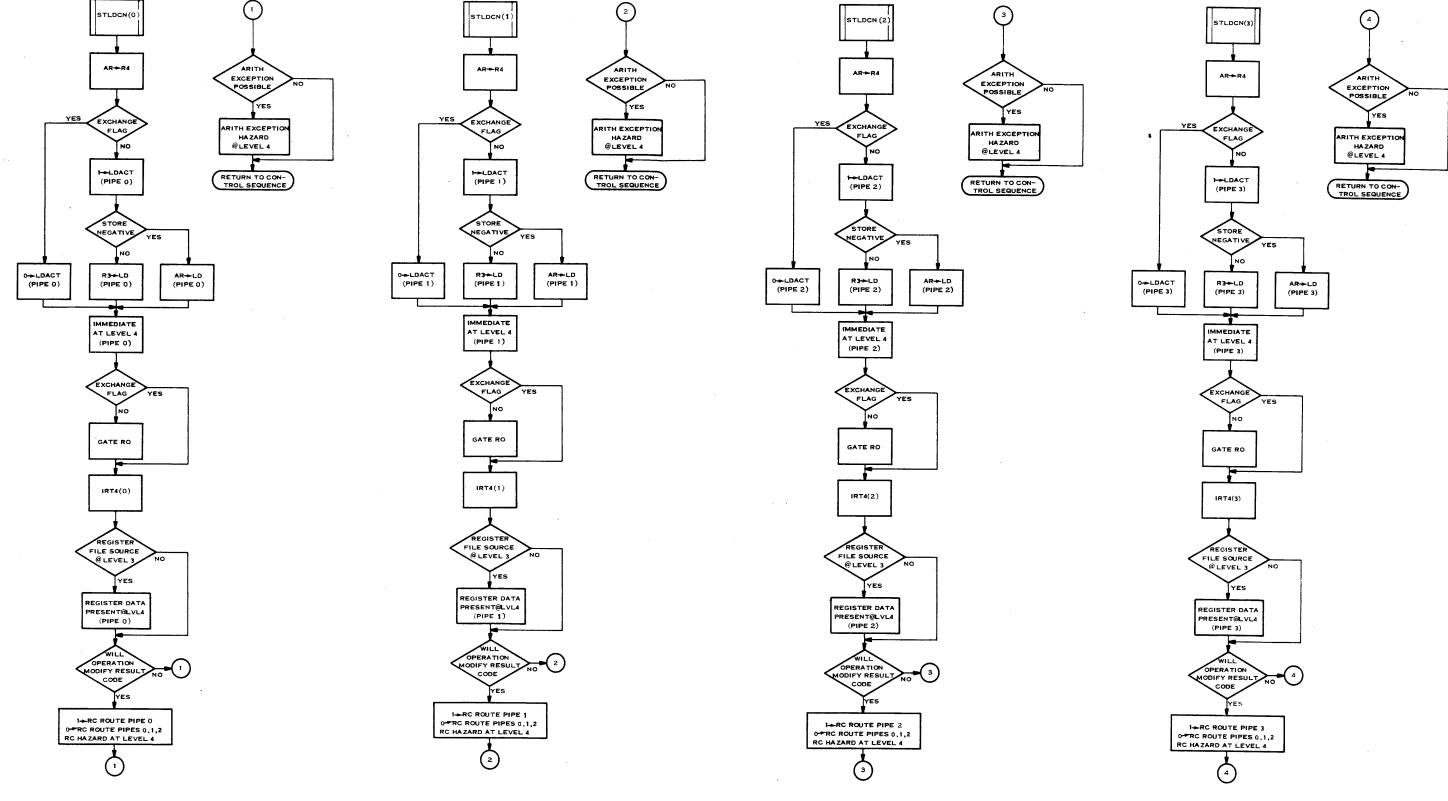

| 4-36   | Level 4 AU Output to File                                   | 4-168 |

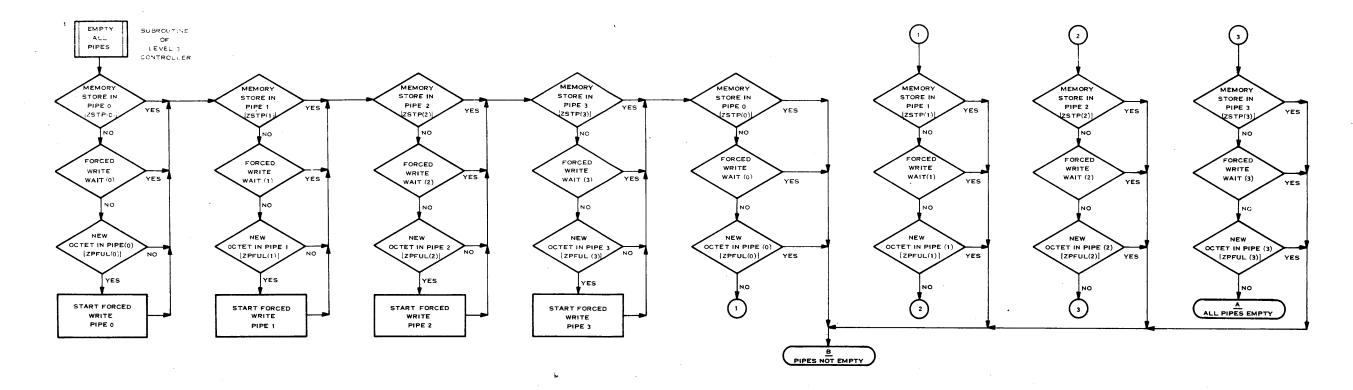

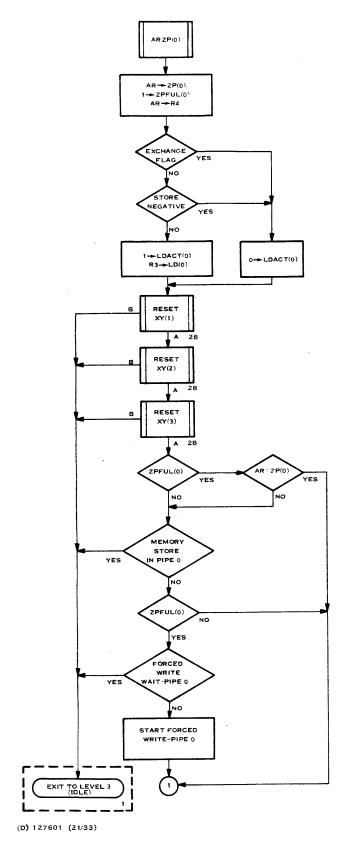

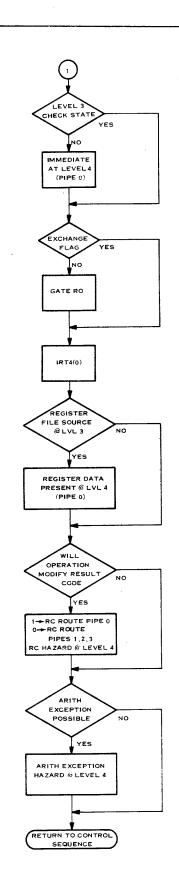

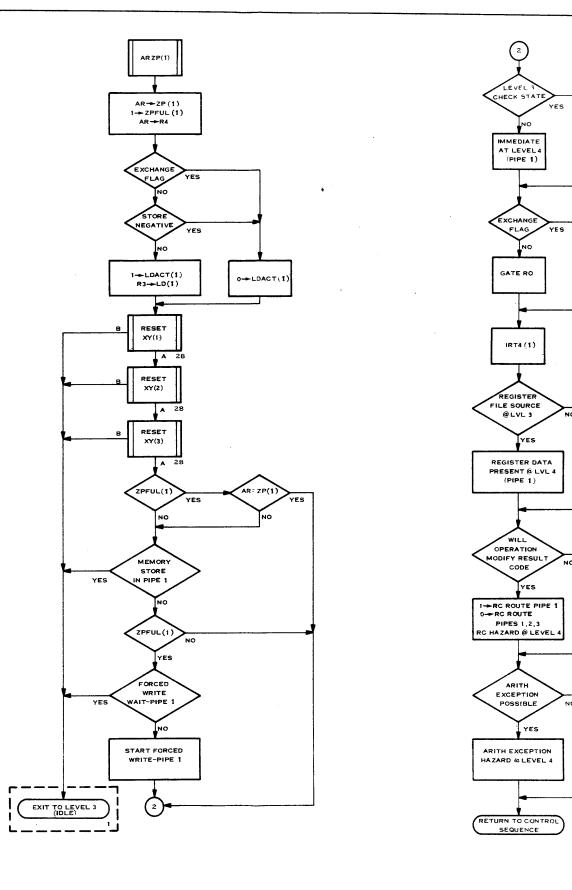

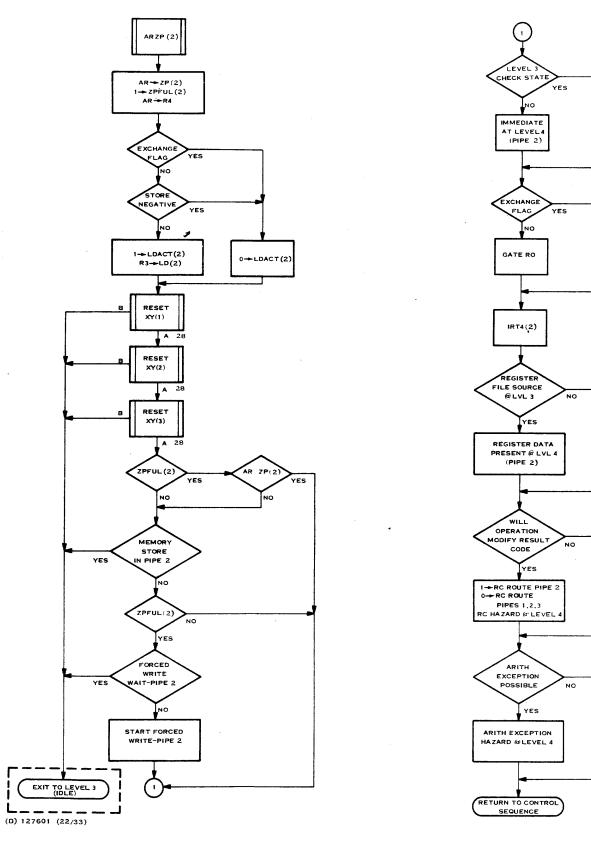

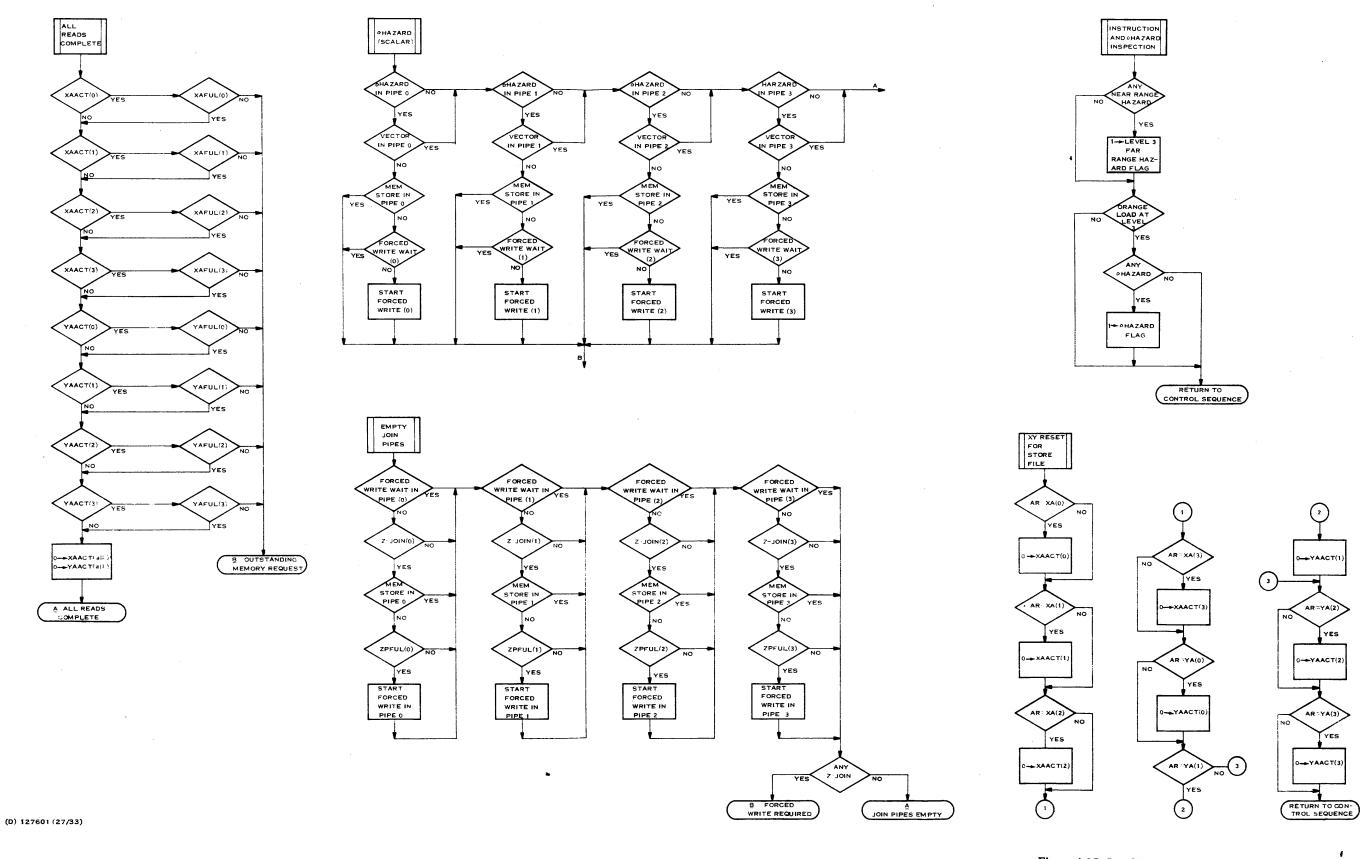

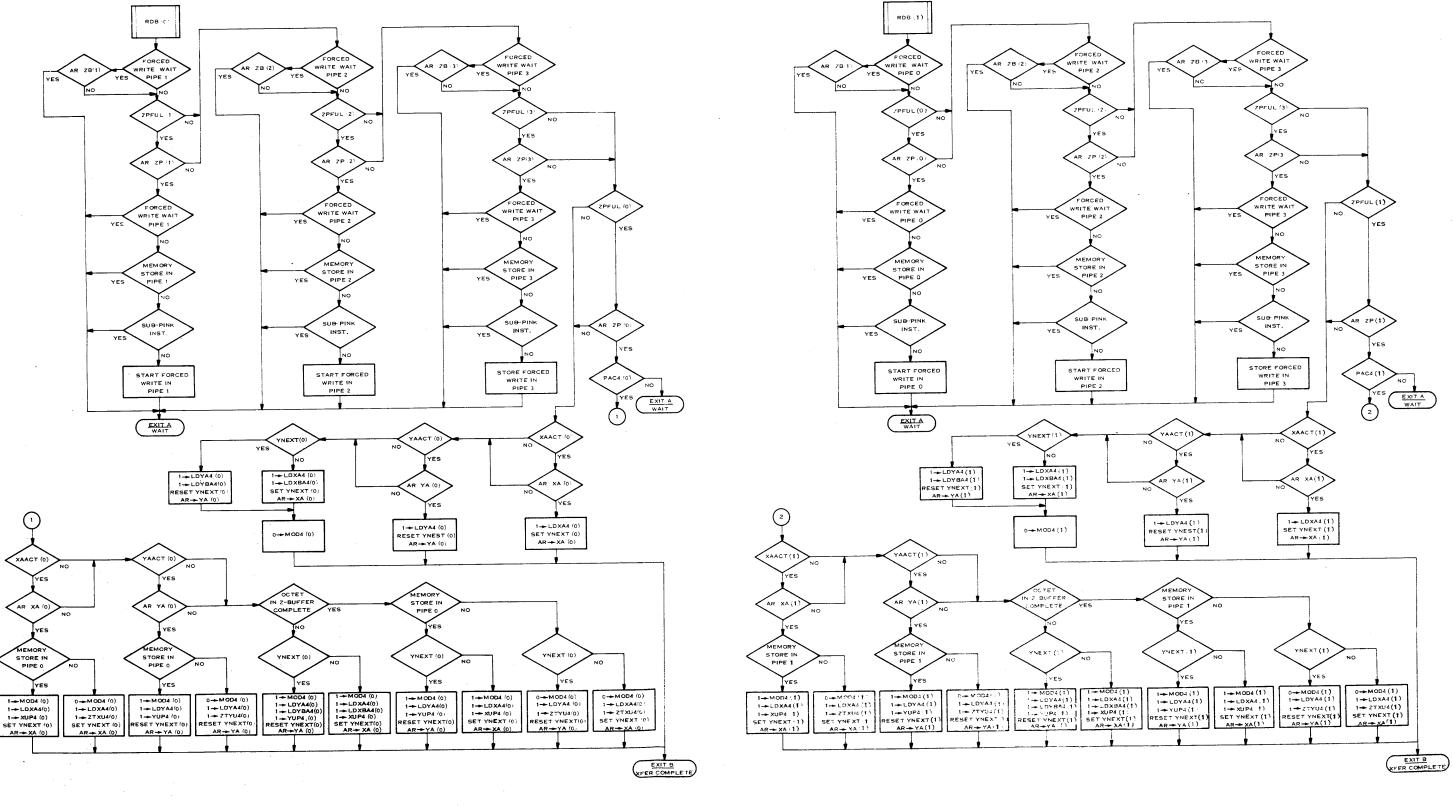

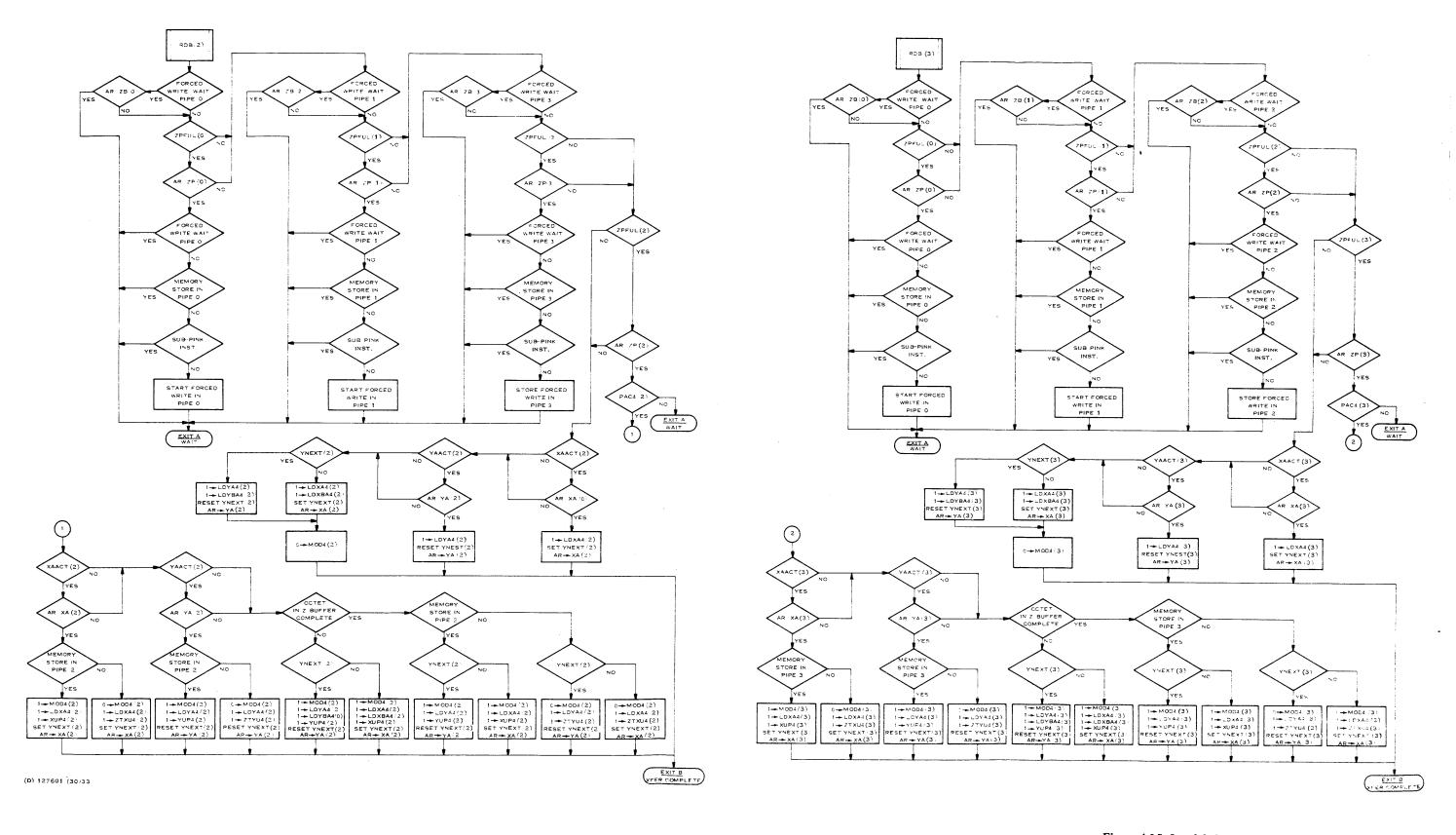

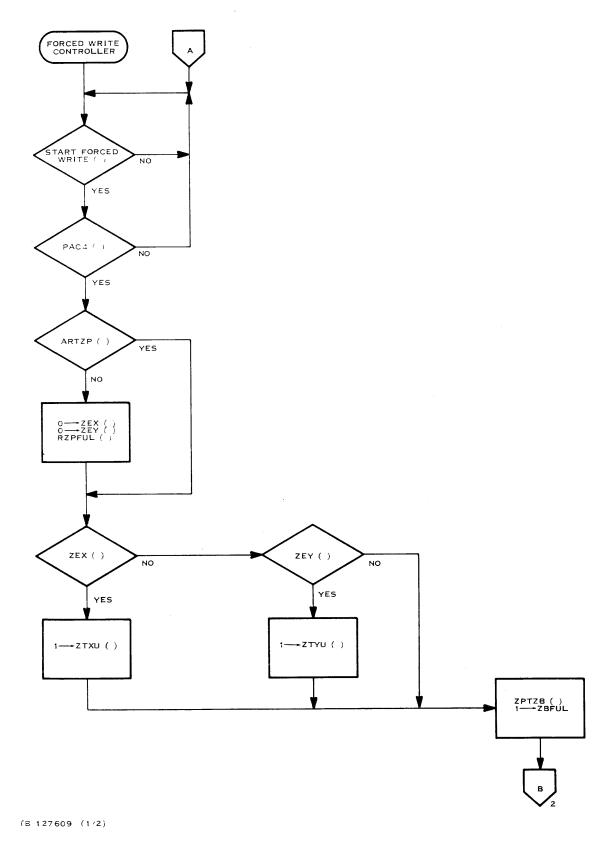

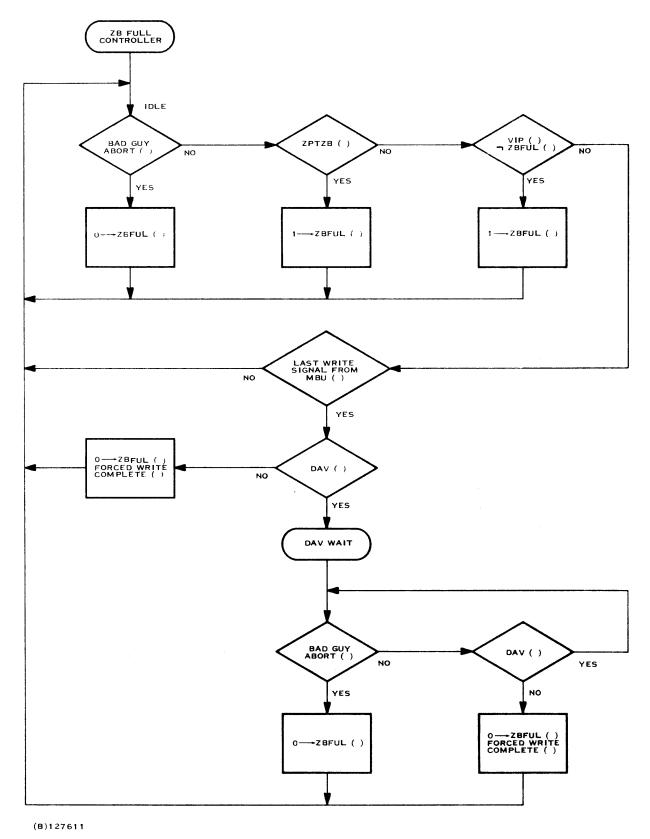

| 4-37   | Level 4 Forced Write Controller                             |       |

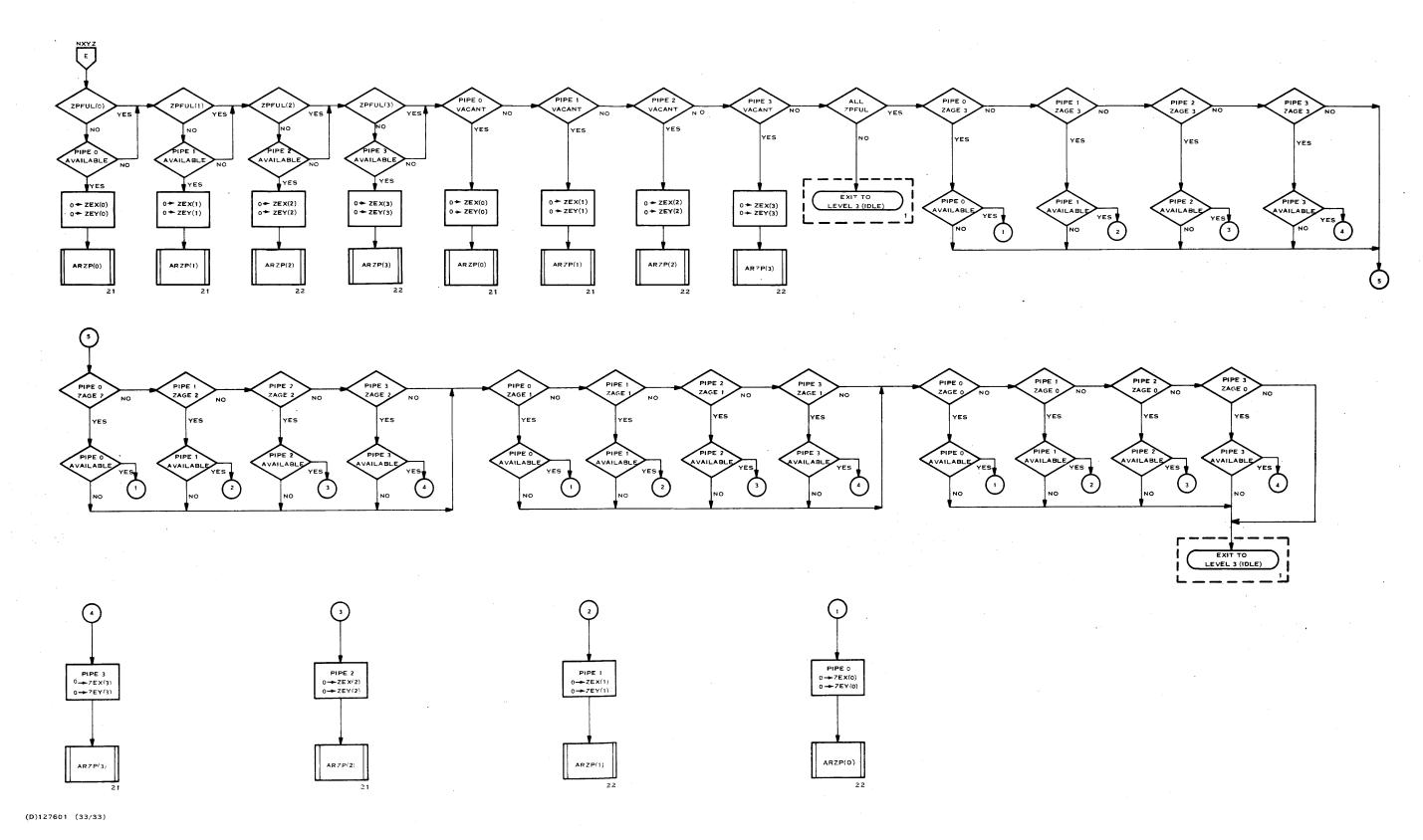

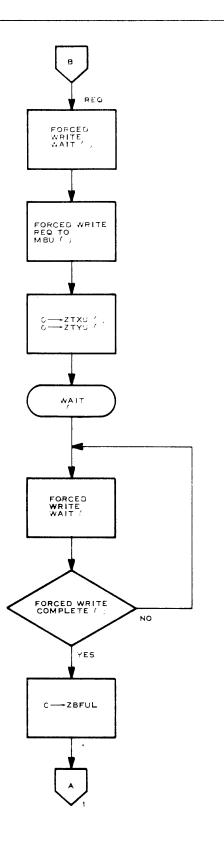

| 4-38   | Level 4 ZPFULL Controller                                   |       |

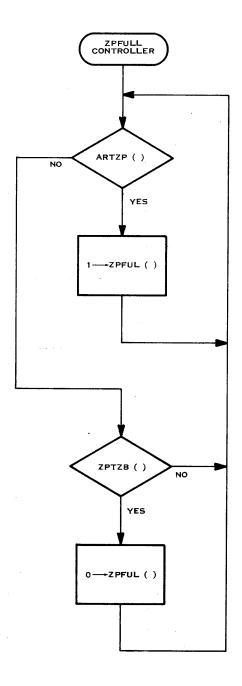

| 4-39   | Level 4 ZBFULL Controller                                   |       |

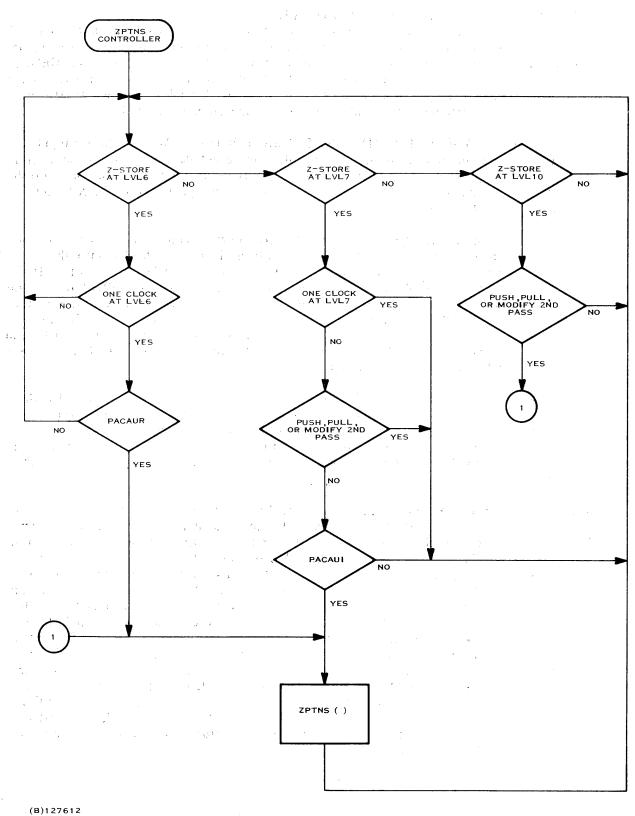

| 4-40   | Level 4 ZPTNS Controller                                    | 4-173 |

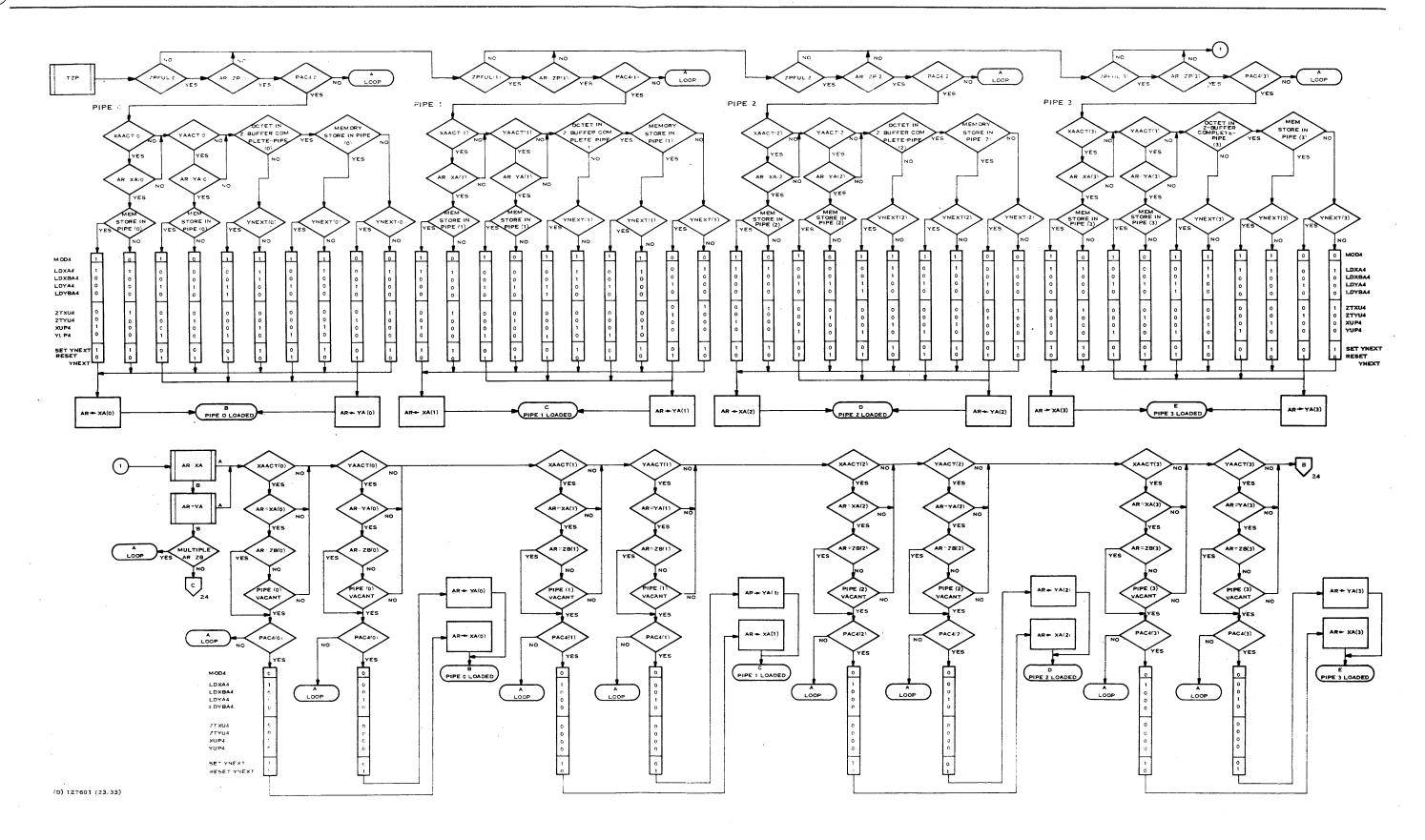

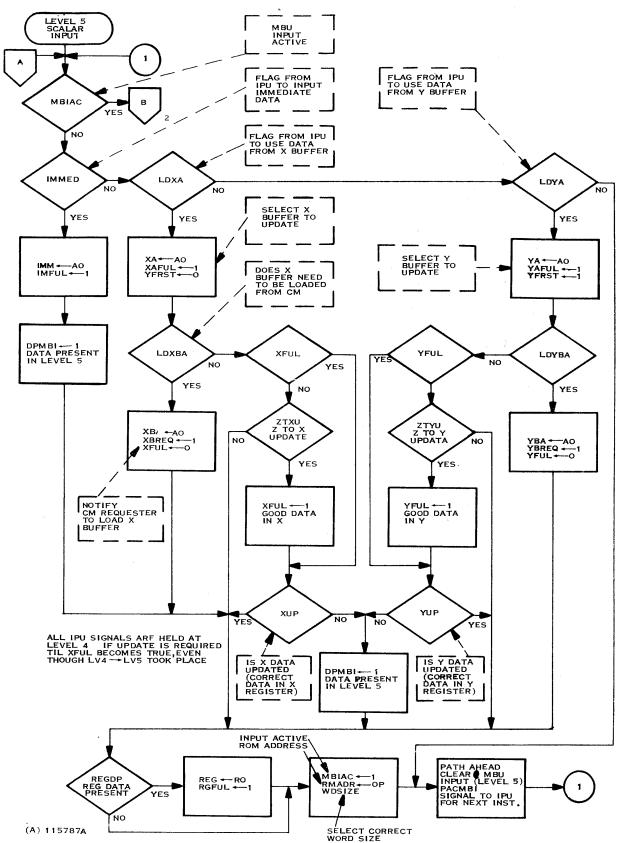

| 4-41   | Level 5 Scalar Input Controller Flowchart                   |       |

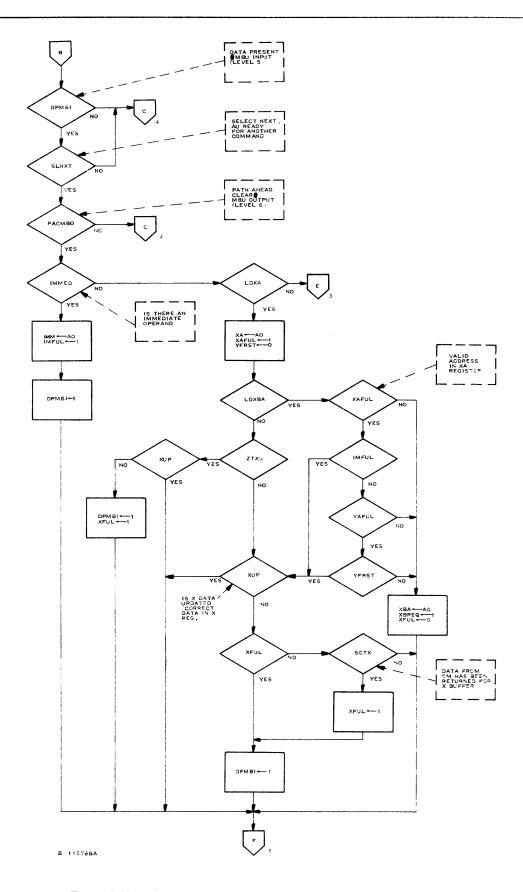

| 4-42   | Level 6 MBU Output Control Flowchart - Scalar               |       |

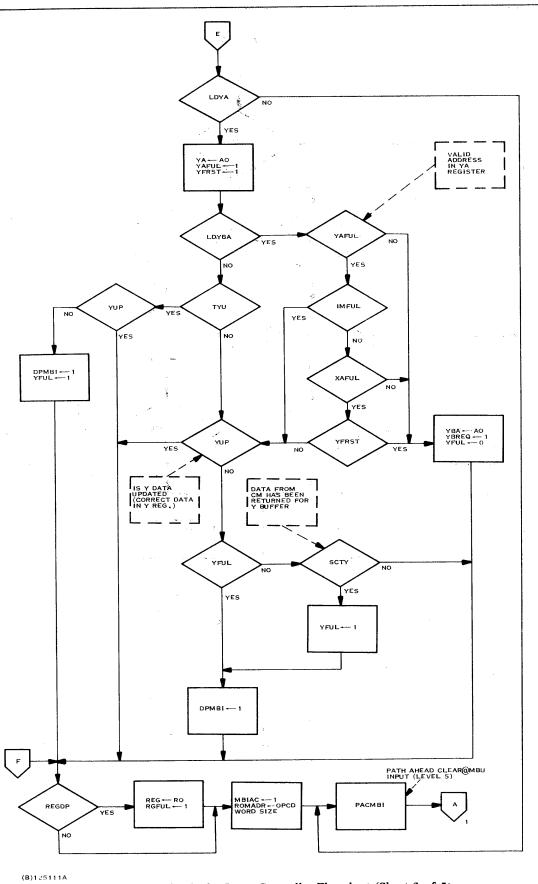

| 4-43   | Level 6 MBU Output Control Flowchart - Vector               | 4-184 |

| 4-44   | Level 6 ROM Address Selection Flowchart (Scalar and Vector) |       |

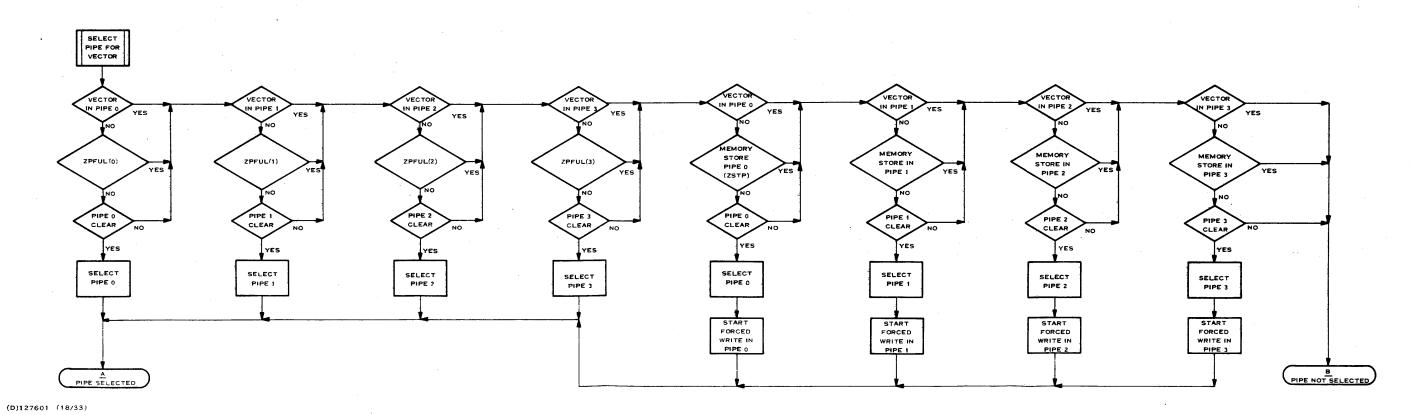

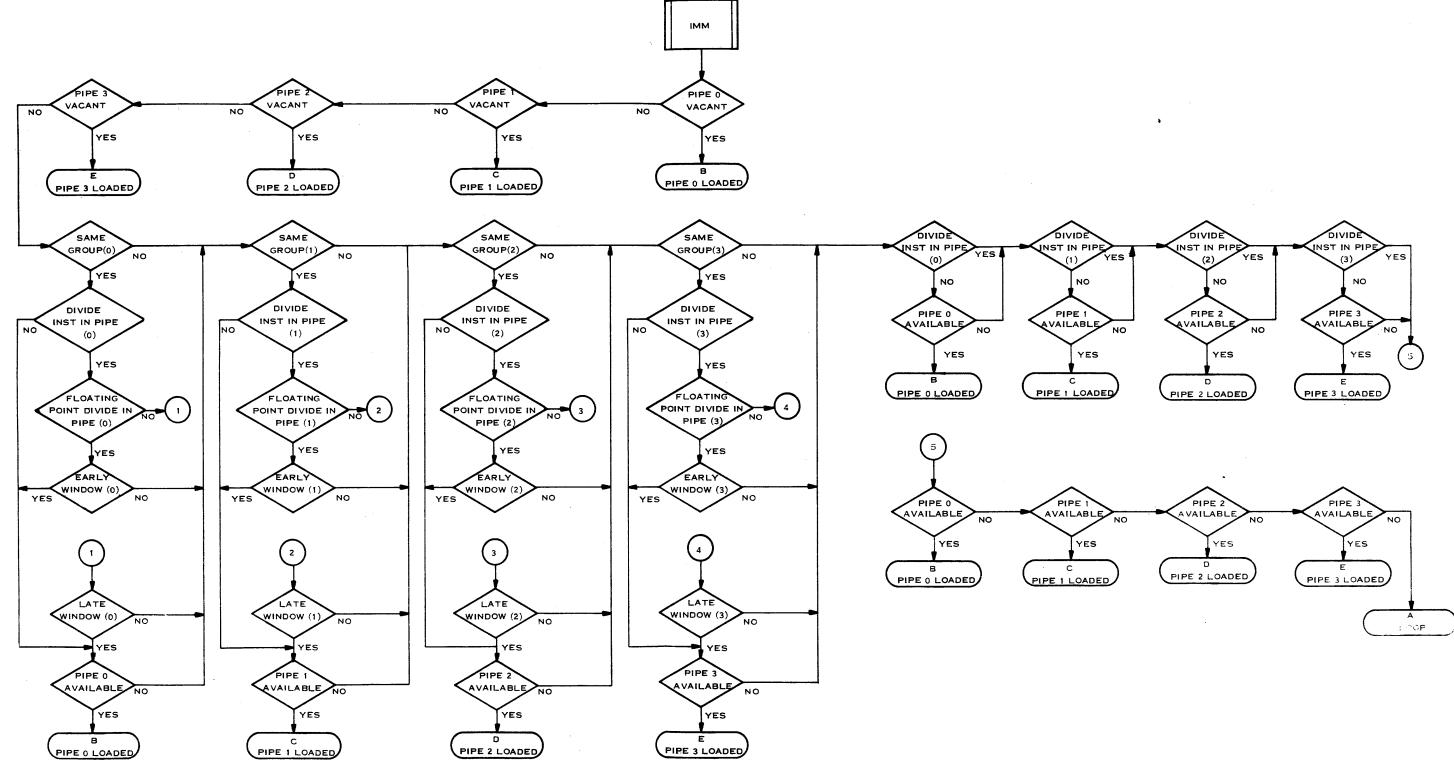

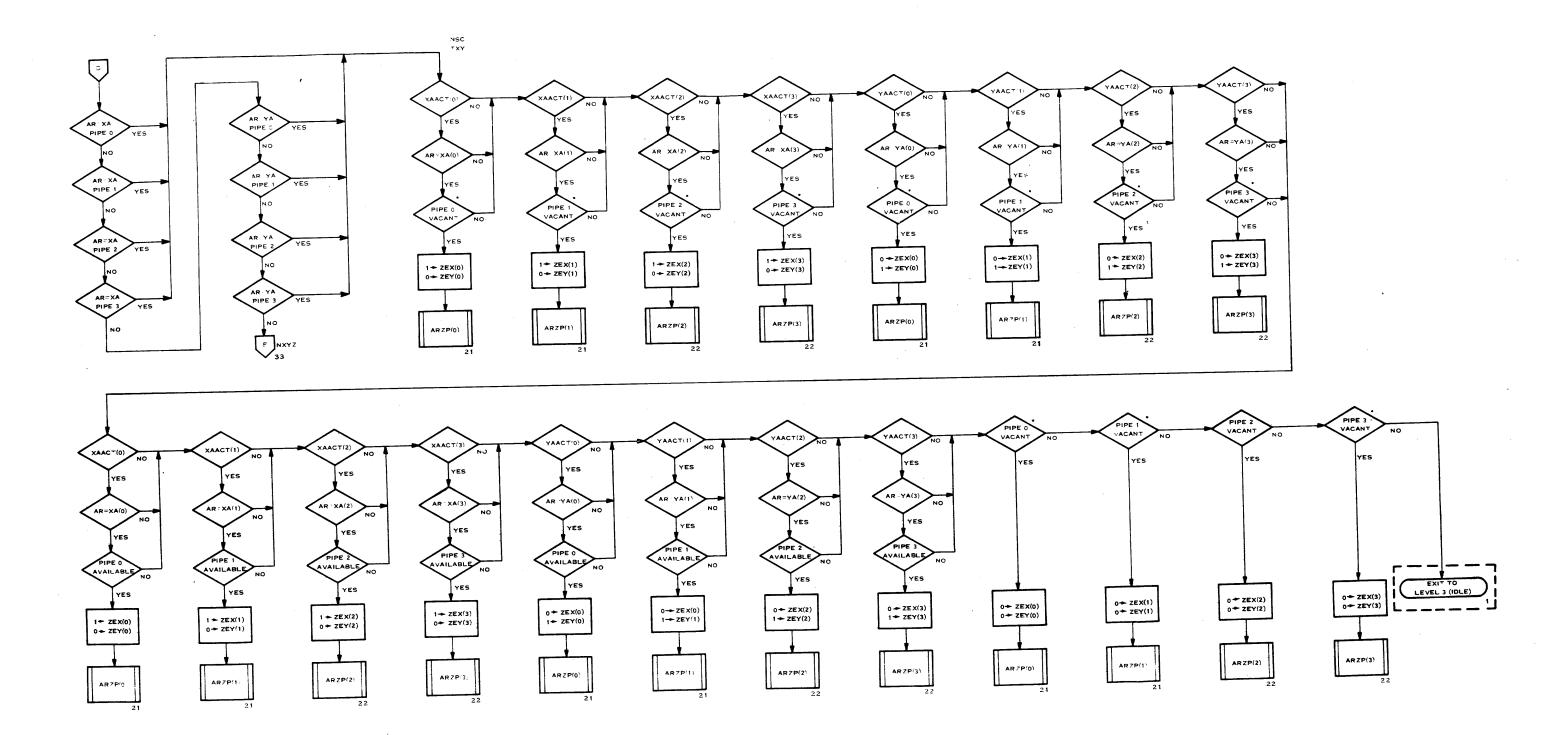

| 4-45   | Select Next Controller Flowchart                            |       |

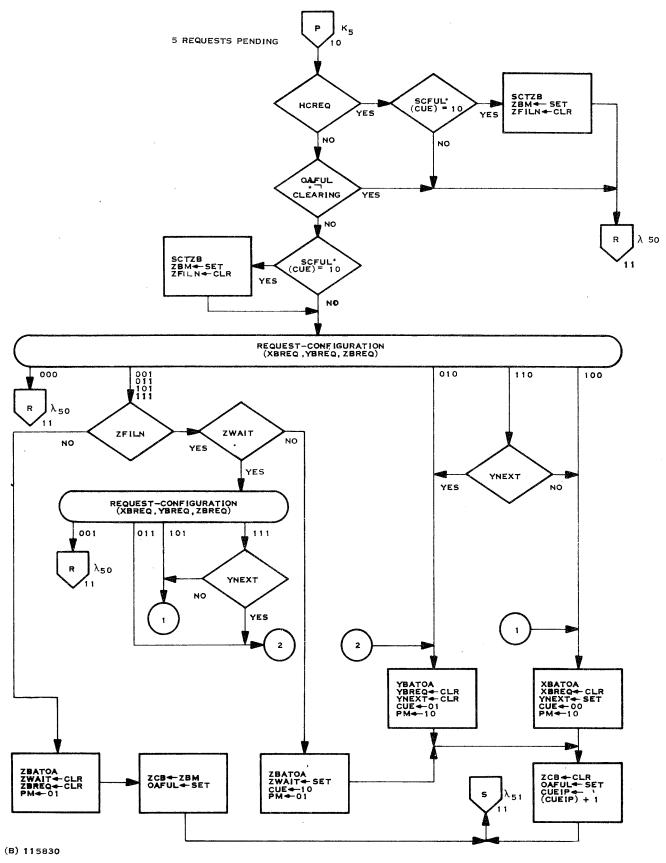

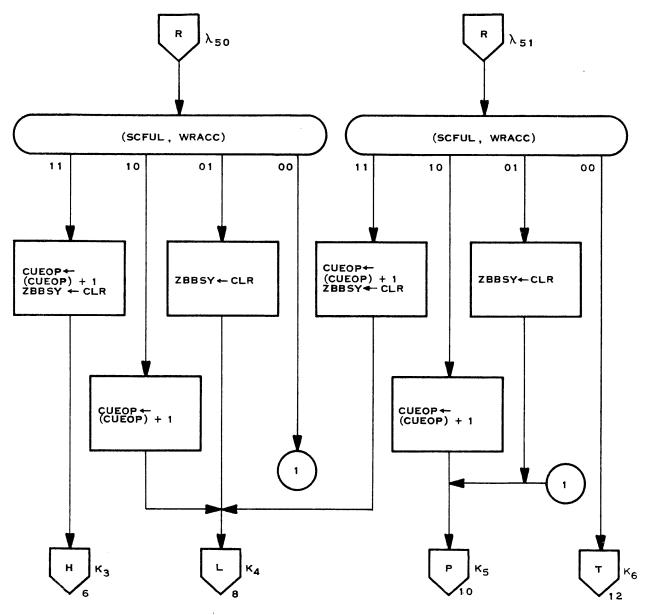

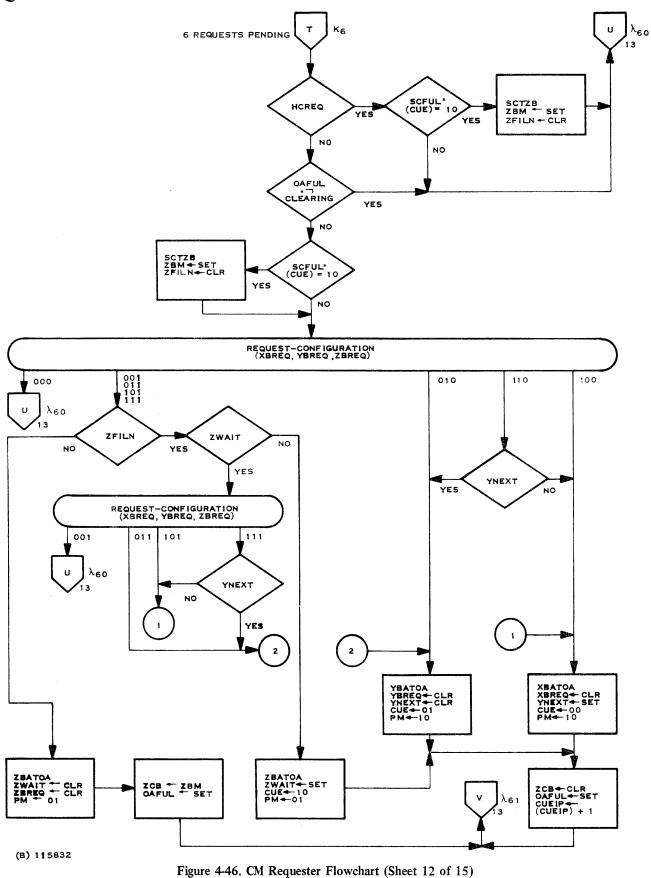

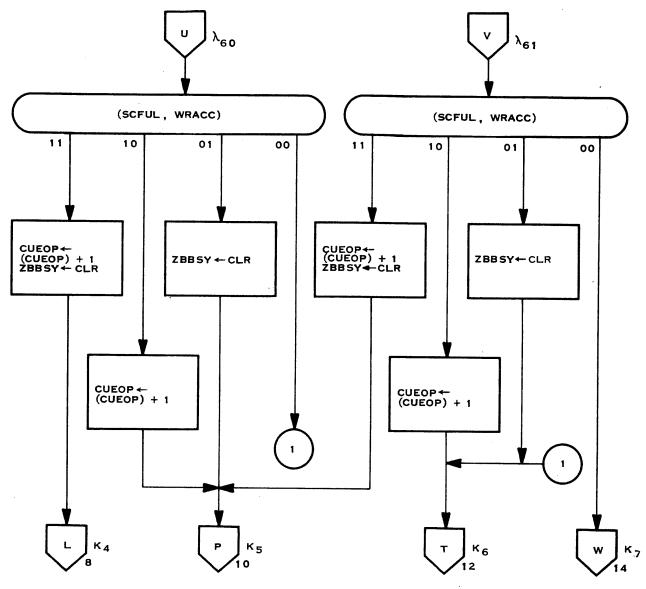

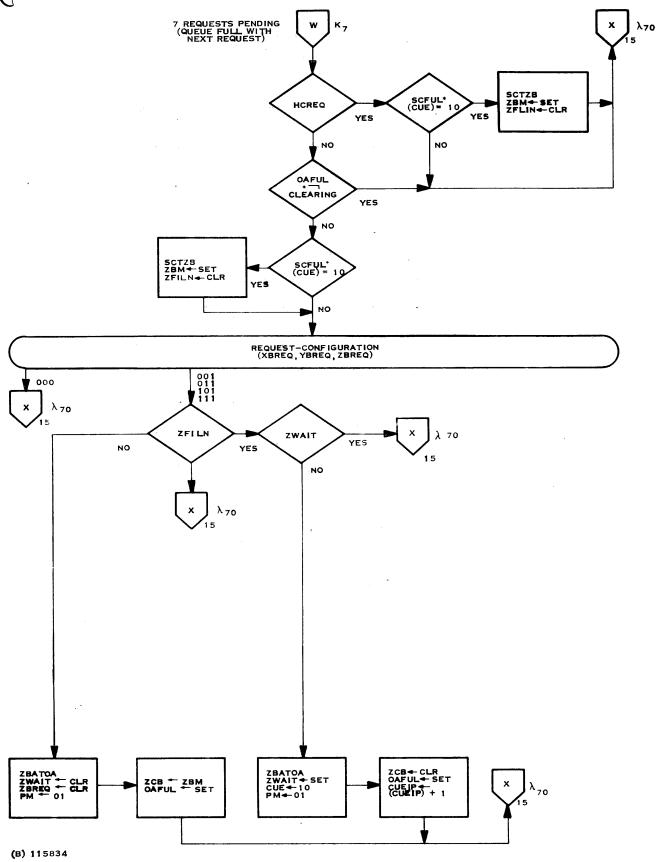

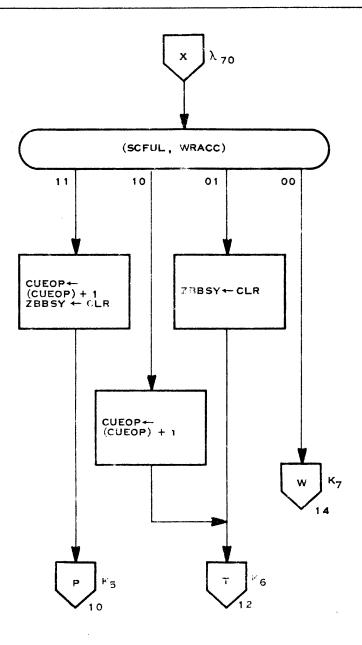

| 4-46   | CM Requester Flowchart                                      |       |

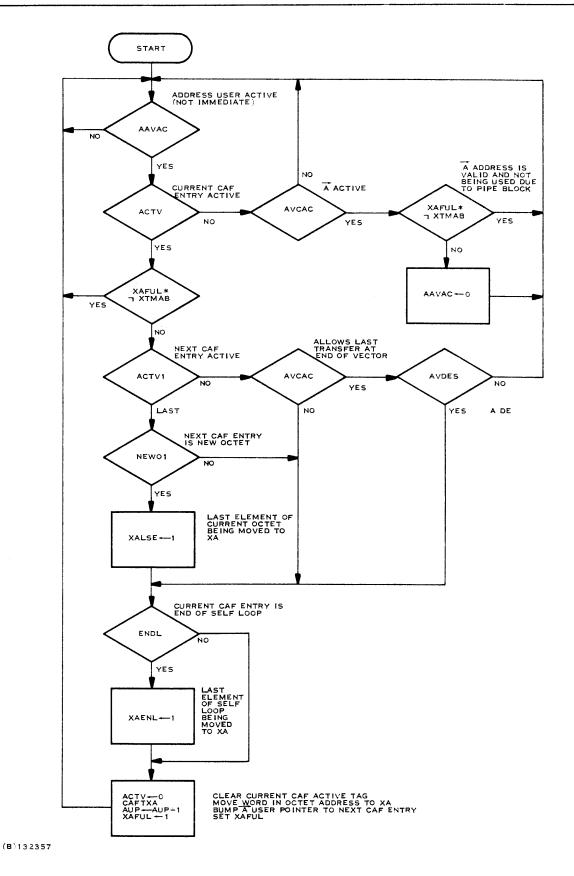

| 4-47   | CAF Output Control Flowchart                                | 4-210 |

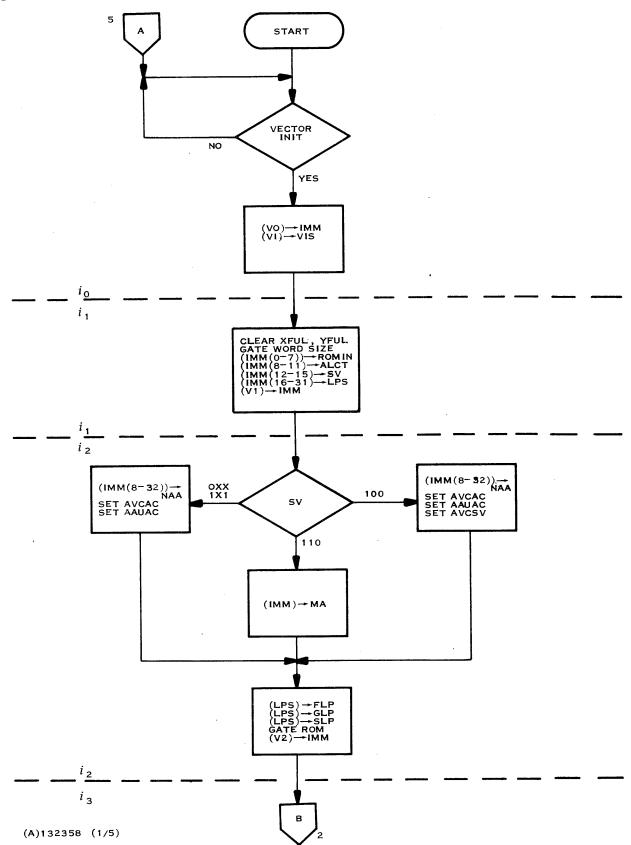

| 4-48   | Vector Initialization Control Flowchart                     |       |

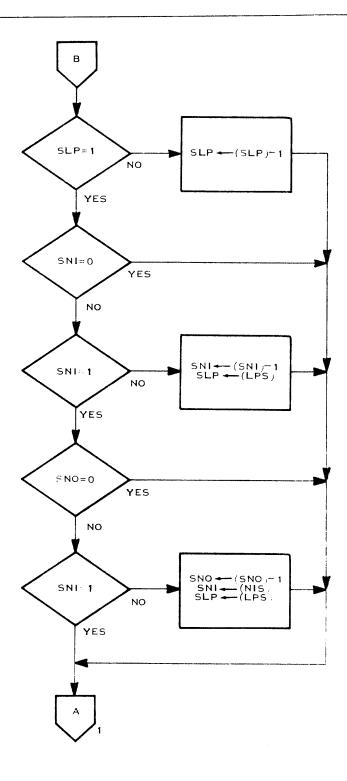

| 4-49   | A/B Vector Address Generation Flowchart                     | 4-216 |

| 4-50   | C Vector Address Generation Flowchart                       |       |

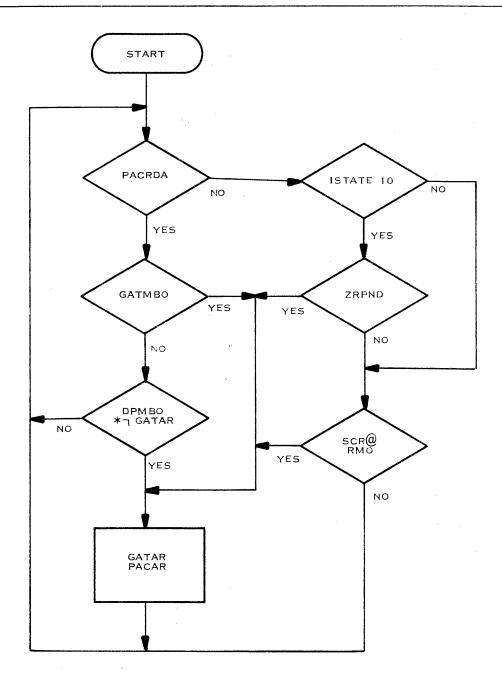

| 4-51   | AU Control - PACR Flowchart                                 |       |

| 4-52   | AU Control - CATAR Flowchart                                |       |

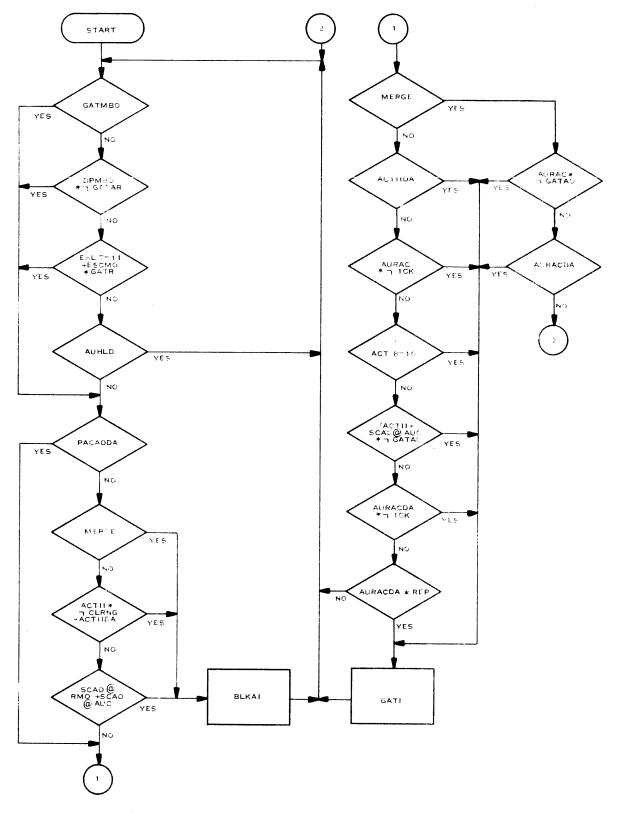

| 4-53   | AU Control - GATAI Flowchart                                |       |

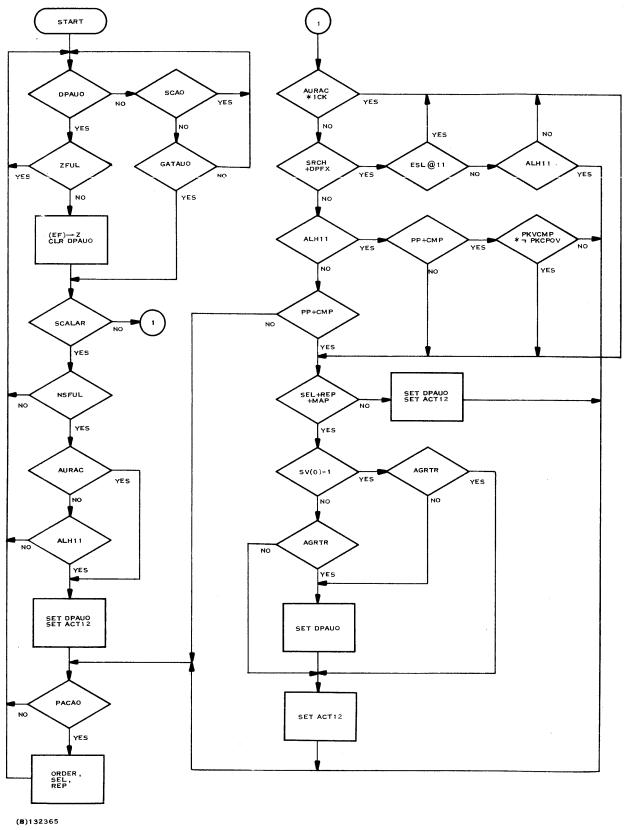

| 4-54   | AU Control - PCAUO Flowchart                                |       |

| 4-55   | AU Control - GATAO Flowchart                                |       |

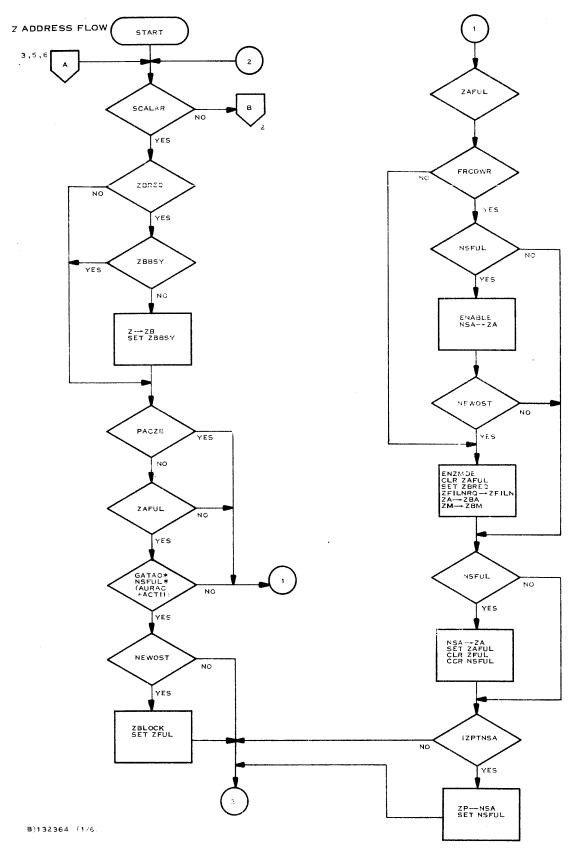

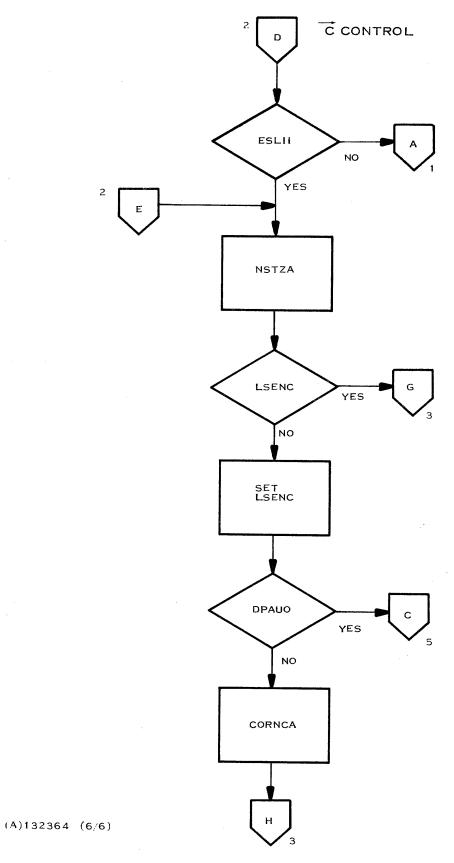

| 4-56   | Z Address Flow and $\overrightarrow{C}$ Control Flowchart   |       |

| 4-57   | Z Data Flow Flowchart                                       |       |

|        | LIST OF TABLES                                              |       |

| Table  | Title                                                       | Page  |

| 1-1    | Central Processor General Characteristics                   | 1-7   |

| 1-2    | Vector Instruction Set                                      |       |

| 1-3    | Scalar Instruction Set                                      |       |

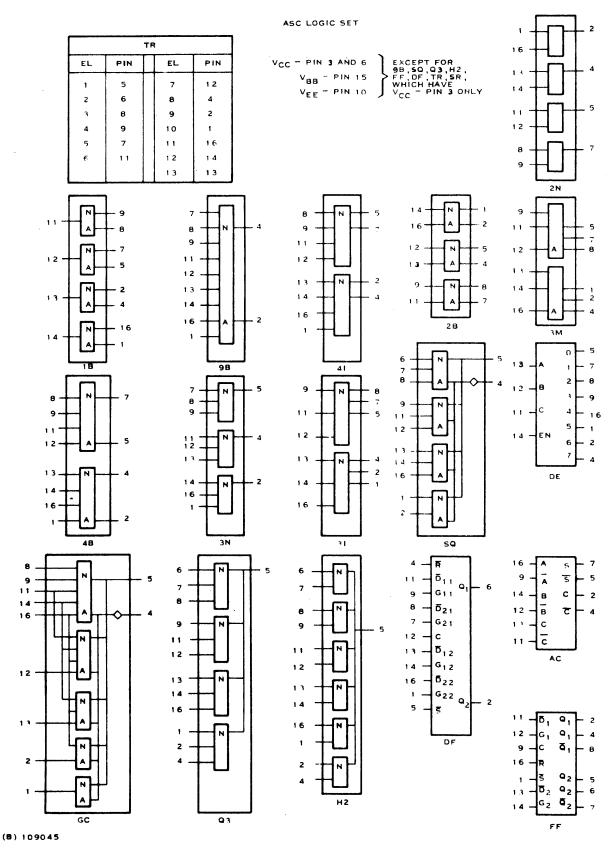

| 1-4    | ECL Circuit Types                                           |       |

| 4-1    | V-File Field Description                                    | 4-17  |

| 4-2    | CP Control Byte Bit Definitions                             | 4-29  |

| 4-3    | CP Response Bit Definitions                                 | 4-30  |

| 4-4    | CP Conditions Byte Bit Definitions                          |       |

| 4-5    | Recode Output Control Signal Definitions                    | 4-54  |

| 4-6    | Recode Circuit Data Analysis                                |       |

#### SECTION I

#### GENERAL DESCRIPTION

#### 1.1 GENERAL

This section describes the operation of the 4-Pipe Central Processor (CP) of the Texas Instruments Advanced Scientific Computer (ASC-4X). It includes a brief system overview of the ASC, a general functional block diagram description of the CP, a physical description of the CP, plus information about the instruction set and words used in the CP. Section 4 of this manual provides a detailed discussion of the CP theory of operation. Other useful charts and data are contained in the appendices of this manual. This manual applies to 4-pipe CP configurations only.

#### 1.2 PURPOSE

The ASC CP accesses program instructions from Central Memory, executes those instructions, and stores the results either within the CP or back into Central Memory. In performing this function, it also monitors program status to detect errors, branches and conflicts, and informs the Peripheral Processor if it is unable to continue a particular operation. The Peripheral Processor controls the selection of programs executed by the CP.

#### 1.3 ASC SYSTEM OVERVIEW

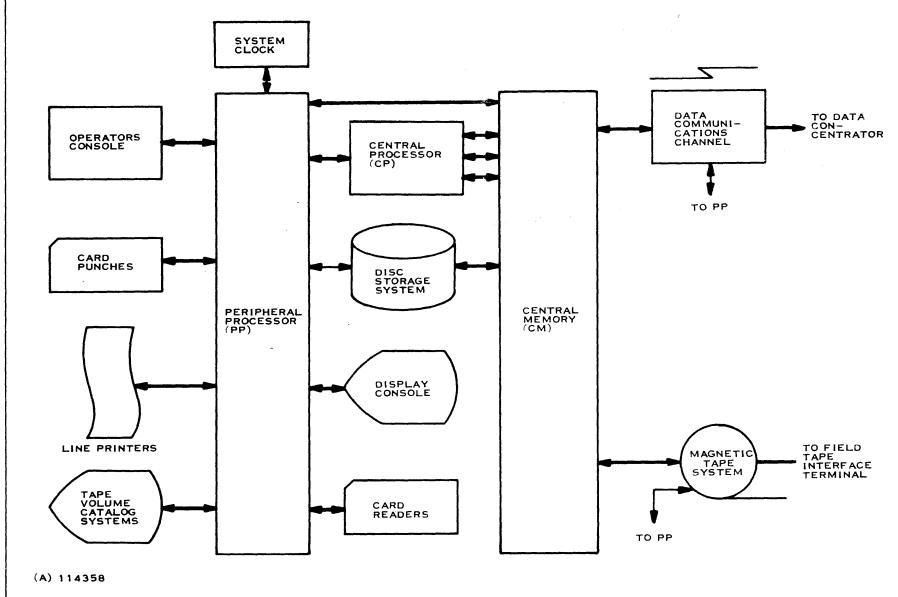

Besides the CP, the ASC includes the following major units:

- Peripheral Processor (PP)

- Central Memory System (CM)

- System Clock

- Disc Storage System

- Magnetic Tape System

- Data Communications Channel

- Paper Peripheral Channels

- Operators Console

- Display Console

- Power System

- Maintenance System.

The relationship of these components is shown in figure 1-1. The CP interfaces directly with Central Memory for instruction and operand fetching, as well as for maintenance purposes. Initial programming sequences are determined by the PP, which also controls CP reaction to certain status conditions and calls. The CP, however, executes programs under its own control.

Figure 1-1. ASC Simplified Block Diagram

#### 1.4 FUNCTIONAL DESCRIPTION

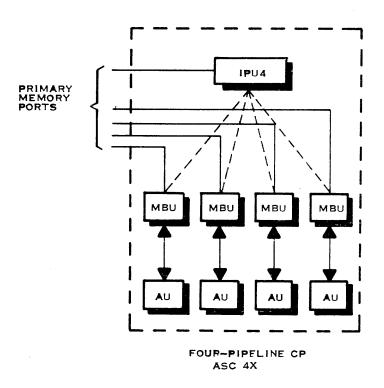

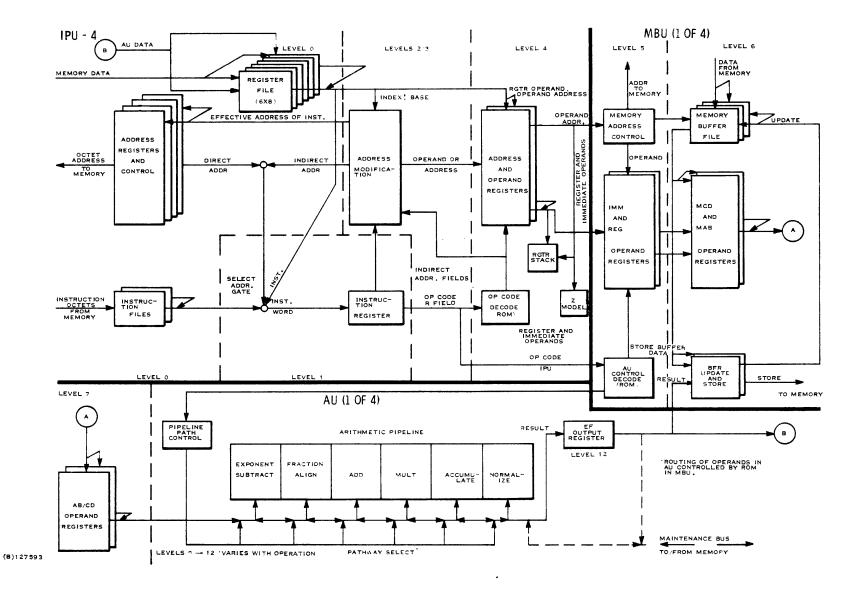

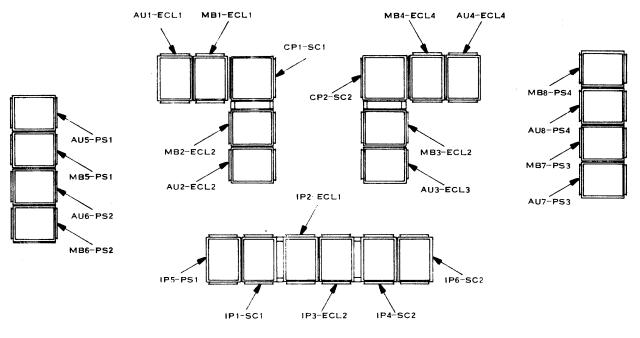

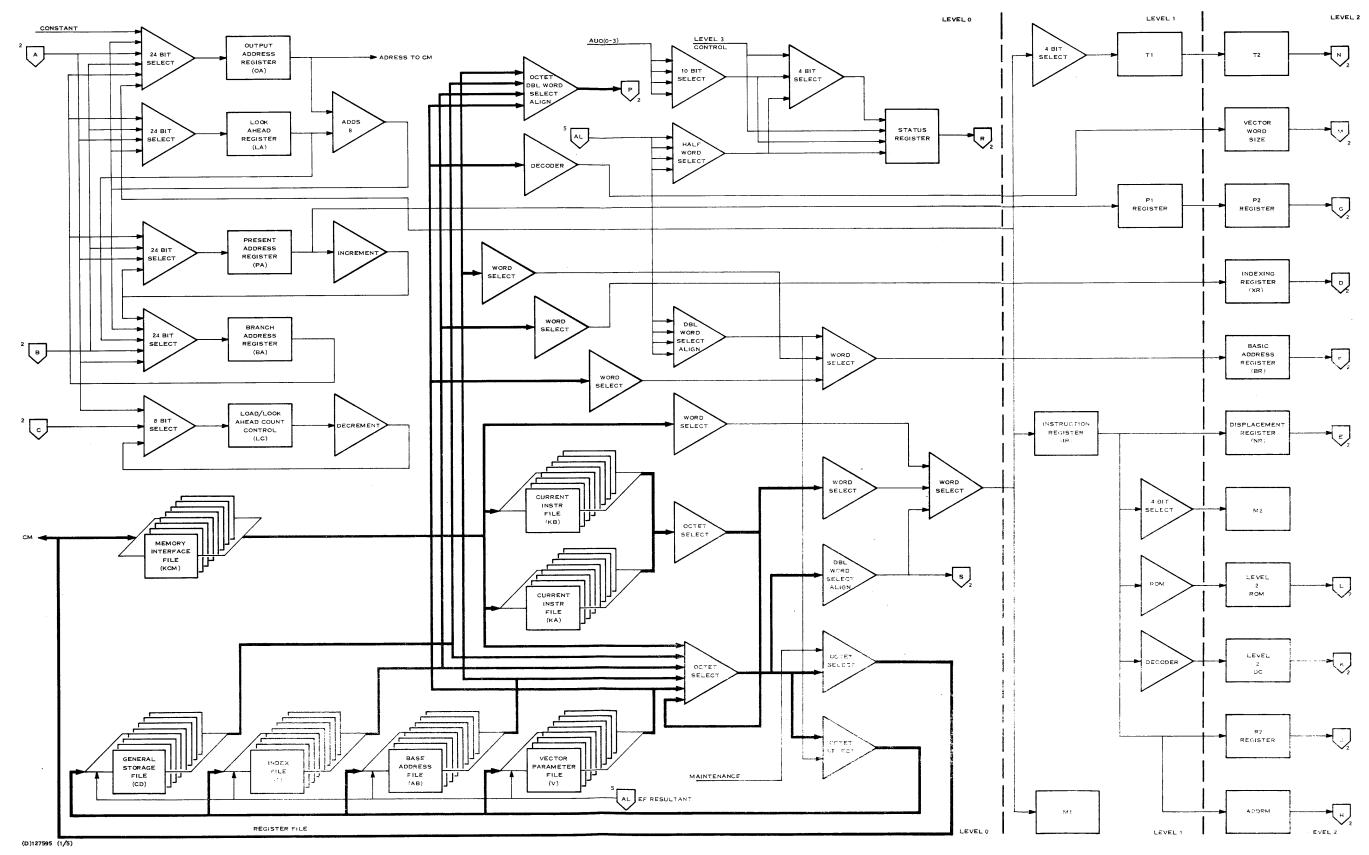

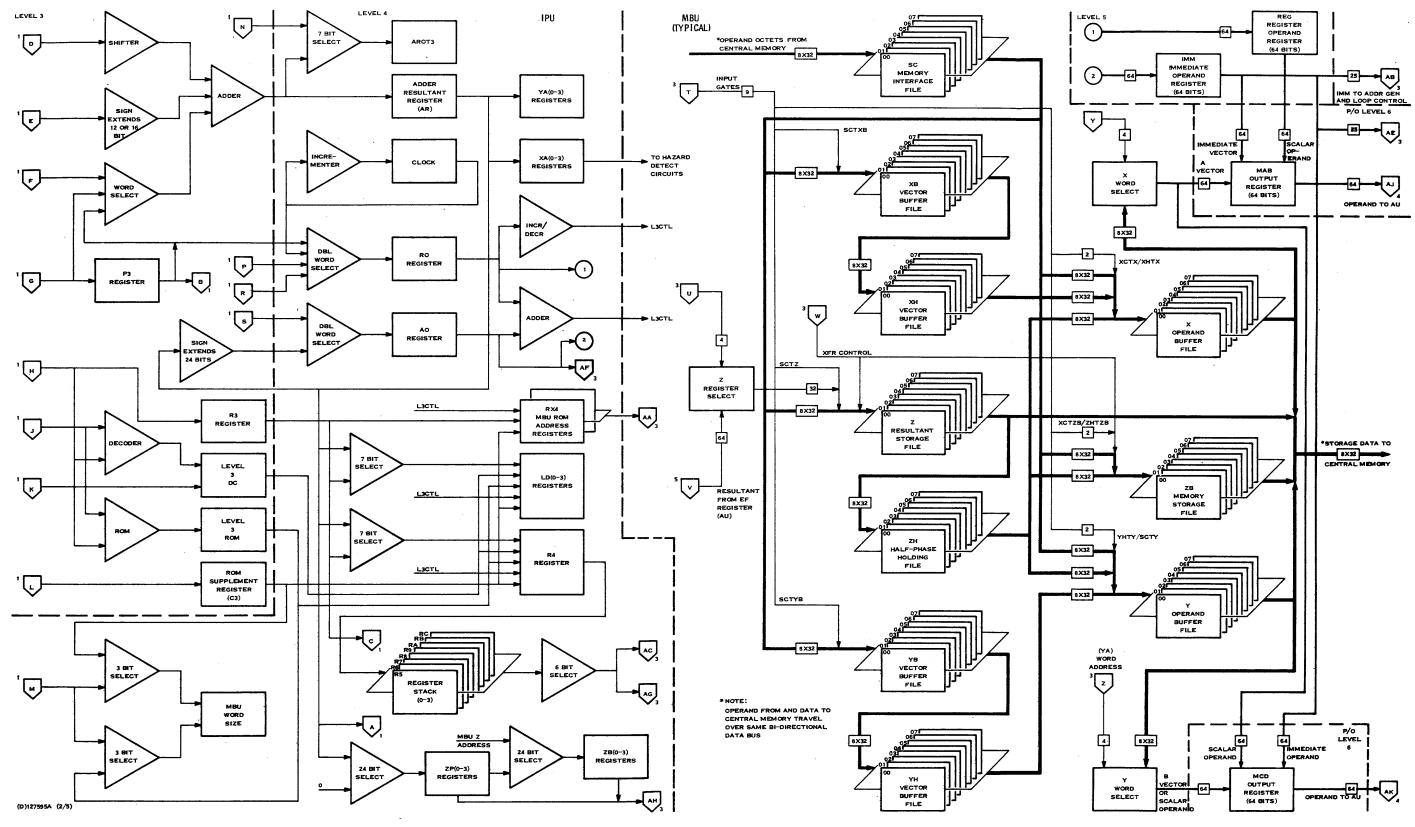

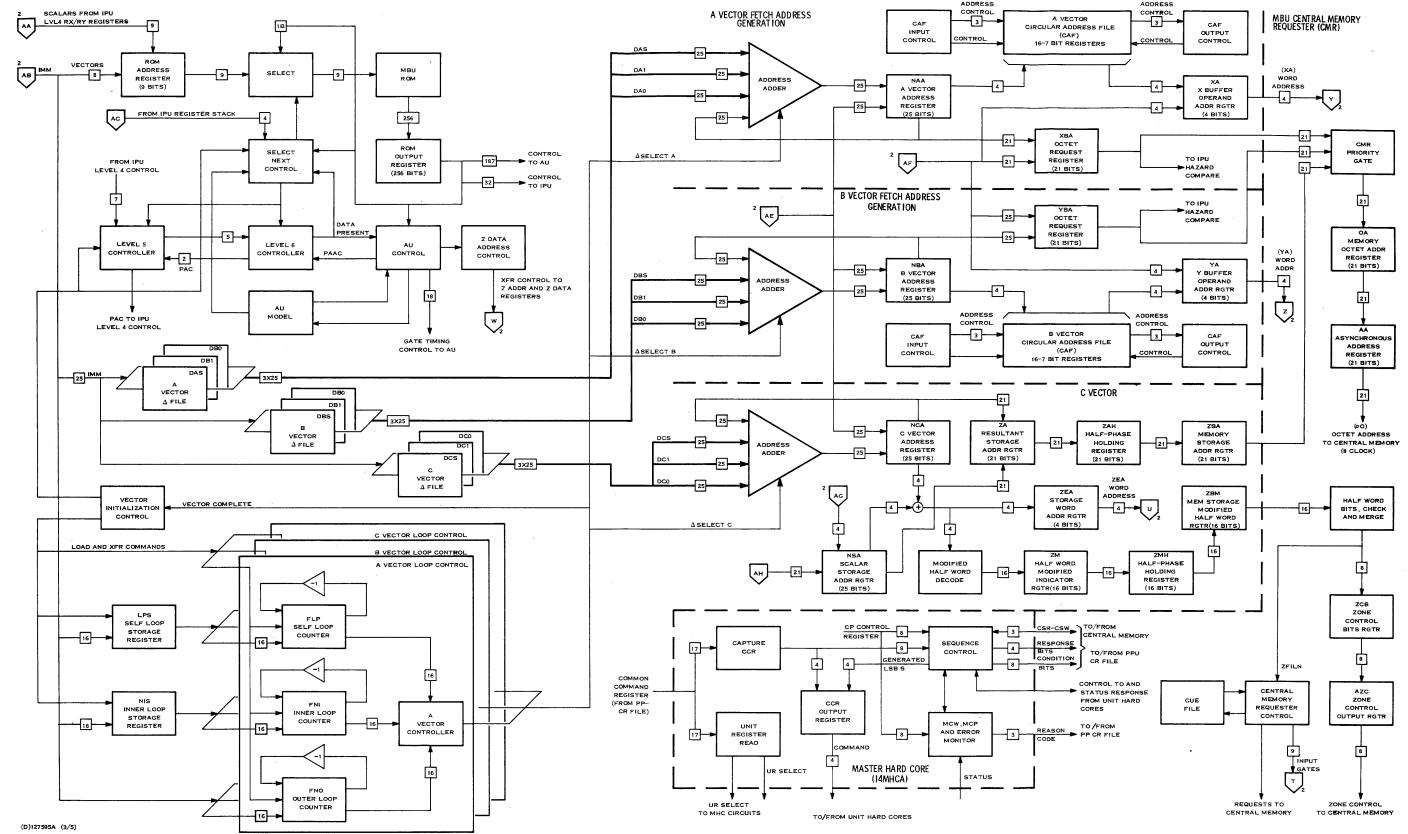

The ASC-4X Central Processor (4XCP) is comprised of nine units - one Instruction Processing Unit (IPU4) to process the CP commands, four Memory Buffer Units (MBU's) to provide central memory operands, and four Arithmetic Units (AU's) to perform the specified arithmetic operations. The structuring of these units is shown in figure 1-2. Figure 1-3 is a block diagram of the 4XCP.

The 4XCP provides four parallel execution pipelines below the IPU. Any mixture of scalar or vector instructions may be in execution simultaneously in the four pipes. In any of the CP configurations, the interaction between an IPU, MBU, and AU is equivalent to that of one pipeline. The flow of data is from the IPU to the MBU, from the MBU to the AU, and then from the AU back to the MBU for stores to memory or back to the IPU for arithmetic results to the register file. The IPU performs all decisions pertaining to the routing of instructions to various pipes. MBU's and AU's are not aware of other MBU-AU pairs.

In the multiple-pipeline CP's, each MBU has its own dedicated memory port. The times-four CP, for example, uses five memory ports; one for the IPU4 and four for the MBU's. The AU details information is loaded from or stored into memory only during maintenance commands and context switching. AU memory requests, therefore, occur infrequently and are routed through an expander cascaded on another expander.

Figure 1-2. 4XCP Unit Structure

Figure 1-3. Central Processor Block Diagram

- 1.4.1 ADDRESS REGISTERS AND CONTROL. Four address registers control the acquisition of instruction word octets (8-word groups) from Central Memory. These registers select the proper instruction word for processing, call up a new octet while the current one is being processed, and provide for branch address acquisition. During indirect addressing, the output of the Address Modification network updates the Output Address Register in this circuit for each new address developed by the network until the terminal effective address is reached. The other registers maintain the program address so that the program resumes when the effective address is reached.

- 1.4.2 REGISTER FILE. The Register File is a memory source contained within the IPU. These registers are loaded by program instructions with data from either memory or the AU output. The file consists of six sets of eight 32-bit register (six octets). Each area in the file has a primary function, such as base addresses for developing effective addresses (15 words), general arithmetic use (16 words), seven index registers, and eight vector parameter registers to define the scope of a specific vector instruction. They may, however, be used for other processes.

- 1.4.3 INSTRUCTION FILES. Two instruction files, each containing one octet (eight words), supply a continuous source of instructions to the Instruction Register. The Address Registers and Control block controls loading and selection from these registers. It first loads one file and begins drawing instructions from the octet in that file. Address Control then loads the second file while the first one empties. Consecutive addresses supply a smooth transition from one file to the next. During indirect addressing, the effective address of an instruction from the Address Modification block selects the output from the instruction files if the address is currently in the files.

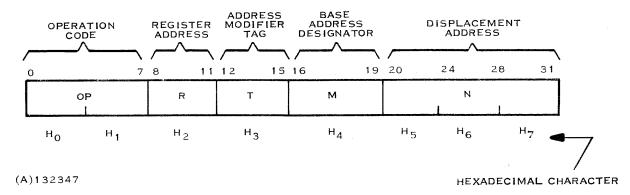

- 1.4.4 INSTRUCTION REGISTER. The Instruction Register receives the selected word from the instruction file and holds it for processing. Depending on the instruction format, the register may contain address bits, address modifiers, and operand and/or an operation code. The register output drives instruction decode and address generation networks.

- 1.4.5 ADDRESS MODIFICATION. When the Instruction Register specifies either direct or indexed addressing, the Address Modification block performs the operations required to generate a new address. This block provides for base address (from Register File) plus displacement modification and/or additional of the contents of one of the seven index registers in the Register File. The circuit permits direct or indirect addressing with or without modification, or the development of an immediate operand. Operands, direct operand addresses, and terminal operand addresses transfer to the MBU's to provide operands for the AU's. If an indirect address develops, it returns to the Output Address Register to retrieve a new instruction word for further address generation. The modification hardware includes input registers for indexing, base address and displacement, an adder, plus a result holding and output register.

- 1.4.6 ADDRESS AND OPERAND REGISTERS. These two registers are the IPU output register. They provide each MBU (according to pre-determined priorities) with either two operands, one operand and an operand address, or just one address.

- 1.4.7 IMM/REG REGISTERS. The Immediate (IMM) and Register (REG) Operand Registers receive operands from the IPU. During vector initialization, the IMM Register also transmits the vector parameters to the MBU Registers to set up the beginning vector conditions. Once a vector operation begins, neither of these registers is used until the next operation begins. Control signals, generated within the MBU, transfer data that is in these registers to the output registers of the MBU during scalar operations.

- 1.4.8 MEMORY ADDRESS CONTROL. This circuit supplies addresses to memory for storing results from the AU vector and store operations and for accessing new operand octets from memory for input to the AU. During scalar operations, operand addresses are supplied from the IPU. If the desired operand is already in the Memory Buffer File, the IPU sends only a 4-bit address to select the output from one of the file registers. If the operand is not in the buffer file, the IPU sends a full 21-bit address to fetch the octet containing the operand from Central Memory and loads it into the buffer file before transferring the operand to the output register. During vector operations, Memory Address Control generates the address of each octet in the vector after the address is initially loaded by the IPU.

- 1.4.9 MEMORY BUFFER FILE. The Memory Buffer File consists of six octet buffers plus an octet receiver/synchronizer register. The buffers are arranged in two three-stage buffers with the output of the final stage available to the output registers. Inputs to the buffers may enter the final file to bypass the delay in the buffering sequence. During scalar operations, Memory Address Control can select the output from either buffer and transfer it to the MCD Operand Register. During vector operations each buffer set supplies a stream of operands to one of the MAB/MCD Operand Registers. Either buffer set may be modified by the result output from the Arithmetic Pipeline (update) during scalars.

- 1.4.10 MAB/MCD OPERAND REGISTERS. These registers supply two operands simultaneously to the AU for processing. The MAB Register receives registers operands from the REG Register during scalar operations, and vector operands from the buffer file during vector operations. The MCD Register receives either immediate operands from the IMM Register or operands from either set of the buffer file during scalar operations. During vector operations the buffer file supplies a stream of operands to the MCD Register.

- 1.4.11 AU CONTROL DECODE. The AU Control Decode is a Read Only Memory (ROM) that designates to the AU which processes must be performed to accomplish the function specified by the Op Code. The decode circuit also supplies control signals to aid in selection of operands for the MAB/MCD registers.

- 1.4.12 BUFFER UPDATE AND STORE. The buffer update provides temporary retention of an octet of AU output. This octet may change the contents of the buffer file, or may be stored into Central Memory when the AU begins to produce results for a new octet.

- 1.4.13 AB/CD OPERAND REGISTERS. These registers are the input phase to the arithmetic pipeline. They receive two operands from the MBU and transfer them to the pipeline when the pipeline segment that performs the first operational step becomes available. Other inputs to these registers come from within the AU to provide a feedback path.

- 1.4.14 PIPELINE PATH CONTROL. This circuit follows the directions of the AU Control ROM in the MBU to perform the gating and sequencing functions required to develop a complete process in the pipeline.

- 1.4.15 ARITHMETIC PIPELINE. The Arithmetic Pipeline is a segmented arithmetic processor whose sequence is determined by the MBU ROM signals. Six segments of the pipe perform independent operations on up to six different sets of operands simultaneously. Each segment is a basic function that, combined in a specific order with other segments, performs arithmetic operations from scalar addition to complex vector operations on both fixed and floating point operands.

1.4.16 EF OUTPUT REGISTER. The EF Output Register receives a result from any segment of the pipeline, except the multiplication segment (output of multiplier is two partial products that must be added to produce a result). The output of this register may return to the Register File in the IPU (scalar operations), may update the data in the Memory Buffer File, or may be stored in memory (vectors and store operations).

#### 1.5 GENERAL CHARACTERISTICS

Table 1-1 lists some of the general characteristics of the ASC Central Processor.

#### 1.6 CP INSTRUCTION SET

The ASC Central Processor performs scalar and vector operations through a powerful array of instructions. The instruction set includes Load and Store functions, arithmetic scalar operations, scalar logical instructions, and branching capabilities. Two special instructions, VECT and VECTL, expand the ASC instructions into the vector mode by loading a new set of parameters into the IPU from the Vector Parameter File. The set of vector parameters includes a vector operation code. The function of the vector operation is defined by an additional set of vector instructions that can be loaded only through this vector mode. Table 1-2 lists the instructions in the normal ASC instruction set with their mnemonic code and operation code; figure 1-4 supplies a mapping of scalar Op Codes. Table 1-3 and figure 1-5 contain similar information for the vector mode instructions. Refer to the ASC programming manuals for a more detailed explanation of the uses of each instruction.

Table 1-1. Central Processor General Characteristics

| Item                            | Characteristic                                                                                        |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Construction                    | Layered pipeline                                                                                      |  |  |  |  |

| Word Size                       | 16 bits (halfword) 32 bits (singleword) 64 bits (doubleword) -fixed point only -fixed point only      |  |  |  |  |

| Instruction word size           | 32 bits (8 Op Code, 4 R-field, 4 T-field, 4 M-field, 12 N-field)                                      |  |  |  |  |

| Memory address size:            |                                                                                                       |  |  |  |  |

| Octet<br>Word                   | 21 bits (sent to CM) 24 bits (internal to CP)                                                         |  |  |  |  |

| Memory transfer size            | 1 octet (256 bits)                                                                                    |  |  |  |  |

| Number of memory paths          | 9: 1-IPU (instruction fetch), 4-MBU's (operand fetch/store) 4-AU's (maintenance - Load/Store Details) |  |  |  |  |

| Operation Modes                 | 2: Scalar and Vector                                                                                  |  |  |  |  |

| Control:                        |                                                                                                       |  |  |  |  |

| Initiate/Terminate<br>Operating | Through CR File in the Peripheral Processor Individual pipe level controllers in CP                   |  |  |  |  |

| CP Clock Period                 | 65 nanoseconds                                                                                        |  |  |  |  |

Table 1-2. Vector Instruction Set

| ASSMB<br>CODE | MCHN<br>CODE | INSTRUCTION                                                        |

|---------------|--------------|--------------------------------------------------------------------|

| VA            | 40           | Vector add, fixed point singleword                                 |

| VAF           | 42           | Vector add, floating point singleword                              |

| VAFD          | 43           | Vector add, floating point doubleword                              |

| VAH           | 41           | Vector add, fixed point halfword                                   |

| VAM           | 44           | Vector add magnitude, fixed point singleword                       |

| VAMF          | 46           | Vector add magnitude, floating point singleword                    |

| VAMFD         | 47           | Vector add magnitude, floating point doubleword                    |

| VAMH          | 45           | Vector add magnitude, fixed point singleword                       |

| VAND          | EO           | Vector logical AND, singleword                                     |

| VANDD         | E1           | Vector logical AND, doubleword                                     |

| VC            | D0           | Vector arithmetic comparison, fixed point singleword               |

| VCAB          | EA           | Vector compare AND singleword boolean                              |

| VCADB         | EB           | Vector compare AND doubleword boolean                              |

| VCAND         | E2           | Vector logical comparison using AND, singleword                    |

| VCANDD        | E3           | Vector logical comparison using AND, doubleword                    |

| VCB           | F0           | Vector compare fixed point singleword boolean                      |

| VCF           | D2           | Vector arithmetic comparison, floating point singleword            |

| VCFB          | F2           | Vector compare floating point singleword boolean                   |

| VCFD          | D3           | Vector arithmetic comparison, floating point doubleword            |

| VCFDB         | F3           | Vector compare floating point doubleword boolean                   |

| VCH           | D1           | Vector arithmetic comparison, fixed point halfword                 |

| VCHB          | F1           | Vector compare fixed point halfword boolean                        |

| VCOR          | E6           | Vector logical comparison using OR, singleword                     |

| VCORB         | EE           | Vector compare OR singleword boolean                               |

| VCORD         | E7           | Vector logical comparison using OR, doubleword                     |

| VCORDB        | EF           | Vector compare OR doubleword boolean                               |

| VD            | 64           | Vector divide fixed point, singleword                              |

| VDF           | 66           | Vector divide floating point, singleword                           |

| VDFD          | 67           | Vector divide floating point, doubleword                           |

| VDH           | 65           | Vector divide fixed point, halfword                                |

| VDP           | 68           | Vector dot product, fixed point singleword                         |

| VDPF          | 6 <b>A</b>   | Vector dot product, floating point singleword                      |

| VDPFD         | 6B           | Vector dot product, floating point doubleword                      |

| VDPH          | 69           | Vector dot product, fixed point halfword                           |

| VEQC          | EC           | Vector logical Equivalence, singleword                             |

| VEQCD         | ED           | Vector logical Equivalence, doubleword                             |

| VFDFX         | A2           | Vector convert floating point doubleword to fixed point singleword |

Table 1-2. Vector Instruction Set (Continued)

| ASSMB<br>CODE | MCHN<br>CODE | INSTRUCTION                                                             |

|---------------|--------------|-------------------------------------------------------------------------|

| VFHFD         | AB           | Vector convert fixed point halfword to floating point doubleword        |

| VFHFL         | A9           | Vector convert fixed point half length to floating point singleword     |

| VFLFH         | <b>A</b> 1   | Vector convert floating point singleword to fixed point halfword        |

| VFLFX         | A0           | Vector convert floating point singleword to fixed point singleword      |

| VFXFD         | AA           | Vector convert fixed point singleword to fixed point doubleword         |

| VFXFL         | <b>A</b> 8   | Vector convert fixed point singleword to floating point singleword      |

| VL            | 50           | Vector search for largest arithmetic element, fixed point singleword    |

| VLF           | 52           | Vector search for largest arithmetic element floating point singleword  |

| VLFD          | 53           | Vector search for largest arithmetic element, floating point doubleword |

| VLH           | 51           | Vector search for largest arithmetic element, fixed point halfword      |

| VLM           | 54           | Vector search for largest magnitude, fixed point singleword             |

| VLMF          | 56           | Vector search for largest magnitude, floating point singleword          |

| VLMFD         | 57           | Vector search for largest magnitude, floating point doubleword          |

| VLMH          | 55           | Vector search for largest magitude, fixed point half-word               |

| VM            | 6C           | Vector multiply, fixed point singleword                                 |

| VMAP          | F8           | Vector map singleword                                                   |

| VMAPB         | FC           | Vector map singleword boolean                                           |

| VMAPD         | FB           | Vector map doubleword                                                   |

| VMAPDB        | FF           | Vector map doubleword boolean                                           |

| VMAPH         | F9           | Vector map halfword                                                     |

| VMAPHB        | FD           | Vector map halfword boolean                                             |

| VMAX          | F4           | Vector maximum/minimum fixed point singleword                           |

| VMAXF         | F6           | Vector maximum/minimum floating point singleword                        |

| VMAXFD        | F7           | Vector maximum/minimum floating point doubleword                        |

| VMAXH         | F5           | Vector maximum/minimum fixed point halfword                             |

| VMF           | 6E           | Vector multiply, floating point singleword                              |

| VMFD          | 6F           | Vector multiply, floating point doubleword                              |

Table 1-2. Vector Instruction Set (Continued)

| ASSMB<br>CODE | MCHN<br>CODE | INSTRUCTION                                         |

|---------------|--------------|-----------------------------------------------------|

| VMG           | D8           | Vector merge singlewords                            |

| VMGD          | DB           | Vector merge doublewords                            |

| VMGH          | <b>D</b> 9   | Vector merge halfwords                              |

| VMH           | 6D           | Vector multiply, fixed point halfword               |

| VNFH          | AD           | Vector normalize fixed point halfword               |

| VNFX          | AC           | Vector normalize fixed point singleword             |

| VO            | D4           | Vector order singlewords, fixed point               |

| VOF           | D6           | Vector order singlewords, floating point            |

| VOFD          | D7           | Vector order doublewords, floating point            |

| VOH           | D5           | Vector order halfwords, fixed point                 |

| VOR           | E4           | Vector logical OR, singleword                       |

| VORD          | E5           | Vector logical OR, doubleword                       |

| VPP           | DC           | Vector peak, fixed point singleword                 |

| VPPF          | DE           | Vector peak, floating point singleword              |

| VPPFD         | DF           | Vector peak, floating point doubleword              |

| VPPH          | DD           | Vector peak, fixed point halfword                   |

| VREP          | B8           | Replace singlewords in vector $\overrightarrow{C}$  |

| VREPB         | BC           | Vector replace singleword boolean                   |

| VREPD         | BB           | Replace doublewords in vector $\overrightarrow{C}$  |

| VREPDB        | BF           | Vector replace doubleword boolean                   |

| VREPH         | <b>B</b> 9   | Replace halfwords in vector $\overrightarrow{C}$    |

| VREPHB        | BD           | Vector replace halfword boolean                     |

| VS            | 48           | Vector subtract, fixed point singleword             |

| VSA           | CO           | Vector arithmetic shift, fixed point singleword     |

| VSAD          | С3           | Vector arithmetic shift, fixed point doubleword     |

| VSAH          | C1           | Vector arithmetic shift, fixed point halfword       |

| VSC           | CC           | Vector circular shift, singleword                   |

| VSCD          | CF           | Vector circular shift, doubleword                   |

| VSCH          | CD           | Vector circular shift, halfword                     |

| VSEL          | В0           | Select singlewords from vector $\overrightarrow{B}$ |

| VSELB         | B4           | Vector select singleword boolean                    |

| VSELD         | В3           | Select doublewords from vector $\overrightarrow{B}$ |

| VSELDB        | B7           | Vector select doubleword boolean                    |

| VSELH         | <b>B</b> 1   | Select halfwords from vector $\overrightarrow{B}$   |

| VSELHB        | <b>B</b> 5   | Vector select halfword boolean                      |

| VSF           | 4 <b>A</b>   | Vector subtract, floating point singleword          |

| VSFD          | 4B           | Vector subtract, floating point doubleword          |

| VSH           | 49           | Vector subtract, fixed point halfword               |

Table 1-2. Vector Instruction Set (Continued)

| ASSMB<br>CODE | MCHN<br>CODE | INSTRUCTION                                                              |

|---------------|--------------|--------------------------------------------------------------------------|

| VSL           | C4           | Vector logic shift, singleword                                           |

| VSLD          | C7           | Vector logical shift, doubleword                                         |

| VSLH          | C5           | Vector logical shift, halfword                                           |

| VSM           | 4C           | Vector subtract magnitude, fixed point singleword                        |

| VSMF          | 4E           | Vector subtract magnitude, floating point singleword                     |

| VSMFD         | 4F           | Vector subtract magnitude, floating point doubleword                     |

| VSMH          | 4D           | Vector subtract magnitude, fixed point halfword                          |

| VSS           | 58           | Vector search for smallest arithmetic element, fixed point singleword    |

| VSSF          | 5 <b>A</b>   | Vector search for smallest arithmetic element, floating point singleword |

| VSSFD         | 5B           | Vector search for smallest arithmetic element, floating point doubleword |

| VSSH          | 59           | Vector search for smallest arithmetic element, fixed point halfword      |

| VSSM          | 5C           | Vector search for smallest magnitude, fixed point singleword             |

| VSSMF         | 5E           | Vector search for smallest magnitude, floating point singleword          |

| VSSNFD        | 5F           | Vector search for smallest magnitude, floating point doubleword          |

| VSSMН         | 5D           | Vector search for smallest magnitude, fixed point half-word              |

| VXOR          | E8 -         | Vector logical Exclusive OR, singleword                                  |

| VXORD         | E9           | Vector logical Exclusive OR, doubleword                                  |

OP BITS 4-7

OP BITS 0-3

| _ | OF BITS 0 3 |     |     |      |      |            |     |     |     |      |      |      |      |     |     |       |       |

|---|-------------|-----|-----|------|------|------------|-----|-----|-----|------|------|------|------|-----|-----|-------|-------|

|   | C           | )   | 1   | 2    | 3    | 4          | 5   | 6   | 7   | 8    | 9    | Α    | В    | С   | D   | E     | F     |

| 0 |             |     | LRL | STZ  | LN   | А          | AI  | А   | Ai  | ISE  | МСР  | FLFX | VECT | SAH |     | AND   | ANDI  |

| 1 |             |     | LEM | STZH | LNH  | АН         | AlH |     |     | ISNE | BCC  | FLFH |      | SAH |     | ANDD  |       |

| 2 |             |     | LAM | SPS  | LNF  | AF         | LEA | А   | Ai  | DSE  | INT  | FDFX |      |     |     | CAND  | CANDI |

| 3 |             |     | LAC | STZD | LND  | AFD        |     |     |     | DSNE | PSH  |      |      | SAD |     | CANDD |       |

| 4 |             |     | L   | ST   | STN  | АМ         | LI  | D   | DI  | BCLE | мсw  |      |      | SL  |     | OR    | ORI   |

| 5 |             | _   | LLL | STLL | STNH | АМН        | LiH | DН  | DIH | BCG  | BRC  |      | 2    | SLH |     | ORD   |       |

| 6 | _           |     | LLA | STRL | STNF | AMF        | LEA | DF  |     | BCLE | XEC  |      |      | RVS |     | COR   | CORI  |

| 7 | c           | - 1 | LD  | STD  | STND | AMFD       |     | DFD |     | BCG  | PUL  |      |      | SLD |     | CORD  |       |

| 8 | F<br>1      | - 1 | L   | ST   | LNM  | s          | SI  | м   | мі  | IBZ  | BLB  | FXFL |      | С   | CI  | XOR   | XORI  |

| 9 | _           |     | LLR | STLR | LNMH | <b>S</b> H | SIH |     |     | IBNZ | BLX  | FHFL |      | СН  | СІН | XORD  |       |

| Α | _           |     | хсн | ѕтон | LNMF | SF         |     | м   | мі  | рвх  | FORK | FXFD |      | CF  |     |       |       |

| В |             |     | LF  | STF  | LNMD | SFD        |     |     |     | DBNZ | NIOL | FHFD |      | CFD |     |       |       |

| С |             |     | L   | ST   | LM   | SM         | LI  | М   | мі  | IBZ  | BXEC | NFX  |      | sc  |     | EQC   | EQCI  |

| D | _           |     | LRR | STRR | LMH  | ѕмн        |     | мн  | мін | IBNZ | BAE  | NFH  |      | sсн |     | EQCD  |       |

| Ε | _           |     | LO  | STO  | LMF  | SMF        |     | MF  |     | DBZ  | PB   | SCLK |      | С   | CI  | -     |       |

| F |             |     | LFM | STFM | LMD  | SMFD       |     | MFD |     | DBNZ | MOD  |      |      | scD |     |       |       |

(A)132345

Figure 1-4. Scalar Op Code Map

Table 1-3. Scalar Instruction Set

| ASSMB<br>CODE | INSTRUCTION                                                                     | MCHN<br>CODE | OPERAND<br>FORMAT |

|---------------|---------------------------------------------------------------------------------|--------------|-------------------|

| Α             | Add to arithmetic register, fixed point singleword                              | 40           | r,[@] [=] n[,x]   |

| A             | Add to base register, fixed point singleword                                    | 60           | r, [@] [=] n[,x]  |

| A             | Add to index or vector parameter register                                       | 62           | r, [@] [=] n[,x]  |

| AF            | Add to arithmetic register, floating point singleword                           | 42           | r,[@] [=] n[,x]   |

| AFD           | Add to arithmetic register, floating point doubleword                           | 43           | r,[@] [=] n [,x]  |

| AH            | Add to arithmetic register, fixed point halfword                                | 41           | r, [@] [=] n[,x]  |

| AI            | Add immediate to arithmetic register, fixed point singleword                    | 50           | r,i[,x]           |

| AI            | Add immediate to base register, fixed point singleword                          | 70           | r,i[,x]           |

| AI            | Add immediate to index or vector parameter register, fixed point singleword     | 72           | r,i[,x]           |

| AIH           | Add immediate to arithmetic register, fixed point halfword                      | 51           | r,i[,x]           |

| AM            | Add magnitude to arithmetic register, fixed point singleword                    | .44          | r,[@] [=] n[,x]   |

| AMF           | Add magnitude to arithmetic register, floating point singleword                 | 46           | r, [@] [=] n[,x]  |

| AMFD          | Add magnitude to arithmetic register, floating point doubleword                 | 47           | r,[@] [=] n[,x]   |

| AMH           | Add magnitude to arithmetic register, fixed point halfword                      | 45           | r,[@] [=] n[,x]   |

| AND           | AND, singleword - arithmetic register                                           | E0           | r, [@] [=] n[,x]  |

| ANDD          | AND, doubleword - arithmetic register                                           | E1           | r, [@] [=] n[,x]  |

| ANDI          | AND immediate, singleword - arithmetic register                                 | F0           | r,i[,x]           |

| В             | Unconditional branch, Assembler supplies R field of 7                           | 91           | [@[=]]n[,x]       |

| BAE           | Branch on arithmetic exception condition true                                   | 9D           | m, [@[=]]n[,x]    |

| BCC           | Branch on compare code true                                                     | 91           | m,[@[=]]n[,x]     |

| BCG           | Branch on arithmetic register greater than                                      | 85           | r,r,n             |

| BCG           | Branch on index or vector register greater than                                 | 87           | r,r,n             |

| BCLE          | Branch on arithmetic register less than or equal                                | 84           | r,r,n             |

| BCLE          | Branch on index or vector register less than or equal                           | 86           | r,r,n             |

| BCM           | Branch on compare code of mixed zeros and ones, Assembler supplies R field of 4 | 91           | [@[=]]n[,x]       |

Table 1-3. Scalar Instruction Set (Continued)

| ASSMB<br>CODE | INSTRUCTION                                                                                                                      | MCHN<br>CODE | OPERAND<br>FORMAT |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|

| BCNM          | Branch on compare code of not mixed,<br>Assembler supplies R field of 3                                                          | 91           | [@[=]]n[,x]       |

| BCNO          | Branch on compare code of not all ones,<br>Assembler supplies R field of 5                                                       | 91           | [@[=]]n[,x]       |

| BCNZ          | Branch on compare code of not all zeros,<br>Assembler supplies the R field of 6                                                  | 91           | [@[=]]n[,x]       |

| BCO           | Branch on compare code of all bits are one.  Assembler supplies R field of 2                                                     | 91           | [@[=]]n[,x]       |

| BCZ           | Branch on compare code of all bits are zero,<br>Assembler supplies R field of one                                                | 91           | [@[=]]n[,x]       |

| BD            | Branch on divide check, Assembler supplies R field of 8                                                                          | 9D           | [@[=]]n[,x]       |

| BDO           | Branch on divide check or floating point exponent overflow, Assembler supplies R field of A                                      | 9 <b>D</b>   | [@[=]]n[,x]       |

| BDU           | Branch on divide check or floating point exponent underflow, Assembler supplies R field of 9                                     | 9D           | [@[=]]n[,x]       |

| BDUO          | Branch on divide check or floating point exponent overflow or underflow, Assembler supplies R field of B                         | 9D           | [@[=]]n[,x]       |

| ЬDХ           | Branch on divide check or fixed point overflow, Assembler supplies R field of C                                                  | 9D           | [@[=]]n[,x]       |

| BDXO          | Branch on divide check or fixed point overflow or floating point exponent overflow, Assembler supplies R field of E              | 9D           | [@[=]]n[,x]       |

| BDXU          | Branch on divide check or fixed point overflow or floating point exponent underflow, Assembler supplies R field of D             | 9D           | [@[=]]n[,x]       |

| BDXUO         | Branch on divide check or fixed point overflow or floating point exponent overflow or underflow, Assembler supplies R field of F | 9D           | [@[=]]n[,x]       |

| BE            | Branch on compare code of equal, Assembler supplies R field of one                                                               | 91           | [@[=]]n[,x]       |

| BG            | Branch on compare code of greater than,<br>Assembler supplies R field of 2                                                       | 91           | [@[=]]n[,x]       |

| BGE           | Branch on compare code of greater than or equal, Assembler supplies R field of 3                                                 | 91           | [@[=]]n[,x]       |

| BL            | Branch on compare code of less than, Assembler supplies R field of 4                                                             | 91           | [@[=]]n[,x]       |

| B€B           | Branch and load base register with program counter                                                                               | 98           | r,[@[=]]n[,x]     |

| BLE           | Branch on compare code of less than or equal,<br>Assembler supplies R field of 5                                                 | 91           | [@[=]]n[,x]       |

Table 1-3. Scalar Instruction Set (Continued)

| ASSMB<br>CODE | INSTRUCTION                                                                                                      | MCHN<br>CODE | OPERAND<br>FORMAT |

|---------------|------------------------------------------------------------------------------------------------------------------|--------------|-------------------|

| BLR           | Branch on logical result                                                                                         | 95           | m,[@[=]]n[,x]     |

| BLX           | Branch and load index or vector register with program counter                                                    | 99           | r, [@[=]]n[,x]    |

| BMI           | Branch on result code of negative, Assembler supplies the R field of 4                                           | 95           | [@[=]]n[,x]       |

| BNE           | Branch on compare code of not equal,<br>Assembler supplies R field of 6                                          | 91           | [@[=]]n[,x]       |

| BNZ           | Branch on result code of not zero, Assembler supplies the R field of 6                                           | 95           | [@[=]]n[,x]       |

| ВО            | Branch on floating point exponent overflow, Assembler supplies R field of 2                                      | 9D           | [@[=]]n[,x]       |

| BPL           | Branch on result code of positive, Assembler supplies the R field of 2                                           | 95           | [@[=]]n[,x]       |

| BRC           | Branch on result code true                                                                                       | 95           | m,[@[=]]n[,x]     |

| BRM           | Branch on result code of bits mixed zeros and ones, Assembler supplies the R field of 4                          | 95           | [@[=]]n[,x]       |

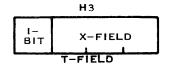

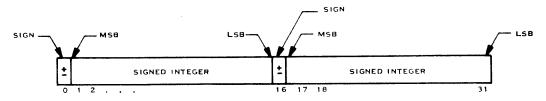

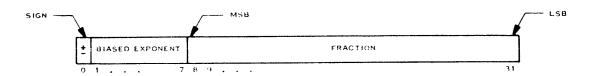

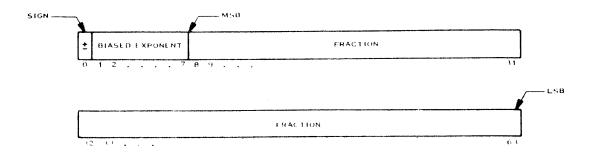

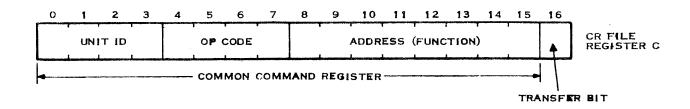

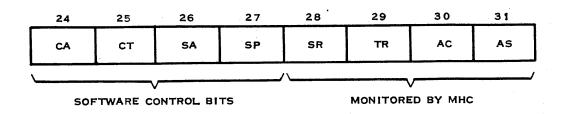

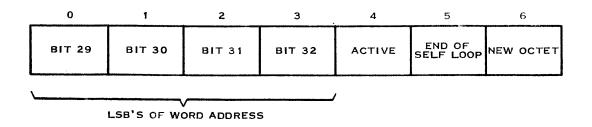

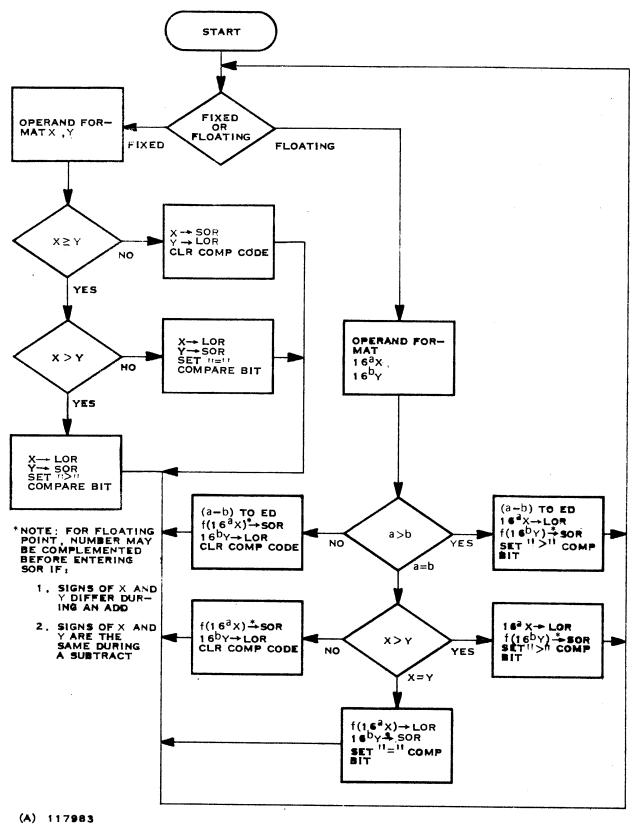

| BRNM          | Branch on result code of bits not mixed zeros and ones, Assembler supplies the R field of 3                      | 95           | [@[=]]n[,x]       |