## OPERATION AND MAINTENANCE INSTRUCTIONS

ASC-4X CENTRAL PROCESSOR (CP)

Volume 2

Equipment Group P.O. Box 2909 Austin, Texas 78767

# TEXAS INSTRUMENTS

#### INTRODUCTION

This manual is volume 2 of a two-volume set of operation and maintenance instructions for the 4-pipe Central Processor, which is used in the Advanced Scientific Computer (ASC) system, manufactured by Texas Instruments Incorporated.

This volume contains the following sections and appendixes:

Section 5 - Maintenance

Section 6 - Parts Listing

Section 7 - Diagrams

Appendix A - Details Maps

Appendix B - 4XIPU Listings and Circuit Board Descriptions

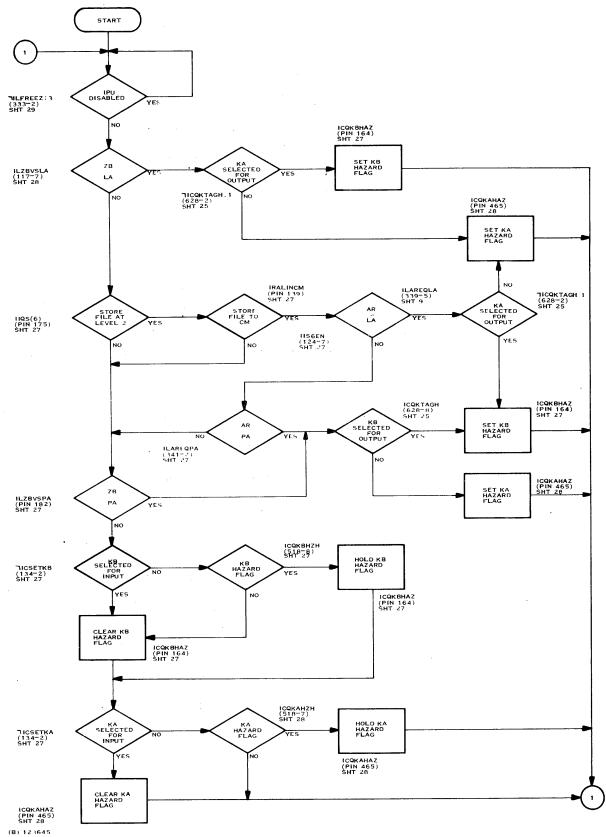

Appendix C - 4XCP Hazard Conditions

Appendix D - Hard Core

The part number for Volume 1 is 931443-2.

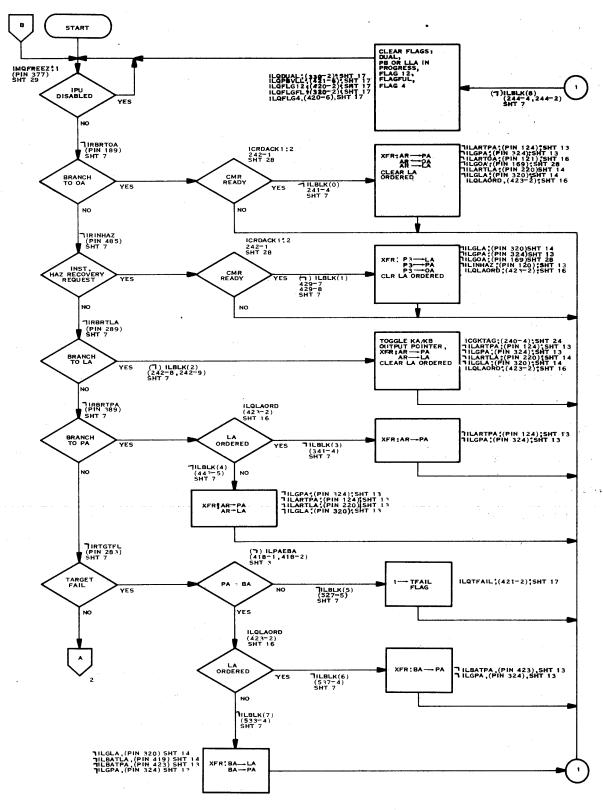

## SECTION V MAINTENANCE

#### 5-1 GENERAL

The maintenance philosophy for the 4-pipe Central Processor consists of running a a series of diagnostic tests to fault isolate to a functional section and the use of AU Functional Logic Descriptions (FLDs), harness lists (in Fiche form), and flowcharts in conjunction with conventional test equipment to fault isolate down to the replaceable card level.

The FLDs available for the 4-pipe CP include:

- IPU4 FLD, part no. 931490

- AU4 FLD, part no. 931491

- MBU4 FLD, part no. 931492

The diagnostic tests available for maintenance of the 4-pipe CP are described in the multi-volume set of ASC System Diagnstics available at each ASC site.

### SECTION VI PARTS LISTING

#### 6-1 INTRODUCTION

This section provides a list of replaceable logic cards and their part numbers for the ASC 4X-Central Processor. The list is intended as a guide for ordering new cards and installing them in the CP. Items such as IC's, screws, washers, etc., are not included.

#### 6-2 LOGIC CARDS

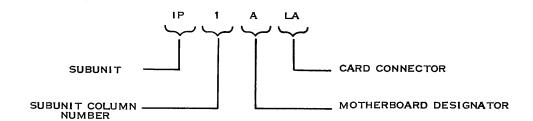

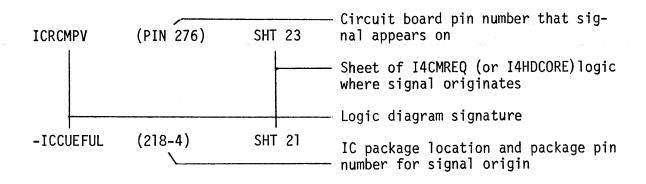

Logic cards for the CP are contained in ten chassis: two IPU's, four MBU's, and four AU's. Each AU and MBU chassis has three motherboards, and each IPU contains two motherboards which hold the logic cards. These motherboards are designated with the letters A, B, and C from top to bottom, respectively. Each card slot in a motherboard is designated with a two letter label, LA to LV. These designators are used to identify the particular card location in the CP. Figure 6-1 illustrates the information contained in a card location designator. The first two letters refer to the chassis. The next character refers to the column. The fourth character designates the motherboard in that column, and the last two letters identify the card slot on that motherboard. Table 6-1 lists all CP logic cards and are arranged by card location. Only one of the four identical MBU and AU pipes is listed.

(A) 115137

Figure 6-1. Card Location Information

Table 6-1. Central Processor Logic Cards

| Card<br>Location                                                                                                 | Function                                                                                                                                                                                                                | Part Number                                                                                                                                                                                                                                  | Card<br>Location                                                                           | Function                                                                                                                                                                                  | Part Number                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP2ALA IP2ALB LC LD LE LF LG LH LI LJ LK LL LM LN LO LP LQ LR LS LT LU LD LC | TERMCRD 14ZHAZ(1) 14ZHAZ(0) 14RHAZ(3) 14HZAZ(2) 14ZHAZ(5) 14ZHAZ(5) 14ZHAZ(1) 14ZHAZ(7) 14ZHAZ(7) 14ZHAZ(6) 14ZHAZ(11) 14RHAZ(2) 14ZHAZ(8) 14ZHAZ(10) 14ZHAZ(10) 14ZHAZ(10) 14ZHAZ(12) 14ZHAZ(13) 14ZHAZ(13) 14ZHAZ(14) | 650296-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1<br>923558-1 | IP2BLA  LB  LC  LD  LE  LF  LG  LH  LI  LJ  LK  LL  LM  LN  LO  LP  LQ  LR  LS  LT  IP2BLU | DUMMY I4HDCORE I4CMREQ I4INFACE(2) I4INFACE(1) I4INFACE(0) I4PIPTOP I4MISC I4VECLAS I4LVL3 TERMCRD I4ROUTE1 I4ROUTE3 I4ROUTE2 I4INFACE(3) BUCTL4-2 DUMMY DUMMY DUMMY DUMMY DUMMY LOGCLK-5 | 695011-1<br>923570-1<br>923573-1<br>923567-1<br>923567-1<br>923567-1<br>923582-1<br>923582-1<br>923585-1<br>650926-1<br>923588-1<br>923594-1<br>923591-1<br>923567-1<br>922700-2<br>695011-1<br>695011-1<br>695011-1<br>695011-1 |

| IP2ALV<br>IP3ALA                                                                                                 | TERMCRD<br>DUMMY                                                                                                                                                                                                        | 650296-1<br>695011-1                                                                                                                                                                                                                         | IP3BLA                                                                                     | DUMMY                                                                                                                                                                                     | 695011-1                                                                                                                                                                                                                         |

| IP3ALB                                                                                                           | DUMMY                                                                                                                                                                                                                   | 695011-1                                                                                                                                                                                                                                     | <b>▲</b> LB                                                                                | DUMMY                                                                                                                                                                                     | 695011-1                                                                                                                                                                                                                         |

| LC<br>LD                                                                                                         | I4FILE(3)<br>I4FILE(7)                                                                                                                                                                                                  | 923549-1<br>923549-1                                                                                                                                                                                                                         | T LC<br>LD                                                                                 | DUMMY<br>I4PIPE(4)                                                                                                                                                                        | 695011-1<br>923561-1                                                                                                                                                                                                             |

| LE                                                                                                               | I4FILE(15)                                                                                                                                                                                                              | 923549-1                                                                                                                                                                                                                                     | LE                                                                                         | I4PIPE(3)                                                                                                                                                                                 | 923561-1                                                                                                                                                                                                                         |

| LF<br>LG                                                                                                         | I4FILE(14)<br>I4FILE(13)                                                                                                                                                                                                | 923549-1<br>923549-1                                                                                                                                                                                                                         | LF<br>LG                                                                                   | I4PIPE(2)<br>I4STATUS                                                                                                                                                                     | 923561-1<br>923564-1                                                                                                                                                                                                             |

| LH                                                                                                               | I4FILE(12)                                                                                                                                                                                                              | 923549-1                                                                                                                                                                                                                                     | LH                                                                                         | I4PIPE(0)                                                                                                                                                                                 | 923561-1                                                                                                                                                                                                                         |

| LI                                                                                                               | I4FILE(11)<br>TERMCRD                                                                                                                                                                                                   | 923549-1                                                                                                                                                                                                                                     | LI                                                                                         | I4PIPE(1)                                                                                                                                                                                 | 923561-1                                                                                                                                                                                                                         |

| LK                                                                                                               | I4FILE(10)                                                                                                                                                                                                              | 650296-1<br>923549-1                                                                                                                                                                                                                         | LJ<br>  LK                                                                                 | TERMCRD<br>ROMCRD L3                                                                                                                                                                      | 650296-1<br>650299-228                                                                                                                                                                                                           |

| LL                                                                                                               | I4FILE(8)                                                                                                                                                                                                               | 923549-1                                                                                                                                                                                                                                     | LL                                                                                         | BUCTL4-2                                                                                                                                                                                  | 922700-2                                                                                                                                                                                                                         |

| LM<br>LN                                                                                                         | I4ADDR(1)<br>I4ADDR(0)                                                                                                                                                                                                  | 923552-1<br>923552-1                                                                                                                                                                                                                         | LM<br>  LN                                                                                 | DUMMY<br>LOGCLK-7                                                                                                                                                                         | 695011-1<br>650356-7                                                                                                                                                                                                             |

| LO                                                                                                               | I4FILE(6)                                                                                                                                                                                                               | 923549-1                                                                                                                                                                                                                                     | L0                                                                                         | ROMCRD L2                                                                                                                                                                                 | 650229-227                                                                                                                                                                                                                       |

| LP<br>LQ                                                                                                         | I4FILE(5)<br>I4FILE(4)                                                                                                                                                                                                  | 923549-1<br>923549-1                                                                                                                                                                                                                         | LP<br>LQ                                                                                   | I4PIPE(5)<br>I4PIPE(6)                                                                                                                                                                    | 923561-1<br>923561-1                                                                                                                                                                                                             |

| LR                                                                                                               | I4FILE(9)                                                                                                                                                                                                               | 923549-1                                                                                                                                                                                                                                     | LR                                                                                         | I4PIPE(7)                                                                                                                                                                                 | 923561-1                                                                                                                                                                                                                         |

| LS<br>LT                                                                                                         | I4FILE(1)<br>I4FILE(0)                                                                                                                                                                                                  | 923549-1                                                                                                                                                                                                                                     | LS                                                                                         | I4MHCA                                                                                                                                                                                    | 932005-1                                                                                                                                                                                                                         |

| ₩ ĽU                                                                                                             | I4FILE(0)                                                                                                                                                                                                               | 923549-1<br>923549-1                                                                                                                                                                                                                         | V LT LU                                                                                    | DUMMY<br>DUMMY                                                                                                                                                                            | 695011-1<br>695011-1                                                                                                                                                                                                             |

| IP3ALV                                                                                                           | DUMMY `´                                                                                                                                                                                                                | 695011-1                                                                                                                                                                                                                                     | IP3BLV                                                                                     | DUMMY                                                                                                                                                                                     | 695011-1                                                                                                                                                                                                                         |

Table 6-1. Central Processor Logic Cards (Continued)

| Card<br>Location                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Part Number                                                                                                                                                                                                                        | Card<br>Location                                       | Function                                                                                                                                                                                                                                                               | Part Number                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MB1ALA B C D E F G H I J K L M N O P Q R               | ROMCRD(0) ROMCRD(8) BUROM(0) ROMCRD(9) ROMCRD(1) ROMCRD(1) ROMCRD(10) BUROM(1) ROMCRD(11) ROMCRD(3) BUCTL4-2 ROMCRD(4) ROMCRD(4) ROMCRD(12) BUROM(2) ROMCRD(13) ROMCRD(5) ROMCRD(6)                                                                                                                                                                                                                                                                               | 650299-207<br>650299-215<br>686490-1<br>650299-216<br>650299-209<br>650299-217<br>686490-1<br>650299-210<br>922700-2<br>650299-211<br>650299-211<br>650299-219<br>686490-1<br>650299-220<br>650299-220<br>650299-213<br>650299-213 | MB1BLA BCDEFGHIJKLMNOPQR                               | DUMMY DUMMY DUMMY BUZAG BUDATA(0) BUDATA(1) BUDATA(2) BUDATA(3) BUDATA(4) BUDATA(5) BUDATA(5) BUDATA(6) BUDATA(7) BUDATA(8) BUDATA(9) BUDATA(10) BUDATA(11) BUDATA(12)                                                                                                 | 695011-1<br>695011-1<br>695011-1<br>650362-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1<br>650365-1                                                                                                             |

| V S T U MB1ALV                                         | ROMCRD(14) BUROM(3) ROMCRD(15) ROMCRD(7) TERMCRD                                                                                                                                                                                                                                                                                                                                                                                                                  | 650299-221<br>686490-1<br>650299-222<br>650299-214<br>650296-1                                                                                                                                                                     | S<br>T<br>U<br>MB1BLV                                  | BUDATA(13) BUDATA(14) BUDATA(15) TERMCRD DUMMY                                                                                                                                                                                                                         | 650365-1<br>650365-1<br>650365-1<br>650296-1<br>695011-1                                                                                                                                                                                                                         |

| MB1CLA  B C D E F G H I J K L M N O P Q R S T U MB1CLV | BUCTL3A BUCMR BUCTL1 BUCTL4A TERMCRD BUCAFA(1) BUCAFA(1) BUADDRA(4) BULOOP(0) BULOOP(3) BULOOP(2) BUADDRA(3) BUADDRA(3) BUADDRA(1) | 931981-1<br>932026-1<br>922691-1<br>931984-1<br>650296-1<br>931966-1<br>931939-1<br>686478-1<br>686478-1<br>686478-1<br>931939-1<br>931939-1<br>931939-1<br>931939-1<br>650296-1<br>931939-1<br>650356-1<br>710258-1<br>695011-1   | AUTALA  B C D E F G H I J K L M N O P Q R S T U AUTALV | TERMCRD AU4XSELA(1) AU4XSELA(0) AU4ADDA(0) AU4ADDA(1) AU4ADDA(2) AU4ADDA(3) AU4ADDA(3) AU4ADDA(5) AU4ADDA(5) AU4ADDA(6) AU4ADDA(7) AU4ADDA(7) AU4CTLIA AU4ADDA(8) AU4ADDA(10) AU4ADDA(11) AU4ADDA(11) AU4ADDA(12) AU4ADDA(13) AU4ADDA(14) AU4ADDA(15) TERMCRD LOGCLK-4 | 650296-1<br>931996-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1<br>931936-1 |

Table 6-1. Central Processor Logic Cards (Continued)

| Card<br>Location                                          | Function                                                                                                                                                                                                        | Part Number                                                                                                                                                                                                                      | Card<br>Location            | Function                                                                                                                                                                                                                                                                                                                                                                                                        | Part Number                                                                                                                                                                                                                      |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUIBLA LB LC LD LE LF LG LH LI LN LN LO LP LQ LR LS LT LU | TERMCRD AUOUTB(0) AUOUTB(1) AUOUTB(2) AUOUTB(3) AUOUTB(4) AUOUTB(5) AUOUTB(6) AUOUTB(7) AUCTL3B AUCTL3B AUCTL2B AUCTL4A AUNORMA(0) AUNORMA(1) AUNORMA(2) AUNORMA(3) AUNORMA(4) AUNORMA(5) AUNORMA(6) AUNORMA(7) | 650296-1<br>931978-1<br>931978-1<br>931978-1<br>931978-1<br>931978-1<br>931978-1<br>931978-1<br>931978-1<br>931972-1<br>931972-1<br>931954-1<br>929338-1<br>929338-1<br>929338-1<br>929338-1<br>929338-1<br>929338-1<br>929338-1 | AUICLA BCDEFGHIJKLMNOPQRSTU | TERMCRD AUMULTA(0) AUSUMD(10) AUSUMD(8) AUSUMD(4) AUSUMD(2) AUSUMD(2) AUSUMD(7) AUSUMD(6) AUSUMD(6) AUSUMD(5) AUSUMD(5) AUSUMD(1) AUSUMD(1) AUSUMD(1) AUSUMD(3) AUSUMD(3) AUSUMD(3) AUSUMD(0) AUSUMD(0) AUSUMD(0) AUSUMD(0) AUSUMD(7) AUSUMD(1) AUSUMD(1) AUSUMD(1) AUSUMD(3) AUSUMD(1) | 650296-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>686487-1<br>929335-1<br>929335-1 |

| AUIBLV                                                    | TERMCRD                                                                                                                                                                                                         | 650296-1                                                                                                                                                                                                                         | AUICLV                      | TERMCRD                                                                                                                                                                                                                                                                                                                                                                                                         | 650296-1                                                                                                                                                                                                                         |

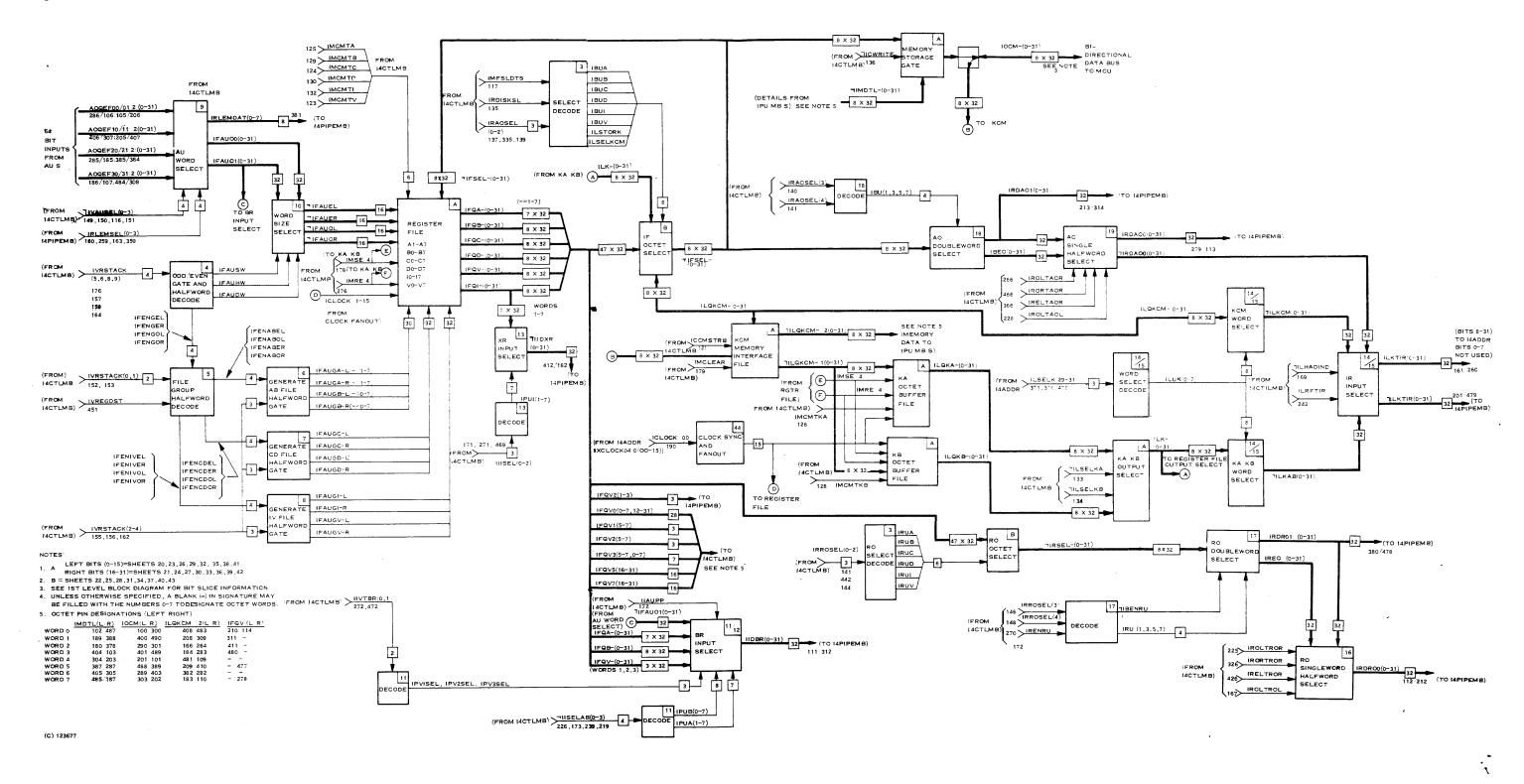

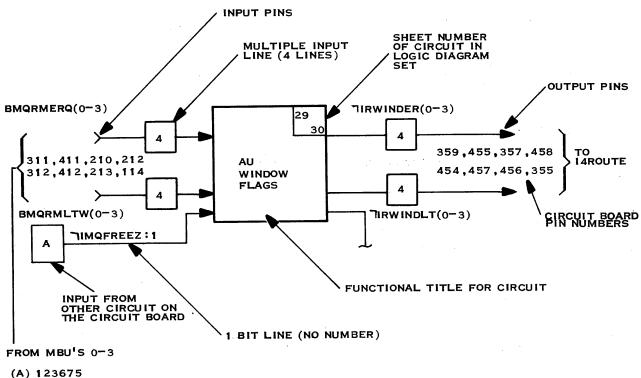

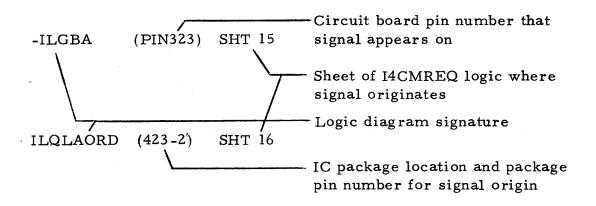

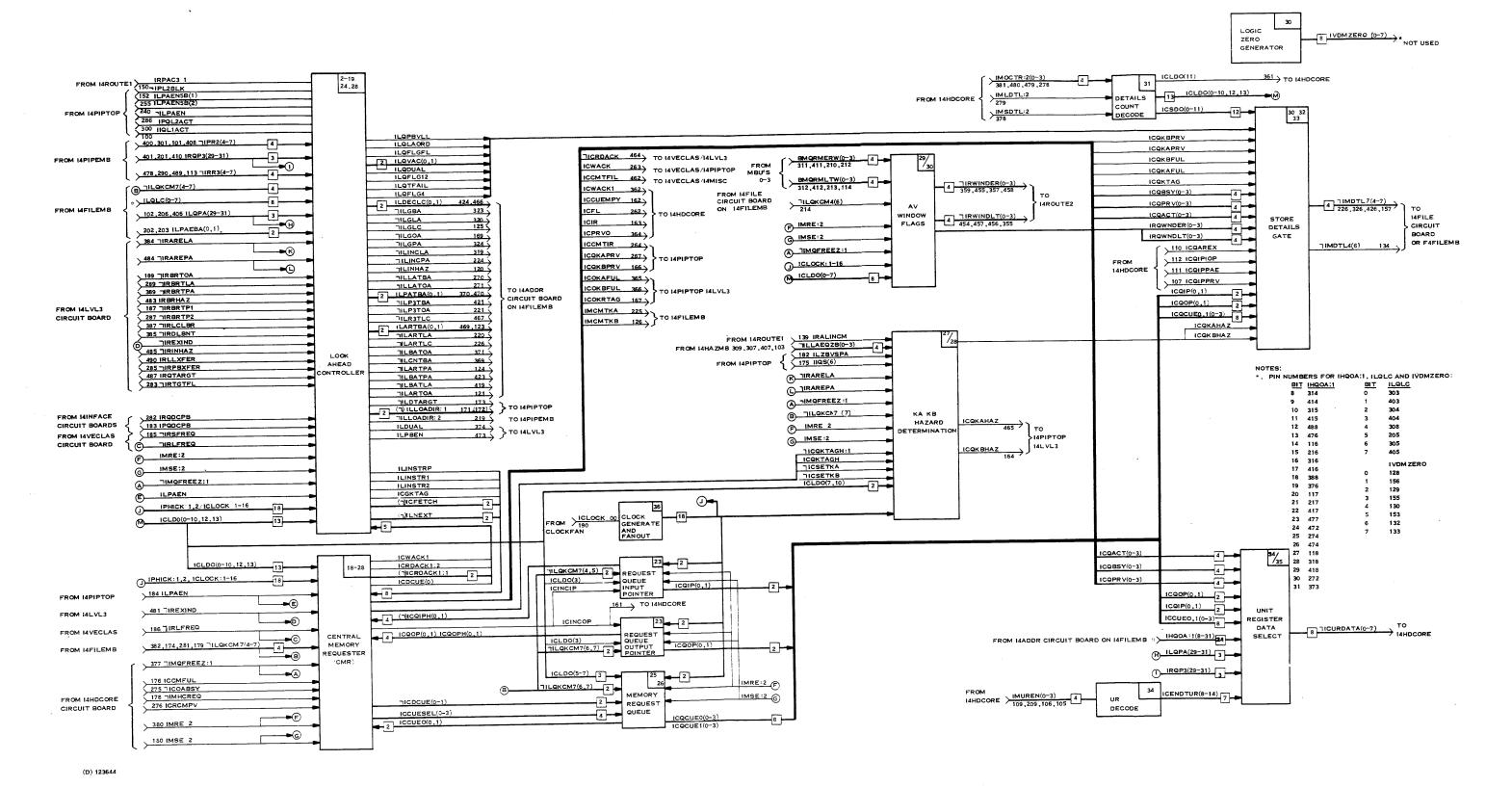

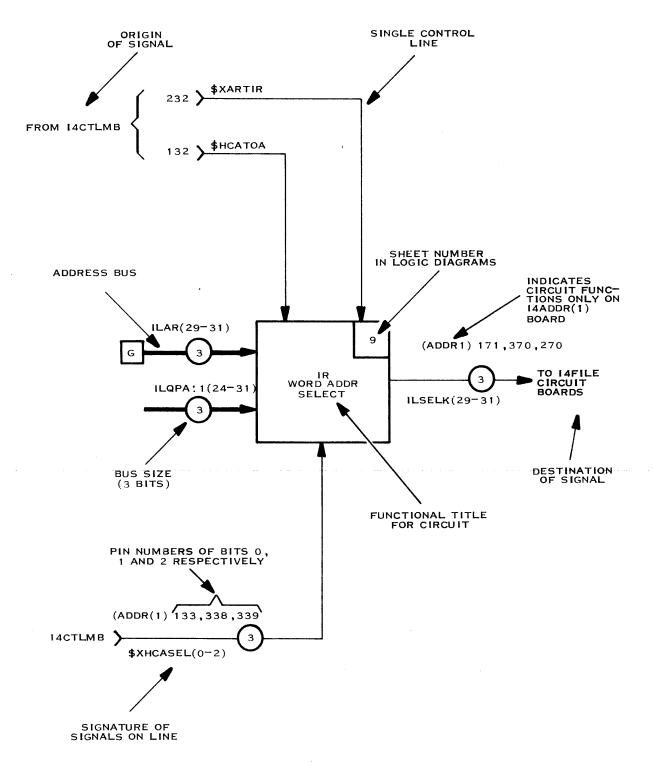

## SECTION VII DIAGRAMS

### 7-1 GENERAL

ASC Hardware Documentation Control at the TI Austin Facility provides each ASC site with the latest logic diagrams and engineer's lists. However, individual logic diagram sets, and the associated engineer's list in Fiche form, may be obtained from them by specifying only the card name. Drawing numbers are not required. Engineer's lists, in Fiche form, for motherboards and harnesses may also be obtained by name. In addition, logic diagrams may be ordered by drawing number from Drawing Control at the TI Austin Facility.

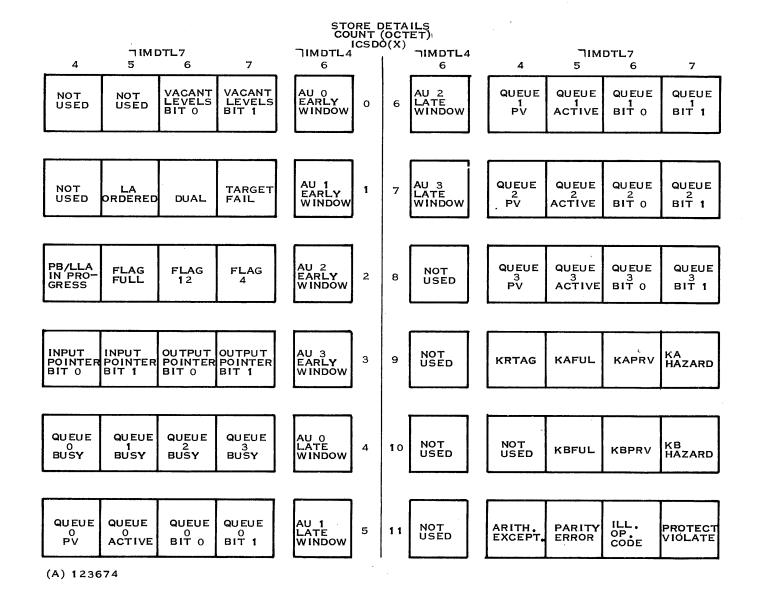

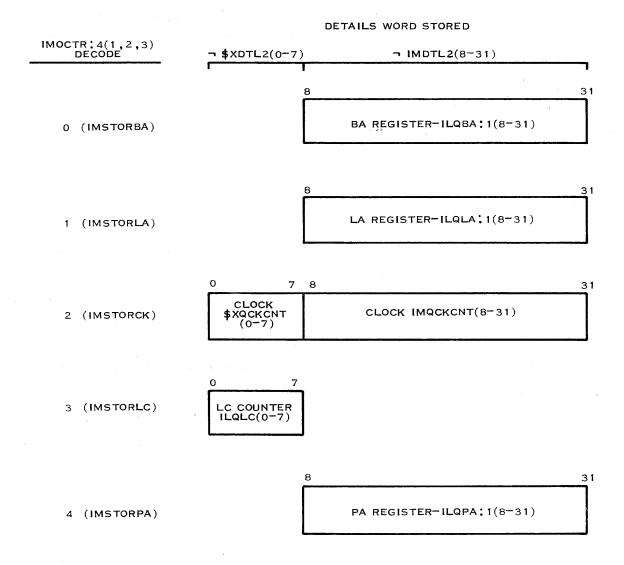

## APPENDIX A DETAILS MAPS

|   |                                  | Page |

|---|----------------------------------|------|

| • | Dedicated CM Locations           | A-1  |

| • | 4XCP Details Map Overview        | A-2  |

| • | 4XCP Status Map and PSW Register | A-3  |

| • | 4XCP Details Locations           | A-4  |

| • | 4X IPU Register Stack            | A-6  |

| • | 4X IPU Details Map               | A-7  |

| • | 4X MBU Details Map               | A-15 |

| • | 4X AU Details Map                | A-23 |

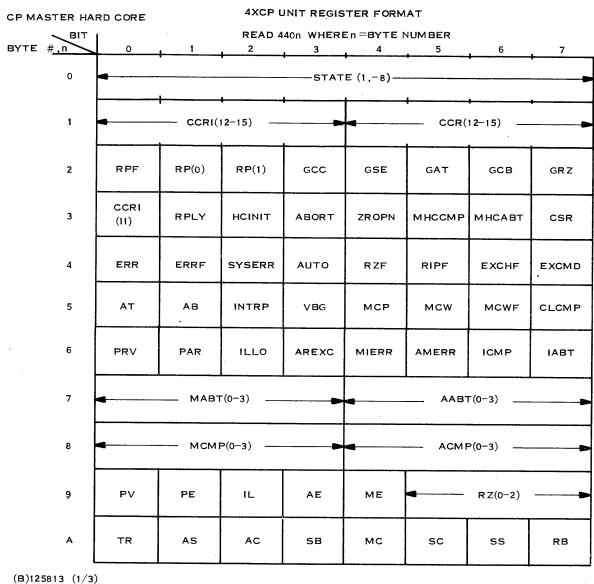

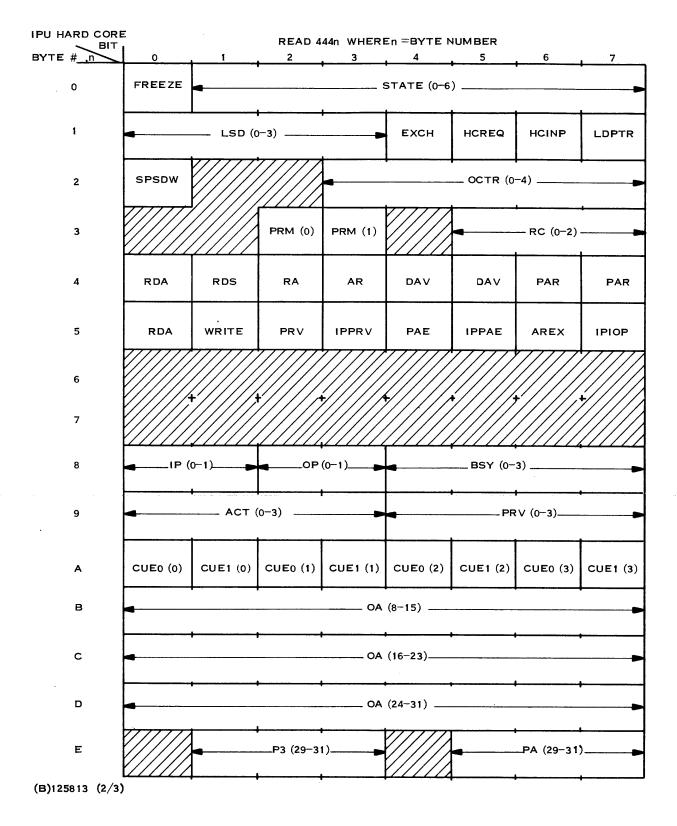

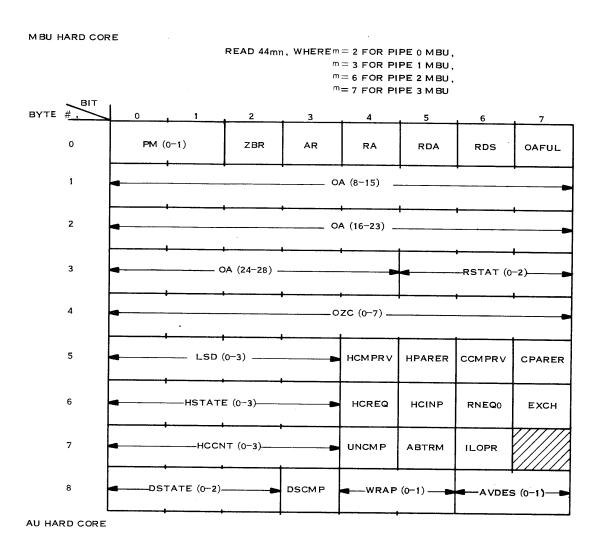

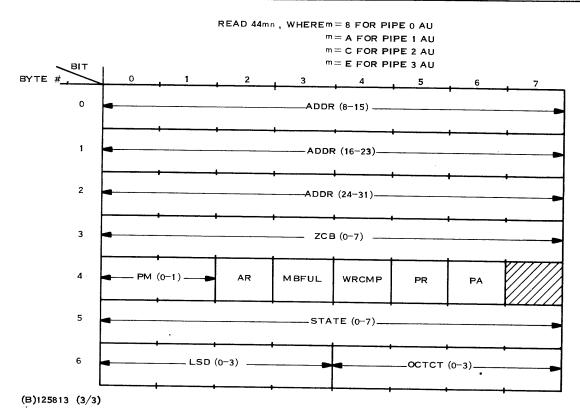

| • | 4X Hard Core Unit Register Maps: |      |

|   | Master Hard Core                 | A-31 |

|   | IPU Hard Core                    | A-32 |

|   | MBU Hard Core                    | A-33 |

|   | AU Hard Core                     | A-33 |

| LOCATION  | FUNCTION                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------|

| (HFX)     |                                                                                                 |

| 00        | Default bootstrap buffer start                                                                  |

| 07        |                                                                                                 |

| 08        |                                                                                                 |

| 0A        |                                                                                                 |

| 14        | Pointer to store Status area (single CP)                                                        |

|           | Pointer to load Status area (single CP)                                                         |

|           | Pointer to store Intermediate area (X1CP) Pointer to load Intermediate area (X1CP)              |

|           | Pointer to store Details area (single CP)                                                       |

| 19        | Pointer to load Details area (single CP)                                                        |

|           | BRSM augmented PC save words                                                                    |

|           | Pointer to MCU Context switch area CP0 Pointer to MCU Context switch area CP1                   |

| 2C        | Pointer to MCU Context switch area CP2                                                          |

|           | Pointer to MCU Context switch area CP3                                                          |

|           | Pointer to store MCU Map and Protect area Pointer to load MCU Map and Protect area              |

|           | ROM RO augmented save words                                                                     |

| 48 - 4F   | ROM R1 augmented save words                                                                     |

|           | ROM R2 augmented save words ROM R3 augmented save words                                         |

|           | ROM Base augmented save words                                                                   |

| 68 - 6F   | ROM PC augmented save words                                                                     |

| 78 - 79   | Pointer to TCC2(0) High Priority queue headers                                                  |

| 80 - 84   | Pointer to TCC2(0) Low Priority queue headers                                                   |

| 88 - 8C   |                                                                                                 |

| 90 - 94   | DISC 2 CA address                                                                               |

| 98 - 9C   |                                                                                                 |

|           | Pointer to TCC2(2) High Priority queue headers Pointer to TCC2(2) Low Priority queue headers    |

| A8 - A9   | Pointer to TCC2(3) High Priority queue headers                                                  |

| AC - AD   | Pointer to TCC2(3) Low Priority queue headers                                                   |

|           | Pointer to TCC2(4) High Priority queue headers<br>Pointer to TCC2(4) Low Priority queue headers |

| B8 - B9   | Pointer to TCC2(5) High Priority queue headers                                                  |

| BC - BD   | Pointer to TCC2(5) Low Priority queue headers                                                   |

| C0 - C1   | Pointer to TCC2(6) High Priority queue headers<br>Pointer to TCC2(6) Low Priority queue headers |

| C8 - C9   | Pointer to TCC2(7) High Priority queue headers                                                  |

| CC - CD   | Pointer to TCC2(7) Low Priority queue headers                                                   |

|           | Pointer to TCC2(8) High Priority queue headers Pointer to TCC2(8) Low Priority queue headers    |

|           | Pointer to TCC2(9) High Priority queue headers                                                  |

| DC - DD   | Pointer to TCC2(9) Low Priority queue headers                                                   |

| E8        |                                                                                                 |

| F2 - F3   |                                                                                                 |

| F4 - F5   | Tape SCB 2                                                                                      |

| F6 - F7   |                                                                                                 |

| 101       | ROM dump final octet address                                                                    |

| 110       | Automatic interrupt ROM exit pointer                                                            |

| 111       | Software interrupt ROM exit pointer                                                             |

| 113       | ROM card boot convert pointer Pointer to TCC2(1) High Priority queue headers                    |

| 11C - 11D | Pointer to TCC2(1) Low Priority queue headers                                                   |

| 120       | Pointer to User Exit area for CP0                                                               |

|           | Pointer to Monitor Entry area for CP0 Pointer to User Exit area for CP1                         |

|           | Pointer to User Exit area for CPI Pointer to Monitor Entry area for CPI                         |

| 124       | Pointer to User Exit area for CP2                                                               |

|           | Pointer to Monitor Entry area for CP2                                                           |

|           | Pointer to User Exit area for CP3 Pointer to Monitor Entry area for CP3                         |

| 128       | Pointer to Monitor Exit area for CP0                                                            |

| 129       | Pointer to User Entry area for CP0                                                              |

| 12B       | Pointer to Monitor Exit area for CPl<br>Pointer to User Entry area for CPl                      |

| 12C       | Pointer to Monitor Exit area for CP2                                                            |

| 12D       | Pointer to User Entry area for CP2                                                              |

| 12E       | Pointer to Monitor Exit area for CP3 Pointer to User Entry area for CP3                         |

| 130 - 133 |                                                                                                 |

| 134 - 137 | ACC 1 Start CA address                                                                          |

| 138 - 13B |                                                                                                 |

| 13C - 13F | ACC J SIGIT CA address                                                                          |

| (B)132488 |                                                                                                 |

Figure A-1. Dedicated CM Locations

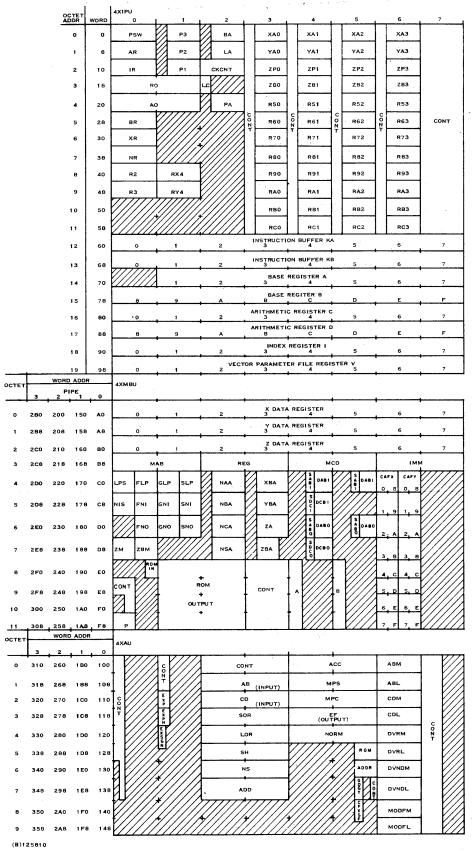

Figure A-2. 4XCP Details Map Overview

(B)125803

Figure A-3. 4XCP Status Map

ARITHMETIC EXCEPTION (AE) -

D - DIVIDE CHECK

1 - FX. PT. OVERFLOW

2 - FL. PT. OVERFLOW

3 - FL. PT. UNDERFLOW

PROTECT ENABLE (PROTEN) - CM PROTECTED

MAP ENABLE (MAPEN) -CM MAPPED

FORK MODE INDICATOR (FORK) - CP IN FORK MODE

MONITOR CALL CONDITION (MCC) - CP TRIED TO EXECUTE AN MCP/MCW

BRANCH OR SKIP CONDITION (BSC)

CP TRIED TO EXECUTE A BRANCH/SKIP

FOR WHICH CONDITION WAS TRUE

(B)125809

Figure A-4. 4XCP Program Status Word (PSW)

Figure A-5. 4XCP Details Locations (Sheet 1 of 2)

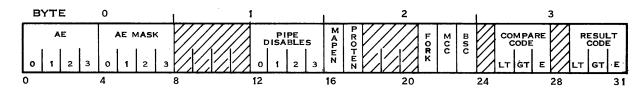

(B)130856A(1 2)

#### **4X DETAILS LOCATIONS**

#### IPU DETAILS MAP

| 4  | I4PIPE(0-7-):  | A DITC (CADD  |     |                |                 |

|----|----------------|---------------|-----|----------------|-----------------|

|    | •              | 4 BITS/CARD   | 10. | 14VECLAS:      | BITS(0-2);      |

| 2. | I4ADDR(0-1):   | 12 BITS/CARDS |     | I4MISC:        | BITS(3-5);      |

| 3. | I4ADDR(0-1):   | 16 BITS/CARD  |     | I4CMREQ:       | BIT(6); BIT(7)  |

| 4. | I4ADDR(0-1):   | 4 BITS/CARD   |     | •              | NOT USED        |

| 5. | I4RHAZ(0-3):   | 2 BITS/CARD   | 11. | 14INFACE(0-3): | 1 BIT/HEX/CARD  |

| 6. | 14ZHAZ(0-3):   | 6 BITS/CARD   | 12. | 14INFACE(0-3): | 4 BITS/CARD     |

| 7. | I4ZHAZ(4-7):   | 6 BITS/CARD   | 13. | 14STATUS:      | BITS (0-3);     |

| 8. | I4ZHAZ(8-11):  | 6 BITS/CARD   |     | I4CMREQ:       | BITS (4-7);     |

| 9. | I4ZHAZ(12-15): | 6 BITS/CARD   |     | 14PIPTOP:      | BITS (8-10);    |

|    |                |               |     | I4ROUTE3:      | BIT (11);       |

|    |                |               |     | 14LVL3:        | BITS (12-15)    |

|    |                |               | 14. | I4FILE(0-15):  | 1 BIT/HALFWORD/ |

|    |                |               |     |                | CARD            |

#### MBU DETAILS MAP

|    |               |                 |     |              | •               |

|----|---------------|-----------------|-----|--------------|-----------------|

| 1. | BUDATA(0-15): | 1 BIT/HALFWORD/ | 7.  | BUCAFA(0):   | COVERS 6L       |

|    |               | CARD            | 8.  | BUCAFA(1):   | COVERS 6R       |

| 2. | BULOOP(0-3):  |                 | 9.  | BUCTL3A      | GATES OUT OL.   |

| 3. | BUADDRA(0-4): | 5 BITS/CARD     |     |              | OCTETS 9-B      |

| 4. | BUCMR         | 1ST BIT         | 10. | BUROM(0-3):  | 1 HALFWORD/CARD |

|    | BUADDR(0-4):  | 1 HEX/CARD      | 11. | BUCMR:       | COVERS 3L.      |

|    | BUZAG:        | LAST HEX        |     |              | BITS 0-8        |

| 5. | BUCMR:        | 1ST 4 BITS;     | 12. | BUCTL4A;     | COVERS 3L,      |

|    | BULOOP(0):    | NEXT 7 BITS     |     | ·            | BITS 9-15,      |

|    |               |                 | 13. | BUCTL3A:     | COVERS 3R       |

|    | BULOOP(1):    | LAST 7 BITS     |     |              | BITS 0-14;      |

| 6. | BUCMR:        | 1ST 4 BITS IN   |     |              | BIT 15, SPARE   |

|    |               | OCTETS 4 AND 6: | 14  | BULOOP(0-3): | 1 HEX/CARD      |

|    | BULOOP(2):    | NEXT 7 BITS     |     | BUROM(0-3):  | 2 BITS/CARD     |

|    | . ,           | , ,             | 15. | DOIGON(U~3); | Z DI 19/CARD    |

|    | BULOOP(3):    | NEXT 7 BITS     |     |              |                 |

|    | ====== (5)    | NEXI / DIIS     |     |              |                 |

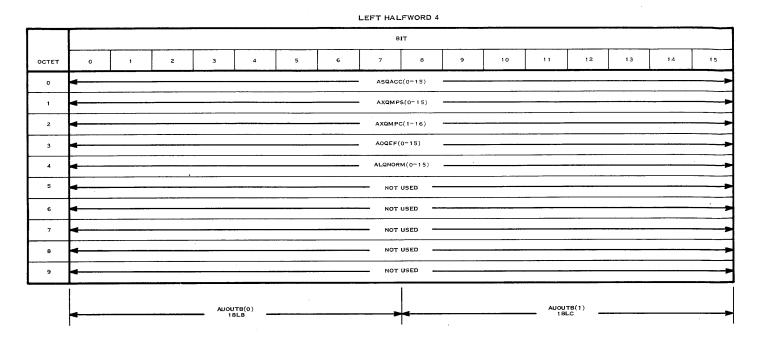

### AU DETAILS MAP

- 1. AUCTL2B BITS (0-2); AUCTL3B BITS (3-7)

- 2. AUCTL5B BITS (0-7)

- 3. AU4ADDA(0-15): ONE HEX/CARD

- 4. AUOUTB(0-8): TWO HEX/CARD; ALSO FANS OUT AUNORM (0-7) AND AUCTL4A

- 5. AUNORMA(0-8): TWO HEX/CARD

- 6. AUCTL4A

- 7. AUMULTA(0-8): ONE HEX/CARD

- 8. AUROMFFB, BITS (0-12); AU4CLT1A, BITS (13-15)

(B)130856A (2/2)

Figure A-5. 4XCP Details Locations (Sheet 2 of 2)

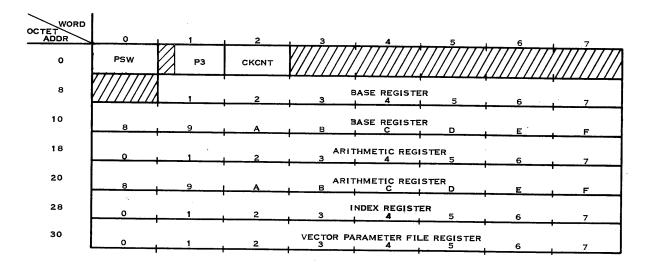

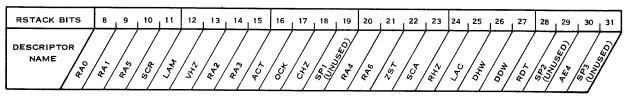

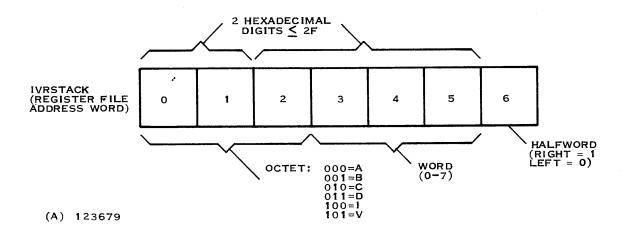

REGISTER STACK FORMAT -  $I \begin{pmatrix} 0 \\ 1 \\ 2 \\ 3 \end{pmatrix} QR \begin{pmatrix} 5 \\ 6 \\ 7 \\ 8 \\ 9 \\ 6 \\ B \end{pmatrix}$  (8-31), IPU DETAILS MAP WORDS 3,4,5, AND 6

SP1

SP2

SP3

SPARE (UNUSED) RSTACK BITS

REGISTER ADDRESS BITS - RA0-6

BITS 0-2 DECODED TO SELECT RF OCTET (A-V)

BITS 4-5 DECODED TO SELECT WORD (0-7) IN OCTET

BIT 6 SELECT LEFT (=0) OR RIGHT (=1) HW IN WORD

SCR - SHORT CIRCUIT REGISTER OPERAND

SCA - SHORT CIRCUIT ALPHA OPERAND

LAM - LOAD ARITHMETIC MASK

LAC - LOAD ARITHMETIC CONDITION

VHZ - VECTOR HAZARD (VPF BEING MODIFIED)

CHZ - COMPARE CODE HAZARD INSTRUCTION TYPE

RHZ - RESULT CODE HAZARD INSTRUCTION TYPE

AEH - ARITHMETIC EXCEPTION HAZARD INSTRUCTION TYPE

ACT - LEVEL 5-C ACTIVITY BIT

OCK - ONE CLOCK INSTRUCTION TYPE

ZST - Z STORE (CM DESTINATION) INSTRUCTION TYPE

DHW - DESTINATION HALFWORD

DDW - DESTINATION DOUBLEWORD

RDT - REGISTER FILE DESTINATION INSTRUCTION TYPE

(B)131560

Figure A-6. 4X IPU Register Stack Format

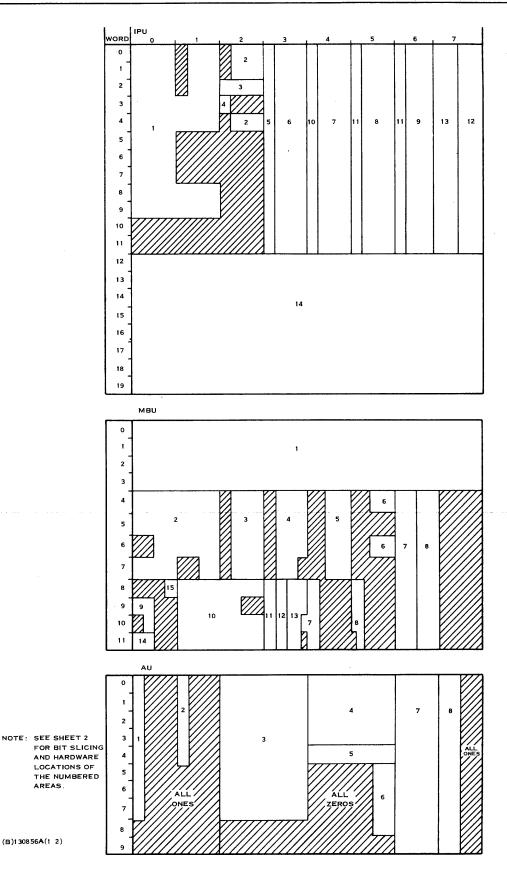

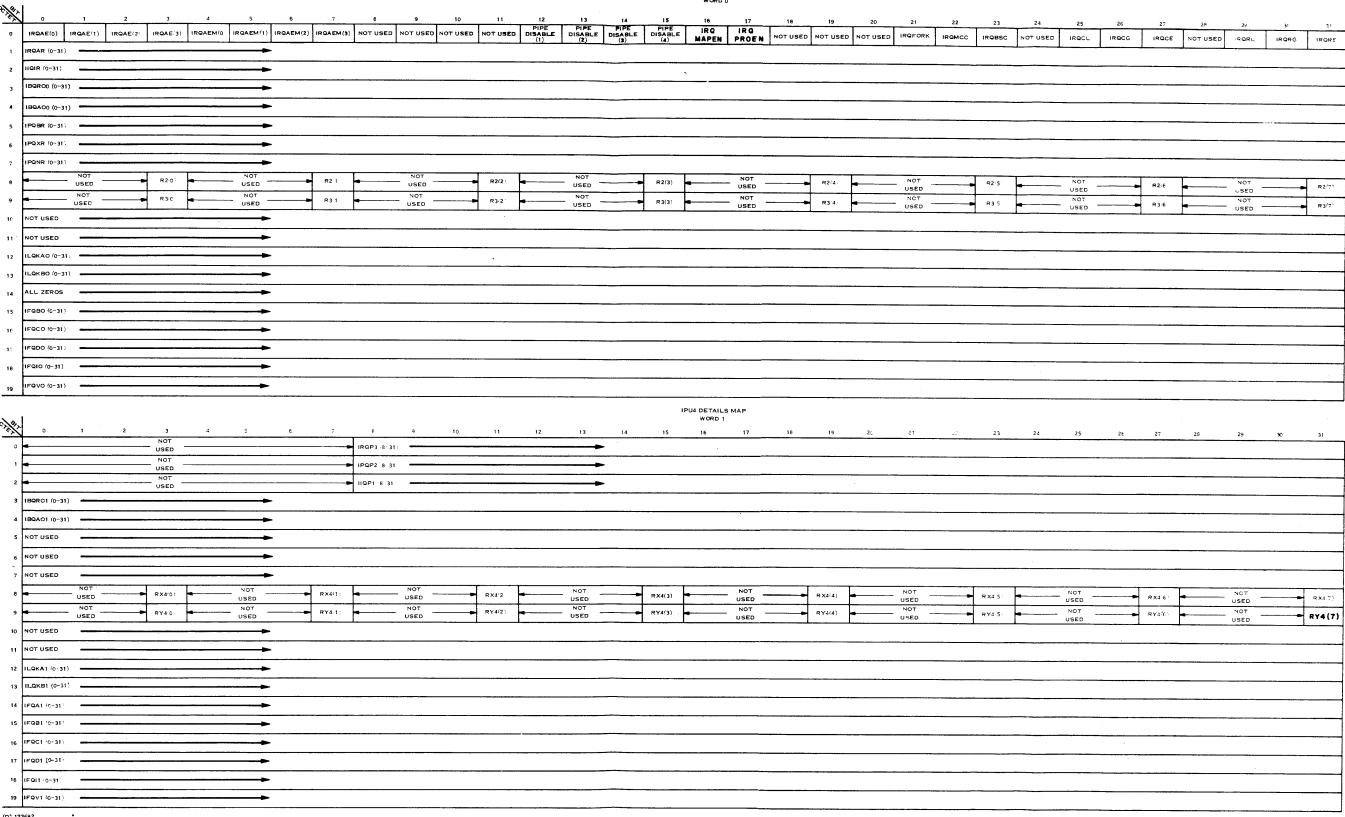

#### IPU 4 DETAILS MAP, WORD 0

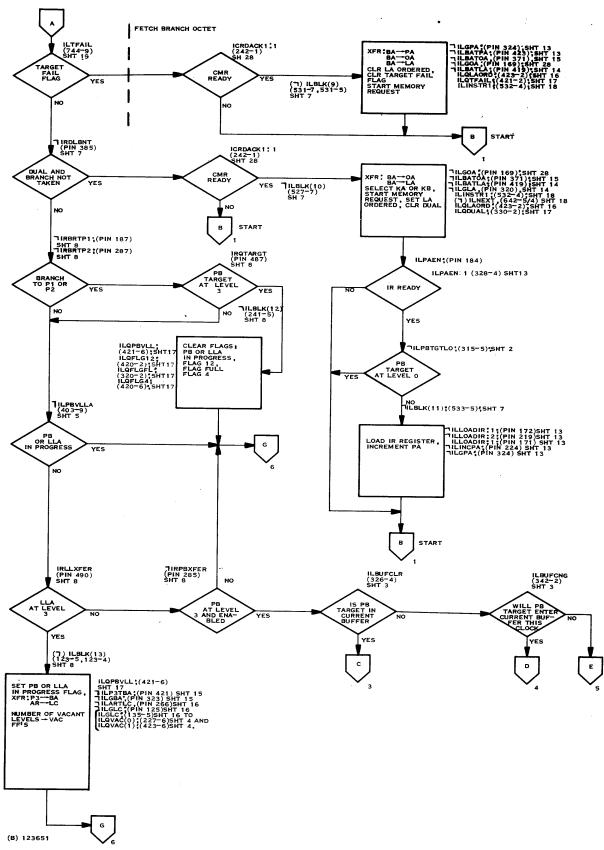

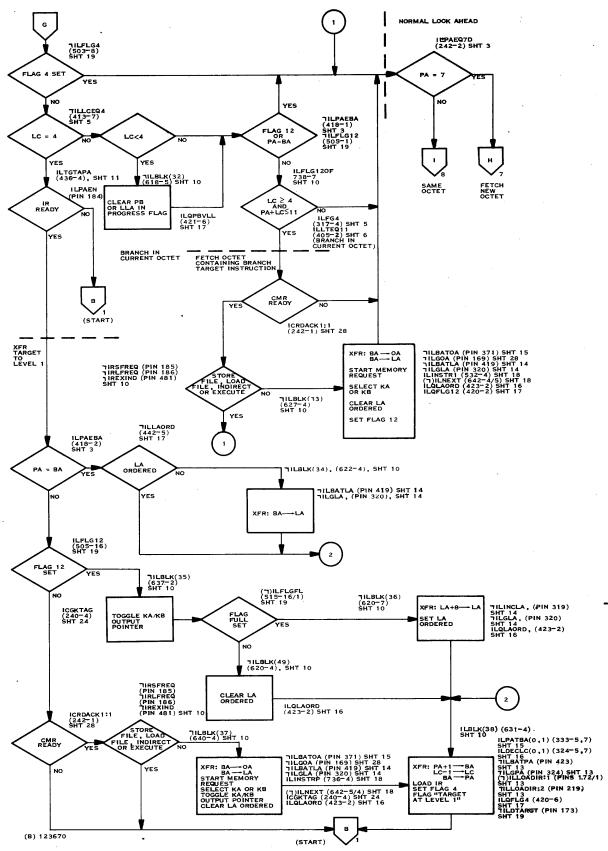

Figure A-7. 4X IPU Details Map (Sheet 1 of 4)

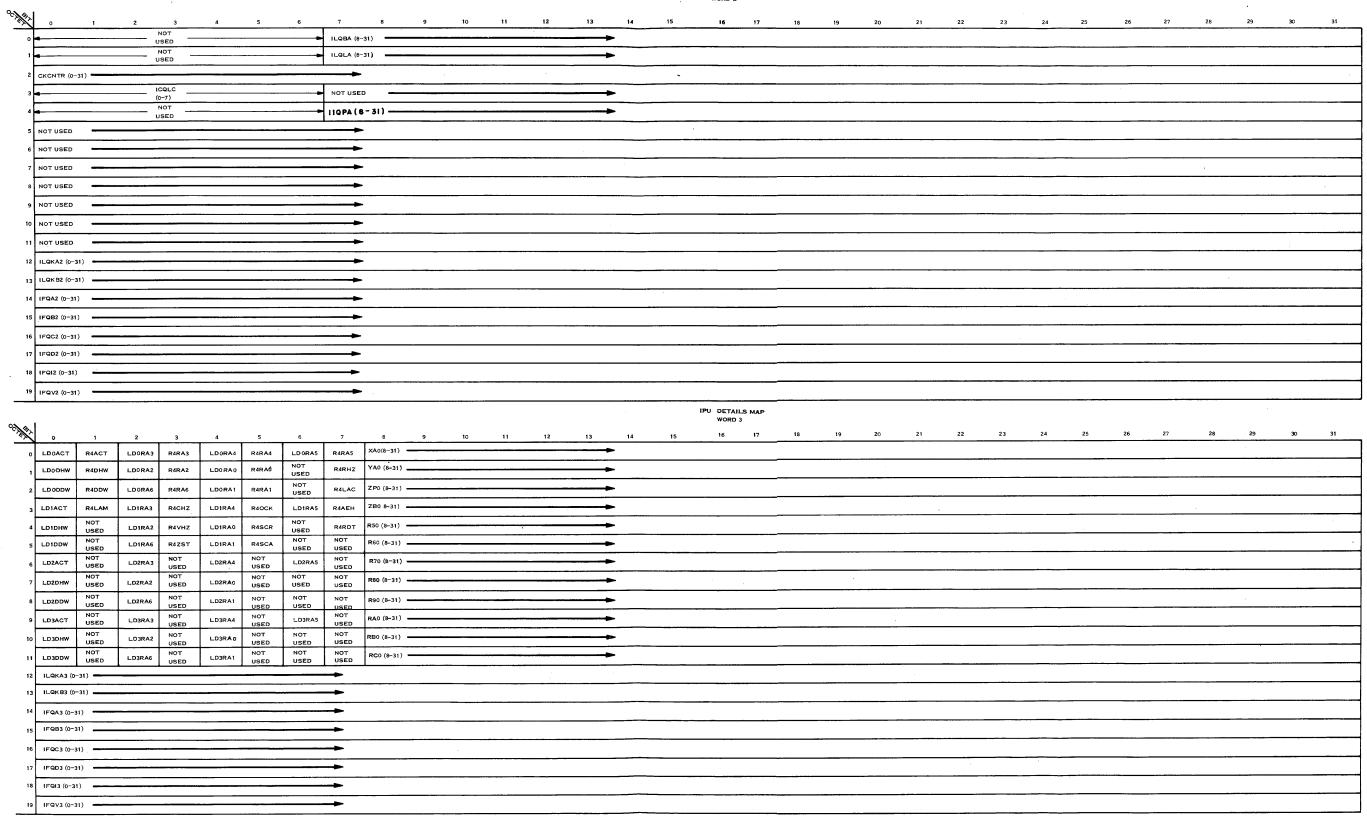

IPU4 DETAILS MAP WORD 2

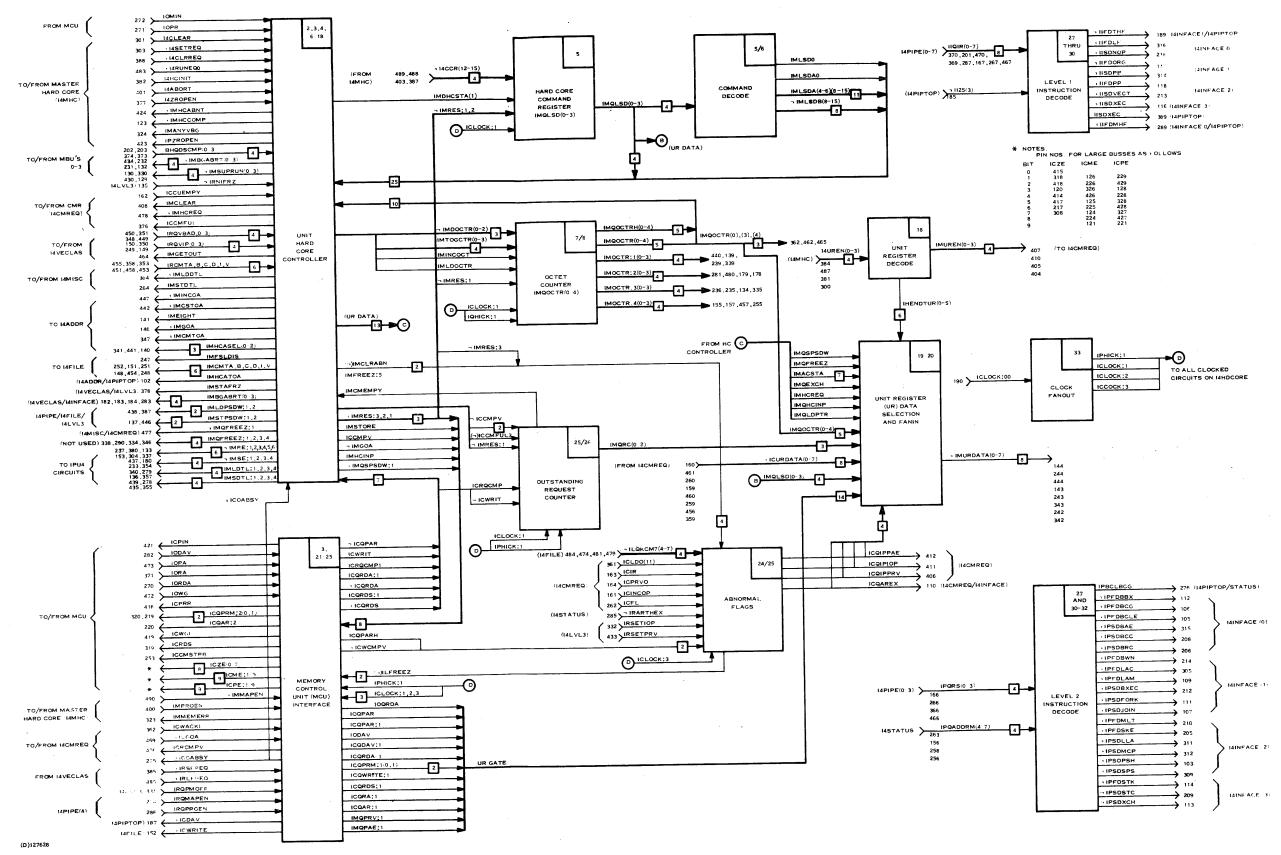

(D) 12368

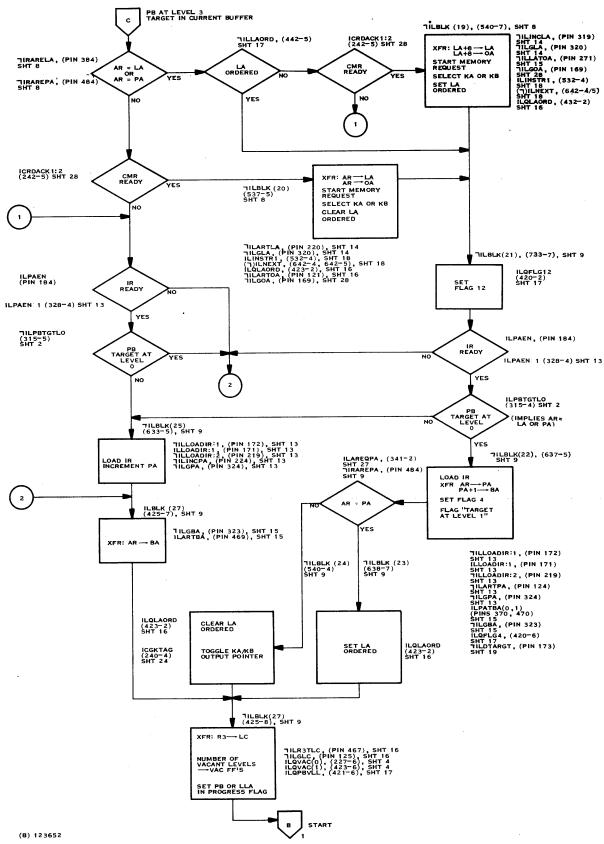

Figure A-7. 4X IPU Details Map (Sheet 2 of 4)

(D) 123684

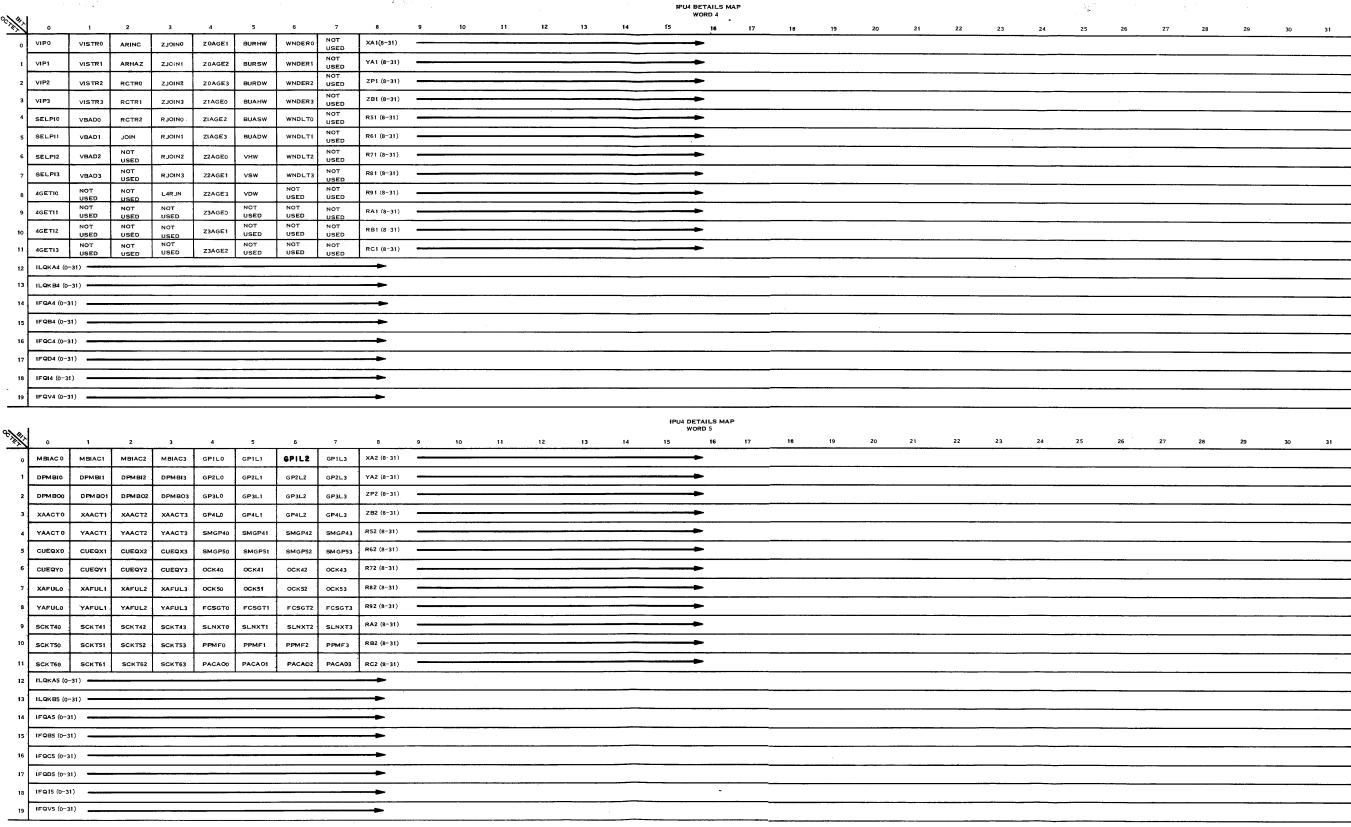

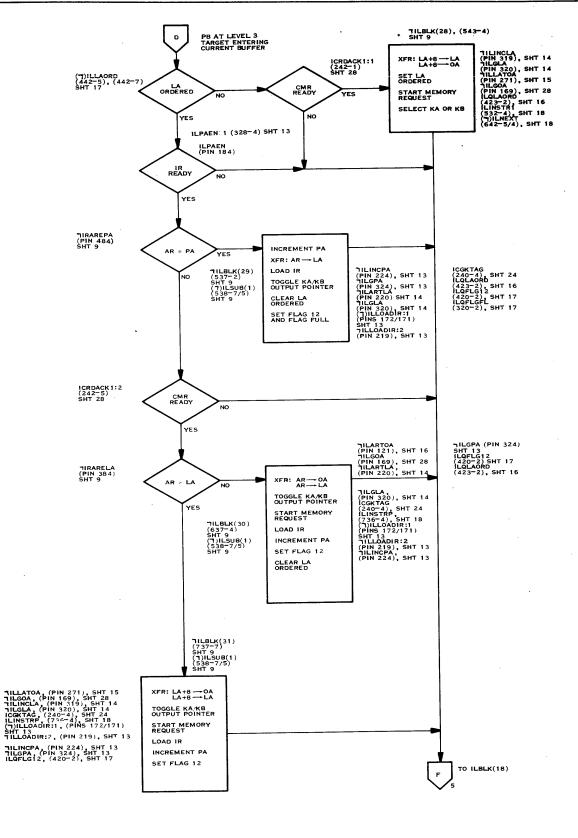

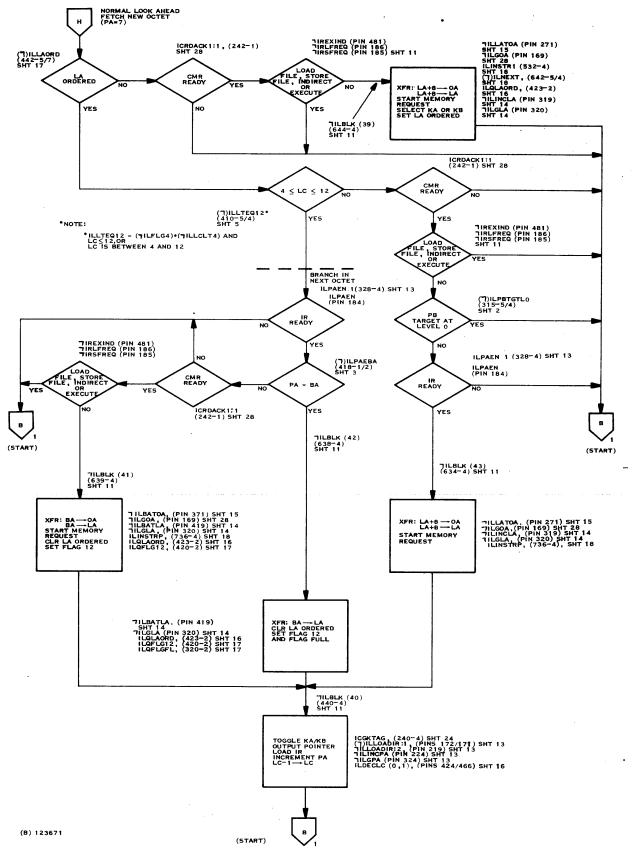

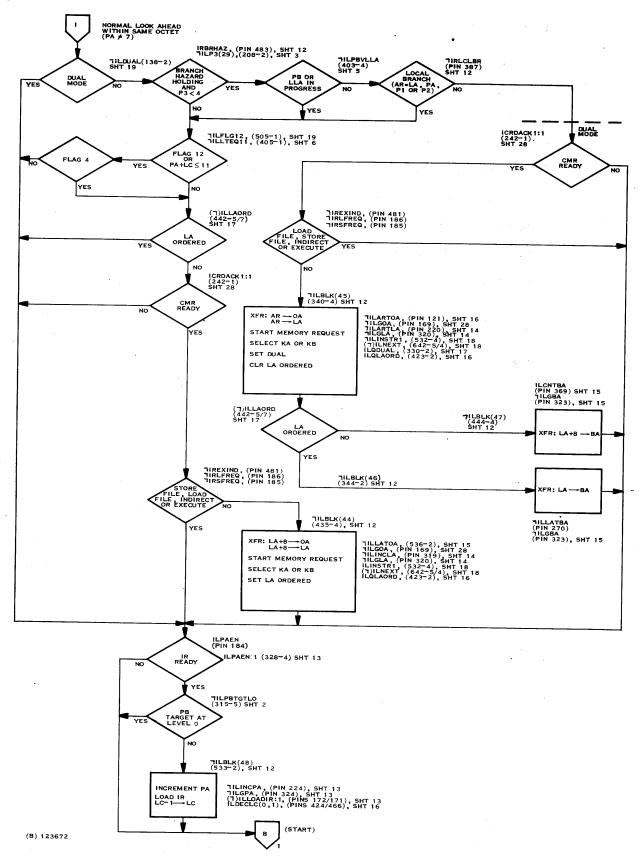

Figure A-7. 4X IPU Details Map (Sheet 3 of 4)

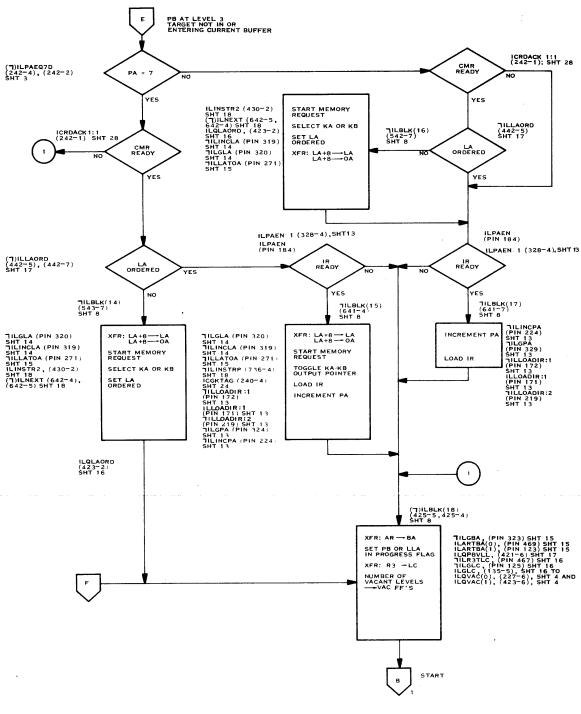

IPU4 DETAILS MAR XA3 (8-31) ENAB3 QIRTO QIRT1 QIR T2 QIRT3 ENAB2 ENAB1 ENA BO YA3 (8-31) MODE MODE2 R OM 8 3 MODEO ROM93 LDXA2 LDXA3 ZP3 (8-31) ROM91 ROM92 LDXBA3 ZB3 (8-31) LDXBA LDXBA ROMAI ROMA2 ROMA3 LDYA2 R53 (8-31) LDYAI ROMB0 ROM B3 LDYA0 R63 (8-31) LDYBA0 LDYBA LDYBA2 LDYBA3 ROMC3 ROMC2 ROMC1 R73 (8-31) REGEW REQFW2 REQFW3 REQFWO R83 (8-31) YUP2 YUP0 YUP1 FWWT3 FWWT1 FWWT2 ZTXU2 ZTXU3 R93 (8-31) ZPFUL3 ZTXU0 ZTXU1 ZPFULO RA3 (8-31) ZBFUL3 ZTYU0 ZTYU1 ZTYU3 ZBFUL2 ZBFULC ZBFULI REGDP2 REGDP3 RB3 (8-31) ZEX3 REGDPO REGDP RC3 (8-31) IMM3 IMM2 ZEY3 IMM1 ZEY0 ZEY1 ZEY2 ILQKA6 (C-31) ILQKB6 (0-31) IFQA6 (0-31) IFQB6 (0-31) IFQC6 (0-31) IFQD6 (0-31) IFQ16 (0-31) IFQV6 (0-31) IPU4 DETAILS MAP PRMGP4 PRMGP3 PRMGP1 PRMAU PRMBR PRMAEH PRMEXN PRMEXM NOT USED PRMRA6 PRMIDW L3PWT PRMRAI NOT L3PPL L3CHK VAC0 VACI CCTR0 LIACT YNEXTO L3ACT CCRT2 CCRT3 CCRT1 NOT USED USED USED NOT USED L3BWN L3IWT L3IHZ RIHIB YNEXT1 PRMDHV DUAL TFAIL CCTRI HQS01 PR VI LAORD RCRT3 RCRT1 RCRT2 C3AU7 C3GP1 C3GP4 C3AU5 C3AU6 C3EXN C3FXM C3AU4 C3RA6 C3RA1 OPDN C3RA0 110502 FRHAZI YNEXT2 CCTR2 FLG12 FLG4 ADDRM4 ADDRM NOT USED NOT USED NOT USED C3SDW C3MDV NOT USED СЗМ C3RHZ C3CAR C3ISW C3DHW C3DDW C3IHW YNEXT3 QIP0 QIP1 L2ACT TARGT1 T10 T11 -T12 T13 USED NOT USED NOT USED USED NOT USED RRMBRI USED PRV3 TARGT3 RRMADW ILOP RRMAHW QBSY3\* ZMAL10 FRHAZ3 QBSY2\* QBSY0\* QBSYI NOT USED NOT USED NOT USED NOT USED RRMSGT RRMIDZ RRMGRN USED RRMSYL CRSLT TRMIN POIND RRMSP 110505 ZMAL11 CUE00 CUE10 FRHAZ2 AROT27 AROT28 AROT29 **АСТО**\* AROT26 NOT USED PDCTH PMOFF MEQO IND3 PDCMH CUE11 TARGT AROT32 PRV1 ACT1\* CUE01 USED USED USED AROT30 AROT31 NOT USED NOT USED NOT USED NOT USED PDCXEC NOT USED PDCVCT NOT USED PDCORG PDCPB USED USED USED HDW PDCLF USED CUE12 11**Q**S07 ZMAL13 PRV2 ACT2\* CUE02 M 12 USED USED USED M13 NOT USED NOT USED NOT USED NOT NOT NOT USED NOT USED RDCXEC NOT RDCPP RDCVCT USED RDCORG L3VPf L3VBR RDCLF RDCNOF NOT NOT USED 119508 L3FLW USED CUE13 M20 ACT3\* CUE03 PRV3 USED USED NOT USED USED RDCSTK RDCSTC RDCLLA RDCPSH RDCXCH RDCBBX RDCBCC RDCBCG RDCBWN RDCBX RDCFR RDCIN L3ORW L3ORM RDCBAE NOT USED NOT USED NOT KAPRV KAHAZ 110509 NOT USED USED USED USED NOT USED NOT USED GAOSC1 RDCSKE RDCSPS GAOSC2 RDCLAM NOT USED RDCLAC RDCBRC GAOSC0 NOT PIRT2 USED M22 UQS10 NOT NOT USED NOT NOT USED KBPRV KBHAZ USED USED USED NOT NOT USED AUIAC3 L7ACT2 DAVWT2 NOT USED L7ACT1 DAVWTI AUIAC2 L7ACT0 NOT USED IPPRV\* STATE PIRT3 IPPAE\* IPIOP\* AREX ILQKA7 (0-31) ILQKB7 (0-31) IFQA7 (0-31) IFQC7 (0-31) IFQD7 (0-31) 1FQV7 (0-31)

(D) 123900

ANOTE DO NOT LOAD ACTO, ACTI, ACT2, ACT3,

QBSY0, QBSY1, QBSY2, QBSY3,

AREX, IPPAE, IPIOP, IPPRV

Figure A-7. 4X IPU Details Map (Sheet 4 of 4)

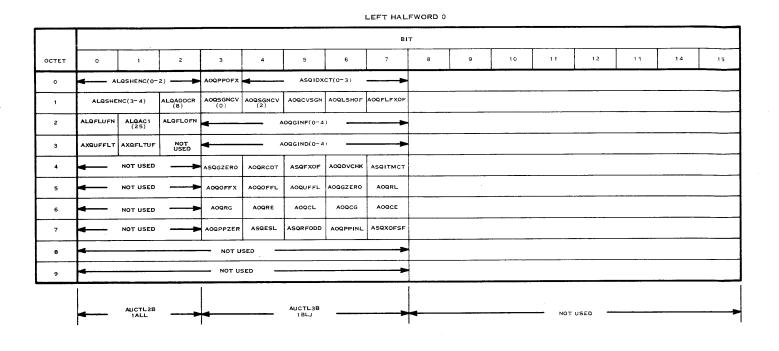

#### LEFT HALFWORD 0

|       | віт            |                |                |                |                |         |             |         |              |       |       |       |               |                 |                 |                 |

|-------|----------------|----------------|----------------|----------------|----------------|---------|-------------|---------|--------------|-------|-------|-------|---------------|-----------------|-----------------|-----------------|

| OCTET | 0              | 1              | 2              | 3              | 4              | 5       | 6           | 7       | 8            | 9     | 10    | 11    | 12            | 13              | 14              | 15              |

| 0     | •              |                |                |                |                |         |             | BRQXOL  | .(0-15)      |       |       |       |               |                 |                 | -               |

| 1     | 4              |                |                |                |                |         |             | BRQYOL  | .(0-15)      |       |       |       |               |                 |                 |                 |

| 2     | -              |                |                |                |                |         |             | BRQZOL  | .(0-15)      |       |       |       |               |                 |                 | -               |

| 3     | -              |                |                |                |                | -       | <del></del> | BIQMAL  | .(0-15)      |       |       |       |               |                 |                 |                 |

| 4     | -              |                |                |                |                |         |             | BLQLPS  | 6(0-15)      |       |       |       |               |                 |                 |                 |

| 5     | 4              |                |                |                |                |         |             | BLQNIS  | (0-15)       |       | · ·   |       |               |                 |                 | -               |

| 6     | •              |                |                |                |                |         |             | - NOT   | JSED —       |       |       |       |               |                 |                 |                 |

| 7     |                |                |                |                |                |         |             | BAQZM   | (0-15)       |       |       |       |               |                 |                 |                 |

| 8     | •              |                |                |                |                |         |             | - NOT   | USED -       |       |       |       |               |                 |                 | -               |

| 9     | BCQ<br>STAT(0) | BCQ<br>STAT(1) | BCQ<br>STAT(2) | BCQ<br>STAT(3) | BCQ<br>ACCT(0) | ACCT(1) | ACCT(2)     | ACCT(3) | BCQ<br>SV(0) | SV(1) | 5v(2) | SV(3) | BCQ<br>HS(0)  | AVCAC(0)        | BCQ<br>AVCAC(1) | BCQ<br>AVCAC(2) |

| 10    | •              |                |                |                |                | - NOT   | USED -      |         |              |       |       |       | BCQ<br>VIS(0) | BCQ<br>AAUAC(0) | BCQ<br>AAUAC(1) | BCQ<br>VCNOP    |

| 11    | •              |                |                |                |                |         |             | BFQP(0  | i=15)        |       |       |       |               |                 |                 |                 |

#### RIGHT HALFWORD 0

|       | віт |   |   |          |   |   |   |           |          |   |    |       |          |    |    |    |

|-------|-----|---|---|----------|---|---|---|-----------|----------|---|----|-------|----------|----|----|----|

| OCTET | 0   | 1 | 2 | 3        | 4 | 5 | 6 | 7         | 8        | 9 | 10 | 11    | 12       | 13 | 14 | 15 |

| 0     | 4   |   |   |          |   |   |   | BRQX0     | R(0-15)  |   |    |       |          |    |    |    |

| 1     | •   |   |   |          |   |   |   | BRQY0     | R(0-15)  |   |    |       |          |    | ., |    |

| 2     | -   |   |   |          |   |   |   | BRQZO     | R(0-15)  |   |    |       |          |    |    |    |

| 3     | 4   |   |   |          |   |   |   | - BIQMAI  | R(0-15)  |   |    | ·     |          |    |    | -  |

| 4     | -   |   |   |          |   |   |   | - BLQFL   | P(0~15)  |   |    |       |          |    |    |    |

| 5     | -   |   |   |          |   |   |   | - BLQFN   | 1(0-15)  |   |    |       |          |    |    |    |

| 6     | •   |   |   |          |   |   | - | - BLQFN   | 0(0-15)  |   |    |       |          |    |    |    |

| 7     | -   |   |   |          |   |   |   | BAQZB     | M(0-15)  |   |    |       |          |    |    |    |

| 8     | -   |   |   | NOT USED |   |   |   | BMOROM IS | <b>-</b> |   |    | BMQRO | MIN(1-8) |    |    |    |

| 9     | -   |   |   |          |   | - |   | - NOT     | USED —   |   |    |       |          |    |    |    |

| 10    | -   |   |   |          |   |   |   | NOT       | USED -   |   |    |       |          |    |    |    |

| 11    | -   |   |   |          |   |   |   | NOT       | USED -   |   |    |       |          |    |    |    |

#### LEFT HALFWORD 1

|       | 917      |   |   |                     |     |            |       |          |            |   |    |     |                                       |                    |                     |    |

|-------|----------|---|---|---------------------|-----|------------|-------|----------|------------|---|----|-----|---------------------------------------|--------------------|---------------------|----|

| OCTET | 0        | 1 | 2 | 3                   | 4   | 5          | 6     | 7        | 8          | 9 | 10 | 11  | 12                                    | 13                 | 14                  | 15 |

| 0     | 4        |   |   |                     |     |            |       | BRQXII   | L(0-15)    |   |    |     |                                       |                    |                     |    |

| 1     | •        |   |   |                     |     |            |       | BRQY1    | L(0-15)    |   |    |     | · · · · · · · · · · · · · · · · · · · |                    |                     | >  |

| 2     | •        |   |   |                     |     |            |       | BRQZ 1   | L(0-15)    |   |    |     |                                       |                    |                     | -  |

| 3     | •        |   |   |                     |     |            |       | • віомв  | L(0-15)    |   |    |     |                                       |                    |                     |    |

| 4     | -        |   |   |                     |     |            |       | BLQGL    | P(0-15)    |   |    |     |                                       |                    |                     |    |

| 5     | •        |   |   |                     |     |            |       | - BLQGN  | I(0-15)    |   |    |     |                                       |                    |                     |    |

| 6     | -        |   |   |                     |     |            |       | - BLQGN  | 0(0-15)    |   |    |     |                                       |                    |                     |    |

| 7     | •        |   |   |                     |     |            |       | - нот    | USED —     |   |    |     |                                       |                    |                     |    |

| 8     | -        |   |   |                     |     |            |       | - BMQROM | ют(0-15)   |   |    |     |                                       |                    |                     |    |

| 9     | -        |   |   |                     |     |            |       | - BMQROM | IOT(16-31) |   |    |     |                                       |                    |                     |    |

| 10    | -        |   |   |                     | вме | PROMOT(32- | 42) — |          |            |   |    | NOT | USED                                  | _                  | 8MQROMOT<br>(45-47) |    |

| 11    | NOT USED | • |   | BMQROMOT<br>(49-53) |     |            | -     |          | NOT USED   |   |    | -   |                                       | BMQROMO<br>(59-63) | T                   |    |

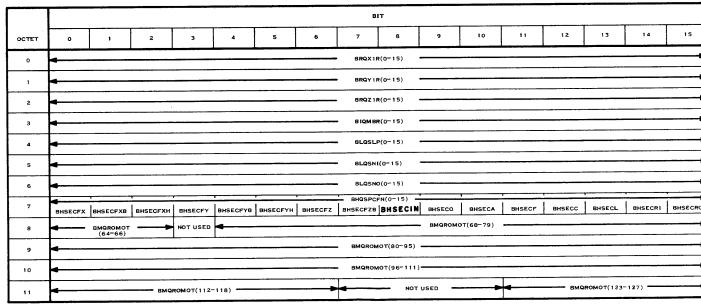

#### RIGHT HALFWORD 1

(D)127613 (1/4)

Figure A-8. 4X MBU Details Map (Sheet 1 of 4)

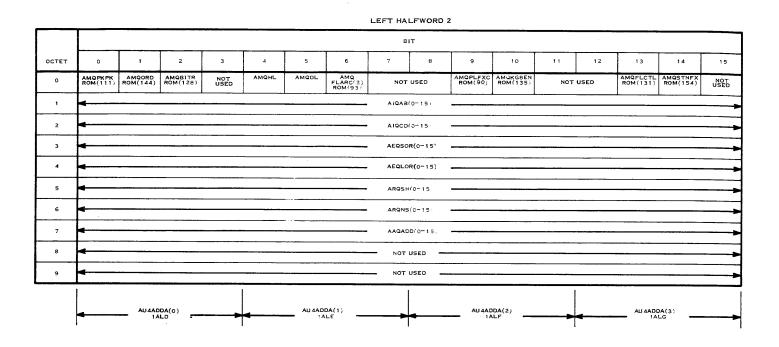

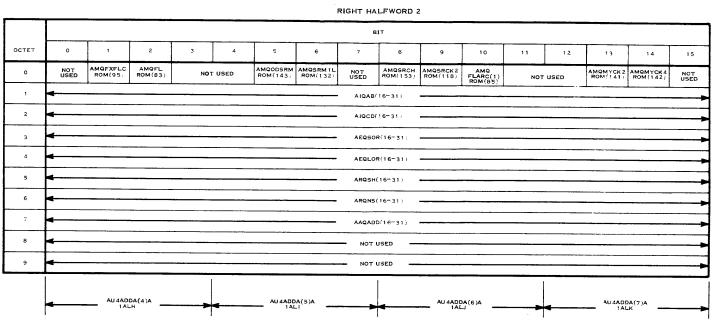

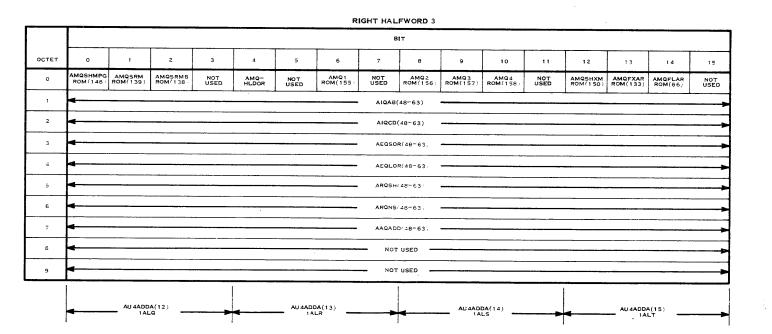

#### LEFT HALFWORD 2

|       | віт |                       |   |          |   |          |         |            |                 |                                       |      |            |      |                       |     |      |

|-------|-----|-----------------------|---|----------|---|----------|---------|------------|-----------------|---------------------------------------|------|------------|------|-----------------------|-----|------|

| ОСТЕТ | 0   | 1                     | 2 | 3        | 4 | 5        | 6       | 7          | 8               | 9                                     | 10   | 11         | 12   | 13                    | 1 4 | 15   |

| 0     | •   |                       |   |          |   |          |         | BRQX2      | L(0-15)         |                                       |      |            |      |                       |     | -    |

| 1     | •   |                       |   |          |   |          |         | BRQY 2     | L(0-15)         |                                       |      |            |      |                       |     | -    |

| 2     |     |                       |   |          |   |          |         | BRQZ 2     | L(0-15)         |                                       |      |            |      |                       |     |      |

| 3     |     |                       |   |          |   |          |         | BIOREGO    | )L(0-15)        |                                       |      |            |      |                       |     | -    |

| 4     | -   |                       |   | NOT USED |   |          |         | •          |                 |                                       |      | BAQNAA(8-1 | 6)   |                       |     |      |

| 5     | •   |                       |   | NOT USED |   |          | -       | -          |                 |                                       |      | BAQNBA(8-1 | 6)   |                       |     |      |

| 6     | •   |                       |   | NOT USED |   |          |         | -          |                 |                                       |      | BAQNCA(8-1 | 6) — |                       |     |      |

| 7     | •   |                       |   | NOT USED |   |          |         | -          |                 |                                       |      | BAQNSA(8-1 | 6)   |                       |     |      |

| 8     | 4   |                       |   |          |   |          |         | вмогомо    | T(128-143)      |                                       |      |            |      |                       |     | _    |

| 9     | -   |                       |   |          |   |          |         | вмогомо    | T(144-159)      |                                       |      |            |      |                       |     |      |

| 10    |     |                       |   |          |   |          | вмогомо | T(160-173) |                 | · · · · · · · · · · · · · · · · · · · |      |            |      |                       | NOT | USED |

| 11    |     | BMQROMOT<br>(176~178) |   | -        |   | NOT USED |         |            | BMQROMOT<br>184 | нот                                   | USED | <u> </u>   |      | BMQROMOT<br>(187-191) |     |      |

## BMQROMOT(224-239)

BMQROMOT(240-249)

OCTET

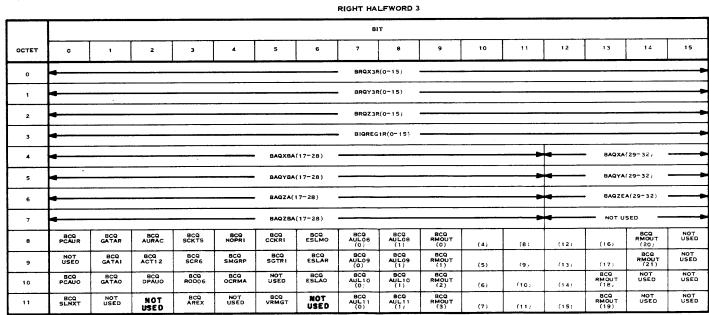

#### LEFT HALFWORD 3

|       | віт                 |                     |                    |                     |                     |                     |              |              |                      |              |              |               |               |              |              |              |

|-------|---------------------|---------------------|--------------------|---------------------|---------------------|---------------------|--------------|--------------|----------------------|--------------|--------------|---------------|---------------|--------------|--------------|--------------|

| OCTET | 0                   | 1                   | 2                  | 3                   | 4                   | 5                   | 6            | 7            | 8                    | 9            | 10           | 11            | 12            | 13           | 14           | 15           |

| ٥     | •                   |                     |                    |                     |                     |                     |              | BRQX3        | L(0-15)              |              |              |               |               |              |              |              |

| 1     |                     |                     |                    |                     |                     |                     |              | BRQY3        | L(0-15)              |              |              |               |               |              |              |              |

| 2     | •                   |                     |                    |                     |                     |                     |              | BRQZ3        | L(0+15)              |              |              |               |               |              |              |              |

| 3     | •                   |                     |                    |                     |                     |                     |              | BIQRE        | 51L(0-15)            |              |              |               |               |              |              |              |

| 4     | •                   |                     |                    | нот                 | used —              |                     |              | >            | •                    |              |              | BAQXBA(8-16)  |               |              |              |              |

| 5     | •                   |                     |                    | том т               | USED -              |                     |              |              | -                    |              |              | BAQYB         | A(8-16)       |              |              | -            |

| 6     | 4                   |                     |                    | нот                 | USED —              |                     |              |              | •                    |              |              | BAQZA         | (8-16)        |              |              | -            |

| 7     | -                   |                     |                    | NОТ                 | USED -              |                     |              | >            | -                    |              |              | BAQZB         | A(8-16)       |              |              |              |

| 8     | BCQ<br>CUEPO<br>(0) | BCQ<br>CUEPO<br>(1) | BCQ<br>CUEO<br>(0) | BCQ<br>CUEO<br>(1)  | BCQ<br>CUE 4<br>(0) | BCQ<br>CUE 4<br>(1) | ZBREQ        | XBREQ        | XBREQ                | BCQ<br>NSFUL | BCQ<br>HWC   | BCQ           | BCQ<br>SWC    | BCQ<br>IMFUL | BCQ<br>MBIAC | BCQ<br>SRMST |

| 9     | BCQ<br>CUEP1<br>(0) | BCQ<br>CUEP1<br>(1) | BCQ<br>CUE1<br>(0) | BCQ<br>CUE 1<br>(1) | BCQ<br>CUE5<br>(0)  | BCQ<br>CUE5<br>(1)  | BCQ<br>Z88SY | BCQ<br>YNEXT | NOT<br>USED          | BCQ<br>ZAFUL | BCQ<br>HWZ   | BCQ<br>DWZ    | BCQ<br>VIC    | BCQ<br>RGFUL | DPM81<br>BCQ | PVCAO        |

| 10    | BCQ<br>CUEP2<br>(0) | BCQ<br>CUEP2<br>(1) | BCQ<br>CUE2<br>(0) | BCQ<br>CUE2<br>(1)  | BCQ<br>CUE6<br>(0)  | BCQ<br>CUE6<br>(1)  | BCQ<br>IZBSY | BCQ<br>ZFILN | NOT<br>USED          | BCQ<br>ZFUL  | BCQ<br>SLPE1 | BCQ<br>SNIE 1 | BCQ<br>SNOE 1 | BCQ<br>YFRST | BCQ<br>DPMBO | BCQ<br>LSENC |

| 11    | BCQ<br>PRVLT        | BCQ<br>PARER        | BCQ<br>CUE3<br>(0) | BCQ<br>CUE3<br>(1)  | BCQ<br>CUE7<br>(0)  | BCQ<br>CUE7<br>(1)  | BCQ<br>ZWAIT | VZAZB        | BCQ<br>V <b>LSTW</b> | CVEND        | BCQ<br>SLPE0 | SNIE0         | BCQ<br>SNOE0  | VORST        | BCQ<br>AGRTR | TOGLE        |

#### (D)127613 (2/4)

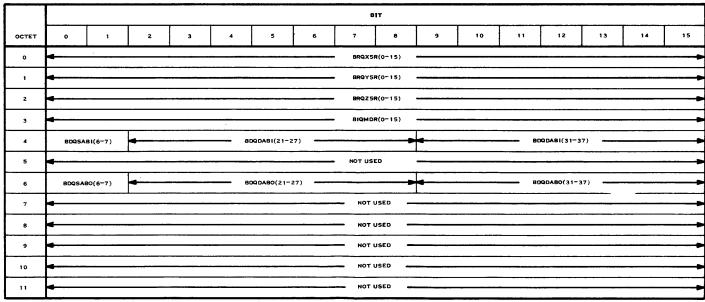

RIGHT HALFWORD 2

BIT

BRQY2R(0-15)

BAQNAA(17-32)

BAQNBA(17-32)

BAQNSA(17-32)

NOT USED

BMQROMOT(192-206)

Figure A-8. 4X MBU Details Map (Sheet 2 of 4)

NOT

#### LEFT HALFWORD 4

|       |               |                     |                      |                       |                      |                      |       | В       | IT      |   |       |        |    |    |        |        |

|-------|---------------|---------------------|----------------------|-----------------------|----------------------|----------------------|-------|---------|---------|---|-------|--------|----|----|--------|--------|

| OCTET | 0             | 1                   | 2                    | 3                     | 4                    | 5                    | 6     | 7       | 8       | 9 | 10    | 11     | 12 | 13 | 14     | 15     |

| 0     | -             |                     |                      |                       |                      |                      |       | BRQX4   | L(0-15) |   |       |        |    |    |        |        |

| 1     | •             |                     |                      |                       |                      |                      |       | - BRQY4 | L(0-15) |   |       |        |    |    |        |        |

| . 2   |               |                     |                      |                       |                      |                      |       | BRQZ4   | L(0-15) |   |       |        |    |    |        |        |

| 3     | -             |                     |                      |                       |                      |                      |       | віомс   | L(0-15) |   |       |        |    |    |        |        |

| 4     | •             |                     |                      |                       |                      |                      | нот   | USED -  |         |   |       |        |    | -  | BDQSAB | 1(0-1) |

| 5     | -             |                     |                      |                       |                      |                      | — нот | USED -  |         |   |       |        |    | -  | BDQSDC | 1(0-1) |

| 6     | •             |                     |                      |                       |                      |                      | - NOT | USED -  |         |   |       |        |    |    | BDQSAB | 0(0-1) |

| 7     | •             |                     |                      |                       |                      |                      | - NOT | USED -  |         |   |       |        |    | -  | BDQSDC | 0(0-1) |

| 8     | BCQDWA<br>(0) | BCQVIA<br>(0)       | BLQFL-<br>PEO<br>(0) | BLQFL-<br>PE1<br>(0)  | BCQFS-<br>TAO<br>(0) | BCQX-<br>FUL<br>(0)  | ◀     |         |         |   | - нот | USED — |    |    |        |        |

| 9     | BCQSWA<br>(0) | BCQAV-<br>SV<br>(0) | BLQFN-<br>IEO<br>(0) | BLQFN-<br>IE 1<br>(0) | BCQFS-<br>TA1<br>(0) | BCQXH-<br>FUL<br>(0) | •     |         |         |   | - NOT | USED — |    |    |        |        |

| 10    | BCQHWA<br>(0) | NOT<br>USED         | BLQFN-<br>OEO<br>(0) | BLQFN-<br>OE 1<br>(0) | BCQXA-<br>ENL<br>(0) | BCQXB-               | •     |         |         |   | — нот | USED   |    |    |        |        |

| 11    | -             | - NOT               | USED -               |                       | BCQXA-<br>LSE<br>(0) | BCQXA-<br>FUL<br>(0) | •     |         |         |   | - NOT | USED - |    |    |        |        |

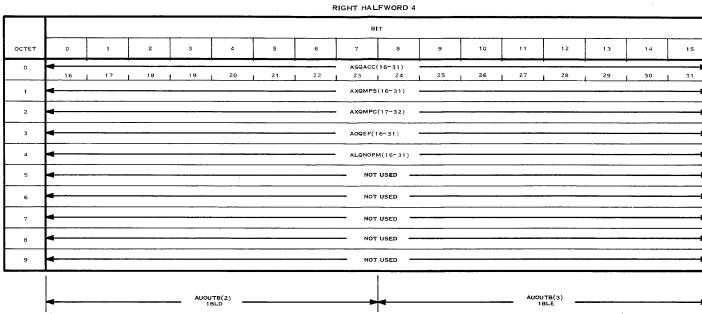

#### RIGHT HALFWORD 4

|       |       |         |   |   | - |             |      | В       | IT      |   |    |     |             |      |    |    |

|-------|-------|---------|---|---|---|-------------|------|---------|---------|---|----|-----|-------------|------|----|----|

| OCTET | o     | 1       | 2 | 3 | 4 | 5           | 6    | 7       | 8       | 9 | 10 | 1.1 | 12          | 13   | 14 | 15 |

| 0     | •     |         |   |   |   |             |      | BRQX4F  | R(0-15) |   |    |     |             |      |    |    |

| 1     | •     |         |   |   |   |             |      | BRQY4F  | R(0-15) |   |    |     |             |      |    | -  |

| 2     | •     |         |   |   |   |             |      | BRQZ 4F | R(0-15) |   |    |     |             |      |    |    |

| 3     | •     |         |   |   |   |             |      | вічмся  | 1(0-15) |   |    |     |             |      |    | -  |

| 4     | BDQSA | BI(2-3) | - |   | = | BDQDABI(1-7 | ) —  |         |         | • |    |     | OQDABI(11-1 | 17)  |    | -  |

| 5     | BDQSD | ¢1(2-3) | • |   |   | BDQDCI(1-7  | ,    |         |         | - |    | 8   | DQDCI(11-1  | 7) — |    |    |

| 6     | BDQSA | BO(2-3) | - |   |   | BDQDABO(1-7 | ·) — |         |         | 4 |    | BI  | DQDABO(11-  | 17)  |    |    |

| 7     | 80950 | CO(2-3) | • |   |   | BDQDCO(1-7  | ,    |         |         | • |    | 8   | DQDCO(11-1  | 7) — |    | -  |

| 8     | •     |         |   |   |   |             |      | — мот   | USED    |   |    |     |             |      |    |    |

| 9     | -     |         |   |   |   |             |      | - NOT   | USED    |   |    |     |             |      |    | -  |

| 10    |       |         |   |   |   |             |      | — мот   | USED -  |   |    |     |             |      |    |    |

| 11    | -     |         |   |   |   |             |      | - NOT   | USED    |   |    |     |             |      |    | -  |

#### LEFT HALFWORD 5

|       |               |                     |                      |                       |                      |                      |       | 8        | IT      |   |       |        |    |    |        |         |

|-------|---------------|---------------------|----------------------|-----------------------|----------------------|----------------------|-------|----------|---------|---|-------|--------|----|----|--------|---------|

| остет | 0             | 1                   | 2                    | 3                     | 4                    | 5                    | 6     | 7        | 8       | 9 | 10    | 11     | 12 | 13 | 14     | 15      |

| 0     | •             |                     |                      |                       |                      |                      |       | - BRQX5I | -(0-15) |   |       |        |    | -  |        | -       |

| 1     | -             |                     |                      |                       |                      |                      |       | BRQY51   | _(0-15) |   |       |        |    |    |        |         |

| 2     | •             |                     |                      |                       |                      |                      |       | BRQZ51   | -(0-15) |   |       |        |    |    |        |         |

| 3     | •             |                     |                      |                       |                      |                      |       | - BIQMDI | _(0-15) |   | -     |        |    |    |        | -       |

| 4     | •             |                     |                      |                       |                      |                      | — NOT | USED -   |         |   |       |        |    | -  | BDQSA  | 31(4-5) |

| 5     | -             |                     |                      |                       |                      |                      |       | - NOT    | USED -  |   |       |        |    |    |        |         |

| . 6   |               |                     |                      |                       |                      |                      | мот   | USED -   |         |   |       |        |    |    | BDQ\$A | BO(4-5) |

| 7     | •             |                     |                      | -                     |                      |                      |       | - NOT    | USED -  |   |       |        |    |    |        |         |

| 8     | BCQDWA<br>(1) | BCQVIA<br>(1)       | BLQFL-<br>PEO<br>(1) | BLQFL-<br>PE 1<br>(1) | BCQFS-<br>TA0<br>(1) | BCQXF-<br>UL<br>(1)  | -     |          |         |   | - NOT | USED — |    |    |        |         |

| 9     | BCQSWA<br>(1) | BCQA-<br>VSV<br>(1) | BLQFN-<br>IE0<br>(1) | BLQFN-<br>IE1<br>(1)  | BCQFS-               | BCQX-<br>HFUL<br>(1) | 4     |          |         |   | NOT   | USEO 🕳 |    |    |        | >       |

| 10    | BCQHWA<br>(1) | NOT<br>USED         | BLQFN-<br>OE0<br>(1) | BLQFN-<br>OE 1<br>(1) | BCQXA-<br>ENL<br>(1) | BCQXB-<br>FUL<br>(1) | •     |          |         |   | NOT   | USED — |    |    |        |         |

| 11    | •             | — нот               | USED -               | -                     | BCQXA-<br>LSE<br>(1) | BCQXA-<br>FUL<br>(1) | •     |          |         |   | NОТ   | USED - |    |    |        |         |

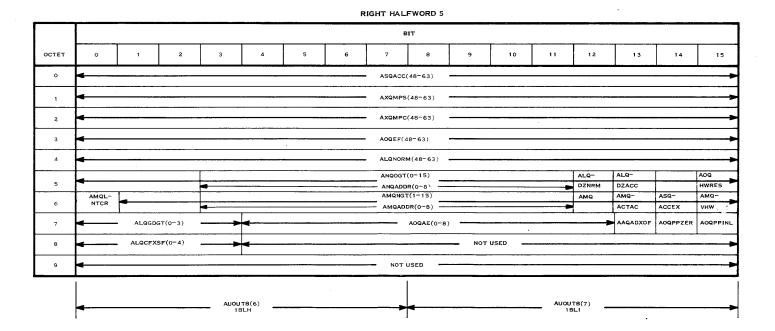

#### RIGHT HALFWORD 5

(D)127613 (3/4)

Figure A-8. 4X MBU Details Map (Sheet 3 of 4)

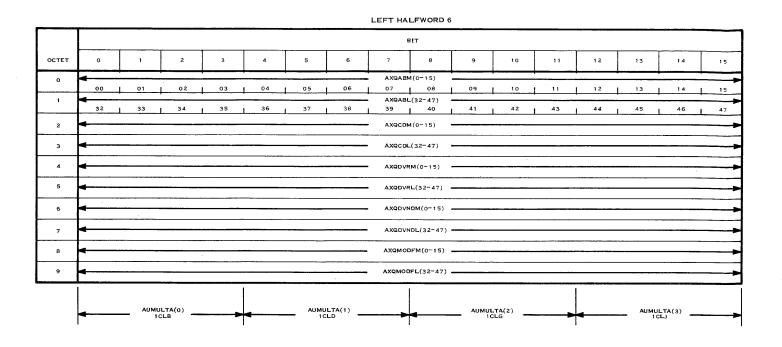

|       |                |                |          |                |                |                |                | LEFT HAL    | FWORD 6         |                 |                 |                 |                 |                 |                 |             |

|-------|----------------|----------------|----------|----------------|----------------|----------------|----------------|-------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------|

|       |                |                |          |                |                |                |                | В           | т               |                 |                 |                 |                 |                 |                 |             |

| OCTET | 0              | 1              | 2        | 3              | 4              | 5              | 6              | 7           | 8               | 9               | 10              | 11              | 12              | 13              | 14              | 15          |

| 0     | 4              |                |          |                |                |                |                | BRQX61      | _(0-15)         |                 |                 |                 | <u> </u>        |                 |                 | >           |

| 1     | -              |                |          |                |                |                |                | BRQY61      | _(0=151         |                 |                 |                 |                 |                 |                 |             |

| 2     | -              |                |          |                |                |                |                | BRQ Z 61    | -(0-15)         |                 |                 |                 |                 |                 |                 |             |