### **TEXAS INSTRUMENTS**

**PROCESSOR**

### **GENERAL DESCRIPTION**

## **EXPLORER™ PROCESSOR GENERAL DESCRIPTION**

#### MANUAL REVISION HISTORY

Revision A.....October 1985

© 1984, 1985, Texas Instruments Incorporated. All Rights Reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Texas Instruments Incorporated.

The computers, as well as the programs that TI has created to use with them, are tools that can help people better manage the information used in their business; but tools—including TI computers—cannot replace sound judgment nor make the manager's business decisions.

Consequently, TI cannot warrant that its systems are suitable for any specific customer application. The manager must rely on judgment of what is best for his or her business.

### THE EXPLORER™SYSTEM HARDWARE MANUALS

| <b>System Level</b> |

|---------------------|

| Hardware            |

| <b>Publications</b> |

| Explorer Unpacking and Inventory Explorer 7-Slot System Installation | 2243216-0001<br>2243140-0001 |

|----------------------------------------------------------------------|------------------------------|

| Explorer System Field Maintenance                                    |                              |

#### System Enclosure Hardware Publications

| Explorer 7-Slot System Enclosure General Description2243143-00Explorer 2-Megabyte Memory General Description2243147-00Explorer Memory General Description2533592-00Explorer Processor General Description2243144-00Explorer Display Unit General Description2243151-00Explorer System Interface General Description2243145-00 | 001<br>001<br>001<br>001 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

#### Mass Storage Hardware Publications

|   | Explorer Mass Storage Enclosure General Description            |

|---|----------------------------------------------------------------|

|   | Explorer Winchester Disk Formatter (ADAPTEC) Supplement        |

|   | to Explorer Mass Storage Enclosure General Description         |

|   | Explorer Winchester Disk Drive (Maxtor) Supplement to          |

|   | Explorer Mass Storage Enclosure General Description            |

|   | Explorer Cartridge Tape Drive (Cipher) Supplement to Explorer  |

| ı | Mass Storage Enclosure General Description                     |

|   | Explorer Cable Interconnect Board (2236120-0001) Supplement to |

|   | Explorer Mass Storage Enclosure General Description            |

|   | Explorer NuBus™ Peripheral Interface                           |

| - | General Description (NUPI board)2243146-0001                   |

|   | 1                                                              |

#### Mass Storage Hardware Vendor Publications

| Series 540 Cartridge Tape Drive Product Description, Cipher Data<br>Products, Inc., Bulletin Number 01-311-0284-1K (¼-inch tape drive) 2249997-0001 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| MT01 Tape Controller Technical Manual, Emulex Corporation,                                                                                          |

| part number MT0151001 (formatter for the ¼-inch tape drive)2243182-0001                                                                             |

| XT-1000 Service Manual, 51/4-inch Fixed Disk Drive,                                                                                                 |

| Maxtor Corporation, part number 20005                                                                                                               |

| (5 <sup>1</sup> / <sub>4</sub> -inch Winchester disk drive, 112 megabytes)                                                                          |

| ACB-5500 Winchester Disk Controller User's Manual,                                                                                                  |

| Adaptec, Inc., (formatter for the $5\frac{1}{4}$ -inch Winchester disk drive) $2249933-0001$                                                        |

|                                                                                                                                                     |

#### Optional Equipment Hardware Publications

Explorer and NuBus are trademarks of Texas Instruments Incorporated. Ethernet is a registered trademark of Xerox Corporation.

### THE EXPLORER™SYSTEM SOFTWARE MANUALS

# Mastering the Explorer Environment

| Explorer Technical Summary                | 2243189-0001 |

|-------------------------------------------|--------------|

| Explorer Operations Guide                 |              |

| Explorer Zmacs Editor Tutorial            |              |

| Explorer Glossary                         | 2243134-0001 |

| Explorer Communications User's Guide      | 2243206-0001 |

| Explorer Diagnostics                      | 2533554-0001 |

| Explorer Master Index to Software Manuals | 2243198-0001 |

| Explorer System Software Installation     | 2243205-0001 |

# Programming With the Explorer

| Explorer Programming Primer | 2537175-0001<br>2243201-0001<br>2243192-0001<br>2243130-0001 |

|-----------------------------|--------------------------------------------------------------|

|                             | 2243200-0001                                                 |

#### **Explorer Toolkits**

| Explorer Natural Language Menu System User's Guide       | 2243202-0001 |

|----------------------------------------------------------|--------------|

| Explorer Relational Table Management System User's Guide | 2243203-0001 |

| Explorer Graphics Toolkit User's Guide                   | 2243195-0001 |

| Explorer Grasper User's Guide                            |              |

| Explorer Prolog Toolkit User's Guide                     | 2243204-0001 |

| Programming in Prolog, by Clocksin and Mellish           |              |

| Explorer Color Graphics User's Guide, Support for the    |              |

| Raster Technologies Model One                            | 2537157-0001 |

| Explorer TCP/IP User's Guide                             |              |

| •                                                        |              |

# System Software Internals

| Explorer System Software Design Notes2243208-0001 |

|---------------------------------------------------|

|---------------------------------------------------|

Explorer is a trademark of Texas Instruments Incorporated.

#### **ABOUT THIS MANUAL**

#### **Purpose**

This manual describes the Texas Instruments Explorer processor. The information in this manual serves as a stand-alone descriptive document for the Explorer processor. The manual is written for original equipment manufacturers (OEMs), system designers, field maintenance people, and Texas Instruments customer representatives (CRs).

#### Contents of This Manual

This manual is divided into four sections as follows:

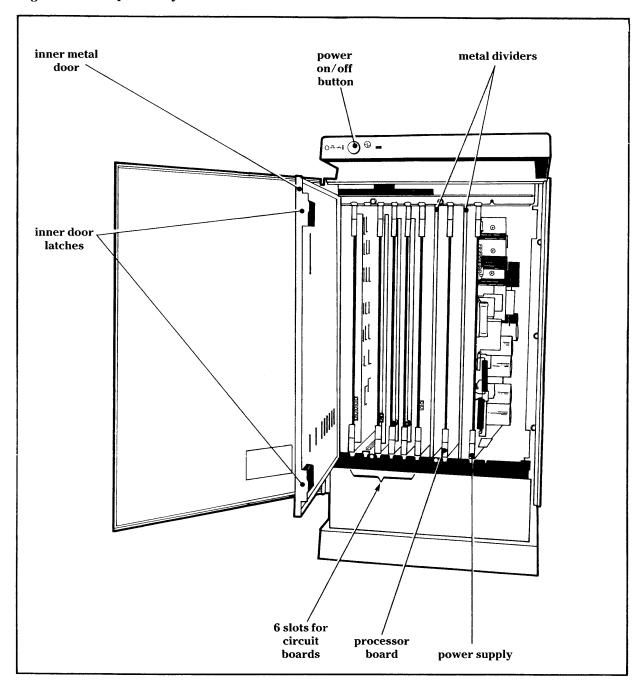

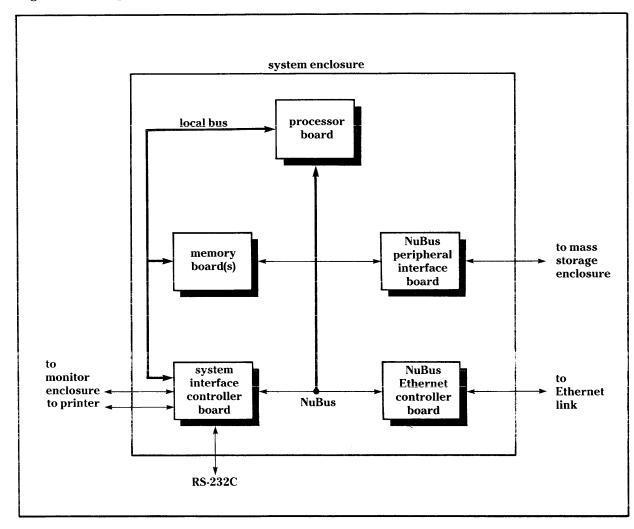

**Section 1:** Introduction — Provides a general description of the Explorer processor, lists its important features, and describes how the processor functions as a part of the Explorer computer system.

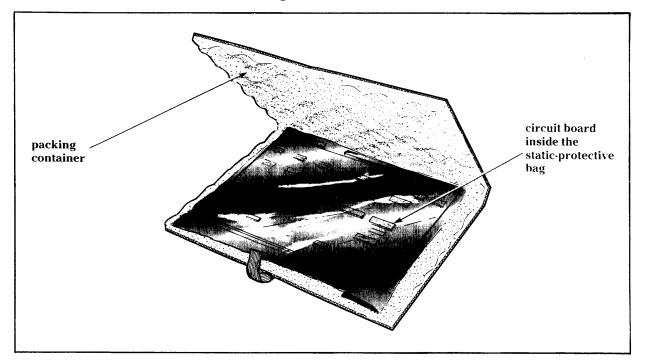

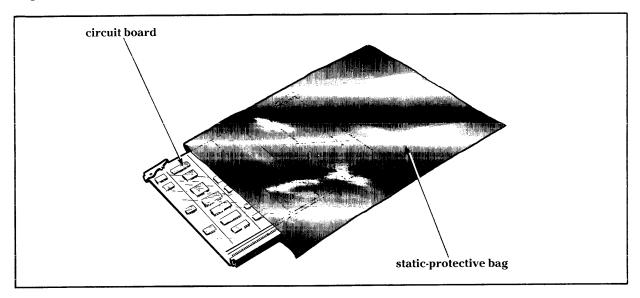

**Section 2:** Installation — Provides unpacking and installation procedures for the Explorer processor.

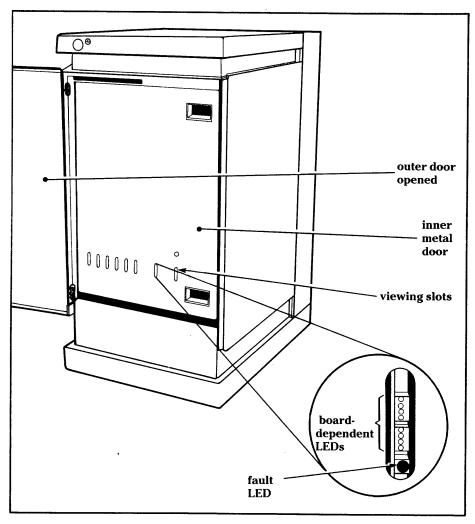

**Section 3:** Operation — Provides operating information that includes how the operator should respond to external and internal resets, and how to interpret fault indicator responses to self-tests.

**Section 4:** System Design and Programming Data — Provides an overall view of the operation of the Explorer processor that is keyed to block diagrams. A basic description of processor data flow, processor control and timing, and macroinstruction and microinstruction formats is also provided.

## **CONTENTS**

| 1         Introduction         1-3         1-3         1-3         1-3         1-3         1-3         1-3         1-3         1-3         1-3         1-2         Explorer Computer System Overview         1-3         1-3         1-2         1-8         1-2         1-8         1-7         1-7         1-2         1-7         1-7         1-7         1-7         1-7         1-7         1-7         1-7         1-7         1-7         1-7         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-8         1-9         1-8         1-9         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10         1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | Paragraph | Title                              | Page                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|------------------------------------|---------------------------|

| 1.1   General   1.3   1.2   Explorer Computer System Overview   1.3   1.2   Explorer Computer System Overview   1.3   1.2   Explorer Computer System Overview   1.4   1.5   1.2   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5   1.5 | 1 |           | Introduction                       |                           |

| 1.2   Explorer Computer System Overview   1.3     1.2.1   Bus Interfaces   1.77     1.2.2   Local Memory   1.8     1.2.3   Board Address Configuration   1.8     1.3   Explorer Processor Features   1.9     1.4   Explorer Processor Specifications   1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ | 1.1       |                                    | 1-3                       |

| 1.2.1   Bus Interfaces   1.7   1.2.2   Local Memory   1.8   1.2.3   Board Address Configuration   1.8   1.3   Explorer Processor Features   1.9   1.4   Explorer Processor Specifications   1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 1.2       | Explorer Computer System Overview  | 1-3                       |

| 1.2.2   Local Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 1.2.1     | Bus Interfaces                     | 1-7                       |

| 1.2.3   Board Address Configuration   1.8     1.3   Explorer Processor Features   1.9     1.4   Explorer Processor Specifications   1.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 1.2.2     | Local Memory                       | 1-8                       |

| 1.4   Explorer Processor Specifications   1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 1.2.3     | Board Address Configuration        | 1-8                       |

| Installation         2.1 Introduction       2-3         2.2 Removal       2-3         2.3 Unpacking Procedure       2-4         2.4 Installation       2-6         3       Operation         3.1 System Start-Up Procedures       3-3         3.2 Processor Board Self-Tests       3-3         4       System Design and Programming Data         4.1 General       4-3         4.2 Processor Operational Overview       4-4         4.3 Processor Functional Description       4-4         4.3.1 Processor Functional Features       4-4         4.3.2 Microinstruction Formats       4-8         4.3.3 Processor Data Paths       4-8         4.3.4 Processor Control Paths       4-11         4.3.5 Processor Timing       4-13         4.3.5.1 Data Pipeline       4-13         4.3.5.2 Control Pipeline       4-14         4.3.6 Memory Map and Memory Interface       4-15         4.3.7 Bus Structure       4-19         4.3.7.1 A Bus       4-19         4.3.7.2 M Bus       4-19         4.3.7.3 R Bus       4-23         4.3.7.6 Local Bus and NuBus       4-23         4.3.7.6 Local Bus and NuBus       4-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 1.3       | Explorer Processor Features        | 1-9                       |

| 2.1       Introduction       2.3         2.2       Removal       2.3         2.3       Unpacking Procedure       2.4         2.4       Installation       2-6         3       Operation       3.1         3.1       System Start-Up Procedures       3-3         3.2       Processor Board Self-Tests       3-3         4       System Design and Programming Data         4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-13         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 1.4       | Explorer Processor Specifications  | 1-10                      |

| 2.1       Introduction       2.3         2.2       Removal       2.3         2.3       Unpacking Procedure       2.4         2.4       Installation       2-6         3       Operation       3.1         3.1       System Start-Up Procedures       3-3         3.2       Processor Board Self-Tests       3-3         4       System Design and Programming Data         4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-13         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9 |           | Inetallation                       |                           |

| 2.2       Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 | 9.1       |                                    | 2-3                       |

| 2.3       Unpacking Procedure       2-4         2.4       Installation       2-6         3       Operation       3.1       System Start-Up Procedures       3-3         3.2       Processor Board Self-Tests       3-3         4       System Design and Programming Data       4-3         4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3.1       Processor Functional Description       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-13         4.3.6       Memory Map and Memory Interface       4-13         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6 <td< td=""><td></td><td></td><td>Removal</td><td>2-3</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |           | Removal                            | 2-3                       |

| 2.4   Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |           |                                    |                           |

| 3.1   System Start-Up Procedures   3-3   3.2   Processor Board Self-Tests   3-3   3-3     4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |           | Installation                       | 2-6                       |

| 3.1   System Start-Up Procedures   3-3   3.2   Processor Board Self-Tests   3-3   3-3     4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9 |           | 0                                  |                           |

| 3.2       Processor Board Self-Tests       3-3         4       System Design and Programming Data       4.1         4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3.1       Processor Functional Description       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       1 Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 | 9.1       | Creation Stout Up Drogodywag       | 2 2                       |

| 4       System Design and Programming Data         4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |           | Processor Poord Solf Tosts         | 3-3<br>2 <sub>-</sub> 2   |

| 4.1       General       4-3         4.2       Processor Operational Overview       4-4         4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 3.2       | Frocessor Doard Sen-Tests          |                           |

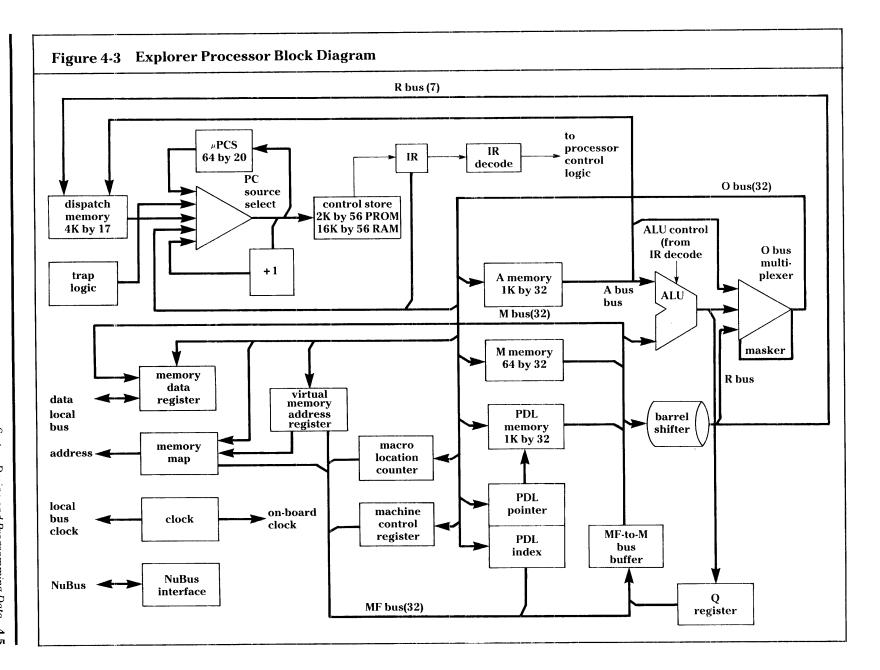

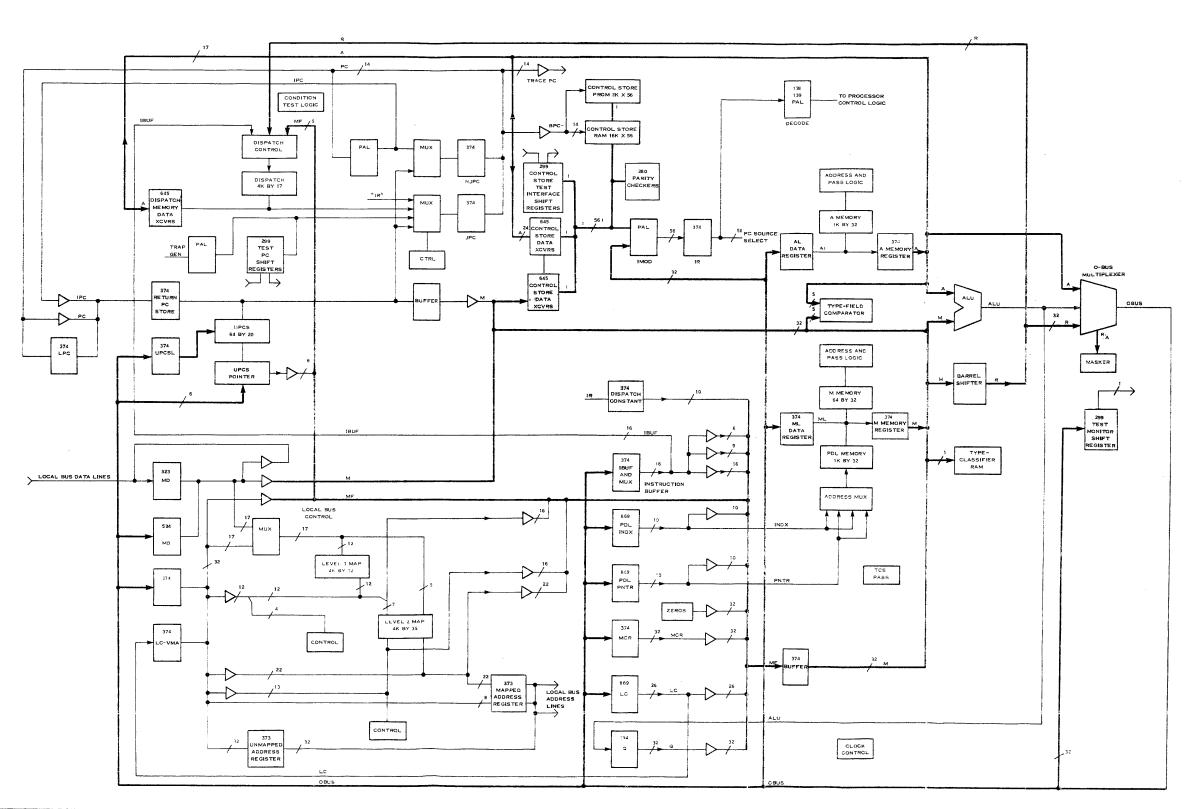

| 4.2       Processor Operational Overview       4-4         4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 |           | System Design and Programming Data | 4.9                       |

| 4.3       Processor Functional Description       4-4         4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |           | General                            | 4-3                       |

| 4.3.1       Processor Functional Features       4-4         4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |           | Processor Operational Overview     | 4-4                       |

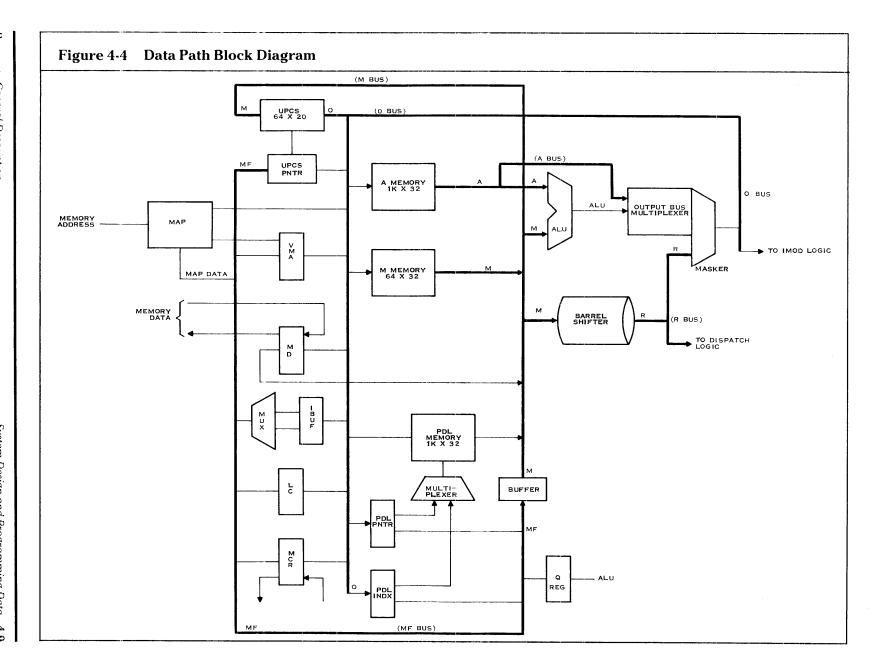

| 4.3.2       Microinstruction Formats       4-8         4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |           | Processor Functional Description   | 4-4                       |

| 4.3.3       Processor Data Paths       4-8         4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-23         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |           |                                    |                           |

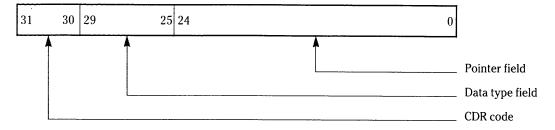

| 4.3.4       Processor Control Paths       4-11         4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |           | Microinstruction Formats           | 4-0                       |

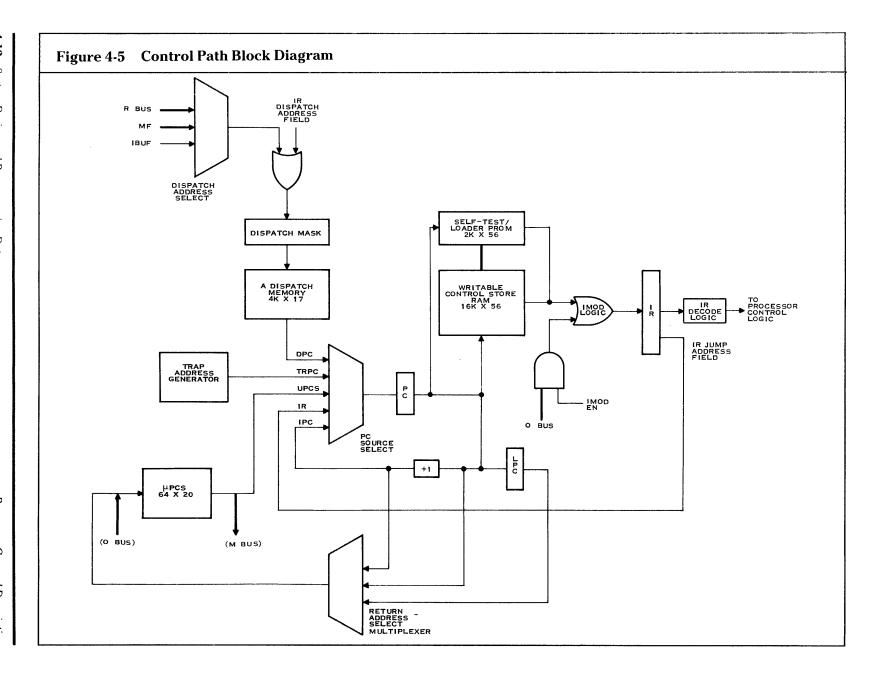

| 4.3.5       Processor Timing       4-13         4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |           |                                    |                           |

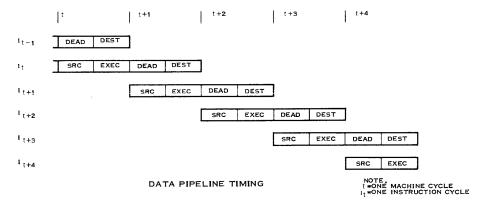

| 4.3.5.1       Data Pipeline       4-13         4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |           |                                    |                           |

| 4.3.5.2       Control Pipeline       4-14         4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |           | Processor Hilling                  | 4-13<br>Δ <sub>-</sub> 13 |

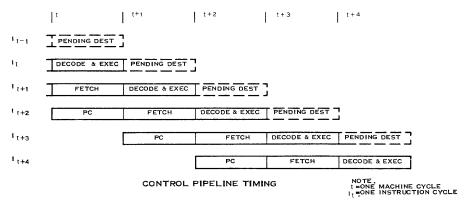

| 4.3.6       Memory Map and Memory Interface       4-15         4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |           | Control Pinolina                   | 4-14                      |

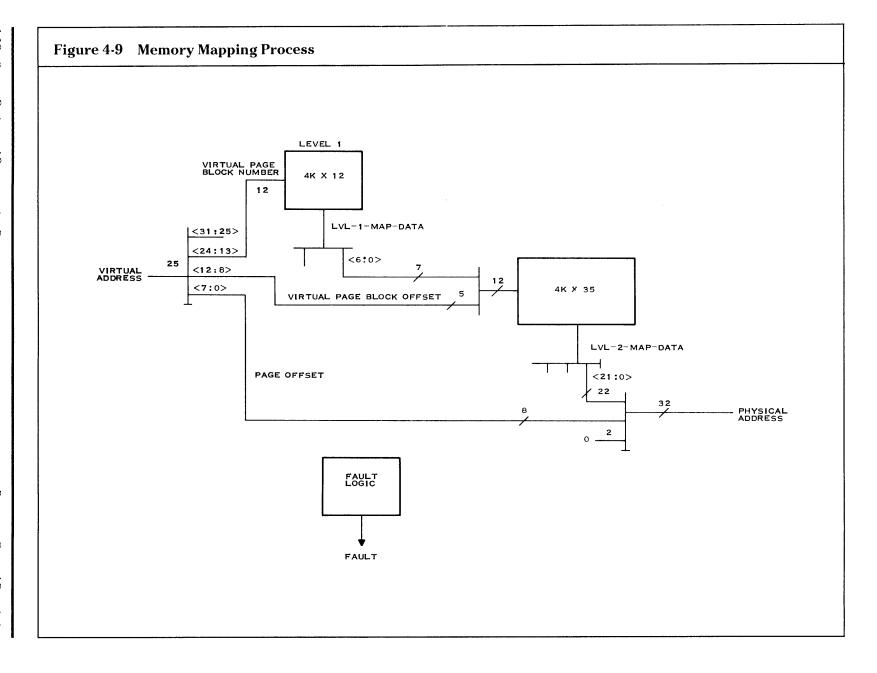

| 4.3.7       Bus Structure       4-19         4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |           | Memory Man and Memory Interface    | 4-15                      |

| 4.3.7.1       A Bus       4-19         4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |           | Rue Structure                      | 4-19                      |

| 4.3.7.2       M Bus       4-19         4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |           | Δ Rue                              | 4-19                      |

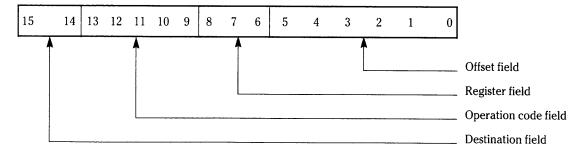

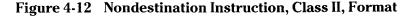

| 4.3.7.3       R Bus       4-23         4.3.7.4       I Bus       4-23         4.3.7.5       O Bus       4-23         4.3.7.6       Local Bus and NuBus       4-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |           | M Rus                              | 4-19                      |