# BCC 500 CPU REFERENCE MANUAL

Chuck Wall

Jack Freeman

THE ALOHA SYSTEM University of Hawaii

Document No. BCC/M-1 December 31, 1973

Contract NAS2-6700

Department of Defense

Advanced Research Projects Agency

ARPA Order No. 1956

#### ABSTRACT

This document provides a complete description of the BCC-500 CPU from a machine language programming point of view. It is expected that most programming will be at a level well above machine language, since the Systems Programming Language (SPL) is completely adequate for most of the systems development. This document represents an updated, edited and revised version of two working documents originally written by Butler Lampson and Charles Simonyi. This manual reflects the changes made to the CPU at the University of Hawaii.

# TABLE OF CONTENTS

|     |                                                                                                                                                                                                                                                                                                              | Page                            |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                 | 3                               |

| 2.  | GENERAL CHARACTERISTICS AND STATE                                                                                                                                                                                                                                                                            | 4                               |

| 3.  | ADDRESS SPACE AND MAP                                                                                                                                                                                                                                                                                        | 7                               |

| 4.  | ADDRESSING FROM INSTRUCTIONS                                                                                                                                                                                                                                                                                 | 16                              |

| 5.  | INDIRECT ADDRESSING                                                                                                                                                                                                                                                                                          | 34                              |

| 6.  | USE OF ADDRESSES BY INSTRUCTIONS                                                                                                                                                                                                                                                                             | 45                              |

| 7.  | FUNCTION CALLS                                                                                                                                                                                                                                                                                               | 47                              |

| 8.  | PROGRAMMED OPERATORS                                                                                                                                                                                                                                                                                         | 62                              |

| 9.  | SYSTEM CALLS                                                                                                                                                                                                                                                                                                 | 63                              |

| 10. | TRAPS                                                                                                                                                                                                                                                                                                        | 64                              |

| 11. | CPU INTERRUPTABILITY                                                                                                                                                                                                                                                                                         | 65                              |

| 12. | ORDINARY INSTRUCTIONS                                                                                                                                                                                                                                                                                        | 70                              |

| 13. | FLOATING POINT                                                                                                                                                                                                                                                                                               | 92                              |

| 14. | APPENDIX CONTENTS                                                                                                                                                                                                                                                                                            | 102                             |

|     | DEFINITION OF INSTRUCTION CODES DEFINITION OF OPR ADDRESSES SUMMARY OF ADDRESSING SUMMARY OF INSTRUCTION ADDRESSING FIXED TRAPS RING-DEPENDENT TRAPS RING-DEPENDENT TRAP IØ: BLLERR SUMMARY OF IMPORTANT CORE ADDRESS SPL PROGRAM TO DEFINE BLL WORD FORMATS SOME FIELDS IN OCTAL FORM CHT HASHING ALGORITHM | 108<br>109<br>110<br>111<br>113 |

## 1. Introduction

This is a reference manual for the BCC 500 central processor unit (CPU). It is intended to be a complete and self-contained description of the characteristics of the processor from the point of view of a machine language programmer (although it is hoped that few programmers will ever have occasion to descend to machine language).

Two considerations have dominated the design of the CPU. They are stated here in the hope that they will make clearer the rationale for some of the machine's characteristics.

- 1) The CPU will be implemented on a somewhat modified version of a BCC microprocessor. This implied that peculiar instruction and addressing sequencing can be used freely.

- 2) The CPU will be programmed almost entirely in SPL or FORTRAN. It is therefore essential that the common constructs of these languages have efficient hardware counterparts. Most notable among them are array referencing, function calls and returns, part word field accessing and string processing.

# 2. General Characteristics and State

The CPU is a 24-bit, word oriented, two's complement machine. It has 64 instructions and a variety of addressing modes. Bits are numbered Ø to 23 with bit Ø on the left (most significant) end of the word. Both single (48-bit) and double (96-bit) precision floating point arithmetic are implemented in hardware.

A process, which may be defined as a program in its execution environment, is called an active process if it is running on the CPU. All the information necessary to define a process is contained in a single page of its virtual memory and is called its context block. When an active process is blocked the following objects must be saved:

- All pages in the process that have been modified;

- The context block;

- The state of the CPU.

The state of the CPU is saved in a fixed location in the context block and consists of 12 registers as illustrated in figure 2.1

| Program Counter               | 23 |

|-------------------------------|----|

| A - register                  | 23 |

| B - register                  | 23 |

| C - register                  | 23 |

| D - register                  | 23 |

| Floating point exponent 11 12 | 23 |

| Index register                | 23 |

| Local environment register    | 23 |

| Global environment register   | 23 |

| Status register (see below)   | 23 |

| Compute Time Clock            | 23 |

| Interval Timer                | 23 |

The status register contains the following fields:

| Ø     | 1 5         | 6 8   | 9 11  | 12 13 | 1.4              | 15    | 16                    |           | 18                                      | 19                    |                  | 21    | 22     | 23                    |  |

|-------|-------------|-------|-------|-------|------------------|-------|-----------------------|-----------|-----------------------------------------|-----------------------|------------------|-------|--------|-----------------------|--|

|       | F<br>D<br>P | TRMOD | PRMOD | CC    | 9<br>4<br>0<br>M | S U F | X<br>U<br>T<br>L<br>T | X M O M T | TDFLAG                                  | P<br>D<br>F<br>L<br>A | C<br>A<br>R<br>R | V O F | 0<br>V | I<br>N<br>S<br>T<br>D |  |

| D. J. |             |       |       |       |                  |       |                       |           | *************************************** | *******               |                  |       |        |                       |  |

| Bit   | Name   | Contents                        |

|-------|--------|---------------------------------|

| 5     | FDP    | Full double precision flag      |

| 6-8   | TRMOD  | Temporary rounding mode         |

| 9-11  | PRMOD  | Permanent rounding mode         |

| 12-13 | CC     | Condition Code                  |

| 14    | 940M   | 940 Mode                        |

| 15    | SUF    | Soft underflow flag             |

| 16    | XUTILT | Utility exit trap flag          |

| 17    | TNOMX  | Monitor exit trap flag          |

| 1.8   | TDFLAG | Temporary double-precision flag |

| 19    | PDFLAG | Permanent double-precision flag |

| 20    | CARRY  | Carry bit                       |

| 21    | TOV    | Temporary overflow bit          |

| 22    | OV     | Overflow bit                    |

| 23    | INSTD  | Instruction terminated bit      |

FIGURE 2.1 CPU STATE

Note that it is convenient in the notation used in the manual to refer to some registers by affixing an "R" to their name. So you will see the following names referring to the same register.

| A | AR | A-register |

|---|----|------------|

| В | BR | B-register |

| C | CR | C-register |

| D | DR | D-register |

| E | ER | E-register |

| X | XR | X-register |

# 3. Address Space and Map

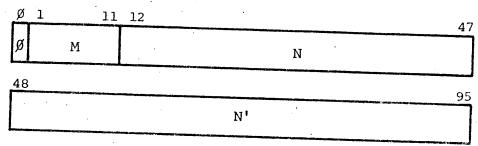

The CPU considers itself at any particular time to be running a process which is defined by its context block. Each process has a 256K address space. The CPU uses 18-bit addresses to specify memory locations. The address space has two significant characteristics:

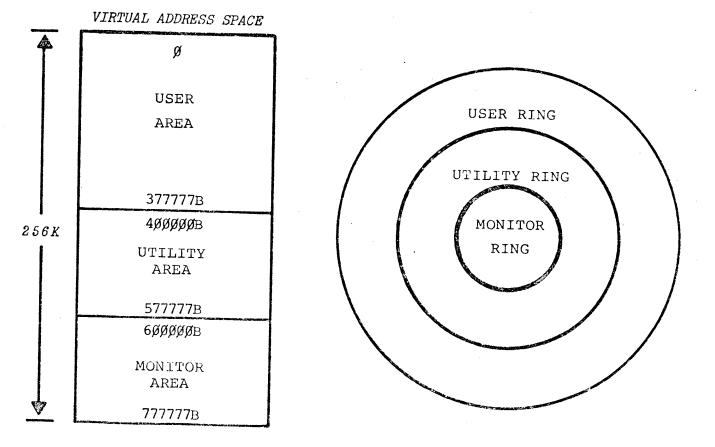

1) it is divided into three rings as follows:

addresses Ø-377777B user ring (lowest)

4ØØØØB-577777B utility ring

6ØØØØB-777777B monitor ring (highest)

The rings are protected from each other according to certain rules. Every memory reference is said to have a <u>source</u>. The source for any references generated by an instruction up to and including a fetch of an indirect word is, for example, the program counter; the source for any reference generated after a fetch of an indirect word up to and including a fetch of the next indirect word is the address of the first indirect word. Every reference also has a <u>target</u>, which is the address being referenced. The following matrix defines those combinations of source and targets which are legal.

|        |         |      | Target  |         |

|--------|---------|------|---------|---------|

|        |         | User | Utility | Monitor |

|        | User    | Yes  | No      | No      |

| Source | Utility | Yes  | Yes     | No      |

|        | Monitor | Yes  | Yes     | Yes     |

#### To summarize:

- a) References from one ring to a higher one are forbidden.

- b) If indirection leads to a lower ring, it is forbidden to return to the same or higher ring during the same instruction. This fact makes it easy, for example, for monitor routines to enforce the user's protection rules when storing into a table provided by the user: they need only do their stores indirect through an address in the user ring, and the ring protection hardware will do the checking automatically.

A forbidden reference causes trap MACC (Memory ACCess error). The target is passed as a parameter to this trap. See figure 3.1 for the two representations of the virtual address space.

FIGURE 3.1 VIRTUAL ADDRESS SPACE AND PROTECTION RINGS

2) The address space is organized into 2048 (2K) word pages, and the precise collection of pages which make up the address space is specified by the map. Pages are named in a manner independent of their location in core, and the mapping hardware uses this location-independent name, together with a table called the core hash table (CHT), to determine the physical core location of a page. The page number (the top 7 bits) of every memory reference thus requires two levels of translation:

from page number to location-independent name from location-independent name to physical page address

The various mechanisms for performing this translation will now be described.

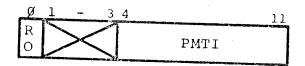

Locations 200B-277B in the context block contain the map of the virtual address space for the process. These 128 half-word entries specify the contents of the corresponding 128 pages of the address space of the process. Each half-word is interpreted as follows:

| Bit  | Name  | Contents                                                                                                       |

|------|-------|----------------------------------------------------------------------------------------------------------------|

| Ø    | MAPRO | Read-only bit. This bit is merged with the RO bit in PMT to make the read-only bit interpreted by the hardware |

| 1-3  | -     | unused                                                                                                         |

| 4-11 | PMTI  | a PMT index                                                                                                    |

FIGURE 3.2 MAP ENTRY

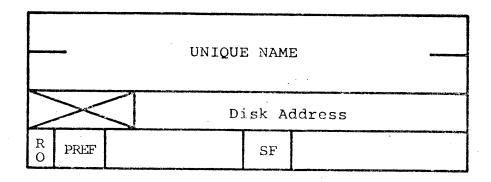

The process memory table (PMT) provides enough information about each page accessible to the process to permit the hardware to access the page. The PMT starts at location 300B in the context block. Each entry is 4 words long; the address in the context block of PMT entry i is therefore 4(i-1) + 300B.

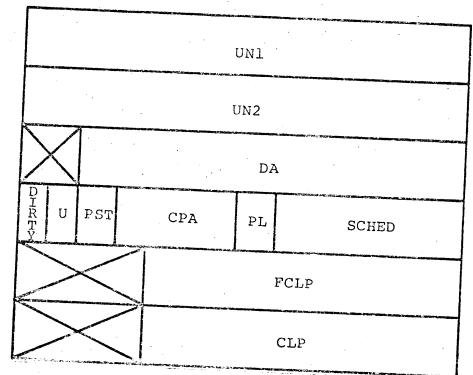

# A PMT entry has the form

| Word | Bits | Name  | Contents                                                                                |

|------|------|-------|-----------------------------------------------------------------------------------------|

| Ğ    | Ø-23 | UNl   | First 24 bits of unique name for the page (Location-independent name)                   |

| 1    | Ø-23 | UN2   | Second 24 bits of unique name for the page                                              |

| 2    | 2-23 | DA    | Disk address of the page                                                                |

| 3    | ø    | PMTRO | Read-only bit                                                                           |

| 3    | 1    | PREF  | Page has been referenced                                                                |

| 3    | 12   | SF    | Page is scheduled for the process (i.e., in core working set and the process is active) |

The other bits are not used by hardware. The unique name is referred to as UN in the text.

FIGURE 3.3 PROCESS MEMORY TABLE ENTRY

Note that there is no provision for execute-only pages, since this device by itself is not sufficient to protect proprietary programs. The sub-process structure of the monitor is supposed to be used for this purpose.

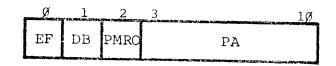

The central processor contains a <u>physical map</u> (PM) which has 128 registers of 11 bits each. One of the registers has the form:

| Bits | Name | Contents                                                                        |

|------|------|---------------------------------------------------------------------------------|

| Ø    | EF   | Empty flag                                                                      |

| 1    | DB   | Dirty bit, set if the page has been stored into since it was read from the drum |

| 2    | PMRO | Read-only bit                                                                   |

| 3-10 | PA   | Physical address of page in a real core of up to 512K.                          |

FIGURE 3.4 PHYSICAL MAP REGISTER

When a new process starts to run on the processor, the empty flag is set in each PM entry. Every address generated by the program must be mapped to convert it from virtual to real so that an access can be made to the real core. This is done by taking the top 7 bits of the 18-bit address and using them to select one of the 128 PM entries. If the empty flag is off, the re-

mainder of the entry is returned. The PA field is prefixed to the last 11 bits of the virtual address to make a read address. If the access is a store and PMRO = 1, the store is aborted and the PRO (Page Read Only) trap is caused. If the access is a store, PMRO =  $\emptyset$  and DB =  $\emptyset$ , the dirty bit in the CHT entry for the page is set and DB is set to 1.

If the empty flag is on, the PM entry must be <u>loaded</u>. Let its index be i. First, entry i of the map (i.e. half-word  $400B \div i$  in the context block) is fetched. If PMTI is  $\emptyset$ , trap PNIM (Page Not In Map) occurs. It it is not  $\emptyset$  MAPRO [i] is saved. Then the PMT entry specified by PMTI [i] is fetched. Call it entry n. If  $SF[n] = \emptyset$ , trap PNIC (Page Not In Core) occurs. PMTRO is saved; if PREF  $[n] = \emptyset$ , it is set to 1; the UN found in PMT [n] is then looked up in the core hash table.

The Core Hash Table contains information about the current contents of core memory. It starts at location 400 in real core and is organized as a chained hash table. The table comes in two parts:

1) The index, called CHTl which is an array of 256 pointers to lists of CHT entries. Each word of CHTl is either END or the address of a CHT2 entry e with the property that HASH (UN(e)) is the address of the CHTl word. If there are several pages in CHT with the same value of HASH (UN), the CHTl word points to one of them, which points to the next using the collision pointer field, and so on until all are chained into the list. The last element has END in its collision pointer. The hashing function HASH is to take the exclusive or of the six 8-bit bytes of the Unique Name (UN) and then the exclusive or of this result with 264B.

2) The body, called CHT2, is an array containing a 6 word entry for each page of real core. Each entry has the form:

|      |       |       | 一个一个一个一个一个一个一个一个一个一个一个一个一个一个一个一个一个一个一个 |

|------|-------|-------|----------------------------------------|

| Word | Bits  | Name  | Contents                               |

| Ø    | Ø-23  | UNl   | First 24 bits of unique name           |

| 1    | Ø-23  | UN2   | Second 24 bits of unique name          |

| 2    | 2-23  | DA    | Disk address of page                   |

| 3    | ø     | DIRTY | Dirty bit                              |

| 3    | 1     | U     | Unavailable bit                        |

| 3    | 2-4   | PST   | Page status                            |

| 3    | 5-12  | CPA   | Core page address                      |

| 3    | 13-15 | PL    | Page lock                              |

| 3    | 16-23 | SCHED | Number of occurrences of page          |

|      |       |       | in loaded working sets                 |

| 4    | 6-23  | FCLP  | Free core list pointer                 |

| 5    | 6-23  | CLP   | Collision PTR                          |

|      |       |       |                                        |

FIGURE 3.5 CORE HASH TABLE ENTRY

If (U OR PST)  $\neq \emptyset$  or the page is not in CHT, trap PNIC occurs. If the page is found, CPA and DIRTY are copied into the PM and PMRO is set to MAPRO OR PMTRO [n].

All the traps (PRO, PNIM, PNIC) which can be generated by the mapping operation are given the virtual address being mapped as a parameter.

To make sure that a particular page is not being used by the CPU, an external processor may request a scan of the physical map. When such a request is received, the PA field of all non-empty registers in the physical map is matched against the contents of cell 2455B + CPU number \*4. If any of them matches, the MAB (Map ABort) trap occurs. The message cell is set to 4B7 upon completion of the scan, regardless of the outcome.

#### 4. Addressing from Instructions

The machine has a rather complex addressing structure. The address calculation is performed in the same way for every instruction, and it may yield either an operand OP or an effective address Q. The format of an instruction and of an indirect address word (IAW) is as follows:

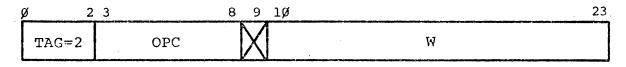

a) Instruction word format

OPC

POP

3-8

9

| 4 | ø 2 | 3    | 8 9         | $1\emptyset$ 2.3 | , |

|---|-----|------|-------------|------------------|---|

|   | TAG | OPC  | P<br>O<br>P | W                |   |

|   | Bit | Name | *****       | Contents         | _ |

|   | Ø-2 | ŢAG  | Ad          | dress TAG field  |   |

Programmed operator bit

Op code

10-23 W Address field

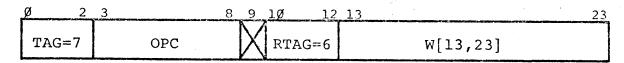

b) Indirect address word format

| Ø 12 |      | 23                                                          |

|------|------|-------------------------------------------------------------|

| IAT  |      | BODY                                                        |

| Bit  | Name | Contents                                                    |

| Ø-1  | TAI  | Tag field which defines the meaning of the rest of the word |

| 2-23 | Body | The meaning depends on IAT                                  |

FIGURE 4.1 INSTRUCTION AND INDIRECT ADDRESS WORD FORMAT

Since the addressing is rather complex, it seems worthwhile to explain in some detail what the various features are for, before describing them precisely. There are a number of points which influenced the design:

- 1) It is necessary to be able to conveniently address a 256K (18-bit) address space, even though an instruction has only a 14-bit address field.

- 2) Programs are normally written in relatively small units, each of which references some private storage of its own and some global storage.

- 3) Array references are very common. Since there is only one index register for holding subscripts, it would be very nice to have a convenient way of using core locations for indexing. Since the languages which are expected to account for a majority of the load on the machine require subscripts to be checked for size before being used, it would be nice to have a cheap and convenient way of doing this. Furthermore, we have to deal with arrays having elements which may occupy 1 (integer), 2 (real), or 4 (double) words. To have to multiply the index by the element size is a great annoyance.

- 4) References to fields which occupy whole words or parts of words relative to a pointer are also common, especially in system code.

- 5) It is essential to have an effective mechanism for handling strings of 8-bit characters. If other byte sizes can also be accommodated, so much the better.

All of these goals are achieved in a fairly economical way by the addressing system. In particular, arrays, strings, and part-word fields are handled by indirect addressing, which allows an absolute 18-bit address to be supplied. The addressing modes available in an instruction allow for immediate operands, addressing relative to the instruction word for referencing the program, and addressing relative to two base registers which are intended to reference the local storage of the subroutine (called the local environment, L) and the global storage of the whole program (called the global environment, G). They also permit indexing to be specified from the X-register or from the first few cells of the local or global environment.

It should be obvious by now that the addressing system is designed to be used by programs which are organized in a very definite way, i.e., into a collection of subroutines or functions (of less than 4K words each), each with local storage (of less than 2K words for scalars), and all with access to a single global storage and communications area (of less than 16K words). The first 128 words of the local and global environments are special; this is because there are 8-bit fields in certain addresses in which the top bit specifies L or G and the remaining 7 bits address one of the first 128 words. The first 32 words are even more special, because there are 6-bit fields in which the top bit specifies L or G and the remaining 5 bits address one of the first 32 words. With this introduction, we proceed

to describe the addressing in detail, together with comments on the intended use of each feature. A reader unfamiliar with this material will find it helpful to read the text following the description of each mode first.

The 3-bit TAG field of an instruction determines one of 8  $\operatorname{ad-dressing}$  modes.

| TAG OPC W                               | 3. |

|-----------------------------------------|----|

|                                         | J  |

| TAG Name Addressing Mode                |    |

| Ø D Direct or G-relative                |    |

| 1 Indirect or G-Indirect                |    |

| 2 , X Indexed                           |    |

| 3 BX Base-Index                         |    |

| 4 PD Pointer-Displacement               |    |

| 5 PDI Pointer-Displacement-Indirect     |    |

| 6 BXD Base-Index-Displacement           |    |

| 7 REL Relative. This one has 6 sub-case | s. |

FIGURE 4.2 ADDRESSING MODES SPECIFIED

BY TAG FIELD

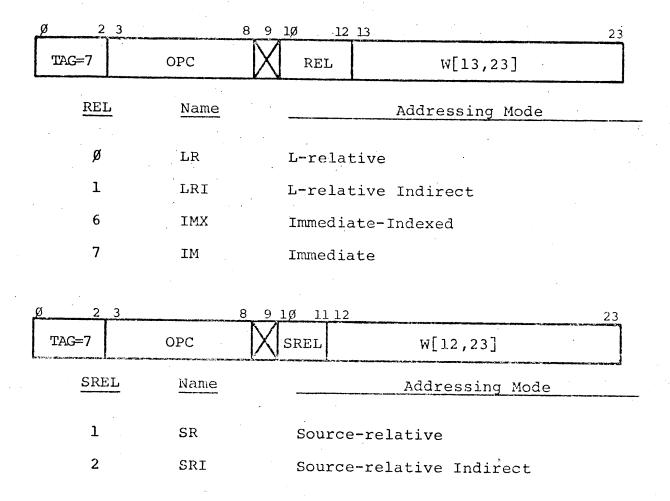

The relative mode has 6 sub-cases, L-relative, source-relative, immediate, indirect L-relative, indirect source-relative and immediate indexed.

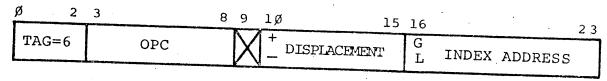

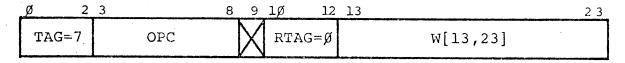

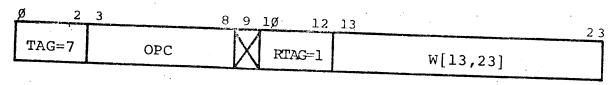

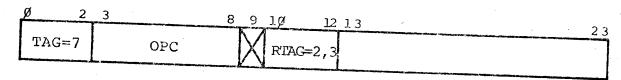

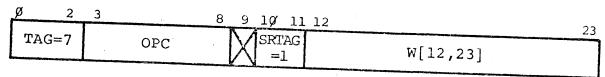

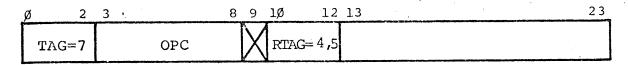

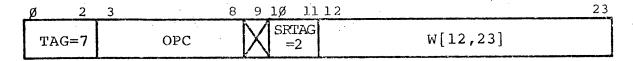

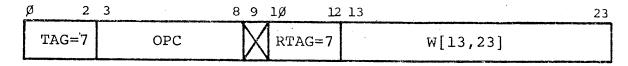

The relative words are formatted as follows:

FIGURE 4.3 RELATIVE ADDRESSING MODES SPECIFIED

BY REL AND SREL

Notice that we have represented the 6 sub-cases of the relative mode by introducing two fields called REL and SREL. This is because in the source relative modes of addressing bit 12 is used as part of the address field. Also we have introduced some new notation. The W[13,23] indicates that we are referring to bits 13 through 23 of the instruction word and that those bits are contained within the address field W of the instruction.

Most of the modes depend on the existence of an <u>indexing register</u> IR, and a <u>source register</u> R. The IR register is not to be confused with the index register X. In fact, it is not part of the state at all; i.e. its value does not have to be preserved from one instruction to the next. The IR is used to hold the 18-bit value which will be used when an indexing operation is called for by the addressing system. It is initialized from X at the beginning of each instruction. Thereafter, it may be loaded from a word specified by a BX or BXD mode or an array indirect word (see below). The source register is initialized to the address of the word from which the instruction has been fetched (normally P).

Some addressing modes compute Q directly from the information in the central registers, the instruction and possibly one memory word used for indexing. Others (the indirect modes) compute directly the location of an <u>indirect address word</u>, and the contents of this word then determines how the addressing computation is to proceed. If indirect addressing is specified, only the values of the IAW address and IR affect the subsequent address computation. We will therefore confine ourselves to specifying those values which describe instruction addressing, and leave the details of indirect addressing for later treatment.

Before we describe the various addressing modes in detail, we define some notation that will be used in defining the various modes.

CONTENTS (N)

will be used to denote the contents of the memory location with address N. Ring checking is performed with R as source and N as target.

IA(N)

implies that the indirect addressing sequence is initiated by:

FUNCTION IA(N);

IAW + CONTENTS(N);

R + N;

\*PROCEED TO PROCESS IAW

By the time it is finished, the IA function will set the value of Q or OP.

Note that special cases of the IA(N) function may be specified for each of the 4 indirect addressing modes where we may want to indicate a particular mode. We may have any one of the following:

NORMAL'IA(N); FIELD'IA(N); STRING'IA(N); ARRAY'IA(N);

W[i,j]

means bits i to j of W (the address field of the instruction) considered as a 24-bit number. W[i,i] is represented by W[i].

SIGNED(W[i,j])

means W[i,j] interpreted as a two's complement number of (j - i + 1) bits.

All instructions start with IR  $\leftarrow$  XR & R  $\leftarrow$  P; in the notation used, the "\$" indicates indirection and "'" (e.g. G'[w]) is used ... the sense of a delimiter between symbols. We now define in detail all the addressing modes with indirect addressing discussed in a separate section which follows.

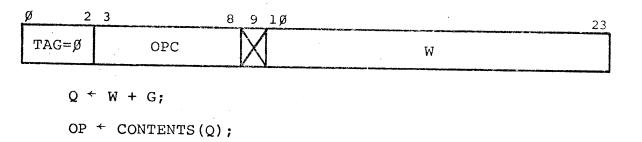

Direct (D) or G-relative:

In the direct or G-relative mode, the effective address is given by the 14-bit address field relative to G. This permits direct addressing of the first 16K of the global environment. The notation in SPL is

OPC G'[W];

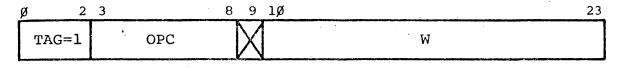

Indirect (I) or G-relative Indirect:

$$IA(W + G);$$

In the indirect mode, any of the first 16K words of the global environment can be used as an IAW (indirect address word) that may point anywhere in the virtual address space.

The notation is

OPC \$G'[W];

Indexed (X):

Q + W + IR;

OP ← CONTENTS(Q);

Since IR is initialized by XR, the effective address is the (18-bit) sum of the indexing register and the address field. The notation is

OPC X'[W];

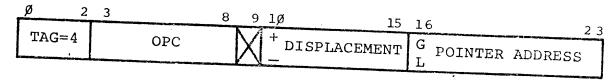

Pointer-Displacement (PD):

Where the pointer field is one of the following:

and the address calculation is:

PTR + IR IF W[16,23] = Ø ELSE

PTR - CONTENTS(G + W[17,23]) IF W[16] = Ø ELSE

PTR - CONTENTS(L + W[17,23]);

DISP - SIGNED(W[1Ø,15]);

Q - PTR + DISP;

OP - CONTENTS(O):

In this mode the address field is divided into an 8-bit pointer address field and a 6-bit signed displacement field. Similar arrangements are used in several other modes; they will be explained here in detail. The top bit of the 8-bit pointer address specifies the environment (1=local,  $\beta$ =global) and the remaining 7 bits address one of the first 128 words in the local or global environments. If pointer address is  $\beta$ , the contents of IR, rather than of word  $\beta$  in G, is specified. The calculation of DISP specified the conversion of a 6-bit number which is to be interpreted as two's complement into a 24-bit two's complement number.

Finally, the effective address is the sum of the pointer (PTR) specified by pointer address and the displacement (DISP). The typical use of this mode is in addressing the nth word of a table entry given a pointer to the start of the entry. If the pointer P is in the first 128 words of either environment, then the word is loaded into A, say by

## LDA P[D]

which is the notation for PD addressing with pointer address P and displacement D.

The notation is

OPC P[D];

where P may be one of the following:

$\emptyset$  or  $G'[\emptyset]$  for PTR  $\leftarrow$  IR;

G'[N] where  $\emptyset \le N \le 127$  for PTR + CONTENTS(G + N);

L'[N] where  $\emptyset \leq N \leq 127$  for PTR + CONTENTS(L + N); and -32 < D < 31

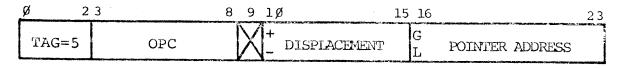

Pointer-Displacement-Indirect (PDI):

Q + PTR + DISP as for PD mode; IA(Q);

This is just indirect addressing in PD mode.

The notation is

OPC \$P[D];

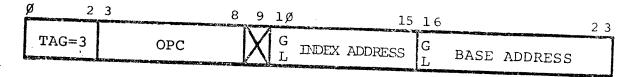

Base-Index:

Where the index address field is one of the following:

INDEX + IR;

1Ø 15

INDEX <- CONTENTS(G + W[11,15]);</pre>

W[11,15]

INDEX \* CONTENTS(L + W[11,15]);

W[11,15]

and the base address field is one of the following:

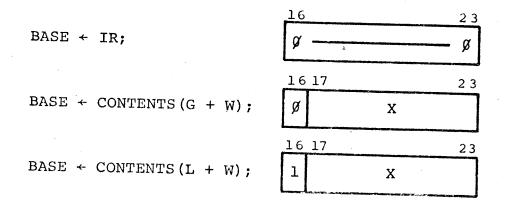

BASE + IR;

16 Ø

BASE  $\leftarrow$  CONTENTS (G + W[17,23]);

1617 W[17,23]

BASE  $\leftarrow$  CONTENTS(L + W[17,23]);

1617 23 1 W[17,23]

and the address calculation is:

BASE  $\leftarrow$  IR IF W[16,23] =  $\emptyset$  ELSE

BASE  $\leftarrow$  G + W[17,23] IF W[16] = Ø ELSE

BASE + L + W[17,23];

IR + IR IF  $W[10,15] = \emptyset$  ELSE

IR + CONTENTS (G + W[11,15]) IF W[1 $\beta$ ] =  $\beta$  ELSE

IR + CONTENTS(L + W[11,15]);

IA (BASE);

This is the array and part-word field mode and is written OPC B[I]

where B is the base and I the index. The 8-bit and 6-bit index are both treated as local or global environment addresses, exactly like the pointer address in PD mode. The index is put into IR and the base specifies an indirect word. If an array is being accessed, B will address an IAW which has the 18-bit base address of the array and specifies indexing. The contents of IR, which was loaded from I, will thus be added to the base address of the array to determine the final 18-bit address, which is just what we require for array referencing. This is not, however, the whole story; the rest will be told when we come to consider the indirect addressing type used for arrays.

Base-Index-Displacement (BXD):

Where the index address field is one of the following:

INDEX  $\leftarrow \emptyset$ ;

23 Ø

INDEX  $\leftarrow$  CONTENTS(G + W[17,23]);

16 17 23 Ø W[17,23]

INDEX  $\leftarrow$  CONTENTS(L + W[17,23]);

16 17 23 1 W[17,23]

and the base address is in the indexing register.

The address calculation is:

BASE + IR;

INDEX  $\leftarrow \emptyset$  IF W[16,23] =  $\emptyset$  ELSE

INDEX  $\leftarrow$  CONTENTS(G + W[17,23]) IF W[16] = Ø ELSE

INDEX  $\leftarrow$  CONTENTS(L + W[17,23]);

DISP  $\leftarrow$  SIGNED(W[1 $\emptyset$ ,15]);

IR + INDEX + DISP;

IA (BASE);

This mode is similar to BX. It assumes that the base address is in the IR. The field thus freed is used to provide a displacement (anything from -32 to +32) of the index. Thus to load B[I + 5] we would write

EAX

LDA (\$X')[I + 5];

where I is the index address, 5 the displacement. See the discussion of arrays in section (5) for more details on the BX and BXD addressing modes.

The notation is

OPC

$$($X')[I + D];$$

where X' is X-register and I the index.

#### Relative (REL):

There are 6 sub-cases, depending on the first three bits of W. We describe each relative mode separately

L-relative (LR):

DISP

$$\leftarrow$$

W[13,23];

$$Q \leftarrow L + DISP;$$

OP + CONTENTS(Q);

The L-relative mode simply addresses a location in the 2K local environment.

The notation is

OPC L'[D];

L-relative indirect (LRI):

DISP  $\leftarrow$  W[13,23];

Q + L + DISP;

IA(Q);

This is simply the indirect counterpart for the L-relative mode. The notation is

OPC \$L'[D];

Source-relative (SR):

causes the instruction to be interpreted as

DISP + SIGNED(W[12,23]);

Q + R + DISP;

OP + CONTENTS (Q);

This mode allows location up to 4000B on either side of the instruction to be addressed. Remember R is initialized to the program counter at the start of the address calculation.

Source-relative-indirect (SRI):

causes the instruction to be interpreted as

DISP  $\leftarrow$  SIGNED(W[12,23]);

Q + R + DISP;

IA(Q);

This is just the indirect counterpart for source relative.

The notation is

OPC \$R'[D];

All the relative modes allow routines to be placed anywhere in memory without modification and to address themselves without difficulty, as long as they are not more than  $2\emptyset48$  words long.

Immediate (IM):

$$OP \leftarrow SIGNED(W[13,23]);$$

The immediate mode permits signed constants in the range -2000B to 1777B to be provided as operands without an additional memory reference. Stores are not allowed and the operand must not be larger than 11-bits.

The notation is

OPC I;

Immediate-indexed (IMX):

$$OP \leftarrow IR + SIGNED(W[13,23]);$$

This adds the contents of IR to the immediate operand.

The notation is

OPC

$$X' + I$$

;

# 5. <u>Indirect Addressing</u>

To prevent infinite loops of the indirect mechanism, a trap, ILIM (Indirect LIMit exceeded), will occur if indirection through more than 16 levels is attempted.

There are four <u>types</u> of indirect addressing: normal, field, string, and array. The type is selected by the first two bits of the word. The intended use of each type is suggested by its name and will now be explained in detail.

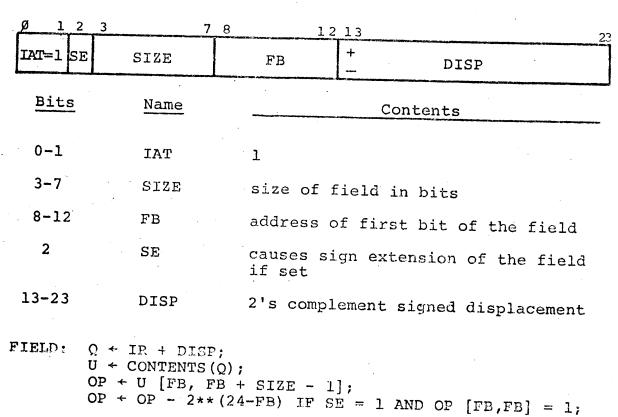

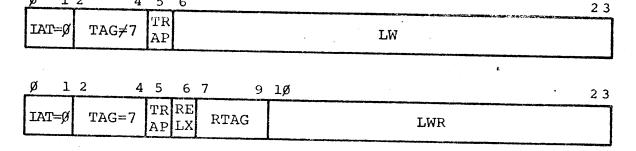

Normal: the IAW has the form

| Ø 1 2   | 4    | 5        | 6 |    |                                                          | 23 |

|---------|------|----------|---|----|----------------------------------------------------------|----|

| IAT=Ø T | AG≠7 | TR<br>AP |   | LW | ASSET TO STANDARD AND AND AND AND AND AND AND AND AND AN |    |

or

| Ø 1   | 2  | 4    | 5        | 6 | 7 | 9    | 1ø | 23    |

|-------|----|------|----------|---|---|------|----|-------|

| IAT=Ø | T. | AG=7 | TR<br>AP |   |   | RTAG |    | LWR . |

| Bits  | Name | Contents                                    |

|-------|------|---------------------------------------------|

| 0-1   | IAT  | Indirect Address Type zero                  |

| 2-4   | TAG  | interpreted exactly like an instruction TAG |

| 5     | TRAP | causes trap IATRP if set                    |

| 6     | RELX | causes indexing for relative modes          |

| 10-23 | LWR  | long address for the relative modes         |

| 6-23  | LW   | long word address                           |

If TRAP is set, the IATRP trap is caused, and R is passed as its argument. Otherwise, TAG and W are interpreted as in an instruction word, with three exceptions:

- 1) if TAG = D, I, or X, LW is used in place of W, and G is not added. In other words, an 18-bit absolute address is supplied.

- 2) if TAG = REL, IR is added to the addresses computed by L and R-relative modes if RELX is set. I.e., indexing is possible with these modes. Also, the 3-bit subtag is found in bits 7-9, thus allowing the LR, LRI, SR, and SRI offsets to be 3 bits longer.

- 3) if TAG = PD or PDI, the mode is <u>read-only direct</u> (ROD) or read-only X-relative (ROX) respectively. These behave exactly like D and X modes except that an attempt to store will cause the ROIA trap with R as parameter.

Normal type permits any word in the address space to be addressed directly. It is generally used for pointers and for the addresses of arrays. Note that although the capabilities are almost identical to those provided by an instruction address, the format is quite different. It is not possible to use an instruction as an indirect word. It also permits indexing of a L-relative or source-relative address, so that arrays in the program of the local environment can be addressed conveniently.

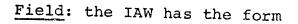

The field which is SIZE bits in length and which starts at bit FB in word DISP + IR is referenced. Both FB and FB + SIZE - 1 must be  $\leq 23$ . If they are not a TI trap will occur. If SE is set, the leftmost bit of the field (bit FB at DISP + IR) will be extended into bits  $\emptyset$  through 23-SIZE of the resulting operand. DISP is taken as a 2's complement number, in the range -1024 to 1023.

The idea here is that IR contains a pointer to a table entry, and that the field descriptor (the IAW) specifies a group of bits at some definite location in the entry. Typically, the pointer might be in PTR within 32 words of L and the field descriptor in F within 128 words of G. Suppose the contents of F is

or in octal DATA 21640003B then we might write

LDA F [PTR]

using base-index addressing. Since PTR appears in the index field, its contents is put into IR. Then F is taken as an IAW. Since it is of type field, it accesses the word at IR + 3, which is CONTENTS (PTR+3); i.e., the fourth word of the object pointed to by PTR. Bits 6 - 12 of this object will be loaded into A. If the word addressed was 01234567B, then A will contain 47B. The field can be used as an operand in any instruction which accesses a single-word operand, this includes both load and store types. Note that fields cannot cross word boundaries.

String: the IAW has the form

| Ø 12      | 34 56   | 23                                                                  |

|-----------|---------|---------------------------------------------------------------------|

| IAT=2 CSI | ZE CPOS | WA                                                                  |

| Bits      | Name    | Contents                                                            |

| Ø-1       | IAT     | 2                                                                   |

| 2-3       | CSIZE   | character size: $\emptyset = 6$ bits, $1 = 8$ , $2 = 12$ , $3 = 24$ |

| 4-5       | CPOS    | character position in word                                          |

| 6-23      | WA      | word address                                                        |

The character at the indicated position in the word addressed by WA is referenced. The following table defines what bits are referenced by the 16 possible combinations of CSIZE and CPOS.

| CSIZE/CPOS | Ø           | 1     | 2     | 3     |

|------------|-------------|-------|-------|-------|

| ø          | <b>Ø-</b> 5 | 6-11  | 12-17 | 18-23 |

| 1          | Ø-7         | 8-15  | 16-23 | X     |

| 2          | Ø-11        | 12-23 | X     | . X   |

| 3          | Ø-23        | X     | X     | X     |

Combinations marked X in the table will cause a TI trap.

The bits referenced are treated exactly like the bits selected by a field IAW.

This type of indirection allows one byte in a string to be referenced. The instruction ISD increments the descriptor to point to the next byte, which may then be referenced. It has the

additional feature of setting the condition code depending on whether the descriptor is equal to the next word or not. The string type and this instruction are intended to be used with four-word string descriptors. The first word points just before the first byte allocated for the string. The second word (read pointer, RP) points to the first character of the string, the third word (write pointer, WP) to the last character. The fourth word points to the last byte allocated for the string. To read the first character, increment RP with ISD, then indirect through it. The case of no characters left can be detected by the abnormal CC setting. To write a character, increment WP with ISD and then store indirect through it. Overflow of available storage can be detected by the CC setting.

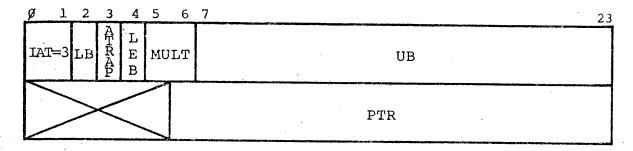

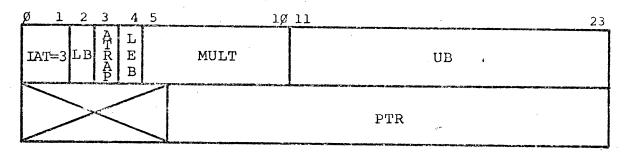

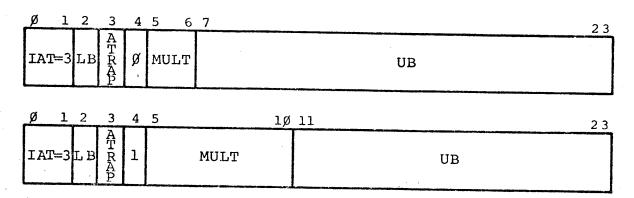

Array: an array descriptor is two words long. Its form is:

$LEB = \emptyset$

or

LEB = 1

| Word:Bit | Name               | Contents                    |

|----------|--------------------|-----------------------------|

| Ø:Ø-1    | IAT                | 3                           |

| Ø:2      | LB                 | lower bound for IR (Ø or 1) |

| Ø:3      | ATRAP              | array trap bit              |

| Ø:4      | LEB                | large element bit           |

| Ø:5-6    | MULT IF<br>LEB = Ø | multiplier for IR           |

| Ø:5-10   | MULT IF<br>LEB = 1 |                             |

| Ø:7-23   | UB IF<br>LEB = Ø   | upper bound for IR          |

| Ø:11-23  | UB IF<br>LEB = 1   |                             |

| 1:6-23   | PTR P              | pointer to array            |

A multiplier of one is coded in the descriptor as zero, two as one, etc. If IR<LB or IR>UB, trap ABE occurs, with R as parameter. If ATRAP = 1 in IAW and the instruction is not LAX, or ATRAP =  $\emptyset$  and the instruction is LAX, trap IATRP occurs with R as parameter.

otherwise, IR  $\leftarrow$  (IR - LB) \* (MULT + 1); T  $\leftarrow$  R + 1; NORMAL'IA(T);

Where NORMAL'IA indicates IA(T) of type normal. This is the most complicated of the IAW types. It is intended to accomplish the following functions connected with array accessing:

- 1) Allow  $\emptyset$  or 1 as lower bound

- 2) Perform a bounds check on the subscript

- 3) Multiply the subscript by the size of the array element, allowing for sizes up to 64

- 4) Check that the number of subscripts supplied is the number expected (see below)

- 5) Provide an 18-bit absolute base address for the array.

Arrays are intended to be stored with marginal indexing. Thus the 2  $\times$  3 one-origined integer array A would appear as follows:

A =

(The three 2-word descriptors are array indirect words.)

The LAX instruction works just like EAX, except that it merges an X tag in XR[2,4] (leaving a normal IAW which specifies indirection) and treats the TRAP bit in an array descriptor as though it were complemented.

Then to do B  $\leftarrow$  A[K,L] we would write

LAX A[K] (BX addressing)

which leaves the address of the descriptor for the Kth row in X followed by

LDA (\$X')[L] (BXD addressing)

STA B

The second subscript can have a constant displacement without complicating things:

$$B \leftarrow A[K,L-4]$$

becomes

rax v[k]

LDA (\$X')[L-4]

STA E

If the first subscript has a displacement, there is a complication, since there is not enough room for three operands in one instruction.

$B \leftarrow A[K+1,L]$  becomes

EAX A

LAX (\$X')[K+1]

LDA (\$X')[L]

STA B

A single subscripted array can be accessed without any extra instructions at all provided the subscript is a variable which can be accessed with an index field of the BX mode. If M is a 10-element integer array, it is allocated thus:

M =

| MULT=Ø, UB=1Ø | M (1)  |

|---------------|--------|

|               | M (2)  |

|               | M (3)  |

|               | M (4)  |

|               | M (5)  |

|               | M (6)  |

|               | M (7)  |

|               | M (8)  |

|               | M (9)  |

|               | M (10) |

and N + M[J] becomes

LDA M[J]

STA N

If the array is integer (1 word items) and bounds checking is not required, the descriptors can be changed to normal indirect words which specify indexing, and no change is required in the instructions of the program.

The purpose of the peculiar behavior of LAX in the case of traps is to check that the proper number of subscripts is provided to an array. The trap bit should be set in the array descriptors except at the last level (the descriptors which point directly to the data) and clear there.

#### 6. Use of Addresses by Instructions

All the instructions compute an effective address Q and/or an operand OP as described above. The use of these quantities once they have been computed, and in particular the error conditions which may arise, depend on the address type of the instruction. There are four address types:

#### 1) Fetch type (F)

These instructions will accept any kind of address. They make use of the 24-bit OP value and possibly Q.

#### 2) Effective-address type (E)

These instructions make use only of the effective address Q, ignoring OP. Immediate addressing causes a TI trap if used with these instructions. Q is ring-checked with R as a source before use; if the check fails a trap MACC will occur.

#### 3) Store type (S)

These instructions make use of the effective address Q and the operand OP. If the address calculation terminated with indirection through a field or string descriptor, the FB and SIZE (for a field) or CPOS and CSIZE (for a string) define a group of bits, say bits i to j. An S type instruction puts bits 23-j+i to 23 of the word to be stored into bits i to j of the word addressed by Q, leaving the rest of this word untouched. Immediate addressing causes a TI trap and indirection through a read-only direct or read-only indexed word causes a RO trap.

#### 4) Double-store type (D)

These instructions make use only of the effective address Q. They trap under the same conditions as S-type instructions.

Note that they are not affected by field or string indirection.

Legal combinations of instructions and addresses are sumarized in the following table:

|                                | F  | E  | S  | D  |

|--------------------------------|----|----|----|----|

| Immediate                      | ok | TI | TI | TI |

| Indirection through ROD or ROX | ok | ok | RO | RO |

| Anything else                  | ok | ok | ok | ok |

Instructions of types S or D will give a PRO trap if Q (or Q+i for instructions which reference double (i=1) or quadruple (i=1,2,3) words) addresses a read-only page.

#### 7. Function Calls

A rather elaborate mechanism for calling functions and returning from them is provided in the hardware of the machine. The purpose is to include all the capabilities required by the FORTRAN and SPL languages directly in the hardware, so as to make software interpretation unnecessary. This is considered extremely important, since programs are expected to be written in small modules, and function calls and returns are consequently expected to be very frequent.

The basic features of the call instruction, BLL, are as follows:

- 1) The old P-counter and local environment are saved and new ones are picked up.

- 2) The new local environment may occupy a fixed area, or it may be allocated space at the end of a stack defined by two locations in the global environemnt. There is a check for stack overflow.

- 3) The caller provides a list of parameter addresses. The called function specifies for each parameter whether it wants the address or the value copied into its local environment. If he requests copying the value, he specifies whether it is 1, 2, or 4 words.

- 4) He also specifies whether or not a parameter is an array. The calling program tells whether it is passing a scalar variable, a scalar value (stores are not legal), an array or an array element (subscripted array). These distinctions permit all the checking for proper matches of arrays with scalars re-

quired by FORTRAN to be done automatically. The case of an actual parameter which is an array element corresponding to a formal parameter which is an array requires software handling and is trapped so that this may be accomplished.

5) Provision is made for an argument to be passed in the central registers.

A number of these points are somewhat subtle and cannot be properly understood unless explained in complete detail, which we now proceed to do.

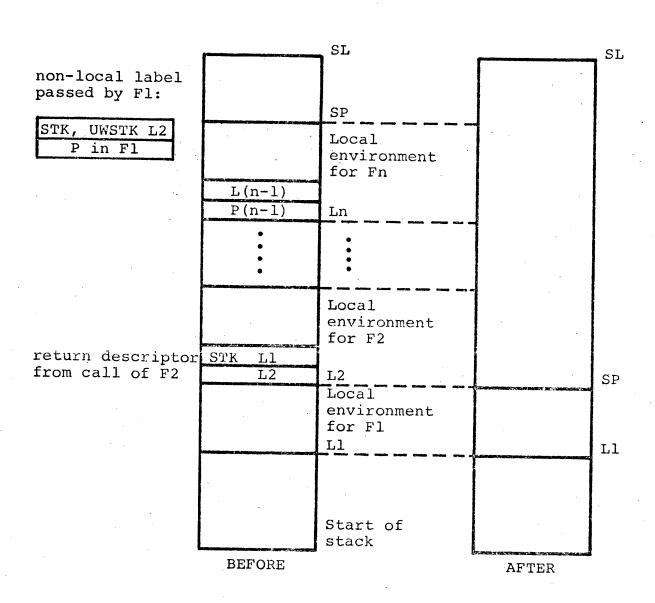

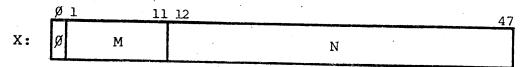

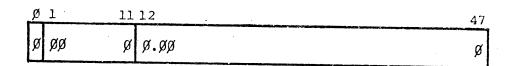

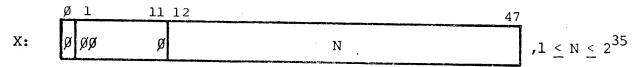

The BLL instruction addresses a branch descriptor, which is a two-word object with the following form:

| Word       | Bit  | Name                | Meaning                                                                            |  |

|------------|------|---------------------|------------------------------------------------------------------------------------|--|

| ø          | Ø-23 | NEWPW               | This word looks like an IAW.<br>Its effective address is computed.                 |  |

| ø          | 4    | SREL                | c.f. REL + SR in Normal IAW                                                        |  |

| Ø          | 5    | TRAP                | Causes IATRP if set                                                                |  |

| Ø          | 9-23 | SRW                 | Signed displacement if SREL is set                                                 |  |

| Ø          | 6-23 | LW                  | Long word addresses                                                                |  |

| , <b>1</b> | Ø    | CLL                 | Call bit. The old P and L are saved if the bit is set.                             |  |

| 1          | 1    | STK                 | The local environment is allocated from the stack if this bit is set.              |  |

| 1          | 2    | CPA                 | Arguments are copied if this bit is set                                            |  |

| 1          | 3    | CPR IF<br>CLL = 1   | The CPA bit in the return descriptor is turned on if this bit is set.              |  |

| 1 .        | 3    | UWSTK IF<br>CLL = Ø | Unwind stack on return.                                                            |  |

| 1          | 4    | REL                 | Source relative label is supplied                                                  |  |

| 1          | 5    | FTN                 | 1 FORTRAN type function                                                            |  |

| 1          | 6-23 | E                   | This number determines the new L; precisely how it does so depends on STK and REL. |  |

When BLL is executed, the first step is to compute the effective address of NEWPW (which is LW if SREL is  $\emptyset$ , otherwise the sign-extended SRW + the address of the NEWPW). This 18-bit number is saved in a temporary register called NEWP; after undergoing further processing it will become the new P-counter. The following steps remain to be performed:

- 1) Obtain new local environment.

- 2) Copy arguments.

- 3) Compute return descriptor (for CALL) and save it in first two words of new local environment.

- 4) Transfer control.

We treat them in the order written, which is also the order in which they are performed. In describing what happens, we shall make use of a number of temporary registers or variables (such as NEWP, which was introduced above).

1) If STK=\$\beta\$, the E field of the descriptor is taken as the new value of L, which we call NEWL. In this case, the function being called is said to have a fixed local environment. Such a function cannot be recursive, and space must be allocated for its local environment at all times. On the other hand, the contents of such a fixed environment is normally preserved between function calls. A FORTRAN function has a fixed environment, for example. Since a call (CLL=1) saves the current L in the E field of the return descriptor, the return (CLL=\$\beta\$) handles E exactly as the call of a fixed function does.

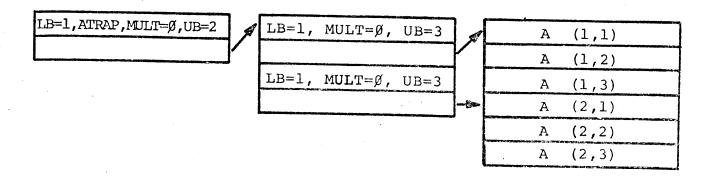

If STK=1, space for the environment is allocated on a stack.

Two words are required to describe the stack, which grows toward increasing memory addresses:

SP, the address of the first unused word, kept in G'[2], the third word of the global environment

SL, the address of the last word allocated for the stack, kept in G'[3].

If the environment is stacked, different actions are required for calls and returns.

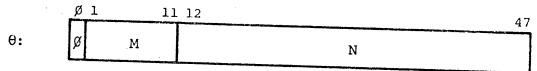

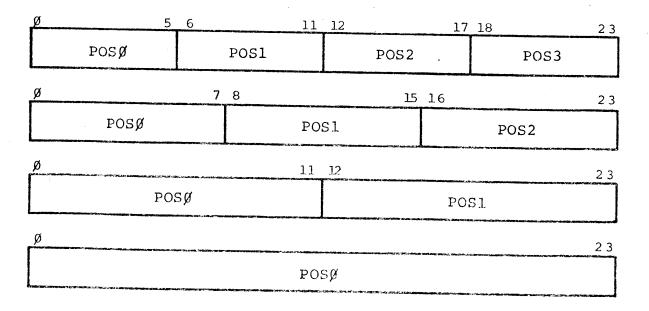

On a call (CLL=1); we compute SP+E. If it is  $\geq$  SL, the STKOV trap occurs. Otherwise, NEWL+SP and SP+SP+E. In other words, E locations are taken from the top of the stack. The situation before and after is shown in figure 1.

On a return (CLL=Ø) what ordinarily happens if STK is set is SP+L; NEWL+E;

in other words, the old L at the time of the call (which was saved in the E field of the return descriptor, as we will see) becomes the new L, and SP is reset to the value it had before the call, which is the current L. The before and after pictures of figure 1, looked at in the opposite order, should help to clarify this. With these rules, calls can be made freely from fixed environment functions to stacked environment ones and visa-versa. The industrious reader may check the four cases.

BEFORE

$\mathtt{SL}$

unused stack

start of stack

FIGURE 7.2 RETURN TO NON-LOCAL LABEL IN F1

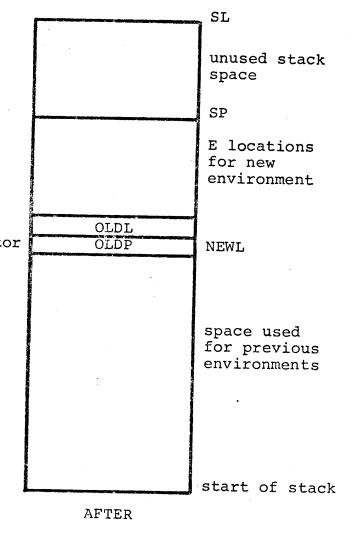

PASSED AS A PARAMETER

Unfortunately, if the return is to a function which is not the one which called the current one, SP is not reset correctly. This is expected to happen only as the result of a branch to a label which has been passed as a parameter (i.e. an error return). When such a parameter is passed (see below) from function Fl with L=L1 to F2 with L=L2, and the descriptor for the call has STK set, the parameter appears in F2 as a BLL descriptor with STK set, UWSTK set and L2 in E (see figure 2). The return (BLL) sees CLL=Ø, STK=1, UWSTK=1 and does.

$SP \leftarrow E$ ; NEWL = the E field of the descriptor addressed by E. This trick allows both SP and L to be set correctly while carrying only one number in the descriptor.

It works regardless of whether Fl and Fn have fixed or stacked environments, but requires F2 to have a stacked environment. When a label is passed to a routine which has a fixed environment, therefore, E is set to L1 and STK, REL turned off. If additional space is allocated on the stack after the call, it will not be freed when a branch is made to this label. It is believed that this deficiency is not very serious.

2) If CPA=1, arguments are copied whenever a BLL is executed. If a function has multiple results, it will have CPR on in its descriptor. This will cause CPA to be turned on in the return descriptor, and the multiple results will be returned by the arguments - copying process when the return is executed. If CPA=0, the BLLERR (2) trap occurs. A summary of all BLLERR traps and their parameters is given in the appendix. The BLLN

instruction should be used if no arguments are being passed; in this case the trap will occur if CPA=1.

The address of (actual) arguments to be copied are specified in the calling program in a list of actual argument words (AAWs) following the BLL instruction. These have a one-to-one correspondence with a list of formal argument words (FAWs) which starts at NEWP.

An argument word is formatted like an instruction. The addressing is interpreted exactly like the addressing for an instruction, but the 7-bit opcode field is treated differently, as follows.

| Bits | Name  | Contents                                                                                                                      |  |  |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3-4  | STR   | <pre>(actual argument only) structure   1 = variable   3 = computed scalar   2 = array element   Ø = array</pre>              |  |  |

| 3    | CADDR | <pre>(formal argument only) copy value    1 = copy address of actual argument    ment Ø = copy value of actual argument</pre> |  |  |

| 4    | FSTR  | <pre>(formal argument only)     l = scalar     Ø = array</pre>                                                                |  |  |

| 5-8  |       | <pre>type Ø = jump (actual argument only) l = integer</pre>                                                                   |  |  |

| 9    | ENDF  | end flag  Ø = not last argument word  l = last argument word                                                                  |  |  |

Argument copying proceeds as follows: two pointers are initialized:

next formal argument word (NFW) initialized to NEWP

next actual argument word (NAW) initialized to P+1

Then FAW + CONTENTS (NFW), and FAW is treated as an instruction

word for the purpose of computing its effective address, which

is put into FQ. Only D or LR addressing is permitted; anything

else will cause the BLLERR trap with class 4.

If ENDF (FAW) =  $\emptyset$ , NFW + NFW + 1 and copying continues. Otherwise, copying stops. If the instruction is BLL, the BLLERR(2) occurs. If it is BLLN go to step (3).

We treat NAW as we treated NFW: AAW + CONTENTS (NAW), R+NAW and its effective address is computed. The address type is F if Type = 1 (integer) otherwise E. BLLERR (5) will occur if the address type is not computable.

If type (AAW) =  $\emptyset$ , the AAW is a jump and its address specifies the next actual argument. Repeat from AAW + CONTENTS (NAW+Q), etc.

If the AAW specifies G-relative addressing with an address of  $\emptyset$  it is taken to refer to the central registers. If CVAL  $\neq \emptyset$  then BLLERR(5) or if TYPE > 6 or STR =  $\emptyset$  then BLLERR(4) will occur.

Next the types are checked. If  $TYPE(FAW) \neq TYPE(AAW)$ , the BLLERR(3) trap occurs, unless one and only one of them is <u>un-known</u>. FSTR and STR are checked according to the following table:

| FSTR   |          | Array | Variable  | Array<br>Element | Computed<br>Scalar |

|--------|----------|-------|-----------|------------------|--------------------|

|        | $\times$ | 0     | . 1       | 2                | 3                  |

| Array  | ø        | OK    | BLLERR(3) | FTNAT            | BLLERR(3)          |

| Scalar | 1        | FTNAT | OK        | OK               | OK                 |

FTNAT means that if FTN =  $\emptyset$ , BLLERR(3) occurs, otherwise the FTNAT bit is set, which will inhibit the skipping of one word in step (4).

The idea here is that if A[I] appears as an actual argument in FORTRAN and the corresponding formal B is dimensioned, an array descriptor for B must be computed, or if A appears as an actual argument and the formal is a scalar, the first element of the array must be found. A software routine is supposed to do this. It needs access to the descriptor for A; the extra incrementing of NAW is to leave room for the address of the descriptor.

Now copying takes place. If CADDR(FAW) = 1, Q is stored at FQ as an absolute IAW, except in the following two cases.

If the AAW supplied and immediate operand it is stored into FQ as an IM type Normal IAW,

If Q is the result of ROD or ROX addressing or STR(AAW) = 3, Q is stored as a read-only absolute (ROD) IAW.

Otherwise, (CADDR(FAW) =  $\emptyset$ ) the value must be copied. The details of this depend on the type:

If TYPE = 1 and STR(AAW)  $\neq \emptyset$ , OP or the A register (in the special case) is copied to FQ.

For TYPE < 6 and STR(AAW)  $\neq \emptyset$ , the number of words specified above is copied from Q to FQ, or from the central registers (A, B, C, and D) to FQ if appropriate.

If TYPE = 3 or TYPE = 4, the floating point number addressed is examined. If it is <u>undefined</u> (see <u>Floating Point</u>) the trap UFN will occur. In case the central registers are used, storing is performed as in the floating point store (STF) instruction. (Refer to <u>Floating Point</u>)

For TYPE = 7 and STR(AAW)  $\neq \emptyset$ , the four-word string descriptor is copied. If the BLL being executed is a <u>system call</u> (as described later), four ring checks are done, with P as source and each of the four word addresses as target. Furthermore, the word addresses must be non-decreasing from one word to the next, and the CPOS and CSIZE fields of the first word are copied into the others. Finally, 2 is forced into the top two bits of each word to ensure that it is a string descriptor.

For TYPE = 8 and STR(AAW)  $\neq \emptyset$  a label is copied as follows:

The first word is made absolute, i.e. Q added to the sign-extended SRW becomes the new LW if SREL is set, then SREL is cleared.

In the second word, if bits 6-23 are  $\emptyset$ , the word is replaced by L if STK =  $\emptyset$ , else

NEWL + the STK and UWSTK bits, if STK = 1.

The basic idea is to supply the proper context, so that the current local environment will be restored if the label is branched to. Refer to the discussion of how to unwind the stack to see why NEWL is used when STK = 1.

If the label is passed by a system call, the absolute address in the first word is ring-checked. Before copying the second word CLL, STK and SREL are cleared and bits 6-23 are checked. If they are not Ø, BLLERR(6) occurs.

For STR(AAW) = Ø the type is ignored. An array descriptor is also copied like a two-word scalar, except that the second word W2 is replaced by an X or ROX IAW with address equal to the effective address which results from treating W2 as an IAW. This permits an array descriptor which uses relative addressing to be passed as a parameter, since the relative address is automatically converted to absolute. If BLL is a system call, in addition two ring checks are done with P as source and both the first and last words of the array as targets. This means that if an array descriptor is passed to a higher ring, the higher ring can use it without fear of accessing storage which the calling program could not have accessed.

When the address or value has been copied, ENDF(AAW) is compared with ENDF(NAW). If they differ, BLLERR(2) occurs. If both are  $\emptyset$ , copying continues with

$NAW \leftarrow NAW + 1$ ;  $NFW \leftarrow NFW + 1$ ;

otherwise it stops. In the latter case NEWP  $\leftarrow$  NFW + 1

3) If the CLL bit is on, a return descriptor is computed and stored at NEWL. It consists of 2 words: NAW + 1

Note that this is the return address

(2B7 \* STK) + (1B7 \* CPR) + L

- i.e., the old local environment, with STK bit on if it is on in the descriptor, and CPA bit on if CPR bit is on in the call descriptor. Note that if STK = 1, then 2B7 \* STK sets the STK bit (bit 1) of the return descriptor on.

- 4) Set L to NEWL, P to NEWP, and continue execution. If the FTN bit is set, skip one word unless the FTNAT flag is on. The instruction skipped presumably will contain a subroutine call to take care of the special cases in FORTRAN mentioned earlier.

In order to state precisely and concisely how this instruction works and to describe the details of ring-checking, an SPL program is presented in the Appendix which duplicates its functioning. This program uses some special functions. (Those not mentioned here refer to fields or functions defined elsewhere in this document.)

- 1) The construction \$X + implies a ring check with R as source and X as target. As the access is a store, the trap PRO may also occur.

- 2) RINGCHECK(X) performs a ring check with R as source and X as target. If the check fails, trap MACC will occur.

- 3) RING(X) produces a number depending on the ring which contains X, say

- l if X is in the user ring

- ${\bf 2}$  if  ${\bf X}$  is in the utility ring

- 3 if X is in the monitor ring

- 4) MENTER(), MEXIT() and INTERRUPT() designate the places where the actions described under "CPU Interruptability" are taken.

- 5) EA(X) initiates the effective address calculation similar to IA(X), but the format of CONTENTS(X) is like an instruction (or an AAW) rather than an IAW.

#### 8. Programmed Operators

If the POP bit of an instruction is 1, it is interpreted as a rather peculiar kind of subroutine call rather than an ordinary machine instruction. Execution proceeds as follows:

the OPC field of the instruction is put into the indexing register (IR) and the instruction:

BLL \$G'[0];

is executed

Presumably word Ø of G will contain the address of a transfer vector. If desired, it may contain an array descriptor which limits the number of programmed operators and supplies a multiplier of 2.

There is one additional feature: BLL will initialize NAW to P, rather than to P + 1, so it will use the instruction word as the first AAW. STR, TYPE and ENDF will be taken from the corresponding bit positions of the first FAW.

# 9. System Calls

Two versions of the OPR instruction provide protected entry points into the system. The MCALL instruction works as follows:

8 bits provided by the OPR are put into IR

a BLL \$BA is executed, with BA = 604000B.

When the BLL is completed,

$G \leftarrow NEWG$ , where NEWG = 600000B.

The intention is that 604000B should contain an array descriptor with

$LB = \emptyset$

UB = total number of defined system calls

MULT = 2

which points to an array of BLL descriptors for the various protected entry points. Note on any calls to the system from a lower ring, G is saved in NEWG[14]. G is restored from G'[14] by any BLL (BLLN, POP, etc.) which crosses the ring boundary into a lower ring.

For calls into the utility the UCALL version of OPR works the same way, except that BA = 400016B and NEWG = 400000B. Note that this is the beginning of the utility ring. Variants of these OPRs exist which execute a BLLN instead of a BLL. (MCALN, UCALN)

The PDFLAG, TDFLAG bits in the status register are cleared by both MCALLs and UCALLs.

MCALLs also set the locked bit of the CPU as described under "CPU interruptability".

# 10. Traps

A machine trap is a forced transfer of control which may occur as a result of a variety of untoward events which may arise during the execution of a program. It does not involve a switch to a new process.

A trap may be fixed or ring-dependent. All fixed traps save the first 10 words of the state in the 10 words starting at 602752B. They then set G to 6000000 and do X + n; BRU 604002B, where n is the trap number. They all have a one word parameter which is put into the A register after the state is stored. The value of the parameter depends on the trap. Like MCALL-s, fixed traps also clear PDFLAG, TDFLAG, 940M and set the LOCKED bit.

A table of all fixed traps is given in the Appendix. Each one is described more fully in its proper place in the manual.

The ring-dependent traps differ in that they send control to a location determined by the ring that P is in. They store P and the parameter at G'[4] and G'[5] respectively and then clear the 940M bit in the status register and do IR + n; BRU \$G'[6].

In 940 mode, if the S bit (bit  $\emptyset$ ) of an instruction and the P bit (bit 2) are set, the instruction is called a SYSPOP. The first 10 words of the state are stored starting at L[3], then A is set to the effective address of the instruction, clear 94 $\emptyset$ M and do X  $\leftarrow$  OPC, BRU L'[2].

# 11. CPU Interruptability

The CPU described in this manual is expected to run as part of a system which includes, among other things,

- 1) Two physical CPUs, which are identical except for a number called the <u>CPU number</u> attached to each CPU. The CPUs are numbered from Ø to 1.

- 2) a separate processor called the  $\mu$ scheduler which is responsible for allocating CPUs to processes. The  $\mu$ scheduler also has facilities for causing the CPU to operate in a single-step mode, in which it stores the state, waits and then reloads it after each instruction execution, and for telling the CPU to stop execution at once (crash).

- 3) A protect mechanism which allows the various processors in the system to be interlocked or synchronized. There are eight protect lines, any of which may be seized by any processor. A line may be seized by only one processor at a time; anyone else attempting to seize the line is refused until the current owner lets it go.

This section describes the behavior of the CPU with respect to

- 1) A STROBE signal, which the µscheduler sends when the CPU is to switch processes

- 2) The single-step and crash signals

- 3) Protect 4, which is used to interlock the CPUs, keeping more than one from being in a locked state.

- 4) The timer trap, which occurs when the interval timer in the state becomes negative

- 5) The XMON and XUTIL traps

- 6) Initialization

# The relevant information is:

- a) Some information in the state

- 1) The ring in which the P-counter is contained

- 2) The XMON trap bit in SR

- 3) The XUTIL trap bit in SR

- 4) The sign bit of the interval timer, which we call TO

- b) Some flip-flops in the microprocessor which are not part of the CPU state

- 1) STROBE, which may be set by another microprocessor, normally the µscheduler

- 2) STEP, which may be set by some external device to make the CPU operate in a single-step mode

- 3) LOCKED, which is not accessible to external devices

- 4) ALARM, which is set when a system crash is impending

- c) The state of Protect 4, which will be called CPUPRO

- d) A location in absolute core called CPUWAIT which is used to keep the CPU idle after the system has crashed or between STEPs.

#### A. Idle State

When it is initialized (by setting the 0 register in the microprocessor to  $\emptyset$ ) the CPU goes into idle state.

IDLE: Clear map scan request;

GOTO IDLE IF NOT STROBE;

Clear STROBE.

PWAIT: T + contents of absolute call (6 + CPU number)

(T is the process' PRT index)

Goto PWAIT if T = Ø;

Clear absolute cell (6 + CPU number);

Clear LOCKED; Clear the map;

Find the page with the name in (T) and (T+1)

Take it as a context block and load the state

from location 2764B-2777B in it (called the SAVE

area). If the page is not found in CHT, send a STROBE2 to the  $\mu$ scheduler with a message 4B7 in absolute cell 2454B + CPU

Start executing instructions at the location given by the P-counter;

The CPU returns to the idle state whenever it dumps the state of a process.

B. Interruption of Program Execution

number \*4 then do like ABORT.

At the start of every instruction, the truth of any of the following conditions will stop execution and cause the indicated action to be taken. The conditions are treated in the order in which they are listed.

- 1) NOT LOCKED AND TO: cause timer overflow trap.

- 2) NOT LOCKED AND STROBE: dump the state into the SAVE area, send a RETURN message to the µscheduler and go into idle state.

- 3) STEP OR ALARM: dump the state into the SAVE area, clear STEP. Clear the wait location (23B + CPU number) and wait until it becomes 12343210B, then reload the state from the SAVE area and proceed.

At every step of indirection, every start of an instruction which is the target of EXU, every parameter of a BLL and in all other places where the CPU might be held up for more than a few microseconds, (MVB, MVS, CPS), conditions 1 and 2 are tested and their indicated actions taken.

#### C. Setting the Bits

XMONT and XUTILT are part of SR and may be set or cleared with SRS, LOADS or XSA.

LOCKED is set by MCALL or fixed trap. It can also be set by SLOK. It is cleared by any BLL or LOADS which leaves the monitor ring (BLL, here, includes all variants: UCALL, MCALL, POP), and can also be cleared by RLOK.

TO can be changed by loading a state from the SAVE area or by the OPR to set the interval timer.

# D. The X Traps

At every BLL or LOADS a check is made for transition into a lower ring. If there is a transition from monitor to utility or user rings, the XMON trap is caused if the XMONT bit is set. Then if there is a transition from utility to user ring, the XUTIL trap is caused if the XUTILT bit is set.

# E. The CPUPRO Signal

This protect is seized automatically at each point where LOCKED is set and cleared at each point where LOCKED is cleared. The programmer can set it himself with the PRO operate, but this is probably unwise.

### 12. Ordinary Instructions

This section contains a complete description of the behavior of the machine when interpreting an instruction word, with the following exceptions:

instructions with POP = 1 are described under "Programmed

Operators"

the BLL instruction is described under "Function Calls"

the floating point instructions are treated in a separate section

effective address computation for all instructions is described under "Addressing"

Each instruction is specified in terms of its operands, its effect on the state of memory of the running process, and any unusual traps it may cause. Traps which are caused by the addressing system are the same for all instructions and are not considered. Traps caused by the map are the same except for the read-only trap. Its occurrence depends on whether the instruction attempts to modify memory; this should be obvious from the instruction description and will not be further mentioned. The address type is S or D for instructions which modify memory.

Part of the state is a 2-bit <u>condition-code</u>. This code is set by the RESULT of most instructions as follows:

Ø if RESULT < Ø

1 if RESULT =  $\emptyset$

2 if RESULT > Ø

The RESULT is indicated in the description of each instruction.

Unless some other change in P is indicated, all instructions end with

$P \leftarrow P + 1$

The INSTD bit in the status register is set to  $\emptyset$  at the end of every instruction, except for LOADS.

The <u>address type</u> of the instruction is indicated for every instruction, e.g.,

LDA (F)

In the description some special notation is used: STORE(X,Y) stores X in the memory location addressed by Y. The storing includes some special logic for (S) type instructions if a field or character is specified as operand (refer to Use of Addresses by Instructions); ABS(T) is the absolute value of T.

ABS(4B7) = 4B7.

#### Summary of Abbreviations