# THE LOGICAL DESIGN OF AN INTERMEDIATE SPEED DIGITAL COMPUTER

Gene M. Amdahl

Department of Physics

University of Wisconsin

June, 1951

## TABLE OF CONTENTS

|                                                                                                                                                                                                   | Pag                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Proface                                                                                                                                                                                           | 11                                           |

| Chapter I - Solution of Problems on a<br>Digital Computer                                                                                                                                         | 1                                            |

| Section 1 - Introduction 2 - Flow of Calculation 3 - Flow of Information 4 - Order System                                                                                                         | 1<br>2<br>7<br>8                             |

| Chapter II - The Proposed Logical Design                                                                                                                                                          | 14                                           |

| Section 1 - Introduction 2 - The Magnetic Drum 3 - The Use of the Drum 4 - First Design Feature 5 - Component Requirements 6 - Second Design Feature 7 - Component Requirements 8 - Modifications | 14<br>15<br>17<br>18<br>19<br>20<br>25<br>27 |

| Chapter III - Choice of Components and Their<br>Operational Requirements                                                                                                                          | 30                                           |

| Section 1 - Introduction 2 - Division of Drum 3 - Supplementary Features 4 - Order Interpreter 5 - Time and Track Selectors 6 - Arithmetic Unit 7 - Input and Output                              | 30<br>31<br>33<br>37<br>40<br>41<br>51       |

| Chapter IV - Evaluation                                                                                                                                                                           | 53                                           |

| Appendix I - Program of a Simple Calculation                                                                                                                                                      | 57                                           |

| Appendix II - Survey of Present Machines                                                                                                                                                          | 63                                           |

| Appendix III - Survey of Computing Machine Components                                                                                                                                             | 74                                           |

| Tables and Diagrams                                                                                                                                                                               | 79                                           |

| List of References                                                                                                                                                                                | 97                                           |

#### PREFACE

The objective of this thesis is to describe the logical design of a general purpose digital computer presenting the arguments underlying the final choices of operation and components. The scope of the thesis is limited to the logical design, including the requirements of all operational components. It is worthy of note that a comparatively large freedom of physical design exists, satisfying the logical requirements which are imposed.

The appendices will include sufficient background material on existing computing machines and components, so that a reasonably careful comparative evaluation may be made from the material presented.

The sources of material for this discussion are very limited and, in many cases, are rather nebulous. In most cases the sources have furnished a background which facilitated the formulation of the overall views presented. Although portions of the thesis may appear to present material without due credit, in most cases the formulation is entirely independent, and if duplication occurs it is without the knowledge of the author.

In particular, the author wishes to acknowledge three sources of informative assistance: The Aberdeen Proving Cround, Haryland, for the opportunity of studying the coding system for the EDVAC, thus learning a great deal about generalized logical systems of computing machines; Engineering Research Associates, Saint Paul, Minnesota, for their assistance in evaluation of the computer and for suggestions for simplification of the controlled delay units in the arithmetic components; Charles H. Davidson, University of Misconsin, for detailed checking of the logical operation, a number of helpful criticisms and suggestions.

At present work is being done on design and testing of physical components of this machine, and arrangements have been made to built it at the University of Wisconsin. Because of its inherent integral synchronization, the machine has been named the WISC, Wisconsin Integrally Synchronized Computer.

#### CHAPTER I

## SOLUTION OF PROELESS ON A DIGITAL COMPUTER

## 1. Introduction

Perhaps the simplest and most profitable approach to the understanding and designing of any physical device is a thorough study of the operations the device may be called upon to perform. In the case of a digital computer this entails a study of computation. This chapter will survey the steps involved in most computation and will emphasize in particular the aspects of routines which may be iterative in any one part of the computation or which may recur in several different parts of the computation. Very few detailed examples will be employed, but it is hoped that the generality of the discussion will make evident the generality of the concepts involved.

The initial step in carrying out any computation is the planning of some procedure which leads to the desired result. The initial procedure will in general contain: (1) organization and reduction of initial data into a readily usable form; (2) arrangement of a sequence of operational steps such that data required to perform a particular operational step are available in the form of initial data or as the results of previous steps, these steps leading, in general, to some point of discrimination and/or iteration; (3) repetition of the previous procedure with different initial data to provide a table of results or to provide some means of controlling changes of initial data to approach results possessing desired properties, such as boundary conditions.

The next step in the computational procedure is to make a further breakdown of the initial plan. In general, this will leave a series of elementary operations to be carried out, such as addition, subtraction, multiplication, division, searching tables of functions, or comparison of results at any point to determine convergence. The less elementary operations such as

extraction of square roots, integration, or generation of simple functions may, of course, also be reduced to the same set of elementary operations. It is of interest to note at this point that the reduction of these less elementary operations into the elementary ones involves the same three major steps that the initial procedure for the overall solution involved. This simple, but very general, logical scheme of computation may easily be diagrammatically formulated, and, with the introduction of a very limited terminology, the complete breakdown of a computation may be easily described or carried out.

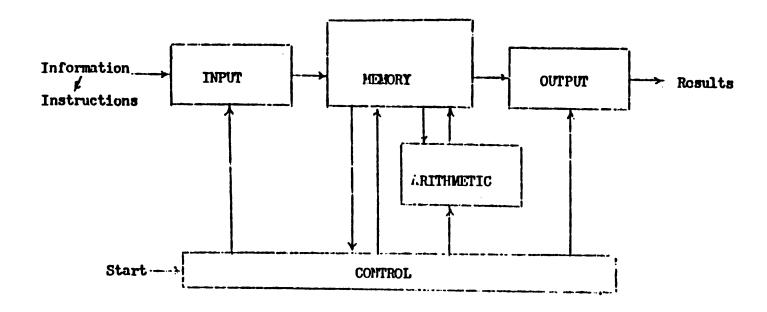

Before going into greater detail on the breakdown of computation, it is advisable to give a very simplified description of a computing machine. A digital computer in general consists of five major components (see Figure 1):

(1) an INPUT device which supplies information (orders and numbers) to the computing machine; (2) a METORY system which stores information until the desired time and presents the information to the desired place upon instruction;

(3) an ARITHMETIC component which performs the desired operations on numbers upon instruction; (4) a CONTROL unit which interprets orders and supplies corresponding instructions to all other units, the orders being supplied by the MEMORY or INPUT or both and under the control of the CONTROL unit itself; and (5) an OUTPUT device which prints or punches the results of a computation.

Numbers and orders are filed in the HEMORY by "location", that is, to obtain a "word" (order or number) from the HEMORY, one must specify the spatial (and in some cases temporal) position of this word in the memory medium.

# 2. Flow of Calculation

This section contains the diagrammatic formulation of the calculational procedure as it is carried out in a computing machine or in hand computation.

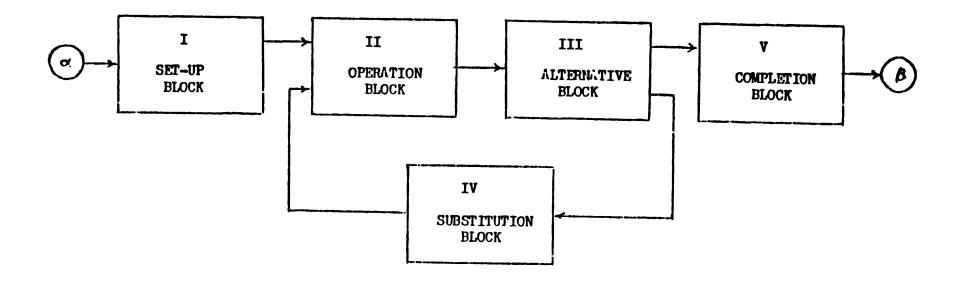

Figure (2) shows the general scheme, which may represent the whole computational scheme and is then called a "sequence", or which may represent

an individual complex operation and is then called a "subsequence". This diagram is composed of "blocks of orders" stored in the memory system of the

computer, each block performing a particular function, and these blocks being

appropriately interconnected; such a diagram is called a "flow diagram". This

diagram represents the flow of calculation and should not be confused with

flow of information.

#### a. Setup Block

This flow diagram of a sequence, or subsequence, begins just after the point (a), where block number (I) is reached. The first block is a "setup block" in which the reduction of initial data and preparation of the following block for the first calculation is carried out. In many subsequences this setup block provides the means of obtaining an initial approximation of sufficient accuracy to reduce materially the number of iterations required to converge to the correct results; for instance in a square root subsequence the determination of the position of the decimal point would be of great assistance. Also, in numerical integration of a differential equation, the process of point by point prediction and correction is handled in a different fashion at the beginning point, or points, than it is throughout the rest of the range of integration. In such cases the setup block would contain the initial calculation procedure.

## b. Operation Block

The second block (II) is called an "operation block". In this block the main body of the calculation is carried out. In an iterative process this block performs the complete set of operations required to obtain the n+lst approximation from the nth approximation, or to predict the value of a function at the n+lst point from the known values at the previous points. In this

operation block the calculational process may be sent through a number of subsequences in order to carry out any non-elementary operations which may be required, such as the extraction of a square root.

An example of the programming of a simple problem is given in Appendix I.

c. Alternative Block

Elock (III) performs a comparison and is called an "alternative block". The comparison may be between the new approximation and the previous one, to see if the convergence is sufficient. The difference between two approximations is in general required to be smaller than some previously assigned number  $\varepsilon$ . The comparison may be made upon index as well, that is, if a fixed number of steps is required, the number of times that the calculation has proceeded through the operation block can be recorded and compared with the stipulated number of steps. As the name "alternative" implies, there is a choice, a choice of returning and going through the iterative process once more, or of going on to the next stage of the computation.

#### d. Substitution Block

If the alternative block sends the calculation through the iterative process once more, the next block reached is the "substitution block" (IV). This substitution block is essentially a restricted version of the "setup block", in that it prepares the operation block for the n+1st operation by changing index and indexed numbers in the required places, just as the setup block prepared it for the first operation. The use of indices, and the necessity of changing them, is to be found in the approximation of a function by the leading terms in its polynomial expansion; in this case each trip through the operation block computes another term in the polynomial by means of the term's index and adds it to the previous sum of terms.

The sbustitution block must also re-file information which depends upon the index. This can readily be demonstrated in examples where computing the nth value requires use of the previous value (n-lst), thus computing the n+lst value requires the use of the nth. Since numbers are specified by storage location, the nth value must be substituted for the n-lst in order to carry out the computation.

This is a fairly complete description of the substitution block and, as well, extends the knowledge of internal requirements of the setup block. The substitution block closes the "loop" and makes the iterative calculation progressive.

## e. Completion Block

If the alternative block sends the calculational process on to the next stage, the last of the blocks (V) is reached. This is the "completion block" and its function is the disposition of the result, or results, of the sequence just outlined. The disposition of results may involve having a table of results printed out, if the loop preceding this completion block was the main computation loop. It may similarly involve filing the results into sequential storage locations for later printing or for use in some other part of the computation if this sequence (in this case, subsequence) is but a portion of the main computation. After completion of the operations in this block, the calculation proceeds to the next stage, denoted by  $(\beta)$ .

## f. Remote Connectors

(a) and ( $\beta$ ) are called "remote connectors". Their function, although perhaps not so easily visualized in some of their forms, is to connect the subsequence into the main computational sequence at any and all desired points. In some computers (a) and ( $\beta$ ) will be physical connections, but in many of the newer ones (a) will represent the location of the first order in this subsequence

and  $(\beta)$  will be the location of the first of a group of orders to be carried out after the completion of the subsequence. An example of this might be a sequence composed of N orders stored in locations  $A_1$ ,  $A_2$ , ...  $A_{\beta-1}$ ,  $A_{\beta}$ , ...  $A_N$ . The computing machine carries out these orders until it reaches the order in location  $\Lambda_{\beta=1}$ , at this point the calculation has progressed to the point where a subsequence is to be used, e.g. a square root, so the order in location  $h_{\beta-1}$  contains the information that the machine is not to carry out the order in  $A_{\beta}$  next, but is to carry out the order in location  $C_1(C_1 = a)$ , which is the first order in the square root subsequence  $(C_1, C_2, \dots C_N)$ . Since the computing machine follows a sequence of orders with no "memory" of its previous history, some means must be provided for putting the information into the order in location C, (the end of the square root sequence) that the following order to be carried out is in the location  $A_{\beta}(A_{\beta} = \beta)$ , thus permitting the original calculation to be carried out. The order which puts this information into  $C_M$  must be read prior to  $A_{\beta-1}$ . There is one additional complication, and this is that the location of the number whose square root is desired must be made available to the square root sequence, for, as presented so far, this number is available to only the A sequence.

The foregoing material has presented the flow of calculation as it is carried out by a human or mechanical computer. The system presented is obviously very flexible, and the ease with which this flow can be directed determines the flexibility of a computing machine. In a number of machines, such as the DIAC as originally planned and built and in most of the I.B.M. computers, the flow was directed by means of physical connections, and the change of problems required rewiring the connections between computer elements. In most later machines the means of supplying orders to the machines have been of such a nature that the need for physical interconnections of the former

type is climinated. This method of supplying orders consists of having a numerical code which stipulates the desired operation, and storing these numbers in some sort of memory medium. The machine proceeds to "read" these numbers stored in its memory and carries out their instructions. Since the memory is not destroyed by reading, and since the machine has access to all parts of this memory, it is possible for the machine to follow the same set of orders over and over again, providing iteration without having to supply a new set of orders for each repetition. With this system of order supply, the flexibility of a computing machine is governed mainly by the orders it is capable of carrying out. The other limitations are the speed with which the machine can carry out a computation, the available memory space, the accuracy with which the individual computations may be carried out, and freedom from mechanical failure. There is one other point to be considered, however, and this is the ease of preparing a problem for solution within the machine; this point will be considered in greater detail in a number of places in the following chapters.

# 3. Flow of Information

the flow of information has not been considered to any appreciable extent.

In order to investigate the flow of information, some study of the forms in which information is utilized is indicated. Information with regard to numbers alone exists in two forms: (1) the size of the number, and (2) location of the number in the memory medium. Once the location of the number is known, the rest of the information is available upon reading the number at this location. Information with regard to orders is much the same, although it will become necessary to expand upon the information that may be stored in a numerically coded order. Nost orders generally consist of requiring a particular

operation to be performed upon a number (numbers) stored in a specified storage location (locations). The requirements of the flow of information of this type can be satisfied in either of two ways: (1) placing the desired number into the stipulated storage location prior to its use, or (2) controlling the storage location specified, in such a manner that it is at all times the proper one. Both of these methods of information flow control are used in most of the computing machines, and the choice between the two is generally determined by the number of operations required to carry them out. An example of this can be found in the square root subsequence; in this subsequence several different operations are performed upon the number (y) whose square root is desired, and it is simpler to move (y) into a storage location which can remain assigned to the square root sequence than it is to change all of the locations specified in the various orders.

There is one more type of information flow to be considered here, and that is the flow of control information, i.e. the correct sequence of orders. In the examples, the subsequences have terminated in a remote connector  $(\beta)$ , where  $(\beta)$  is the storage location of the order following the order which shunted the calculational process into the subsequence. Since this subsequence should be available to other parts of the computation, the location  $(\beta)$  will differ depending upon which part of the computation required the subsequence at this time; hence  $(\beta)$  will have to be provided before entering the subsequence in order to guarantee proper reentry into the computation. This type of information flow control is similar to the second numerical type, i.e. proper control of the storage location specified.

# 4. Order System

The remainder of this chapter will be concerned with the properties of a system of orders capable of carrying out this generalized computational

scheme. The system of orders described will be those which are to be employed in the computing machine presented in later chapters, but a few references will be made to systems which are in use in other machines. In particular, mention should be made of the possibility of breaking these orders into much more elementary operations which can be combined to correspond to those described below; this is done in a large number of the new machines and its merit depends upon the machine design.

#### a. The Arithmetic Orders

The first set of orders to be described are the arithmetic orders:

Addition, Subtraction, Multiplication and Division. Each of these four orders supply four items of information: (1,2) the storage locations of the two operands, (3) the specified operation, and (1) the storage location in which the result is to be stored.

#### b. The Information Flow Order

The order controlling the internal flow of information is described next, this is the "Extract" order. The Extract order has the property of being able to extract any part of a word in one storage location and any part of a word in another location, combine these two parts to form a new word which is to be stored in a third storage location. It is also important to mention that the information in the two original storage locations is not affected by this procedure and that the previous information in the third storage location is completely annihilated and replaced. This extract order is, then, obviously capable of transferring a number into any desired storage location or to substitute new storage location specifications into other orders. In addition to satisfying these requirements of information flow, the extract order is capable of performing far more exotic operations such as providing one number with the algebraic sign of another, removing a specified group of

digits from a number for separate arithmetical operations, e.g. arithmetical operations to be performed on exponents, and a host of other possibilities.

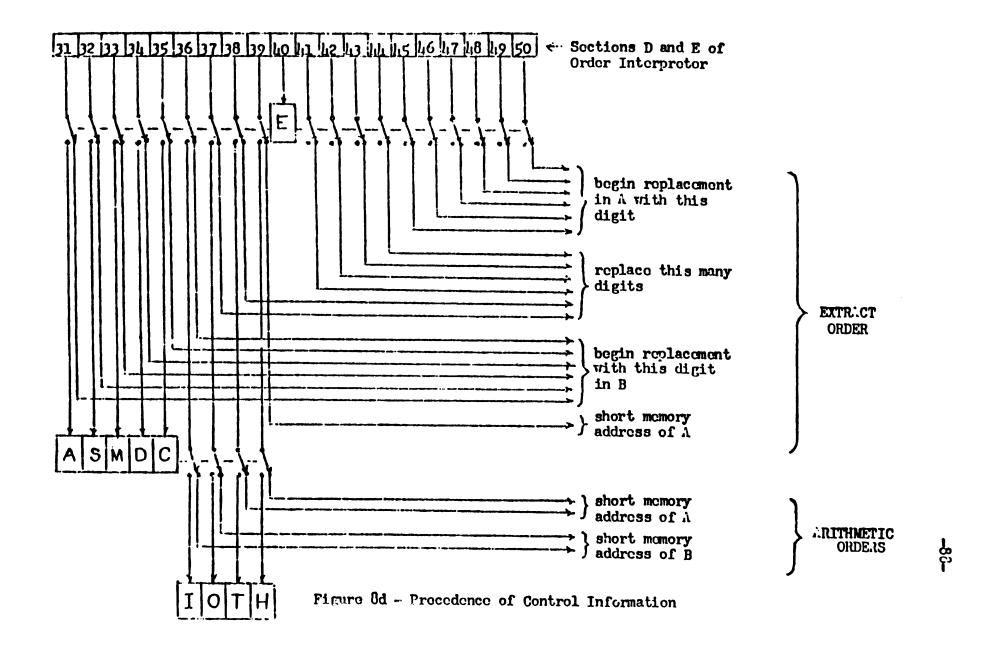

The Extract order supplies seven items of information: (1,2) the storage locations of two operands, (3) the statement that this is an Extract order, (4) the position of the first of the group of digits in the first operand which are not to be used in making the new word, (5) the number of digits which are not to be used, (6) the first of the group of digits in the second operand which will be used instead, and (7) the storage location in which this newly formed word will be stored.

## c. Flow of Calculation Order

There are two orders controlling the flow of calculation: Transfer and Comparison. These two orders control which chain of orders will be carried out in the immediate future. In the EDVAC the Transfer order occurs as a part of every order, that is, every order stipulates the location of the order that is to follow. In many machines, and in particular in the machine proposed in this thesis, orders are read from sequential storage locations. Since it is desirable to make a single subsequence available to all parts of the main computational sequence where needed, some means must be available to transfer from the sequence to a subsequence and back again, the Transfer order will generally be used to carry out these operations. In an iterative process it is also desirable to be able to use the same set of orders over and over again until completed, some means must also be provided for this, with the additional provision that this order has contained within itself the ability to determine the necessity of reiteration, such an order is the Comparison order (sometimes called a Conditional Transfer order).

The Transfer order contains two items of information: (1) the statement that this is a Transfer order, and (2) the storage location in which the

following order is to be found.

The Comparison order is a combination of the Subtraction and Transfer orders, and contains four items of information: (1,2) the storage locations of two operands, (3) the statement that this is a Comparison order (subtraction specified), and (4) the storage location in which the following order is to be found if the result of the subtraction is zero or negative. Since this machine reads orders from sequential storage locations, a positive result exerts no control and the machine continues reading orders in the original sequence.

## d. The Communication Orders

The orders that allow communication between the machine and the exterior world are the "Read-in" and "Read-out" orders. These orders can be made very general, although in the machine proposed, the present plans are, at least for the initial construction, to restrict them to a minimum. They can, however, be expanded without alteration of the original construction to take on a broader scope. The general formulations, and then the restricted versions will be presented.

The Read-in order can stipulate: (1) read in from a particular source of information (several choices) (2) beginning from a stipulated position in this source and storing this information sequentially into storage locations beginning with (3) the first storage location specified and continue filling to (4) the final designated storage location, and (5) the location of the order which follows the Read-in order.

The initial plans for the proposed machine are to have a single input mechanism and to arrange material within it so that the desired information is supplied in the proper sequence.

The Read-out order has the same general and restricted formulation as does the Read-in order.

## e. Halt Computation Order

The final order required to complete the order system is the Halt order. This stops the operation of the machine. This order has two uses in general, to stop the machine after the computation has been completed, or to stop the machine at any desired point in the computation in order to study the results available to check on the calculation or to make decisions on computational procedures.

A total of ten orders has permitted the computing machine to carry out the general computational scheme formulated earlier in this chapter. They provide for the arithmetic operations, the control of the flow of information, the control of the flow of calculation (including the determination of the necessity of reiteration), communication between the computing machine and the exterior world, and ability to halt the computation at any desired point.

## f. Storage of Orders

Up to this point it has been implicitly assumed that some sort of memory system for storing words (orders and/or numbers) has been incorporated, and that the desired word may be obtained by specifying its location within the memory system. No mention has been made of requiring separate memory systems for orders and numbers, and, indeed, separate memory systems are not required. It is common practice to store numbers and orders interchangeably throughout the memory system, not even reserving some section of the memory for orders and the rest for numbers, except that sequences of orders must be placed in sequential storage locations. The advantage of this system of storing "words" is found in the maximum utilization of storage capacity,

for if a sequence of orders have been used and are no longer required, this space may be used for the storage of intermediate results, new data or new orders, whichever is most desirable.

Perhaps the first reaction to the intermingling of numbers and orders is to raise the question: how can the machine tell the difference between a number and an order? The answer is: it cannot and does not need to, for in programming a problem the machine is furnished a connected calculational path and the "order reader" reads only the words which form the steps of this path, thus coming into contact with orders alone.

## CHAPTER II

#### THE PROPOSED LOGICAL DESIGN

## 1. Introduction

The objective in the design of this computing machine is simplicity, simplicity of construction and of problem preparation. In achieving this objective the requirements of reasonably high speed of operation and general applicability must necessarily be satisfied, if an instrument of considerable utility is to result.

In achieving general applicability and simplicity of problem programming, great care was exercised in choosing a set of orders which had extreme flexibility and yet were a minimum in number with easily and well defined functional properties. The set of orders chosen is dependent upon the design of the machine itself, in particular, it is dependent upon whether the arithmetic unit is self-programmed or not. The chosen set of orders described in the first chapter are for a self-programmed arithmetic unit and are, consequently, a much simpler set than would have otherwise been required.

In the formulation of this logical design, two types of interrelations must be considered: (1) the interrelation of simplicity of construction and simplicity of problem programming, i.e. a reduction of complexity of the machine should not shift a corresponding burden upon the programmers; and (2) the interrelation between operating components making up the machine. These two will be considered in greater detail in the arguments to follow.

The criteria to be satisfied by the design are: a minimum of parts are to be used and all component's capabilities are to be fully exploited.

The arguments leading to the chosen design will not be presented in detail, but sufficient information to indicate the line of reasoning will be included.

Parallel operations on numbers in a machine which uses a cyclic memory

is wasteful of arithmetic equipment, for the average time required for locating numbers in the memory system is long compared to the time required for performing the arithmetic operations. This does not allow efficient utilization of the arithmetic unit's capabilities.

Similarly, use of a static or rapid cycle memory in a machine which performs serial operations is wasteful of memory equipment, for the memory supplies numbers more rapidly than they are treated. Use of a longer cycle memory would offer a considerable increase in memory capacity without appreciably affecting the total operation time.

It is evident that to attain a reasonable balance in operating times, two designs are possible: (1) parallel operation with a static memory system or (2) serial operation with a cyclic memory in which the time required for the arithmetic operations is approximately equal to the memory cycle time.

In order to utilize a minimum of parts, the chosen design will be the second, for both the serial arithmetic unit and the cyclic memory system require a considerably smaller amount of equipment than do the others. However, this combination is much slower than the first, and represents an intermediate speed rather than a high speed computer. It should be pointed out that the actual speed of the proposed machine is dependent on the memory medium utilized, and that the use of a memory medium of the same nature as that employed in several "high speed" computers will yield approximately equal operating speeds.

## 2. The Magnetic Drum

In order to expand upon the logical design, and to go into the details of the requirements of the associated components, it is advisable to choose

<sup>\*</sup> Refer to Appendix III for the properties of the components which provide for these operations.

a physical model which can be described with relative ease. The actual model to be chosen will be the magnetic drum, however, it should be borne in mind that the magnetic drum is but a vehicle for exposition, and that the context and diagrams may be readily translated into any cyclic memory system.

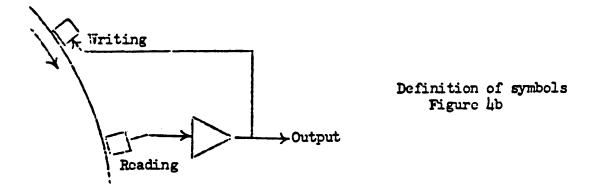

The magnetic drum itself is perhaps a sufficiently new device that some explanation of its operation should be included. Physically, it consists of a cylindrical drum which is rotated about its axis. Bounted on a fixed framework about the drum are reading and writing heads, each head reads and/or writes onto a peripheral track about the drum as it turns by. A large amount of information may be stored in any peripheral track and a large number of such tracks may be spaced along the length of the drum.

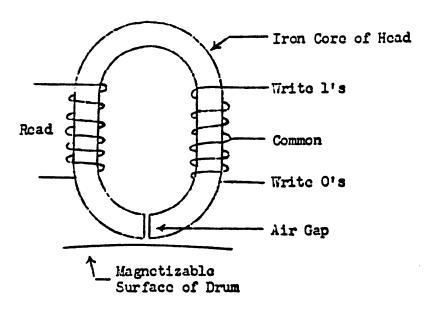

The surface of this cylindrical drum is sprayed with a thin coating of magnetic iron oxide, which can record a pulse of magnetic polarization in either of two opposing directions. In practice, the entire surface is magnetized uniformly in one direction to provide a "zero" background, and the presence of a "one" is indicated by a small region of opposite polarity. A reading and/or writing head consists of a magnetic core with one or more windings having an air gap mounted in very close proximity to the surface of the drum (see Figure 5). To write a number, a pulse of current is sent through a winding at the desired instant, producing a momentary high magnetizing force at the air gap, and hence magnetizing a tiny region of the surface. This region is called a cell. These pulses are in one direction for a "one"; the opposite for a "zero". Since the momentary magnetizing forces are sufficiently high to override the previous condition of the cell area, it is never necessary to crase as such, for the action of writing a new number automatically replaces any old information with the new. In reading, the sequence of cells (or digits) passing the air gap induces voltage pulses in the windings.

which are amplified, shaped and supplied to the other components of the computing machine.

## 3. The Use of the Drum

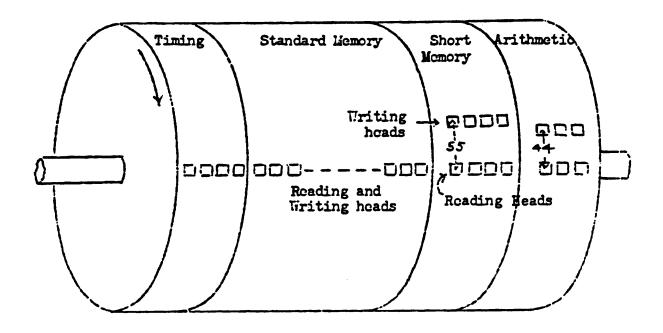

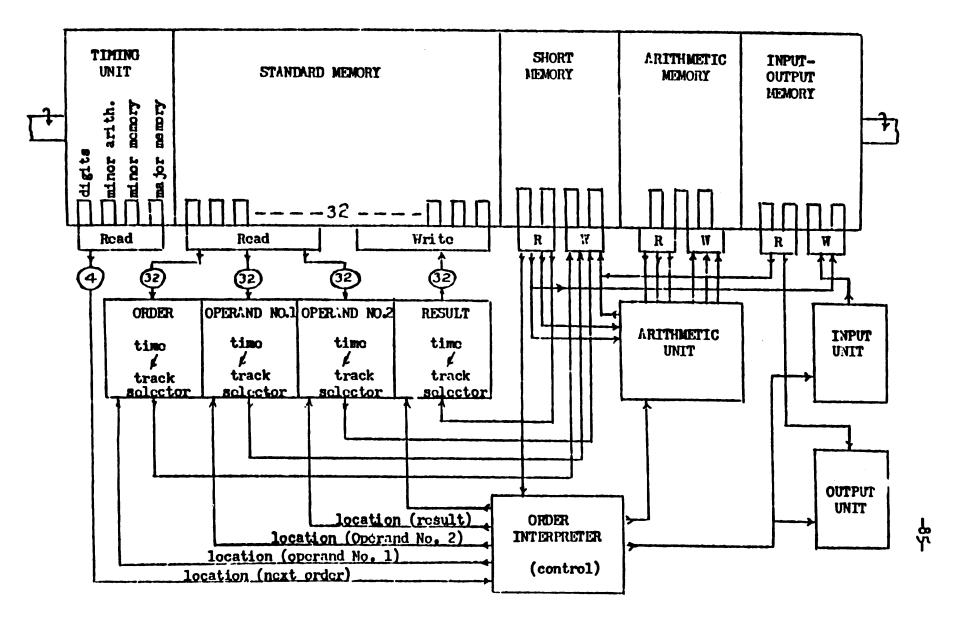

In the proposed computing machine the drum is divided longitudinally into four sections: (1) timing tracks, (2) standard memory, (3) short memory, and (4) arithmetic tracks (see Figure 4).

In the <u>timing</u> section several (four, as will be shown) tracks are used to provide timing pulses for synchronization of the operating circuits.

The <u>standard memory</u> section corresponds to the memory system of the general computing machine described in Chapter I and Appendix III, and will be used to store words (numbers and/or orders) for the computing machine. The standard memory consists of a number of parallel tracks around the drum. In each track several words can be stored, these words are stored in serial form, for the arithmetic unit is of the serial type and must receive numbers in this form. A given word stored in this memory will pass one of the reading heads at a certain time during each cycle of the drum so the word may be "read" by specifying which track this word is in and at which angular position about the drum.

A rather unique feature is obtained by wiring a pair of these reading and writing heads in a feedback circuit (see Figure 1). If the reading head furnishes its information to the writing head which leads it by an angle  $\theta$ , information once supplied to the pair will be repeated over and over with a period  $\theta/2\pi$  times the period of the drum. Such a circuit is called a "recirculator". This recirculator becomes in effect a short memory where a limited amount of information may be stored to be continuously available. The actual function of the short memory will be to store numbers between the standard memory and the arithmetic unit, for if a number is read out of the

standard memory before the arithmetic unit can accept it, this number must be recirculated until it is accepted. A consequence of this function of short memory is, that the angle 0 between reading and writing heads should be equal to the angle subtended by a word in standard memory, so that a recirculating word will always be in phase with the word positions in standard memory. (The requirement of a short memory is unique to the proposed computing mechanic).

The <u>arithmetic</u> section of the drum will also consist of recirculators, these recirculators will be used for storage of the operands and the partial results during the arithmetic operation, providing a relatively inexpensive storage medium for this purpose. The rest of the logical design must be known before the requirements of this arithmetic section can be described satisfactorily.

In operation, the computing machine will go through four basic steps:

(1) locate the desired order in standard memory and interpret this order,

(2) locate the two operands in standard memory which are called for in this order,

(3) perform the specified operation on these two operands, and

(1) file the result of this operation into the stipulated storage location in standard memory. It should be noted that three words are located and read from standard memory and that one word is being written back into it.

1. First Design Feature

Steps 1, 2 and 4 of the above operation may require one full revolution of the drum, for the word can be obtained only when the specified location in standard memory is passing the reading and writing heads.

The first design feature will be to allow one full revolution of the drum for carrying out each of the four steps outlined. This guarantees that steps 1, 2 and 4 will be completed during their allotted times, but demands

also that the time required for carrying out the most difficult arithmetic operation (step 3) be less than or equal to the revolution time of the drum.

The operation now consists of four revolutions of the drum, each revolution guaranteeing the successful completion of one of the basic steps. These four steps may now be overlapped with those of other operations such that four steps may be carried out simultaneously (see Table 1): (1) order N is being located, (2) the two operands called for in order N-1 are being located, (3) the operation specified in order N-2 is being carried out in the arithmetic unit, and (4) the result of order N-3 is being filed away into the stipulated storage location. There are, then, four simultaneous steps being carried out, each referring to a different order or operation, so that the result is an accomplishment of a complete operation every revolution of the drum.

## 5. Component Requirements

Returning to the standard and short memory sections of the drum, it may be seen that during a given revolution four words are communicated between the standard memory and the rest of the computing machine. An order and two numbers (or operands) are read out of standard memory, the order being destined for an "order interpreter" (see Figure 6) which will translate the serial digital information into static control voltages for the rest of the machine, and the two numbers destined for the arithmetic unit to be operated upon. The fourth word communicated is a number, the result of an arithmetic operation, which is written into standard memory.

The order and two operands read out of standard memory are located some time during the memory cycle and must be stored until the end of this cycle, at which time they are delivered to their respective destinations. The "result" number is delivered from the arithmetic unit at the beginning of the

memory cycle and must be stored until it can be written into the proper position in standard memory. The function of the short memory section is to provide the storage for these four words, and it is obvious that four recirculators are required for this purpose.

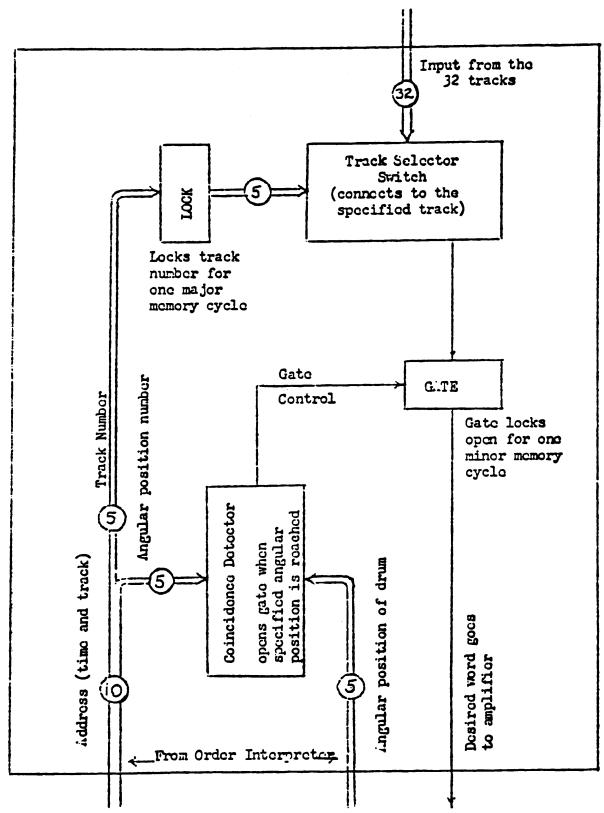

It might also be noted at this point that some sort of unit will be required to "connect" the desired location in standard memory to the short memory recirculator which is (or is to be) temporarily storing the information (see Figure 6). The properties of such a unit are: it must be capable of arranging for connection of the recirculator to the desired track in standard memory, and to close this connection during the proper part of the memory cycle to pick out only the one desired location. Such a unit is called a "time and track selector", and four of these units are required if it is desired to be able to connect to storage locations which are passing the reading and writing heads at the same time, one being required for each recirculator. The information of which track and time (angular position) to contact is supplied by the "order interpreter", for this information is contained in the orders.

# 6. Second Design Feature

The requirement of the first design feature was that the time for the longest arithmetical operation be less than or equal to the period of rotation of the drum (or memory period). The second design feature is concerned with maximizing the efficiency of the arithmetic unit under such restrictions. The efficiency is greatest when the operation time is precisely equal to the period of the cyclic memory, and the achievement of this constitutes the second design feature. The combination of the two design features can best be termed "INTEGRAL SYNCHRONIZATION", for all units of the computing machine form an integrated system, carrying out their functions simultaneously and

in identical periods of time.

This second design feature immediately imposes difficulties in efficient utilization of the operation time, for with "fixed point" number representation the various arithmetical operations are performed in different lengths of time; multiplication and division take about n times longer for n-digit numbers than addition and subtraction. In addition to this, of all number representations (with respect to base) only the binary system permits division to be performed as rapidly as multiplication may be performed; and then only under rather stringent conditions, i.e. the dividend must be less than twice the divisor.

These are not essential difficulties however, for they are removed by the introduction of two numerical features, both of which are desirable from the point of view of simplicity of construction or simplicity of problem preparation. These features are: (1) binary representation of numbers and (2) a floating binary point. The binary representation allows multiplication and division to be performed in the same length of time, provided the conditions for division are satisfied. The floating binary point makes it possible to satisfy at all times the condition on the division process, thus speeding it up. The floating point also makes the operations of addition and subtraction require the same length of time as multiplication and division, but accomplishes this by reducing the rate of performance of the first two. The reduction in speed of addition and subtraction should not really be considered a loss however, for the time is available and the additional operations are certainly of a useful nature.

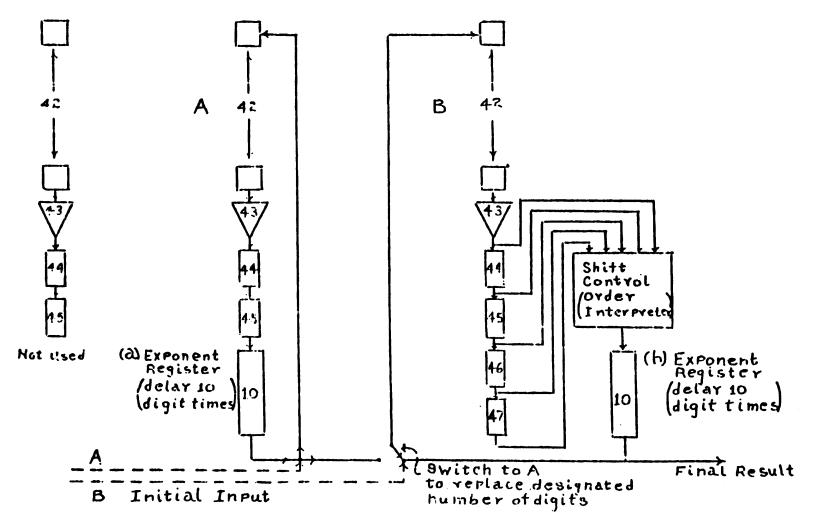

The introduction of the floating-point feature does require some additional equipment for addition and subtraction of exponents and for control of shifting numbers, but the increase is not very large relative to the amount

of equipment already involved. In addition greater storage capacity is required to store an equal quantity of numbers, for the values of the exponents must also be stored, however, a corresponding increase in useful information is made available.

To complete the requirements that must be satisfied before integral synchronization may be achieved, an analysis of the relationship between the memory and arithmetic units must be made. The first analysis will ignore the requirements of providing short periods of time between numbers, sufficient to perform switching operations.

Multiplication furnishes the simplest example and will be used to initiate the analysis. In multiplication of two n-digit numbers, each of the n digits of the multiplicand must be multiplied in turn by each of the n digits of the multiplier, forming a total of  $n^2$  partial products with their corresponding powers of two (binary system). The product is obtained in binary form by summing the n<sup>2</sup> partial products. In actuality the process of summation of the partial products is accomplished by summing each partial product as it is formed, thus requiring no additional time. The formation of partial products occurs as rapidly as digits are presented to the multiplication component, so n2 digit-times are required for the formation of the product. It is desirable to have the memory system supply the n digits of each operand to the arithmetic unit at the same rate as the internal storage (arithmetic section of the drum) of the arithmetic unit supplies them to the multiplier, so that a speed matching device is not needed; hence, to maintain integral synchronization between the arithmetic and memory systems, the period of the memory system must also be equal to n<sup>2</sup> digit-times. The addition of the exponents, which must also be performed, is carried out in a special exponent

register and is done simultaneously with the rest of the operation.

In the following chapter it will be shown that the division process will require precisely the same length of time, i.e. n<sup>2</sup> digit-times.

Addition and subtraction do not always require n<sup>2</sup> digit-times, the actual time varying from 2n to n<sup>2</sup> digit-times, but n<sup>2</sup> are required to assure completion, hence these two operations will be considered to utilize the full capabilities of the arithmetic unit as well as multiplication and division;

The requirement of  $n^2$  digit-times making up one period of the cyclic memory imposes relationships between the number of digits of information in a word (significant digits, exponent value and the algebraic signs of the number and exponent make up a word), the number of significant digits in a number, and the number of words which fit into one period of the memory. These relationships must be satisfied if maximum utilization of the memory and arithmetic units are to be realized. An additional condition, for maximum use of order information, might also be imposed: that the number of words in a memory period be equal to an integral power of two. Designating m as the number of digits in a word, n as the number of significant digits, and  $2^{\frac{1}{2}}$  as the number of words in a memory period, the relationships are:

(1)  $n^2 = m \times 2^{\frac{1}{2}}$ , (2) m > n, and (3) m, n, n are integers. The spectrum of n and n for a given value of n may be generated by a single integer n, where n = 1, 2, 3, ... (n = 0 generates n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n = n =

$$\frac{\mathbf{j}-\text{even}}{\mathbf{n}} = 2^{\mathbf{j}} + \mathbf{k} \times 2^{\mathbf{j}/2}$$

$$\mathbf{m} = 2^{\mathbf{j}} + \mathbf{k} \times 2^{\mathbf{j}/2} + \mathbf{k}^2$$

The choice of j and k must be made in such a fashion that n and m are reasonable values, and the choices will be taken to be: j = 5, k = 1, yielding  $2^{j} = 32$ , n = 40 and m = 50. This represents 32 words in a memory period, 40 significant digits in a number and 50 digits to represent a word (number or order). 40 of the 50 digits in a number are the significant digits, 8 are used as the exponent value, and 2 are to be used for the algebraic signs of the number and the exponent. The numbers are to be represented as  $\pm p \times 2^{\pm q}$  where 1 > p > 1/2 and 255 > q > 0. The 40 significant binary digits are approximately equivalent to 12 decimal digits, and the  $2^{\pm 255}$  range in number size is approximately equivalent to  $10^{\pm 75}$ .

It was mentioned earlier that provision of some "dead space" for performing switching operations is required. This switching time must be provided between words in the memory system and between significant digit groups in the arithmetic unit. Let the switching time provided in the arithmetic unit be equal to a digit-times, and that between words in the memory unit be equal to  $\beta$  digit-times, where  $\alpha$  and  $\beta$  are integers. The set of altered relationships are: (1)  $n(n+\alpha) = 2^{\frac{1}{2}}(m+\beta)$ , (2) m n, and (3) n, m, j,  $\alpha$ ,  $\beta$  are integers. The spectrum of m and n are yielded by the original set of equations, and an additional set of equations for generating the spectrum of  $\alpha$  and  $\beta$  by a second integer, h, is provided:

$$\frac{\mathbf{j}-\text{odd}}{\alpha = h \times 2^{\frac{1}{2}}}$$

$$\frac{\mathbf{j}-1}{2} \qquad h = 1, 2, 3, \dots$$

$$\beta = h \times (2^{\frac{1}{2}} + k)$$

j-even

$$c = h \times 2^{j/2}$$

$$\beta = h \times (2^{j/2} + k)$$

The above equations do not yield the complete spectrum for even k, but the complete spectrum may be obtained by choosing a new factor  $h'=2^{-g_x}h$ , where g equals the number of factors of two in k, not exceeding  $\frac{j-1}{2}$  for odd j or  $\frac{j}{2}$  for even j. These cases are not of great interest, for the numbers yielded do not represent cases of practical interest.

h is again chosen to be 1, yielding  $\alpha$ =4 and  $\beta$ =5. Actually the choice of h is determined by the operation time of the switches, and  $\alpha$  and  $\beta$  are very reasonable values. In addition to this  $\beta$ - $\alpha$ =1 could be used as additional storage space in the memory if switching required about the same length of time in either place, but the switching operation is more complex in the memory system than in the arithmetic unit so the additional time is useful.

The result of the choices yield an integrally synchronized memory system and arithmetic unit with an operating period of \$40×44=32×55=1,760 digit-times, so the magnetic drum must have space to store exactly 1,760 digits in each peripheral track. The two digit-time groupings, 44 and 55, will constitute a "minor arithmetic cycle" and a "minor memory cycle" respectively; and the total of 1,760 digit-times will constitute a "major memory cycle".

## 7. Component Requirements

The component requirements of "standard memory" and "short memory" were fairly well established from the first design feature, except that the number of words in a particular track in standard memory was not known, but has just been chosen to be equal to 32. This fixes the requirements of the spacing angle between the reading and writing heads of the short memory recirculators, for they must subtend the same angle as a word in standard

memory, or 2m/32 radians (55 digit-spaces). The requirements of the other units previously described ("order interpreter" and "time and track selectors") remain as stated, but will be enlarged upon in the following chapter.

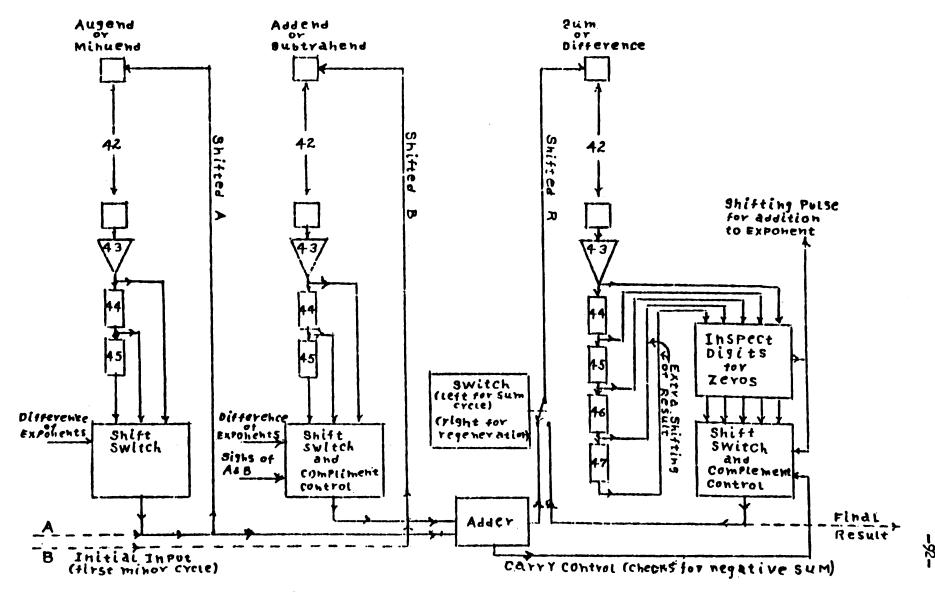

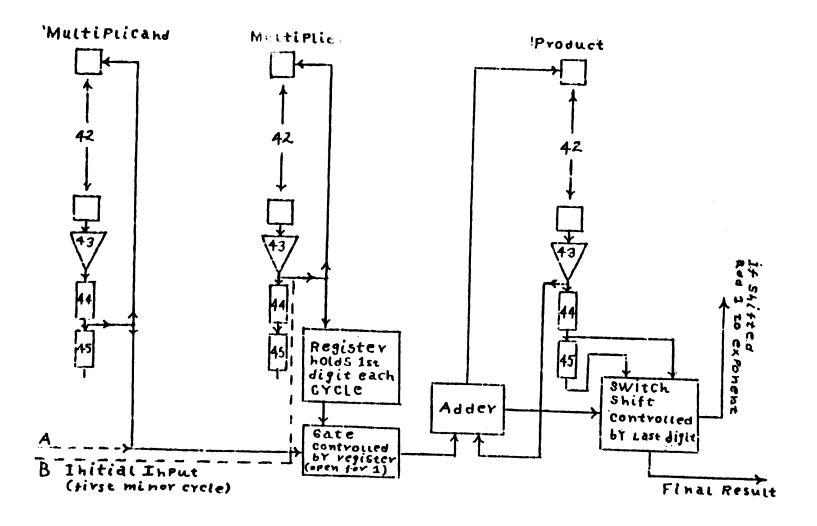

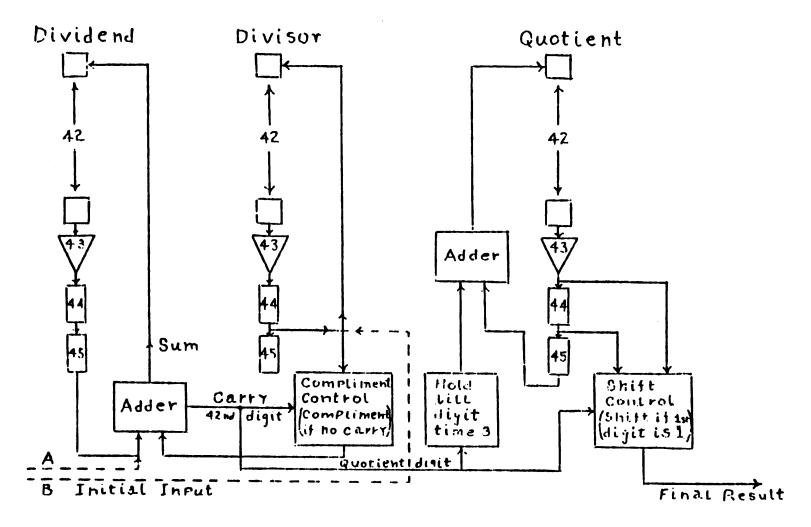

The second design feature fixes the requirements of the arithmetic and timing sections of the magnetic drum. The recirculators in the arithmetic unit must span an angle about the drum equal to that of hh digit-spaces, for these recirculators must store the hO significant digits of a number and also the h digits of "dead space" for switching operations must be included. Three such recirculators are required: two for the two operands which are read into the arithmetic unit at the beginning of the major memory cycle, and one for storage of the results at intermediate points in the arithmetic process (such as the sum of partial products at any point in the multiplication, the quotient digits generated at any point in division, the sum or difference in addition and subtraction).

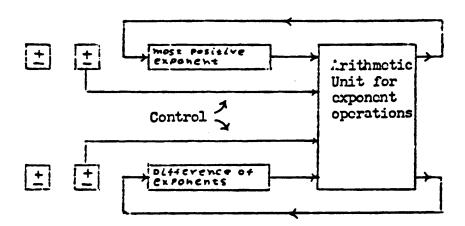

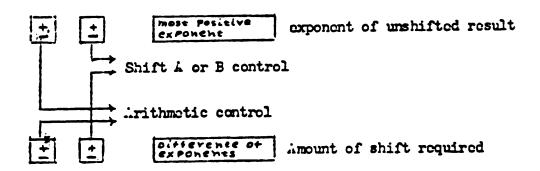

Since the arithmetic section of the drum stores only the significant digits of the numbers, the complete arithmetic unit must provide additional storage space and operational equipment for storing and adding the exponents. These exponents must also be used to provide control of the relative shift between addend and augend or minuend and subtrahend (this will be discussed in the next chapter).

Although it was just stated that the spacing of the recirculators in the arithmetic section should be 44 digit-spaces, actually a control of this spacing must be exerted, allowing values of 43-44-45 digit-spaces, for shifting the numbers to the right, none at all, or to the left of the binary point, respectively, one digit per minor arithmetic cycle.

The <u>timing</u> section of the drum is provided to synchronize the three other sections, supplying "markers" indicating the stage of the various

cycles to the corresponding units concerned. These markers must be of four kinds: (1) digit-time markers, which are required by all units to synchronize inter-storage communication; (2) minor memory cycle markers, which synchronize the standard and short memory systems and also the "time and track" selecting switches; (3) minor arithmetic cycle markers, which synchronize the operation of all the elements in the arithmetic unit; and (1) a major memory cycle marker, which signals the beginning of each operational step, including transfer of information between the arithmetic and short memory sections, transfer of newly located orders from the short memory unit to the "order interpreter", and a number of other applications.

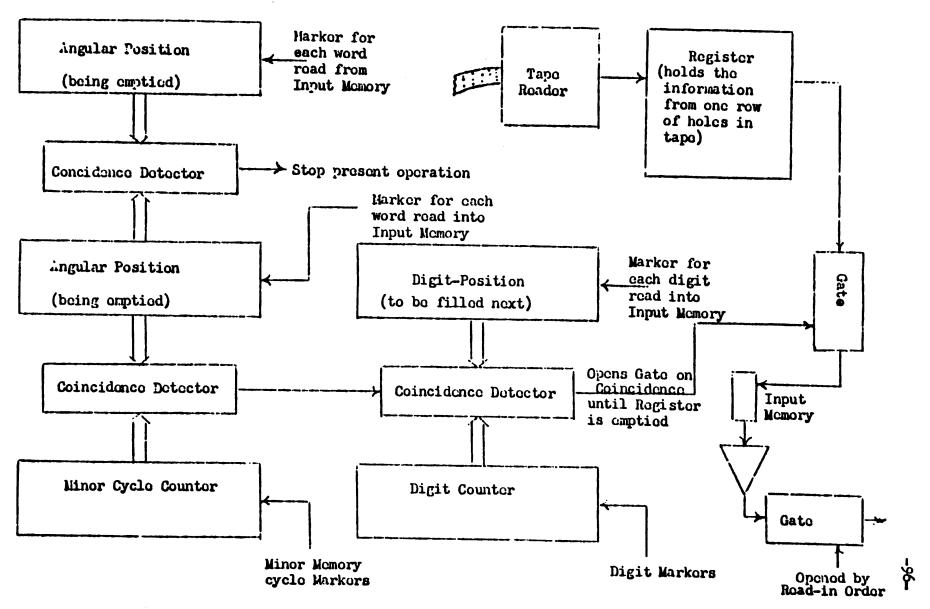

Although not properly introduced in this section, the "input" and "output" units must establish communication with standard memory, and will do so through two of the four short memory recirculators which are provided. To establish communication these units must also be properly synchronized with the short memory system, and will require digit, minor memory, and major memory markers from the timing section. These functions will be considered in the next chapter.

## 8. Modifications

#### a. Input and Output

It was stated in the first chapter that the two communication orders (Read-in and Read-out) have possibilities for expansion to include several input and output units. These additional units would be of use in supplying or producing tables of functions for the machine. They can be added without appreciable change in the original construction.

## b. Storage Capacity

So far no statements have been made about the storage capacity available in standard memory, except that each "track" in the system can store 32 words

and that a number of tracks may be used in parallel. The maximum number of tracks, N, is dependent on the order system, and N=32 is a maximum for the order system previously defined, since the number of digits available in an order for specifying addresses (storage locations) is limited. A change in the Extract order, involving the replacement of one of the original operands by the new word constructed, would allow N=512 as a maximum.

## c. Time and Track Selectors

In the component requirement subsection of the first design feature it was stated that four time and track selectors were required if it was desired to connect to storage locations which passed the reading and writing heads at the same time. An alternative to this would be to have two time and track selectors, one for reading and one for writing into standard memory. The single reading time and track selector could function for all three of the reading operations by providing an additional switch for connecting to any of the three short memory recirculators. The programmer would have to prepare the computations so that none of the three words being read from standard memory would appear during the same minor memory cycle. This would place a certain additional responsibility on the programmer, but the flexibility of the machine would not be appreciably impaired.

## d. Special Storage Locations

Before concluding this chapter it is of interest to point out a difficulty which is peculiar to the simultaneous performance of operational steps (refer to Table 1). If order N calls for either or both of its operands to be the result of the N-2nd order or the N-1st order, a dilemma exists, for these results have not yet been filed into standard memory, so are not available during the corresponding "locate operands" cycle. It will be noted, however, that the result of the N-2nd order is available during this time in

the "result" short memory recirculator, and will remain there until replaced during the first minor memory cycle of the next major memory cycle (the word not being destroyed when written into standard memory), which is the operation cycle for order N. Thus it is possible to just read this result from its short memory recirculator into the desired arithmetic section recirculator during that first minor memory cycle.

Similarly the result of the N-1st order is being generated in the arithmetic unit during the "locate operand" cycle of the Nth order, so it will be available to read back into the desired arithmetic section recirculator for the following operation cycle of order N.

The introduction of these two special "memory addresses" into the order system allows simpler programming procedures and more efficient use of the computing machine.

<sup>\*</sup> The availability of the result in short memory was first recognized by C. H. Davidson, University of Wisconsin.

#### CHAPTER III

# CHOICE OF COMPONENTS AND THEIR OPERATIONAL REQUIREMENTS

## 1. Introduction

In the design of the first model of the "integrally synchronized computer", which is to be built at the University of Wisconsin\*, it has been decided to incorporate components which would require a minimum of developmental research. The memory unit which appeared to most nearly satisfy the requirement was the magnetic drum, particularly because of the ease of synchronization between the three memory sections. Another advantage is that commercially available magnetic drums have digit-periodicities of very nearly the value required, i.e. their maximum storage capacity per "track" is about 15% in excess of the required 1,760 digits.

The ease of synchronization when utilizing the magnetic drum is a property of the system itself, for the complete memory system consists of a uniformly moving medium, and timing markers placed on this make the medium serve as its own "clock" independent of its speed (within the limits of the marker-sensing equipment utilized).

There is an additional advantage and a disadvantage is using a magnetic drum storage system. The advantage is that the information stored on the magnetic drum is non-volatile, allowing the computing machine to be shut down overnight even though the problem is unfinished; or, if a check shows an error has developed in the computer, it may be repaired and the problem may frequently be started from the point of the previous check rather than starting at the beginning. The disadvantage of the magnetic drum is that it is essentially a low speed device, presenting digits at a frequency of 100 kilocycles in comparison to the 1 megacycle frequency achieved in mercury delay lines. However, in a way this is advantageous for building the first model, for the

<sup>\*</sup> This model has been named "WISC", Wisconsin Integrally Synchronized Computer.

development of circuits for handling the lower frequencies is considerably easier.

## 2. Division of Drum

The division of the drum into sections according to function is shown in Figure 5. The five sections are: (a) Timing, (b) Standard Memory, (c) Short Memory, (d) Arithmetic Memory and (e) Input and Output. With the exception of section (e) these sections are identical to those required in Chapter II. The use of the Input and Output section will be discussed in the latter part of this chapter.

## a. Timing

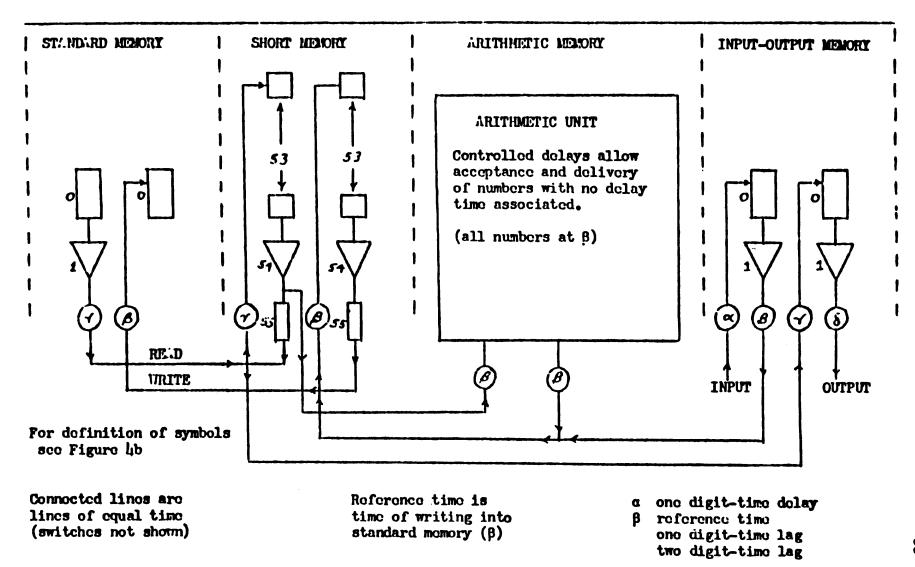

The Timing section will contain four reading heads, which will read the timing markers for digit-times (1760 per revolution), minor arithmetic cycles (40 per revolution), minor memory cycles (32 per revolution), and major memory cycles (1 per revolution).

To maintain precise synchronization throughout, without the use of precision equipment, all digits will be written onto the drum in coincidence with digit timing-markers; similarly the reading of digits from the drum will be done in coincidence with these timing-markers, but delayed an amount equal to the inherent delay of the system.

## b. Standard Memory

The Standard Memory section will contain 32 combination reading and writing heads, each serving to read or write information in a particular track around the drum. In each track there are spaces for storing 32 words, so the total storage provided totals 102h words. Connected to these 32 reading stations are three parallel track selection units, each of which can connect an amplifier to any of the 32 tracks. The outputs of these three amplifiers are the three words: (1) the next order, (2) and (3) the two operands called

for in the present order. Connected to the 32 writing stations in a single track selector which connects the "writing amplifier" to the desired track for recording new information on the drum. In general the new information will be the result of an arithmetical or extract operation, but the words supplied by the input mechanism will be recorded on the drum through this same channel. Similarly, the output of one of the three track selectors connected to the 32 reading stations will be supplied to the output mechanism for permanent external recording.

## c. Short Memory

The Short memory section consists of four tracks with reading and writing heads separated by 53 digit spaces (Refer to Figure 4). Three tracks store the new order and the two operands of the present order from the time of receipt from Standard Memory until they are required at their respective destinations. The fourth track stores the result of an operation from the time of receipt from the Arithmetic Unit until erased by the receipt of a new result one major cycle later, the result being available all during this cycle for duplication in the desired location in the Standard Memory. The new order will be transferred from the Short Memory storage track into the Order Interpreter (See Figure 6) during the last minor memory cycle of the major cycle in which it is read from Standard Memory. In the event that this new order is not located until this last minor memory cycle (at which time success of location is assured) the new order is read directly from Standard Memory into the Order Interpreter without requiring the intermediate storage. The two operands will be transferred from Short Memory into the Arithmetic Unit during the first minor memory cycle of the following major cycle; simultaneously, the result just obtained in the Arithmetic Unit is transferred into the fourth Short Memory track for filing into the required Standard Memory position sometime

during this major cycle.

## d. Arithmetic Memory

The Arithmetic Memory section consists of three tracks with reading and writing heads separated by 42 digit spaces. Two of these tracks will receive the two operands from Short Memory and the third will be used to store the result of the operation until delivered to Short Memory at the beginning of the next major cycle.

## e. Input and Output

The Input and Output section will consist of four tracks with combination reading and writing heads. Two of the tracks will be used to store information read from the Input mechanism, but which Standard Memory is not ready to receive. The other two tracks store information delivered by the Standard Memory, but which the Output mechanism is not ready to receive.

Since each track holds 32 words, a total of 64 words of intermediate storage is supplied for each purpose.

## 3. Supplementary Features

#### a. Recirculators

The magnetic drum is provided with a single inherent period, which is the time for one revolution, but two additional periods are required, short memory requiring 55 digit-times and arithmetic memory requiring blu. These additional periods can easily be produced by the feedback circuit in Figure 4. In such a circuit the information written onto the surface of the drum at the writing-head location is carried past the reading-head location a number of digit-times later. This information is now fed back to the reading-head, amplified, and supplied to external circuits and back to the writing-head again. In this fashion a number of digits, not exceeding the digit-time

delay between reading and writing heads, may be made available periodically. Such a system is termed a "recirculator", and recirculators having delay times of 53 and 42 digit-times will be used for the short and arithmetic memories, respectively. (The 53 and 42 digit-times rather than 55 and 44 will be explained when inherent and controlled delays are taken into account).

#### b. Delays

Before proceeding any farther, the question of inherent and controlled delays must be considered, for they are necessary to the operation of the Arithmetic Unit and to the synchronization of the machine. In the process of "writing" on the magnetic drum a pulse of current is used to set up an intense magnetic field at a spot on the surface of the drum (see Figure 5), permanently magnetizing it; this current pulse is triggered by a digit marker, so the current pulse reaches its maximum a short time later than the digit marker, an additional inherent delay is to be found in the amplifier. As a result of this delay it is difficult to use the output of the amplifier to directly recontrol the writing process, for the inherent delay is less than one digit-time. The simplest means for solving this problem is to increase the delay of the amplifier so that the total inherent delay becomes exactly equal to one digit-time; any additional delay that may also be desired is to be added in increments of one digit-time. The obvious difficulty that arises at this point is that the digit read from the drum is one digit-time later than when written, which still makes it impossible to control writing processes. The way out of this apparent dilemma is to run portions of the computing machine one digit-time behind the rest, with means for regaining the lost time in communication between these sections. The system of "time stabilization" proposed here is comparatively simple, and is shown in Figure 7. It will be noted that the regaining of the digit time is accomplished by means of recirculators.

#### c. Shifting Registers

In concluding the discussion of delay, it might simplify later discussion to state that the one-digit delay units which will most probably be used are special "flip-flop" units (units having two stable states of conduction) which take on the state of conduction determined by two input trigger pulses. One of these pulses is called a reset pulse, and the receipt of this pulse causes the "flip-flop" unit to take on the state of conduction designated as "zero". If the unit was in the "zero" state prior to the application of the reset pulse no change occurs, but if it was in the "one" state, a change in the state of conduction occurs. The change in state of conduction may be used to generate a trigger pulse similar to the reset pulse but later in time. The "change of state" trigger pulse is used as the second input trigger pulse to an adjacent "flip-flop" unit and causes this unit to take on the "one" state." Considering a chain of such "flip-flop" units having a given configuration of conduction states, the simultaneous application of reset pulses to all units causes each unit to take on the "zero" state. Those units which were previously in the "ond state generate "change of state" pulses which are applied to the following unit in each case, causing the following unit to take on the "one" state. In effect, then, the configuration of conduction states moves one unit down the chain each time the reset pulses are supplied. Such a chain is called a "shifting register", and converts a serial input of information into a static setting on the flip-flop units. In application in the wisconsin machine, the present plans are to attain the full one-digit inherent delay in reading by having such a flip-flop unit as the output stage of the amplifier.

One more point to be considered about the "flip-flop" units is that the units are to be symmetrical, so that the "zero" state and the "one" state

differ only in the respect that the potentials at two corresponding points in the circuit are reversed; this will be useful for obtaining complements of a number by "reading the opposite side" of the flip-flop units (the complement also requires the addition of 1 in the least significant position).

#### d. Assignment of Digits

In order to discuss the operation of the Order Interpreter the assignment of digits in the orders should be described. In Figure 8 a set of four diagrams are shown which picture in reasonable detail: (a) assignment of digits in a number, (b) general assignment of digits in an order, (c) detailed assignment of digits in an order, and (d) precedence of control information. There are a few items of information regarding the assignments which are of interest. In the numbers the arrangement of the digits are such that the loast significant of the digits in both the numerical and exponent groups are at the left; and appear first in time throughout the computer; in addition all numbers which are to be handled in the Arithmetic Unit will have a 1 in the 40th digit (most significant) space, with the exception of numbers for special purposes (i.e., which are to be added or subtracted only). In the orders the 40th digit is retained as a 1 for all but the extract order, this is provided so that addition of constants to the order addresses (locations in Standard Memory) for operations on sequences of numbers may be accomplished without modifying the Arithmetic Unit; similarly the exponent section is kept free in all but the extract order so that a single step is all that is needed for addition of constants to the order addresses. Keeping the exponent section free docs require dual assignment of digits in several cases and the significance of digits in these positions depend on the presence of other digits, as shown in the last diagram in Figure 8. More compact grouping of the order digits could be attained by using binary notation, but additional circuitry

would be required for this. The "Short Hemory" digit assignments are for specifying either of the operands to be results of the previous or second previous operations; only one such Short Memory assignment is available in the extract order, but this is sufficient to allow consecutive extract operations on a given word.

Sufficient information is now available to cover the operational requirements of the rest of the computer units. These units will be taken in the crder: (1) Order Interpreter, (2) Time and Track Selectors, (3) Arithmetic Unit (covering each operation required), and (1) Imput and Output Units.

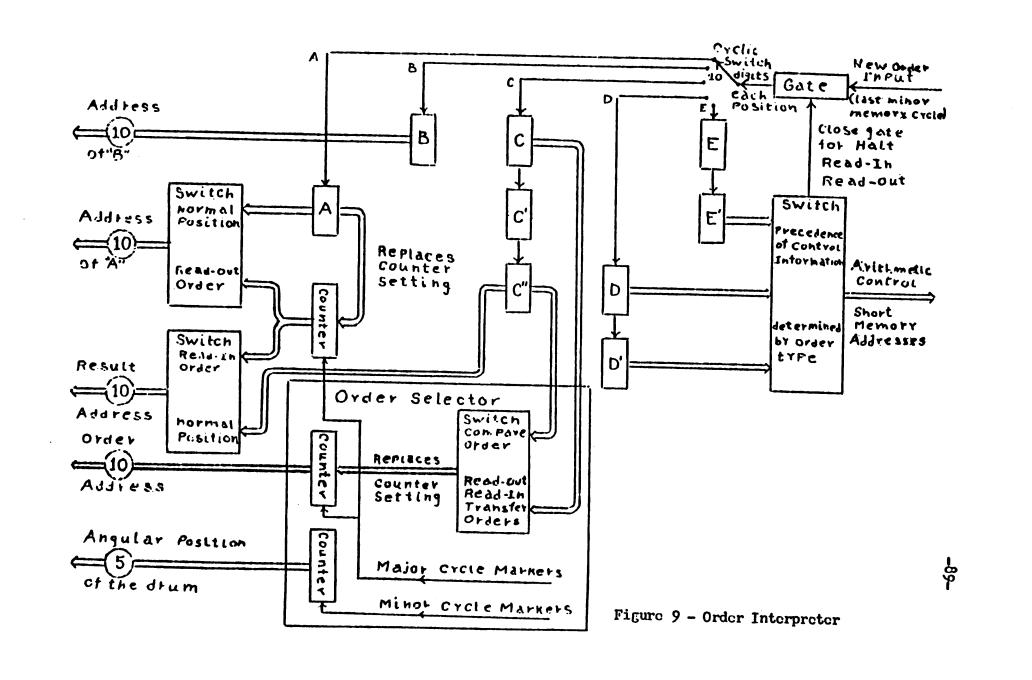

## 4. Order Interpreter

"shifting registers" which receive the new order in serial form from the new order Short Memory track, or from Standard Memory if located in the last minor memory cycle. This information transfer takes place during this last minor memory cycle and remains as static information on the shifting register for at least one major memory cycle. It should be noted that the information is divided into 5 parallel 10-digit groups (A, B, C, D, E), and that the (C) group consists of three series units (C, C', C"); also the (D) and (E) groups censist of two series units (D, D') and (E, E'). The number of units in series is determined by the number of major cycles during which the information must be kept available. The input to the 5 parallel groups governed by a cyclic switch, allowing 10 digits to be read into each.

#### a. The (A) and (B) Groups

The (A) and (B) units contain (for addition, subtraction, multiplication, division, comparison, and extract orders; A, S, M, D, C, & E) the locations in Standard Memory of the two operands called for in the order, and are required only during the following major memory cycle. In the case of the specification of a Short Memory address, any location may be specified in the (A) and (B)

section (zero being the simplest), and the word in this location will be located and placed in Short Memory, where its future will be governed by the Short Memory address specified in the order.

In the cases of the other four orders (Read-in, Read-out, Transfer, and Halt; I, O, T, / H) the (A) and (B) units contain information of a different nature. For I and O orders the (A) unit holds the address in Standard Memory into or out of which the first of a sequence of words will be transferred. This address will be increased by 1 each major memory cycle (except for a special case discussed in the Input and Output section), allowing the transfer of a new word every major cycle from Input to Standard Memory or Standard Frmory to Output. The (B) unit, for I and O orders, will hold the address up to which this process will continue. For T and H orders any information may be placed in the (A) and (B) units, but the words in these addresses will be located and sent to the Arithmetic Unit where some uncontrolled operation will be performed, however, the result of this operation will not be allowed to be written into Standard Memory.

#### b. The (C) Group

The three (C) units serve two purposes. In the A, S, E, D, and E orders, the (C) unit holds the address in Standard Memory into which the result of the operation will be written. The input to the (C) section causes the information in (C) to be shifted to (C') and that of (C') to be shifted to (C"); making the information in these units available for three major cycles. This is necessary, for the address into which the result of an operation is to be written cannot be used until this result is available for storage, which is during the third major memory cycle following the receipt of the order by the Order Interpreter. The second purpose served by the (C) unit is the storage of the address of the following order in the case of T, I, and O orders; the C order uses this position for storing the address of the following order under the condition that

the result of a subtraction is zero or negative, but the information as to the result of the subtraction is not available until the end of two major memory cycles, so this must be kept available for transfer into the Order Selector section until the result is known. In the T order this new address must be transferred immediately to the Order Selector, and in I and O order a similar transfer must be made, but the new order cannot be read until the completion of the I and O operations, which may take a large number of major cycles.

Returning to the C order and the operation of the Order Selector section of the Order Interpreter, it was stated that the address of the following order was to be found in the (C) unit in case of a zero or negative result of a subtraction. The function of the Order Selector is to supply the addresses of the orders to the Order 'Time and Track Selector', and it accomplishes this function by adding 1 to the previous order address every major memory cycle, thus providing orders from sequential storage locations; transfer from this sequence of orders is provided for by the C, T, I, and O orders and is accomplished by replacing the address in the Order Selector by the new address supplied in the order. Since the result of the subtraction in the C order is not known for two whole major memory cycles, the Order Selector will continue reading orders from the same sequence for the two following cycles; in the case of a positive result two of the desired operations have then already been started, and in the case of a zero or negative result the new order address is placed in the Order Science and the results of the two undesired orders are not allowed to be written into Standard Memory (they become available for writing after the result of the comparison isknown), and it is as though they had never been carried out. In addition to the above, the result of the subtraction in a Comparison order must not be written into Standard Hemory.

#### c. The (D) and (E) Groups

The (D) and (E) units of the Order Interpreter shifting register contain the information of the order type. The control digits in these sections determine the type of information contained in the (A), (B), and (C) units as well as in the (D) and (E) units and are not generally needed until the operands for the order have been located (except for T, I, O and H), which means they must be stored until the second major memory cycle during which they are used.

As shown in Figure 9, the statement that this is an Extract order (digit 40=0) causes a particular interpretation to all of the digits in the (D) and (E) sections. The statement that this is not an Extract order but is one of the arithmetic orders (A, S, M, D, C) (digit 40=1 and one of digits 31-35 are 1) causes a particular interpretation of the (T, I, O, H) group of digits (no interpretation is made of the (E) group in any but the Extract order, so they may be left blank or given values for special operations in the Arithmetic Unit). The statement that this is not an Extract or an arithmetic order (digit 1:0=1 and digits 31-35 are zero), allows the T, I, O, and N group to represent these four orders. The properly interpreted digits supply control voltages wherever needed throughout the computer, and are used generally for the setting of electronic switches.

# 5. Time and Track Scleetors