# the UNIVAC® 490 Real-Time System

# GENERAL DESCRIPTION

# UNIVAC 490 Real-Time System

# **Contents**

| 1. | UNIVAC 490 REAL-TIME SYSTEM                     |    |

|----|-------------------------------------------------|----|

|    | The Real-Time Concept                           | 1  |

|    | General Characteristics of the Real-Time System | 2  |

|    | High-Speed Communications Linkage               | 2  |

|    | Data Storage Facilities                         | 2  |

|    | Features and Applications                       | 2  |

|    | Processing Interrupt                            | 2  |

|    | Solid-State Design                              | 3  |

|    | Computer-to-Computer Configurations             | 3  |

|    | High-Speed Random Access Storage                | 3  |

|    | A "Time Conscious" System                       | 3  |

|    | Incremental Clock                               | 3  |

|    | Incremental Interrupt Clock                     | 3  |

|    | Day Clock                                       | 3  |

|    | High Internal Computing Speeds                  | 4  |

|    | Equipment Enclosure                             | 4  |

|    | Flexible Input-Output Facilities                | 4  |

|    | Automatic Programming                           | 4  |

|    | Floating-Point Arithmetic                       | 4  |

|    | Programming Checks                              | 4  |

|    | Special Programming Features                    | 5  |

|    | Powerful Instruction Repertoire                 | 5  |

|    | Absolute Efficiency                             | 5  |

|    | Library of Programmed Routines                  | 5  |

|    | Core Storage Search                             | 5  |

|    | Wired Memory                                    | 5  |

|    | Application Versatility                         | 6  |

| 2. | REAL-TIME COMPUTER                              |    |

|    | Storage Section                                 | 7  |

|    | Octal Notation                                  | 7  |

|    | Control Section                                 | 8  |

|    | Arithmetic Section                              | 8  |

|    | Arithmetic Registers (Operational Registers)    | 9  |

|    | Transient Registers                             | 10 |

|    | Operator Console                                | 11 |

|    | Computer Control Panel                          |    |

|    | Console Keyboard and Printer                    |    |

|    | Wired Memory                                    |    |

|    | **nea memory                                    | тT |

# 3. SYSTEM COMPONENTS AND CONFIGURATIONS

|          | Central Site Equipment                                | 12 |

|----------|-------------------------------------------------------|----|

|          | Peripheral Units                                      | 12 |

|          | Peripheral Systems                                    | 12 |

|          | Magnetic Drum Storage                                 | 14 |

|          | Magnetic Tape Storage                                 | 15 |

|          | High-Speed Card Reader                                | 16 |

|          | Punch-Verifier Unit                                   | 16 |

|          | High-Speed Printer                                    | 17 |

|          | Transmission and Communications                       | 18 |

|          | Input-Output Channels                                 | 18 |

|          | Data Transfers                                        | 18 |

|          | Buffer Mode                                           | 18 |

|          | Input-Output Control                                  | 18 |

|          | External Equipment Requirements                       | 19 |

|          | Remote Input-Output Devices                           | 19 |

|          | Keyboard Printer                                      | 19 |

|          | Uniset Console                                        | 20 |

|          | The Uniset                                            | 21 |

|          | Format Control Panel                                  | 21 |

|          | Communications Equipment                              | 21 |

|          | Communications Systems                                | 23 |

|          | Party Line Network                                    | 23 |

|          | Scanner - Selector                                    | 23 |

|          | Party Line Communications System                      | 23 |

|          | Transfer Function                                     | 24 |

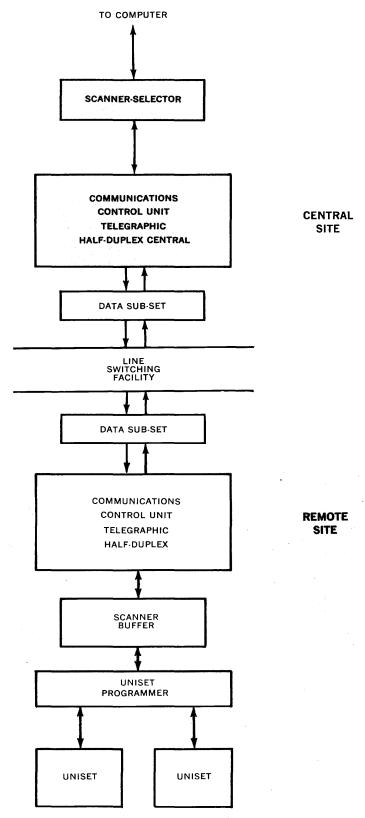

|          | Line Switching Network (Direct Distance Dialing)      | 24 |

|          | Communications Control Unit (Telegraphic Half-Duplex) | 24 |

|          | Communications Equipment for Special Devices          | 26 |

| <b>.</b> | INSTRUCTIONS                                          |    |

|          | Instruction Word                                      | 27 |

|          | Instruction Cycle                                     | 27 |

|          | Instruction Repertoire                                | 28 |

|          | Shift Instructions                                    | 28 |

|          | Simple Read Instructions                              | 29 |

|          | Store Instructions                                    | 29 |

|          | Arithmetic Read Instructions                          | 30 |

|          | Comparison Instructions                               | 30 |

|          | Selective Instructions                                | 31 |

|          | Replace Instructions                                  | 31 |

|          | Jump Instructions                                     | 32 |

|          | Special Program - Modifying Instructions              | 33 |

just as feedback is used by a computer to control a missile's path...

... up-to-the-minute data from

a UNIVAC Real-Time System can help influence the course of business curves.

# 1. UNIVAC 490 Real-Time System

The UNIVAC 490 Real-Time System is a large-scale, general purpose digital computing system specifically designed for the dynamic organization which has diverse operations demanding stricter control based on real-time computing. This new system extends valuable techniques of real-time processing, long restricted to a limited number of special military applications such as missile guidance, to the broader field of commercial problems.

Remington Rand's installation of UNIVAC Airlines Reservation Systems at several major airlines demonstrated the power of real-time processing. A centrally located UNIVAC File-Computer provides flight information in a fraction of a second to ticket offices scattered throughout the country. The well-documented success of the Airline Reservations System proved the potential of real-time processing and served as the incentive for its full development.

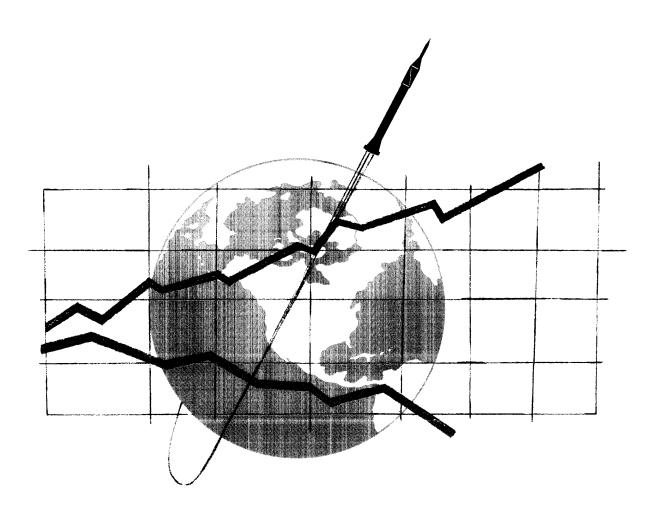

Now, with the Real-Time System, the full commercial potential of real-time processing can become an integral part of your business, bringing with it an efficiency and control only approximated by other devices. In fact, just as feedback is used by a computer to control a missile's path and counteract disrupting forces, up-to-the-minute data from a real-time system can help an organization influence the course of a number of its business curves as they are formed.

# THE REAL-TIME CONCEPT

The real-time concept is the fulfillment of management's desire for a method of re-

versing the direction of a business curve before it gains momentum and attains black-and-white finality. Up-to-the-minute indications of business activity enable the real-time user to detect the suggestion of a downturn and correct it immediately, in much the same way as a guided missile's course is adjusted as it hurtles to its target. If, for example, sales have dipped slightly, the Real-Time Computer will allow management to discover this fact immediately, instead of waiting for quarterly reports. As a result, management's remedial actions are effectively timed. And it is the timely decision which has the greatest significance in the intensified competition of business and industry today. To assure timeliness in organizational activities, it is necessary to utilize a real-time processing system, with its ability to communicate with many remote locations and its large storage facilities, to reflect sales, profits, costs, production, and other pertinent data.

Thus, the real-time concept is a significant advance in data-processing, a field which heretofore employed batch processing only. That is, master data, or information which is altered infrequently or in a known manner, was updated at intervals, upon the accumulation of enough transaction data, or information characterized by essentially random and unpredictable incidence. Realtime processing, however, eliminates the lag between the occurrence of transactions and their postings to a master file. By updating the master file immediately upon receipt of a new transaction from a remote source, the Real-Time System can present a truly current report of the status of any application—a feat impossible for the batchprocessing computer with its externally stored master data.

# GENERAL CHARACTERISTICS OF THE REAL-TIME SYSTEM

The specific design and function of the remote input-output units of the UNIVAC 490 Real-Time System are dictated by the nature of the individual application. In general, however, input units are able to accept transaction data with speed and reliability while the output units display results with accuracy and clarity. The computing unit of the system is general purpose, and therefore, ideal for all types of applications.

#### **High-Speed Communications Linkage**

Common carriers, such as American Telephone and Telegraph, Western Union, American Cable and Radio, afford high-speed communication facilities for two-way transmission of data between the central site Computer and the remote input-output units. Transactions originating at remote points are conveyed along these wires directly to the Computer where they are immediately evaluated and processed. Then the result is returned to the originator and other appropriate distant points, the whole transaction being accomplished in seconds.

#### **Data Storage Facilities**

Since the UNIVAC 490 Real-Time System applies transaction data to the master file information as the transaction data occurs, the system employs extensive data-storage facilities which are capable of storing entire master files of information. In addition, these facilities are of the random access type allowing immediate access to master file information.

#### **FEATURES AND APPLICATIONS**

In addition to existing applications best performed by this system, there is a growing number of vital data-processing problems that depend on this type of automation—the UNIVAC 490 Real-Time System—for their effective solution.

The many outstanding features of the UNIVAC 490 Real-Time System are particularly suited to applications in which processing timeliness is vitally important, perishability is a factor, or decision-making is based on data originating simultaneously at separate, remote points. Some of these features, such as solid-state components and microsecond internal computing speeds, represent the latest design advances in the electronic computer field. Other features of the system, such as the ability to communicate with remote locations and to perform both real-time and batch-processing applications, are entirely new developments.

Some of the major features of the UNIVAC 490 Real-Time System are described briefly in the following paragraphs.

#### **Processing Interrupt**

An outstanding feature of the UNIVAC 490 Real-Time System is its capacity to process real-time and batch-processing applications concurrently. This impressive data-processing innovation is made possible through a unique feature that permits remote external units to interrupt Computer processing with information of high precedence.

With this feature the maximum processing potential of the system is realized. For example, when once the master data for a particular real-time application is recorded in storage, the Computer can be used to process a "batch" application. Then, whenever transaction data for the real-time problem is entered into a remote external unit, the Computer's batch-processing is interrupted to permit handling the high priority real-time transaction and sending the processed results to the external unit.

Upon completion of the real-time processing, the Computer automatically returns to the batch application. Further, if the real-time information handled during the interrupt bears on the interrupted application, the latter can be updated by the real-time data, thereby assuring that all subsequent processing is up to date.

#### Solid-State Design

The solid-state components and circuitry of the UNIVAC 490 Real-Time System offer numerous advantages including standardized production of components and the reduction of maintenance procedures to a few relatively simple operations. In addition to ease of production and maintenance, solid-state circuits also impart a high degree of operating reliability to the Computer while reducing the power, cooling, and space requirements of the system.

#### **Computer-to-Computer Configurations**

The UNIVAC 490 Real-Time System's ability to coordinate, through communication networks, the activities of several Computers located at various points, allows the user to increase his data-processing system to meet any sudden business expansion.

#### **High-Speed Random Access Storage**

To meet the extremely demanding requirements of real-time processing, the UNIVAC 490 Real-Time System is equipped with data-storage facilities (drums, tapes) that are more expansive and versatile than those of most present-day computing systems. The Computer has an internal core memory with a capacity of 32,768 or 16,384 30-bit words.

#### A "Time Conscious" System

Processing timeliness, an inherent characteristic of real-time processing, requires the system to be extremely "time conscious." Three precision electronic chronometers provide the system with a timing sensitivity unmatched by other computing systems.

#### **Incremental Clock**

This built-in clock is used for a wide variety of program-timing purposes. It can be used to log the receipt times of aperiodic real-time input data. Each input message and its receipt time may be recorded together. This clock is also used in connection with the preparation of statistical and analytical reports dealing with the frequency of certain transactions.

#### Incremental-Interrupt Clock

This "program-set" clock counts up to 32,768 milliseconds. Upon reaching its upper limit, the Incremental-Interrupt Clock unconditionally interrupts the Computer at the end of the instruction being handled, regardless of the type of instruction. The clock count is maintained in core storage. The Incremental-Interrupt Clock is vital to the functioning of a real-time system because one of the primary uses of this clock is timing subroutine operations. If a momentary fault arising from improper programming throws the Computer into a closed loop, or if a fault occurring during the execution of an instruction halts the Computer, the Incremental-Interrupt Clock restarts the Computer by means of an interrupt, thus providing automatic fault recovery. The interrupt can be used to notify maintenance personnel that a closed loop has occurred. If completing an operation takes longer than desired, this clock is also used to interrupt the Computer and thereby allow program attention to be directed to items of more immediate importance.

# **Day Clock**

A feature particularly suited to real-time problems is the 24-hour Day Clock. As an auxiliary device, this electronic clock causes an external interrupt of Computer processing once every minute. Thus, "keeping time" is placed completely under the programmer's direction.

Since program control is shifted once every minute to a set address in the Computer, the Day Clock can be used to initiate a variety of subroutines. For example, by using a compare routine on the address reserved for timing purposes, reports can be generated at any desired time of the day, week or month. These reports could provide up-to-the-minute information and analyses of company status. Error-checking routines, trace routines, output conversions, management report programs, maintenance routines, and memory dumps are some of the many routines which can be initiated by the Day Clock.

#### **High-Internal Computing Speeds**

Along with its high-speed random access storage facilities, which allow a high data-transmission rate between the Computer and peripheral units, the UNIVAC 490 Real-Time System also features instruction execution times measured in microseconds. Instruction access and execution time totals 12 microseconds for most instructions.

#### **Equipment Enclosure**

The physical arrangement of the Computer, its peripheral units, and the operator's control panel demonstrate the UNIVAC 490 Real-Time System's revolutionary equipment enclosure concept. This modern equipment installation technique affords the operator an unrestricted view of all significant indicators and displays. It also positions the peripheral units within easy reach to allow the operator to attend to them when necessary.

Maintenance personnel, located outside the operator's enclosure, have unrestricted access to all equipment even though it is in operation. Any element of the system may be monitored for maintenance without interfering with operating personnel.

In terms of economy of installation, the equipment enclosure design concept presents the additional advantages of greatly reducing floor-space requirements and eliminating the need for expensive false floors.

#### Flexible Input-Output Facilities

The UNIVAC 490 Real-Time System can communicate directly with a wide variety of commercially available input-output units and custom-designed data-originating devices. The system's Computer is also capable of communicating directly with other computers. The inherent flexibility of the system's input-output channels enables the UNIVAC 490 Real-Time Computer to perform this diversity of input-output data communicating functions.

A large number of system input-output channels are employed for communications between the Computer and peripheral site units such as high-speed printers, mass-storage units, card readers, and tape-handling units. These same channels can be used to accommodate an almost unlimited number of remote data-originating devices by using a special input-output buffer mode. Two input-output channels are utilized for communications between the UNIVAC 490 Real-Time Computer and other computers.

#### **Automatic Programming**

The system features a very flexible compiling system which allows mnemonic expression of computer-oriented instructions. Instructions and addresses to which they refer can be given alpha-numeric names. Program check-out can be accomplished with special aids which include post mortem and register dumping routines. A subroutine mechanism facilities compilation of subroutines into a final program. The compiling system also has a high-level, problem-oriented language in which computer programs are written. This compiler interprets general statements and automatically generates the necessary machine instructions which perform the stated function.

#### Floating-Point Arithmetic

The UNIVAC 490 Real-Time Computer floating-point format is based on a two-program-word information unit, one mantissa and one characteristic word. The length of the mantissa is 28 bits, and the length of the characteristic is 15 bits, including a sign. It is a three-address system in which four index-registers are used to designate the operand and the function codes. As a complete software system, it includes input-output conversion and function evaluation.

# **Programming Checks**

An important characteristic of the UNIVAC 490 Real-Time System is operat-

ing reliability, a mandatory requirement of a system designed for real-time processing. Although the system's reliability is achieved through solid-state components, a number of program checks and error-detection procedures also contribute to the system's highly reliable performance. The system features a routine for automatic restarting after an error is detected and corrected. Because transaction data in real-time applications is usually independent and unrelated to previously entered information, the system provides a routine that preserves the transaction data being processed should an error occur.

#### SPECIAL PROGRAMMING FEATURES

Special programming features enable the UNIVAC 490 Real-Time System to process virtually any type of commercial or scientific data-processing application. In addition to latest engineering advances incorporated into the logic of the system, a host of special software programming features associated with the system allows the user to cut programming costs to a minimum.

# **Powerful Instruction Repertoire**

The sixty-two function code values in the instruction repertoire can be modified by the system to provide unlimited programming versatility. Much of the real programming power of the computer lies in the unique format of the instruction word. Of the thirty bit positions in the instruction word, nine serve as special purpose designators. When these designators are used in combination with the function codes, the computer can perform more than 25,000 basic programming operations.

#### **Absolute Efficiency**

Execution of a stored program of instructions on the Real-Time Computer proceeds in a series of steps. Very often, however, the unique requirements of real-time problems necessitate programming a large number of jump and skip operations. The prevalence of these operations arises because the processing activities of a real-time com-

puter involve serving a large number of remote peripheral units that are constantly demanding computer attention on an immediate or near-immediate basis.

Since skip and jump programming operations are inherent in real-time processing, the internal logic of the UNIVAC 490 Real-Time Computer causes these operations to be handled in a manner approaching absolute efficiency. For example, because the next instruction is in "review" while the current instruction is being executed, a skip instruction brings the computer—at no loss of time—directly to the resumption point without leafing through intervening instructions. Jump instructions are processed by the computer with similar efficiency.

#### **Library of Programmed Routines**

A major problem often encountered in the installation of a new type of computing system is the large amount of programming required to put the system in operation. Because the UNIVAC 490 Real-Time System evolved from prototype systems which are now performing successfully at commercial, government, and military installations, an extensive library of proven programming routines, including compiler and assembly systems, is available to the user immediately.

#### Core Storage Search

From a programming standpoint, a very desirable and practical provision of the UNIVAC 490 Real-Time System is the feature which allows the entire core storage, or selected portions of it, to be searched automatically and rapidly. Programming the search operation requires the use of only two instructions.

# **Wired Memory**

A permanent memory is built into the Computer for program input and automatic error recovery. It consists of sixteen 30-bit words of storage, and is wired to fit the specialized needs of the Computer user. This storage may be accessed by a program, but can only be changed manually.

#### **Application Versatility**

Designed primarily for real-time applications, this system can effectively handle numerous commercial and scientific batch-processing applications. Yet it is the real-time function of the system that brings a significant new dimension to electronic data-processing—fingertip access to a powerful computer from many remote points.

The ability to consult vast quantities of updated files in a random manner with immediate program response makes this system ideal whenever an application hinges on exacting time requirements. Thus, whenever time is of great importance as it is where perishability is involved or where customer service must be rapid or where

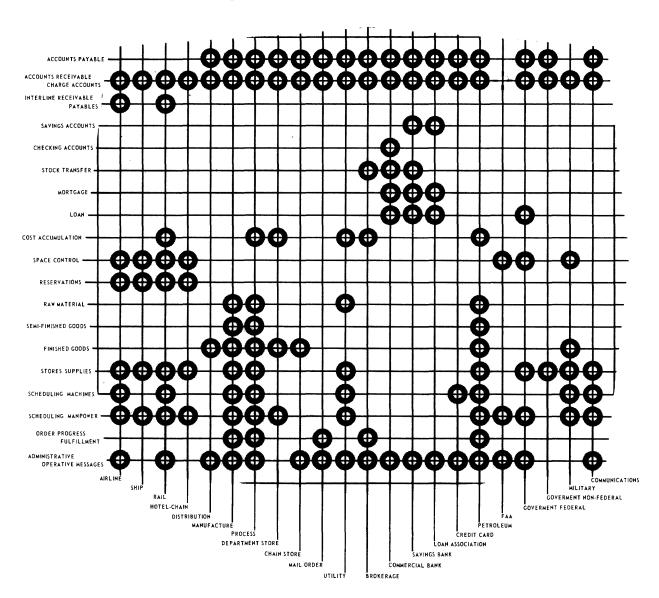

information from several sources must be interrelated for subsequent operations, the UNIVAC 490 Real-Time System can handle the application more effectively than any other system. For example, if a warehouse can make known the availability and quantity of its perishable goods, the points of sale can order their full requirements. In the area of production, to cite another example, work-in-process control can be carefully followed and interim cost figures developed to determine the desirability of alternate methods of production, as well as optimum manufacturing quantities. The UNIVAC 490 Real-Time System, then, has been conceived for use on an unlimited variety of applications. Figure 1–1 shows some real-time data-processing areas listed by industry and application.

Figure 1-1. Real-Time Data-Processing Applications

# 2. Real-Time Computer

The Computer in the UNIVAC 490 Real-Time System is a stored program computer designed for processing large quantities of data on a real-time basis. The Computer has large internal magnetic core storage, great programming flexibility, and a versatile input-output section.

The Computer forms the heart of any UNIVAC 490 Real-Time System. Its solid-state arithmetic and logical circuitry perform tens of thousands of processing operations every second, in both batch-processing and real-time modes.

Some outstanding features of the Real-Time Computer are listed below:

- Access time to all core storage locations of 1.9 microseconds; ability to store and to select information randomly

- 30-bit word length with a 15-bit half-word option

- Repertoire of 62 basic instructions which can be modified to produce over 25,000 different instructions

- Single address instructions with provision for address modification

- Multiple program capabilities

- Ability to perform rapid data exchanges with external equipment without main program attention

- Real-time clock for automatically initiating various

Computer operations at predetermined times

- Parallel one's complement binary notation

#### STORAGE SECTION

Internal storage of the Computer consists of banks of ferrite cores. Thousands of these cores can be mounted within a square printed-circuit frame. Each core is capable of assuming either of two stable magnetic states: one represents binary zero; the other, binary one.

At the option of the user, magnetic core storage is available in banks of 16,384 or 32,768 computer words. Access to information in core storage is random since it is independent of the address selected. Words can be inserted into or removed from any address in core storage at a rate of six microseconds per word. Figure 2–1 shows the basic internal data word.

#### **Octal Notation**

Although the UNIVAC 490 Real-Time Computer is a binary computer, the problem of converting large decimal numbers into binary notation sometimes becomes cumbersome. For this reason, binary notation is expressed in what is known as octal form. The conversion from binary to octal notation simply involves dividing the binary digits into consecutive sets of three from right to left, and then reading these sets in decimal. For example, a full core storage system requires the use of 32,768 storage addresses. Representation of the upper limit storage address in binary nota-

Figure 2-1. Basic Internal Data Word

tion requires the use of 15 bits. This same decimal number, however, can be represented by five octal digits.

| Decimal |     | 32,767 |     |     |     |  |  |

|---------|-----|--------|-----|-----|-----|--|--|

| Binary  | 111 | 111    | 111 | 111 | 111 |  |  |

| Octal   | 7   | 7      | 7   | 7   | 7   |  |  |

It should be noted that the working digits in the octal system are 0 through 7. The word octal means eight; therefore, when counting in octal notation, the number after seven is ten. In the Real-Time Computer, the function code values, the operand address, and the operand itself (when the 15-bit option is used) are expressed in octal notation.

#### **CONTROL SECTION**

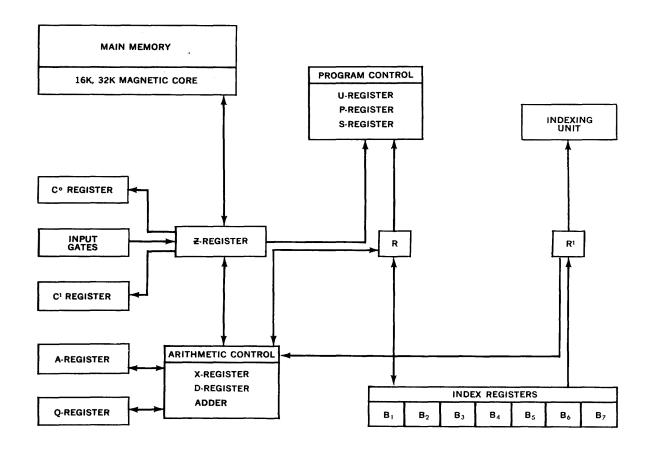

In addition to the magnetic core storage section, the Computer has two other sections, arithmetic and control (Figure 2-2). The control section is responsible for the operations that take place during the sequential execution of instructions. It also coordinates the flow of data between the arithmetic and storage sections.

#### ARITHMETIC SECTION

The arithmetic section is composed of the circuits and registers used to perform arithmetic and logical operations. These operations are performed in a parallel bi-

Figure 2-2. Simplified Logical Diagram of the UNIVAC Real-Time Computer

nary mode. The arithmetic mode is one's complement subtractive.

The high internal computing speeds of the Computer allow arithmetic operations to be carried out at microsecond speeds. For example, additions and subtractions are performed in a maximum of 12 microseconds. The ability of the computer to perform arithmetic operations simultaneously with input-output data transfers makes it ideally suited to the processing of real-time problems.

The UNIVAC 490 Real-Time Computer contains a number of registers which holds data during computation. These registers are designated by a letter or letter-numeral combination, and they are interconnected by parallel transmission paths through which information flows during processing.

They fall into two categories: operational and transient. Operational registers contain information from one instruction to another and are referred to in the operational description of each instruction. Transient registers, on the other hand, are temporary storage locations that are always cleared at the end of an instruction.

#### **Arithmetic Registers (Operational Registers)**

# A-Register

The A-Register or Accumulator is the principal 30-bit arithmetic register. It has adding and shifting properties. In most arithmetic operations, the result is retained in register A for use in later program steps. For example, after addition or subtraction, the sum or difference remains in the accumulator; after multiplication the most significant half of the product is gathered in the accumulator; after division, the remainder is left there.

The contents of register A may be shifted right or left, as described in the instruction repertoire. Left shifts are circular or cyclic, and in a right shift the sign bit is extended by the number of bit positions shifted and the lower order digits are discarded.

# Q-Register

The Q-Register is a 30-bit auxiliary arithmetic register. Its principal function is to assist the A-Register in multiply, divide, and logical operations. Register Q has shifting and logical properties, and performs adding or counting functions as well.

The contents of the Q-Register may be shifted right or left, in the same manner as the contents of the A-Register. As shown in Figure 2–2 all communication with the Q-Register is through the X-Register. Logical multiplication is performed on a transmission path between the Q- and X-Registers.

# A- and Q-Registers In Combination

Certain instructions shift the contents of the A- and Q-Registers as a single 60-bit register, with the A-Register representing the most significant half of the double-length quantity. To illustrate, the Q-Register holds the multiplier at the beginning of a multiply operation. As the product is formed, by repeated additions and shifts, the multiplier digits are shifted to the right and discarded. In their place, the lower order digits of the double-length product are shifted into the Q-Register from the accumulator.

During a divide operation, a process essentially the reverse of multiplication takes place. The double-length dividend is shifted to the left, and the quotient bits are inserted in the rightmost position of the Q-Register. At the end of the divide sequence, the quotient is assembled in the Q-Register, and the remainder is left in the accumulator.

# P-Register

The P-Register (15-bits) is the Program Address Counter. This register holds the address of the next sequential instruction throughout the program. As each program address is transferred from the P-Register to the S-Register, the contents of the P-Register are increased by one. When Jump instructions are executed, the P-Register is cleared and a new program address is entered.

# B-Register

The B-Registers (15-bits each) are Address-Modifying Registers generally used for indexing minor loops in a program. The contents of one register may be used to increment the operand address before execution of an instruction. Seven such registers are provided and labeled B¹ through B³. The B³ register also serves as a counter in the repeat mode where a selected instruction is executed the number of times specified (covered later in instruction 70).

#### **Transient Registers**

The following registers are used in the manipulation of instruction words and data words during the execution of an instruction. These registers are not referenced in the description of the instructions and do not retain information from one operation to the next.

# X-Register

The X-Register (30-bits) functions as an arithmetic communication register. It has complementing, but not shifting, properties. The X-Register receives the operand from storage during all arithmetic operations. All communication between the A-and Q-Registers and the rest of the operational registers or the adder output is via the X-Register.

# K-Register

The K-Register (6-bits) functions as a shift counter for all arithmetic operations involving shifts. The maximum shift count permitted is 60. Multiply and divide operations are controlled by presetting the K-Register to 30. The K-Register then counts the operational steps.

# S-Register

The S-Register (15-bits) holds the storage address during memory references. At the beginning of a storage access period, the address is transferred to the S-Register. The contents of the S-Register are then translated to activate the storage selection system.

# Z-Register

The Z-Register (30-bits) serves as an Operand Buffer for storage references. During the read portion of the storage access period, the Z-Register is cleared. The digit-reading amplifiers are then sampled to set the contents of Z corresponding to bits in the storage. During the write portion of the storage access period, the Z-Register controls the inhibit circuits in order to write or restore the disturbed storage register. Input data is gated directly to the Z-Register.

# U-Register

The U-Register (30-bits) is the Program Control Register. In other words, it holds the instruction word during the execution of an operation. The operation code and the various execution modifiers are translated from appropriate sections of this register. If an address modification is required before execution, the contents of the appropriate B-Register are added to the contents of the low order 15-bits of the U-Register.

# R-Register

The R-Register (15-bits) functions as a communications register for all internal transmissions to the B-Registers.

# $R^{1}$ -Register

The R¹-Register (15-bits) functions as a communication register for all internal transmission from the B-Registers. It holds the incrementing quantity during address modification.

# D-Register

The D-Register (30-bits) is the Arithmetic Register which holds the operand, for presentation to the adder, during the execution of arithmetic operations.

# C-Register

The C-Registers are communication buffer registers through which computer output data are synchronized. There are two C-Registers, C<sup>0</sup> and C<sup>1</sup>. C<sup>0</sup> is used to com-

municate output data to peripheral devices on 12 different channels. C<sup>1</sup> is used to communicate output data on two different channels to other computers. Input data is gated directly to the Z-Register.

#### **OPERATOR CONSOLE**

The UNIVAC 490 Real-Time Computer is equipped with a console that includes controls that allow varied manually governed operations including special modes, Incremental Clock Interrupt Disable Switch, Programmed Jump Switches, and the Wired Memory Switch.

The two-way Wired Memory Switch, located on the operator console, is marked "start" and "neutral."

#### **Computer Control Panel**

# Registers found on the maintenance panel include the following:

| 1. | C₀-REGISTER              | 8.  | B₄-REGISTER              |

|----|--------------------------|-----|--------------------------|

| 2. | C <sub>1</sub> -REGISTER | 9.  | B <sub>5</sub> -REGISTER |

| 3. | Q-REGISTER               | 10. | B <sub>6</sub> -REGISTER |

| 4. | A-REGISTER               | 11. | B <sub>7</sub> -REGISTER |

| 5. | B <sub>1</sub> -REGISTER | 12. | U-REGISTER               |

| 6. | B₂-REGISTER              | 13. | S-REGISTER               |

| 7. | B₃-REGISTER              | 14. | P-REGISTER               |

|    |                          |     |                          |

# Manual controls are provided on the Computer Control Panel which allow:

- The execution of consecutive program steps at a low rate.

- 2. The execution of one consecutive Computer clock phase (¼ of a cycle) for each depression of a switch.

- 3. The execution of one consecutive program step for each depression of a switch.

- Operation that is normal except that the Computer does not stop when it executes a programmed stop instruction.

- 5. The Day Clock to be disconnected.

- 6. The Increment Clock to be disconnected.

- The automatic recovery feature to be disconnected.

Because of their use in programming operations, some of the indicators and manual controls listed above are duplicated on the operator's console.

#### Console Keyboard and Printer

Located at the Computer Console, the Console Keyboard will normally be usable: during program debugging, while making changes to programs, schedules, or tables;

when initiating type-outs of interest to the operators or UNIVAC Center supervisory personnel; and in controlling the system. There are no restrictions as to the size of the units of information entered by this device, or of the type-outs, so long as computer formats are used and program provision is made.

#### Wired Memory

As mentioned earlier the purpose of the wired memory is to provide automatic reading of new programs into the Computer with protection against erasing vital instructions in the wired memory. The wired addresses parallel the first 16 core storage addresses (00–17, octal). Whether the Computer operates with words in wired or core, depends on the position of the 3-way Wired Memory Switch on the Computer Control Panel and the two-way switch on the Operator Console.

#### The positions of this switch are:

- 1. Automatic Recovery

- 2, Neutral

- 3. Bootstrap

When the Computer is on and the Wired Memory Switch is turned to Bootstrap, the Computer starts the wired program in the wired memory at address 00. During the normal operation of the Computer, any reference to the address between 00 and 17 (octal) refers to the address in the wired memory.

When the switch is in Automatic Recovery, and a fault interrupt occurs, the Computer will perform the program as wired in the Wired Memory starting at address 14. A fault interrupt is caused when an Incremental Clock Interrupt or millisecond timeout or an illegal function (00 or 77) occurs. A millisecond time-out occurs when, for some reason, the Incremental Clock was not updated. All other references to addresses between 00 and 17 (octal) refer to words in core storage.

When the switch is in Neutral, the Computer ignores the wired memory and uses address 00 through 17 (octal) in core storage.

# 3. System Components and Configurations

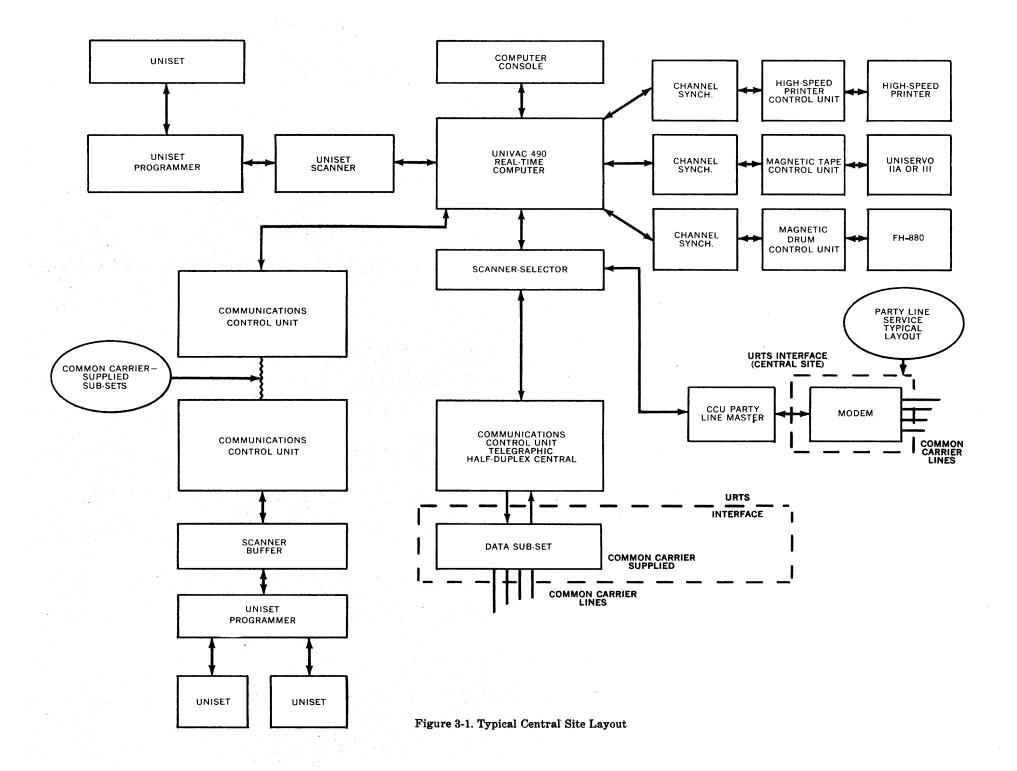

The individual components which combine to form a particular UNIVAC Real-Time System configuration vary in number and type according to the application. Each component of a UNIVAC Real-Time System, however, falls into one of the following categories:

- 1. Remote Inquiry-Answering Devices

- 2. Communications Equipment

- 3. Central Site Equipment

Remote inquiry-answering devices situated at many different locations have access to the Computer and other central site equipment through communications equipment. Conversely, the same communications equipment provides the central site units with access to the remote units.

The communications equipment is divided between the remote inquiry-answering devices and the central site equipment. In actual operation, input information is entered at a remote inquiry-answering device which activates communications equipment at the same location. The information is transmitted via communications lines to communications equipment at the central site where it is fed into the Computer for processing. Output information emanating from the Computer is fed through the communications equipment to the proper inquiry-answering device at a remote location.

# **CENTRAL SITE EQUIPMENT**

Central site equipment used with a UNIVAC Real-Time System includes a

Real-Time Computer, various peripheral units such as card readers, storage units, and magnetic tape units, and communications equipment. Using master data maintained at the central site, the Computer and its peripheral units process all information received from input-output devices at many remote locations. By means of the communications equipment, input is received by the Computer and results are returned to the inquirer.

The following paragraphs discuss the Real-Time Computer and its peripheral units.

# **Peripheral Units**

The Real-Time Computer can accommodate a large variety of peripheral units. For example, it can handle UNIVAC Solid-State Subsystems equipment such as the High-Speed Printer, the High-Speed Card Reader, and the Punch-Verifier Unit. Uniservo IIA and Uniservo III tape handlers can be connected to the system. In addition, mass-storage devices of the random access type such as flying-head drums, can also be incorporated into a Real-Time System.

# **Peripheral Systems**

The central site peripheral systems are listed as follows:

Flying-Head Drum Subsystem

A Channel Synchronizer A Drum Control Unit One to eight Drum Units

Magnetic Tape Subsystem

A Channel Synchronizer

A Magnetic Tape Control Unit

One to Twelve Magnetic Tape-Handling

Units (Uniservo IIA)

High-Speed Printer Subsystem

A Channel Synchronizer

A High-Speed Printer Control Unit

One or two High-Speed Printers

Card Equipment Subsystem

A Channel Synchronizer

A Card Equipment Control Unit

A High-Speed Reader

A Punch-Verifier Unit.

To communicate with the computer each peripheral subsystem utilizes an input-out-put channel. Any one of the peripheral systems may be connected to any one of the 12 input-output computer channels. Thus as many as 12 peripheral subsystems in various combinations may be connected to the 12 Computer input-output channels.

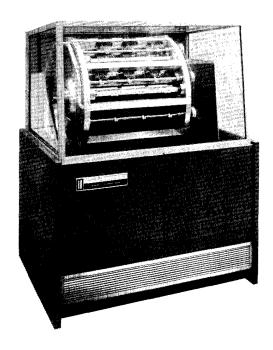

# **Magnetic Drum Storage**

In addition to major features such as large capacity and high-speed random access these mass-storage units employ the flying head (air-floating head) technique which combines aerodynamic and pneumatic principles. The read-write heads float at one-half a thousandth of an inch or less from the oxide-coated surface of the drum, on a boundary layer of air, generated by the rotation of the drum. The read-write heads are suspended in position by the opposing forces of the boundary layer of air and the head-positioning mechanism.

# Flying-Head Drum Storage FH-880

In the FH-880 Drum Storage Unit forty head blocks are positioned around the drum. Mounted in each are 22 read-write heads, one for each recording track which revolves beneath the block. The read-write heads record information on the drum surface at a density of 490 bits per inch while it revolves at 1800 revolutions per minute. Recording frequency is approximately 1 megacycle.

There are 128 6-track bands across the drum. Each band can store 6,144 computer words, allowing a total of 786,432 words to be recorded on the drum. Average access time to information stored on the FH 880 drum is one-half drum revolution or 17 milliseconds.

# Read-Write Operations

The 30-bit computer words are divided into five 6-bit groups as they are recorded on the surface of the drum. Each 6-bit group is written in parallel followed by the next group and so on until the word is written. Each word is considered one angular address and has a parity bit associated with it.

When performing a read or write operation on the flying-head drum storage, the computer:

- 1. Sets up a buffer mode

- 2. Sends a function word to the storage control unit via the channel synchronizer.

The function word contains the starting address and a code specifying which operation is to be performed. The end of the Computer buffer mode will stop the operation.

When a read is to be performed, the storage system locates the starting address and reads the word at that location, and then the input request signal is sent. If an "acknowledge" is received before the beginning of the next word, the information can be read into the Computer as fast as it comes off the drum. This rate can be varied by integral powers of 2, starting from 16.4 microseconds up to a maximum of 262 microseconds. Consecutive words are read into the Computer until the buffer mode ends.

The write operation is similar to the read operation except that the output request signal is transmitted to the Computer immediately upon receipt of the function word. Then the storage system looks for the address and receives a word from the Computer at the same time.

#### Drum Search

Two types of drum search are available, each using a one-word identifier. One type will locate the matching word and store its address. The other initiates a read operation starting with the word following the matching word.

Overflow words can be inserted at any location preceded by an end of block which is represented by thirty 1-bits. These words will contain an address and an identifying code. When an overflow word is reached during a search, the search will stop at that point and the overflow address is sent to the computer. The search can be reinitiated under program control at the location specified by the overflow address. The End of Block word can also stop a search before a find has been made.

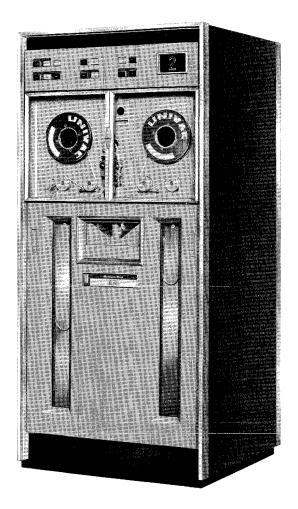

# Magnetic Tape Storage

As many as 12 UNISERVO IIA magnetic tape units may operate with a UNIVAC

Real-Time Computer through a tape control unit and a channel sychronizer.

The multiple control units and large storage facilities of the Computer provide for simultaneous tape reading, tape writing, and computation. This means that a 2400-foot reel of tape, containing a data-history file, may be read, updated, and rewritten on an output tape in the time required to read the original file.

The tape units provide fast tape-mounting and ease of operation. A switch on the front panel of each unit permits interchanging of metallic or Mylar\* tape. A number of checks is incorporated into the unit to provide and maintain accuracy of information as it is read or recorded.

<sup>\*</sup>Mylar is a registered trademark of E. I. du Pont de Nemours and Company, Inc.

Tape can be moved in a forward or backward direction at a speed of 100 inches per second. Reversal time is 600 milliseconds. Data bits are recorded on the tape in parallel form and characters in serial form at a density of 250 or 125 bits per inch. There are eight recording channels, one is used for parity bits, two for the zone; four, for numerics; and one, for the sprocket pulse. Thus, any 6-bit code plus an odd or even check bit may be employed.

The UNIVAC Real-Time Computer can also accommodate UNIVAC III System magnetic-tape-handling units.

#### HIGH-SPEED CARD READER

The 80-column card High-Speed Reader is a fast, accurate punched card input unit capable of reading up to 600 cards per minute. The complete accuracy of each read operation performed by the High-Speed Reader is assured through two distinct readings of each 80-column input card.

Data cards stacked in the input magazine are fed into the continuously revolving rollers that transport them through both reading stations, after which they are sent

to a stacker. During its course through the transport mechanism, a card conveys its contents to the Computer when it is brushsensed at the second read station. When once inserted between the rollers, a card moves without interruption until it reaches its stacker. If it were possible to halt the High-Speed Reader instantaneously in the midst of its card-cycling, the following situation would be revealed. First of all, four cards would be committed to the system. The first card in transit from the input magazine, would be near the rollers. Depending on the exact stopping point in a cycle, the next two cards, would be either at or approaching each of the two reading stations. The progress of the fourth card would have been suspended at some point on its way to a stacker. It is this ability to feed and read cards at the same time which enables the High-Speed Reader to reach and sustain its input speed at a maximum rate.

Misfeeds, row misregistration, jams and full stacker are detected; a stacker full signal is provided. Reading at two stations provides full data-checking.

#### **PUNCH-VERIFIER UNIT**

The 80-column Punch-Verifier Unit can punch up to 150 cards per minute. The unit

consists of an input magazine, a punch station, a post-read station, and two output stackers. The post-read station assures the accuracy of information punched into cards. Verification of punched data is performed at the post-read station on a hole count basis.

A word-for-word check or verification may be easily programmed, eliminating the necessity for a complicated checking procedure. A compact control panel, in open view, advises the operator of all conditions occurring within the unit at any given moment.

The input magazine, or card-feed bin, holds the stack of cards into which information is to be punched. It has a holding capacity of 600 cards. There is a card-lifting lever which may be depressed to assist in the removal of unprocessed cards. A card weight which fits over the top card in the input stack ensures a positive, uniform feed, down to and including the final card.

During the time that a card is in transit to the punch station, the proper punches for that card can be set up. Electrical signals are used to energize a set of actuator magnets. All of the actuators are contained in a 960 magnet matrix, one for each possible hole position on the card, and the energized actuators correspond to the positions which are to be punched. After the card has been punched, a cam action then opens the card stop and the card moves to the post-read station for verification. From the post-read station, the cards move into the stackers.

Two output stackers, or bins, are contained in a convenient hinged assembly which swings out for maintenance. The bins are designated stacker 1 and stacker 0. Each stacker is capable of holding 850 to 1200 cards. When either stacker is full, microswitches underneath it stop the unit, and an indication is given on the control panel.

#### THE HIGH-SPEED PRINTER

The High-Speed Printer is capable of printing output information, intermediate results, distributed accumulations and balances, and final reports at a rate of 600 lines per minute.

Basically, the Printer is designed around 128 print wheels which revolve at high speeds. These wheels correspond to the horizontal printing positions across the page. Each print wheel contains 26 alphabetic, 10 numeric, and 15 special characters such as the period, dollar sign, ampersand, colon, and semicolon. Character spacing is ten to the inch across. Line spacing is six to the inch vertically with variable spacing options available to the programmer.

In addition, the paper feed will handle sprocket-fed paper (including card stock, either blank or preprinted) from 4 to 27 inches in over-all width. At least four carbon copies can be made by using paper between 11 and 13.5 pounds in weight. Furthermore, impression control permits variation in the strength of the printing hammer stroke, and fine vertical adjustments of the Printer in operation. The Printer will stop automatically if it detects a low paper supply.

# TRANSMISSION AND COMMUNICATIONS Input-Output Channels

Communication of data between the Real-Time Computer and its central site peripheral units, remote input-output devices, and other computers is achieved through 14 input-output channels. These channels are actually plug-in cables containing various lines which are used to conduct and control information.

Two of these channels are reserved for communication between the Computer and other computers that may be included in a UNIVAC Real-Time System. Depending on the specific requirements of the applications to be performed and on the UNIVAC Real-Time System configuration, the remaining 12 channels may be used as required with remote input-output devices and central site peripheral units.

#### **Data Transfers**

Any part of the Computer's internal core storage can be used as an input-output data buffer storage area, with the exception of the few special core storage locations that are reserved for the Incremental Clock and the interrupts. The Computer itself can continue main-program processing without constant interruption by the various inputoutput units. Information is transferred between the Computer and its external units (remote input-output devices and central site peripheral units) in "blocks" of data. A block of data is a series of words or half-words having consecutive core memory addresses, starting with a program-determined first word and ending with a program-determined last word or an external interrupt.

#### **Buffer Mode**

A buffer mode transfer, which occurs independent of main program control, is used to transfer blocks of data between inputoutput units and core storage. Before execution of a buffer mode transfer of data, the program must perform the following steps:

- 1. Activate the channel to be used for the information transfer, allowing the Computer to recognize data requests on that channel.

- Load the channel's index register with the data control word. (The lower and upper halves of the data control word contain the beginning and ending address of the section of core storage involved in the transfer.)

- 3. Send the proper function word or words to the peripheral unit.

Data is then transferred between the Computer core storage and the peripheral device without main program intervention. When a word is transferred to or from storage, one is added automatically to the lower half of the control word. The data transfer is terminated when the Computer senses that the upper and lower halves of the control word are equal. Steps one and two above are accomplished with one of the Initiate Buffer instructions, and step three is performed by the Enter External Function instruction.

#### **Input-Output Control**

Equipment external to the Computer is controlled by function words which activate external function control lines. The function word is translated into a discrete set of actions codes by the external unit. The use of program-generated function words, rather than Computer instructions, in controlling peripheral equipment allows the Computer logic to be independent of the characteristics of input-output units. This permits nearly any type of digital device to be connected to the Computer without modifying computer logic.

Interrupt words are generated by the external units and transmitted to the Computer on the input data lines to inform the Computer program of the operating status of the peripheral unit or its desire to initiate or terminate a transfer. An interrupt

word is distinguished from data by activating the external interrupt control lines. Activation of these lines causes the Computer program to jump unconditionally to a storage address associated with the particular input-output channel. From there, the Computer will execute a subroutine which analyzes the interrupt word and prescribes the appropriate action to be taken (Figure 3-2).

#### **External Equipment Requirements**

All peripheral units employed in real-time systems must have characteristics suited to both the system and the application. The following capabilities are invariably required of any peripheral unit in a real-time system:

- 1. Ability to accept, translate, and execute function words

- 2. Ability to respond to data-channel input-output acknowledge signals.

- 3. Ability to produce input-output request signals.

The following capabilities are almost always required of peripheral units in a real-time system:

- 1. Ability to generate interrupt words.

- 2. Temporary storage to store as many bits as the peripheral unit transmits in a single transaction.

- Temporary storage capable of storing the full repertoire of function codes for the specific peripheral unit.

#### REMOTE INPUT-OUTPUT DEVICES

Because the central site equipment can communicate directly with nearly any type of external digital equipment, remote inquiry answering devices of many different designs can be part of a UNIVAC 490 Real-Time System. Usually, remote inquiry-answering units are especially designed to meet the specific requirements of a particular real-time application. The following paragraphs describe briefly various remote inquiry-answering units now in use at real-time system installations.

#### **Keyboard Printer**

The Keyboard Printer permits keyboard insertion of transaction data and printed page output of computer responses at speeds of 60, 75, or 100 words per minute, depending upon the telegraphic service. The keyboard and printer can be used separately or in combination. Faster printing speeds are available with high-speed telephone communication lines.

The keyboard is the operator's basic means of alpha-numeric input to the system for all information, except that which can be entered via the data keys. The unit employs a full four-bank keyboard with 10 numeric keys, 26 alphabetic keys, 11 special character keys, and a space bar.

| NAME                | ORIGIN      | MEANING                                          | EFFECT                                                                      |

|---------------------|-------------|--------------------------------------------------|-----------------------------------------------------------------------------|

| Output Acknowledge  | Computer    | Computer is transmitting an output word          | Initiates cycle whereby output<br>unit accepts and processes<br>output word |

| Output Data Request | Output Unit | Output unit is ready to receive next output word | Computer forms next output word and sends output Acknowledge                |

| Input Data Request  | Input Unit  | Input unit is transmitting an input word         | Computer accepts input word and sends input Acknowledge                     |

| Input Acknowledge   | Computer    | Computer is receiving the input word             | Initiates cycle whereby input unit produces next input word.                |

Figure 3-2. Input-Output Control Signals

The basic correction facility incorporated in the UNIVAC alpha-numeric equipment operates on a field basis. When an error is detected immediately after it occurs, as in the case of a wrong key being operated, the field-erase key is depressed, resulting in the printing of an error symbol after the faulty entry. The correct entry can then be made. If an error is not discovered until after the transaction has been entered, it can be corrected by means of an appropriate change transaction.

The printing unit prepares a copy of all transaction data as it is typed on the keyboard. Computer responses are also printed by the printing unit.

The Keyboard Printer may be supplied with special features which make it an extremely versatile input-output device. For example, the unit can be used to prepare multilith masters, multiple interleaved carbon sets, horizontal and vertical tabulation, as well as a large variety of printed page requirements. For extremely accurate feeding of forms, the unit is also available with pin-feed platens. It may be used to print payroll checks and a variety of order and invoice forms, and can be programmed to extract selected portions of a transmitted message at various locations.

At the option of the user, the Keyboard Printer can be equipped with a format control panel. This auxiliary device can be used to permit greater condensation of data. It also assures that all segments of the

data message are transmitted. Housing 21 to 35 pushbutton illuminators, the format control panel is used by the operator to identify specific types of transactions and data fields being entered. By observing which field buttons are illuminated, the operator is informed of transaction data items which are necessary to carry out the indicated transaction.

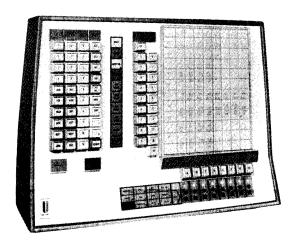

#### **Uniset Console**

The Uniset Console is a keyboard device specifically designed to meet point-of-sale operating requirements of an airline company. Connected on-line with the Computer, this device interrogates the system for flight information by means of its keyboard. Indicator lamps display requested information as well as the Computer's reply. Relevant flight information is stored on a series of transparent cards. When inserted in the Uniset Console by its operator, this information is identified to the Computer.

The Computer identifies each Uniset by a four decimal digit identification number which is read from four manually settable number switches contained within the set's housing. Although developed originally for Airlines Reservations Systems, the Uniset is readily adaptable to various other general applications.

#### The Uniset

The Uniset is actually a unitive configuration, in a modern modular arrangement, of the combined features of the Keyboard Printer and the Uniset Console.

Functioning as a general-purpose remote input-output device, it allows rapid and accurate interrogation of the Computer. Basically, the Uniset comprises an alphanumeric keyboard, a format control panel, printer card mount, and data keys. The keyboard is the principal medium for inserting transaction data. The unit's fourbank keyboard contains 10 numeric keys, 26 alphabetic keys, and 11 special character keys. Careful attention to color and placement of the various elements permits operation of the Uniset quickly and accurately, with a minimum of effort. Because of the assistance automatically supplied by the equipment during the entry of the data, the complete transaction is carried out smoothly, with a minimum of delay, through the use of the format control keys. The key devices operate with a light touch, yet, like all the Uniset components, are rugged in design to assure reliable operation under the heavy use to which they are exposed.

In addition to printing responses as they are received from the Computer, the

printer provides the operator with a printed copy of input transaction data entered on the keyboard. Employing a unique printing mechanism, the unit is quiet in operation and all printed copy can easily be seen by the Uniset operator.

#### Format Control Panel

The format control panel is a set of 21 to 35 illuminated pushbuttons which are used by the operator to identify specific types of record transactions (for example, new record, reconfirm, cancellation, and so on) and the particular fields being entered (for example, name, phone, remarks, and so on). By observing which field buttons are dimly illuminated, the operator is notified of the items of information required to carry out the transaction he has indicated. Upon depression of one of the dimly illuminated buttons, it "brightens." Upon depression of the next desired dimly illuminated button, that button brightens and the previous brightly illuminated button extinguishes. Thus if an operator is interrupted during a transaction the brightness of illumination of the buttons reminds him of the stage of the entry.

The card mount provides the operator with a convenient and fast method of limiting the inquiry to a specific area or portion of transaction data. The segment data keys consist of three groups of keys which are used for entering specific parts of transaction information.

#### **COMMUNICATIONS EQUIPMENT**

In the UNIVAC 490 Real-Time System, remote inquiring-answering devices are connected to the centrally located Computer through communications lines made available by common carriers. Communications equipment located at both the central and the remote sites converts data into a format that can be transmitted over the communication lines. Information arriving at the central site in common carrier form is retranslated by other special equipment into a form usable by the Computer.

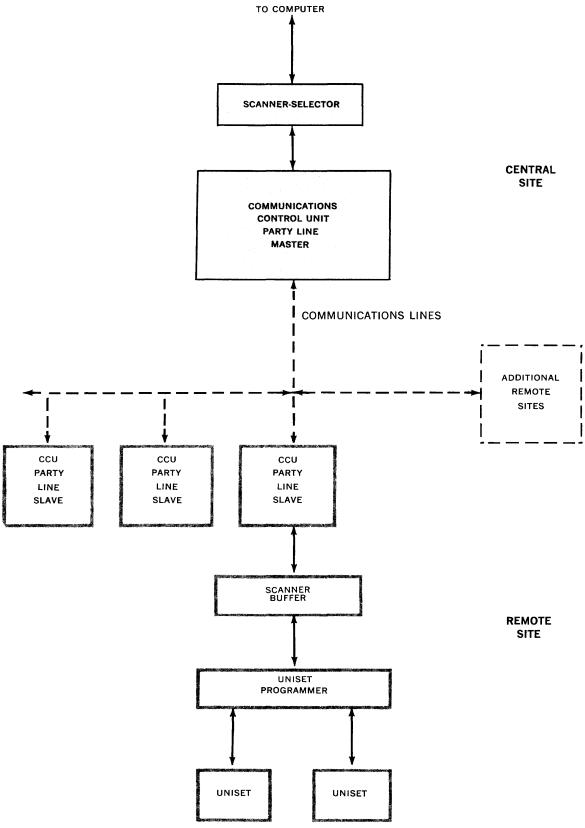

Figure 3-3. Party Line Network

This equipment also controls the various communications circuits to prevent interference and to provide equal availability of circuits to all points having access to the system. Configurations of this equipment vary according to the type of communications lines employed by the system.

# **COMMUNICATIONS SYSTEMS**

Many types of communications systems may be used to transmit information between remote input-output devices and the centrally-located Real-Time Computer. Selection of a system is based upon the application to be performed and the number of remote devices to be used. Configuration of a system varies according to its type. Two of the many communications systems which may be employed are the party line and the line switching network (Direct Distance Dialing).

#### PARTY LINE NETWORK

In a party line network (Figure 3-3), remote input-output devices are connected to a Uniset Programmer. This unit may connect, for example, two Keyboards plus Printers to a Scanner-Buffer. The Programmer provides control functions for the two remote devices sharing it.

# Scanner-Selector

The Scanner-Selector (S-S) is a device used for connecting up to 16 peripheral units to a single pair of UNIVAC 490 Real-Time Computer input-output channels. It is a simple device in that it does not attempt to directly switch all signal lines on all 32 cables, but instead, switches a single line to each peripheral unit, as an indication that that unit may or may not switch those signal lines it uses. No data storage or buffering is required in the S-S; each peripheral unit provides its own computer

communication capability via a set of common busses. Each S-S is capable of operating with others, for building a cascaded "scanner complex," allowing many more than the basic 16 peripheral units to share a single computer channel pair.

#### PARTY LINE COMMUNICATIONS SYSTEM

The Party Line Communications System is a digital communications system. It consists of two functional types of digital terminal equipments, master and slave, connected by a communications facility. One master and a number of slave terminals compose a maximum Party Line Communications System. The master terminal is called a Communications Control Unit, Party Line Master (CCU-PLM) and each slave is called a CCU-PLS.

The Party Line Communications System provides bidirectional communication between digital data-processing equipment at the CCU-PLM location and data-handling equipment at each of the CCU-PLS locations. Direct intercommunication between CCU-PLS terminals is not permitted. Only one CCU-PLS may communicate with the CCU-PLM at a given time.

The communications facility is typically a voice-band channel with full-duplex capability. The channel terminations are digital data subsets (modem units). Each slave terminal is electrically bridged across the party line sending pair and receiving pair that terminate at the master station site.

Data transmission between the Central Processor and a remote station is initiated by selective polling (calling) of each CCU-PLS in turn. A polled CCU-PLS communicates with the CCU-PLM as if a direct connection existed between the two with all other CCU-PLS units disconnected. Bidirectional communication continues until

the CCU-PLS is told to "hang up" by the data-handling equipment at the remote site. The "Hang Up" signal occurs at the end of a message sent to the Central Processor. The message content indicates to the Central Processor that communication with that station is complete. The Central Processor then instructs the CCU-PLM to poll the next CCU-PLS.

A polled CCU-PLS responds with data when data is made available by a remote data-handling device or with a "No Data" control code. The "No Data" control code causes the CCU-PLM to poll the next CCU-PLS.

#### **Transfer Function**

As each Communications Control Unit becomes ready for a one-word buffer transfer, it requests service of the Scanner-Selector (S-S). The S-S sequentially examines the scanner request lines from one of the sixteen stations, and, upon locating a scanner request signal on one of these lines, the scanner transmits a select pulse to the control circuit of that station. The control circuit then initiates the transfer of a data word from the character register to the Computer, or vice versa, depending upon the direction of transfer.

Normally, the scanning circuit is released by terminating the scanner request signal upon the transfer of one Computer word. Transfer of the next word from the same Communications Control Unit is accomplished after one complete cycle of the Scanner-Selector.

The tagging circuit of the Communications Control Unit forms an identifier in the low order 15-bits of the Computer word. The identifier specifies a message buffer area in core storage. The identifier is held until the end of the message while the data character is transferred as the upper 15 bits of the Computer word.

# LINE SWITCHING NETWORK (DIRECT DISTANCE DIALING)

The second type of communications line configuration for the Real-Time System is the Line Switching Network (Figure 3-4). This line configuration may use telegraph or voice grade facilities. Line switching service is a network where connections are made only when communications are desired.

# COMMUNICATIONS CONTROL UNIT, TELEGRAPHIC HALF-DUPLEX

The Communications Control Unit, Telegraphic Half-Duplex (CCU-THD) is a bidirectional signal converter and adapter for use between a telegraphic channel terminal device and a character input-output register of a computer or remote peripheral device. It serves to relay data from the computer via a telegraphic channel to the remote device, and vice versa. The CCU-THD may utilize Direct Distance Dialing to set up the channel to the proper destination. Operation is half-duplex; therefore, data moves in only one direction at any given time, reversing at some other time.

The CCU-THD handles seven-bit serial asynchronous nine and one-half unit characters at the telegraphic interface, and sixbit parallel characters at the computer or peripheral device interface. It can be adjusted to standard bit rates in the range of 45 to 75 bits per second as well as to high-speed rates in the range of 600 to 750 bits per second if used on voice-band channels. For operation on high-speed channels, polling circuits may be made available to replace the dialing circuits in which case it is called CCU-PHD.

The CCU-THD may use a modified Baudot code of seven bits. The first five bits are standard Baudot code. The sixth bit is used to distinguish letter codes from figure codes. A zero (space) in the sixth bit designates the codes of the codes of the codes of the codes.

Figure 3-4. Line Switching Network

nates the code as letters, while a one (mark) designates the code as figures. The seventh bit is a parity check bit added by the CCU to data leaving the Computer, and deleted by the CCU from data entering the remote device, and vice versa. The seventh bit is a one or zero as needed to maintain odd parity.

The seventh bit code appears only on the communications channel. The CCU-THD presents an error indicating line and six parallel data lines to the Computer or peripheral device. A one on the error line indicates the concurrent data did not meet the parity check when received. Conversely a zero indicates it did.

The CCU-THD also checks message (longitudinal) parity. The transmitting CCU generates a message parity check code at the end of a message which is compared with the message parity count at the receiving CCU. If they do not compare, a one is presented to the error line.

The CCU-THD contains an interchangeable internal circuit designated a Function Converter which makes its interface compatible with interfaces of a wide variety of data-handling terminal devices.

# COMMUNICATIONS EQUIPMENT FOR SPECIAL DEVICES

A Communications Control Unit, Telegraphic Master, Simplex (CCU-TMS) is used for putting teletypewriter devices and data subsets on-line with the real-time system. It is a unidirectional signal converter and adapter for use between a Computer output channel and the Scanner-Selector and telegraphic channel sending terminal. It accepts 6-bit parallel characters from the S-S, converts them to 5-bit code characters, and sends them to a telegraphic transmitting terminal.

Operation of the unit may be adjusted to any standard telegraphic bit rate. The CCU-TMS also generates control pulses for an exchange service telegraphic terminal unit on ten control lines at the rate of ten pulses per second, and in response to dial code 6-bit straight-binary characters received from the Scanner-Selector.

A Communications Control Unit, Telegraphic Slave, Simplex (CCU-TSS) is also used with common carrier teletypewriter equipment. It is a single direction signal converter and adapter used between a telegraphic channel receiving terminal and the Scanner-Selector. It receives 5-bit serial coded characters from the communications terminal and converts them to 6-bit codes for entry into the Scanner-Selector. The CCU-TSS can be adjusted to accept any standard telegraphic character rate.

# 4. Instructions

#### INSTRUCTION WORD

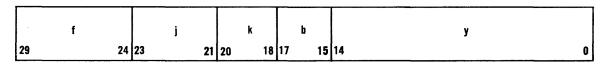

As shown in Figure 4-1, each 30-bit instruction word is composed of five designators.

# f Designator

The function code designator, f, is a six-bit code that specifies the principal operation—shift, store, add, and so on—to be performed by a program step. Sixty-two function code values constitute the UNIVAC Real-Time System repertoire of instructions.

#### y Designator

The Y designator is a 15-bit code from which is derived either the address of the operand, or, when the k designator equals 0 or 4, the operand itself.

#### **b** Designator

The operand address modification designator, b, is a 3-bit code that governs the first modification of y. This modication involves adding to y the contents of a B-register designated by b.

#### k Designator

The operand-interpretation designator, k, is usually a 3-bit code that controls the procedure by which the operand is obtained

and/or stored. The effect of k is different for each of three instruction categories: read, store, and replace.

The operand interpretation designator also controls data transmissions during store operations.

# j Designator

The branch-condition designator, j, is usually a 3-bit code that may be interpreted as a skip or jump-condition designator, a register designator, or a repeat modification designator.

#### INSTRUCTION CYCLE

The instruction execution cycle begins with a storage access period that transfers the address of the next instruction from register P to register S. Next the 15-bit contents of the storage address register, (register S) are translated, activating the storage selection system, which transmits a 30-bit instruction from memory into register U.

As soon as it enters register U, the instruction word assumes control over the execution of the remaining phases of the program step.

The instruction word function code and various designators are then translated. If address modification is specified, the contents of the designated index register are

Figure 4-1. Instruction Word

added to the address portion (15 low order bits) of the instruction in register U before execution. Now the control mechanism performs the operations designated by the instruction word; that is, it executes the program step—add, subtract, compare, and so on.

The instruction word remains in register U until it is replaced by the succeeding instruction word at the beginning of the next program step.

# INSTRUCTION REPERTOIRE

The programming operations executed by the 62 function code designators are listed below. In describing the operations, the following conventions are used.

- ( ) the contents of the storage location or register enclosed within the parentheses.

- the quantity on the left is transferred to the storage location or register on the right.

- A the accumulator, a 30-bit shift register.