For Internal Use Only

This document is provisional in nature and is intended as a vehicle for meeting immediate needs with regard to system familiarization and orientation. UNIVAC  $(\mathbb{R})$  Division of Sperry Rand Corporation reserves the right to change and/or modify such information contained herein as may be required by subsequent system developments.

REGISTERED TRADEMARK OF THE SPERRY RAND CORPORATION

PRINTED IN U.S.A.

@1966-SPERRY RAND CORPORATION

# UNIVAC 9200/9300 HARDWARE REFERENCE MANUAL

# TABLE OF CONTENTS

Page

| Organization of the UNIVAC 9200/9300 • • • • • • • • • • • • • • • • • • |    |

|--------------------------------------------------------------------------|----|

| Program Instructions - General • • • • • • • • • • • • • • • • • • •     |    |

| Binary Instructions                                                      |    |

| Logical Instructions                                                     |    |

| Decimal Instructions                                                     |    |

| Branch Instructions                                                      |    |

| Expanded Instruction Repertoire (Multiply, Divide, Edit)22               |    |

| State Control Instructions                                               |    |

| Input/Output Control                                                     |    |

| General Purpose Input/Output Channel                                     |    |

| Basic Peripherals                                                        |    |

| Peripheral Control                                                       |    |

| Control Panel                                                            |    |

| Operation Description •••••••••••••••••••••••••••••••                    |    |

| Physical Characteristics                                                 |    |

| Instruction Repertoire Summary                                           | 4  |

| Multiply, Divide and Edit Timing • • • • • • • • • • • • • • • • • • •   | ۱. |

|                                                                          |    |

## ORGANIZATION OF THE UNIVAC 9200/9300

The Central Processor Unit consists of four operational sections which are described below.

## MAIN STORAGE:

The main storage of the UNIVAC 9200 is characterized by 1.2 microsecond cycle time while the UNIVAC 9300 has a 0.6 microsecond cycle time. Each addressable position of main storage consists of a nine bit unit called a byte. The bit combination within a byte can represent alphabetic, numeric (decimal), binary or logical data. The main storage is used to store data received from input peripherals, results of processed data, data to be distributed to output peripherals, program instructions and control information.

| Bit Parity |

|-----|-----|-----|-----|-----|-----|-----|------------|

|     | 1   | 2   | 3   | 4   | 5   | 6   | 7          |

Figure 1. Byte Representation

Storage Boundaries:

Locations in main storage memory are numbered consecutively from 0 through available memory. The maximum address of the UNIVAC 9200 is 16,383 and for the UNIVAC 9300, 32,767. Bytes may be addressed separately or in groups. The address of a group of bytes is the left most byte of the group. Two consecutive bytes constitute a halfword if the most significant byte starts at an even address such as 0, 2, 4, etc.

| Byte 1 |     | Byte | 2 |    |

|--------|-----|------|---|----|

| 0      | _ 7 | 8    |   | 15 |

Figure 2. Halfword Representation

Instructions use two halfword (4 bytes) or three halfword (6 bytes) representations and are restricted to halfword boundaries. For instructions which specify a fixed length field, the second operand is restricted to halfword boundaries. If the field lengths are variable, boundary restrictions do not apply. All fixed or variable length operands are addressed at the most significant byte position regardless of instruction processing, i.e., right to left or left to right. For instructions with variable length operands, the length is specified as a binary number which is 1 less than the count; thus a length count of 1 is expressed by zero.

NOTE: Although the hardware length is expressed as one less than the actual count, the Assembler allows the programmer to specify the exact field length he desires.

#### Parity Checking:

Each 9-bit byte of memory uses the ninth bit to store odd parity. Odd parity is derived by summing the number of 1 bits within the other 8-bits. If the sum is even, the parity bit value is made a 1. If the sum is already odd, the parity bit value is made a 0. This parity check bit is checked as data are read out of memory and is regenerated when data are altered as result of processing. Parity is also generated when data are introduced into the processor from peripherals or other sources that do not already have a parity bit included in their data format. In other parts of this description of the central processing unit the parity bit will not be mentioned except as the source of a possible error condition. If a processor parity error that is detected during the transfer of data to and from the peripherals occurs, it is considered a peripheral parity error and will be covered in the input/output error section.

#### MEMORY ORGANIZATION:

The following memory map (Figure 4) shows the specifically assigned memory areas of the first 260 bytes of memory.

Processor State Control:

Associated with the UNIVAC 9200/9300 are two types of instructions, an instruction set for use by the programmer and a state control instruction set. State control instructions are concerned with changing the Program State Control (PSC). The PSC words have the following organization (Figure 5).

There are two program states: Processor and 1/0. In the Processor PSC, interrupt is never inhibited; in the 1/0 PSC, interrupt is always inhibited. Also, in the 1/0 state restricted memory locations 0 through 63 can be accessed without a processor abnormal error being generated. There are two banks of General Purpose registers, one associated with each PSC. Depending upon which PSC the program is operating within, designations refer to only one of the two sets of registers.

- DS -- Device Status

- DA -- Device Address

Figure 4

| CC A 00000 | 00000000 | Р | Processor PSC |  |  |  |  |  |

|------------|----------|---|---------------|--|--|--|--|--|

| CC A 00000 | SRC      | P | I/O PSC       |  |  |  |  |  |

| 0          |          |   |               |  |  |  |  |  |

Figure 5

## CONTROL SECTION:

The control section controls the sequencing of instructions and interprets and controls the execution of each individual instruction. The cycling of main storage is initiated by this section. The control section also handles all interrupt handling and error checking. The control section also maintains the program address location counter and handles the different processor mode of operation.

## ARITHMETIC SECTION:

The arithmetic section performs all data manipulations including logical and numerical arithmetic, data comparison and shifting. This section also performs single or double indexing of operand addresses. The adder in this section performs arithmetic in two's complement form.

Sixteen arithmetic registers each two bytes wide are used for arithmetic and indexing. The registers are divided into two sets of eight registers. One set is associated with the Processor Program State Control, and the other associated with the Input/Output Program State Control. The arithmetic registers are specified by address 8 through 15. Addresses  $0_8$  through  $7_8$  are illegal.

There are three classes of arithmetic operation in the UNIVAC 9200/9300.

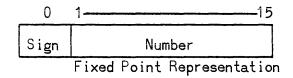

Fixed-Point Arithmetic:

A fixed-point arithmetic operand is a 16 bit binary value (halfword). The most significant bit represents the sign, and the least significant 15 bits contain the binary number. Signed binary arithmetic is only performed within the boundaries of the arithmetic registers.

Decimal Arithmetic:

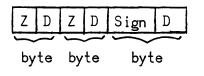

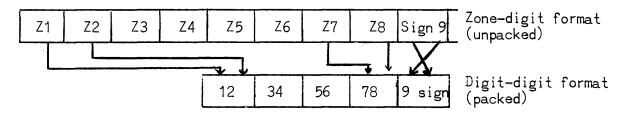

Decimal numbers are variable in length and exist in two formats, unpacked decimal numbers and packed decimal numbers. The unpacked decimal format is divided between zones and digits within a byte. The zone is represented in the most significant 4 bits, the digit in the least significant 4 bits.

Figure 6. Unpacked Decimal Format

Where a decimal number field is represented in unpacked format, the sign of the number is in the zone position of the least significant digit.

The packed decimal format contains decimal digits in the 4 most significant and the 4 least significant bits of each byte. The least significant byte of the field contains the sign in the 4 least significant bits.

| by | уt | е | by | te | by | /te |  |

|----|----|---|----|----|----|-----|--|

|    | Ь  | d | d  | d  | d  | S   |  |

Figure 7. Packed Decimal Format

Sign Bits:

The binary value of the sign bits will be interpreted as follows:

| 0000 through | 1000 – negative number<br>1001 – negative number                     |

|--------------|----------------------------------------------------------------------|

|              | 1010 - positive number - generated by instructions<br>in ASCII mode  |

|              | 1011 - negative number - generated by instructions<br>in ASCII mode  |

|              | 1100 - positive number - generated by instructions<br>in EBCDIC mode |

|              | 1101 - negative number - generated by instructions<br>in EBCDIC mode |

|              | 1110 - positive number<br>1111 - positive number                     |

# Logical Operations:

Comparing, translating, editing, bit setting and testing are provided by the arithmetic section. Logical operations may be performed on fixed length and variable length operands. Logical operations on fixed length operands are performed in the registers and logical operations on variable length operands are performed in main storage memory. The determination of where the logical operation is performed is made by the instruction format.

#### INPUT/OUTPUT:

The input/output section initiates, directs and monitors the transfer of data between main storage and the peripheral devices. The UNIVAC 9200/9300 interfaces directly with the bar printer, serial reader and serial punch. It is possible to interface with other devices through a General Purpose Channel. (See state control instruction set section and input/output section.)

The speed of the processor allows memory time-sharing. Memory timesharing makes it possible for programs to share memory access with many peripherals without distorting the sequence of instructions while data are transferred to and from various peripheral devices. Memory sharing makes it possible for all peripherals to perform at or near their rates speeds without undue processing delay. Input/Output Interrupt:

An 1/0 interrupt is permitted only at the end of a program instruction in the Processor Program State Control. As each instruction ends in the Proc. PSC, the peripheral interrupt request line is examined. If the request line reveals a pending interrupt request, interrupt is granted. When interrupt is granted, program control is shifted to the 1/0 Program State Control (1/0 PSC). Also, the device address and status are stored in fixed locations in memory. For a more detailed explanation of PSC operations see sections on state control instructions and input/output control.

ERROR CHECKING:

The processor will detect certain programming errors and parity errors and stop.

Programming Errors:

If the program attempts a read or write function at an address beyond the capacity of a particular processing unit, a processor abnormal will result. While operating in the Processor Program State Control mode, addresses to the restricted memory area (0-63) will cause an address error. Any write into the print buffer during a print scan will also cause an address error.

Parity Errors:

The processor will detect and stop the program on parity errors as described in the section on parity checking.

Divide Check:

A divide check error will result if a quotient digit greater than nine (9) is formed during a divide order.

#### PROGRAM INSTRUCTIONS

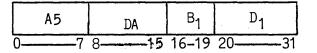

The instructions process fixed length binary numbers, variable length decimal numbers, fixed and variable length logical data, and direct peripheral devices. To perform these functions, three instruction formats are used: RX (register to storage and storage to register), SI (instruction to storage), and SS (storage to storage).

## INSTRUCTION FORMATS:

RX Instruction Format:

The RX instructions consist of 4 bytes. They all reference one of the operating halfword registers. These registers may be used to load, store, compare, add, subtract, or branch; and they also may be used as index registers for the RX and other instructions. The instruction format is shown below. Bits 12 through 15 are not used and will be all zeros.

| Register | Address   |

|----------|-----------|

| Operand  | Operand 2 |

| OP Code | R <sub>1</sub> | 0000  | B <sub>2</sub> | D <sub>2</sub> |

|---------|----------------|-------|----------------|----------------|

| 07      | 8-11           | 12-15 | 16-19          | 2031           |

Figure 8. RX Instruction Format

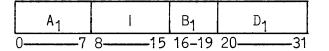

#### SI Instruction Format:

The SI instructions consist of 4 bytes. These instructions contain one operand from the instruction (immediate data) and another operand from memory and are used for testing or storing immediate data. The instruction format is as follows:

|         | lmmediate<br>Data<br>Operand | Ad             | dress<br>rand 1 |

|---------|------------------------------|----------------|-----------------|

| OP Code | 1 <sub>2</sub>               | B <sub>1</sub> | D <sub>1</sub>  |

| 0       | 7 8                          | 16-19          | 2031            |

Figure 9. SI Instruction Format

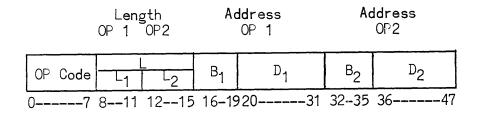

#### SS Instruction Format:

The SS instructions consist of 6 bytes. These instructions control the transfer of data from storage to storage and are used for decimal operations, translate operations, transfer operations, logical operations, and pack-unpack operations. These instructions have variable length operands, the length is specified as a binary number which is 1 less than the actual count; thus, a length count of 1 is expressed by four or eight zeros. The instruction format is as follows:

Figure 10. SS Instruction Format

#### OPERAND ADDRESSING:

An operand may be obtained from memory either by direct addressing or by indexing.

Instructions specify direct addressing by means of an 0 in the most significant bit of the B-field. When the most significant bit of the B-field contains an 0, the three remaining bits of the field are used to extend the D-field by two bits to make a combined direct address instruction field length of 15 bits. A direct address instruction appears as follows:

| B <b>-1</b><br>4 E                  | - |   | d | D-field<br>12 Bits |  |  |  |  |  |   |

|-------------------------------------|---|---|---|--------------------|--|--|--|--|--|---|

| 0                                   | Х | Х | Х | <pre></pre>        |  |  |  |  |  | X |

| 7 zero<br>Direct Address<br>15 Bits |   |   |   |                    |  |  |  |  |  |   |

Figure 11. Direct Address Format

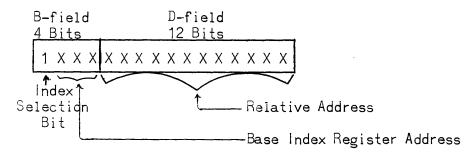

Instructions specify indexing by means of a 1 bit in the most significant bit of the B field. When the most significant bit of the Bfield is 1, the B-field is used to choose one of the eight binary arithmetic registers. The address portion of any indexed address instruction appears as follows:

The specified register supplies the base address which is added to the 12-bit value contained in the D-field on the instruction. The result of this addition now becomes the effective address of the instruction. Any carry beyond 15 bits that may have occurred will be ignored. The following table shows the range of valid addresses that apply for either direct or indexed addressing. Unlisted addresses will unconditionally cause an error, but only when the improper access is made. Therefore, certain instructions which do not have any operand cycles, may have non-valid addresses without giving an error. For example, the direct address, or the calculated indexed address at a Halt and Proceed instruction, which becomes the display information, may have any desired binary value without causing an error condition.

> 0 ---- 63 Restricted memory 64 ---- 8191 Permissible 8192 ---- 12287 Permissible if the memory is 12K, 16K(or 32K on 9300) 12288 ---- 16383 Permissible if the memory is 16K(or 32K on 9300) 16384 ---- 32767 Permissible if the memory is 32K

The addressing of restricted memory under Processor PSC Control results in an error stop. Restricted memory may, however, be addressed under I/O PSC Control without an error stop. I/O devices may read out data from restricted memory without an error stop, however, only during initial load may an I/O device write into restricted memory.

The memory locations 128 to 259 inclusive are reserved for the print buffer. Any attempt to write into the first 128 of these locations during a print operation (excluding paper spacing) will also result in an addressing error.

OP CODES:

The OP Code designations are expressed by two hexadecimal notations for the 8 bit code as shown in Figure 12.

| Binary                                                                               | Hexadecimal                                         |

|--------------------------------------------------------------------------------------|-----------------------------------------------------|

| 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A |

| 1011<br>1100<br>1101<br>1110<br>1110<br>1111                                         | B<br>C<br>D<br>E<br>F                               |

Figure 12

## BINARY INSTRUCTIONS:

The binary instructions that control the use of the arithmetic registers are:

- 1. Store halfword

- 2. Load halfword

- 3. Add halfword

- 4. Subtract halfword

- 5. Compare halfword

The following table shows some of the binary values that can be expressed in the halfword registers or their correspondent halfwords in memory.

| Binary Number       | Decimal Equivalent | Bit Representation  |

|---------------------|--------------------|---------------------|

| 2 <sup>15</sup> -1  | 32767              | 0111 1111 1111 1111 |

| 2 <sup>8</sup>      | 256                | 0000 0001 0000 0000 |

| 2 <sup>0</sup>      | 1                  | 0000 0000 0000 0001 |

| 0                   | 0                  | 0000 0000 0000 0000 |

| -2 <sup>0</sup>     | -1                 | 1111 1111 1111 1111 |

| -21                 | -2                 | 1111 1111 1111 1110 |

| -2 <sup>8</sup>     | -256               | 1111 1111 0000 0000 |

| -2 <sup>15</sup> +1 | -32767             | 1000 0000 0000 0001 |

| -2 <sup>15</sup>    | -32768             | 1000 0000 0000 0000 |

Binary numbers in the registers are expressed as positive and negative numbers. A zero in the most significant bit indicates a positive number. A one in the most significant bit indicates a negative number. Negative numbers are expressed by the 2's complement value of the number. Thus, a plus 1 as shown in the table has a 1 in the least significant bit and the remaining bits are all 0's. For a minus 1, all 16 bits are 1's.

#### CONDITION INDICATORS:

Associated with the Program State Control are condition codes. These condition codes are used to indicate the result of the last instruction performed if they were employed by the instruction. There are four mutually exclusive settings of these codes. The codes are stored in the Program State Control words as follows:

The following table shows the results of addition, subtraction, and comparison.

Condition Indicator Setting

|                                                       | 0                     | _1_                                                                                    | _2_                      | 3                    |

|-------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|--------------------------|----------------------|

| Compare Halfword<br>Subtract Halfword<br>Add Halfword | equal<br>zero<br>zero | <zero< td=""><td>high<br/>≻ zero<br/>≻ zero</td><td>overflow<br/>overflow</td></zero<> | high<br>≻ zero<br>≻ zero | overflow<br>overflow |

The binary instructions all use the RX format, which is as follows:

| Register<br>Operand |                 |                |       |                | iress<br>and 2 |

|---------------------|-----------------|----------------|-------|----------------|----------------|

|                     | OP C <b>ode</b> | <sup>R</sup> 1 | 0000  | B <sub>2</sub> | D <sub>2</sub> |

|                     | 07              | 811            | 12-15 | 16-19          | 2031           |

Figure 13. RX Instruction Format

In this format,  $R_1$  specifies the arithmetic register containing operand 1, and  $B_2-D_2$  specifies the second operand address either indexed or direct with an implied length of a halfword.

| Store Halfword: | STH | OP Code 40 |

|-----------------|-----|------------|

|-----------------|-----|------------|

This instruction stores the contents of the specified arithmetic register at the specified memory address.

Load Halfword: LH OP Code 48

This instruction loads the arithmetic register with the halfword specified by the operand 2 address.

Add Halfword: AH OP Code AA

The halfword operand in memory is added to the contents of the specified register. Several examples of binary arithmetic and their resulting condition codes are as follows:

| R<br>B–D          | OP1<br>OP2<br>R                 | 0000000101010101<br>111111010101011<br>0000000   | +341<br><u>+-341</u><br>+ 0    | <u>CC</u><br>0 | (Zero)     |

|-------------------|---------------------------------|--------------------------------------------------|--------------------------------|----------------|------------|

| R<br>B <b>-</b> D | <b>0</b> P1<br><b>0</b> P2<br>R | 1111111010101011<br>0000000101010101<br>111111   | -341<br><u>-+341</u><br>-682   | 1              | (Positive) |

| R<br>B <b>-</b> D | 0P1<br>0P2<br>R                 | 0000000101010101<br>000000010101010101<br>000000 | +341<br><u>++341</u><br>+682   | 2              | (Negative) |

| R<br>B-D          | 0P1<br>0P2<br>R                 | 011111111111111<br>00000000000000000<br>1000000  | +32767<br><u>+ 1</u><br>-32768 | 3              | (Overflow) |

Subtract Halfword:

SH

## OP Code AB

This instruction is performed in the same manner as the add halfword instruction except that the 2's complement of the halfword operand 2 field is added to the specified register. The preceding examples show some results of binary addition and subtraction.

Compare Halfword:

CH

OP Code 49

This instruction algebraically compares the contents of the designated register with the designated halfword in memory. The results of the comparison are shown in the condition code table.

Binary Overflow:

Binary overflow occurs when the sign is changed erroneously from plus to minus or minus to plus, which happens when an attempt is made to develop a larger negative or positive number than can be expressed in 15 bits.

LOGICAL INSTRUCTIONS:

The following instructions deal with the logical manipulation of data and are not necessarily related in function to binary or decimal arithmetic.

Logical Instructions Using the SI Format:

The SI format is employed in certain logical instructions.

Β1 OP Code D1 12 -15 16-19 20-

In these instructions the 1 portion of the instruction is used either for an immediate second operand or it is ignored. The B and D-fields are normally used to specify the first operand address. The instructions using S1 format are:

- 1. Halt and Proceed

- 2. Test Under Mask

- 3. AND

- 4. OR

- 5. Compare Immediate

- 6. Move Immediate

- 7. Add Immediate

Halt and Proceed

HPR

OP Code A9

This instruction causes the processor to stop and an indication to be set on the control panel. The  $B_1$  and  $D_1$  part of the instruction can be used to display the reason for the halt. If bit 16 = 0, bits 17 through 31 of the instruction word will be displayed. If bit 16 = 1, normal indexing will result and the value of the indexed address will be displayed. Depressing start will cause the next instruction in sequence to be executed.

Test Under Mask

ТΜ

OP Code 91

This instruction uses the  $(1_2)$  immediate operand bits that are 1's to test for equivalent 1's in the byte of memory specified by B<sub>1</sub> and D<sub>1</sub>. If all the 1 bits in the mask are matched against 0 bits in the byte tested, the condition code will be 0. If some of the 1 bits in the mask have corresponding 1 bits in the byte tested, the condition code is 1. If all the 1 bits in the mask have corresponding 1 bits in the byte tested, the condition code is 3. If the mask is 0, the resultant condition code setting will also be 0.

AND

#### NI

OP Code 94

This instruction forms a logical product (AND) of the 12 bits of the instruction with one byte of memory specified by the B-D field. If the corresponding bits of 12 and the one byte of memory are both 1's the result will be 1, otherwise the result will be zero. If all the bits of the memory byte are 0's at the end of the instruction, the condition code will be set to 0. If all or some of the bits of the memory byte are 1's, the condition code is set to 1.

OP Code 95

This instruction forms the logical sum (OR) of the 12 bits of the instruction with one byte of memory specified by the B-D field. All 1 bits of the 12 field are superimposed onto the memory byte. All 0 bits of the 12 field leave the corresponding bits in the memory byte unchanged. If all bits of the memory byte are 0 at the end of the instruction, the condition code is set to 0. If all or some of the bits of the memory byte are 1, the condition code is set to 1.

01

Compare Immediate CLI

This instruction compares the contents of the  $I_2$  field of the instruction to the B-D byte of memory. A full 8 bits are compared without regard to sign. If the  $I_2$  value is equal to the compared byte of memory, the condition code is set to 0. If the byte of memory is less than the  $I_2$  value, the condition indicator is set to 1. If the byte of memory is greater than the  $I_2$  value, the condition code is set to 2.

Move Immediate

This instruction stores the  $I_2$  value of the instruction at the byte of memory specified by the B-D field.

Add Immediate

OP Code A6

OP Code 92

Sign bit 0 is Positive Sign bit 1 is Negative

This instruction adds the 12 bits of the instruction to the halfword in memory specified by  $B_1-D_1$ . The sign of the 12 value is extended from the first byte of the halfword in memory through the second byte of the halfword. The condition code will be set to 0 at the end of the instruction if the answer is zero; to 1 if the answer is minus; to 2 if the answer is plus; and to 3 if an overflow condition causes the sign to be erroneously changed. The following table shows the results of some sample examples of binary addition via this instruction.

OR

MV I

AI

| S<br>0000000101010101<br>← S<br>00110100<br>0000000110001001                     | +341<br><u>+ 52</u><br>+393    | CC<br>2 | (Positive) |

|----------------------------------------------------------------------------------|--------------------------------|---------|------------|

| s<br>01111111111111111<br>← 00000001<br>s<br>1000000000000000000000000000        | +32767<br><u>+ 1</u><br>-32768 | 3       | (Overflow) |

| s<br>( <u>11111110101010111</u> )<br>← <u>00110100</u><br>S<br>(1111110110111111 | -341<br><u>+ 52</u><br>-289    | 1       | (Negative) |

| s<br>00000000000010000<br>← 11110000<br>0000000000                               | +16<br><u>-16</u><br>+ 0       | 0       | (Zero)     |

| s<br>h000000000000000000000000000000000000                                       | -32768<br><u>- 1</u><br>+32767 | 3       | (Overflow) |

Logical Instructions Using the SS Format:

These instructions use the SS format to manipulate data logically in one area of storage against data in another area of storage or to transfer data from one storage area to another storage area. The L field in these instructions is 8 bits in length and governs both operands. The L field can specify from 1 to 256 characters.

| OP | Code | L   | <sup>B</sup> 1 | D <sub>1</sub> | B <sub>2</sub> | D <sub>2</sub> |  |

|----|------|-----|----------------|----------------|----------------|----------------|--|

| 0  | 7    | 815 | 16-19          | 2031           | 32-35          | 3647           |  |

The instructions which are covered under this category are:

- 1. Move Characters

- 2. Compare Logical

- 3. Translate

- 4. AND

- 5. OR

- 6. Move Numeric

Move Characters:

MVC

OP Code D2

In this instruction, L characters can be transferred from the memory address specified by  $B_2-D_2$  to the memory address specified by  $B_1-D_1$ . Characters are unaltered in the transfer and are not checked for any validity except for parity. The instruction is processed from left to right.

Compare Logical:

# CLC

OP Code D5

In this instruction, L characters of operand 1 and operand 2 are compared with each other. The results of the comparison are shown by the condition indicator. If both operands are equal, the condition indicator is set to 0. If operand 1 is less than operand 2, the condition code is set to 1. If operand 1 is greater than operand 2, the condition code is set to 2. The instruction is processed from left to right and is terminated early upon the first inequality.

Translate:

#### TR

OP Code DC

This instruction translates any 8-bit code to any other 8-bit code. Each 8-bit code of the desired field is translated in sequence from left to right. Each 8-bit code of the first operand is used as an argument to increment the address specified by  $B_2-D_2$  so that the derived address can be used to obtain from memory the translated code value which replaces the character to be translated. The translation table, unless restricted by program operation (operand 1 character values), is 256 characters in capacity. The operation proceeds until L + 1 characters have been translated.

AND:

NC

OP Code D4

This instruction forms a logical product (AND) with L + 1 characters of operand 2 and operand 1. If the corresponding bits of both operands are 1, the result is 1; otherwise, the result is 0. If all the bits of the logical product in operand 1 are 0, the condition code is set to 0. If all or some of the bits of the logical product in operand 1 are 1, the condition code is set to 1. This instruction proceeds from left to right. This instruction forms a logical sum (OR) with L characters of operand 2 and operand 1. All 1 bits of operand 2 are superimposed on operand 1. All 0 bits of operand 2 leave the corresponding bits of operand 1 unchanged. If all the bits of operand 1 are 0's at the end of the instruction, the condition code is set to 0. If all or some of the bits in operand 1 are 1's, the condition code is set to 1. This instruction proceeds from left to right.

|  | Move N | Numeric: | MVN | OP | Code | Ι | )' |  |

|--|--------|----------|-----|----|------|---|----|--|

|--|--------|----------|-----|----|------|---|----|--|

In this instruction, L + 1 numeric-digits minus the zone digits are transferred from the memory address specified by  $B_2-D_2$  to the memory address specified by  $B_1-D_1$ . The zone portions of the  $B_1-D_1$  field are unaltered as the numeric portions are replaced. The two operand characters are not checked for validity except for parity. The instruction is processed from left to right.

## DECIMAL INSTRUCTIONS:

The following instructions are primarily concerned with decimal calculations or decimal digit manipulations. These instructions all use the SS format.

|   | 7      | 8-11 | 12-15 | 16-19 | 2031 | 32-35 | 3647 |

|---|--------|------|-------|-------|------|-------|------|

| O | ⊃ Code | L1   | L2    | B1    | Dı   | Bo    | Da   |

The following is a list of decimal instructions:

- 1. Pack

- 2. Unpack

- 3. Compare Decimal

- 4. Add Decimal

- 5. Subtract Decimal

- 6. Move with Offset

- 7. Zero and Add

The SS format used in decimal manipulations splits the L field into four bits for each operand. Thus, the maximum number of bytes that can be handled in any decimal instruction is 16.

The add decimal and subtract decimal instructions should be executed using operands that are in the packed format only. They will interpret bits 4 through 7 of the least significant byte of the operand fields as sign codes when performing the arithmetic. The sign code which is inserted into the result in operand 1 will be determined by the sign of the answer and the ASCII Control Code bit in the controlling Program State Control word. Pack:

This instruction packs decimal data which are in the unpacked zonedigit data format to the packed digit-digit data format.

This instruction proceeds from right to left. The first byte of operand 2 is assumed to have the sign of the field to be packed. As the diagram shows, the sign and digit positions are reversed when operand 2 is transferred to the operand 1 location. All other bytes of operand 1 receive two digits from operand 2. If operand 2 is exhausted before operand 1, 0's are assumed for the remaining positions of operand 2. If operand 1 is exhausted before operand 2, the remainder of operand 2 is ignored.

UNPK

#### Unpack:

This instruction is the reverse of the pack instruction. It also proceeds from right to left. The first byte of operand 2 is assumed to contain the sign. This instruction reverses the sign and digit positions when storing the first byte of operand 2 in operand 1. All remaining digits of operand 2 are placed in operand 1 sequentially in the numeric position of operand 1 with 1111 (if binary coded decimal) or 0101 (if ASCII code) placed in the zone portion of operand 1. If operand 1 is too short to contain all the unpacked digits from operand 2, the remaining digits are ignored. If operand 2 is exhausted before operand 1 is filled, 0's are assumed for the remainder of the operand 2 digits to complete the operation.

### Compare Decimal:

CP

## OP Code F9

OP Code F3

This instruction algebraically compares  $L_1 + 1$  bytes of operand 1 with L2 + 1 bytes of operand 2;  $L_1$  must always be equal to or greater than  $L_2$ . If  $L_1$  is larger than  $L_2$ , 0's are assumed to extend operand 2. The instruction proceeds from right to left, and both operands remain unchanged when the instruction ends. The comparison sets the condition code to 0 for equality, to 1 if operand 1 is low, and to 2 if operand 1 is high. Add Decimal:

This instruction adds decimally  $L_2 + 1$  bytes of operand 2 to  $L_1 + 1$  bytes of operand 1; L1 must always be equal to or greater than  $L_2$ . Addition is performed algebraically. The condition code will be set to 0 at the end of the instruction if the answer is zero; to 1 if the answer is minus; to 2 if the answer is plus; and to 3 if an overflow beyond the field results from the addition. The sign in the case of overflow will reflect the sign of the true answer even if the answer is zero; otherwise, on a zero answer the sign is always plus. The instructions proceed from right to left, and in the case where operand 2 is shorter than operand 1, 0's are assumed for the remaining digits of operand 2.

Subtract Decimal:

SP

OP Code FB

This instruction is performed in the same manner as add decimal except that the sign of operand 2 is reversed.

Move with Offset:

MVO

OP Code F1

This instruction proceeds from right to left. Its function is to transfer  $L_2+1$  bytes of operand 2 to  $L_1+1$  bytes of operand 1 and to shift the digits left by four bits. It also preserves the first four least significant bits of the least significant byte of operand 1. This instruction is used to position for later packed addition and subtraction. This instruction can effectively shift data either right or left. If  $L_2$  is less than  $L_1$ , 0's will be assumed for operand 2 and will fill the remaining positions of operand 1. If  $L_2$  is greater than  $L_1$ , the remaining digits will be ignored. This operation does not affect the condition code, and no check is made for validity of the digits shifted.

#### Zero and ADD:

ZAP

OP Code F8

This instruction is essentially a move instruction proceeding from right to left;  $L_1$  must be equal to or greater than  $L_2$ . The instruction clears operand 1 to 0's before adding operand 2. The condition code will reflect the sign and the value of operand 2; however, a -0 cannot result from this operation.

#### BRANCH OPERATIONS:

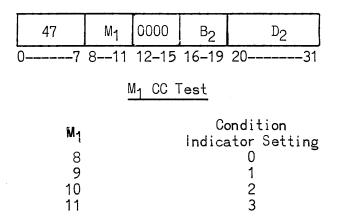

The following instructions are primarily concerned with changing the program sequence or branching from one sequence of operations to another. These instructions use the RX format. The following are the branch instructions:

- 1. Branch on Condition

- 2. Branch and Link

## Branch on Condition:

This instruction uses the four  $M_1$  bits to test none, some, or all of the possible states of the condition indicator. Each bit in the  $M_1$  portion tests the presence of one of the possible four condition settings. If a condition setting is met by the test, a branch will occur. The branch address is determined by a binary value of  $B_2-D_2$  either as a direct address or an indexed address. If  $M_1$  is all 0's, the result is a no-op or skip. If the mask is all 1's, the resultant instruction is an unconditional branch. The instruction does not change the condition indicator setting.

Branch and Link:

BAL

OP Code 45

| 45 | R <sub>1</sub> | 0000  | B <sub>2</sub> | D <sub>2</sub> |

|----|----------------|-------|----------------|----------------|

| 07 | 811            | 12-15 | 16-19          | 2031           |

This instruction is an unconditional branch instruction. It stores the program address, which points at the next instruction in logical sequence, in the register specified by  $R_1$ , and branches to the address specified by  $B_2-D_2$ .

### SS FORMAT INSTRUCTIONS

#### EXPANDED INSTRUCTION REPERTOIRE:

The Multiply, Divide and Edit instructions which are described in the three succeeding sections are available as a factory or field installable feature.

Multiply Decimal: MP OP Code FC

This instruction multiplies OP1 by OP2 placing the product in OP1. L<sub>1</sub> + 1 specifies the size of the product and L<sub>2</sub> + 1 is the size of the multiplier. The size of the multiplier originally in OP1 equals L<sub>1</sub> minus L<sub>2</sub>. If more than L<sub>1</sub>-L<sub>2</sub> digits are in the multiplicand, the most significant digits will be ignored.

The length of the operands are expressed in numbers of bytes of packed decimal data. The condition codes will not be changed by this instruction. The sign of the product is determined by the normal rules of arithmetic.

Programming Restrictions:

- A. The multiplier and multiplicand field may not overlap.

- B. OP1 must contain at least L<sub>2</sub> + 1 leading decimal zeros prior to multiplying.

- C. The sign position of OP1 (multiplier) must contain a value greater than 9.

In addition to obtaining an incorrect result, memory fields beyond OP1 may be altered if the above restrictions are not met. No error indicator will be set.

Divide Decimal: DV

OP Code FD

The divide instruction divides the  $L_1 + 1$  bytes of OP1 by the  $L_2 + 1$  bytes of OP2, developing the Quotient right justified in the  $L_1$  minus  $L_2$  most significant bytes of OP1. The remainder is right justified in the  $L_2 + 1$  least significant bytes of OP1.

The operand field lengths are specified in numbers of bytes of packed decimal data. The sign of the Quotient is determined by the normal rules of arithmetic. The sign of the remainder is the same as the original OP1 sign (dividend).

## Programming Restrictions:

A.  $L_1$  must be greater than  $L_2$ .

B. The sign of OP1 (dividend) must contain a value greater than 9.

C. The divisor and dividend fields may not overlap.

In addition to an incorrect result, memory fields beyond OP1 may be altered or a Divide Check error may occur, if the above restrictions are not met.

Divide Check Error:

If a Quotient digit greater than nine is formed, a divide check error will occur and the processor will stop immediately.

A quotient digit greater than 9 will occur if the absolute value of OP2 is not greater than the absolute value of the  $L_2 + 1$  most significant bytes of OP1; thus, it follows that OP2 must be non-zero and OP1 must contain at least one most significant zero.

Edit:

ED

OP Code DE

The edit instruction proceeds from left to right unpacking and expanding OP2 into the  $L_1$  + 1 bytes of OP1. Editing is controlled by a pattern of bytes originally in OP1. The value inserted in the zone position will F<sub>16</sub> in EBCDIC mode or 5<sub>16</sub> in ASCII mode.

The instruction format is as follows:

| DE | L | B1D1 | B <sub>2</sub> D <sub>2</sub> |

|----|---|------|-------------------------------|

| 07 | 8 | 16   | 32-47                         |

The data from the most significant byte of OP1 is retained and used as a FILL character for the editing that follows. Zero suppression and character insertion are controlled by the Significant (S) Indicator associated with the Edit instruction. Characters in OP2 are unpacked into OP1 or suppressed whenever a Digit Select Byte (DSB) is encountered in any position of the OP1 edit pattern. The DSB is a hexadecimal 20 and operates as described below.

## Zero Suppression:

The S Indicator will be set (turned on) whenever a non-zero digit is encountered in OP2. If the S Indicator is set the DSB in OP1 will be replaced by the corresponding digit, including zeros, in OP2. If the S Indicator is not set the DSB will be replaced by the FILL character when the corresponding digit in OP2 is a zero. The S Indicator is in the reset (off) condition when editing begins. Once the S Indicator is set it remains set. If leading zeros must be retained the S Indicator can be set by a Significant Start Bit (SSB), hexadecimal 21, placed in the edit pattern in the position that is to contain the first leading zero. The S Indicator may be reset (turned off) by a Field Separator Byte (FSB), hexadecimal 22, anywhere in the OP1 pattern. The FSB will itself be replaced by a FILL character.

Character Insertion:

Any character other than DSB, FSB or SSB encountered in OP1 will be retained in OP1 if the S Indicator is set. OP2 will not be accessed. If the S Indicator is reset the values will be replaced by FILL characters.

Any sign accessed in OP2 will be ignored, a positive sign will, however, reset the S Indicator. Therefore, OP2 must contain a number of valid digits (zeros included) equal to the sum of the DSB's and SSB's in OP1. A sign is examined at the time when a digit immediately to its left is accessed. The value of the sign position must exceed hexadecimal 9.

Condition codes are set as follows:

CC set to 00: OP2 is zero CC set to 01: OP2 is negative or unsigned CC set to 10: OP2 is positive

In the case of multiple field editing, CC will not reflect any part of OP2 which precedes the last FSB in the OP1 pattern.

### STATE CONTROL INSTRUCTIONS

State control instructions for the UNIVAC 9200/9300 are those which alter the Program State Control (PSC).

The privileged instructions use the SI format and are:

- 1. Load State

- 2. Store State

3. Supervisor Request Call

PSC OPERATIONS:

Load State:

## LPSC

OP Code A8

This instruction replaces or modifies the Processor or 1/0 Program State Control Word and directs the instruction sequence to proceed under control of either of the PSC words. The PSC load must have a halfword boundary specified for  $B_1-D_1$ . This instruction is also used to restrict the operator Alter and Display functions to memory location 4.

Bits 8 and 9 control the modification of a PSC word as follows:

| Bit<br>8 | Bit<br>9 | Modification                                                                           |

|----------|----------|----------------------------------------------------------------------------------------|

| 0        | 0        | PSC remains unchanged                                                                  |

| 0        | 1        | Load full PSC word start at B <sub>1</sub> -D <sub>1</sub> address (halfword boundary) |

| 1        | 0        | Set ASCII bit to O (off); leave remainder of PSC word<br>unchanged                     |

| 1        | 1        | Set ASCII bit to 1 (on); leave remainder of PSC word<br>unchanged                      |

Bit 10 specifies which PSC word to be acted upon as follows:

bit 10 = 1 Modify or load I/O PSC word. bit 10 = 0 Modify or load processor PSC word. Bit 11 specifies the PSC word which will control the next instruction as follows:

bit 11 = 1 1/0 PSC word has control. bit 11 = 0 Processor PSC word has control.

Bits 12 and 13 control the Alter and Display functions as follows:

bit 12 = 1 Alter and Display will be restricted to location 4. bit 13 = 1 Remove restriction.

If both bits are zero, the alter state is unchanged. If both are ones, the result is unpredictable.

## Store State:

SPSC

OP Code AO

This instruction will store the PSC word in the memory position designated by  $B_1-D_1$ . The PSC that is stored is determined by bit 10 where a O specifies processor PSC and a 1 specifies I/O PSC. For storing PSC, the storage area specified by B-D must have a halfword boundary.

Supervisor Request Call:

OP Code A1

SRC

This instruction stores the I bits in the SRC portion of the I/O PSC and sets interrupt request. Fields  $B_1-D_1$  in this instruction are ignored. Note that the interrupt will be granted immediately when operating in the processor PSC but will be stored if in the I/O PSC. The acceptance of this interrupt request will not cause a channel number or any status information to be stored.

## INPUT/OUTPUT CONTROL

There are various sets of memory locations assigned for use with input/output control units. Each set consists of an area of memory (called a Buffer Control Word) which is used for storing data storage addresses and character counts, where applicable, and other details pertaining to the specific input/output function performed.

INPUT/OUTPUT PROGRAM PROCEDURE:

Input/output control requires the following software steps:

- Load the proper Buffer Control Word with the necessary information required by the control unit, provided the unit is not busy.

- 2. Issue an input/output instruction which specifies the device address and the function to be performed.

- 3. Test the Condition Indicator to determine if the instruction was accepted.

- 4. Test the status of the device when the operation is completed (normally indicated by the generation of an interrupt) to determine if the operation was successful.

Input/output instructions all use the SI format in which the I portion is used to specify the Device Address. The  $B_1-D_1$  portion of the instruction functions in the normal manner, either allowing indexing or direct addressing.

## INPUT/OUTPUT INSTRUCTION:

Execute 1/0:

XIOF

OP Code A4

| A 4 | Ď1  | <sup>B</sup> 1 | D <sub>1</sub> | FS  | Н   |     |

|-----|-----|----------------|----------------|-----|-----|-----|

| 07  | 815 | 16-19          | 20             | 24- | -27 | —31 |

This instruction is used to initiate a function on the device specified by the Device Address (DA). The Buffer Control Word associated with the device must have been loaded with the information required by the particular device. The Function Specification (FS) defines the type of operation to be initiated. Some devices require part of the FS to be placed in the Buffer Control Word. The H bit of the FS(27) is reserved to inhibit the generation of all interrupt requests when the operation ends.

The execution of an XIOF instruction sets the condition codes as follows for the basic peripherals (card reader, printer and punch): A device is "BUSY" from the time of acceptance of one 1/0 instruction until an Interrupt Request is granted or is reset by Test 1/0. If an XIOF is not accepted, a TIO will store the status to indicate why.

When an interrupt is granted, the indicators of the device are reset, and the status of the device is stored in memory location DS. The device number is stored in memory location DA.

On a Test I/O instruction (TIO) the status byte is stored in the memory location specified by  $B_1-D_1$ .

| <del>&lt;</del>                    | Busy                               | >                                                                                      |

|------------------------------------|------------------------------------|----------------------------------------------------------------------------------------|

| < Working                          | >                                  | Available - Waiting for<br>Interrupt to be granted                                     |

| lssues 1/0<br>Instruction          | I/O Interrupt<br>Request Generated | Interrupt Accepted or<br>Test I/O Clears Request                                       |

| Test I/O yields Busy<br>indicators | does not reset                     | I/O Order Rejected                                                                     |

| 1/0 Order Rejected                 | ~                                  | Test I/O Stores Status<br>and Resets Indicators<br>Plus Clearing Interrupt<br>Requests |

|                                    |                                    |                                                                                        |

Timing Diagram of a General Peripheral Cycle

Test I/O Status

TIO

OP Code A5

This instruction tests the peripheral specified by the Device Address. The status of the addressed unit is stored at the address specified by  $B_1-D_1$ . This instruction clears the device status storage for the device if it is not working. It should be noted that interrupt request is part of the device status and will be cleared by this instruction. If the device is working, then status will not be reset. The instruction sets the following condition codes on basic peripherals:

### GENERAL PURPOSE INPUT/OUTPUT CHANNEL

The General Purpose Input/Output Channel feature provides an interface to which devices other than the basic reader, printer and punch may be attached. The channel allows attachment of eight control units, each capable of controlling eight devices. The channel operates at 100,000 bytes per second in a multiplex mode. Each control unit receives input or output servicing for one character time.

The channel accepts 1/0 instructions from the CPU and generates the initial selection sequence required to control and test control units and their associated devices. The channel will generate the necessary sequences to respond to the various requests of the CPU. The UNIVAC 9200/9300 memory, registers and arithmetic circuits are shared by the General Purpose 1/0 Channel.

#### CHANNEL ADDRESSING:

Execute 1/0 and Test 1/0 operations:

When execute or test 1/0 instructions are issued to devices <u>other</u> than the basic peripherals (Device Address  $\neq 1, 2$  or 3) and the channel feature is present, the channel will attempt to execute the Initial Selection Sequence or 1/0 Command. If the addressed device is off-line or does not exist the channel will reject the command and produce an error condition code.

#### Subchannels:

A subchannel is required to sustain a data transfer operation concurrently with other data transfer operations. The subchannel is part of the General Purpose Input/Output Multiplexer Channel. The Multiplexer Channel is capable of handling data transfer operations from several concurrently operating subchannels so long as the maximum system data rate is not exceeded and no device is monopolizing the interface by operating in burst mode.

Devices operating in burst mode monopolize the channel facilities by holding the channel active for the duration of an entire Input/ Output operation. Once the channel has assumed control over the time shared Central Processor, the UNIVAC 9200/9300 may not be accessed, until the channel is freed. Basic peripherals may transfer data in burst mode but the UNIVAC 9200/9300 processor is effectively locked out during this interval.

#### BUFFER CONTROL WORDS:

Each Subchannel requires a four-byte Buffer Control Word (BCW) in the main memory. The BCW's contain initial and working data counts, data addresses and control bits. <u>The program must load the proper</u> <u>BCW with the proper initial conditions before issuing any EXECUTE</u> <u>1/0 order to any subchannel. Note also that program modifications of the</u> BCW of a working Subchannel is a delicate matter. Eleven BCW's have been reserved for the channel (Memory locations  $84 - 127_{10}$ ). The channel therefore may have eight Subchannels. Note that the channel may also use the BCW's allotted to Basic peripherals if these are not present in some systems.

Device, Control Unit & Subchannel Numbering:

Control Units may be assigned any appropriate address or group of addresses at installation time. The channel recognizes two Device Address formats, one for <u>shared subchannels</u> and one for <u>non-shared</u> <u>subchannels</u>. Devices that share a Control Unit and are not able to transfer data concurrently may share a subchannel. A subchannel may be shared by up to eight devices. A shared Control Unit with more than eight devices would require at least two subchannels.

Devices operating through <u>Non-shared</u> Subchannels have addresses with the binary format:

0000SSSS where SSSS is the subchannel address.

Devices sharing subchannels have addresses with the binary format:

1SSSSdddd where SSSS is the Subchannel number and dddd is a particular device number.

BCW Location:

The location of the most-significant Byte (BCOO) of Subchannel N is memory location  $64_{10} + 4N$ , where N = SSSS (000 0000 01SS SSOO in binary).

Status Byte Format:

During Initial Selection, occurring on EXECUTE 1/0 or TEST 1/0, and on termination of 1/0 operations, Control Units present a STATUS BYTE with the following format:

> Bit 0 - Attention 1 - Status Modifier 2 - Control Unit End 3 - Busy 4 - Channel End 5 - Device End 6 - Unit Check 7 - Exception

This status byte is stored in program-specified locations on Test 1/0 instruction and in location  $66_{10}$  when the channel is allowed to interrupt the program.

Condition Code Summary:

When an EXECUTE I/O or TEST I/O Instruction is issued via the channel the result of the operation is summarized in the Condition Code placed in the appropriate Program State Control area.

| CC<br>Code | EXECUTE 1/0                                                                                                                                                                           | TEST I/O                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 00         | Command Accepted<br>No channel error<br>STATUS Byte all<br>zero except for end bits.<br>(Status = 0000,XX00)                                                                          | Device Available<br>No Channel Error<br>Status Byte = 0000,0000                                             |

| 10         | Device, Control Unit<br>or Channel Busy<br>Command Rejected<br>No Channel Error<br>STATUS, if any,<br>all zeros except Busy or<br>Busy & Status Modifier Bits<br>(Status - 0X01,0000) | Device, Control Unit, or<br>Channel Busy.<br>No Channel error.<br>Status, if any, = 0X01,0000               |

| 01         | STATUS PENDING<br>Command Rejected<br>No Channel Error<br>Status other than<br>Busy or End bits.<br>Status ≠ 0X01,0000<br>or 0000,XX00                                                | NON-ZERO STATUS STORED<br>and Cleared.<br>No Channel Error<br>Status other than Busy.<br>Status ≠ 0X0X,0000 |

| 11         | Device Control Unit<br>or Channel<br>NOT OPERATIONAL<br>Probe return or<br>Channel-detected Error                                                                                     | Device, Control, or<br>Channel NOT operational.<br>PROBE RETURN or<br>Channel-detected Error.               |

Note that the channel may be momentarily busy on rare occasions, having just committed itself to a Service Request sequence as the 1/0 instruction was being staticized.

Note also that a programming error, namely addressing a non-existent device, can generate the 11 condition code.

Buffer Control Word Formats:

When a Control Unit initiates a sequence in order to request or present data or to present a status byte, the Control Unit presents a Device Address along with appropriate control signals. This address is placed in the channel's Device Address Register where it is used to determine the location of the proper BCW. The action taken by the channel depends upon the contents of the BCW. The normal BCW format is shown below:

| WMT | ВΥ    | /TE COUNT<br>(13 bits) | 0 | DATA    | ADDRESS<br>(15 bits) |

|-----|-------|------------------------|---|---------|----------------------|

| E   | 3000  | BC01                   |   | BC10    | BC11                 |

| 6   | 54+4N | 64+4N+1                | 6 | 54+4N+2 | 64+4N+3              |

Basic Format: WM ≠ 11

W - Data Direction Bit

Loc.

W = 0 for Read: (input) operations.

M - Addressing Mode Bit

M = 0 for forward  $(A + 1 \Rightarrow A)$  Sequence.

M = 1 for backward (A-1  $\Rightarrow$  A) Sequence.

## T - Termination Bit

If T = 1, no data will be transferred, the BCW will

not be modified by the channel and the Termi nate (Function Out) response will be given to

Data Requests.

The Channel will set T = 1 after the transfer of a byte of data causes the Byte Count to go to zero. The channel will <u>not</u> erase a T bit.

Byte Count: This field is decremented by the channel whenever a byte of data is transferred. An initial count of zero gives a block length of 8192 bytes if T = 0.

Note that a Control Unit may terminate an operation before the count becomes zero. On termination this field indicates the difference, if any, between the initial Byte Count and the number of bytes actually transferred.

Data Address: This field is fetched by the channel and used as the address for the current byte of data. The address is modified in the BCW under control of the M bit in preparation for the next byte. On termination this field indicates where the next byte would have gone had the operation continued (last address  $\pm$  1).

Note the necessity for agreement between the W and M bits and the 1/0 command initiated via the subchannel.

#### ALTERNATE BCW FORMAT:

This alternate Format (LT Format) is provided so that the system can handle devices that transfer a continuous stream of data at relatively low speeds, more specifically Communications Line terminals for remote inquiry stations, computer-to-computer transmissions, etc. The main variation is the fixed-length wrap-around buffer addressing sequence which could be called a limited form of data chaining. This operation is defined by <u>program</u> and not by any device characteristic. The LT format, described below, is specified when the W and M bits are both ones, which would specify "write backwards" in the normal format.

| LT BCW | Format |  |

|--------|--------|--|

|--------|--------|--|

| 11TB | <u>Status</u><br>4 5 6 7 | К    | 0 | DATA /<br>8 bits<br>fixed | ADDRESS<br>7 bits<br>variable |

|------|--------------------------|------|---|---------------------------|-------------------------------|

| BCOO |                          | BC01 |   | BC10                      | BC11                          |

T - Terminate Bit

If T = 1 no data will be transferred, the Data Address will not be modified, the channel will give the Terminate response to Data Requests. The channel will set T = 1 when "Wrap-around error" occurs (see B Bit below). The channel will not erase a T bit.

B - Buffer End Bit

When the address modification generates a carry from the 2<sup>5</sup> bit position of the data address (when the address is modified to an integral multiple of 64<sub>10</sub>) the channel sets the B bit to one and generates on LT Summary Interrupt Request. The B bit alerts the program that a 64 byte buffer segment has ended. The program is expected to remove the B bit when the buffer segment is ready for use by the channel again. If the channel finds a B bit remaining in the BCW when the End of Buffer Segment occurs again, the channel sets the T Bit to one so that the data will not be overlaid. This is the "Wrap-Around error" situation. The channel will not erase a B bit.

Data Address: This field contains the address of the next data byte to be transferred. The address modification in the LT format is always  $A + 1 \rightarrow A$ , Mod 128. This sequence, with the B-bit, gives the effect of alternating the use of two adjacent 64-byte buffer areas.

Status Field: When a device operating in the LT mode initiates a sequence to present status, bits 4 - 7 of the Status Byte are merged (OR function) into this field. If the CPU allows the Interrupt the entire status byte is also placed in the Interrupt Entry area and the LT summary Interrupt Request is reset. If the Interrupt is not allowed the LT Summary Interrupt Request is set.

K Field - Address trap: If a device operating in the LT mode attempts to present status and bits 4 and 5 in the status field of the BCW were previously both zero, the 8 least significant bits of the Data Address are transferred to the K field. If either bit 4 or bit 5, in the BCW was previously a one the transfer does not occur.

Data Direction Control: No control bits are provided in this format for data direction. In the LT format oddnumbered devices are assumed to be executing Input operations, even-numbered devices are assumed to be executing Output operations. The data direction is controlled by the least-significant bit of the device address transmitted at the beginning of the Control Unit initiated sequence. BAR PRINTER, 250 LPM:

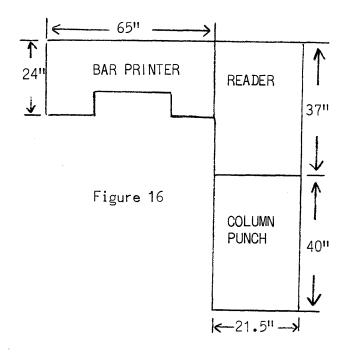

The line printer operates at 250 lines per minute with a 63character font. The paper-skipping speed is 25 inches per second. Paper spacing is controlled by program with a paper loop. Line spacing is six to the inch. Horizontal spacing is ten characters to the inch. The printer is assigned a reserved area of memory for storage of data to be printed, and it will print only from this area. The printer will use only the low-order six bits of each byte and will scan for printing the 96 (9200 only), 120, or 132 characters within its reserved memory area.

Options to this basic printer are:

- 1. Expansion of the number of print positions from 96 to 120 or 132.

- 2. A replaceable character font of 48 printable characters which will allow 16 numeric and special characters to be printed at 500 LPM on the basic 250 LPM printer. This font will require program translation.

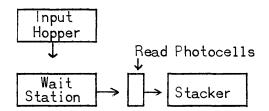

CARD READER, (400 CPM-COLUMN)

The card reader included with this system operates at 400 cards per minute. The unit has four functional stations: input hopper, read wait, read, and stacker. The hopper capacity is 1200 cards, and the stacker capacity is 1500 cards. Reading is accomplished on a demand cycle with only one card committed at a time. A full 80 columns will be read during each read cycle at all times unless the card is a stub card.

Data may be presented to the processor in two formats: compressed mode and image mode.

Options to the basic reader are:

- 1. 51 column stub card feature

- 2. 66 column stub card feature

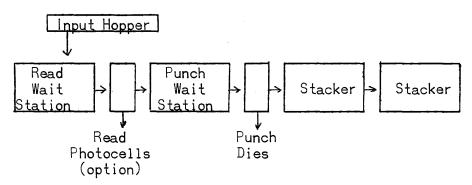

CARD PUNCH 75 to 200 CPM:

The card punch provides the means of punching cards in compressed or binary image mode in a serial or column-by-column manner. The unit has six functional stations: input hopper, ready, wait, punch, and output stackers. The input hopper has a capacity of 1200 cards, and the output and reject stackers have a capacity of 850 and 850 cards, respectively. The speed varies from 75 to 200 cards per minute depending upon location of the last column punched. Punching always starts at the first column. Punched data is (echo) checked. The card punch will be able to handle cards scored for subsequent separation into stub cards.

A pre-punch read station is available as an option to permit reading and punching along the same card path.

Stacker select is performed automatically by the hardware for error cards; however, program-controlled stacker select is available as an option.

The card punch may be omitted from this system.

Card Code Translation (80 Column Card):

When an 80 column card is read or punched with hardware compression, the hardware compression is to or from an 8-bit code in memory. This 8-bit code is not one of the internal processing codes and requires program translation to be processed after a card is read into memory and a program retranslation to generate the 8-bit code for punching a card. The hardware translation of row punches in the 80 column card to or from an 8-bit code are shown in the following table.

Row Punched holes

Punches in rows 1 through 7 generate the following bit combinations

|    | Bi    | ts | <u>123</u> |

|----|-------|----|------------|

| No | Punch | =  | 000        |

| 1  | 11    | =  | 011        |

| 2  | 11    | =  | 101        |

| 3  | 11    | Ξ  | 001        |

| 4  | 11    | =  | 010        |

| 5  | 11    | =  | 100        |

| 6  | 11    | ₽  | 111        |

| 7  | 11    | =  | 110        |

If more than one row punch from 1 through 7 is present on a card, the combined codes will be OR'ed together; thus, a 2 and a 5 punch will appear to have been a 2 punch.

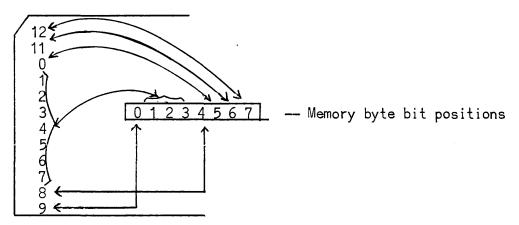

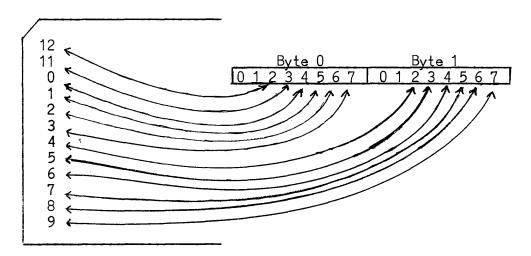

#### Card Code Image Mode:

When an 80 column card is read or punched in the image mode, the twelve possible punched holes of a column are represented by 1's in two bytes of memory. As shown in the diagram, bit positions 0 to 1 are unused in the image mode. When punching the image mode one's in bit position 0 to 1 will be ignored. When reading or punching in the image mode the 80 columns of the card occupy 160 bytes of memory. These 160 bytes are consecutively occupied by 2 bytes for each consecutive column in a card starting at column 1. Bits 0 and 1 of the data bytes will be cleared to zeros on an image read.

Internal Codes:

There are 256 possible code combinations that can be represented by any eight bit byte of memory. As described in a previous subsection, card code translation is to or from a compressed code. This compressed code generated by the card reader must then be translated to the desire internal code for processing and retranslated from the internal code to the compressed code for punching. There are two sets of internal codes which are subsets of the 256 possible code combinations which will be used to select the two bar printer graphics. Figures 1 and 2, following, contain the 63 character print set and the 48 character print set.

23

4567

10

Q

R

S

Т

U

٧

W

Х

Y

Ζ

+

&

%

#

9

11

0

1

2

3

4

5

6

7 8

9

•

\*

\_

|      | 00      | 01       | 10           | 11            |

|------|---------|----------|--------------|---------------|

| 0000 |         | ρ.       |              | 0             |

| 0000 | NP<br>A | <u>ل</u> | -            | <u>0</u><br>1 |

| 0010 | В       | K        | S            | 2             |

| 0011 | С       | L        | Т            | 2<br>3        |

| 0100 | D       | М        | U            | 4             |

| 0101 | E       | N        | V            | 5             |

| 0110 | F       | 0        | W            | . 6           |

| 0111 | G       | Р        | X            | 7             |

| 1000 | H       | Q        | Y            | 8             |

| 1001 | 1       | R        | Ζ            | 9             |

| 1010 | ¢       | <b>!</b> | $\backslash$ | :             |

| 1011 | •       | \$       | 9            | #             |

| 1100 | <       | *        | %            | . @           |

| 1101 | (       | )        | _            | 1             |

| 1110 | +       | ;        | >            | Ξ             |

| 1111 |         | -1       | ?            | Ħ             |

|      | 00 | 01 |

|------|----|----|

| 0000 | A  | NP |

| 0001 | В  |    |

| 0010 | С  |    |

| 0011 | D  |    |

| 0100 | E  |    |

| 0101 | F  |    |

| 0110 | G  |    |

| 0111 | Н  |    |

| 1000 |    |    |

| 1001 | J  |    |

| 1010 | K  |    |

| 1011 | L  |    |

| 1100 | M  |    |

| 1101 | N  |    |

| 1110 | 0  |    |

| 1111 | Ρ  | NP |

# Figure 14

63 Character Graphic Set assigned to the six bit printer synchronizer code. Figure 15

48 Character Graphic Set assigned to the six bit printer synchronizer code.

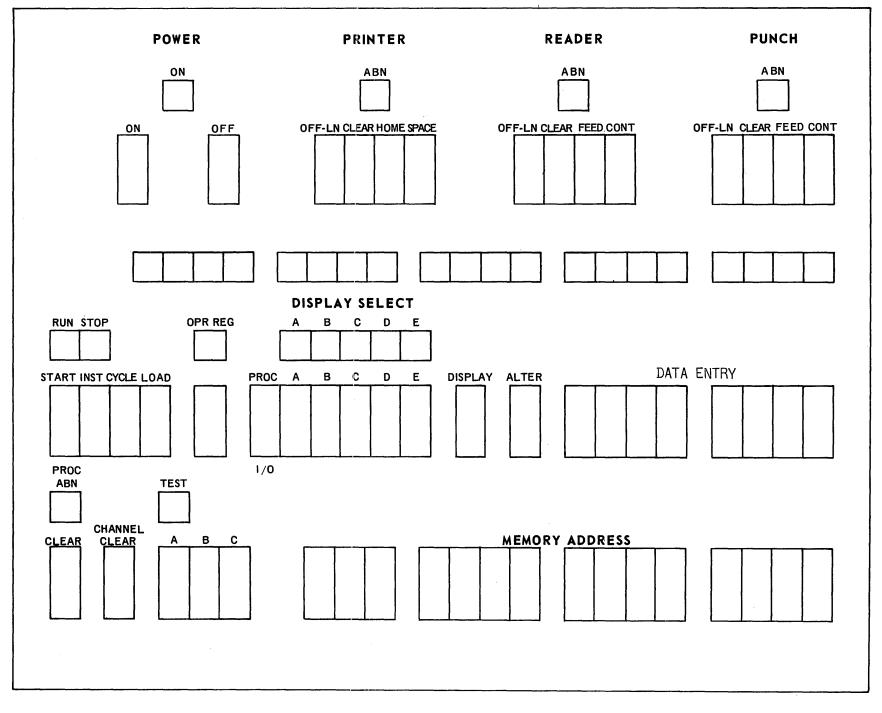

#### IND IV IDUAL PERIPHERAL CONTROL REQUIREMENTS

Each peripheral unit associated with the processor, whether attached as a basic unit or by way of the general purpose channel, has unique control requirements.

#### PRINTER:

The printer's sequence of the operation is to print and then advance paper. To allow the maximum amount of time to prepare the next line of data and to store it in the specified print area, interrupt is generated and the next XIOF can be issued before the paper advance operation is completed from the last XIOF instruction.

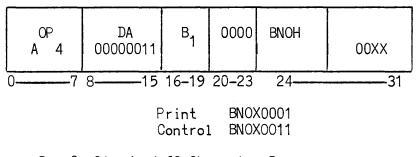

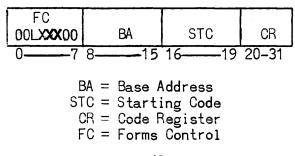

The printer Execute 1/0 instruction has the following format:

- B = 0 Standard 63 Character Bar

- B = 1 Optional 48 Character Bar

- N = 1 Print Numeric if 48 Character Bar option is activated

- H = 1 Inhibit all interrupts

There are only two valid print instructions, print and control, the Bar selection is a modifier to these codes and is only effective if the Bar Print option has been included as part of the active system. Any other codes will cause invalid operations. Print may be given with or without paper advance. Control is used for paper feeding without printing.

Processing will continue during all 1/0 instructions. If the H bit is set to one all interrupts from the device will be inhibited. The TIO instruction should then be used to determine the status of the device.

The buffer control word for the printer contains the following data:

Software does not load CR, STC, or BA because these three bytes are under complete hardware control. If they are inadvertently changed by a program, a loss of printer control will probably result.

The Forms Control byte is loaded by the program once it has been determined either by a TIO or an interrupt that it is permissible. The Forms Control byte will not be changed by the execution of a printer function. The four bits which designate the desired forms action as follows:

> L X X X 0 0 0 0 Space 0 lines 0 0 0 1 Space 1 line 0 0 1 0 Space 2 lines 1 X X X Select any of 7 paper loop channel controls by matching holes in the paper loop to the 1 bits in the X bits.

There are two paper loop conventions:

X X X 1 1 1 for home paper 0 0 1 for form overflow

If a hole combination is sought under paper loop control that is not punched on the tape, a runaway paper condition will result.

The status byte contains information pertaining to the result of the last issued order or the next to last issued order. The status indications are as follows:

| 1. | A11 | zeros | = No | indicators | set; | function | performed |

|----|-----|-------|------|------------|------|----------|-----------|

|    |     |       | as   | specified. |      |          |           |

- 2. Bit 7 set to 1 = Paper Low\* as a result of paper spacing. Until the paper condition is corrected, this indicator will occur for each XIOF. Paper low will be indicated when the bottom edge of the form is 15 1/3" ± 1/3" from print line.

- 3. Bit 6 set to 1 = Form overflow\* 001 sensed at paper loop station, while single or double spacing.

- 4. Bit 5 set to 1 = Interrupt request pending. This status bit is only set if the TIO function clears a pending interrupt before it is accepted. This status bit does not indicate an error.

Bit 4 set to 1 = Instruction does not agree with bar switch setting.

Bit 3 set to 1 = Data Parity or Control Parity error on last XIOF instruction - stops printer immediately.

Bit 2 set to 1 = Memory overload occurred on last XIOF instruction - stops printer immediately.

Bit 1 set to 1 = Paper Runaway\* - Forms Control lost. No further orders will be accepted without operator intervention.

Bit 0 set to 1 = Abnormal or Not Ready

\* These conditions are recognized following the normal interrupt request, therefore the previous function will be properly completed except in the case of Paper Runaway where paper has been spaced improperly. If another XIOF has already been accepted it will be aborted and an interrupt will be generated. If the next XIOF is not issued until after detection of the condition, the order will be accepted, then aborted and an interrupt request will be generated. Any error that happens before paper is advanced will void paper advancing.

Interrupt requests will occur at the following times:

- 1. End of print before associated paper feed is started.

- 2. Immediately following an accepted paper feed order before paper advancing has begun, unless a previously initiated paper feed order is in progress. In this case the interrupt is delayed until the previously initiated paper feed order has been completed.

- 3. Upon the abortion of an order due to detection of Paper low, Forms overflow, or Forms Runaway as a result of a preceeding order.

- 4. Upon termination of an operation due to any other error condition.

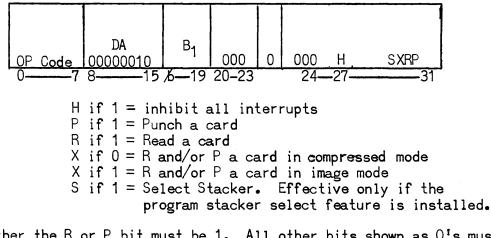

CARD READER INSTRUCTION CONTROLS:

The card reader test 1/0 instruction performs normally as described in the general section on the TIO instruction.

The Execute 1/0 instruction for the card reader has the following format:

| OP Code | DA<br>00000001                | <sup>B</sup> 1 | 0000                       | 000  | Н   | 0X10 |

|---------|-------------------------------|----------------|----------------------------|------|-----|------|

| 07      | 815                           | 16-19          | 20-23                      | 24-  | -27 | 31   |

|         | ОООНОО1О<br>ОООНО11О<br>Н = 1 | Read           | Trans]<br> mage<br>pit all | Mode |     | 3    |

These two combinations of bits, in the direct  $B_1-D_1$  field or the indexed  $B_1-D_1$ , are the only permissible combinations of reader XIOF instructions. Any other combination may cause an error.

Processing will continue during all 1/0 instructions. If the IH bit is set to one all interrupts from device will be inhibited. The TIO instructions should then be used to determine the status of the device.

The buffer control word for the card reader contains the following data:

| HTS | Col. | Base | Address |

|-----|------|------|---------|

| 07  | 815  | 1623 | 2431    |

- HTS = Hardware temporary storage reserved for the reader. This Byte should not be loaded by the program.

- Col. = The number of columns to be read. This must always be 80. At the end of a card operation this count will be decremented to zero.

- Base Address = The starting address where the card will be read into. This must always be an even address. At the end of a card operation this address will point to the Byte immediately following the last Byte of information read from the card.

The status byte contains information pertaining to the result of the last issued order or the next to last issued order. The status indications are as follows:

- 1. All zeros = No indicators set, function performed as specified.

- 2. Bit 5 set to 1 = Interrupt request pending. This status bit is only set if the TIO function clears a pending interrupt before it is accepted. This status bit does not indicate an error.