# **MEMORY PROTECTION**

an option for the Varian Data Machines 620/f Computer System

Specifications Subject to Change Without Notice

varian data machines/a varian subsidiary © 1971

98 A 9908 490

98 A 9908 490

**JULY 1971**

#### **FOREWORD**

The 620/f Memory Protection Manual defines and explains the logical, electrical, and mechanical parameters that control and interface between a Varian Data Machines 620/f computer and the memory protection option.

The six sections of the manual:

- Introduce the memory protection option in relation to the system

- Describe its installation and interfacing

- Give a detailed theory of operation

- Describe testing and troubleshooting procedures for maintaining it in the field

- · Reference all hardware wirh drawings, parts lists, and wire lists

|  |  |  |  | (           |

|--|--|--|--|-------------|

|  |  |  |  |             |

|  |  |  |  |             |

|  |  |  |  | (           |

|  |  |  |  |             |

|  |  |  |  | (           |

|  |  |  |  |             |

|  |  |  |  | (           |

|  |  |  |  |             |

|  |  |  |  |             |

|  |  |  |  | ii yagan ii |

|  |  |  |  |             |

## CONTENTS

# TABLE OF CONTENTS

| SEC                      | INTRODUCTION                                                          |     |

|--------------------------|-----------------------------------------------------------------------|-----|

| 1.1<br>1.2<br>1.3<br>1.4 | System Overview Functional Description Error Sequences Specifications |     |

| SEC                      | TION 2 INSTALLATION                                                   |     |

| 2.1                      | Physical Description                                                  | 2-7 |

| 2.2                      | System Layout and Planning                                            | 2-1 |

| 2.3                      | System Interconnection                                                | 2-1 |

| 2.4                      | Signal Interfaces                                                     | 2-2 |

| SEC                      | TION 3 OPERATION                                                      |     |

## **CONTENTS**

| C | Е | $\boldsymbol{\Gamma}$ | т | 10 | N | 1 |

|---|---|-----------------------|---|----|---|---|

|   |   |                       |   |    |   |   |

## THEORY OF OPERATION

| 4.2       Device Address Decoder       4         4.3       Function Control Logic       4         4.4       Segment Address Register       4         4.5       Mask Register       4         4.6       Segment Address Status Logic       4         4.7       Error Detector       4         4.8       CPU Control Logic       4-1         4.9       Interrupt Request Logic       4-1         4.10       Instruction Address Register       4-1         4.11       A Bus Driver       4-1         4.12       Mnemonics       4-1         4.13       Programming Considerations       4-3         SECTION 5         MAINTENANCE         5.1       Equipment       5         5.2       Test Program       5         5.3       Troubleshooting       5         5.4       Reference Documents       5 | 4.1  | A Bus Receiver               | 4-1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|------|

| 4.4       Segment Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2  | Device Address Decoder       | 4-1  |

| 4.5       Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.3  | Function Control Logic       | 4-1  |

| 4.6       Segment Address Status Logic       4         4.7       Error Detector       4         4.8       CPU Control Logic       4-1         4.9       Interrupt Request Logic       4-1         4.10       Instruction Address Register       4-1         4.11       A Bus Driver       4-1         4.12       Mnemonics       4-1         4.13       Programming Considerations       4-3         SECTION 5         MAINTENANCE         5.1       Equipment       5         5.2       Test Program       5         5.3       Troubleshooting       5                                                                                                                                                                                                                                            | 4.4  | Segment Address Register     | 4-2  |

| 4.7       Error Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5  | Mask Register                | 4-2  |

| 4.7       Error Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.6  | Segment Address Status Logic | 4-4  |

| 4.9       Interrupt Request Logic       4-1         4.10       Instruction Address Register       4-1         4.11       A Bus Driver       4-1         4.12       Mnemonics       4-1         4.13       Programming Considerations       4-3         SECTION 5         MAINTENANCE       5         5.1       Equipment       5         5.2       Test Program       5         5.3       Troubleshooting       5                                                                                                                                                                                                                                                                                                                                                                                  | 4.7  |                              |      |

| 4.10 Instruction Address Register       4-1         4.11 A Bus Driver       4-1         4.12 Mnemonics       4-1         4.13 Programming Considerations       4-3         SECTION 5         MAINTENANCE         5.1 Equipment       5         5.2 Test Program       5         5.3 Troubleshooting       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.8  |                              |      |

| 4.11 A Bus Driver       4-1         4.12 Mnemonics       4-1         4.13 Programming Considerations       4-3         SECTION 5         MAINTENANCE         5.1 Equipment       5         5.2 Test Program       5         5.3 Troubleshooting       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.9  |                              |      |

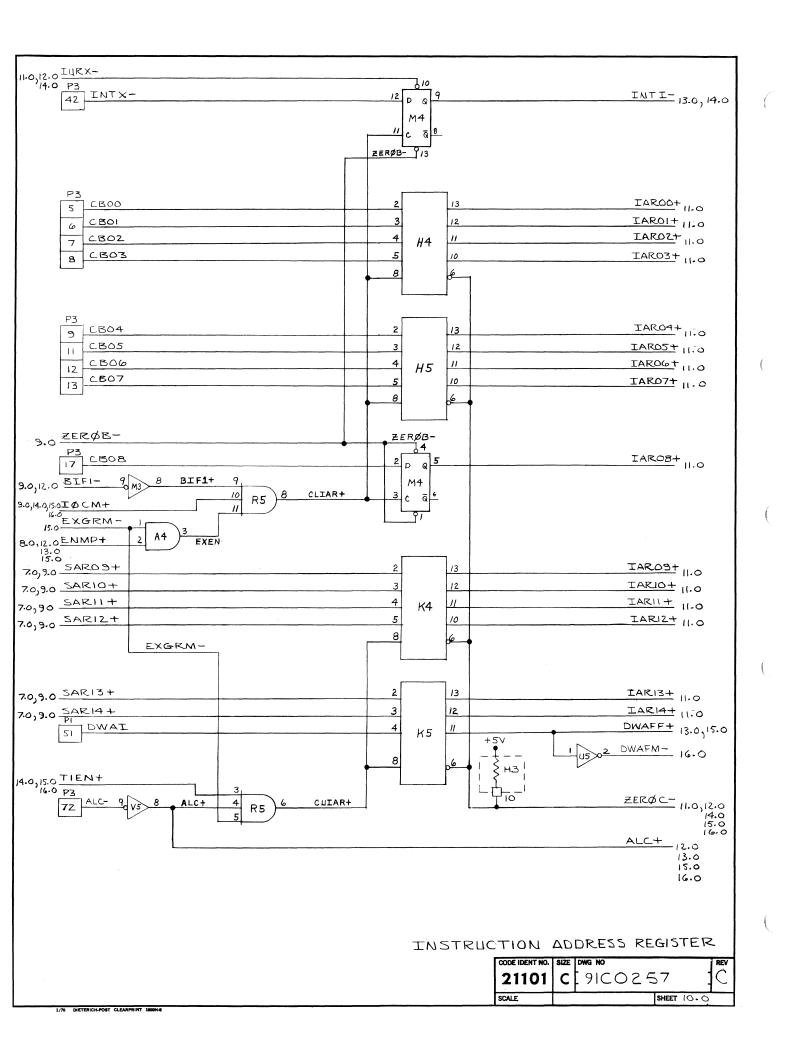

| 4.11 A Bus Driver       4-1         4.12 Mnemonics       4-1         4.13 Programming Considerations       4-3         SECTION 5         MAINTENANCE         5.1 Equipment       5         5.2 Test Program       5         5.3 Troubleshooting       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.10 | Instruction Address Register | 4-12 |

| 4.13 Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.11 |                              |      |

| SECTION 5  MAINTENANCE  5.1 Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.12 | Mnemonics                    | 4-13 |

| MAINTENANCE         5.1 Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.13 | Programming Considerations   | 4-30 |

| 5.1       Equipment       5         5.2       Test Program       5         5.3       Troubleshooting       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SEC1 | TION 5                       |      |

| 5.2Test Program55.3Troubleshooting5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | MAINTENANCE                  |      |

| 5.3 Troubleshooting 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.1  | Equipment                    | 5    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.2  |                              |      |

| 5.4 Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.3  | Troubleshooting              | 5-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.4  | Reference Documents          | 5-8  |

## **SECTION 6**

## DRAWINGS AND PARTS LISTS

## CONTENTS

# LIST OF ILLUSTRATIONS

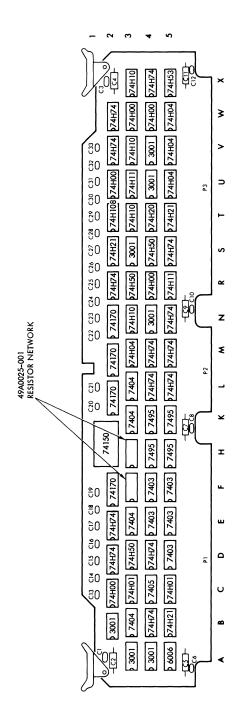

| 1-1 | Memory Assignment example       | 1-2 |

|-----|---------------------------------|-----|

| 1-2 | Memory Protection Block Diagram | 1-4 |

|     | MP Component Layout Assembly    |     |

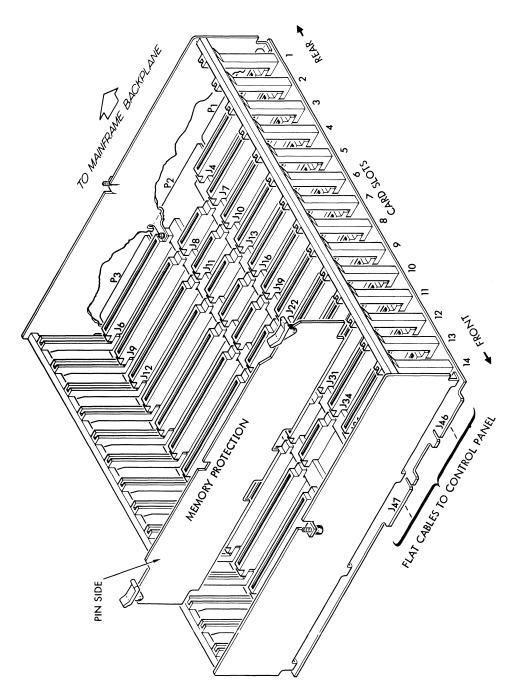

| 2-2 | MP Card Location                | 2-3 |

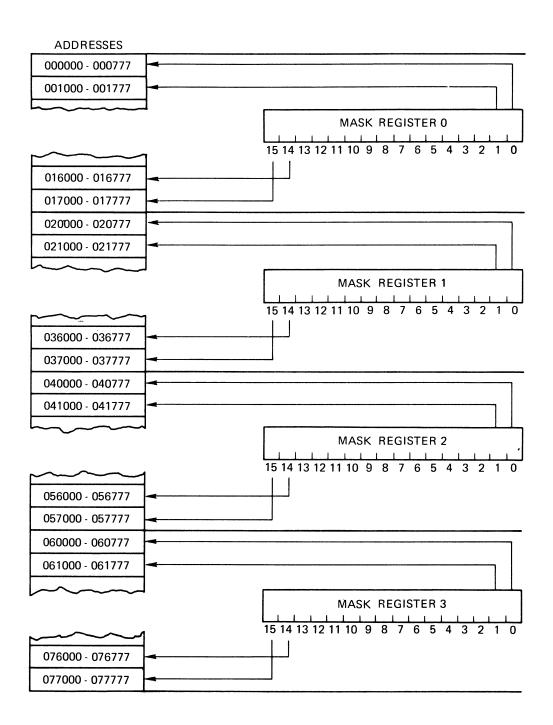

|     | Mask Register Bit Assignment    |     |

| 4-2 | Error Detection Timing          | 4-5 |

|     | <u>-</u>                        |     |

|     |                                 |     |

# **LIST OF TABLES**

| 1 - 1 | Memory Protection Specifications |      |

|-------|----------------------------------|------|

|       | MP Input Interface Signals       |      |

|       | MP Output Interface Signals      |      |

|       | MP Mnemonic Definitions          |      |

| 4-2   | MP Instructions                  | 4-33 |

( ( )

#### 1.1 SYSTEM OVERVIEW

The Model 620/f-05 Memory Protection (MP) is a mainframe option for the Varian Data Machines 620/f computer system. The MP prevents unauthorized entry into and modification of protected areas of core memory by programs residing in unprotected areas.

A single circuit card contains the entire MP. The MP card plugs into the central processing unit (CPU) tray of the computer.

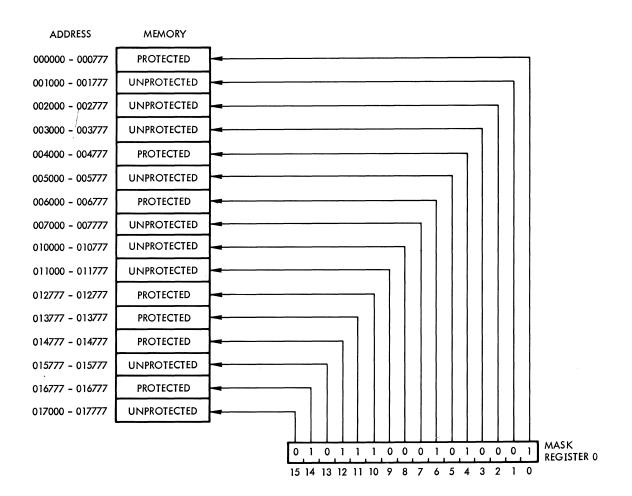

The MP divides core memory into blocks (or segments) of 512 consecutive words. Under program control, these segments can be selectively designated protected. Segments not specifically designated protected are, therefore, unprotected. The MP stores the protected/unprotected status of the segments in four 16-bit mask registers. These registers can store the status of up to sixty-four 512-word segments. Thus, the MP is suitable for use in any 620/f installation, including the maximum 32,000-word (32K) memory system. Figure 1-1 illustrates typical memory segment assignments.

Using the stored memory-segment status, the MP monitors the address of the current instruction and that of the following instruction and the location specified by the effective address to determine error conditions.

When a program is operating from an unprotected segment, the MP detects the following operations as errors:

- a. Program overflow into a protected area

- b. Writing in a protected area

- c. Jumping to a protected area

- d. Executing an I/O instruction in an unprotected area

- e. Executing a halt instruction in an unprotected area

If these operations are attempted, the program aborts and jumps to one of eight preassigned memory addresses. From these addresses, the program can be directed to a user-written subroutine for analysis and correction.

98 A 9908 490 1-1

VT11-1149

Figure 1-1. Memory Assignment Example

#### NOTE

In this manual, numbers beginning with a digit other than zero are decimal numbers, and numbers with a leading zero are octal.

1.2

#### **FUNCTIONAL DESCRIPTION**

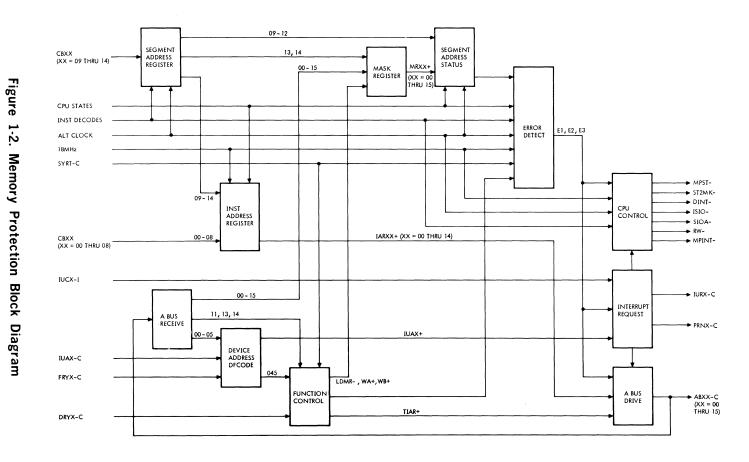

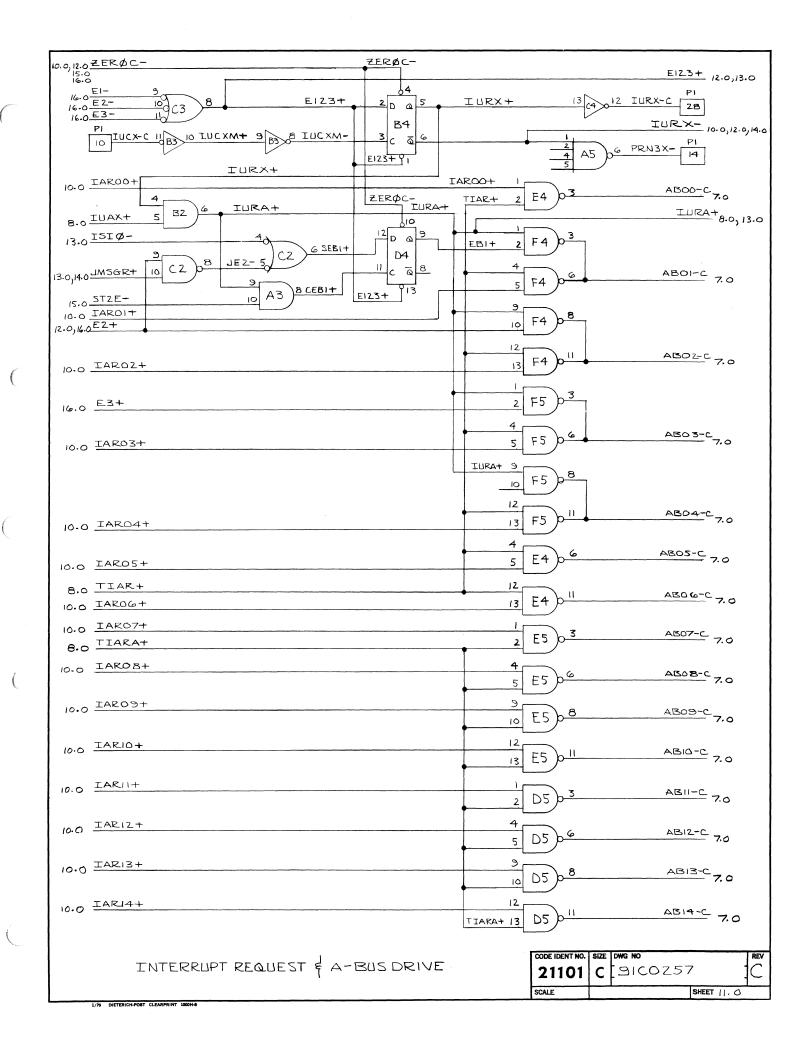

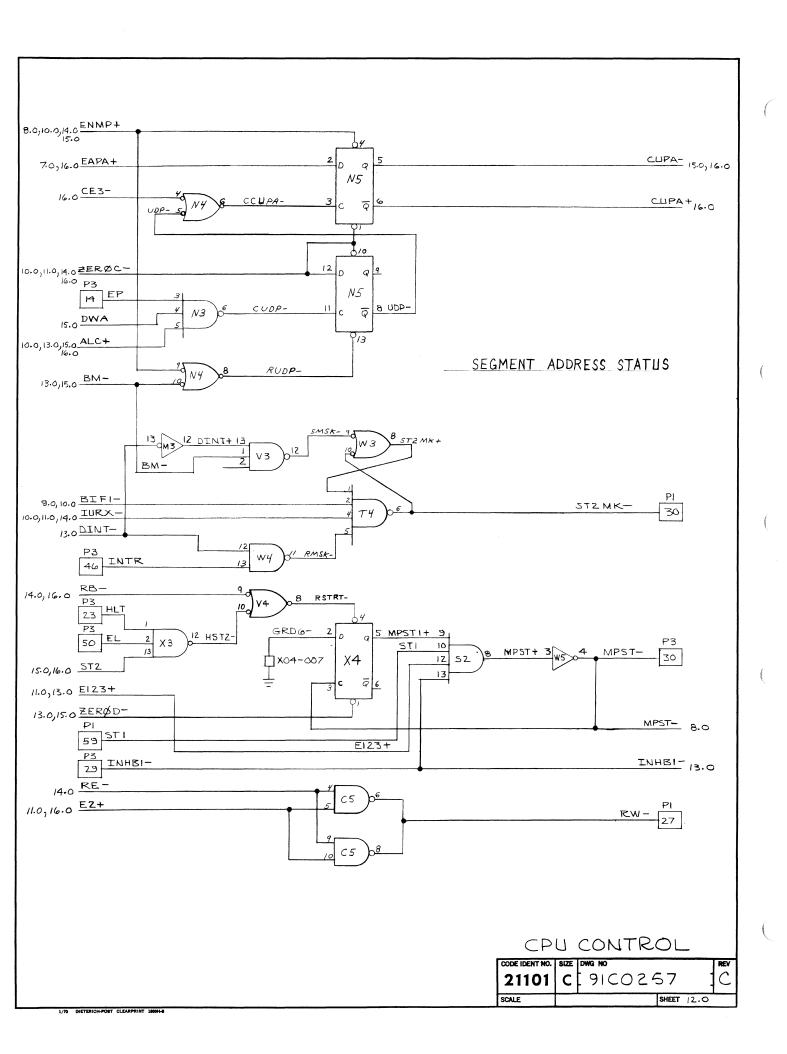

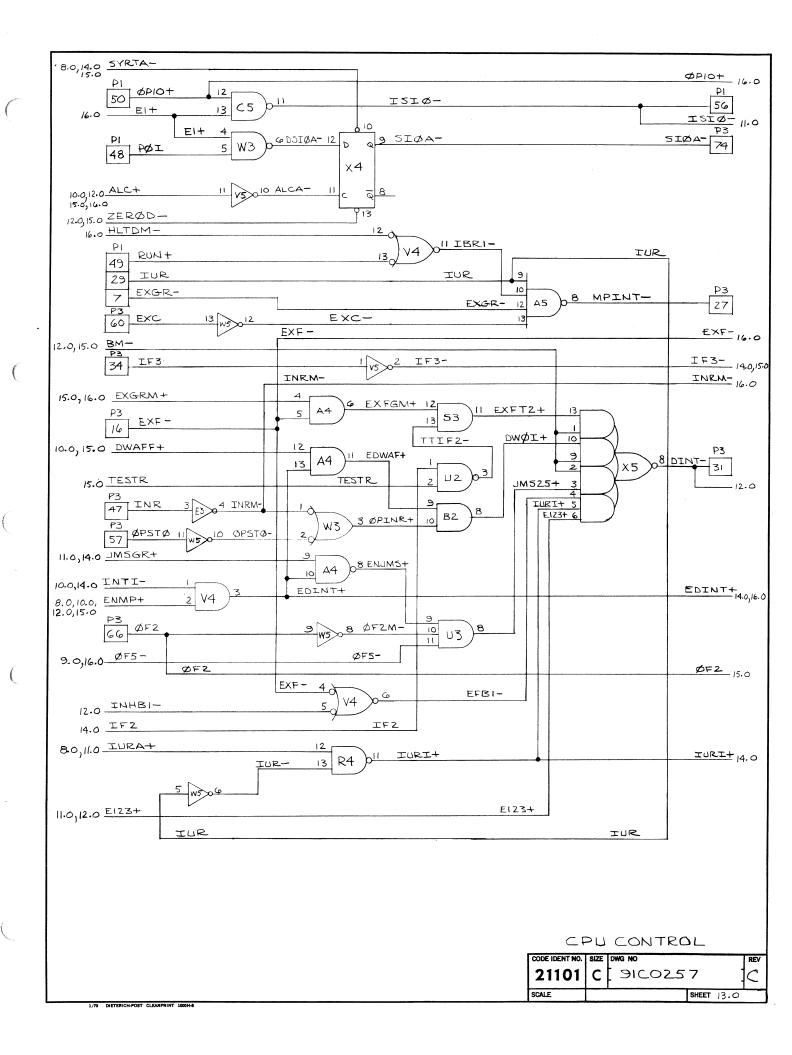

The MP is functionally divided into eleven sections: A-bus receiver, device address decoder, function control logic, segment address register, mask register, segment address status logic, error detector, CPU control logic, interrupt request logic, instruction address register, and A-bus driver (figure 1-2).

#### 1.2.1 A-Bus Receiver

This section buffers the A-bus signals from the CPU and inverts them for use in the mask register, device address decoder, and function control logic.

## 1.2.2 Device Address Decoder

This section decodes MP device address 045 from A-bus lines AB00 – C through AB05 – C and presents the address, with FRYX – C and IUAX – C, to the function control logic for identification of external control and data transfer instructions to MP.

## 1.2.3 Function Control Logic

This section responds to external control and data transfer instructions from the CPU by providing control signals to the error detector, mask register, and A-bus driver.

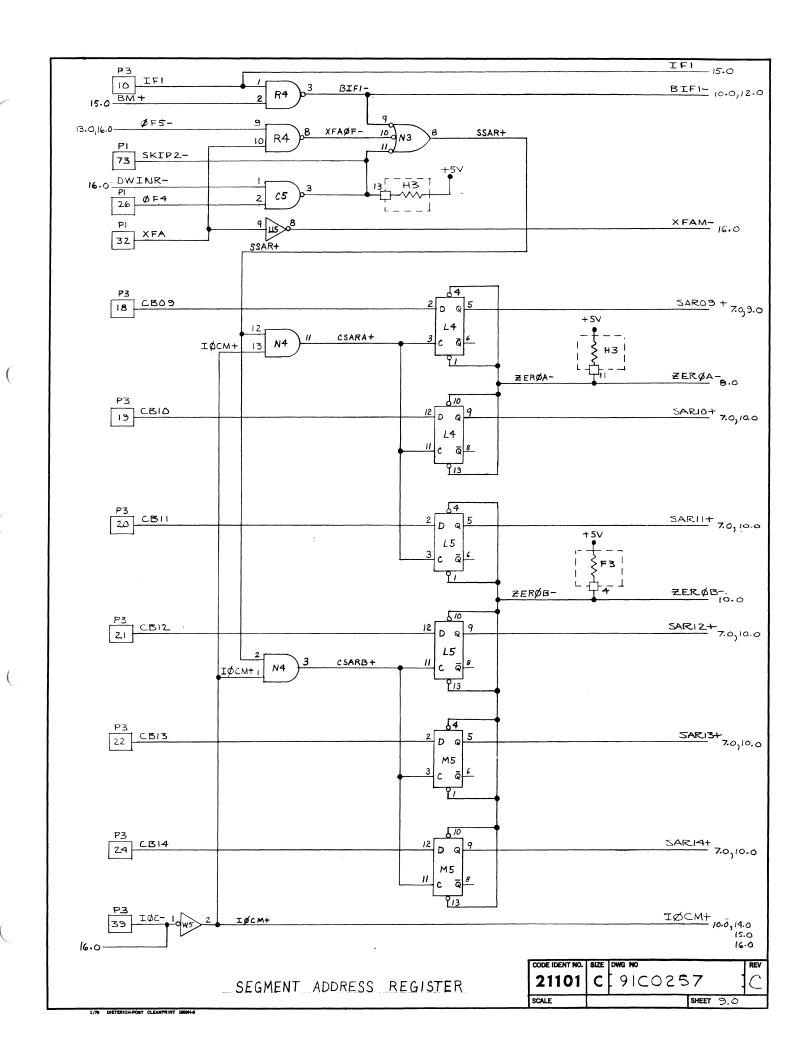

## 1.2.4 Segment Address Register

This section stores the contents of C-bus bits 9-14 for use by the segment address status logic, instruction address register, and mask register. These six bits comprise the memory segment address.

1-4

## 1.2.5 Mask Register

This section stores the status, protected or unprotected, of all segments—of memory. Setting a bit in the mask register protects the corresponding—512-word segment of memory. If a bit is reset, the corresponding segment is unprotected.

During error detection by the MP, mask register outputs, selected by the most significant two bits of the segment address register output, are gated to the segment address status logic.

# 1.2.6 Segment Address Status Logic

This section decodes the least significant four bits of the 16-bit address stored in the segment address register. The result is ANDed with the corresponding status output of the mask register to determine whether the addressed segment of memory is protected or unprotected. The status thus determined is gated to the error detector and represents the status of the effective address or of the current word.

#### 1.2.7 Error Detector

This section detects and stores error conditions as determined by the segment address status logic, CPU state, CPU instruction, and timing. Error conditions remain stored until the resultant interrupt cycle is complete. Section 1.3 defines the MP-detected error sequences.

# 1.2.8 CPU Control Logic

This section generates special signals to control CPU operation during an error sequence.

# 1.2.9 Interrupt Request Logic

This section raises an interrupt request to the CPU when an error is detected by the error detector. It disables lower-priority device controller interrupts during MP interrupt servicing.

## 1.2.10 Instruction Address Register

At the end of each instruction fetch memory cycle, this section stores the contents of the CPU P register plus one. It is continually updated until an error is encountered, at which time the MP is disabled by the resultant error interrupt. Further updates are thus inhibited until an I/O instruction in the error subroutine reenables the MP.

The nine least significant bits of the instruction address register are loaded from C bus bits 0-8. The six most significant bits are loaded from the output of the segment address register.

#### 1.2.11 A-Bus Driver

This section gates the interrupt address to the A-bus during an interrupt. It also gates the contents of the instruction address register to the A-bus during a data transfer in operation.

# 1.3 ERROR SEQUENCES

MP detects the following error types: halt, overflow, I/O, write, and jump.

#### 1.3.1 Halt Error

A halt error occurs if:

- a. A halt instruction located in an unprotected memory segment is executed.

- b. A halt instruction located in any area of memory is executed using an execute instruction that is located in an unprotected segment.

When a halt error is detected, the program completes execution of the halt instruction and the CPU halts after fetching the instruction at the interrupt address. After a 110-nanosecond delay, the MP causes the CPU to enter the run mode, at which time the instruction at the interrupt address is executed.

#### NOTE

MP does not detect a halt error if the halt is caused by pressing the STEP switch on the computer control panel. To prevent inadvertent use of STEP, lock the control panel switches by setting the power switch to PWR ON DISABLE.

## 1.3.2 Overflow Error

An overflow error occurs if a program is operating from an unprotected segment and the P register increments into a protected segment.

#### NOTE

When the last address in an unprotected segment contains the second word of a jump, indexed jump, jump and mark, jump and set return, or bit test instruction for which the jump condition is met, an overflow error does not exist.

When an overflow error is detected, the last instruction in the unprotected segment is executed, even if the second word of a two-word instruction is located in the protected segment. The CPU is then interrupt to address 030.

An I/O, write, or jump error can occur simultaneously with an overflow error.

#### 1.3.3 I/O Error

An I/O error occurs when:

- a. Execution of a one-word I/O instruction or the first word of a two-word I/O instruction from a location in an unprotected segment is attempted.

- b. Execution of an I/O instruction located anywhere in memory is attempted using an execute instruction in an unprotected segment.

When an I/O error is detected, the I/O instruction in process is executed and the CPU is interrupted to address 022 (or to 032 if an overflow error also exists). In all such cases, however, external control instructions and data transfers between the CPU and device controllers are inhibited; thus, the contents of memory and the A, B, and X registers are not modified by the I/O instruction.

#### 1.3.4 Write Error

A write error occurs when an attempt is made to write into a location in a protected area and either the instruction is located in an unprotected area or the instruction is the result of an execute instruction located in an unprotected area. If a write error is detected, the instruction is executed; however, the write cycle is changed to a read cycle. The CPU is then interrupted to address 024 (or to 034 if an overflow error also exists).

## 1.3.5 Jump Error

A jump error occurs when an attempt is made to jump or skip to a location in a protected area and the first word of the jump-type instruction lies in an unprotected area. If a jump error is detected, the instruction is executed; however, the write cycle is changed to a read cycle in the case of a jump-and-mark instruction. The CPU is then interrupted to address 026 (or to 036 if an overflow error also exists.)

## 1.3.6 Intermediate Conditions

In several cases, error detection occurs late in the execution of the instruction or immediately after instruction execution during the forced interrupt wait state. The detection of the error is based in part on conditions existing earlier in the execution cycle and, in the case of execute instructions, before execution is initiated.

Therefore, the following intermediate conditions are detected and stored by the MP:

- a. If a one-word instruction or the first word of a two-word instruction lies in the last address of an unprotected area, the MP sets the W1UP flip-flop during the fetch portion of the execution cycle.

- b. If an execute instruction lies in an unprotected area, the EXUP flip-flop is set 110 nanoseconds after the CPU enters state IF1 of the fetch portion of the instruction to be executed. This condition exists until the fetch portion of the execution of the second instruction following the execute instruction.

## 1.3.7 Multiple Errors

#### 1.3.7.1 ONE-WORD INSTRUCTIONS

Halt, I/O, write, and overflow errors can occur during the execution of a one-word instruction from an unprotected area. Halt, I/O, and write errors are mutually exclusive and cannot occur in combination since they depend on the instruction being executed. However, an overflow error can occur simultaneously with any of them.

When both I/O and overflow errors occur, the overflow interrupt address (030) masks the interrupt address of the I/O error (022), resulting in the composite address of 032.

Similarly, the simultaneous occurrence of write and overflow errors produces the composite address of 034. The overflow error interrupt address (030) masks the interrupt address of the write error (024).

Detection of an overflow error is inhibited during a halt instruction. (Note that a halt error necessarily exists when overflow occurs during a halt instruction.)

#### 1.3.7.2 TWO-WORD INSTRUCTIONS

The following tabulations illustrate possible error combinations during the execution of two-word instructions from an unprotected area.

98 A 9908 490 1-9

Both words in an unprotected area, but neither word is in the last address

| Instruction                                                                                      | Definite Error | Conditional Error                   |

|--------------------------------------------------------------------------------------------------|----------------|-------------------------------------|

| 1/0                                                                                              | 1/0            |                                     |

| Extended write or incre-<br>ment and replace                                                     |                | Write                               |

| Immediate write or incre-<br>ment and replace                                                    |                | Write                               |

| Execution (condition met)                                                                        |                | Halt or I/O, but not simultaneously |

| Jump, jump and mark, in-<br>dexed jump, jump and set<br>return, or bit test (con-<br>dition met) |                | Jump                                |

| Skip if register equal (condition met)                                                           | ·              | Jump                                |

First word in the last address of an unprotected area, second word protected

| Instruction                                                                         | Definite Error | Conditional Error |

|-------------------------------------------------------------------------------------|----------------|-------------------|

| 1/0                                                                                 | Overflow, I/O  |                   |

| Extended read                                                                       | Overflow       |                   |

| Extended write or incre-<br>ment and replace                                        | Overflow       | Write             |

| Immediate read                                                                      | Overflow       |                   |

| Immediate write or incre-<br>ment and replace                                       | Overflow       | Write             |

| Execution (condition met)                                                           | Overflow       |                   |

| Execution (condition not met)                                                       | Overflow       |                   |

| Jump, jump and mark, indexed jump, jump and set return, or bit test (condition met) | Overflow       | Jump              |

| Jump, jump and mark, or bit test (condition not met)                                | Overflow       |                   |

| Skip if register equal (condition met)                                              | Overflow, jump |                   |

| Skip if register equal (condition not met)                                          | Overflow, jump |                   |

Second word in the last address of an unprotected area, next area protected:

| Instruction                                                                                      | Definite Error | Conditional Error |

|--------------------------------------------------------------------------------------------------|----------------|-------------------|

| 1/0                                                                                              | Overflow, I/O  |                   |

| Extended read                                                                                    | Overflow       |                   |

| Extended write or incre-<br>ment and replace                                                     | Overflow       | Write             |

| Immediate read                                                                                   | Overflow       |                   |

| Immediate write or incre-<br>ment and replace                                                    | Overflow       | Write             |

| Execution (condition met)                                                                        | Overflow       |                   |

| Execution (condition not met)                                                                    | Overflow       |                   |

| Jump, jump and mark, in-<br>dexed jump, jump and set<br>return, or bit test (con-<br>dition met) |                | Jump              |

| Jump, jump and mark, or bit test (condition not met)                                             | Overflow       |                   |

| Skip if register equal (condition met)                                                           | Overflow, jump |                   |

| Skip if register equal (condition not met)                                                       | Overflow, jump |                   |

## 1.4 SPECIFICATIONS

The MP functional, physical, and electrical specifications are listed in table 1-1.

98 A 9908 490 1-11

## **Table 1-1. Memcry Protection Specifications**

#### **Parameter**

#### Description

Organization

Consists of A-bus receiver, device address decoder, function control logic, segment address register, mask register, segment address status logic, error detector, CPU control logic, interrupt request logic, instruction address register, and A-bus

driver

Capability

Protects up to sixty-four 512-word memory

segments

Operational Modes

Detects halt, overflow, I/O, write, and

jump errors

Priority Assignment

Always assigned the highest priority with

respect to the DMA/interrupt scheme

I/O Capability

Six external control and eight data transfer

instructions

Timing Sources

18-MHz and 9-MHz clocks from CPU

Logic Levels

Internal

Positive logic:

True:

+2.4 to +5.25V dc

False:

0.0 to + 0.45 V dc

1/0

Negative logic:

True:

0.0 to + 0.45 V dc

False:

+2.4 to +5.25V dc

Size

One 3-by-15-inch (7.7 x 38.1 cm) wired-

socket circuit card

Interconnection

Plugs into slot 12 of the 620/f CPU motherboard

Input Power

+5.0V dc at 2.5 amperes

Operational Environment

0 to 50 degrees C, 0 to 90 percent relative

humidity without condensation

|  |   |  |  |  | ( |

|--|---|--|--|--|---|

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  | ٠ |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  | ( |

|  |   |  |  |  | ( |

|  |   |  |  |  |   |

|  |   |  |  |  | £ |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

|  |   |  |  |  |   |

It is recommended that Varian Data Machines Customer Service engineers install the MP. Logic diagrams, assembly drawings, and wiring information are provided at the time of purchase.

## 2.1 PHYSICAL DESCRIPTION

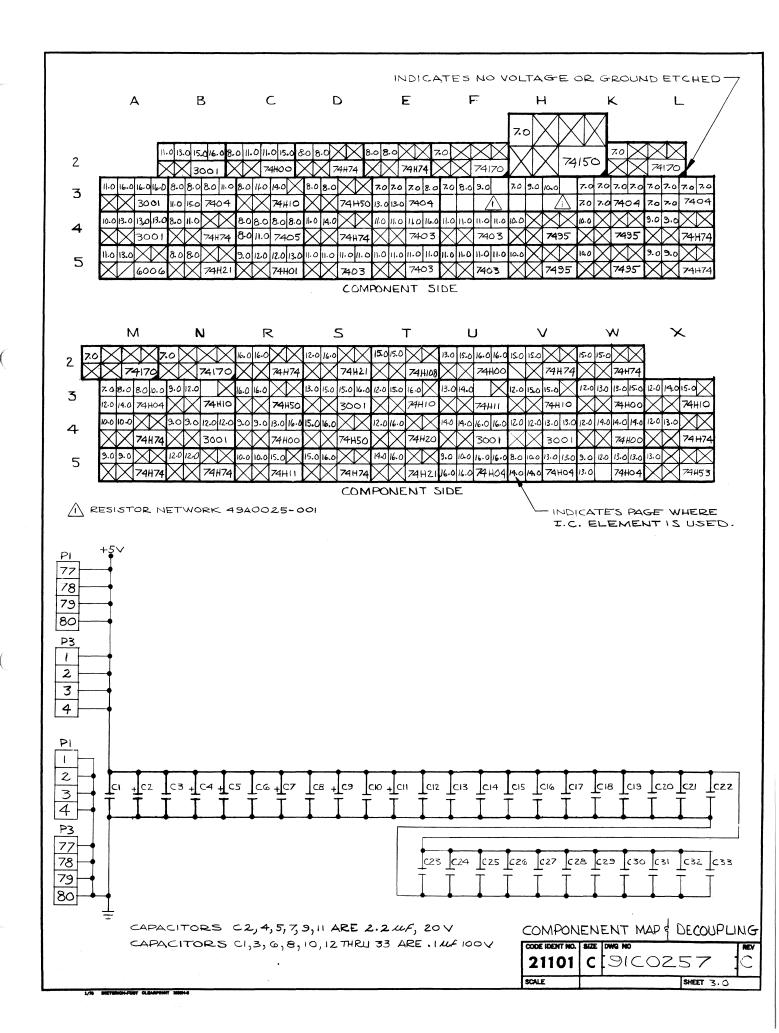

The MP is on a 3-by-15-inch (7.7 x 38.1 cm) wired-socket card (part number 44P0480-000). Circuit elements are intergrated circuits (ICs) and discrete components (figure 2-1). All connections to the MP are made through the 190-terminal card-edge connector that mates with the corresponding connector in the CPU tray.

## 2.2 SYSTEM LAYOUT AND PLANNING

The MP ciruit card is located in card slot 12 of the CPU tray. The card slots in the CPU tray are numbered 1 through 14 from rear to front as you face the front panel. Figure 2-2 shows the MP card mounted in the CPU tray.

## 2.3 SYSTEM INTERCONNECTION

The MP ciruit card is inserted into its designated card slot when the CPU tray is extended out the front of the mainframe and held by an extender assembly bolted to the front of the mainframe.

Insert the card into the mounting guides of slot 12 with the component side of the card toward the backplane connectors.

Apply moderate pressure to seat the card-edge connectors firmly into the mating connectors on the CPU tray. To prevent damage to the connectors or to the nylon guides, ensure that even pressure is applied across the top of the card during insertion. Avoid applying excessive pressure on the CPU tray and the extended assembly by supporting them from beneath during card insertion.

The card has ejector handles for unseating it from its mating connectors. To remove a card, lift the inside edge of the ejector handles; then lift the card from the slot.

VT12-0345

Figure 2-1. MP Component Layout Assembly

VT13-0267

98 A 9908 490

Figure 2-2. MP Card Location

2-3

## 2.4 SIGNAL INTERFACES

The MP interfaces with the computer via the control lines listed in tables 2-1 and 2-2. A ciruit-card connector pin number follows each signal mnemonic. For definitions of the mnemonics, refer to section 4.

Table 2-1. MP Input Interface Signals

| Signal   | Pin Number | Signal   | Pin Number |

|----------|------------|----------|------------|

| AB00 - C | P1-76      | CB11     | P3-20      |

| AB01 - C | P1-75      | CB12     | P3-21      |

| AB02 - C | P1-74      | CB13     | P3-22      |

| AB03 - C | P1-72      | CB14     | P3-24      |

| AB04 - C | P1-71      | DRYX - C | P1-6       |

| AB05 - C | P1-70      | DWA      | P3-69      |

| AB06 - C | P1-69      | DWAI     | P1-51      |

| AB07 - C | P1-68      | EBT -    | P1-31      |

| AB08 - C | P1-67      | EL       | P3-50      |

| AB09 - C | P1-66      | EP       | P3-14      |

| AB10 - C | P1-65      | EXC      | P3-60      |

| AB11 - C | P1-64      | EXF      | P3-16      |

| AB12 - C | P1-63      | EXGR     | P1-9       |

| AB13 - C | P1-62      | EXGR -   | P1-7       |

| AB14 - C | P1-61      | FRYX - C | P1-12      |

| AB15 - C | P1-60      | HLT      | P3-23      |

| ALC -    | P1-73      | HLTD     | P1-58      |

| CB00     | P3-5       | IF1      | P3-10      |

| CB01     | P3-6       | IF2      | P3-33      |

| CB02     | P3-7       | IF3      | P3-34      |

| CB03     | P3-8       | IJMP     | P3-45      |

| CB04     | P3-9       | INHB1 -  | P3-29      |

| CB05     | P3-11      | INR      | P1-47      |

| CB06     | P3-12      | INTR     | P3-46      |

| CB07     | P3-13      | INTX -   | P3-42      |

| CB08     | P3-17      | IOC -    | P3-39      |

| CB09     | P3-18      | IUAX - C | P1-8       |

| CB10     | P3-19      | IUCX - C | P1-10      |

| IUR      | P1-29      | POI      | P1-48      |

Table 2-1. MP Input Interface Signals (continued)

| Signal  | Pin Number | Signal   | Pin Number |

|---------|------------|----------|------------|

| JSR -   | P3-43      | RUN +    | P1-49      |

| JUMP -  | P3-41      | SKIP2 -  | P1-73      |

| OF1     | P1-38      | SRE      | P3-32      |

| OF2     | P3-66      | STJMK -  | P3-40      |

| OF4     | P1-26      | ST1      | P1-59      |

| OF5 -   | P1-18      | ST2      | P3-26      |

| OPSTO   | P3-57      | ST2 -    | P3-25      |

| OP10+   | P1-50      | SYRT - C | P1-17      |

| OSAFC - | P1-37      | TESTR    | P1-57      |

| PA -    | P3-28      | XFA      | P1-32      |

|         |            | XF1 -    | P3-15      |

Table 2-2. MP Output Interface Signals

| Signal   | Pin Number | Signal   | Pin Number |

|----------|------------|----------|------------|

| AB00 - C | P1-76      | AB12 - C | P1-63      |

| AB01 - C | P1-75      | AB13 - C | P1-62      |

| AB02 - C | P1-74      | AB14 - C | P1-61      |

| AB03 - C | P1-72      | DINT -   | P3-31      |

| AB04 - C | P1-71      | ISIO -   | P1-56      |

| AB05 - C | P1-70      | IURX - C | P1-28      |

| AB06 - C | P1-69      | MPINT -  | P3-27      |

| AB07 - C | P1-68      | MPST -   | P3-30      |

| AB08 - C | P1-67      | PRN3X -  | P1-14      |

| AB09 - C | P1-66      | RW -     | P1-27      |

| AB10 - C | P1-65      | SIOA -   | P3-74      |

| AB11 - C | P1-64      | ST2MK -  | P1-30      |

( • ( (

# SECTION 3 OPERATION

There are no operating controls or indicators on the MP circuit card. Data and control are under CPU program control (refer to section 4.13).

|  |  | ( |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | ( |

|  |  |   |

|  |  |   |

|  |  | ( |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

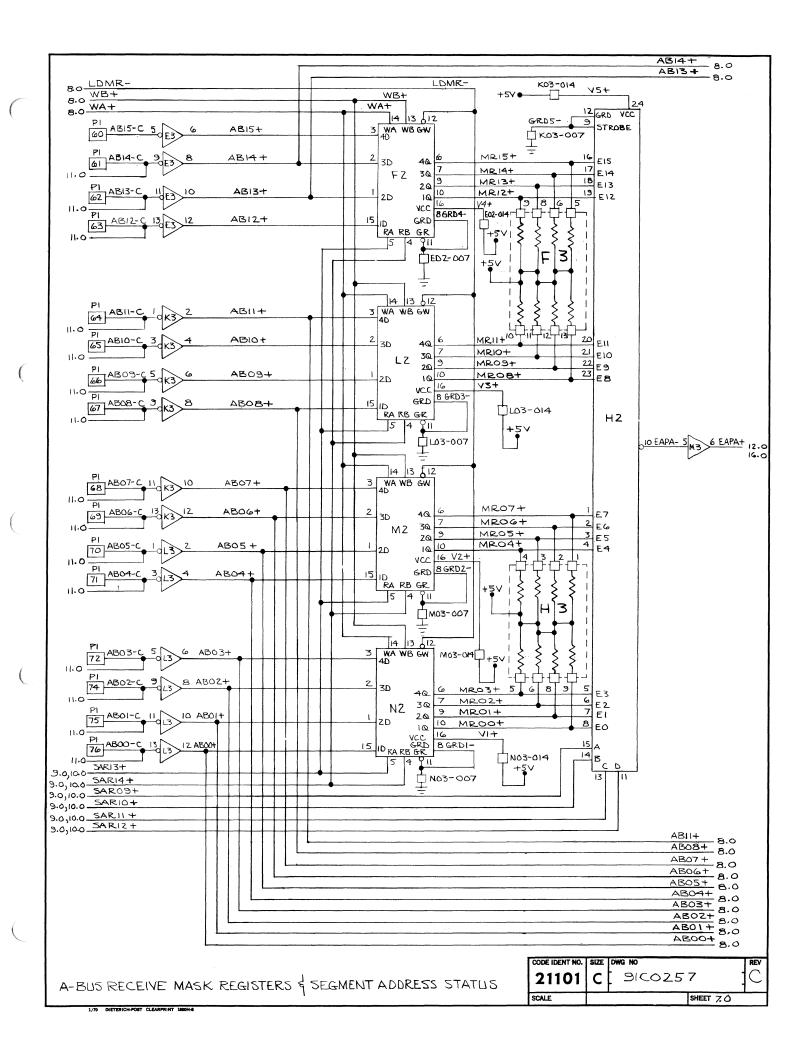

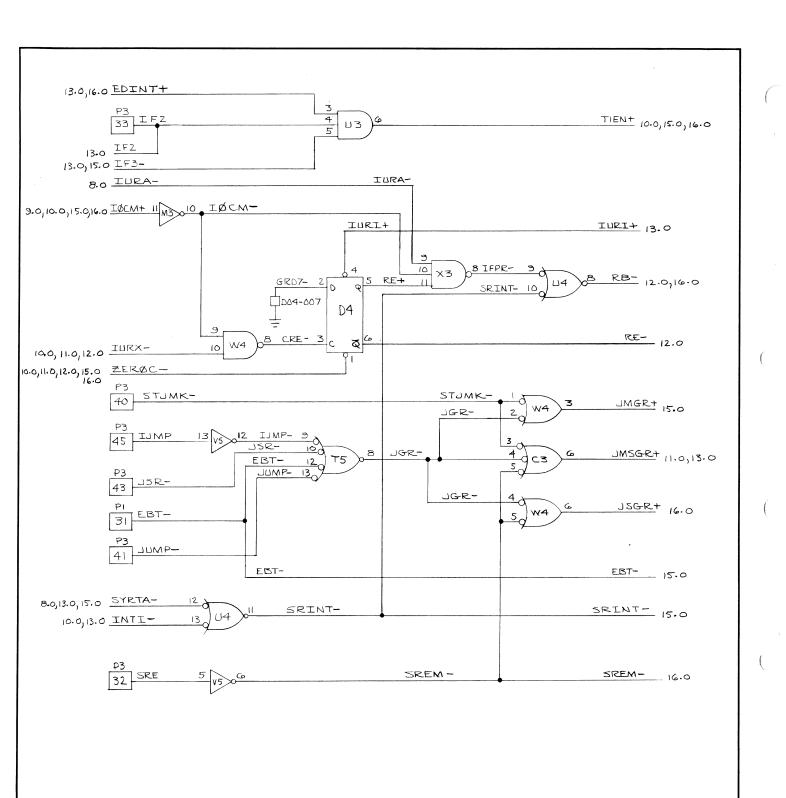

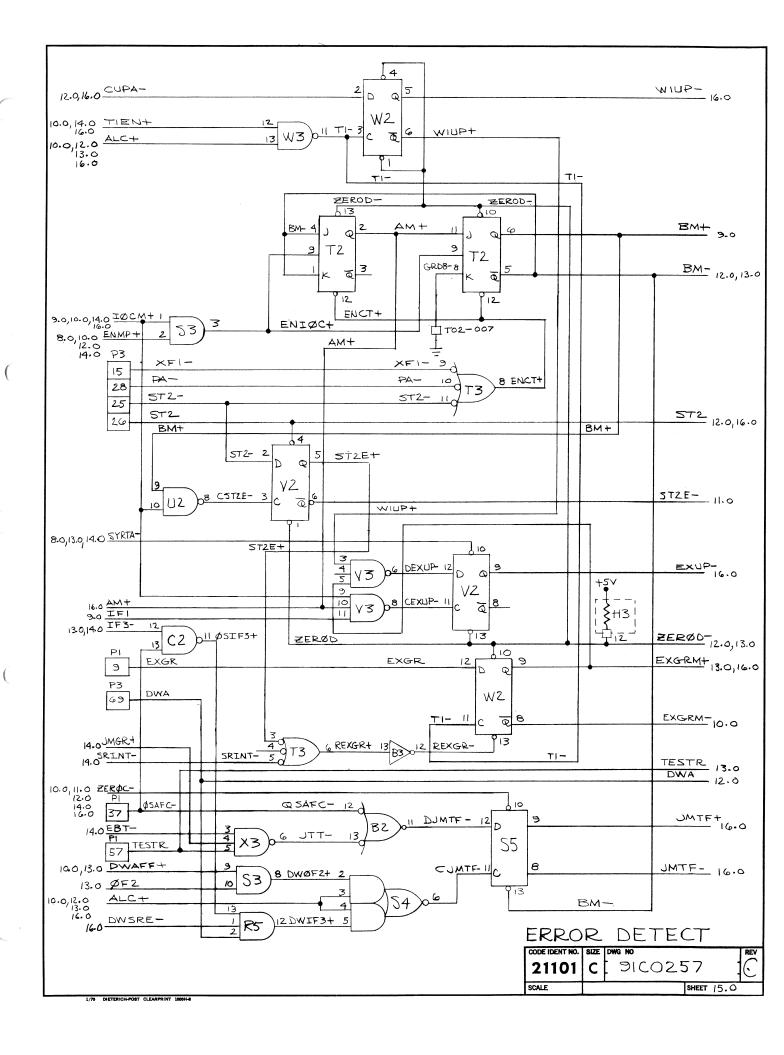

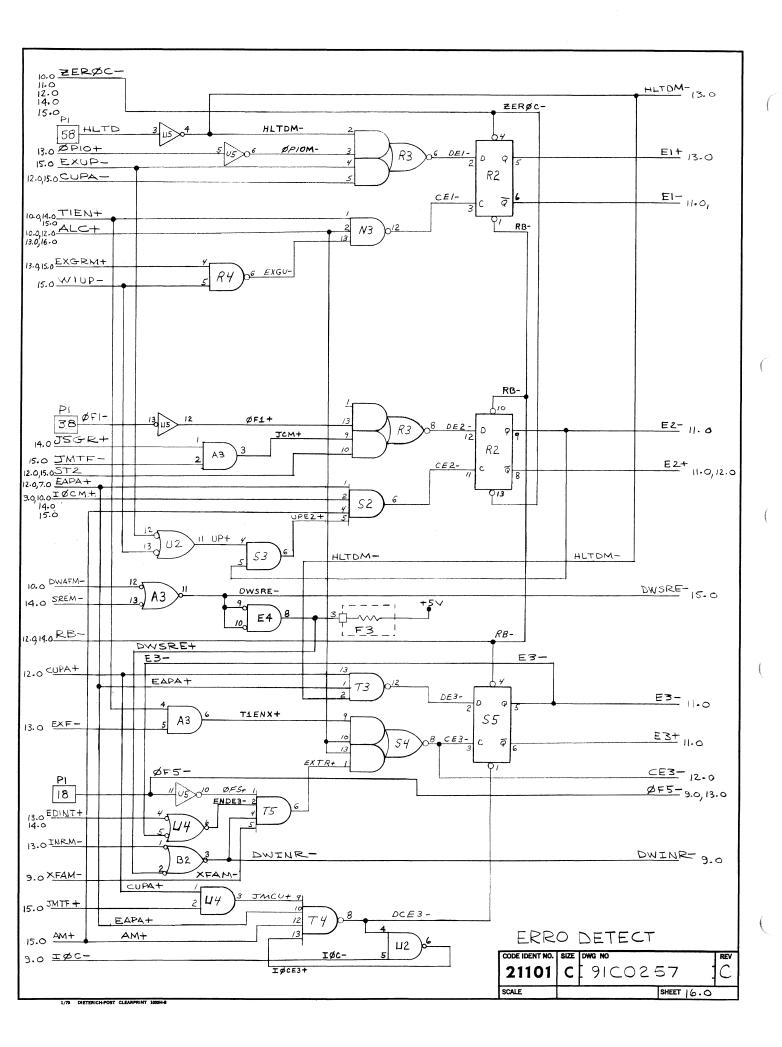

The following subsections describe the eleven functional sections of the MP: A-bus receiver, device address decoder, function control logic, segment address register, mask register, segment address status logic, error detector, CPU control logic, interrupt request logic, instruction address register, and A-bus driver. The MP mnemonics are listed in section 4.12 and programming considerations are given in section 4.13.

In the following descriptions, numbers in parentheses indicate the location of the chips on the circuit card. The first number locates the sheet; the following letter and number designate the chip location.

#### 4.1 A-BUS RECEIVER

The A-bus receiver buffers the A-bus signals, AB00 – C through AB15 – C (7E3, 7L3, 7K3), from the CPU and inverts them to AB00 + through AB15 + to provide data paths for the mask register, device address decoder, and function control logic functions.

The inverted A-bus signals are routed to the four mask registers to establish the protected and unprotected areas of memory. AB00+ through AB05+ go to the device address decoder to derive the MP device address (8B5). AB06+, AB07+, AB08+ (8B4. 8E2), AB11+ (8C3), AB13+, and AB14+ (8D3) represent the coded external control and data transfer instructions in function control operations.

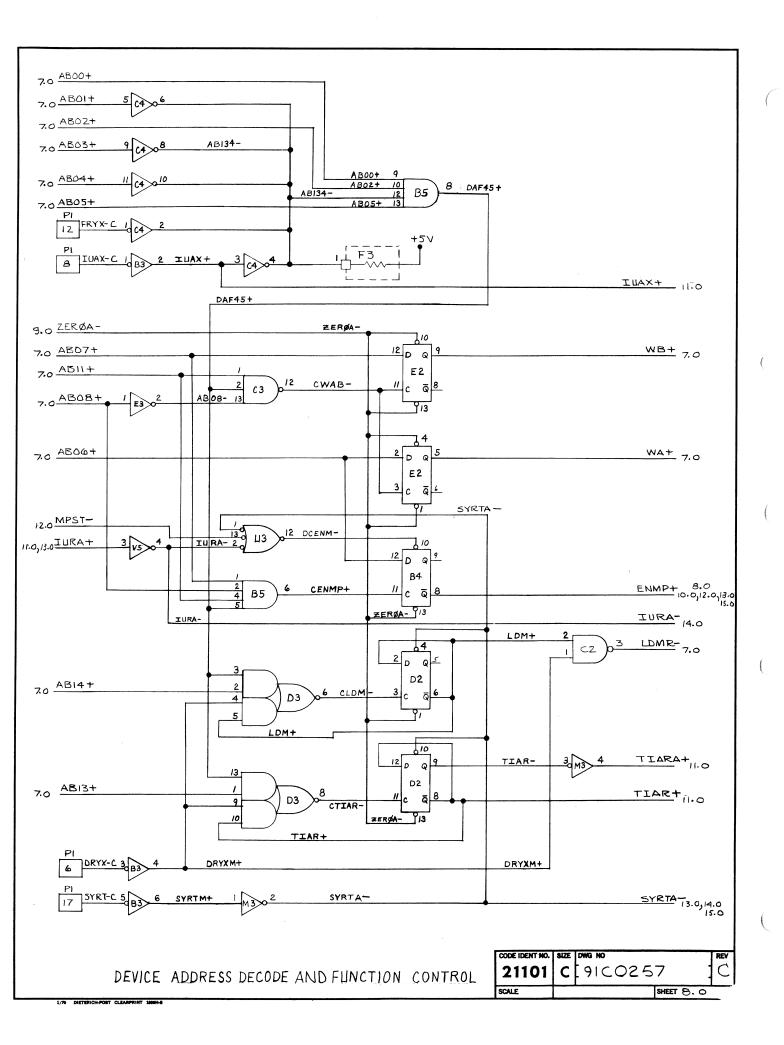

## 4.2 DEVICE ADDRESS DECODER

The device address decoder decodes the state of AB00 + through AB05 + (8B5) in the presence of FRYX – C (8C4) and IUAX – C (8B3) to generate the MP Device Address (DAF45) signal (8B5). DAF45 then goes to the function control logic.

#### 4.3 FUNCTION CONTROL LOGIC

External control (EXC) instructions on AB06+, AB07+, AB08+ (7K3), and AB11+ (7K3) are decoded and, with DAF45+, set flip-flops WA (8E2), WB (8E2) and ENMP (8B4). WA+ and WB+ select a mask register. When AB14+ (7E3) and DAF45+ are true, flip-flop LDM is set. LDM+, with the CPU Data Ready (DRYX – C) signal (8B3), loads the data from the A-bus receiver into the selected mask register.

4-1

The ENMP flip-flop (8B4) sets when the MP is addressed by EXC instruction 0100645 and is reset by 0100745. ENMP+ activates the instruction address register, segment address status logic, and error detector. The ENMP, LDM, and TIAR flip-flops can be reset by SYRT – C (8B3). When AB13+ (7E3) and DAF45+ (8B5) are true, flip-flop TIAR (8D2) is set to transfer the data on AB00 – C through AB14 – C from the instruction address register to the CPU.

## 4.4 SEGMENT ADDRESS REGISTER

C-bus signals CB09 through CB14 are used as data inputs to flip-flops SAR09 through SAR14 (9L4, 9L5, 9M5). During the CPU memory access time, SSAR + (9N3) clocks the six flip-flops. SAR13 + and SAR14 + select a mask register. SAR09 + through SAR12 + select one of the 16 outputs of the mask register. SAR09 + through SAR14 + are also routed to the instruction address register during IF3 (state 3 of the CPU instruction fetch cycle).

#### 4.5 MASK REGISTER

The mask register consists of four 4x4 register files. Each register file provides four bits of a selected mask register (7H2).

Each of the four MP mask registers contains 16 bits corresponding to 8,192 words of memory and each mask register bit controls a 512-word segment of memory. If the mask bit is one, the corresponding 512-word segment is protected; if zero, the segment is unprotected. Mask register 0 controls the low-order 8,192 words of memory, and mask register 3, the high-order 8,192 words. The mask register bit assignment is illustrated in figure 4-1.

WA + and WB + select a mask register for writing. LDMR - (8C2) is generated from the function control logic to load the data on AB00 + through AB15 + into a selected mask register. SAR13 + and SAR14 + from the segment address register select a mask register for reading out to the segment address status logic.

VT11-0237A

Figure 4-1. Mask Register Bit Assignment

98 A 9908 490

## 4.6 SEGMENT ADDRESS STATUS LOGIC

The segment address status logic detects the status of the addressed 512-word segment of memory. The protected/unprotected status of the addressed segment, EAPA + (7M3), is then gated to the error detector as the status of the effective address or as the status of the current word.

SAR09 + through SAR12 + from the segment address register are decoded, and the result selects one of the outputs of the mask register, MR00 + through MR15 + (7F2, 7L2, 7M2, 7N2). The status of the addressed memory segment, EAPA + is output to the error detector. If EAPA + is true, the addressed 512-word segment is protected. If EAPA + is false, it is unprotected.

The CUPA flip-flop (12N5) stores the information that an instruction word or effective address is in an unprotected or protected area. CUPA is clocked by the UDP flip-flop 110 nanoseconds after the P register in the CPU is incremented or changed. The UDP flip-flop is set each time the P register is modified. CUPA is routed to the error detector.

#### 4.7 ERROR DETECTOR

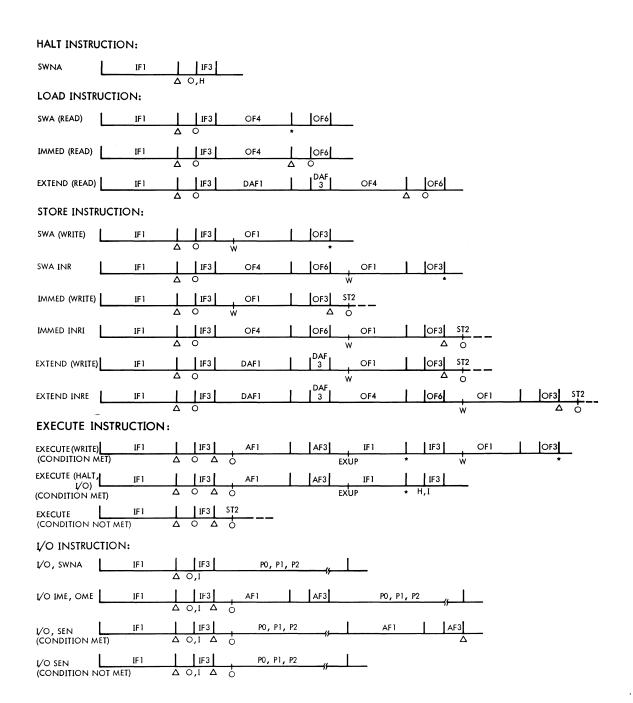

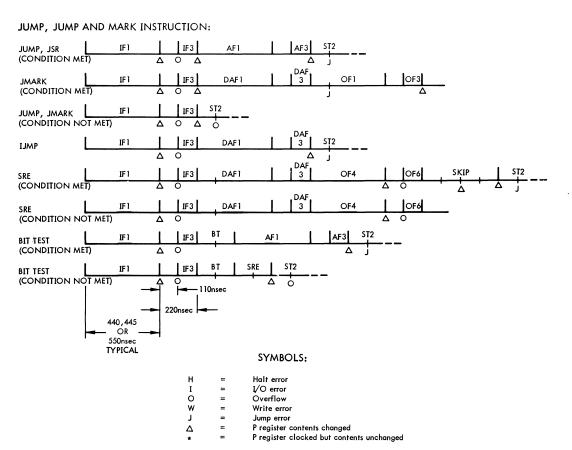

Error detector outputs are routed to the CPU control logic, interrupt request logic, and the A-bus driver. Figure 4-2 shows the error detection timing diagram.

The W1UP flip-flop (15W2) stores the unprotected or protected status of the address of the first word of each instruction. During the instruction fetch cycle of any instruction, detection of the above condition occurs when the CPU enters the IF3 state. If a one-word instruction or the first word of a two-word instruction lies in the last address of an unprotected area, W1UP is set.

The EXGRM flip-flop (15W2) is set by an execute (XEC) instruction. If W1UP is also set, EXUP sets. Detection of this condition occurs 110 nanoseconds after state IF1 of the next instruction-fetch cycle is entered. EXUP remains set until the fetch cycle of the second instruction following the XEC instruction. EXUP – is routed to the error flip-flops.

VT12-0355

Figure 4-2. Error Detection Timing

#### INSTRUCTION ABBREVIATIONS:

| SWNA   | = | One-word nonaddressing          |

|--------|---|---------------------------------|

| SWA    | = | One-word addressing             |

| INR    | = | Increment and replace           |

| IME    | = | Input to memory                 |

| OME    | = | Output from memory              |

| SEN    | = | Sense I/O                       |

| IMMED  | = | Immediate                       |

| INRI   | = | Increment and replace immediate |

| EXTEND | = | Extended                        |

| INRE   | = | Increment and replace extended  |

| BT     | = | Bit test                        |

| JSR    | = | Jump and set return:            |

| IJMP   | = | Indexed jump                    |

| JMARK  | = | Jump and mark                   |

| SRE    | = | Skip if register equal          |

|        |   |                                 |

VT12-0356

Figure 4-2. Error Detection Timing (continued)

The AM and BM flip-flops (15T2) comprise a 110-nanosecond counter—for control timing and error detection. The counter is held reset—except during memory access, the first part of an I/O cycle, or the CPU—interrupt wait state ST2. ENCT + (15T3) enables the 18-MHz clock to the counter when the MP is enabled.

The ST2E flip-flop (15V2) stores the CPU interrupt wait state. It is set during all but the first 165 nanoseconds of ST2. ST2E – clocks EB1 in the A-bus driver and ST2E + resets flip-flop EXGRM.

JMGR + (14W4), JMSGR + (14C3), and JSGR + (14W4) are ORed combinations of the jump- and skip-type instruction decodes (14T5) from the CPU instruction register.

JMGR + gates the D input of the JMTF flip-flop (15S5). JSGR + is routed to the CPU control logic as part of the dummy interrupt (DINT) gating logic (13X5).

The JMTF flip-flop (15S5) enables the setting of the E3 overflow error flip-flop (16S5) except during jump-type instructions (excluding skip) for which the test condition is true. If the second word of a two-word instruction is in the last address of an unprotected area and if JMTF is set, an overflow error, E3, is detected.

JMTF is clocked in state IF3 during the execution of two-word addressing instructions (except extended, immediate, and skip if register equal) or in state OF2 for extended and immediate instructions. JMTF is dc reset by the BM flip-flop when the BM flip-flop is set.

The E1 flip-flop (16R2) sets when it detects halt and I/O errors. CE1 - (16N3) clocks E1, and RB - (14U4) resets it. For a halt error, the CPU is interrupted to address 020, and, for an I/O error, to address 022 or to 032 if an overflow error also occurs.

During the instruction fetch cycle, halt errors are detected upon entry to CPU state IF3. The CPU halts to enter state ST1 after fetching the instruction at the interrupt address. Detection of the halt error causes the MP to hold MPST – true. Thus, CPU reenters the run mode 110 nanoseconds after halting in ST1. MPST – is removed when the error interrupt has been processed.

During the instruction fetch cycle, I/O errors are detected upon entry to CPU state IF3. The contents of memory and of the A, B, and X registers remain unmodified by the I/O instruction when the Inhibit Start I/O (ISIO – ) is held true immediately before and during CPU state P0. The MP makes the Simulated I/O Active (SIOA – ) signal true 110 nanoseconds after the CPU enters state P0. The CPU steps to state P1 110 nanoseconds later. The MP then makes SIOA – false 110 nanoseconds after entering state P1. The CPU steps to state P2 110 nanoseconds later from which it then exits automatically after another 110 nanoseconds to complete I/O instruction execution.

The E2 flip-flop (16R2) detects write and jump errors. It is clocked by CE2 - (16S2) and reset by RB - .

If an operand store instruction (with either a one-word or the first word of a two-word instruction lying in an unprotected area) attempts to write into a protected area or, if it is being executed by an XEC instruction that lies in an unprotected area, the E2 flip-flop is set, indicating a write error. For a write error, the CPU is interrupted to address 024 (or to 034 if an overflow error also occurs).

All store-type instructions end with an operand store cycle. Write errors are detected 110 nanoseconds after CPU state OF1 of the store cycle is entered to change the write cycle to a read cycle. To change a write cycle to a read cycle, the read/write input (RW –) to the memory must be near OV within 150 nanoseconds after the Memory Start (MST –) signal goes true at the beginning of state OF1.)

The E2 flip-flop is set when a jump error is detected. A jump error occurs when a jump, indexed jump, jump and mark, jump and set return, bit test, or skip if register equal operation into a protected area is attempted from an unprotected area. For a jump error, the CPU is interrupted to address 026 or to 036 if an overflow error also occurs.

A jump error is detected at the beginning of the OF1 portion of a jump and mark operand cycle. Thus, as in the case of the other operand store instructions, the error is detected during the last instruction cycle.

The jump, indexed jump, jump and set return, and bit test instructions—end with an address cycle. The final (effective) address is not available until—the final address cycle is nearly complete. To provide time for error—detection, the Simulated (Dummy) Interrupt (DINT—) signal is held true—during AF3 or DAF3 of the last address cycle. The CPU is thus forced to go to—the interrupt wait state ST2, and error detection occurs 110 nanoseconds after entering ST2. If no jump error is detected and overflow does—not occur, DINT— goes false and the CPU executes the next instruction. If a jump error is detected, DINT— remains true, holding the CPU—in ST2 while an interrupt request is issued by the MP.

The optional Skip If Register Equal (SRE) instruction terminates in a special skip cycle, and the final address is not available until late in the final cycle. Jump error detection for an SRE instruction is, therefore, the same as that for a jump instruction.

A jump error cannot occur during the conditional jump instructions if the jump condition is not met. However, overflow errors can occur.

The E3 flip-flop (16S5) detects overflow errors. If a one-word instruction or either the first or second word of a two-word instruction lies in the last address of an unprotected area and the next instruction in sequence lies in a protected area, the E3 flip-flop is set for an overflow error. If the second word of a jump-type or jump and mark instruction lies in an unprotected area, E3 can be dc set by DCE3 – (16T4). E3 is clocked by CE3 – (16S4) and reset by RB – . For an overflow error, the CPU is interrupted to address 030. If an overflow error is detected concurrently with an I/O, write, or jump error, the CPU is interrupted to composite interrupt address 032, 034, or 036, respectively.

For a one-word instruction and the first word of a two-word instruction, overflow errors are detected when the CPU enters state IF3 during the instruction fetch cycle. For the second word of a two-word instruction (except extended), overflow errors are detected 110 nanoseconds after the CPU leaves state IF3. For the second word of an extended instruction, overflow errors are detected when OF6 is entered (read) or 110 nanoseconds after leaving OF3 (write or INR).

With the MP enabled, TIEN + (the first half of CPU state IF2) enables the clock to halt. I/O, and overflow error detection, and to the W1UP flip-flop. TIEN + also enables the clock to the instruction address register.

RB – resets the E1, E2, and E3 flip-flops at the end of the MP interrupt. Resetting the flip-flops causes the IURX (11B4) and EB1 (11D4) flip-flops to reset. The error flip-flops can be reset by SYRT – C or by the INTI flip-flop (10M4). INTI – inhibits error detection.

### 4.8 CPU CONTROL LOGIC

The CPU control logic generates seven special signals to control CPU operations: ISIO – , SIOA – , MPINT – , DINT – , ST2MK – , MPST – , and RW – .

When an error is detected during execution of an I/O instruction, the ISIO gate (13C5) and SIOA flip-flop (13X4) are activated. ISIO – inhibits—the CPU start I/O signal to the I/O section, thereby inhibiting I/O operations. SIOA – simulates the I/O active signal, causing the CPU to proceed—through the I/O sequence (PO. P1, and P2) even though the I/O section is inhibited.

The MPINT gate (13A5) provides parallel gating with a CPU circuit to bypass most of the interrupt inhibits for noninterruptable instructions. The number of noninterruptable instructions was decreased so that, in a real-time operating system, interrupts can be more rapidly processed.

When any error is detected, the MP must wait until the next trailing edge of IUCX – C before raising its interrupt request. To guarantee that no further instructions are executed by the CPU after the error is detected, DINT – (13X5), which is routed directly to the CPU, is brought true. DINT – true forces the CPU to ST2 after executing the instruction and holds the CPU in that state until the MP interrupt request is raised.

If a jump condition is not met, DINT – sets the CPU to ST2 to allow for overflow error detection.

The ST2 mask logic (12T4), with DINT – , holds the CPU in ST2 to prevent initiation of the I/O cycle. ST2MK – true inhibits the interrupt sequence when DINT – is true until the MP detects an error, at which time ST2MK – goes false and the interrupt sequence is allowed to proceed. If no error is detected, DINT – goes false, followed by ST2MK – . The CPU then proceeds to the next instruction.

The MPST1 flip-flop (12X4) stores a halt instruction and enables the MPST + (12S2) gate, when a halt error is detected, MPST - (12W5) true restarts the CPU immediately after the CPU halt that results when a halt is attempted in an unprotected area.

The RW logic gate (12C5) controls the read/write control line to the memory. If a write or jump error is detected, RW – goes true (at the beginning of state OF1), changing the memory write cycle to a read cycle to prevent memory modification.

### 4.9 INTERRUPT REQUEST LOGIC

In the interrupt request logic, the IURX flip-flop (11B4) generates the MP interrupt request (IURX +) signal to the CPU when an error is detected by the error detector. IURX + is set on the trailing edge of the CPU Interrupt clock (IUCX - C) signal (11B3) when E123 + (11C3) is true.

When an MP interrupt request is raised, priority signal PRN3X – (11A5) goes high and disables priority to all device controllers lower in the 620/f priority chain.

#### 4.10 INSTRUCTION ADDRESS REGISTER

The 15-bit instruction address register (IAR) stores the value of the P register plus one at the end of each instruction fetch cycle. The IAR is updated at each instruction fetch cycle until the MP detects an error. The MP can, thus, locate the address of the instruction in error. During an error interrupt routine, further update of the IAR is inhibited until the MP is reenabled.

IAR00 + through IAR14 + (10H4, 10H5, 10K4, 10K5) from the IAR are routed to the A-bus driver and, during a data transfer in, are gated out to the CPU. Bits CB00 through CB08 arrive directly from the C-bus, and are clocked into the IAR by CLAIR. SAR09 + through SAR14 + arrive from the segment address register and are clocked into the IAR by CUIAR.

The interrupt inhibit (INTI) flip-flop (10M4) inhibits error detection by the MP during the processing of interrupts generated by other device controllers. Also, flip-flop DWAFF (10K5) generates DWAFF + to the error detector during DWAI.

#### 4.11 A-BUS DRIVER

The A bus driver gates error interrupt addresses to the CPU during an MP-generated error interrupt. This circuit also gates the contents of the instruction address register to the CPU during a data transfer in.

The error interrupt addresses are encoded on A-bus lines AB01 – C through AB04 – C. When the MP-generated IURA + (11B2) is true, the interrupt address gates are enabled depending on the detected error conditions. Also, flip-flop EB1 + is set when I/O or jump errors are detected. Note that EB1 + is used to make AB01 – C true so that the interrupt address is maintained on the A bus during interrupt acknowledgement.

The A-bus driver also transfers the contents of the instruction address register (IAR) to the A-bus. AB00 – C to AB14 – C correspond to the contents of IAR00 + through IAR14 + . The transfer is accomplished when the function control logic receives a transfer in instruction, i.e., the TIAR flip-flop is set. TIAR + (6D4) gates IAR00 + through IAR07 + to the A bus as bits AB01 – C through AB07 – C. Similarly, bits IAR08 + through IAR14 + are gated out to the A-bus as AB08 – C through AB14 – C by TIARA + (8M3).

### 4.12 MNEMONICS

The mnemonics used in the MP are listed alphabetically in table 4·1. The source column lists the location of the signal's source on MP logic diagram 91C0257; the first number is the drawing sheet number and the following letter and number, the chip location on the circuit card (except for connector P1 and P3). Refer to section 6 for the logic diagram. Each signal's function is briefly described.

Table 4-1. MP Mnemonic Definitions

| Mnemonic              | Source                           | Description                                                                                                               |

|-----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| AB00 - C to<br>AB15 - | 11D5,11E4,<br>11F4,11E5,<br>11F5 | 620/f CPU internal I/O data lines                                                                                         |

| AB00+ to AB15+        | 7E3,7L3,<br>7K3                  | A bus driver output to the mask register                                                                                  |

| AB134 -               | 8C4                              | ANDed A-bus, function ready,<br>and interrupt acknowledge signals<br>to form a partial decode of the<br>MP device address |

| ALCA -                | 13V5                             | Alternate clock (inverted); clocks the SIOA flip-flop                                                                     |

| ALC -                 | P3-72                            | Gated 9.0-MHz alternate clock from CPU; inhibited during XF1 portion of each memory cycle                                 |

| AM +                  | 15T2                             | Output of the first flip-flop of a two-flip-flop 110-nanosecond counter; used in error detection                          |

| BIF1 -                | 9R4                              | Timing window for loading the seg-<br>ment address register and lower<br>half of instruction address regis-<br>ter        |

Table 4-1. MP Mnemonic Definitions (continued)

| Mnemonic                       | Source                                      | Description                                                                                               |

|--------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| ВМ                             | 15T2                                        | Output of the second flip-flop of a two-flip-flop 110-nanosecond counter; provides control section timing |

| CB00-CB07<br>CB08<br>CB09-CB14 | P3-5 to P3-13<br>P3-17<br>P3-18 to<br>P3-24 | C-bus bits 0-14; buffered outputs from the adders of the CPU data loop                                    |

| CCUPA -                        | 12N4                                        | Clock input to the CUPA flip-flop                                                                         |

| CEB1+                          | 11A3                                        | Clock input to the EB1 flip-flop                                                                          |

| CENMP+                         | 8B5                                         | Clock input to the ENMP flip-flop                                                                         |

| CEXUP -                        | 15V3                                        | Clock input to the EXUP flip-flop                                                                         |

| CE1 -                          | 16N3                                        | Clock input to the E1 flip-flop                                                                           |

| CE2 -                          | 16S2                                        | Clock input to the E2 flip-flop                                                                           |

| CE3 -                          | 16S4                                        | Clock input to the E3 flip-flop                                                                           |

| CJMTF -                        | 15S4                                        | Clock input to the JMTF flip-flop                                                                         |

| CLDM -                         | 8D3                                         | Clock input to the LDM flip-flop                                                                          |

| CLIAR +                        | 10R5                                        | Clock input to bits 0-8 of the Clock input to bits 0-8 of the instruction address register                |

| CRE -                          | 14W4                                        | Clock input to the RE flip-flop segment address register                                                  |

| CSARA +                        | 9N4                                         | Clock input to bits 9-11 of the segment address register                                                  |

Table 4-1. MP Mnemonic Definitions (continued)

|          | Table 4-1. Will Willellion | iic beliiitions (continued)                                                                                                          |

|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic | Source                     | Description                                                                                                                          |

| CSARB+   | 9N4                        | Clock input to bits 12-14 of the                                                                                                     |

| CST2E -  | 15U2                       | Clock input to the ST2E flip-flop                                                                                                    |

| CTIAR -  | 8D3                        | Clock input to the TIAR flip-flop                                                                                                    |

| CUDP -   | 12N3                       | Clock input to the UDP flip-flop                                                                                                     |

| CUIAR +  | 10R5                       | Clock input to bits 9-14 of the instruction address register                                                                         |

| CUPA     | 12N5                       | Output of the CUPA flip-flop;<br>stores the protected/unprotected<br>status of each instruction word<br>and of the effective address |

| CWAB -   | 8C3                        | Clock input to the WA and WB flip-flops                                                                                              |

| DAF45 +  | 8B5                        | MP device address 045 decoded and ANDed with the function ready and interrupt acknowledge signals                                    |

| DCENM -  | 8U3                        | Dc reset input to the ENMP flip-flop                                                                                                 |

| DCE3 -   | 16T4                       | Dc set input to the E3 flip-flop                                                                                                     |

| DEXUP -  | 15V3                       | D input to the EXUP flip-flop                                                                                                        |

| DE1 -    | 16R3                       | D input to the E1 flip-flop                                                                                                          |

| DE2 -    | 16R3                       | D input to the E2 flip-flop                                                                                                          |

| DE3 -    | 16T3                       | D input to the E3 flip-flop                                                                                                          |

| DINT -   | 13X5                       | Dummy (simulated) interrupt to CPU; places and holds CPU in the interrupt wait state (ST2) to provide time for error detection       |

Table 4-1. MP Mnemonic Definitions (continued)

| NA       | Source | Description                                                                                                                                                               |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic |        | ·                                                                                                                                                                         |

| DJMTF –  | 15B2   | D input to the JMTF flip-flop                                                                                                                                             |

| DRYXM +  | 8B3    | Inverted from DRYX -C                                                                                                                                                     |

| DRYX - C | P1-6   | Data Ready signal on CPU internal I/O control bus                                                                                                                         |

| DSIOA -  | 13W3   | D input to the SIOA flip-flop                                                                                                                                             |

| DWA      | P3-69  | Decoded two-word addressing signal from the CPU instruction register; when true, the register contains a two-word instruction                                             |

| DWAFF +  | 10K5   | Output of DWAFF flip-flop; set dur-<br>ing immediate or extended two-word<br>addressing instructions                                                                      |

| DWAFM -  | 10U5   | Inverted from DWAFF                                                                                                                                                       |

| DWAI     | P1-51  | Decoded two-word immediate addressing signal from the CPU instruction register; when true, the register contains an extended or immediate two-word addressing instruction |

| DWIF3+   | 15R5   | State IF3 during all two-word addressing instructions except extended, immediate, and skip if register equal                                                              |

| DWINR -  | 16B2   | All extended, immediate, and skip if register equal (two-word) instructions except increment and replace                                                                  |

| DWOF2 +  | 15\$3  | State OF2 during all extended and immediate (two-word) instructions                                                                                                       |

Table 4-1. MP Mnemonic Definitions (continued)

| Mnemonic | Source    | Description                                                                                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DW0I +   | 13B2      | Operand store or increment and re-<br>place during extended or immediate<br>(two-word) instructions with MP<br>enabled; enables dummy interrupt |

| DWSRE    | 16A3,16E4 | OR of extended, immediate, and skip if register equal instruction register decodes                                                              |

| EAPA -   | 7H2       | Status of the address of the first or second word of an instruction or of the effective address                                                 |

| EBT -    | P1-31     | When true, the instruction register contains a bit test instruction                                                                             |

| EB1 +    | 11D4      | Enable A-bus bit 1 flip-flop; stores conditions for which bit 1 must be made true during an MP-generated interrupt                              |

| EDINT+   | 13V4      | Enable dummy interrupt; enables MP and indicates that no externally generated interrupt is in process                                           |

| EDWAF+   | 13A4      | Extended or immediate instruction with MP enabled                                                                                               |

| EFB1 -   | 13V4      | Generated when EXF and INHB1 are false; inhibits the dummy interrupt                                                                            |

| EL       | P3-50     | Enables CPU L register clock                                                                                                                    |

| ENCT+    | 15T3      | Enables the AM/BM counter                                                                                                                       |

| ENDE3 -  | 16U4      | Enables MP and resets flip-flop E3                                                                                                              |

Table 4-1. MP Mnemonic Definitions (continued)

|          | Table 4-1. Will Willellion | c Deminions (commuca)                                                                                                  |

|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Mnemonic | Source                     | Description                                                                                                            |

| ENIOC+   | 15\$3                      | 18-MHz clock gated to AM/BM counter when the MP is enabled                                                             |

| ENJMS+   | 13A4                       | Indicates that a jump, jump and mark, or skip instruction is in the instruction register                               |

| ENMP+    | 8B4                        | MP enabled flip-flop; stores enabled/<br>disabled MP status                                                            |

| EP       | P3-14                      | Enables CPU P register clock                                                                                           |

| EXC      | P3-60                      | When true, the instruction register contains an external control instruction                                           |

| EXEN -   | 10A4                       | Indicates that the instruction register does not contain an execute instruction                                        |

| EXFGM +  | 13A4                       | Execute instruction decoded but execution condition not met                                                            |

| EXFT2 +  | 13\$3                      | Execute instruction decoded, execute condition not met, and test not true during IF2                                   |

| EXF -    | P3-16                      | Execute condition met flip-flop; set at the end of IF2 during an execute instruction if the execution condition is met |

| EXGR     | P1-7,P1-9                  | When true, the instruction register contains an execute instruction                                                    |