# 70 Series Option Board Operation and Service

# 70 SERIES OPTION BOARD OPERATION AND SERVICE MANUAL

98A 9906 054 FEBRUARY 1978

The statements in this publication are not intended to create any warranty express or implied. Equipment specifications and performance characteristics stated herein may be changed at any time without notice. Address comments regarding this document to Sperry Univac, Mini-Computer Operations, Publications Department, 2722 Michelson Drive, P.O. Box C-19504, Irvine, California, 92713.

4 1978 SPERRY RAND CORPORATION-

λ.

#### CHANGE RECORD

| Page<br>Number | issue<br>Date | Change Description                |

|----------------|---------------|-----------------------------------|

| Various        | 1/78          | Deleted all references to Varian. |

|                |               | .•                                |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               | <u>.</u>                          |

|                |               | ·                                 |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               | •                                 |

|                |               |                                   |

#### Change Procedure:

When changes occur to this manual, updated pages are issued to replace the obsolete pages. On each updated page, a vertical line is drawn in the margin to flag each change and a letter is added to the page number. When the manual is revised and completely reprinted, the vertical line and page-number letter are removed.

### LIST OF EFFECTIVE PAGES

| Page Number  | Change in Effect  |

|--------------|-------------------|

| A11          | Complete revision |

|              |                   |

|              |                   |

|              |                   |

|              |                   |

|              |                   |

|              | •<br>·            |

|              |                   |

|              | ·                 |

|              | • •               |

|              |                   |

|              |                   |

|              |                   |

|              | .·                |

|              |                   |

| 9244731-0098 |                   |

### TABLE OF CONTENTS

## SECTION 1 GENERAL DESCRIPTION

| 1 1 FUNCTIONAL DESCRIPTION                            |              |

|-------------------------------------------------------|--------------|

| 1.1.1 Teletype Controller                             | 1.1          |

| 1.1.2 Power Failure/Restart                           | 1-1          |

| 1.1.3 Real-Time Clock                                 | 1.1          |

| 1 1.4 Memory Protection                               | 1.3          |

| 1.1.5 Memory Parity                                   |              |

| 1.1.6 Priority Memory Access                          |              |

| 1.2 SPECIFICATIONS                                    |              |

| 1.3 RELATED PUBLICATIONS                              |              |

|                                                       |              |

| SECTION 2 INSTALLATION                                |              |

|                                                       |              |

| 2 1 INSPECTION                                        | Z-1          |

| 2.2 PHYSICAL DESCRIPTION                              |              |

| 2 3 INTERCONNECTION                                   | 2.1          |

| SECTION 3 OPERATION                                   | <b>3</b> . l |

| SECTION 4 THEORY OF OPERATION                         |              |

| ,                                                     |              |

| & 1 TELETYPE CONTROLLER                               | 4-1          |

| 4.1.1 Signal Interfaces.                              | 4.]          |

| 4.1 1.1 Teletype Interface                            |              |

| 4.1.1.2 PIM Interface                                 |              |

| 4.1.2 Circuit Description                             |              |

| 4.1.2.1 Initial Condition                             |              |

| 4 1.2.2 TC/Common-Logic Interface                     |              |

| 4.1.2.3 TC Output (Write)                             |              |

| 4 1.2 4 Loading the Output Buffer and MOS Transmitter | 4-10         |

| 4.1.2.5 Output to the TTY                             |              |

| 4 1.2.6 TC Input (Read)                               |              |

| 4.1.3 Programming                                     |              |

| 4.2 POWER FAILURE/RESTART                             | 4-13         |

| 4.2.1 Timing                                          | 4-14         |

| 4.2.2 Circuit Description                             |              |

| 4.2.3 Programming                                     |              |

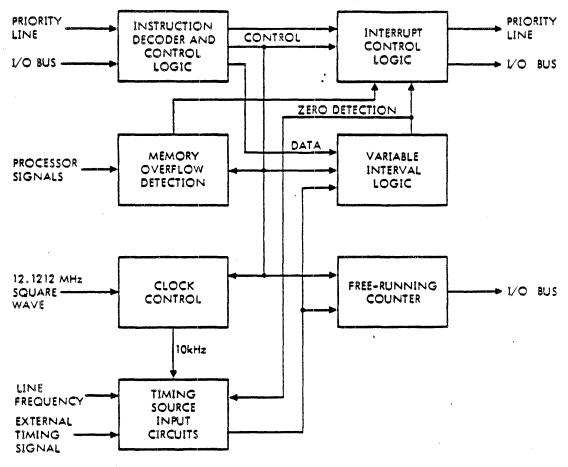

| 4.3 REAL-TIME CLOCK                                   | 4-18         |

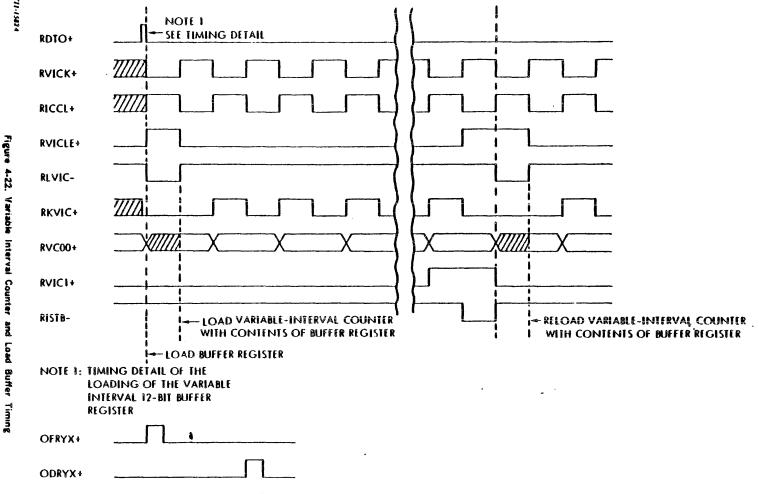

| 4.3.1 Timing                                          | 4-20         |

| 4.3.2 Circuit Description                             | 4.20         |

| 4.3.2.1 Instruction Decoder and Control Logic         |              |

| 4.3.2.2 Free-Running Counter                          |              |

| 4.3.2.3 Clock Control Logic                           |              |

| 4.3.2.4 Input Timing Source                           |              |

| 4.3.2.5 Variable Interval Logic                       |              |

| 4.3.2.6 Memory Overflow Detection Logic               |              |

| 4.3.2.7 Interrupt Control Logic                       |              |

| 4.3.3 Programming                                     |              |

| 4.4 MEMORY PROTECTION                                 |              |

| 4.4.1 Error Sequences.                                |              |

#### CONTENTS

| 4.4.2 Circuit Description                               | 4.33  |

|---------------------------------------------------------|-------|

| 4.4.3 Programming                                       | 4-34  |

| 4.5 MEMORY PARITY                                       | 4-35  |

| 4.5.1 Circuit Description                               | 4-35  |

| 4.5.2 Programming                                       | 4.3€  |

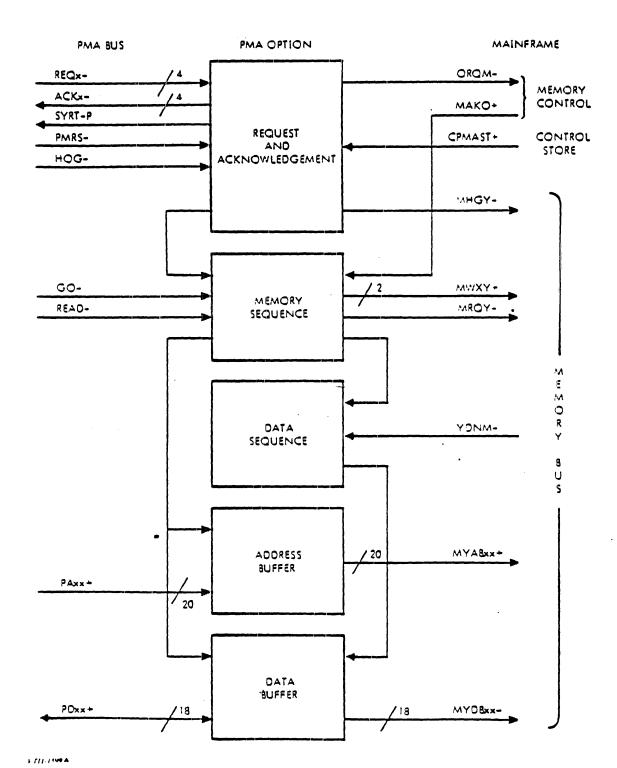

| 4.6 PRIORITY MEMORY ACCESS                              | 4.36  |

| 4.6.1 PMA Option/Controller Interface                   | 4.37  |

| 4.6.2 Timing                                            | 4.37  |

| 4.6.3 Circuit Description                               |       |

| 4.6.4 Programming                                       | 4.45  |

| SECTION 5 MAINTENANCE                                   |       |

| 5.1 TELETYPE CONTROLLER                                 | . 5.1 |

| 5.1.1 Equipment                                         |       |

| 5.1.2 Test Programs                                     |       |

| 5.1.3 TC/TTY Troubleshooting                            |       |

| 5 2 POWER FAILURE/RESTART                               |       |

| 5.2.1 Equipment                                         |       |

| 5 2.2 Test Program                                      |       |

| 5.2.3 Troubleshooting                                   |       |

| 5.3 REAL TIME CLOCK                                     |       |

| 5 3 1 Equipment                                         |       |

| 5.3.2 Test Program                                      |       |

| 5.3.3 Troubleshooting                                   |       |

| 5.4 MEMORY PROTECTION                                   |       |

| 5.4.1 Equipment                                         | . 5.3 |

| 5 4 2 Test Program                                      | . 5-3 |

| 5 4 3 Troubleshooting                                   |       |

| 5 5 PARITY                                              | . 5.5 |

| 5.6 PRIORITY MEMORY ACCESS                              | . 55  |

| 5.6.1 Equipment                                         | . 56  |

| 5.6.2 Troubleshooting                                   | . 56  |

| SECTION 6 MNEMONICS                                     |       |

| 6 L TELETYPE CONTROLLER                                 |       |

| 5 2 POWER FAILURE RESTART                               |       |

| 6 3 REAL TIME CLOCK                                     |       |

| 6.4 MEMORY PROTECTION                                   | -     |

| 65 MEMORY PARITY                                        | -     |

| 6 6 PRIORITY MEMORY ACCESS                              | 5 5   |

| LIST OF ILLUSTRATIONS                                   |       |

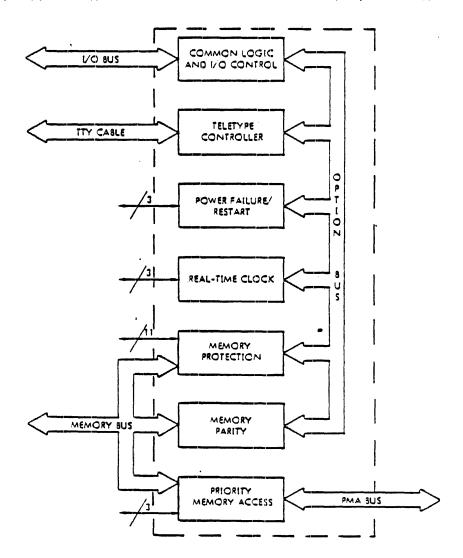

| Figure 1-1. Option Board Block Diagram                  | . 1.7 |

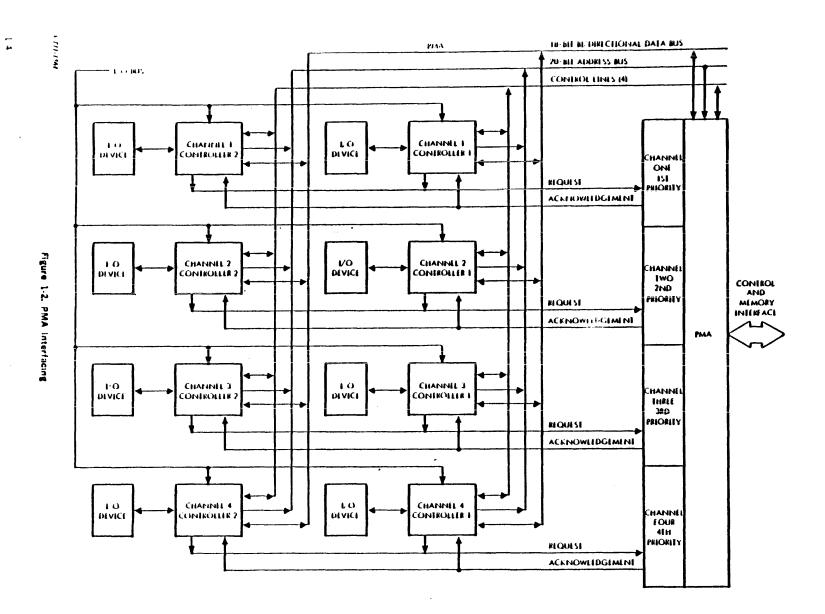

| Figure 1.2. PMA Interfacing                             |       |

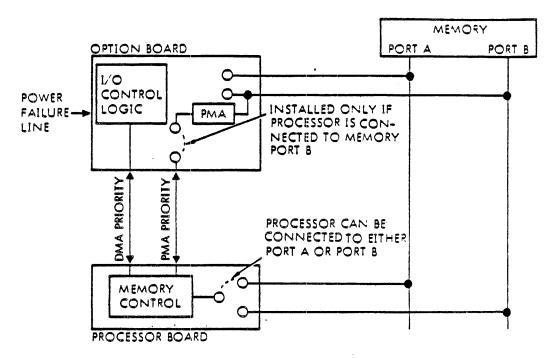

| Figure 1 3. Memory Access                               |       |

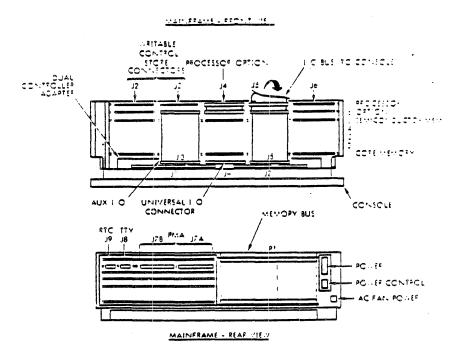

| Figure 2-1. The Option Board Installed                  |       |

| Figure 4-1. Common-Logic Timing for Data-Transfer-In    |       |

| Figure 4-2, TC Block Diagram                            |       |

| Figure 4-3. TC Clock Jumpers for Various Transfer Rates | 4.3   |

| rigure 4.4. Optical Coupler Isolation for  | TC/TTY Interface 4-5                    |

|--------------------------------------------|-----------------------------------------|

| Figure 4-5. Typical TTY Character          | 4.5                                     |

| Figure 4-6. Input Character Sampling       | 4-6                                     |

| Figure 4-7. Maladjusted Input Clock        | 4.6                                     |

| Figure 4-8. TC Software Initialization Tim | ning                                    |

| Figure 4-9. Processor-to-TC Output Timin   | 4.8                                     |

| <del>-</del>                               | 4.9                                     |

|                                            | 4.10                                    |

| - · · · · · · · · · · · · · · · · · · ·    | 4 10                                    |

|                                            | ram                                     |

| -                                          | ver Supply-PF/R Interface 4 14          |

| - · · · · · · · · · · · · · · · · · · ·    | R-Processor Interface                   |

|                                            | Power Supply-PF/R Interface             |

|                                            |                                         |

|                                            | PF/R-Processor Interface                |

| •                                          |                                         |

|                                            | e 4·18                                  |

| •                                          | 4 19                                    |

| · ·                                        | 4 19                                    |

|                                            | ed Load Buffer Timing                   |

| Figure 4-23. Variable-Interval Interrupt T | iming                                   |

| Figure 4-24 Typical RTC Service Routine    | 4.27                                    |

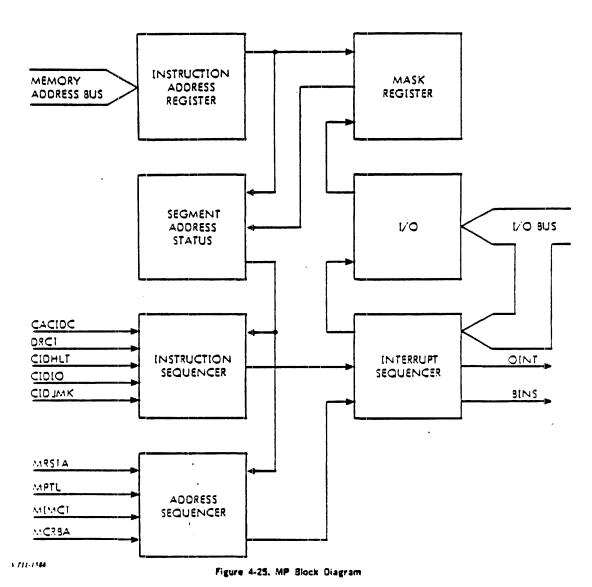

| Figure 4-25. MP Block Diagram              | 4 2 <b>8</b>                            |

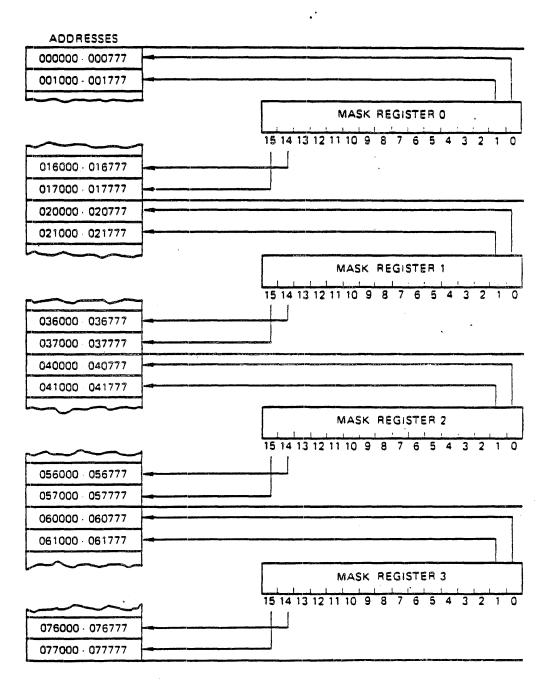

| Figure 4-26. Mask Register Bit Assignme    | nt                                      |

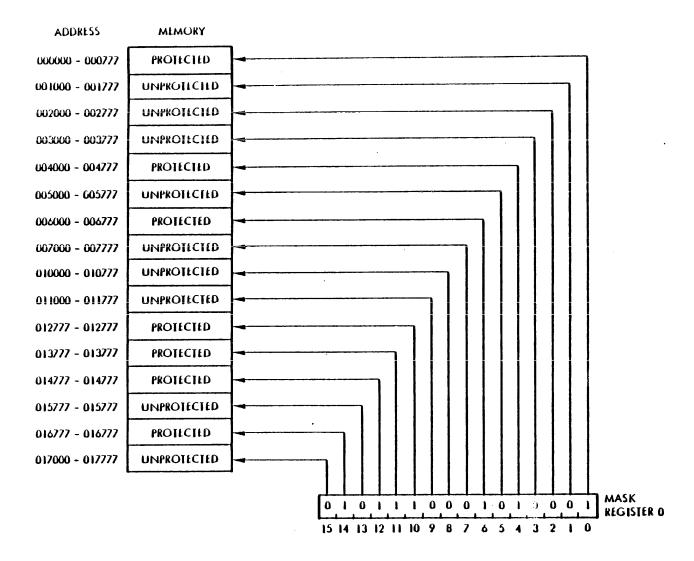

| Figure 4-27. Memory Assignment Example     | e4 3C                                   |

| Figure 4-28 Parity Option                  | <u>.</u>                                |

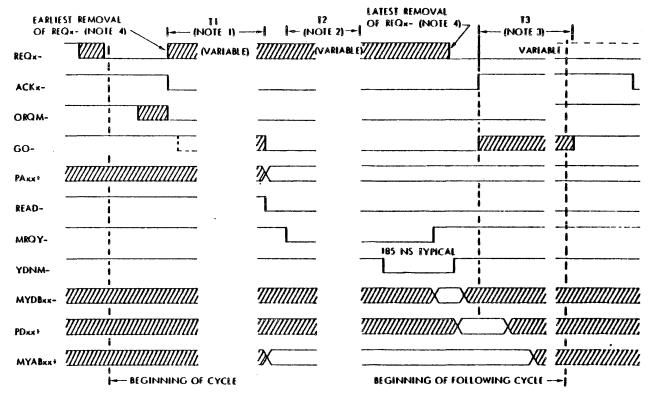

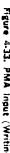

| Figure 4-29. Typical PMA Control-Line-Ou   | ıt                                      |

| Figure 4-30. Typical PMA Bidirectional-Bi  | us Line                                 |

|                                            | ne-In 440                               |

|                                            | 4.41                                    |

| -                                          | 4 42                                    |

|                                            | 4 64                                    |

| -                                          | ram                                     |

|                                            | •                                       |

| LIST                                       | OF TABLES                               |

| Table 1-1. Option Board Configurations     |                                         |

| Table 1-2. Option Board Specifications     |                                         |

| Table 1-3. TC Specifications               | 1 6                                     |

| Table 1-4. PF/R Specifications             | 1.6                                     |

|                                            |                                         |

| ·                                          | 1.7                                     |

| •                                          | *************************************** |

| •                                          | 8 . 1                                   |

|                                            |                                         |

|                                            |                                         |

|                                            | 4.12                                    |

|                                            | 4 20                                    |

|                                            | Design C'n etc.                         |

| Table 4-5. MP Error Conditions Possible    |                                         |

| ·                                          | ected Area4-32                          |

| Table 4-6. MP Error Conditions Possible    | •                                       |

| •                                          | ected Area4-32                          |

| •                                          | Errors                                  |

| Table 4-8. MP I/O Instructions             | 4.35                                    |

|                                            | **************************************  |

# SECTION 1 GENERAL DESCRIPTION

This manual contains the specifications installation information immemories lists maintenance data, and theory of operation for the option board. Depending on the system configuration, the option board contains some or all of the following features.

- · Common logic

- · I O Control logic

- Teletype controller (TC)

- · Keyboard display terminal controller

- · Power failure restart (PF R)

- · Real-time clock (RTC)

- Memory protection (MP)

- · Memory parity logic

- Priority memory access (PMA) (see note)

Note PMA cannot be added in the field

#### 1.1 FUNCTIONAL DESCRIPTION

The V70 Series option board contains mainframe features for the SPERRY UNIVAC V70 Series Computer Systems. Table 1-1 lists the fine available option board configurations together with current requirements for each -5V doperating voltage. The current requirements for the -12V dc and -24V dc operating voltages are listed in table 1-2 and are the same for all configurations.

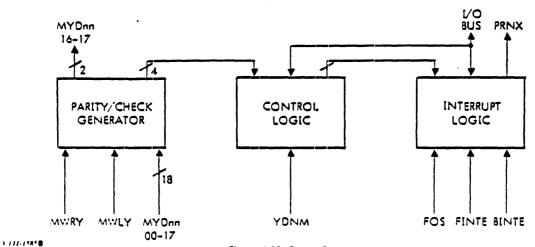

Figure 1-1 is a block diagram of the option board and its interfaces. Communication between the option board and the processor board is through the common logic. Buffer repowering in the common logic reduces the load on the processor. I.O. bus and also reduces the numbers of integrated circuits. (IC) required for the options. The processor. I.O. control section, which is located on the uption board, is discussed in the V70 Series Processor Manual.

#### 1.1.1 Teletype Controller

The Teletype controller (TC) is a control and interface device for data transfers between the processor board and a Model 33 or 35 Teletype. Data is transferred between the processor board and the TC in 8-bit bytes over the IrO bus under either interrupt or sense control. Data is transferred between the TC and the Teletype over a serial, asynchronous, full duplex interface.

Note The keyboard/display terminal (CRT) uses the same controller (with minor modification) as the Teletype Throughout this manual, all references to Teletype (TTY) also pertain to CRT

Table 1-1. Option Board Configurations

|   | Configurations                                                                    | Current   |

|---|-----------------------------------------------------------------------------------|-----------|

| ı | I/O control logic                                                                 | 25 amps   |

| 2 | Common logic, 1:0 control logic, Memor, parity logic                              | 33 amps   |

| 3 | Common logic 1/0 control logic RTC TC/CRT PF R                                    | 5.5 amps  |

| 4 | Common logic   C control logic Memoli, parity logic* RTC, TC CRT PF R             | 59 amps   |

| 5 | Common logic. I O control logic Memity parity logic*, RTC, TC CRT PF R MP         | 79 amps   |

| 6 | Common logic 1 O control logic Memory parity logic : RTC CRT (only) PF R 142      | 79 amps   |

| 7 | Common logic 1.0 control logic Memory parity logic*, RTC TC CRT PF R PMA          | 100 amps  |

| 8 | Common logic, ITO control logic, Memory parity logic*, RTC, TC CRT, PF R, MP, PMA | 12 C amps |

| 9 | Common logic 1 O control logic Memory parity logic*, RTC, CRT (only) PF P MP, PMA | 12.0 amps |

The memory parity logic is functional only when the entire system memory is comprised of optional parity core and or parity semiconductor memory modules (18 bit)

#### 1.1.2 Power Failure/Restart

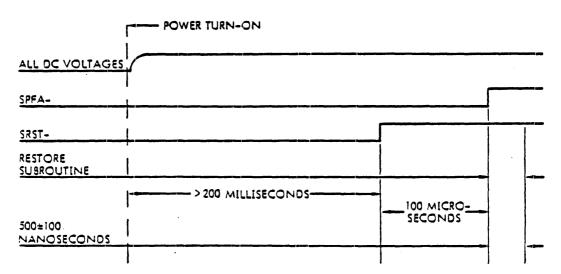

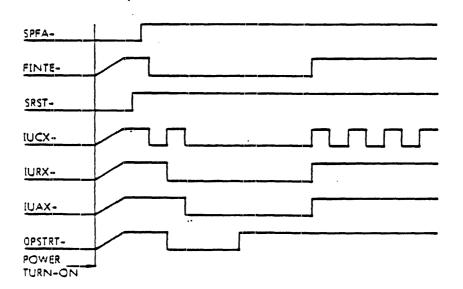

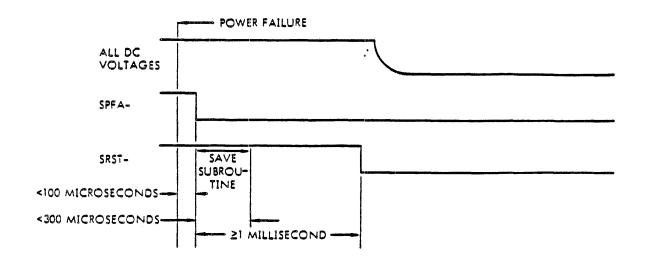

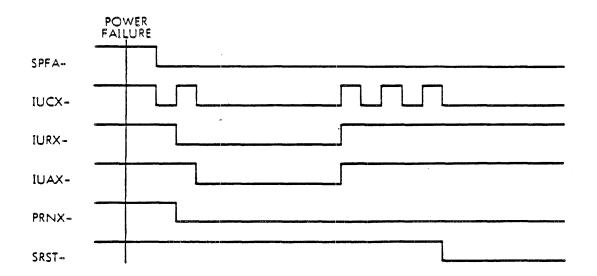

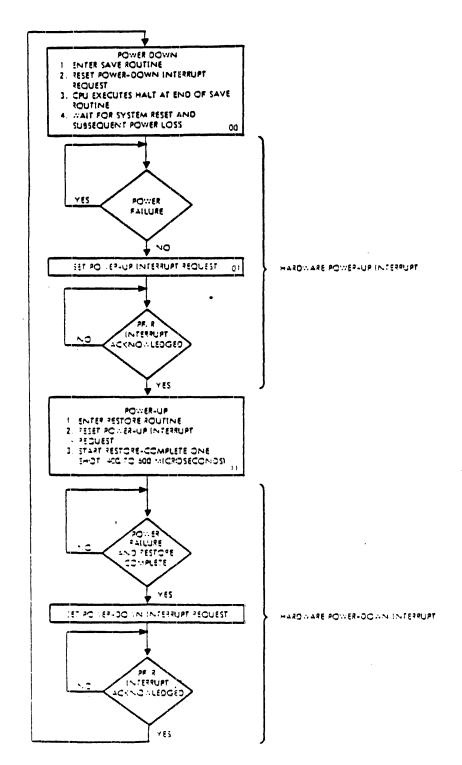

The power failure/restart (PF R) protects during loss or reduction of ac prime power, the program in progress and the contents of computer memory and registers. Upon restoration of power, the PF R automatically restarts, the computer and causes it to reenter the interrupted program at the point of interruption.

Power reduction, failure or turn-off initiates a power-down cycle during which the PF R completes execution of the current instruction and then interrupts the processor directing it to the address of the SAVE subroutine. This service subroutine loads the contents of the volatile registers (A. B. X. P. and overflow) into preselected addresses in memory. After the execution of SAVE, the PF R disables the processor and memory until power is restored.

When power is restored so that all power-up conditions are satisfied, the PF/R enables the processor and memory, initiates the system-start signal, and directs the processor to the address of the RESTORE subroutine. This service subroutine reloads the registers with the saved data, and contains a jump instruction that directs the processor to reenter, the program at the point of interruption and continue execution.

#### 1.1.3 Real-Time Clock

The real-time clock (RTC) provides the following real-time functions:

- Variable-interval interrupt

- Memory-overflow interrupt

- · Readable free-running counter

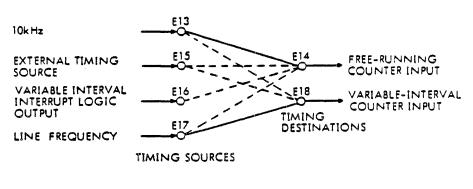

The variable-interval interrupt has three preselectable hardware timing sources: (1) a 10 kHz signal (standard unless otherwise specified), (2) line frequency from the power supply, or (3) a user-supplied external source. The

software-selectable interval can be anywhere in the range one to 4,095.

The memory-overflow interrupt, which operates in conjunction with the Variable-Interval Interrupt (VII), is implemented by loading an increment-memory-and-replace instruction into the VII address. This is monitored by the overflow-detection logic, which triggers the memory-overflow interrupt when the contents of the variable-interval-interrupt are incremented to 040001.

The 16-bit readable free-running counter is continually updated and read under program control. Counter timing is based on the 10kHz-clock, the variable-interval interrupt rate, the line frequency, or a user-supplied external source.

V 711-1460 1

Figure 1-1. Option Board Block Diagram

#### 1.1.4 Memory Protection

Memory protection (MP) prevents unauthorized or unintentional program access to, or modification of, protected areas of memory.

Memory is divided into 512-word segments, each of which can be either protected or unprotected. Segments not designated as protected are, by definition, unprotected. The protected/unprotected status of each segment is stored in the MP in four 16-bit mask registers that are loaded by I/O instructions from the processor. These mask registers can store the status of up to 64 memory segments.

The MP monitors the address of the instruction being processed, the address specified by the next instruction in sequence, and the address specified by the effective address. Using this information and the status of the stored segment, the MP determines and operates on errors.

When a program is executed in unprotected memory, any of the following operations constitutes an error:

- Overflowing into a protected segment

- Writing into a protected segment

- · Jumping into a protected segment

- Executing an I/O instruction in an unprotected segment

- Executing a halt instruction in an unprotected segment.

When the MP detects an error, execution of the current instruction is completed. However, if the instruction specifies writing or I/O operations, the contents of the A. B., and X registers and memory are not modified. Processor program processing is then interrupted and directed to one of five preassigned memory addresses. From this address, the program is directed to a user-written service subroutine for error analysis and correction.

NOTE: By definition, an error cannot exist during the execution of a protected instruction even when it indirectly references an unprotected address.

When the memory map option is installed, memory protection is disabled.

#### 1.1.5 Memory Parity Logic

The memory parity logic generates and checks parity for all memory access. The parity check/generator generates parity on memory writing operations, and checks it on reading operations. The parity control generates an interrupt request when a parity error is detected. The parity logic is functional only when the entire system memory is comprised of optional parity core memory and/or parity semiconductor memory modules (18 bit).

#### 1.1.6 Priority Memory Access

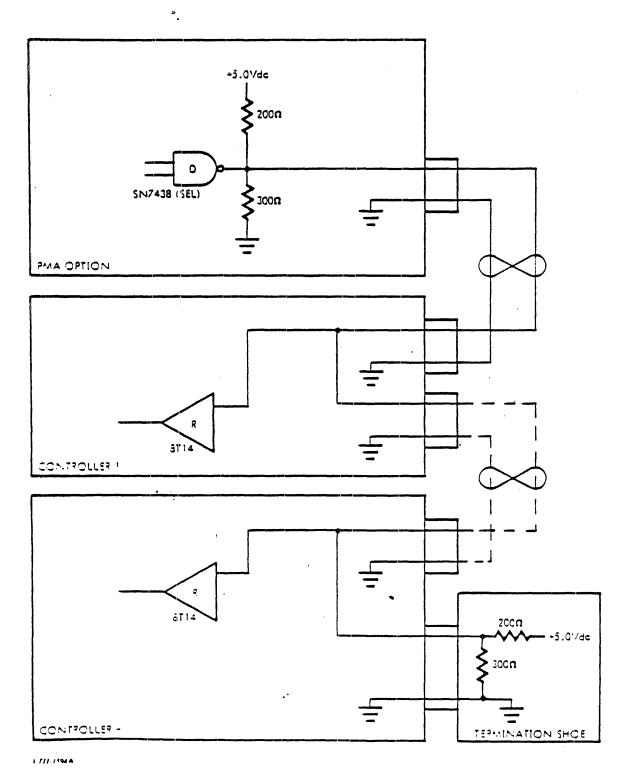

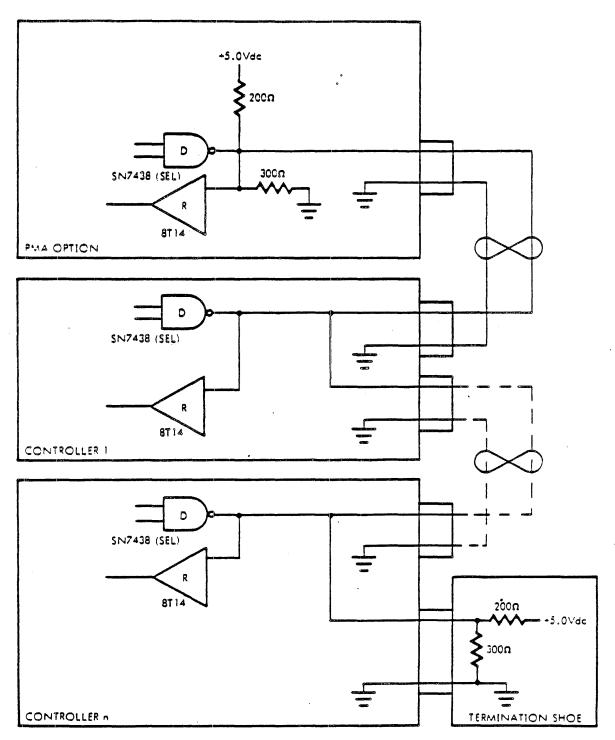

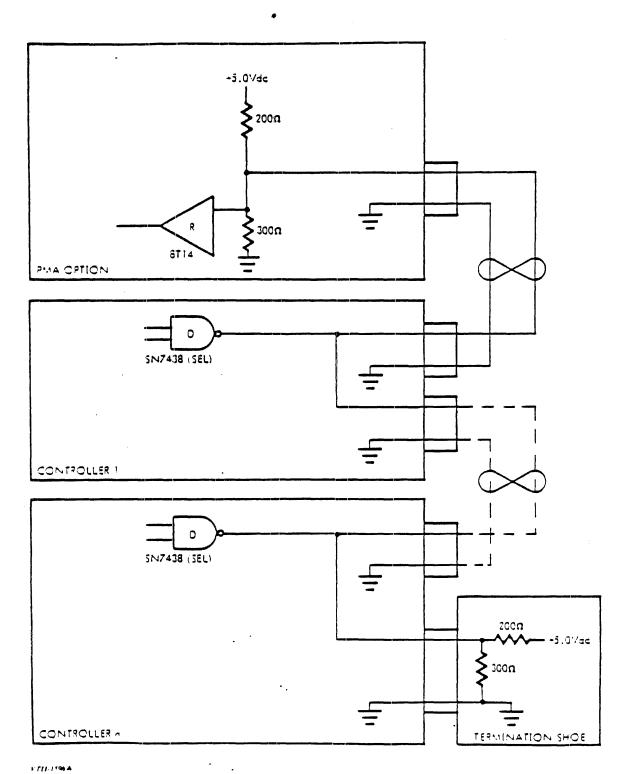

The priority memory access (PMA) is the interface (figure 1-2) between memory and the four data-transfer channels. The channels have hardware-fixed priorities. All signals transmitted on these channels are controlled by an interface scheme that makes the interface independent of circuit and cable speed. This permits processing of data using a wide variety of transfer rates and circuit speeds.

The PMA continuously scans the four channels and generates acknowledgments as required. The order of priority for memory access on the B port is:

- · PMA

- Direct memory access (DMA)

- 620 compatible direct memory access

- Processor

In dual port systems in which the processor is configured on port A, requests to separate memory modules will cause both requests to be serviced at the same time (figure 1-3)

After receiving an acknowledgment, the PMA controller clears the request unless consecutive memory cycles are required, in which case the line remains set. The controller then enables the 20-bit address bus, gates the data onto the 16/18-bit bidirectional bus, and, if a reading operation was requested, enables the read line. When the buses are stable, the data transfer begins. When the PMA detects the memory-data-ready signal from memory, it gates the data to the PMA bus and clears the acknowledgment. For reading operations, the controller uses the trailing edge of the acknowledgment signal to clock the data.

Up to eight controllers can share the PMA option. Where several controllers are connected to a given channel, only one can be active at a time.

The memory access logic scans the PMA and DMA request lines at the main system clock rate. If the lines are not enabled, the processor controls all memory cycles. If the PMA, DMA, or 620 compatible DMA request lines are enabled, the processor is locked out of memory after a request is recognized, and no other unit has access to memory as long as a PMA request is enabled. PMA requests thus take priority over those from the DMA. PMA requests are, however, ignored in case of power failure.

#### 1.2 SPECIFICATIONS

Tables 1-2 through 1-8 contain the physical, electrical, and operational specifications for the option board and each of the options.

Note: The processor, parity, and PMA are all connected to part B on a V72 system.

WT11-1562A

Figure 1-3. Memory Access

Table 1-2. Option Board Specifications

| Parameter               | Description                                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Organization            | Contains circuits for the common logic. I/O control logic, TC, PF R RTC MP memory parity logic, and PMA on a 15.6-by-19-inch (39.6-by-48 3-cm) circuit board.                                |

| Logic Levels            | High: +2.4 to +5.5V dc<br>Low: 0.0 to +0.5V dc                                                                                                                                               |

| Interconnection         | Plugs into the backplane of the computer mainframe, interface signals are routed via card-edge connectors. PMA bus and TC signals pass through separate connectors at the rear of the board. |

| Power requirements      | - 12V dc at 10 milliamperes<br>24V ac at 10 milliamperes<br>+5V dc at 12 amperes (maximum)                                                                                                   |

| Operational Environment | 0 to 50 degrees C; 0 to 90 percent relative humidity without condensation                                                                                                                    |

### GENERAL DESCRIPTION

Table 1-3. TC Specifications

| Parameter          | Description                                                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Organization       | Contains input and output registers, timing control circuitry for simultaneous two-way transmission, and processor/TTY interface logic |

| Peripheral Device  | Sperry Univad modified Model 33 ASR 35 ASR, or 35 KSR Teletype unit                                                                    |

| Transmission Speed | Controlled by TTY: ten characters per sec-<br>ond (100 milliseconds per character) at either<br>random or sustained rate               |

| Modes of Operation | Input: from TTY keyboard or paper-tape reader                                                                                          |

|                    | Output: to TTY printer or paper-tape punch                                                                                             |

| Device Address     | 001                                                                                                                                    |

| Memory Access      | Controlled by the processor                                                                                                            |

| Interrupts         | Write ready and read ready available to PIM                                                                                            |

Table 1-4. PF/R Specifications

٠.

| Parameter           | Description                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------|

| Organization        | Contains sequencer logic, power-up power-<br>down logic, start-processor logic, and<br>interrupt logic |

| Priority Assignment | Second only to MP on 1/0 bus                                                                           |

| Interrupt Addresses | Power-down SAVE subroutine at 040 and 041: power-up RESTORE subroutine at 042 and 043                  |

| Service Subrautines | When power fails, SAVE stores volatile register contents, then halfs the processor                     |

|                     | When power is restored, RESTORE reloads volatile registers, then enables program resumption            |

Table 1-5. RTC Specifications

| Parameter          | Description                                                                                                                                                                                                                                                                                                                                 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modes of Operation | Variable-interval interrupt, memory overflow interrupt, interval accumulation time-of-day accumulation, and event accumulation                                                                                                                                                                                                              |

| FRC Capability     | Counts up to 0177777 with three hardware-ilelectable timing sources                                                                                                                                                                                                                                                                         |

| I- O Capability    | Seven external control and two data transfer instructions                                                                                                                                                                                                                                                                                   |

| Timing Sources     | 10 kHz ± 1 percent, squarewave; variable interval interrupt range 100 microseconds to 409.5 milliseconds (in 100-microsecond increments)                                                                                                                                                                                                    |

| ·                  | Line frequency, derived from 24V rms sinewaye, variable-interval interrupt range (norminal) 16.7 milliseconds to 68.3 seconds (in 16.7-millisecond increments) at 60 Hz, and 20.0 milliseconds to 81.9 seconds (in 20.0-millisecond increments) at 50 Hz.  External timing (user-supplied): minimum positive duration, 5.0 microseconds min |

|                    | imum negative duration 5.0 microseconds                                                                                                                                                                                                                                                                                                     |

| Interrupt Priority | Determined by position on the priority chain                                                                                                                                                                                                                                                                                                |

Table 1-6. MP Specifications

| Parameter           | Description                                         |

|---------------------|-----------------------------------------------------|

| Protection capacity | Up to 64 segments (512-word) of memory              |

| Modes of Operation  | Detects half overflow 1/0, writing, and jump errors |

| Interrupt Priority  | Highest on the I-O bus priority chain               |

| I/O Cacability      | Six external control and eight data transfer        |

Table 1-7. PARITY Specifications

| Parameter          | Description                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Mode of Operation  | Interrupt logic issues interrupt request upon detection of a parity error                                                                  |

| Interrupt Priority | Follows PF/R and MP on the I/O bus                                                                                                         |

| 1/0                | I/O interface via the interval I/O bus logic                                                                                               |

| Bus                | Generates and checks parity on either the A or B bus, but not both. The hardware-selectable bus is the same as that used by the processor. |

#### GENERAL DESCRIPTION

#### Table 1-8. PMA Specifications

| Number of Channels Four, with hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e-assigned priority                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tributed among the four<br>active controller per<br>time) |

| Maximum Cable Length 20 feet (6 meters)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                           |

| Latency (Typical for 530 nanoseconds (m<br>10-foot cable assuming 1190 nanoseconds (d<br>60 nanosecond user<br>controller delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • •                                                       |

| Maximum transfer rate (Typical for 10-foot 1.10 MHz (write cable assuming 60 nanosecond user-controller called a controller delay)  Semiconductor merical 1.10 MHz (write cable assuming for nanosecond user-controller called a controller for memory delay)  1.01 MHz (write called a controller for memory called a | e)<br>d)<br>e)                                            |

| Control Signals Interlocked respons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ses to all signals al-<br>nous operation                  |

| Priority Second only to PF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | я                                                         |

#### 1.3 RELATED DOCUMENTATION

Occuments such as logic diagrams, schematics and parts lists are supplied in a system documentation package. This manual is assembled when the equipment is shipped, and reflects the configuration of a specific system.

The following list contains the part numbers of other manuals pertinent to the V70 series computers (the x at the end of each document number is the revision number and can be any digit 0 through 9):

| Title                             | Manual Number |

|-----------------------------------|---------------|

| V70 Architecture Reference Manual | 98A 9906 00x  |

| V70 Processor Manual              | 98A 9906 02x  |

| V70 Semiconductor Memory Manual   | 98A 9906 04x  |

| V76 System Reference Manual       | 98A 9906 23x  |

| V77-600 System Reference Manual   | 98A 9906 40x  |

| MAINTAIN III Manual               | 98A 9952 07x  |

# SECTION 2 INSTALLATION

This section describes the steps to be taken during the unpacking and installation of the option board, gives a physical description of the board, and lists the pin assignments.

2.1 INSPECTION

The option board has been inspected and packed to ensure its arrival in good working order. To prevent damaging the board, take reasonable care during unpacking and handling. Check the shipping list to ensure that all equipment has been received. Immediately after unpacking, inspect the equipment for shipping damage. If any is found.

- · Notify the transportation company

- · Notify Sperry Univac

- Save all packing material

#### 2.2 PHYSICAL DESCRIPTION

The option board is a 15.6-by-19-inch (39.6-by-48.3-cm) printed circuit (PC) board that mounts in any mainframe chassis slot (figure 2-1).

The integrated circuits (ICs) on the option board are dualin-line, plastic-encased chips. Under certain circumstances, some ceramic ICs are used.

#### 2.3 INTERCONNECTION

The option board interfaces with other system components through card-edge connectors plus connectors mounted at the rear of the board. These connectors carry all signals indicated by the block diagram (figure 1–1) as interfacing with the rest of the system. TC and PMA-bus signals pass through the connectors at the rear of the board to special cables leading to the Teletype and PMA controller (respectively). The memory bus provides the interface between memory and the option board (MP. PARITY, and PMA). Except for the PMA, which does not use the 1.0 bus all 1/0 signals between the CPU and the option board are repowered in the option board common logic and distributed via the option bus within the board.

Option-board pin assignments are listed as part of the logic diagram (9180401) in the system documentation package. The signal mnemonics are defined in section 6

Figure 2-1. Typical Option Board installation

5711-2083A

# SECTION 3 OPERATION

The option board has no operating controls or indicators. Computer operations that affect the option board are explained in the V70 Series Processor Manual

#### **SECTION 4**

#### THEORY OF OPERATION

Option-board logic (logic diagram 9180401) may consist of one or more of the circuit blocks shown in the option board block diagram (figure 1-1). Signal mnemonics for the option board are defined in section 6. As shown in figure 1-1, all option board features (except PMA) are interconnected by the option bus. This bus is the interface between the individual sections and the option board common logic. The common logic in turn is the interface between the option board and the bidirectional I/Q bus which carries data and control signals to and from the rest of the system.

The PMA has its own PMA bus. The three options that deal directly with memory (MP PARITY, and PMA) are also connected to the memory bus.

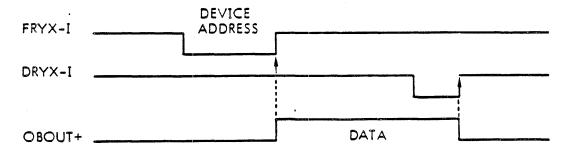

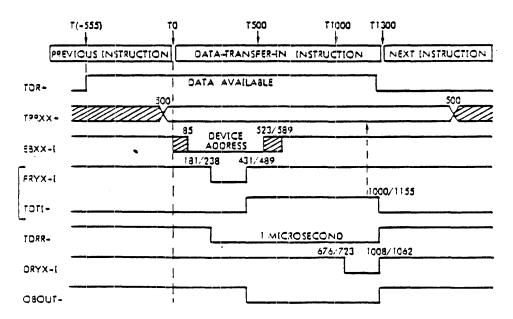

The common logic circuits consist of buffered system control lines (IUJX-1 to OIUJX+, DRYX-1 to ODRYX+, FRYX-1 to OFRYX+, SYRT-1 to OSYRT+, IUAX-1 to OIUAX+, IUCX-I to OIUCX+, and OIURX- via OIURX+ to IURX-1) and a set of mutually exclusive drivers and gates that either transfer data from the option bus (OB00-through OB15-) to the bidirectional I/O bus (EB00-1 through EB15-1) or vice versa. Thus, for a data-transfer-in (timing figure 4-1), receivers are disabled by OBOUTA- and OBOUTB+ while the drivers are enabled by OBOUTA- and OBOUTB+. On data-transfer-out, the reverse is true. LK82+ creates the 12.1212 MHz internal option-board clock.

#### 4.1 TELETYPE CONTROLLER

The Teletype controller (TC) (figure 4-2) consists of the following functional blocks instruction decoding and control logic. MOS transmitter receiver. TC clock, data-transfer-out buffer register, and the TTY interface logic

The instruction decoding and control logic responds to processor data-transmission requests and supplies interrupt signals for priority interrupt module (PIM) control. The TC

decodes the device address (01) from the low-order six bits of the option bus (OB00— through OB05—) producing TDA + after ANDing with not interrupt acknowledge (OIAUX—). If an address is on the option bus, it is recognized when OIUAX + is false. The I=0-TC interface provides for TC initialization and storage for processor-TC data transfers in a two-word format. The control logic generates signals to control other TC logic blocks, including the MOS transmitter-receiver. It also provides logic for external control instructions and initialization.

The MOS transmitter receiver is a single 40-pin chip. It monitors all data transfers between the TC and the TTY including parallel-to-serial data conversion and transmission to the TTY, serial-to-parallel data conversion for transfer from the TTY to the processor, and data flags to the instruction decoding and control logic.

The TC clock supplies timing signals to the MOS transmit ter/receiver and the control logic by counting-down a 24 2424 MHz signal from the processor internal crystal-controlled oscillator. The counter can be programmed using jumpers to vary the transfer rate (figure 4.3).

The data-transfer-out buffer register provides the necessary buffering for data transmission

The TTY interface logic provides a three-line interface from the TC to the TTY. The interface lines are isolated from the TC by optical couplers to control possible high voltages in the TTY interface (up to 140V ac during power surges).

#### 4.1.1 Signal Interfaces

The TC interfaces with the basic computer and a factory modified TTY. No other options are required however, the TC can interface with a PIM to provide character ready interrupts.

V 711-1563

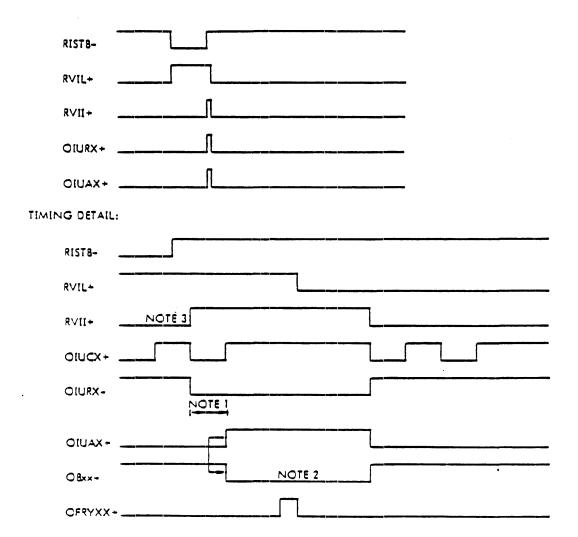

Figure 4-1. Common-Logic Timing for Data-Transfer-In

| BAUD RATE | E42<br>TO<br>E43 | E40<br>TO<br>E41 | E38<br>TO<br>E39 | E36<br>TO<br>E37 | E34<br>TO<br>E35 | OT | E30<br>TO<br>E31 | E28<br>TO<br>E29 | TO | E24<br>TO<br>E25 | TO | E20<br>TO<br>E21 |

|-----------|------------------|------------------|------------------|------------------|------------------|----|------------------|------------------|----|------------------|----|------------------|

| 110 bps * | ×                | X                | X                | x                |                  | X  | X                | X                |    | X                |    | X                |

| 150 bps   | ×                |                  | ×                | x                | X                | x  |                  | ×                | X  | X                | X  |                  |

| 300 bps   |                  | X                | X                |                  | X                | ×  | ×                | x                |    |                  |    |                  |

| 1200 bps  |                  |                  | ×                | ×                |                  |    | ×                | ×                | ×  | ×                |    | ×                |

X = INSTALL JUMPER

\* = 110bps IS STANDARD

VT11-1565A

Figure 4-3. TC Clock Jumpers for Various Transfer Rates

#### 4.1.1.1 Teletype Interface

The TC interfaces a model 33 or 35 TTY via the option board TTY connector. The TTYs are modified at the factory prior to delivery to the customer. To modify the 33 ASR TTY.

- a Set the TTY for 20 mA operation. This includes the addition of a wire that enables the TTY to supply "battery" for the send and receive data loops to the clock card (the TTY is the current source for the TC P optical couplers).

- b. Set the TTY for full-duplex operation.

- c. Disable the WRU contacts.

- d. Disable parity on the keyboard.

- e. Modify the answer-back drum.

- f. Install the 180801 function lever.

The model 35 is similarly modified. Model 33 and 35 TTYs are electrically interfaced and cabled to the TC in almost the same manner, even though they are physically quite different in appearance and in their internal operation.

The cable used for the TC/TTY interface for the 33 ASR runs from S connector plug P2 in the TTY to option board TC connector J8 at the rear of the CPU. The S connector is located at the right rear, top row second connector from the right. The TTY cable is normally 20 feet long with nine leads, three of which are used with standard Teletypes.

The TTY end of the cable (F2) includes two other wires Pins 7, 4, and 5 are interconnected. These connections tie together internal TTY leads prought into the S connector plug as part of the wiring. Note that both ends of the cable are keyed to ensure proper mating.

#### NOTE

The TTY cable is normally installed at the TTY by Sperry Univac before customer delivery. The model 33 TTY requires about 3 amperes of ac power, and the model 35 TTY about 6 amperes.

TTY DESIGN: The 33 ASR is primarily designed for light to medium use. Normally, it is the basic computer input/output device and is the most widely used unit. Its full-duplex operating mode allows simultaneous input and output.

The 35 ASR performs the same function as the 33 ASR, but it is designed for heavy sustained use.

The 35 KSR is used for keyboard send/receive only and lacks the paper tape punch (PTP) and paper tape reader (PTR) capability of the ASR models. The operating characteristics are similar to model 33 keyboard operation. This unit is also designed for heavy, sustained use.

TTY INPUT METHODS: TTY input can be via the keyboard or the PTR. At the keyboard, the operator types at a random rate not greater than 10 characters per second (cps), the maximum rate for TTY input. Standard eight-level paper tapes are read by the PTR at a rate of 10 cps.

TTY OUTPUT METHODS: TTY output is either printed (typed) or punched on paper tape. For the printer or the PTP, the TC sends control codes or data at a random rate or at the maximum output rate of 10 cps. Data are printed, or control functions, such as line feed or carriage return, are performed on the printer. Similarly, control codes regulate the operation of the PTP, and data are punched into eight-level paper tape.

TTY SWITCHES: The ON/OFF switch controls the motor. The power supply and battery for TC relay drivers remain on, independent of this switch.

The line switch controls the TC/TTY interface. In the ON-LINE position, the interface is complete, and the TTY is under CPU control. In the OFF-LINE position, the TTY is independent of the TC, and can be used for printing or preparing tapes.

The following switches control the tape and are not on the 35 KSR. The START, STOP, FREE switch on the PTR causes the tape to move in START, to stop in STOP, and to be released from the sprocket drive wheel in FREE, Pressing BSP on the PTP backspaces the tape one character, Pressing REL removes pressure from the tape. Pressing LOCK ON locks the punch on (prevents change of punch status). Pressing UNLGCK unlocks the punch and enables punch status change by the TC or from the keyboard.

The 35 ASR mode switch mechanism enables the following operating modes.

| Position | Keyboard | Reader   | Printer  | Punch    |

|----------|----------|----------|----------|----------|

| K        | On line  | Disabled | On line  | Off Line |

| KΤ       | On line  | Qn line  | On line  | On line  |

| T        | Off line | On line  | On line  | Off-line |

| TTS      | Off line | On line  | Disabled | Off line |

| TTR      | Off line | Oisabled | Oisapled | On line  |

TTY FUNCTION CODES: The TTY receives the following control codes from the TC that cause it to perform specific functions. An enabling code must follow a disabling code. (Codes R. T. Q. and S are not applicable to the 35 KSR.)

| Code      | Bit Format | Function        |

|-----------|------------|-----------------|

| Control A | 10000001   | Enable printer  |

| Control D | 10000011   | Disable printer |

| Control R | 10010010   | Enable punch    |

| Control T | 10010100   | Disable punch   |

| Cantral Q | 10010001   | Enable reader   |

| Control S | 10010011   | Disable reader  |

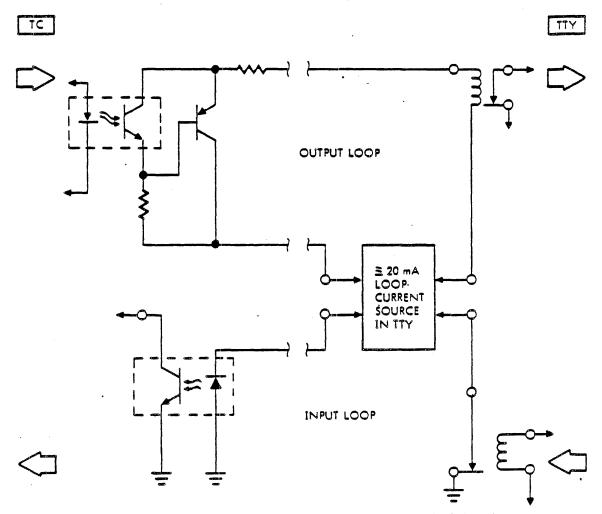

OPTICAL COUPLER ISOLATION: Optical couplers (figure 4.4) in the TC comprise the actual interface between the TC and the TTY. The couplers physically and electrically isolate

the two units. The receiving coupler, is driven by the TTY. The sending coupler, is driven by the TC. The couplers switch approximately 20 milliamperes of current on or off the line. This method of interfacing is called "make/ break". Each coupler can be said to drive or be driven by a current loop. When there is current flowing through a coupler, the current loop is closed. The line is then in the make condition (also referred to as the mark condition). When no current is flowing through the coupler, the current loop is open. The line is then in the break condition (also referred to as the space condition). The steady state of the loops is the mark condition when both the computer and TTY power supplies are on, and both couplers are active. When computer power is off the current loop is maintained on the transmitter via the coupler and is kept in the mark condition. When the TTY power is off, the steady state of the current loop is in the break condition, and neither is active.

Except for the difference in switching control location, the input and output loops have identical functions. The factory-modified system is full-duplex to provide simultaneous transmission of data in both directions.

The current source for the two loops originates in the TTY and is sometimes referred to as "battery." The TC uses no loop source current, since it is isolated by the optical couplers. Typical current in a factory-modified TTY interface loop is 20 mA.

The coupler-controlled current-loop interface method enables the processor-TC and the TTY to be placed far apart without noise interference, ground loops, etc., affecting the system. Normally, the TTY cable is 20 feet long.

When either the TTY or the TC sends data, the optical couplers operate (make or break) to conform to the character pattern being sent. Characters are sent or received serially by the current loop.

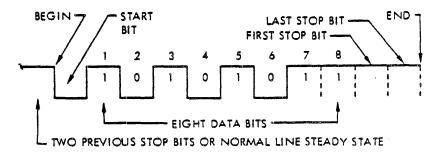

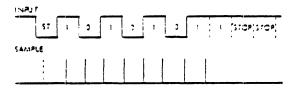

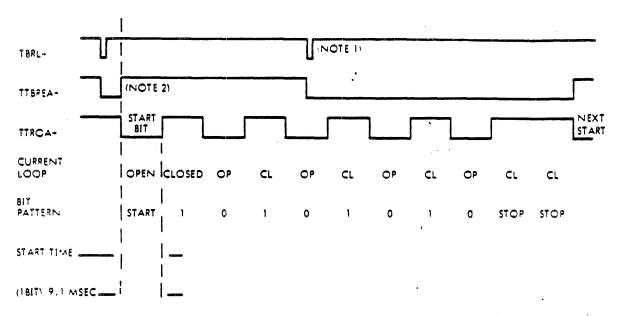

TTY CHARACTER BIT FORMAT: Each Teletype character or command is serial and is divided into 11 periods or bits consisting of one start bit, eight data bits, and two stop bits (see figure 4-5).

The bit pattern for the character shown in figure 4-5 is 10101011. The bit length is 9.1 milliseconds and the bit rate is 110 bits per second (bps). The character length is 100 milliseconds, and the character rate is 10 cps. The start bit is always a space = zero bit = no current in loop = loop open. Data bits are either mark or space. A mark = one bit = current in loop = loop closed.

The eighth data bit is always mark. It can be used by the TTY as an even parity bit (optional). The stop bits in the character bracket the data bits. This simplifies the design and operation of the TC input circuitry.

NOTE: Equivalent, not actual, circuit with two independent current loops for full-duplex operation. The current loops may have a single common current source and return wire. Isolation is achieved by optical couplers.

VT11-1562

Figure 4-4. Optical Coupler Isolation for TC/TTY Interface

VT11-1368

Figure 4-5. Typical TTY Character

#### NOTE

The expression, the ETY is running open, means the send loop to the TTY lacks current = steady spacing condition. This occurs if coupler K2 remains open, if the loop current source fails, or if the send loop opens at any point.

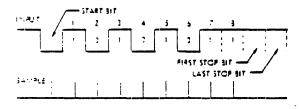

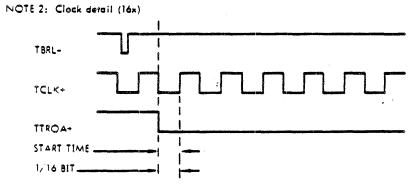

TTY INPUT CHARACTER: The receiving circuitry synchronizes at start-bit time. The bit pattern is sampled and shifted in the center of the start bit and continues at the center of each data bit through to the eighth data bit (figure 4.6), When the last data bit has been sampled and shifted, the character is ready for transfer to permanent storage (e.g., the computer). The TC enables transfer to the CPU at the end of the first stop bit. The stop bit period is used for the transfer of the character to the processor; therefore, these bits are not sampled.

6.411 Vest

Figure 4-6. Input Character Sampling

To keep the receiving unit synchronized with the sending TTY, the receiving oscillator or equivalent timing circuit must be allowed to stop and restart when the start bit for the next character occurs. If the sending device outputs a new start bit before the receiving oscillator has time to stop and recover, the two units are out of synchronization and erroneous data result. The next new character start bit may occur immediately after the stop bit or may not occur for an indefinite time interval. This is typical of asynchronious transmission. The receiving unit must be able to receive and synchronize to new data at any time.

TTY OUTPUT CHARACTER: The TTY is assumed ready to receive data at any time. The TC output sequence begins when a character is loaded in the MOS transmitter. A continuously running oscillator circuit is synchronized when ready to send a start bit. All bit times (start and data) are equal, and each bit takes 16 oscillator periods.

When the last data bit is sent, the TC obtains a new character from the CPU in preparation for the hext character transmission. The oscillator in the TC continues to run during the stop bit. Typically, the TC obtains a new character during the last stop bit. If there are no more output characters, the TC oscillator continues running and places a steady one-bit level on the output line. The TTY can then await a new start bit which occurs on the next output character.

ASYNCHRONOUS TRANSMISSION: The previous paragraphs detailed basic TTY input and output. Several points should be stressed:

- The sending unit transmits at a full or random rate at any time.

- The receiving unit must be able to accept data at any time, at a full or random rate.

- The receiving unit must resynchronize with each new start bit (every character) to maintain proper synchronization.

- d. The length of the output character must be carefully maintained. The receiving circuit can normally tolerate some distortion (less than 1/2 bit per total character). The waveforms of figure 4-7 illustrate an example of proper output character length but maladjusted input timing.

V-711-0558

Figure 4-7. Maladjusted Input Clock

#### 4.1.1.2 PIM Interface

The TC provides two interrupt line outputs: one (IUSB—I) indicates that the input buffer is ready, a second (IUAA—I) indicates that the transmitter is ready for another byte of data. These lines must be wired to PIM interrupt line inputs when it is desired to operate the TTY under interrupt control rather than sense control. The computer system must, of course, contain a PIM to operate under interrupt control.

#### 4.1.2 Circuit Description

The TC operating theory described nervin is a sequential series of functional operations that exercise the TC circuits. To better understand the functional operation of the circuits themselves, refer to logic diagram 9180401 (system documentation package), timing diagrams (figures 4.8 through 4-12), mnemonics (section 6), and interface data (section 4.1.1)

#### 4.1.2.1 Initial Condition

When computer power is first turned on, the TC and the processor circuitry are in an undefined state. Pressing the RESET switch on the control panel initializes the TC (and the processor) to properly perform various functions under program control. This enables the TC to monitor the TTY for input characters and to accept output characters from the processor to the TTY. When initialized, the TC also

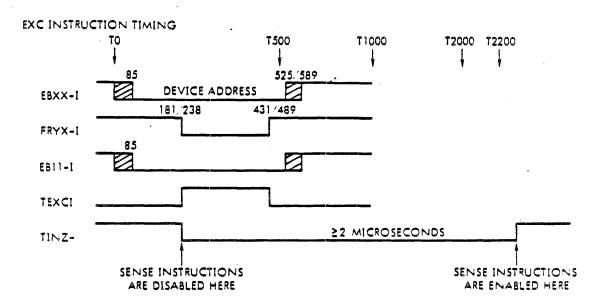

#### SENSE INSTRUCTION TIMING

Figure 4-8. TC Control Timing

transmits a steady mark to the TTY by keeping the transmitting optical coupler active. The TC can also be initialized under program control but the instruction cannot be issued while the TC is in communication with the TTY. Figure 4-8 shows the software initialization timing.

#### NOTE

An initialization instruction performs the same function as pressing the RESET switch.

#### 4.1.2.2 TC/Common-Logic Interface

The processor controls the TC with external control and data transfer instructions via the option bus. When such an instruction is issued, the following device sequence occurs: TDA + is high if the proper address (01) is put

on the option bus and OIUAX + is low (no interrupt or DMA) TDA + high enables the instruction-generation gates

The functions of the option bus signals are OBCO- through OBO5- enable the device address signal TDA+ OBO6- enables the output-ready sense response TTS+. OBCO- enables the input-ready sense response TRS+ in addition, the bidirectional signals OBCO- through OBCO- enable the data-transfer-out buffer register OB11- enables the software reset one-shot, OB12- enables sense response SERX- i, OB13- enables the input sequence, and OB14- enables the output sequence.

OIUAX + inhibits TC selection when the processor has an interrupt or direct memory access (DMA) in process. The processor can issue any of several instructions. All of the following instructions issue a device address and OFRYX + (FRYX+i) and several issue ODRYX + (DRYX+i).

#### THEORY OF OPERATION

- a. Sense output ready (OB06-): OFRYX + only

- b. Sense input ready (OB07-): OFRYX + only

- c. Execute (initialize) (OB11-): OFRYX + only

- d. Output (load transmit buffer register) (OB14--): OFRYX + and ODRYX +

- Input (read input buffer register) (OB13—): OFRYX + and ODRYX +

Figures 4-8, 4-9, and 4-12 contain the timing diagrams for these instructions.

If a sense condition is met, SERX-II goes low. Under sense control a sense instruction is normally issued before input or output. SERX-II low is enabled by either TTBREA + or TRS+, the latter being the AND of TOE- and TDRA+

TTEREA + and TRS + signify respectively that the TC has an input character or is ready to accept an output character.

When initialized, the TC is set to enable immediate output under processor control. TRS + is not true until the TTY has loaded a complete character into the receiving half of the receiver/transmitter.

When the processor issues an output instruction, an OFRYX+/ODRYX+ sequence sets and resets flip-flop TDTO+. When the processor issues an input instruction, an OFRYX+/ODRYX+ sequence sets and resets flip-flop TDTI+.

#### 4.1.2.3 TC Output (Write)

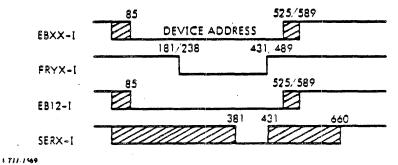

During a TC output operation, portions of the TC common-logic interface, output timing control, the MOS trans-

Figure 4-9. Processor-to-TC Output Timing

NOTE 1: The MOS transmitter is double-buffered to permit loading of a second character at any time during the transmission of the first character except when TTBREA+ is low.

Start time, the negative transition of TTROA+ for the start bit, is on the first negative transition of TCLK+ following the negative, asynchronous TBRL- pulse.

VT11.1571

Figure 4-10. TC Data-Transfer-Out Timing

mitter receiver, and portions of the TC/TTY interface are used. Circuit elements are control flip-flops, a group of gates enabled by the option-bus signals, a programmable free-running clock that is synchronized with the processor, the transmitting half of the MOS transmitter/receiver, and an output coupler to the TTY with associated drivers. The data and control output waveforms illustrate the loading of the output from the processor to the TC and thence to the device (figures 4–9 and 4–10). For these waveforms, as-

sume that the TC has been initialized, the transfer rate is 110 bps, the data is in 11-bit format, the processor has sensed write ready and has issued an output instruction, and the output character is 10101010 binary. Data are output from the processor in a two-word format, the first contains the device address (01) and tee function, and the second is character data. The device address is sampled on the trailing edge of FRYX—I, and data are sampled on the trailing edge of DRYX—I.

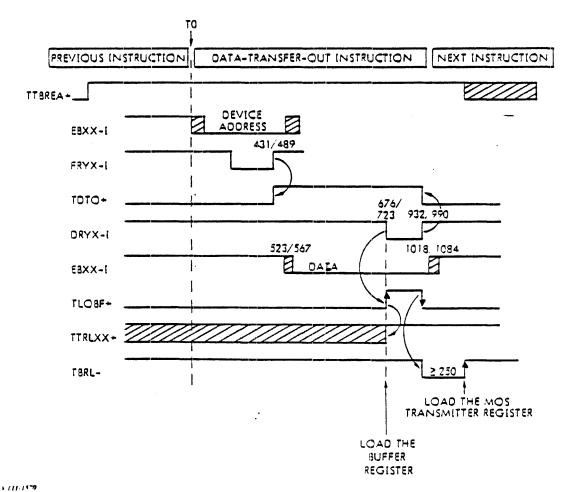

## 4.1.2.4 Loading the Output Buffer and MOS Transmitter

Loading of the output buffer register occurs from the leading to the trailing edge of DRYX-1. The data present on the buffer register inputs at the trailing edge of DRYX-1 are latched into the buffer and presented to the MOS transmitter via TTD80+ through TTD87+. The trailing edge of DRYX-1 also enables the TBRL- loading signal to the MOS transmitter. The character to be transmitted is loaded into the MOS transmitter on the trailing edge of TBRL-.

#### 4.1.2.5 Output to the TTY

When the character to be transmitted has been loaded into the MOS transmitter buffer register, automatic data-

transmission begins. The MOS device generates the startbit, eight data bits, and two stop-bits without the intervention or supervision by the TC. The MOS transmitter serial-output signal TTRO+ goes low to signal, via the optical coupler, the beginning of transmission.

#### 4.1.2.6 TC Input (Read)

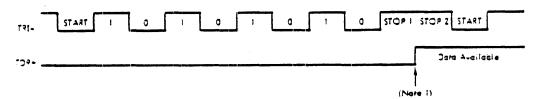

During a TC input operation, portions of the TC/TTY or TC/Infoton interface, input timing control, the MOS transmitter/receiver, and portions of the TC/common-logic interface are used. Circuit elements are control flip-flops, a group of gates to enable the option bus, and an input optical coupler from the TTY. The data and control waveforms illustrate the loading of the input from the device to the TC and thence to the processor (figures 4–11 and 4–12). For these waveforms, assume that the TC has been ini-

NOTE 1: At a continuous transfer rate, the processor has approximately one "character time" to respond and read the character out of the MOS receiver. If an input instruction is not issued during this period, data are last.

+ f11-15°2

Figure 4-11. Input Timing TTY to TC

6 711 15°1

Figure 4-12, TC Oata-Transfer-In Timing

tialized, the device has just begun to transmit a character. and the input optical coupler is deactivated. Character reading is initiated by the negative transition of TRIsignaling the start-bit. From this transition to the positive transition of the data-ready signal TDR+ all operations are under control of the MOS transmitter. The positive transition of TDR+ indicates that the character has been received and loaded into the MOS device. About 500 nanoseconds later the data appear at the MOS device outputs TRR00 + through TRR07 +. The processor has approximately one "character time" to execute a datatransister-in instruction before data are lost. During the execution of this instruction, the common-logic drivers are enabled by OBOUT- low TDRR- clears the TDR flip-flop within the MOS device, and prepares the next character. Data are transferred to the processor on the training edge

#### 4.1.3 Programming

The TC can be programmed directly under processor control (with or without interrupts).

The TC can supply interrupts (input ready and output ready) to the PIM when this option is included in the computer system, thus saving computing time and simplifying software since programmed delay and sense loops can be avoided. With this feature, the program running in the processor is interrupted at the proper time.