## VMICPCI-7696

# Single Board Pentium $II^{@}$ Embedded Module Processor-Based System Slot CompactPCI $^{@}$ CPU

**Product Manual**

#### **FCC**

This card has been tested and met FCC Rules, Part 15, Class B.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference, and

- (2) This device must accept any interference received, including interference that may cause undesired operation.

#### CE

This card has been tested and met the following standards:

EN60950

EN55022

EN61000-3-2

EN61000-4-11

EN61000-4-6

EN61000-4-4

EN61000-4-3

EN61000-4-2

VMIC declares this card meets CE Conformity.

#### **UL1950**

This card has been tested and met UL1950: 1992 (including Amendments A1:1993, A2:1993, A3:1995, and A4:1997).

**Special Considerations:**

- 1) A suitable fire and electrical enclosure shall be provided.

- 2) The input to the unit is considered to be an isolated SELV source.

- 3) A maximum operating base plate of 105 degrees C must be observed .

#### COPYRIGHT AND TRADEMARKS

© Copyright 1999. The information in this document has been carefully checked and is believed to be entirely reliable. While all reasonable efforts to ensure accuracy have been taken in the preparation of this manual, VMIC assumes no responsibility resulting from omissions or errors in this manual, or from the use of information contained herein.

VMIC reserves the right to make any changes, without notice, to this or any of VMIC's products to improve reliability, performance, function, or design.

VMIC does not assume any liability arising out of the application or use of any product or circuit described herein; nor does VMIC convey any license under its patent rights or the rights of others.

For warranty and repair policies, refer to VMIC's Standard Conditions of Sale.

AMXbus, BITMODULE, COSMODULE, DMAbus, Instant OPC wizard logo, IOWorks Access, IOWorks Foundation, IOWorks man figure, IOWorks Manager, IOWorks Server, MAGICWARE, MEGAMODULE, PLC ACCELERATOR (ACCELERATION), Quick Link, RTnet, Soft Logic Link, SRTbus, TESTCAL, "The Next Generation PLC", The PLC Connection, TURBOMODULE, UCLIO, UIOD, UPLC, Visual Soft Logic Control(Ier), VMEaccess, VMEmanager, VMEmonitor, VMEnet, VMEnet, II, and VMEprobe are trademarks. The I/O Experts, The I/O Systems Experts, The Soft Logic Experts, and The Total Solutions Provider are service marks of VMIC.

The I/O man figure, IOWorks, UIOC, Visual IOWorks, and WinUIOC are registered trademarks of VMIC.

ActiveX is a trademark. Microsoft, Microsoft Access, MS-DOS, Visual Basic, Visual C++, Win32, Windows, Windows NT, and XENIX are registered trademarks of Microsoft Corporation.

MMX is a trademark and Celeron is a registered trademark of Intel Corporation.

PICMG and CompactPCI are registered trademarks of PCI Industrial Computer Manufacturers' Group.

Other registered trademarks are the property of their respective owners.

### VMIC

All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless granted express written permission from VMIC.

## Table of Contents

| Overview                           |    |

|------------------------------------|----|

| Organization of the Manual         |    |

| References                         |    |

| Safety Summary                     |    |

| Safety Symbols Used in This Manual | 21 |

| Chapter 1 - Features and Options   | 23 |

| CompactPCI® Features               |    |

| VMICPCI-7696 Product Options       | 27 |

| Chapter 2 - Installation and Setup | 29 |

| Unpacking Procedures               |    |

| Hardware Setup                     |    |

| Installation                       |    |

| BIOS Setup                         |    |

| Front Panel Connectors             |    |

| PMC Site Connector                 |    |

| LED Definition                     |    |

| Chapter 3 - PC/AT Functions        | 41 |

| CPU Socket                         | 42 |

| Physical Memory                    | 42 |

| I/O Port Map                       | 43 |

| PCI-to-PCI Bridge                  | 45 |

| PC/AT Interrupts                   | 45 |

| PCI Interrupts                     | 48 |

| Integrated Peripherals             | 51 |

| Ethernet Controller                |    |

|     | 10BaseT                                       | 52 |

|-----|-----------------------------------------------|----|

|     | 100BaseTx                                     | 52 |

|     | Remote Ethernet Booting                       | 52 |

|     | BootWare Features:                            | 52 |

|     | Video Graphics Adapter                        | 53 |

| Cha | apter 4 - Embedded PC/RTOS Features           | 55 |

|     | Timers                                        | 56 |

|     | General                                       | 56 |

|     | Timer Interrupt Status                        | 56 |

|     | Clearing the Interrupt                        | 57 |

|     | Timer Programming                             |    |

|     | Architecture                                  |    |

|     | Writing                                       | 60 |

|     | Reading                                       |    |

|     | Mode Definitions                              |    |

|     | Flash Disk                                    | 65 |

|     | Configuration                                 | 65 |

|     | Functionality                                 | 66 |

|     | Advanced Configuration                        | 66 |

|     | Flash Disk (Optional)                         | 69 |

|     | Installing the DiskOnChip                     | 69 |

|     | Configuring the DiskOnChip as the Boot Device | 69 |

|     | Configuring the DiskOnChip as the First Drive | 70 |

|     | Watchdog Timer                                | 71 |

|     | Time of Day Registers                         | 73 |

|     | Time of Day Alarm Registers                   | 74 |

|     | Watchdog Alarm Registers                      | 75 |

|     | Command Register                              | 75 |

|     | Battery Backed SRAM                           | 77 |

| Cha | apter 5 - Maintenance                         | 79 |

|     | Maintenance Prints                            | 79 |

|     | J1 Connector Pinout                           | 83 |

|     | J2 Connector and Pinout                       |    |

|     | J3 Connector Pinout                           | 85 |

|     | J5 Connector and Pinout                       | 86 |

|     | Ethernet Connector Pinout (J12)               | 87 |

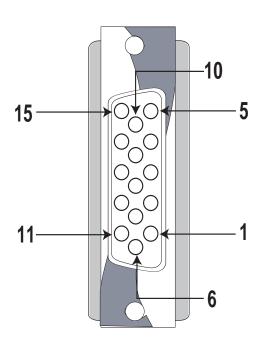

|     | Video Connector Pinout (J11)                  | 88 |

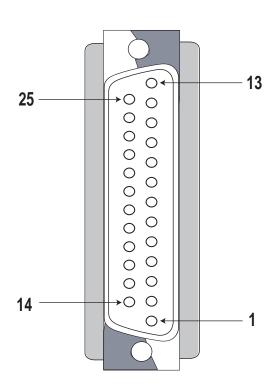

| Parallel Port Connector Pinout (P2)                  |

|------------------------------------------------------|

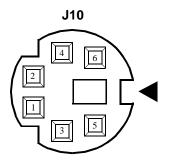

| Keyboard and Mouse Connectors and Pinout (J10)       |

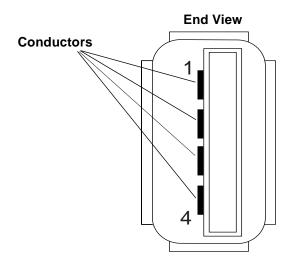

| USB Connector (J9)                                   |

| PMC Connector Pinout                                 |

| PMC J7 Connector and Pinout92                        |

| PMC J6 Connector and Pinout93                        |

| PMC J4 Connector and Pinout94                        |

| 94                                                   |

| Driver Software Installation                         |

| Windows for Workgroups (Version 3.11)                |

| Windows 95                                           |

| Windows 95 INF Update Utility for Intel(TM) Chipsets |

| Bus Master IDE Driver for Windows 95                 |

| Windows NT (Version 4.0)                             |

| System BIOS Setup Utility                            |

| BIOS Features Setup                                  |

| LANWorks BIOS Setup                                  |

| Boot Protocol                                        |

| Default Boot                                         |

| Local Boot                                           |

| System BIOS Setup Utility                            |

| Standard CMOS Setup                                  |

| Setting The Date                                     |

| Setting The Time                                     |

| Primary Master/Slave                                 |

| Secondary Master/Slave 112                           |

| Floppy Disk Drive                                    |

| Floppy Drive A                                       |

| Floppy Drive B                                       |

| Video                                                |

| Halt On                                              |

| Memory                                               |

| BIOS Features Setup                                  |

| Virus Warning 114                                    |

| CPU Internal Cache                                   |

| External Cache                                       |

| CPU L2 Cache ECC Checking                            |

| Quick Power On Self Test                             |

|     | Boot From Lan First        | 115 |

|-----|----------------------------|-----|

|     | Boot Sequence              | 115 |

|     | Swap Floppy Drive          | 115 |

|     | Boot Up Floppy Seek        | 115 |

|     | Boot Up NumLock Status     | 115 |

|     | Gate A20 Option            | 116 |

|     | Typematic Rate Setting     | 116 |

|     | Typematic Rate (Chars/Sec) | 116 |

|     | Typematic Delay (Msec)     | 116 |

|     | Security Option            | 116 |

|     | PCI/VGA Palette Snoop      | 116 |

|     | Assign IRQ for VGA         | 116 |

|     | OS Select For DRAM>64MB    | 116 |

|     | HDD S.M.A.R.T. Capability  | 117 |

|     | Report No FDD For WIN95    | 117 |

| Chi | pset Features Setup        | 118 |

|     | Advanced Options           | 118 |

|     | SDRAM(CAS Lat/RAS-to-CAS)  | 118 |

|     | SDRAM RAS Precharge Time   | 118 |

|     | SDRAM CAS Latency Time     | 119 |

|     | SDRAM Precharge Control    | 119 |

|     | DRAM Data Integrity Mode   | 119 |

|     | System BIOS Cacheable      | 119 |

|     | Video RAM Cacheable        | 119 |

|     | 8 Bit I/O Recovery Time    | 119 |

|     | 16 Bit I/O Recovery Time   | 119 |

|     | Memory Hole at 15M-16M     | 120 |

|     | Passive Release            | 120 |

|     | Delayed Transaction        | 120 |

|     | AGP Aperture Size (MB)     | 120 |

|     | CPU Warning Temperature    | 120 |

|     | CPU Shutdown               | 120 |

| Po۱ | wer Management             | 121 |

|     | ACPI Function              | 121 |

|     | Power Management           | 121 |

|     | PM Control by APM          | 122 |

|     | Video Off Method           | 122 |

|     | Video Off After            | 122 |

|      | Modem Use IRQ                     | 122 |

|------|-----------------------------------|-----|

|      | Doze Mode                         | 122 |

|      | Standby Mode                      | 122 |

|      | Suspend Mode                      | 122 |

|      | HDD Power Down                    | 122 |

|      | Throttle Duty Cycle               | 123 |

|      | VGA Active Monitor                | 123 |

|      | Resume By Ring                    | 123 |

|      | Resume By Alarm                   | 123 |

|      | Wake Up On LAN                    | 123 |

|      | CPU Clock Throttle                | 123 |

|      | IRQ 8 Break Suspend               | 123 |

|      | Reload Global Timer Events        | 123 |

| PnF  | P/PCI Configuration               | 124 |

|      | PNP OS Installed                  | 124 |

|      | Resources Controlled By           | 124 |

|      | Reset Configuration Data          | 124 |

|      | IRQ n Assigned to                 | 125 |

|      | DMA n Assigned to                 | 125 |

|      | Used Mem Base Addr                | 125 |

| Inte | grated Peripherals                | 126 |

|      | IDE HDD Block Mode                | 126 |

|      | IDE Primary Master PIO            | 126 |

|      | IDE Primary Slave PIO             | 126 |

|      | IDE Primary/Secondary Master UDMA | 127 |

|      | IDE Primary/Secondary Slave UDMA  | 127 |

|      | On-Chip Primary PCI IDE           | 127 |

|      | On-Chip Secondary PCI IDE         | 127 |

|      | Onboard PCI SCSI Chip             | 127 |

|      | USB Keyboard Support              | 127 |

|      | Init Display First                | 127 |

|      | Onboard FDC Controller            | 127 |

|      | Onboard Serial Port 1/2           | 128 |

|      | UART 2 Mode                       | 128 |

|      | Onboard Parallel Port             | 128 |

|      | Parallel Port Mode                | 128 |

| BIC  | S Operations                      | 130 |

|      | BIOS Control Overview             | 130 |

| Functional Overview         |  |

|-----------------------------|--|

| Data Book References        |  |

| Device Address Definition   |  |

| ISA Devices                 |  |

| PCI Devices                 |  |

| Device Interrupt Definition |  |

| PC/AT Interrupt Definition  |  |

| ISA Device Interrupt Map    |  |

| PCI Device Interrupt Map    |  |

| Directory SRAM              |  |

| **File: T_SRAM.C            |  |

| Directory Timers            |  |

| **File: CPU.H               |  |

| ** File: PCI.H              |  |

| **File: PCI.C               |  |

| **File: T_Timers.C          |  |

| **File: Timer.C             |  |

| Directory WATCHDOG          |  |

| **File: Watchdog.H          |  |

| **File: WDT0_RST.C          |  |

## List of Figures

| Figure 1-1  | VMICPCI-7696 Block Diagram                                     | 25  |

|-------------|----------------------------------------------------------------|-----|

| Figure 2-1  | VMICPCI-7696 Embedded Module, and Jumper Locations             | 32  |

| Figure 2-2  | Installing a PMC Card on the VMICPCI-7696                      | 38  |

| Figure 2-3  | Front Panel LED Positions                                      | 39  |

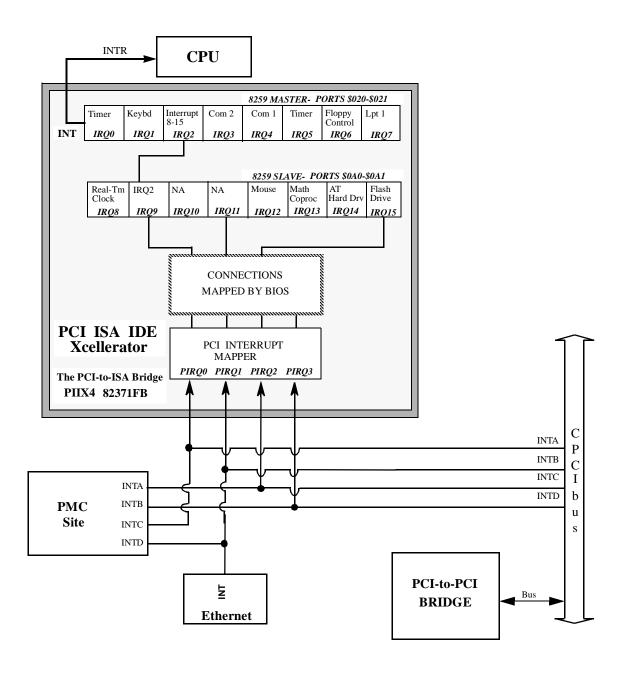

| Figure 3-1  | Connections for the PC Interrupt Logic Controller              | 50  |

| Figure 4-1  | Timer Interrupt Status Register Read/Steps                     | 56  |

| Figure 4-2  | Timer Interrupt Status Register                                | 57  |

| Figure 4-3  | Clearing the Timer Interrupt Status Register                   | 57  |

| Figure 4-4  | 82C54 Diagram                                                  | 58  |

| Figure 4-5  | Internal Timer Diagram                                         | 59  |

| Figure 4-6  | Typical System Configuration                                   | 65  |

| Figure 4-7  | Watchdog Alarm Block                                           | 71  |

| Figure A-1  | VMICPCI-7696 Connector and Jumper Locations                    | 82  |

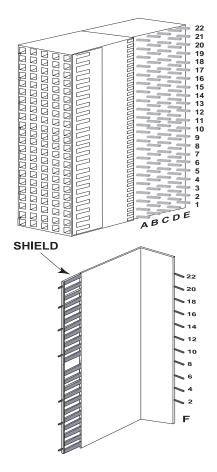

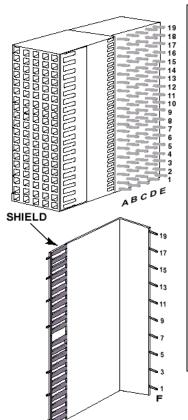

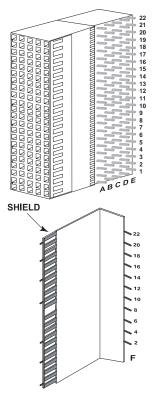

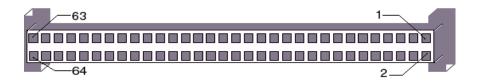

| Figure A-2  | J1 Connector and Pinout                                        | 83  |

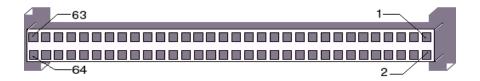

| Figure A-3  | J2 Connector and Pinout                                        | 84  |

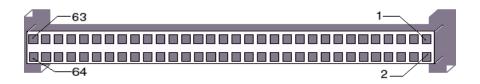

| Figure A-4  | J3 Connector and Pinout                                        | 85  |

| Figure A-5  | J5 Connector and Pinout                                        | 86  |

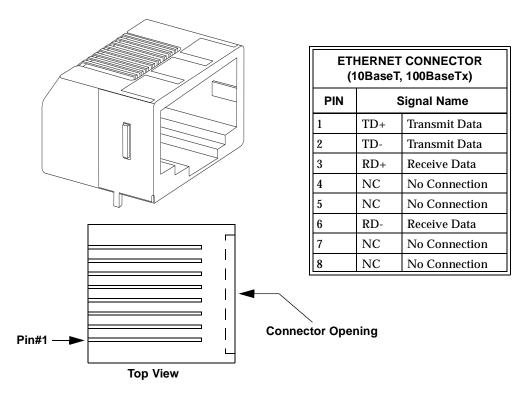

| Figure A-6: | Ethernet Connector and Pinout                                  | 87  |

| Figure A-7  | Video Connector and Pinout                                     | 88  |

| Figure A-8  | P2 Connector and Pinout                                        | 89  |

| Figure A-9  | Keyboard/Mouse Connector and Pinout                            | 90  |

| Figure A-10 | USB Connector Pinout                                           | 91  |

| Figure E-1  | VMICPCI-7696 Block Diagram                                     | 131 |

| Figure E-2  | BIOS Default Connections for the PC Interrupt Logic Controller | 138 |

VMICPCI-7696 Product Manual

## List of Tables

| Table 1-1  | PC/AT I/O Features                                               | 24 |

|------------|------------------------------------------------------------------|----|

| Table 2-1  | CPU Board Connectors                                             | 33 |

| Table 2-2  | Password Clear (User Configurable) - Jumper (E3)                 | 33 |

| Table 2-3  | Factory Configured - AGP Enable Jumper E4 (Not Populated)        | 34 |

| Table 2-4  | Factory Configured - Host Frequency Jumper E5 (Not Populated)    | 34 |

| Table 2-5  | Factory Configured - PIIX4E Battery Jumper (E6)                  | 34 |

| Table 2-6  | Factory Configured - Watchdog Timer jumper (E7)                  | 34 |

| Table 2-7  | Factory Configured - Clock Speed Select Jumper (E8)              | 34 |

| Table 2-8  | Factory Configured - SRAM Battery Jumper (E10)                   | 35 |

| Table 2-9  | Programmable Timer Clock Select (User Configurable) Jumper (E11) | 35 |

| Table 2-10 | Factory Configured - Reserved Jumper (E12)                       | 35 |

| Table 2-11 | Factory Configured - DiskOnChip Address SEL Jumper (E13)         | 35 |

| Table 2-12 | Factory Configured - Boot Block Lock Jumper (E17)                | 35 |

| Table 2-13 | Factory Configured - Boot Block Lock (E18)                       | 35 |

| Table 3-1  | VMICPCI-7696 I/O Address Map                                     | 43 |

| Table 3-2  | PC/AT Hardware Interrupt Line Assignments                        | 45 |

| Table 3-3  | PC/AT Interrupt Vector Table                                     | 46 |

| Table 3-4  | NMI Register Bit Descriptions                                    | 49 |

| Table 3-5  | Supported Graphics Video Resolutions                             | 53 |

| Table 4-1  | I/O Address of the Control Word Register and Timers              | 57 |

| Table 4-2  | Control Word Format                                              | 60 |

| Table 4-3  | ST - Select Timer                                                | 60 |

| Table 4-4  | RW - Read/Write                                                  | 60 |

|            |                                                                  |    |

| Table 4-5  | M - Mode 6 <sup>2</sup>                                    | 1  |

|------------|------------------------------------------------------------|----|

| Table 4-6  | BCD6                                                       | 1  |

| Table 4-7  | Read-Back Command Format                                   | 2  |

| Table 4-8  | Read-Back Command Description62                            | 2  |

| Table 4-9  | Status Byte                                                | 3  |

| Table 4-10 | Status Byte Description                                    | 3  |

| Table 4-11 | LOAD Bit Operation 65                                      | 3  |

| Table 4-12 | Watchdog Registers72                                       | 2  |

| Table 4-13 | Time of Day Alarm Registers                                | 4  |

| Table A-14 | Keyboard/Mouse Y Splitter Cable                            | 0  |

| Table A-1  | PMC J7 Connector Pinout                                    | 2  |

| Table A-2  | PMC J6 Connector Pinout93                                  | 3  |

| Table A-3  | PMC J4 Connector Pinout94                                  | 4  |

| Table E-1  | ISA Device Mapping Configuration                           | 35 |

| Table E-2  | PCI Device Mapping Configuration                           | 36 |

| Table E-3  | PCI Device Interrupt Mapping by the BIOS                   | 39 |

| Table E-4  | Default PIRQx to IRQx BIOS Mapping with all Devices Loaded | 40 |

## **Overview**

#### Introduction

VMIC's VMICPCI-7696 is a complete IBM PC/AT-compatible Pentium II Embedded Module processor-based computer with the additional benefits of Eurocard construction and full compatibility with the CompactPCI Specification Rev. 2.1. The VMICPCI-7696 with advanced CPCI interface and SDRAM that is dual-ported to the CPCI bus, is ideal for CPCI system controller applications.

The single-slot CPU board functions as a standard PC/AT, executing a PC/AT-type power-on self-test, then boots up MS-DOS, Windows 3.11, Windows 95, Windows NT, or any other PC/AT-compatible operating system. The PC/AT mode of the VMICPCI-7696 is discussed in Chapter 3 of this manual.

The VMICPCI-7696 also operates as a CPCI peripheral slot CPU and interacts with other CPCI modules via the on-board embedded bridge.

The VMICPCI-7696 programmer may quickly and easily control CPCI bus functions simply by linking to a library of interrupt and control functions. This library is available with VMIC's VMISFT-9421 IOWorks Access software for Windows NT users.

The VMICPCI-7696 also provides capabilities beyond the features of a typical PC/AT compatible CPU including general-purpose timers, a programmable watchdog timer, a bootable flash disk system, remote LANboot, and nonvolatile, battery-backed SRAM. These features make the unit ideal for embedded applications. These nonstandard PC/AT functions are discussed in Chapter 4 of this manual.

### **Organization of the Manual**

This manual is composed of the following chapters and appendices:

**Chapter 1 - VMICPCI-7696 Features and Options** describes the features of the base unit followed by descriptions of the associated features of the unit in operation on a CPCI bus.

**Chapter 2 - Installation and Setup** describes unpacking, inspection, hardware jumper settings, connector definitions, installation, system setup, and operation of the VMICPCI-7696.

**Chapter 3 - PC/AT Functions** describes the unit design in terms of the standard PC memory and I/O maps, along with the standard interrupt architecture.

**Chapter 4 - Embedded PC/RTOS Features** describes the unit features that are beyond standard PC/AT functions.

**Chapter 5** - **Maintenance** provides information relative to the care and maintenance of the unit.

**Appendix A - Connector Pinouts** illustrates and defines the connectors included in the unit's I/O ports.

**Appendix B - LANWorks BIOS** describes the menus and options associated with the LANWorks BIOS.

**Appendix C** - **Basic Input/Output System** describes the menus and options associated with the Award (system) BIOS.

**Appendix D** - **Device Configuration:** I/O and Interrupt Control provides the user with the information needed to develop custom applications such as the revision of the current BIOS configuration to a user-specific configuration.

#### References

For the most up-to-date specifications for the VMICPCI-7696, please refer to:

#### VMIC specification number 800-657602-000

#### Pentium II® Processor with MMX™ Technology

January 1997, Order Number 243185-001 Intel Corporation 2200 Mission College Blvd. P.O. Box 58119 Santa Clara, CA 95052-8119 (408) 765-8080

#### Intel 82440BX AGP set: 82443BX Host Bridge/Controller

Intel Corporation 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119

#### Intel 21554 Embedded PCI Bridge

Intel Corporation 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119

#### Intel 21143 10/100 Mb/s Ethernet LAN Controller

Intel Corporation 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119

#### Intel 82440BX PCIset ISA Bridge

82371EB PCI ISA IDE Xcellerator (PIIX4E) 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119

#### PCI Local Bus Specification, Rev. 2.1

PCI Special Interest Group P.O. Box 14070 Portland, OR 97214 (800) 433-5177 (U.S.) (503) 797-4207 (International) (503) 234-6762 (FAX)

#### SMC FDC37C67X Enhanced Super I/O Controller

SMC Component Products Division 300 Kennedy Drive Hauppauge, NY 11788 (516) 435-6000 (516) 231-6004 (FAX)

#### ISA & EISA, Theory and Operation

Solari, Edward Annabooks 15010 Avenue of Science, Suite 101 San Diego, CA 92128 USA ISBN 0-929392 -15-9

#### 82C54 CHMOS Programmable Internal Timer

Intel Corporation 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119

#### Flash ChipSet Product Manual

SanDisk Corporation 140 Caspian Court Sunnyvale, CA 94089-9820

#### DS 1384 Watchdog Timekeeping Controller

Dallas Semiconductor 4461 South Beltwood Pwky. Dallas, TX 75244-3292

#### M-Systems Corporate Headquarters

USA Office 39899 Balentine Dr. Suite 335 Newark, CA 94560 Tel: 510-413-5950 Fax: 510-413-5980 Email: info@m-sys.com

#### S3 Trio 3d AGP Video Controller

P.O. Box 58058 Santa Clara, CA 95052-8058 (408) 588-8000

#### CMC Specification, P1386/Draft 2.0 from:

IEEE Standards Department Copyrights and Permissions 445 Hoes Lanes, P.O. Box 1331 Piscataway, NJ 08855-1331, USA

#### PMC Specification, P1386.1/Draft 2.0 from:

IEEE Standards Department Copyrights and Permissions 445 Hoes Lanes, P.O. Box 1331 Piscataway, NJ 08855-1331, USA For a detailed description and specification of the CompactPCI bus, please refer to:

#### CompactPCI™ Specification PICMG 2.0 R2.1

PCI Industrial Computer Manufactures' Group 301 Edgewater Place Suite 220 Wakefield, MA 01880 (617) 224-1100 (617) 224-1239 (FAX) www.picmg.org (Web)

The following is useful information related to remote ethernet booting of the VMICPCI-7696:

#### Microsoft Windows NT Server Resource Kit

Microsoft Corporation ISBN: 1-57231-344-7 www.microsoft.com

#### **Safety Summary**

The following general safety precautions must be observed during all phases of the operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product.

VMIC assumes no liability for the customer's failure to comply with these requirements.

#### **Ground the System**

To minimize shock hazard, the chassis and system cabinet must be connected to an electrical ground. A three-conductor AC power cable should be used. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet.

#### Do Not Operate in an Explosive Atmosphere

Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.

#### **Keep Away from Live Circuits**

Operating personnel must not remove product covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone

Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.

#### Do Not Substitute Parts or Modify System

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to VMIC for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings**

Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing, and adjusting.

#### Safety Symbols Used in This Manual

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 V are so marked).

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. Before operating the equipment, terminal marked with this symbol must be connected to ground in the manner described in the installation (operation) manual.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

The STOP symbol informs the operator the that a practice or procedure should not be performed. Actions could result in injury or death to personnel, or could result in damage to or destruction of part or all of the system.

The WARNING sign denotes a hazard. It calls attention to a procedure, a practice, a condition, which, if not correctly performed or adhered to, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, a practice, or a condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

The NOTE sign denotes important information. It calls attention to a procedure, a practice, a condition or the like, which is essential to highlight.

VMICPCI-7696 Product Manual

## Features and Options

#### **Contents**

| CompactPCI® Features         | <br>26 |

|------------------------------|--------|

| VMICPCI-7696 Product Options | <br>27 |

#### Introduction

The VMICPCI-7696 performs all the functions of a standard IBM PC/AT motherboard with the following features:

- Single-slot CPCI bus 6U Eurocard form factor

- Includes a high-performance Intel Pentium II® Embedded Module processor

- Up to 256 Mbyte of Synchronous DRAM

- AGP video with 4 Mbyte SDRAM

- Real-time clock/calendar

- · Front panel reset switch and miniature speaker

- Onboard port for keyboard and mouse

- UltraEIDE hard drive, floppy drive through the CPCI J3 connector

- Onboard fast Ethernet controller supporting 10BaseT and 100BaseTX interfaces

- Front panel "vital sign" indicators (power, UltraEIDE hard drive activity, Ready, and Ethernet status)

- Three general-purpose programmable 16-bit timers

- Software-selectable watchdog timer with reset

- Optional M-Systems DiskOnChip flash memory (12 to 72 Mbyte available)

- 16 Mbyte of bootable flash on secondary IDE

- · 32 Kbyte of battery-backed SRAM

- Two Serial ports, one available by way of the front panel RJ11 connector and both available through the CPCI J3 connector

- One enhanced parallel port available on the front panel and through the CPCI J3 connector

- Two USB Ports: one available on the front panel, and one through the CPCI J3 connector (rear I/O)

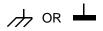

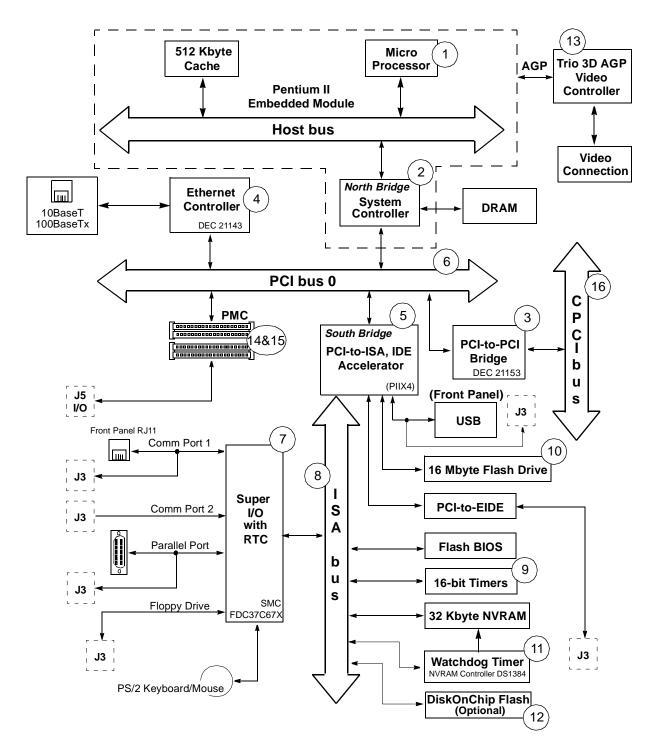

The VMICPCI-7696 supports standard PC/AT I/O features such as those listed in Table 1-1. Figure 1-1 on page 25 shows a block diagram of the VMICPCI-7696 emphasizing the I/O features, including the PCI-to-PCI bridge. The serial, parallel, IDE, and floppy signals are also routed through the backplane to VMIC's (optional) VMIACC-0576 CompactPCI Rear Transition Utility Board.

Table 1-1 PC/AT I/O Features

| I/O FEATURE                                                                             | IDENTIFIER            | PHYSICAL ACCESS                                                             |

|-----------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|

| Two high-performance<br>16550-compatible serial port                                    | COM1, COM2            | One through the front panel RJ11, both through CPCI J3 Connector (See Note) |

| One Enhanced Parallel Port, Supports<br>ECP/EPP Modes                                   | Parallel              | Through front panel and CPCI J3 connector (See Note)                        |

| AT-Style Keyboard/Mouse Controller                                                      | M/K                   | Front Panel PS/2-Style Connector, Mini-DIN<br>Circular (female)             |

| AGP Video Controller with 4 Mbyte<br>SDRAM                                              | SVGA                  | Front Panel DB15HD High Density (female)                                    |

| Real-Time Clock/Calendar with miniature speaker                                         | Date, Time, and sound |                                                                             |

| On-board fast Ethernet controller<br>supporting 10BaseT and 100BaseTX<br>interfaces     | LAN                   | Front Panel R-J45                                                           |

| Floppy Disk Controller                                                                  | Drive A               | Through CPCI J3 (See Note)                                                  |

| Ultra EIDE Hard Drive Controller                                                        | Drive C               | Through CPCI J3 (See Note)                                                  |

| Two USB Ports                                                                           | USB                   | One through the front panel, the other through CPCI J3                      |

| Hardware Reset                                                                          | RST                   | Front Panel Push-Button                                                     |

| Power Status, Hard Drive Activity,<br>Ready, and Ethernet Status for each<br>controller | LED Indicators        | Front Panel                                                                 |

The VMIACC-0576 CompactPCI Rear Transition Utility Board provides USB, RJ-45 serial port connectors (2), standard (DB25) parallel port connector, IDE and Floppy connectors, by way of the CompactPCI backplane Connector (J3).

Figure 1-1 VMICPCI-7696 Block Diagram

### CompactPCI® Features

In addition to its PC/AT functions, the VMICPCI-7696 has the following CompactPCI features:

- · Single-slot, 6U height CPCI board

- Complies fully with Revision 2.1 of the PCI Local Bus Specification

- Complies fully with Revision 1.1 of the *PCI-to-PCI Bridge Architecture Specification*

- Complies with Revision 2.1 of the CompactPCI Specification

- Implements delayed transactions for all PCI configuration, I/O, and memory read commands-up to three transactions simultaneously in each direction

- Allows 152 bytes of buffering (data and address) for upstream posted memory write commands and 88 bytes of buffering for downstream posted memory write commands- up to nine upstream and five downstream posted write transactions simultaneously

- Allows 152 bytes of read data buffering upstream and 72 bytes of read data buffering downstream

- Provides concurrent primary and secondary bus operation to isolate traffic

- · Provides enhanced address decoding

- Includes addressing and VGA palette snooping support

- Supports PCI transaction forwarding for the following commands

- All I/O and memory commands

- Type 1 to Type 1 configuration commands

- Type 1 to Type 0 configuration commands (downstream only)

- All Type 1 to special cycle configuration commands

- Includes downstream lock support

- Supports both 5 and 3.3 V signaling environments

The VMICPCI-7696 is a versatile single-board solution for CPCI control with familiar PC/AT operation.

### **VMICPCI-7696 Product Options**

VMIC's VMICPCI-7696 is built around three fundamental hardware configurations. These involve processor power, RAM memory, and the optional DiskOnChip flash memory size. *These options are subject to change based on emerging technologies and availability of vendor configurations.*

The options and current details available with the VMICPCI-7696 are defined in the device specification sheet available from your VMIC representative.

## Installation and Setup

#### **Contents**

| Unpacking Procedures | 30 |

|----------------------|----|

| Hardware Setup       | 31 |

| Installation         |    |

#### Introduction

This chapter describes the hardware jumper settings, connector descriptions, installation, system setup, and operation of the VMICPCI-7696.

### **Unpacking Procedures**

Any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage, and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to VMIC Customer Service together with a request for advice concerning the disposition of the damaged item(s).

Some of the components assembled on VMIC's products may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

#### **Hardware Setup**

The VMICPCI-7696 is factory populated with user-specified options as part of the VMICPCI-7696 ordering information. The CPU speed, RAM size, and flash memory size are not user-upgradable. To change CPU speeds, RAM/flash size, contact customer service to receive a Return Material Authorization (RMA).

VMIC Customer Service is available at: 1-800-240-7782.

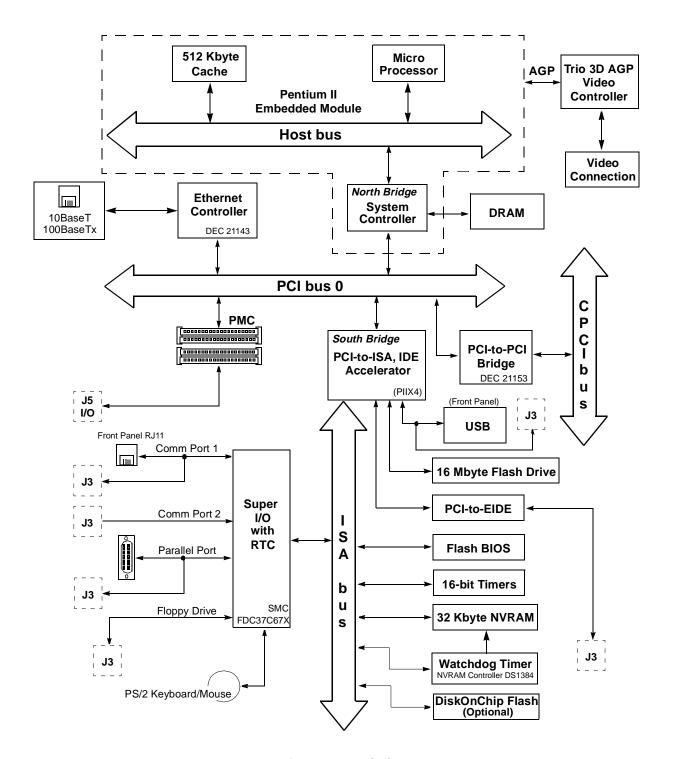

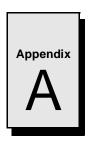

The VMICPCI-7696 is tested for system operation and shipped with factory-installed header jumpers. The physical location of the jumpers and connectors for the single board CPU are illustrated in Figure 2-1 on page 32. The definitions of the CPU board jumpers and connectors are included in Table 2-1 through .

All jumpers are factory configured and should not be modified by the user. There are three exceptions: the Programmable Timer Clock Select (E11), the Password Clear (E3), and the Watchdog Timer (E7). Modifying any other jumper will void the Warranty and may damage the unit. The default jumper condition of the VMICPCI-7696 is expressed in Table 2-1 through Table 2-3 with **bold text** in the table cells.

Figure 2-1 VMICPCI-7696 Embedded Module, and Jumper Locations

Table 2-1 CPU Board Connectors

| Connector  | Function                   |

|------------|----------------------------|

| J10        | Mouse/Keyboard Connector   |

| J9         | USB Connector              |

| J13        | COM1                       |

| J3         | COM1/COM2                  |

| J3, P2     | Parallel Port Connector    |

| J12        | Ethernet Connector         |

| J11        | Video Connector            |

| J3         | Floppy Interface Connector |

| E15        | ITP Test Header            |

| E16        | Port 80 Test Header        |

| J3         | EIDE Connector             |

| E2         | Fan Connector              |

| J6, J7, J4 | PMC Slot                   |

| J1, J2     | Compact PCI Connectors     |

Table 2-2 Password Clear (User Configurable) - Jumper (E3)

|                               | Jumper Position |

|-------------------------------|-----------------|

| Normal                        | Out             |

| Clear NVRAM/CMOS/<br>Password | In              |

The BIOS has the capability (not currently enabled) of password protecting casual access to the unit's CMOS set-up screens. The Password Clear jumper allows for a means to clear the password feature, this might be necessary to perform in the case of a forgotten password.

To clear the CMOS password:

- 1. Turn off power to the unit

- 2. Install a jumper at E3

- 3. Power up the unit

- 4. Turn off the power to the unit and remove the jumper from E3

When power is reapplied to the unit, the CMOS password will be cleared.

Table 2-3 Factory Configured - AGP Enable Jumper E4 (Not Populated)

| AGP Enable  | Jumper Position |

|-------------|-----------------|

| AGP Enable  | Out             |

| AGP Disable | In              |

Table 2-4 Factory Configured - Host Frequency Jumper E5 (Not Populated)

| Host Frequency | Jumper Position |

|----------------|-----------------|

| 66 Mhz         | Out             |

| 100 Mhz        | In              |

Table 2-5 Factory Configured - PIIX4E Battery Jumper (E6)

| PIIX4E Battery | Jumper Position |

|----------------|-----------------|

| Enabled        | In              |

| Disabled       | Out             |

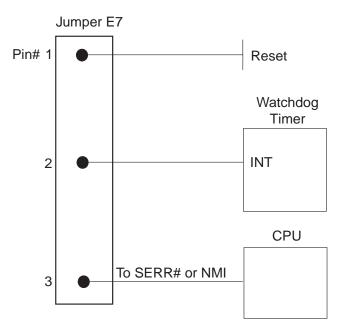

Table 2-6 Factory Configured - Watchdog Timer jumper (E7)

| Select                           | Jumper Position |

|----------------------------------|-----------------|

| Watchdog Timer Reset             | 1-2             |

| No Watchdog Timer Reset or SERR# | Out             |

| Watchdog Timer SERR#             | 2-3             |

Table 2-7 Factory Configured - Clock Speed Select Jumper (E8)

| CPU Bus Frequency<br>(MHz) | PCI Bus<br>Frequency (MHz) | E8 Position |

|----------------------------|----------------------------|-------------|

| 66.6                       | 33.3                       | 2-3         |

| 100                        | 25                         | 1-2         |

Table 2-8 Factory Configured - SRAM Battery Jumper (E10)

| SRAM Battery | Jumper Position |

|--------------|-----------------|

| Enabled      | In              |

| Disabled     | Out             |

Table 2-9 Programmable Timer Clock Select (User Configurable) Jumper (E11)

| Select | Jumper Position |

|--------|-----------------|

| 2 MHz  | 1-2             |

| 1 MHz  | 2-3             |

Table 2-10 Factory Configured - Reserved Jumper (E12)

| Reserved | 1 - 2 | Out |

|----------|-------|-----|

| Reserved | 2 - 3 | Out |

Table 2-11 Factory Configured - DiskOnChip Address SEL Jumper (E13)

| DiskOnChip | Jumpe | r Position |

|------------|-------|------------|

| D000       | 1 - 2 | In         |

| E000       | 2 - 3 | In         |

Table 2-12 Factory Configured - Boot Block Lock Jumper (E17)

| Select                 | Jumper Position |

|------------------------|-----------------|

| Boot Block Programming | 1 - 2           |

| No Program             | 2 - 3           |

Table 2-13 Factory Configured - Boot Block Lock (E18)

| Select   | Jumper Position |

|----------|-----------------|

| Reserved | 1-2             |

| Reserved | 2 -3            |

| Reserved | Omitted         |

35

#### Installation

The VMICPCI-7696 conforms to the CompactPCI physical specification for a 6U board. The VMICPCI-7696 is a system slot only board. It can be plugged directly into any standard chassis accepting this type of board. The following picture illustrates the symbol use to identify the slots in a standard CPCI chassis.

This symbol identifies peripheral slot

CAUTION: Do not install or remove the board while power is applied.

The following steps describe the VMIC recommended method for installation and powerup of the VMICPCI-7696:

- 1. Make sure power to the equipment is off.

- 2. If a PMC module such as VMIC's VMIPMC-7441 is to be used, connect it to the VMICPCI-7696 prior to board installation. Refer to the Product Manual for that particular board for configuration and setup.

- 3. The VMICPCI-7696 must be installed in the designated system slot of the CompactPCI backplane (See symbols above for selection of the correct slot).

**The VMICPCI-7696 requires forced air cooling.** It is advisable to install blank panels over any exposed slots. This will allow for better air flow over the VMICPCI-7696 board.

- 4. Insert the VMICPCI-7696 into the CompactPCI chassis system slot. While ensuring that the board is properly aligned and oriented in the supporting board guides, slide the board smoothly forward against the mating connector. Use the ejector handles to firmly seat the board.

- 5. All needed peripherals can be accessed from the front panel and the rear I/O VMIACC-0576 Rear Transition utility board. Each connector is clearly labeled on the front panel, and detailed pinouts are in Appendix A.

- 6. The VMICPCI-7696 features a Flash Disk resident on the board. Refer to Chapter 4 for set up details.

- 7. If an external drive module is installed, the BIOS Setup program must be run to configure the drive types. See Appendix C to properly configure the system.

- 8. If a drive module is present, install the operating system according to the

9. A keyboard and a mouse are required if the user has not previously configured the system

See Appendix B for instructions on installing VMICPCI-7696 peripheral driver software during operating system installation.

### **BIOS Setup**

The VMICPCI-7696 has an on-board BIOS Setup program that controls many configuration options. These options are saved in a special nonvolatile, battery-backed memory chip and are collectively referred to as the board's "CMOS configuration." The CMOS configuration controls many details concerning the behavior of the hardware from the moment power is applied.

The VMICPCI-7696 is shipped from the factory with hard drive type configuration set to AUTO in the CMOS.

Details of the VMICPCI-7696 BIOS setup program are included in Appendix D.

#### **Front Panel Connectors**

The front panel connections, including connector pinouts and orientation, for the VMICPCI-7696 are defined in detail in Appendix A. Rear panel connections are defined in detail in the Installation Guide for the VMIACC-0576.

## **PMC Site Connector**

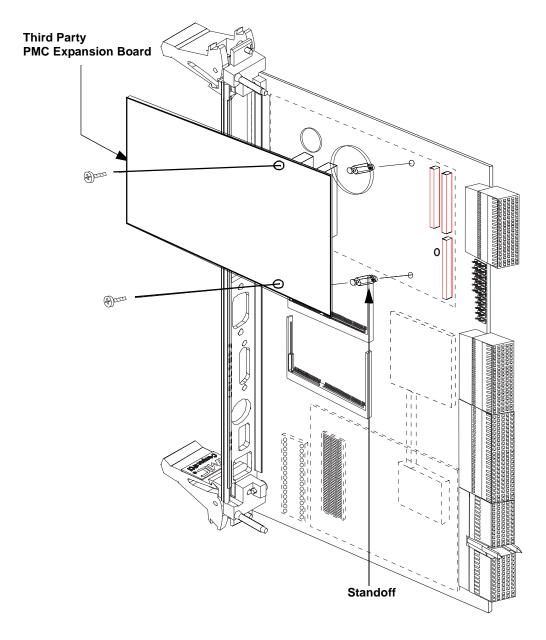

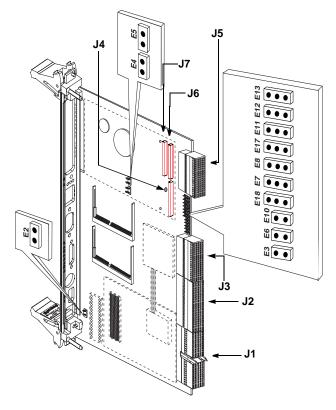

The VMICPCI-7696 supports IEEE-P1386 Common Mezzanine Card Specification with a 5 V PMC site. Figure 2-2 shows the installation of the PMC card on the VMICPCI-7696.

Figure 2-2 Installing a PMC Card on the VMICPCI-7696

## **LED Definition**

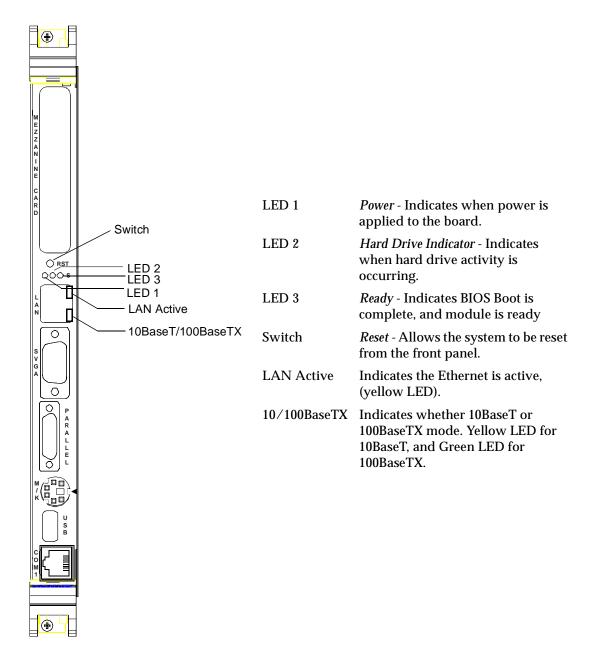

Figure 2-3 Front Panel LED Positions

# **PC/AT Functions**

## **Contents**

| CPU Socket               | 12 |

|--------------------------|----|

| Physical Memory          | 12 |

| I/O Port Map4            | 13 |

| Integrated Peripherals   | 51 |

| Ethernet Controller      | 52 |

| Video Graphics Adapter 5 | 53 |

## Introduction

The VMICPCI-7696 is a complete IBM PC/AT-compatible Pentium II® embedded module processor-based computer. The design includes a high-speed microprocessor with current technology memory, and optional Msystems DiskOnChip flash. Reference the VMIC product specifications for available component options.

Because the design is PC/AT compatible, it retains standard PC memory and I/O maps along with standard interrupt architecture. Furthermore, the VMICPCI-7696 includes a PCI-compatible Ethernet controller.

The following sections describe in detail the PC/AT functions of the VMICPCI-7696.

#### **CPU Socket**

The VMICPCI-7696 CPU socket is factory populated with a , high-speed Pentium II processor. The CPU speed and RAM/flash size are user-specified as part of the VMICPCI-7696 ordering information. The CPU speed is not user-upgradable.

To change CPU speeds, RAM size, or flash size contact customer service to receive a Return Material Authorization (RMA).

VMIC Customer Service is available at: 1-800-240-7782.

## **Physical Memory**

The VMICPCI-7696 provides Synchronous DRAM (SODIMM) as on-board system memory. Memory can be accessed as bytes, words, or longwords.

The VMICPCI-7696 accepts two 144-pin SODIMM DRAM modules for a maximum memory capacity of 256 Mbyte. The on-board DRAM is dual-ported to the CPCI bus through the PCI-to-PCI bridge. The memory is addressable by the local processor.

When using the Configure utility of VMIC's IOWorks Access with Windows NT 4.0 to configure RAM, do not request more than 25 percent of the physical RAM. Exceeding the 25 percent limit may result in a known Windows NT bug causing unpredictable behavior during the Windows NT boot sequence and require the use of an emergency repair disk to restore the computer. The bug is present in Windows NT 4.0 service pack level 3. It is recommended that an emergency repair disk be kept up-to-date and easily accessible.

The VMICPCI-7696 provides 16 Mbyte of flash memory (See Note) accessible through the Secondary IDE port. The VMICPCI-7696 BIOS includes an option to allow the board to boot from the flash memory or from the Ethernet port.

The VMICPCI-7696 is also available with an optional M-systems DiskOnChip flash up to 72 Mbytes. Reference the VMICPCI-7696 Product Specification for available flash memory options.

The VMICPCI-7696 memory includes 32 Kbyte of battery-backed SRAM addressed at \$D8000 to \$DFFFF. All but the first 14 bytes are accessable as SRAM. Bytes \$D8000 through \$D800D are reserved for the Watchdog Timer registers. The battery-backed SRAM can be accessed by the CPU at anytime, and is used to store system data that must not be lost during power-off conditions. Battery support for the 32 Kbyte of SRAM is B1 and uses Jumper E10.

Memory capacity may be extended as parts become available.

## I/O Port Map

The Pentium II processor-based CPU includes special input/output instructions that access I/O peripherals residing in I/O addressing space (separate and distinct from memory addressing space). Locations in I/O address space are referred to as *ports*. When the CPU decodes and executes an I/O instruction, it produces a 16-bit I/O address on lines A00 to A15 and identifies the I/O cycle with the M/I/O control line. Thus, the CPU includes an independent 64 Kbyte I/O address space which is accessible as bytes, words, or longwords.

Standard PC/AT hardware circuitry reserves only 1,024 byte of I/O addressing space from I/O \$000 to \$3FF for peripherals. All standard PC I/O peripherals such as serial and parallel ports, hard and floppy drive controllers, video system, real-time clock, system timers, and interrupt controllers are addressed in this region of I/O space. The BIOS initializes and configures all these registers properly; adjusting these I/O ports directly is not normally necessary.

The assigned and user-available I/O addresses are summarized in the I/O Address Map, Table 3-1.

I/O ADDRESS SIZE IN **HW DEVICE PC/AT FUNCTION RANGE BYTES** \$000 - \$00F 16 DMA Controller 1 (Intel 8237A Compatible) \$010 - \$01F 16 Reserved S020 - S021 2 Master Interrupt Controller (Intel 8259A Compatible) S022 - S03F 30 Reserved \$040 - \$043 4 **Programmable Timer** (Intel 8254 Compatible) S044 - S05F 30 Reserved \$060 - \$064 5 Keyboard, Speaker, Eqpt. Configuration (Intel 8042 Compatible) \$065 - \$06F 11 Reserved 2 S070 - S071 Real-Time Clock. \$072 - \$07F 14 Reserved S080 - S08F 16 **DMA Page Registers** S090 - S091 2 Reserved \$092 1 Alt. Gate A20/Fast Reset Register **S093** 1 Reserved

Table 3-1 VMICPCI-7696 I/O Address Map

Table 3-1 VMICPCI-7696 I/O Address Map (Continued)

| /O ADDRESS<br>RANGE | SIZE IN<br>BYTES | HW DEVICE      | PC/AT FUNCTION                                         |

|---------------------|------------------|----------------|--------------------------------------------------------|

| \$094               | 1                |                |                                                        |

| \$095 - \$09F       | 11               |                | Reserved                                               |

| \$0A0 - \$0A1       | 2                |                | Slave Interrupt Controller<br>(Intel 8259A Compatible) |

| \$0A2 - \$0BF       | 30               |                | Reserved                                               |

| \$0C0 - \$0DF       | 32               |                | DMA Controller 2<br>(Intel 8237A Compatible)           |

| \$0E0 - \$16F       | 142              |                | Reserved                                               |

| \$170 - \$177       | 8                | PIIX4          | Secondary Hard Disk Controller                         |

| \$178 - \$1EF       | 120              |                | User I/O                                               |

| \$1F0 - \$1F7       | 8                | PIIX4          | Primary Hard Disk Controller                           |

| \$1F8 - \$277       | 128              |                | User I/O                                               |

| \$278 - \$27F       | 8                | I/O Chip*      | LPT2 Parallel I/O*                                     |

| \$280 - \$2E7       | 104              |                | Reserved                                               |

| \$2E8 - \$2EE       | 7                | UART*          | COM4 Serial I/O*                                       |

| \$2EF - \$2F7       | 9                |                | User I/O                                               |

| \$2F8 - \$2FE       | 7                | Super-I/O Chip | COM2 Serial I/O<br>(16550 Compatible)                  |

| \$2FF - \$36F       | 113              |                | Reserved                                               |

| \$370 - \$377       | 8                | Super-I/O Chip | Secondary Floppy Disk Controller                       |

| \$378 - \$37F       | 8                | Super-I/O Chip | LPT1 Parallel I/O                                      |

| \$380 - \$3E7       | 108              |                | Reserved                                               |

| \$3E8 - \$3EE       | 7                | UART*          | COM3 Serial I/O*                                       |

| \$3F0 - \$3F7       | 8                | Super-I/O Chip | Primary Floppy Disk Controller                         |

| \$3F8 - \$3FE       | 7                | Super-I/O Chip | COM1 Serial I/O<br>(16550 Compatible)                  |

| \$3FF - \$4FF       |                  |                | Reserved                                               |

| \$500 - \$503       | 4                | 82C54 Timer    | Programmable Internal Timer                            |

| \$504 - CFF         |                  |                | Reserved                                               |

$<sup>^{\</sup>ast}$  While these I/O ports are reserved for the listed functions, they are not implemented on the VMICPCI-7696. They are listed here to make the user aware of the standard PC/AT usage of these ports.

## PCI-to-PCI Bridge

The VMICPCI-7696 uses the Intel 21153 PCI-to-PCI bridge to interface between the primary PCI bus of unit and the CompactPCI (CPCI) bus. The CompactPCI bus appears as a secondary PCI bus, and all devices in the seven peripheral slots of the CPCI chassis are auto detected by the BIOS and respond to normal PCI accesses.

## **PC/AT Interrupts**

In addition to an I/O port address, an I/O device has a separate hardware interrupt line assignment. Assigned to each interrupt line is a corresponding interrupt vector in the 256-vector interrupt table at \$00000 to \$003FF in memory. The 16 maskable interrupts and the single Non-Maskable Interrupt (NMI) are listed in Table 3-2 along with their functions. Table 3-3 on page 46 details the vectors in the interrupt vector table. The interrupt number in HEX and decimal are also defined for real and protected mode in Table 3-3 on page 46.

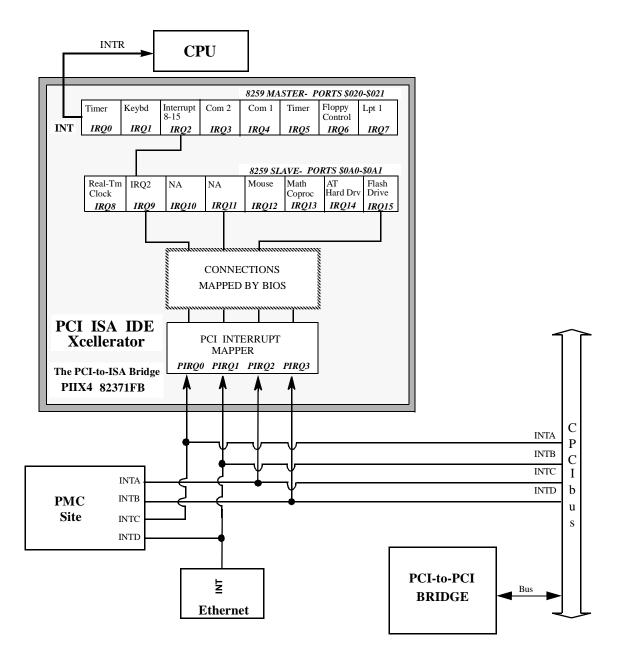

The interrupt hardware implementation on the VMICPCI-7696 is standard for computers built around the PC/AT architecture, which evolved from the IBM PC/XT. In the IBM PC/XT computers, only eight interrupt request lines exist, numbered from IRQ0 to IRQ7 at the PIC. The IBM PC/AT computer added eight more IRQx lines, numbered IRQ8 to IRQ15, by cascading a second slave PIC into the original master PIC. IRQ2 at the master PIC was committed as the cascade input from the slave PIC. This architecture is represented in Figure 3-1 on page 50.

To maintain backward compatibility with PC/XT systems, IBM chose to use the new IRQ9 input on the slave PIC to operate as the old IRQ2 interrupt line on the PC/XT Expansion Bus. Thus, in AT systems, the IRQ9 interrupt line connects to the old IRQ2 pin (pin B4) on the AT Expansion Bus (or ISA bus).

| IRQ | AT FUNCTION                                      | COMMENTS                                 |

|-----|--------------------------------------------------|------------------------------------------|

| NMI | Parity Errors<br>(Must be enabled in BIOS Setup) | Used by VMICPCI-7696<br>PCIbus Interface |

| 0   | System Timer                                     | Set by BIOS Setup                        |

| 1   | Keyboard                                         | Set by BIOS Setup                        |

| 2   | Duplexed to IRQ9                                 |                                          |

| 3   | COM2/COM4                                        |                                          |

| 4   | COM1/COM3                                        |                                          |

| 5   | Timer                                            | Assigned to On-Board Timer               |

| 6   | Floppy Controller                                |                                          |

| 7   | LPT1                                             |                                          |

| 8   | Real-Time Clock                                  |                                          |

Table 3-2 PC/AT Hardware Interrupt Line Assignments

Table 3-2 PC/AT Hardware Interrupt Line Assignments (Continued)

| IRQ | AT FUNCTION      | COMMENTS            |  |

|-----|------------------|---------------------|--|

| 9   | Old IRQ2         | SVGA or Network I/O |  |

| 10  | Not Assigned     | Determined by BIOS  |  |

| 11  | Not Assigned     | Determined by BIOS  |  |

| 12  | Mouse            |                     |  |

| 13  | Math Coprocessor |                     |  |

| 14  | AT Hard Drive    |                     |  |

| 15  | Flash Drive      |                     |  |

Table 3-3 PC/AT Interrupt Vector Table

| INTERR | UPT NO. | IRQ  | REAL MODE                                     | DDOTECTED MODE                                       |  |

|--------|---------|------|-----------------------------------------------|------------------------------------------------------|--|

| HEX    | DEC     | LINE | REAL MODE                                     | PROTECTED MODE                                       |  |

| 00     | 0       |      | Divide Error                                  | Same as Real Mode                                    |  |

| 01     | 1       |      | Debug Single Step                             | Same as Real Mode                                    |  |

| 02     | 2       | NMI  | Memory Parity Error,<br>CompactPCI Interrupts | Same as Real Mode<br>(Must be enabled in BIOS Setup) |  |

| 03     | 3       |      | Debug Breakpoint                              | Same as Real Mode                                    |  |

| 04     | 4       |      | ALU Overflow                                  | Same as Real Mode                                    |  |

| 05     | 5       |      | Print Screen                                  | Array Bounds Check                                   |  |

| 06     | 6       |      |                                               | Invalid OpCode                                       |  |

| 07     | 7       |      |                                               | Device Not Available                                 |  |

| 08     | 8       | IRQ0 | Timer Tick                                    | Double Exception Detected                            |  |

| 09     | 9       | IRQ1 | Keyboard Input                                | Coprocessor Segment Overrun                          |  |

| 0A     | 10      | IRQ2 | BIOS Reserved                                 | Invalid Task State Segment                           |  |

| ОВ     | 11      | IRQ3 | COM2 Serial I/O                               | Segment Not Present                                  |  |

| 0C     | 12      | IRQ4 | COM1 Serial I/O                               | Stack Segment Overrun                                |  |

| 0D     | 13      | IRQ5 | Timer                                         | Same as Real Mode                                    |  |

| 0E     | 14      | IRQ6 | Floppy Disk Controller Page Fault             |                                                      |  |

| 0F     | 15      | IRQ7 | LPT1 Parallel I/O                             | Unassigned                                           |  |

| 10     | 16      |      | BIOS Video I/O                                | Coprocessor Error                                    |  |

Table 3-3 PC/AT Interrupt Vector Table (Continued)

| INTERRUPT NO. |     | IRQ  | DEAL MODE                                                  | DDOTFOTED MODE    |  |

|---------------|-----|------|------------------------------------------------------------|-------------------|--|

| HEX           | DEC | LINE | REAL MODE                                                  | PROTECTED MODE    |  |

| 11            | 17  |      | Eqpt Configuration Check                                   | Same as Real Mode |  |

| 12            | 18  |      | Memory Size Check                                          | Same as Real Mode |  |

| 13            | 19  |      | XT Floppy/Hard Drive                                       | Same as Real Mode |  |

| 14            | 20  |      | BIOS Comm I/O                                              | Same as Real Mode |  |

| 15            | 21  |      | BIOS Cassette Tape I/O                                     | Same as Real Mode |  |

| 16            | 22  |      | BIOS Keyboard I/O                                          | Same as Real Mode |  |

| 17            | 23  |      | BIOS Printer I/O                                           | Same as Real Mode |  |

| 18            | 24  |      | ROM BASIC Entry Point                                      | Same as Real Mode |  |

| 19            | 25  |      | Bootstrap Loader                                           | Same as Real Mode |  |

| 1A            | 26  | IRQ8 | Real-Time Clock                                            | Same as Real Mode |  |

| 1B            | 27  |      | Control/Break Handler                                      | Same as Real Mode |  |

| 1C            | 28  |      | Timer Control                                              | Same as Real Mode |  |

| 1D            | 29  |      | Video Parameter Table Pntr                                 | Same as Real Mode |  |

| 1E            | 30  |      | Floppy Parm Table Pntr                                     | Same as Real Mode |  |

| 1F            | 31  |      | Video Graphics Table Pntr                                  | Same as Real Mode |  |

| 20            | 32  |      | DOS Terminate Program                                      | Same as Real Mode |  |

| 21            | 33  |      | DOS Function Entry Point                                   | Same as Real Mode |  |

| 22            | 34  |      | DOS Terminate Handler                                      | Same as Real Mode |  |

| 23            | 35  |      | DOS Control/Break Handler                                  | Same as Real Mode |  |

| 24            | 36  |      | DOS Critical Error Handler                                 | Same as Real Mode |  |

| 25            | 37  |      | DOS Absolute Disk Read                                     | Same as Real Mode |  |

| 26            | 38  |      | DOS Absolute Disk Write                                    | Same as Real Mode |  |

| 27            | 39  |      | DOS Program Terminate,<br>Stay Resident  Same as Real Mode |                   |  |

| 28            | 40  |      | DOS Keyboard Idle Loop                                     | Same as Real Mode |  |

| 29            | 41  |      | DOS CON Dev. Raw Output                                    | Same as Real Mode |  |

| 2A            | 42  |      | DOS 3.x+ Network Comm                                      | Same as Real Mode |  |

Table 3-3 PC/AT Interrupt Vector Table (Continued)

| INTERR | ERRUPT NO. IRQ REAL MODE |       | DDOTECTED MODE           |                   |

|--------|--------------------------|-------|--------------------------|-------------------|

| HEX    | DEC                      | LINE  | REAL MODE                | PROTECTED MODE    |

| 2B     | 43                       |       | DOS Internal Use         | Same as Real Mode |

| 2C     | 44                       |       | DOS Internal Use         | Same as Real Mode |

| 2D     | 45                       |       | DOS Internal Use         | Same as Real Mode |

| 2E     | 46                       |       | DOS Internal Use         | Same as Real Mode |

| 2F     | 47                       |       | DOS Print Spooler Driver | Same as Real Mode |

| 30-60  | 48-96                    |       | Reserved by DOS          | Same as Real Mode |

| 61-66  | 97-102                   |       | User Available           | Same as Real Mode |

| 67-71  | 103-113                  |       | Reserved by DOS          | Same as Real Mode |

| 72     | 114                      | IRQ10 | Not Assigned             |                   |

| 73     | 115                      | IRQ11 | Not Assigned             |                   |

| 74     | 116                      | IRQ12 | Mouse                    |                   |

| 75     | 117                      | IRQ13 | Math Coprocessor         |                   |

| 76     | 118                      | IRQ14 | AT Hard Drive            |                   |

| 77     | 119                      | IRQ15 | Flash Drive              |                   |

| 78-7F  | 120-127                  |       | Reserved by DOS          | Same as Real Mode |

| 80-F0  | 128-240                  |       | Reserved for BASIC       | Same as Real Mode |

| F1-FF  | 241-255                  |       | Reserved by DOS          | Same as Real Mode |

## **PCI** Interrupts

Interrupts on Peripheral Component Interconnect (PCI) Local Bus are optional and defined as "level sensitive," asserted low (negative true), using open drain output drivers. The assertion and de-assertion of an interrupt line, INTx#, is asynchronous to CLK. A device asserts its INTx# line when requesting attention from its device driver. Once the INTx# signal is asserted, it remains asserted until the device driver clears the pending request. When the request is cleared, the device de-asserts its INTx# signal.

PCI defines one interrupt line for a single function device and up to four interrupt lines for a multifunction device or connector. For a single function device, only INTA# may be used while the other three interrupt lines have no meaning. Figure 3-1 on page 50 depicts the VMICPCI-7696 interrupt logic pertaining to CompactPCI operations and the PMC site.

Any function on a multifunction device can be connected to any of the INTx# lines. The Interrupt Pin register defines which INTx# line the function uses to request an interrupt. If a device implements a single INTx# line, it is called INTA#; if it implements two lines, they are called INTA# and INTB#; and so forth. For a multifunction device, all functions may use the same INTx# line or each may have its own (up to a maximum of four functions) or any combination thereof. A single function can never generate an interrupt request on more than one INTx# line.

The slave PIC accepts the CompactPCI interrupts through lines that are defined by the BIOS. The BIOS defines which interrupt line to utilize depending on which system requires the use of the line.

The PCI-to-PCI Bridge has the capability of generating a Non-Maskable Interrupt (NMI) via the PCI SERR# line. Table 3-4 describes the register bits that are used by the NMI. The SERR interrupt is routed through logic back to the NMI input line on the CPU. The CPU reads the NMI Status Control register to determine the NMI source (bits set to 1). After the NMI interrupt routine processes the interrupt, software clears the NMI status bits by setting the corresponding enable/disable bit to 1. The NMI Enable and Real-Time Clock register can mask the NMI signal and disable/enable all NMI sources.

Table 3-4 NMI Register Bit Descriptions

|       | Status Control Register<br>(I/O Address \$061, Read/Write, Read Only)                                                                                                                                                                                          |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit 7 | SERR# NMI Source Status (Read Only) - This bit is set to 1 if a system board agent detects a system board error. It then asserts the PCI SERR# line. To reset the interrupt, set bit 2 to 0 and then set it to 1. When writing to port \$061, bit 7 must be 0. |  |  |  |  |  |  |

| Bit 2 | Bit 2 PCI SERR# Enable (Read/Write) - 1 = Clear and Disable, 0 = Enable                                                                                                                                                                                        |  |  |  |  |  |  |

|       | Enable and Real-Time Clock Address Register (I/O Address \$070, Write Only)                                                                                                                                                                                    |  |  |  |  |  |  |

| Bit 7 | NMI Enable - 1 = Disable, 0 = Enable                                                                                                                                                                                                                           |  |  |  |  |  |  |

Figure 3-1 Connections for the PC Interrupt Logic Controller

## **Integrated Peripherals**

The VMICPCI-7696 incorporates the SMC Super-I/O chip. The SMC chip provides the VMICPCI-7696 with a standard floppy drive controller, USB port, two 16550 UART-compatible serial ports, and one enhance parallel port with ECP/EPP modes. The Ultra-EIDE hard drive interface is provided by the Intel 82371EB (PIIX4E) PCI ISA IDE Xcelerator chip. All ports are located on the J3 connector, for use with VMIC's VMIACC-0576 CompactPCI Rear Transition Utility Board.

#### **Ethernet Controller**

The network capability is provided by the DEC's 21143 Ethernet Controller. This Ethernet controller is PCI bus based and is software configurable. The VMICPCI-7696 supports 10BaseT and 100BaseTx Ethernet.

#### 10BaseT

A network based on the 10BaseT standard uses unshielded twisted-pair cables, providing an economical solution to networking by allowing the use of existing telephone wiring and connectors. The RJ-45 connector is used with the 10BaseT standard. 10BaseT has a maximum length of 100 meters from the wiring hub to the terminal node.

#### 100BaseTx

The VMICPCI-7696 also supports the 100BaseTx Ethernet. A network based on a 100BaseTx standard uses unshielded twisted-pair cables and a RJ-45 connector. The 100BaseTx has a maximum deployment length of 100 meters.

#### **Remote Ethernet Booting**

The VMICPCI-7696 is capable of booting from a server over the Ethernet. Utilizing Lanworks BootWare <sup>®</sup>. BootWare gives you the ability to remotely boot the VMICPCI-7696 using Netware, TCP/IP, or RPL network protocols. The Ethernet must be connected through the LAN front panel (RJ-45) connector to boot remotely. This feature allows users to create systems without the worry of disk drive reliability, or the extra cost of adding Flash drives.

#### **BootWare Features:**

- Netware, TCP/IP, RPL Compatible

- Unparalleled boot sector virus protection

- · Detailed boot configuration screens

- · Comprehensive diagnostics

- · Optional disabling of local boots

- Dual-boot option lets users select network or local booting

# Video Graphics Adapter

The SVGA port on the VMICPCI-7696 is controlled by a S3 Trio 3D AGP chip with 4 Mbyte video DRAM. The video controller chip is hardware and BIOS compatable with the IBM EGA and SVGA standards supporting both VESA high-resolution and extended video modes. Table 3-5 shows the graphics video modes supported by the Trio 3D video chip.

Screen Maximum **Maximum Refresh** Resolution Colors Rates (Hz) 640 x 480 16 M 85 800 x 600 16 M 85 1,024 x 768 16 M 85 1,280 x 1,024 64 K 60 1600 x 1200 64 K 60

Table 3-5

Supported Graphics Video Resolutions

Not all SVGA monitors support resolutions and refresh rates beyond  $640 \times 480$  at 60 Hz. Do not attempt to drive a monitor to a resolution or refresh rate beyond its capability.

The VMICPCI-7696's processor includes a 64-bit access to video memory with no-wait states. Video I/O registers are accessed using the AGP bus.

The floppy disks supplied with the VMICPCI-7696 contain drivers for Windows, Windows 95, and Windows NT (4.0) operating systems. Appendix B contains instruction on the incorporation of the drivers during system installation.

CHAPTER 4

# Embedded PC/RTOS Features

## **Contents**

| Timers                | 56 |

|-----------------------|----|

| Flash Disk            | 65 |

| Flash Disk (Optional) | 69 |

| Watchdog Timer        | 7  |

| Battery Backed SRAM   | 77 |

## Introduction

VMIC's VMICPCI-7696 features additional capabilities beyond those of a typical IBM PC/AT-compatible CPU. The unit provides three software-controlled, general-purpose timers along with a programmable Watchdog timer for synchronizing and controlling multiple events in embedded applications. The VMICPCI-7696 also provides a bootable Flash Disk system, and 32 kbyte of nonvolatile, battery-backed SRAM. These features make the unit ideal for embedded applications, particularly applications where standard hard drives and floppy disk drives cannot be used.

#### **Timers**

#### General

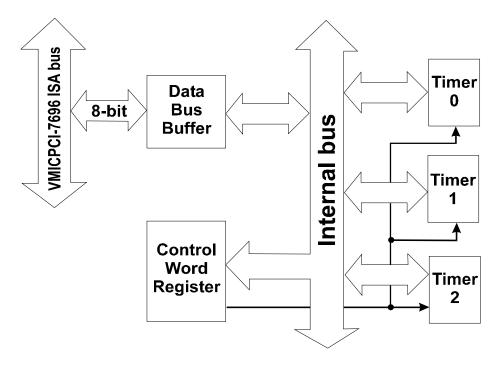

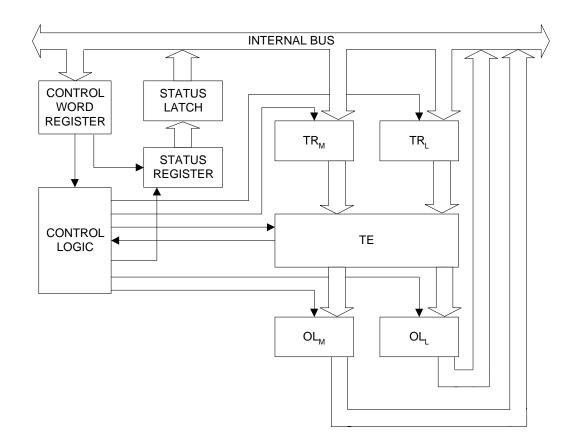

The VMICPCI-7696 provides a user-programmable 82C54 internal timer/counter. The 82C54 provides three independent, 16-bit timers each operating at a 1 or 2 MHz clock speed. This is determined by the configuration of jumper E11; reference Table 2-9 on page 35 of Chapter 2. These timers are completely available to the user, and are not dedicated to any PC/AT function. These timers may be used to generate system interrupts.

Events can be timed by either polling the timers or generating a system interrupt via circuity external to the 82C54. The external circuity consists of logic which generates the interrupt and a Timer Interrupt Status register which indicates which of the three Timers generated an interrupt.

The 82C54 timers are mapped at I/O address \$500. The interrupt used by the Timers is IRQ5. The Timer Interrupt Status register is available via the Power Management I/O address space. The access to this space is explained in the Timer Interrupt Status section.

#### **Timer Interrupt Status**

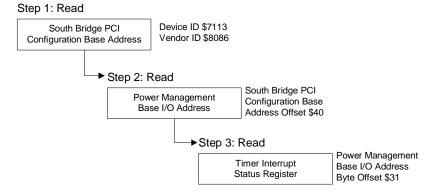

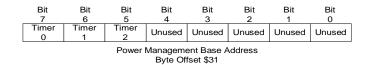

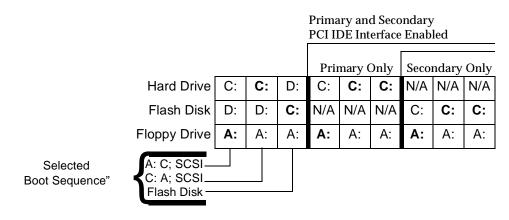

A single interrupt, IRQ5, is used by all three Timers. A Timer Interrupt Status register is provided in order to determine which Timer(s) initiated an interrupt. The Interrupt Status Register is a general-purpose input register located (refer to Figure 4-1), external to the 82C54, at offset \$31 from the Power Management Base I/O address. The interrupt status register address can be found by first determining the PCI Configuration Base address for Device ID \$7113 and Vendor ID \$8086. The Power Management Base I/O address can be found by reading offset \$40 from this PCI Configuration address. The Timer Interrupt Status register bits are located at offset \$31 from the Power Management Base I/O address, bits 5, 6, and 7.

Figure 4-1 Timer Interrupt Status Register Read/Steps

A byte read of offset \$31 from the Power Management Base I/O address is used to obtain these bits. Bits 5, 6, and 7 correspond to Timers 2, 1, and 0, respectively

Figure 4-2 Timer Interrupt Status Register