# KENNEDY FORMATTER MODEL 9219

Customer Engineering Reprint Product Maintenance Manual

# **PREFACE**

# Second Edition (October 1983)

This is the first update of the KENNEDY model 9219 Formatter maintenance manual and obsoletes 729-0250 and 729-0258. Updates and/or changes to this document will be published as Product Service Notices (PSN's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

<sup>©</sup> Copyright WANG Labs., Inc. 1981, 1983

# FCC NONCERTIFIED EQUIPMENT

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# SECTION INTRO-DUCTION

# MODEL 9219 SPECIFICATIONS

# 1.1 INTRODUCTION

The industry compatible Model 9219 is designed to format seven and nine track NRZI and/or phase encoded tapes. It can be used in conjunction with 10 through 125 ips tape transports and contains the electronies required to read or write ANSI and IBM compatible formats. When only the NRZI format is desired, the unused phase electronies may be omitted. Electrical and mechanical specifications are provided in paragraph 1.2.

The address and control logic circuits accept input commands from the computer and convert these commands into signals which initiate the desired operations of the selected tape transport.

All timing, as well as data transmission to and from the tape deck and formatter, is controlled by means of a 12 bit bipolar Shottky microprocessor. The time required to execute one complete instruction is 347 nsec. Several options have been made available through switchable IC's on the 4831 interface board. The formatter can also be selected for the speeds and densities of any one of up to four tape units. (Refer to paragraph 2.5.)

The 1 to 1 wiring configuration of the masterboard's foil pattern permits the user to interchange the circuit boards. This eliminates the possibility of inserting a circuit board into the wrong slot and possibly overloading IC's. It also makes the boards easily accessible for troubleshooting.

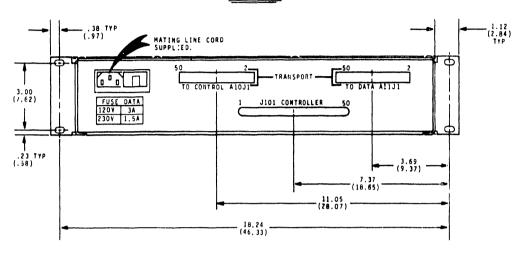

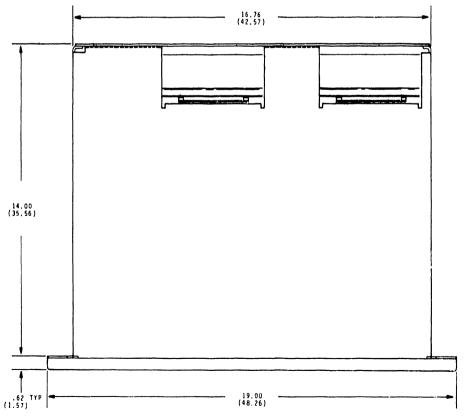

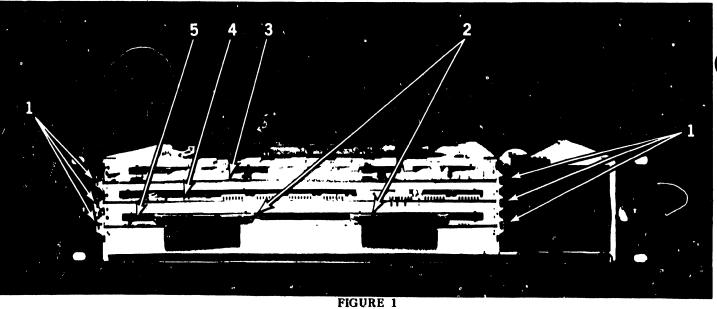

The unit is mounted on a 3.5 inch panel for installation in a standard 19 inch EIA equipment rack. Figure 1-1 is an Outline and Installation Drawing.

There are no controls or indicators on the Model 9219 Formatter. A switch for selection of 115 vac or 230 vac primary power input is located at the rear of the formatter.

# 1.2 ELECTRICAL AND MECHANICAL SPECIFICATIONS

| Dimensions                                          |

|-----------------------------------------------------|

| Formatter mounting                                  |

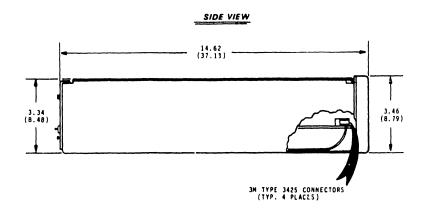

| Height 3.34 inches (8.48 cm)                        |

| Width 16.76 inches (42.57 cm)                       |

| Depth (from mounting surface)                       |

| Depth (overall) 14.62 inches (37.13 cm)             |

| Front panel width 19.0 inches (48.26 cm)            |

| Weight 20.6 pounds (9.33 kg)                        |

| Shipping weight                                     |

| Operating environment                               |

| Ambient temperature $+2^{\circ}$ to $+50^{\circ}$ C |

| Relative humidity (noncondensing) 15% to 95%        |

| Altitude                                            |

| Power requirements                                  |

| 50 to 60 Hz, single phase                           |

| Single density 50 VA                                |

| NRZ1 and phase encoded                              |

| Drivers open collector type                         |

| Receivers standard 220/330 ohm                      |

# REAR VIEW

410-4030

BOTTOM VIEW

FIRST DIMENSIONS ARE SHOWN IN INCHES. DIMENSIONS IN PARENTHESES ARE IN CENTIMETERS.

FRONT VIEW

410-4030

Figure 1-1.

Outline and Installation Drawing

Model 9219

# SECTION 2 INTER-FACE CHARAC-TERIS-TICS

# MODEL 9219 INTERFACE CHARACTERISTICS

# 2.1 INTERFACE SIGNAL CHARACTERISTICS

Signals from the controller to the Model 9219 must conform to the following specifications:

Levels: Low=true=0 volt

High=false=+3 volts (approx)

Pulses: Low=true=0 volt

High=false=+3 volts (approx)

Minimum pulsewidth: 1 microsecond

Edge transmission delay: No greater than 200 nsec over 20 foot cable

Output signals from the Model 9219 are driven by open collector type line drivers capable of sinking up to 36 ma (25 standard unit loads) in the low true state. The interface circuits are designed so that a disconnected wire results in a false signal.

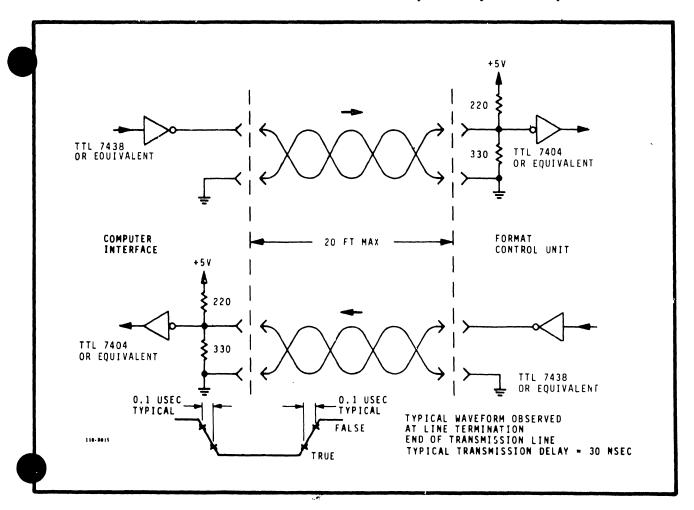

Figure 2-1 shows the configuration of the line drivers and receivers. A twisted pair is required for each input and output. Maximum recommended length of the interconnecting cables is 20 feet. The connector pin assignments are provided in paragraph 2.4.

# 2.2 INTERFACE INPUT SIGNALS

(Controller to Formatter)

The following paragraphs describe the specifications and functions for each input signal required from the computer interface to the formatter. Under the signal name are listed its mnemonic designation and the connector and active pin designations for the input signal line. Connector designations refer to the interface cable connector that mates with the corresponding card edge connector on the formatter. An I/O signal list is provided in Table 2-1.

# FORMATTER ADDRESS

FAD

Level

P101-B1

A level which selects one of two formatters. FAD false selects formatter address 0; FAD true selects formatter address 1. The formatter addresses are determined by an address switch on the formatter PCBA. Normally, the formatter must be selected in order to perform any formatter operations.

Figure 2-1. Typical Interface Configuration

| Signal                                      | MNEMONIC   | LEVEL<br>OR<br>PULSE |

|---------------------------------------------|------------|----------------------|

| INTERFACE INPUTS                            |            |                      |

| (CONTROLLER TO FORMATTER)                   |            |                      |

| FORMATTER ADDRESS                           | FAD        | L                    |

| TRANSPORT ADDRESS                           | TADO, TADI | L                    |

| INITIATE COMMAND                            | GO         | P                    |

| REVERSE/FORWAR®                             | REV        | L.                   |

| WRITE/READ                                  | WRT        | L                    |

| WRITE FILE MARK                             | WFM        | L                    |

| EDIT                                        | EDIT       | L                    |

| ERASE                                       | ERASE      | L                    |

| REWIND                                      | REW        | P                    |

| DENSITY SELECT                              | DEN        | L                    |

| PARITY SELECT                               | PAR        | I.                   |

| OFFLINE COMMAND                             | OFI.       | P                    |

| LAST WORD                                   | LWD        | l.                   |

| FORMATTER ENABLE                            | FEN        | L.                   |

| WRITE DATA LINES                            | WP,W0-W7   | l.                   |

| INTERFACE OUTPUTS (FORMATTER TO CONTROLLER) |            |                      |

| FORMATTER BUSY                              | FBY        | L                    |

| DATA BUSY                                   | DBY        | L                    |

| HARD ERROR                                  | HER        | P                    |

| CHECK CHARACTER GATE                        | CCG        | L                    |

| IDENTIFICATION                              | IDENT      | L                    |

| CORRECTED ERROR                             | CER        | P                    |

| FILE MARK                                   | FMK        | P                    |

| WRITE STROBE                                | WRST       | P                    |

| READ STROBE                                 | RSTR       | P                    |

| READ DATA LINES                             | RP, R0-R7  | L                    |

| READY                                       | RDY        | L                    |

| REWINDING                                   | RWD        | L                    |

| LOAD POINT                                  | LDP        | L                    |

| 7 TRACK/9 TRACK                             | 7TK/9TK    | L                    |

| ONLINE                                      | ONL        | L                    |

| FILE PROTECT                                | FPT        | L                    |

| END OF TAPE                                 | EOT        | 1.                   |

| NRZI/PE                                     | NRZI/PE    | L                    |

Table 2-1. Input/Output Signal List

# TRANSPORT ADDRESS

TADO TAD1 Levels P101-A1; P101-B3

The states of these lines determine which of up to four transports are selected by the formatter. The following lists defines the tape transport addresses produced as a result of the various TAD0, TAD1.

| TAD0 | TAD1 | ADDRESS |

|------|------|---------|

| 0    | 0    | SLT0    |

| 0    | 1    | SLT1    |

| 1    | 0    | SLT2    |

| 1    | 1    | SLT3    |

# INITIATE COMMAND

| GO | Pulse | P101-A3 |

|----|-------|---------|

A pulse which initiates any command specified by the command lines described in the following paragraphs. Information on the command lines is copied in the corresponding formatter flip-flops on the trailing edge of the GO pulse. FBY is set true when the GO pulse is given with the formatter and the selected transport ready.

## COMMAND LINES

The levels on these lines issue a command to the formatter on the trailing edge of the GO pulse. The REV, WRT, WFM, EDIT, ERASE, PAR and DEN levels must be held steady from 0.5 microsecond prior to the trailing edge to 0.5 miscrosecond following the trailing edge of the GO pulse.

### REVERSE

REV

Level

P101-B4

A level which initiates reverse tape motion when true. When false, this level specifies forward tape motion.

### WRITE

WRT

Level

P101-A4

Write mode is specified when this level is true; read mode is specified when this level is false.

# WRITE FILE MARK

WFM

Level

P101-A25

When this level and WRT are true, the formatter will write a file mark on the tape.

### EDIT

EDIT

Level

P101-A6

EDIT true and REV true modify the read reverse stop delay to optimize head positioning for a subsequent edit operation. When the EDIT level is true and WRT is true, the OVW (overwrite) line is activated and the selected transport operates in the edit mode.

# ERASE

**ERASE**

Level

P101-B7

ERASE true and WRT true cause the formatter to execute a dummy write command. The formatter will issue a normal write command but no data will be recorded. A length of tape, as defined by LWD, will be erased. A dummy write file mark command will be issued when ERASE, WRT/READ and the WFM command lines are true. During this operation, approximately 3.75 inches (9.52 cm) of tape will be erased.

# **DENSITY SELECT**

DEN Level

(Optional, 7 Track NRZI only)

When true, this optional level selects the lower of two possible data transfer packing densities. When this level is false, the higher packing density is selected.

# PARITY SELECT

PAR

Level

P101-B10

P101-A9

(NRZI only)

The levels on this line control the parity mode for write or read data transfer. When true the even (BCD) parity mode is selected; when this level is false, the odd (binary) parity mode is selected.

# REWIND

REW

Pulse

P101-B12

A pulse which causes the selected on line transport to rewind to load point. This pulse is directly routed to the transport and does not cause the formatter to go busy.

# OFFLINE COMMAND

OFL

Pulse

P101-A12

This pulse causes the selected transport to go offline without causing the formatter to go busy.

### LAST WORD

LWD

Level

P101-B13

When this level is true during a write or erase command, it indicates that the next character to be strobed into the formatter is the last character of the record. LWD goes true when the last data character is placed on the interface lines.

# FORMATTER ENABLE

FEN

Level

P101-A13

When false, this level causes all formatters in the system to revert to the quiescent state. This line may be used to disable the formatters if controller power is lost or to clear formatter logic when illegal commands or unusual conditions occur.

# WRITE DATA PARITY & WRITE DATA LINES

WP, W0-W7

Levels

(Refer to Pin List)

These lines are present in both NRZI and PE formatters and will be defined for each application.

# (1) NRZI Formatter

These 9 lines transmit write data from the controller to the formatter. Lines WP, W0-W7 are utilized for 9-channel operation; lines WP, W2-W7 are used for 7-channel operation.

For 9-channel operation the 8 data bits appearing on W0-W7 are written onto the corresponding channels on tape; for 7-channel operation W0 and W1 are not utilized and the remaining 6 data bits are written onto tape. In either case, W7 corresponds to the least significant bit of the character.

Line WP is optional and is utilized only if it is required to write the parity bit specified by the customer. When this option is not employed the formatter generates parity internally on the basis of data contained on W0-W7, together with the current parity mode.

The first character of a record should be available on these lines within one character period after DBY goes true and remain until the trailing edge of the first WSTR is issued by the formatter.

The next character of information must then be placed on these lines within onehalf of a character period.

Subsequent characters of a record are processed in this manner until LWD is set true by the controller when the last character is transmitted.

## (2) PE Formatter

The 8 write data lines (9 in the case of external parity option) are utilized to transmit write data from the controller to the formatter. W0 corresponds to the most significant bit and W7 to the least significant bit of each character.

The first character of a record should be available on these lines less than 40 character periods after DBY goes true and remain until the trailing edge of the first WSTR is issued by the formatter. The next character of information must then be placed on these lines within one-half of a character period.

Subsequent characters of a record are processed in this manner until LWD is set true by the controller when the lost character is transmitted.

# 2.3 INTERFACE OUTPUTS (formatter to controller)

The 7 track interface output signal is used exclusively in the NRZI formatter; all other interface outputs are common to both NRZI and PE formatters. Pins B24 and B23 (grd) output the CHECK CHARACTER GATE from NRZI formatters and the IDENTIFICATION from PE formatters. The controller must allow for this signal when combination NRZI/PE formatters are used. All pulsewidths must be 1 microsecond wide (min.).

### FORMATTER BUSY

**FBY**

Level

P101-B22

When true, this level inhibits further commands to the formatter. The level goes true on the trailing edge of GO when a command is issued by the controller. FBY will remain true until tape motion ceases.

# **DATA BUSY**

DBY

Level

P101-A22

This level goes true when the tape is up to speed, has traversed the IBG, and the formatter is about to

write data or look for a read signal on the tape. DBY remains true until data transfer is completed and the appropriate post record delay is completed. DBY goes false when the capstan starts to decelerate the

# HARD ERROR

P101-A24 Pulse HER (NRZI Mode)

When true, this pulse indicates a read error. This line will be true during read operations when one or more of the following occurs:

- Longitudinal parity error (1)

- Improper record format (2)

- CRCC parity error (3)

- Vertical parity error on a data character (4)

In all cases except a vertical parity error, HER will be pulsed after the complete record has been read. In the case of a vertical parity error, the HER line will be pulsed when a read strobe (RSTR) pulse is issued for the character in error. DBY goes false after all error information has been transferred to the controller.

# CORRECTED ERROR

P101-B25 CER Pulse (PE Mode Only)

When true, this pulse indicates that a single track dropout has been detected and the formatter is performing an error correction.

# HARD ERROR

HER Pulse P101-A244 (PE Mode)

When true, this pulse indicates that an uncorrectable read error has occurred and that the record should either be reread or rewritten. Here is a table illustrating the possible HER/CER signal combinutions, together with their meaning:

### SIGNAL STATES

HER

0 = No Errors Detected 0

1 = Single Channel Error 0 0 = Postamble or VRC ERROR Only -1

All Channels Believed Good

1 = Multiple Channel Errors or: Excessive Skew or: Single Channel Failure w/Postamble VRC Error

This timing chart illustrates the HER/CER minimum pulse widths at various tape speeds:

# HER/CER

A: 2 msec min. (12.5 ips) 1 msec min. (25 ips) 0.67 msec min. (37.5 ips)

# CHECK CHARACTER GATE

CCG Level P104-B24

(NRZI mode only)

This level is set true by the NRZI formatter when the

read information being transmitted to the controller is a cyclic redundancy check character (CRCC) or a longitudinal redundancy check character (LRCC). When data characters are transmitted, CCG goes false. Data and check information can be distinguished by gating READ STROBE (RSTR) with CCG or its inverse.

### IDENTIFICATION

**IDENT** Level P101-B24 (PE Mode)

When true, this level identifies PE tapes. PE tapes are detectable in the read forward mode by the presence of an identification burst on the parity channel.

# **FILE MARK**

FMK Pulse P101-A25

File mark is pulsed when a file mark is detected on the tape during a read operation or during a write file mark operation in a read-after-write transport. The FMK line will be pulsed after a complete file mark record has been read. Error conditions should be ignored when a file mark is detected.

# TRANSPORT STATUS AND CONFIGURATION LINES

These lines indicate the status and configuration of the selected transport to the controller after being gated with the formatter address signal, FAD. The low true transport status lines are: READY (RDY), ON LINE (ONL), REWINDING (RWD), FILE PROTECT (FPT), LOAD POINT (LP), and END OF TAPE (EOT).

Transport configuration lines are NRZ/PE, 7TK/9TK and LOW/HIGH.

# WRITE STROBE

WSTR Pulse P101-A34

This line pulses each time a data character is written onto tape. WSTR samples the write data lines WP. W0-W7 from the controller and copies this information character by character into the formatter write logic. The first character should be available prior to the first write strobe pulse and succeeding characters should be set up within half a character period after the trailing edge of each write strobe pulse. The write strobe is also active during variable length erase commands; however, the data being copied into the formatter will have no meaning.

# **READ STROBE**

RSTR Pulse P101-B36

This line consists of a pulse for each character of read information to be transmitted to the controller. These signals should be used to sample the read data lines RDP, RD0-RD7.

In NRZI formatters, the transmission of CRC and LRC data characters will be flagged by the check character gate (CCG) signal as described under HARD ERROR (HER).

# **READ DATA LINES**

RP, R0-R7

Levels

(See Pin List)

In the NRZI formatter, RP and R0-R7 are utilized for 9 channel operation; lines RP and R2-R7 are utilized for 7 channel operation. In PE formatters the 9 PE channels are assigned to RP, R0-R7.

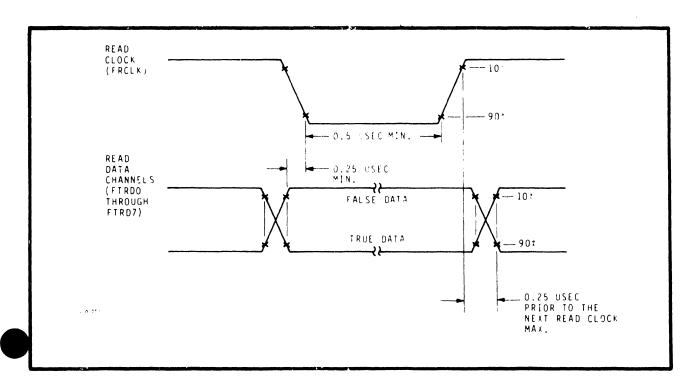

Each character read from tape is made available by parallel sampling the read lines with READ STROBE. Since the data remains on the read data lines for a full character period, the corresponding RSTR pulses are timed to occur after approximately the center of the character period.

# 2.4 INTERFACE CABLING REQUIREMENTS

The cables connecting the Format Control Unit to the tape transports are normally supplied with the system, and so are the cable connectors that mate with the card edge connectors on the units required for the interface cabling. The intercabling requirements are the same for NRZI or the dual density NRZI/phase encoded systems.

Twisted pair cabling should be used to reduce intercable crosstalk. All wires should be 24 AWG, minimum, with a minimum insulation thickness of 0.1 inch. Each pair should have not less than one twist per inch, and maximum cable length should not exceed 20 feet.

# 2.5 OPTIONS, SPEED AND DENSITY SELECTION (Refer to Table 2-1).

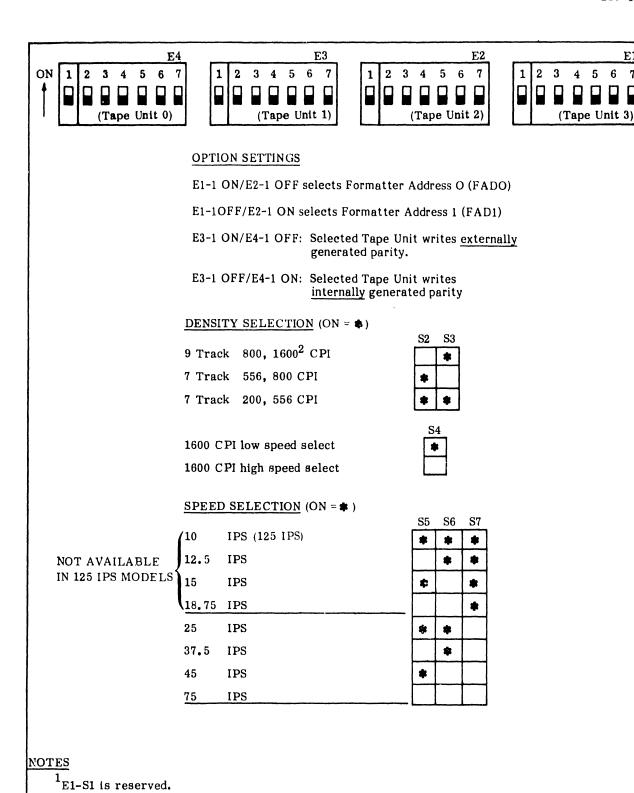

Tape speed and density as well as certain options are controlled by means of E1 through E4 on the interface board. Tape unit 0 is controlled by E4; tape unit 1 is controlled by E3, etc.

The options are selectable by switches S1 on E1 through E4. Switches S1 on ICs E1 and E2 determine whether formatter 0 or 1 is addressed. The positions of E3-1 and E4-1 determine whether internal or external parity is written on tape. Switches S2 through S7 on E1 through E4 supply tape unit commands and status signals to and from the individual tape units. Switch S2 on E1 through E4 is turned ON to select a 7 track tape unit; OFF to select a 9 track tape unit.

Switch S3 selects between 556/800 cpi and 200/556 cpi tape densities for 7 track tape units.

Switch S4 is reserved for PE applications and selects between a preset high or low tape speed. Since the PE board can only operate at two speeds, the formatter must be set up so that only two tape speeds are selectable at 1600 cpi. NRZI units have no such limitations.

Switches 5 through 7 can be set to various binary combinations for tape speed selection. Tape speeds possible are: 10 ips, 12.5 ips, 15 ips, 18.75 ips, 25 ips, 37.5 ips, 45 ips and 75 ips.

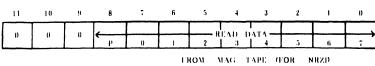

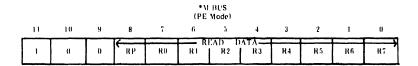

Figure 2-4. Read Data Timing

E1

7

<sup>2</sup>1600 CPI density requires P.E. re d recovery board.

# 2.6 DAISY CHAINING

The Model 9219 formatter can be connected to as many as four tape transports of varying tape speeds and character densities.

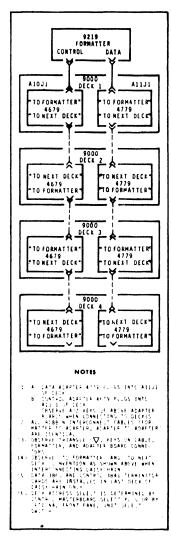

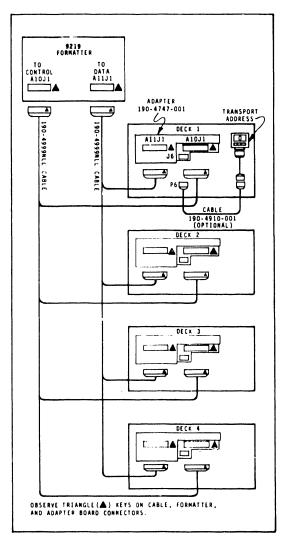

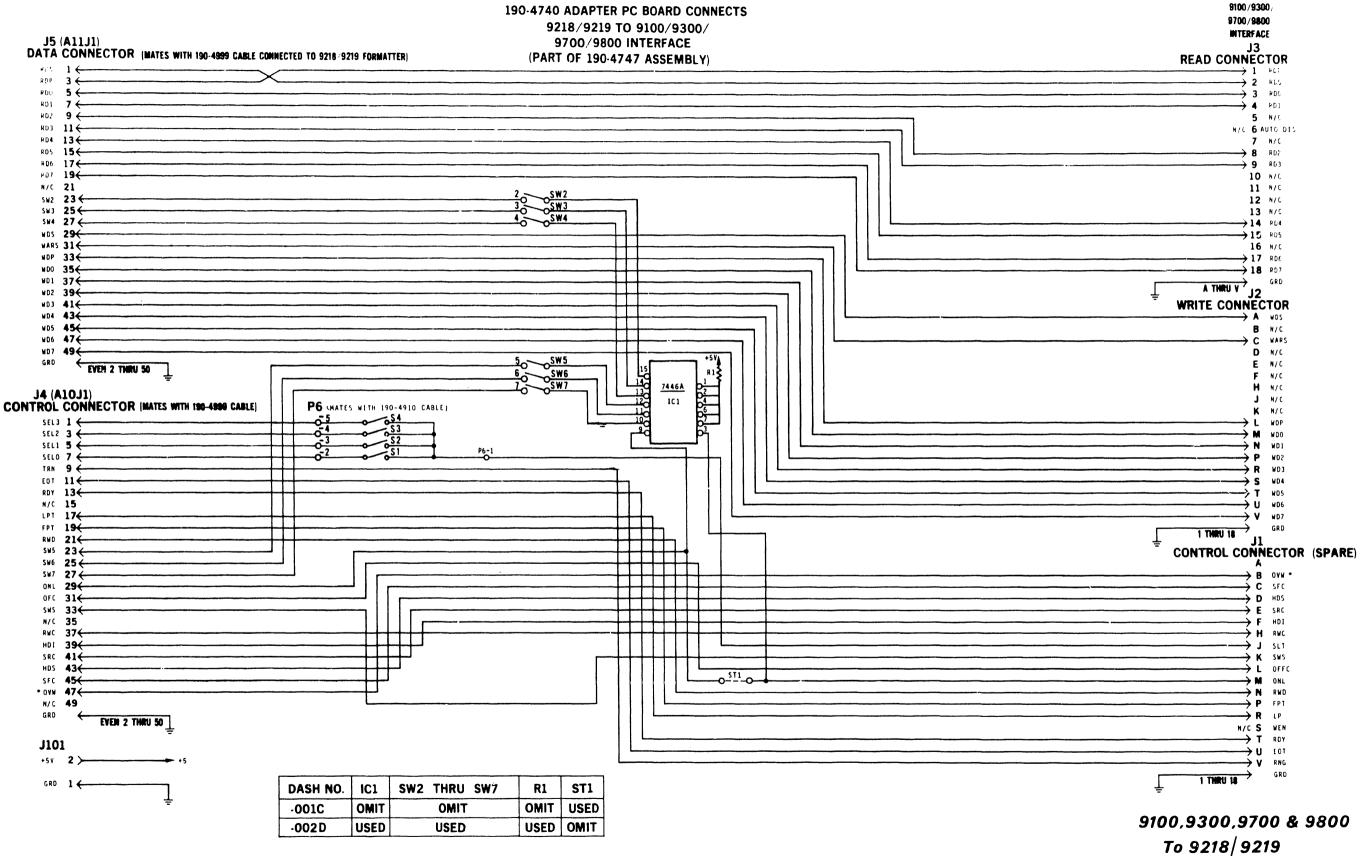

To connect the Model 9219 to Model 9000 transports, order one 190-4999-001 cable, one 190-4679-001 control adapter and one 190-4779-001 data adapter per transport. Figure 2-5 illustrates the daisychain connection. Note that the 3860 Data Terminator and the 3841 Control Terminator cards are only installed in the last deck of the daisychain.

To connect the Model 9219 to 9100, 9300, 9700 and/or 9800 tape transports, order one 190-4747-001 adapter board per transport and two 190-4999-NLL cables.

(When ordering, substitute the number of transports in the daisychain for N; and the total cable length in feet for LL. Twenty feet is the maximum length Figure 2-6 illustrates the daisychain available.) connection. As in Model 9000 daisvchain installations, the 3860 Data Terminator and the 3841 Control Terminator cards are installed in the last deck of the chain only. The 4747 adapter board contains a tape unit address select switch. Thus, each deck in the chain can be assigned an address. (SW1 on=tape unit one on; SW2 on=tape unit 2 on, etc). The tape unit address can also be controlled by the address select switch on the front panel of each transport. In this instance, all address switches on the adapter boards should be in the OFF position. A 190-4910-001 cable is used to connect the tape unit address switch to the 4747 adapter board.

Figure 2-5. Daisychain Connection-9219 to 9000 Transports

Figure 2-6. Daisychain Connection-9219 to 9100,9300,9700,9800 Transports

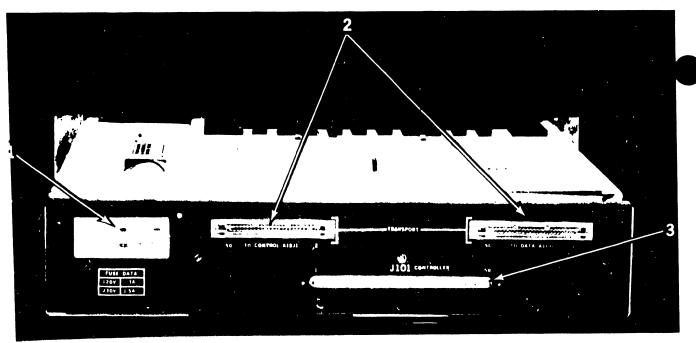

# J101, Model 9219 Formatter. Mates with P101 from Controller (SEE NOTE 1)

| PIN<br>(SIG/GRD) | MNEMONIC | SIGNAL                            | IN/OUT |

|------------------|----------|-----------------------------------|--------|

| A1/A2            | TADO     | Transport Address 0               | IN     |

| A3/A2            | GO       | Initiate Command                  | IN     |

| A4/A5            | WRT      | Write/Read                        | IN     |

| A6/A5            | EDIT     | Edit                              | IN     |

| A7/A8            | THR1     | Read Threshold Level 1 (Not Used) |        |

| A9/A8            | DEN      | Density Select (See Note 2)       | IN     |

| A10              |          | No Connection                     |        |

| A12/A11          | OFL      | Offline Command                   | IN     |

| A13/A14          | FEN      | Formatter Enable                  | IN     |

| A15/A14          | WP       | Write Data Parity                 | IN     |

| A16/A17          | W1       | Write Data 1                      | IN     |

| A18/A17          | W3       | Write Data 3                      | IN     |

| A19/A20          | W5       | Write Data 5                      | IN     |

| A21/A20          | W7       | Write Data 7                      | IN     |

| A22/A23          | DBY      | Data Busy                         | OUT    |

| A24/A23          | HER      | Hard Error                        | OUT    |

| A25/A26          | FMK      | File Mark                         | OUT    |

| A27/A26          | ONL      | On Line                           | OUT    |

| A28/A29          | FPT      | File Protect                      | OUT    |

| A30/A29          | EOT      | End of Tape                       | оит    |

| A31/A32          | NRZI/PE  | NRZI/PE                           | OUT    |

| A33/A32          | SGL      | Single (Not Used)                 |        |

| A34/A35          | WRST     | Write Strobe                      | OUT    |

| A36/A35          | RP       | Read Data Channel P               | OUT    |

| A37/A38          | R1       | Read Data Channel 1               | OUT    |

| A39/A38          | R3       | Read Data Channel 3               | OUT    |

| A40/A41          | R5       | Read Data Channel 5               | OUT    |

| A42/A41          | R7       | Read Data Channel 7               | OUT    |

| A43-47           |          | No Connection                     |        |

| A48,49,50        |          | +5vde                             |        |

| B1/B2            | FAD      | Formatter Address                 | IN     |

| B3/B2            | TAD1     | Transport Address                 | IN     |

| B4/B5            | REV      | Reverse/Forward                   | IN     |

| B6/B5            | WFM      | Write File Mark                   | IN     |

| B7/B8            | ERASE    | Erase                             | IN     |

| B9/B8            | THR2     | Read Threshold Level 2 (Not Used) |        |

| B10/B11          | PAR      | Parity Select (See Note 2)        | IN     |

| B12/B11          | REW      | Rewind                            | IN     |

| B13/B14          | LWD      | Last Word                         | IN     |

Table 2-2. Interface Pin List

J101, Model 9219 Formatter (continued)

| PIN<br>(SIG/GRD) | MNEMONIC | SIGNAL                         | IN/OUT |

|------------------|----------|--------------------------------|--------|

| B16/B17          | W0       | Write Data 0                   | IN     |

| B18/B17          | W 2      | Write Data 2                   | IN     |

| B19/B20          | W4       | Write Data 4                   | IN     |

| B21/B20          | W6       | Write Data 6                   | IN     |

| B22/B23          | FBY      | Formatter Busy                 | OUT    |

| B24/B23          | CCG      | Check Character Gate (Note 2)  | OUT    |

| B24/B23          | IDENT    | Identification (Note 3)        | OUT    |

| B25/B26          | CER      | Corrected Error                | OUT    |

| B27/B26          | RDY      | Ready                          | оит    |

| B28/B29          | RWD      | Rewinding                      | OUT    |

| B30/B29          | LDP      | Load Point                     | OUT    |

| B33/B32          | 7TK/9TK  | 7 Track/9 Track                | OUT    |

| B34/B35          | SPEED    | Low/High Tape Speed (Not Used) | OUT    |

| B36/B35          | RSTR     | Read Strobe                    | OUT    |

| B37/B38          | R0       | Read Data 0                    | OUT    |

| B39/B38          | R2       | Read Data 2                    | OUT    |

| B40/B41          | R4       | Read Data 4                    | OUT    |

| B42/B41          | R6       | Read Data 6                    | OUT    |

| B43-47           |          | No Connection                  |        |

| B48,49,50        |          | Ground                         |        |

NOTE 1:

Due to space limitations, the B terminals are unmarked. However, the B terminal numbers correspond to the A terminal numbers on the opposite side of the circuit board.  $\Box$

NOTE 2:

Used in NRZI configurations only.

NOTE 3:

Used in PE configurations only.

Control Connector, Model 9219 Formatter Mates with 190-4999-XXX Control Cable

| PIN     |          | 1 190-4999-AAA Control Caple |        |

|---------|----------|------------------------------|--------|

| SIG/GRD | MNEMONIC | SIGNAL                       | IN/OUT |

| 1/2     | SEL3     | Tape Address Select 3        | OUT    |

| 3/4     | SEL2     | Tape Address Select 2        | OUT    |

| 5/6     | SEL1     | Tape Address Select 1        | OUT    |

| 7/8     | SEL0     | Tape Address Select 0        | OUT    |

| 9/10    | RNG      | Tape Running                 | IN     |

| 11/12   | EOT      | End of Tape                  | IN     |

| 13/14   | RDY      | Ready                        | IN     |

| 15/16   |          | Not Used                     |        |

| 17/18   | LDP      | Load Point                   | IN     |

| 19/20   | FPT      | File Protect                 | IN     |

| 21/22   | RWD      | Rewind                       | OUT    |

| 23/24   |          | Not Used                     |        |

| 25/26   |          | Not Used                     |        |

| 27/28   |          | Not Used                     |        |

| 29/30   | ONL      | Online                       |        |

| 31/32   | OFFC     | Offline Command              | OUT    |

| 33/34   | sws      | Set Write Status             | OUT    |

| 35/36   | SEL      | Tape Unit Select             | OUT    |

| 37/38   | RWC      | Rewind Command               | OUT    |

| 39/40   | HDI      | High Density Indicator       | IN     |

| 41/42   | SRC      | Synchronous Reverse Command  | OUT    |

| 43/44   | HDS      | High Density Status          | OUT    |

| 45/46   | SFC      | Synchronous Forward Command  | OUT    |

| 47/48   | OVW      | Overwrite                    | OUT    |

Data Connector, Model 9219 Formatter Mates with 190-4999-XXX Data Cable

| PIN<br>SIG/GRD | MNEMONIC | SIGNAL                       | IN/OUT |

|----------------|----------|------------------------------|--------|

| 1/2            | RDS      | Read Data Strobe             | IN     |

| 3/4            | RDP      | Read Data Channel P          | IN     |

| 5/6            | R D0     | Read Data Channel O          | IN     |

| 7/8            | RD1      | Read Data Channel 1          | IN     |

| 9/10           | RD2      | Read Data Channel 2          | IN     |

| 11/12          | RD3      | Read Data Channel 3          | IN     |

| 13/14          | RD4      | Read Data Channel 4          | IN     |

| 15/16          | RD5      | Read Data Channel 5          | IN     |

| 17/18          | RD6      | Read Data Channel 6          | IN     |

| 19/20          | RD7      | Read Data Channel 7          | IN     |

| 21/22          | RGAP     | Read Gap Detect              | IN     |

| 23/24          |          | Not Used                     |        |

| 25/26          |          | Not Used                     |        |

| 27/28          |          | Not Used                     |        |

| 29/30          | WDS      | Write Data Strobe            | OUT    |

| 31/32          | WARS     | Write Amplifier Reset Strobe | OUT    |

| 33/34          | WDP      | Write Data Channel P         | OUT    |

| 35/36          | WD0      | Write Data Channel O         | OUT    |

| 37/38          | WD1      | Write Data Channel 1         | OUT    |

| 39/40          | WD2      | Write Data Channel 2         | OUT    |

| 41/42          | WD3      | Write Data Channel 3         | OUT    |

| 43/44          | WD4      | Write Data Channel 4         | OUT    |

| 45/46          | WD5      | Write Data Channel 5         | OUT    |

| 47/48          | WD6      | Write Data Channel 6         | OUT .  |

| 49/50          | WD7      | Write Data Channel 7         | OUT    |

# SECTION 3 THEORY 0F OPERA-TION

# THEORY OF OPERATION

### 3.1 GENERAL

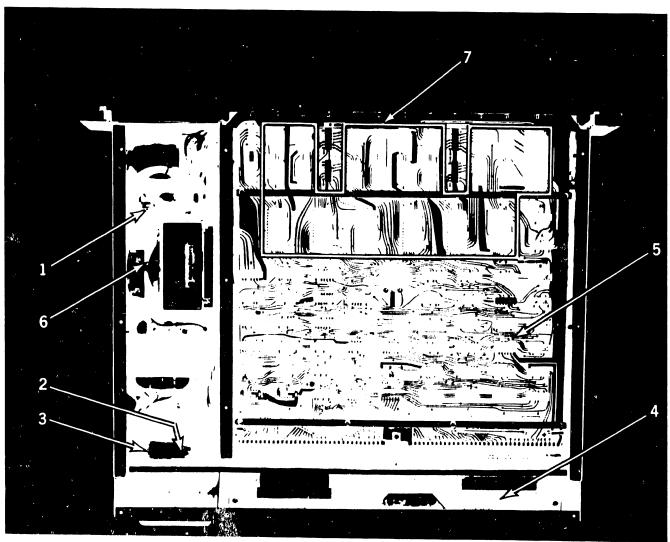

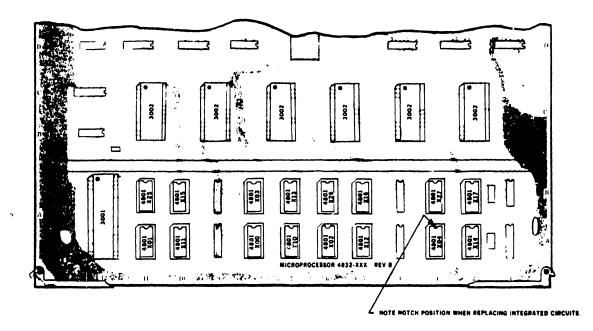

The Model 9219 Formatter consists of a microprocessor, an interface board, a masterboard and an optional PE read board required for phase encoded data applications. The one-to-one circuitry configuration of the masterboard makes all tape deck I/O signals available to these boards at the same relative pin positions.

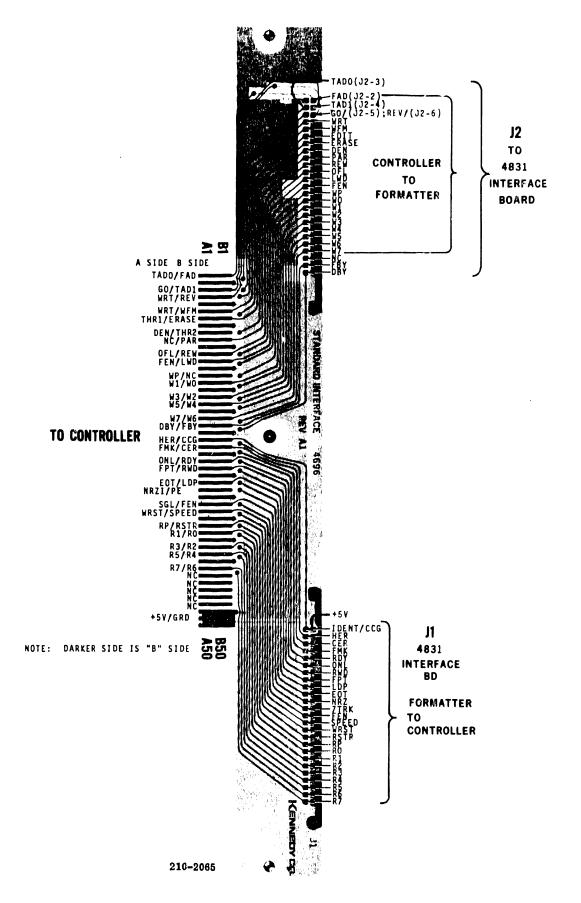

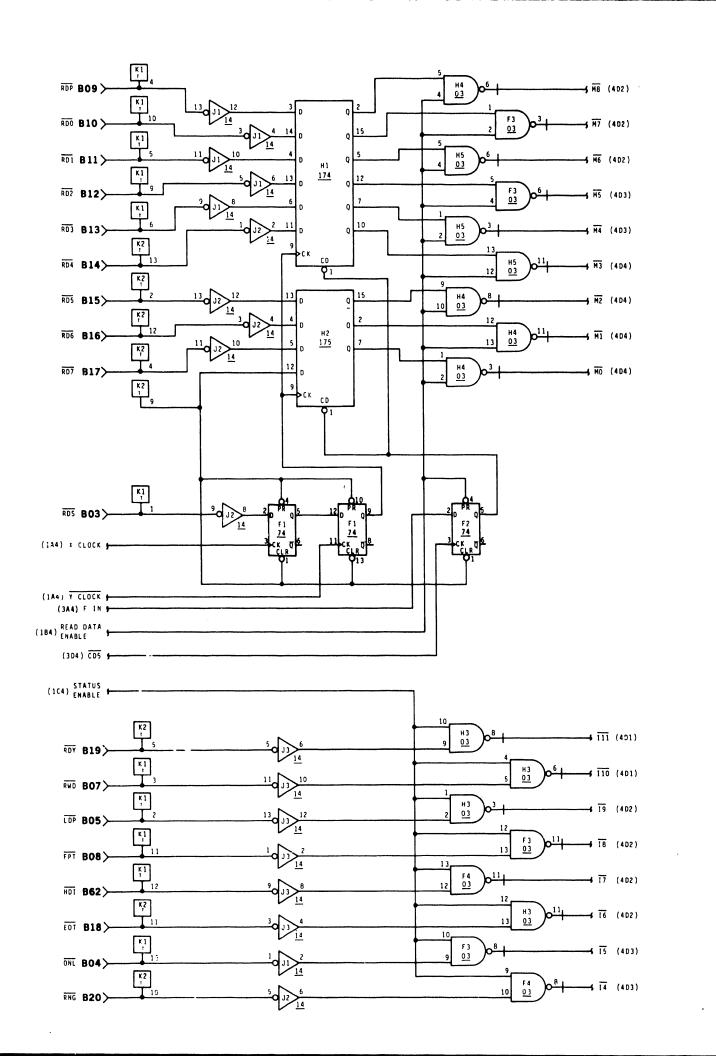

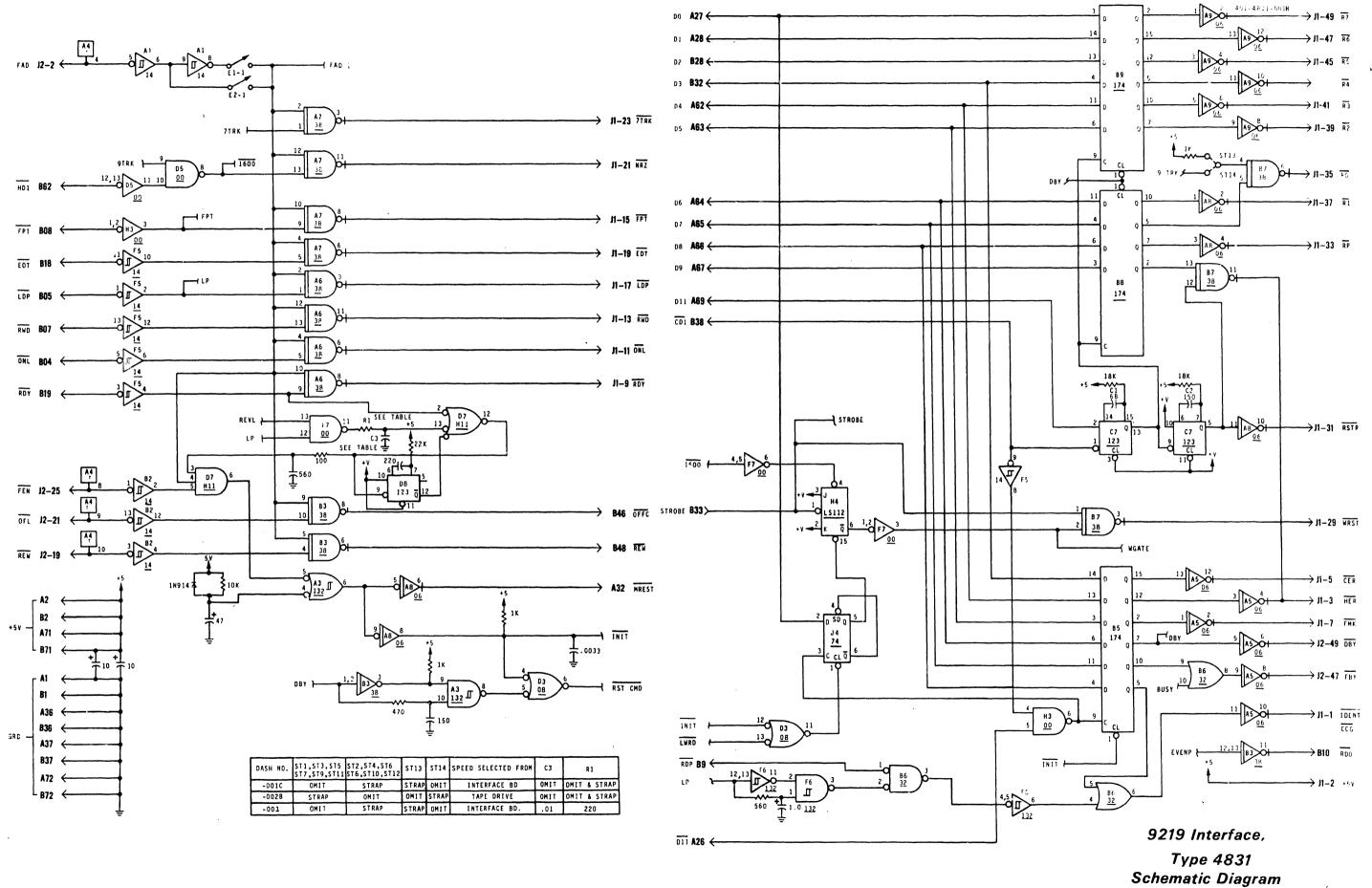

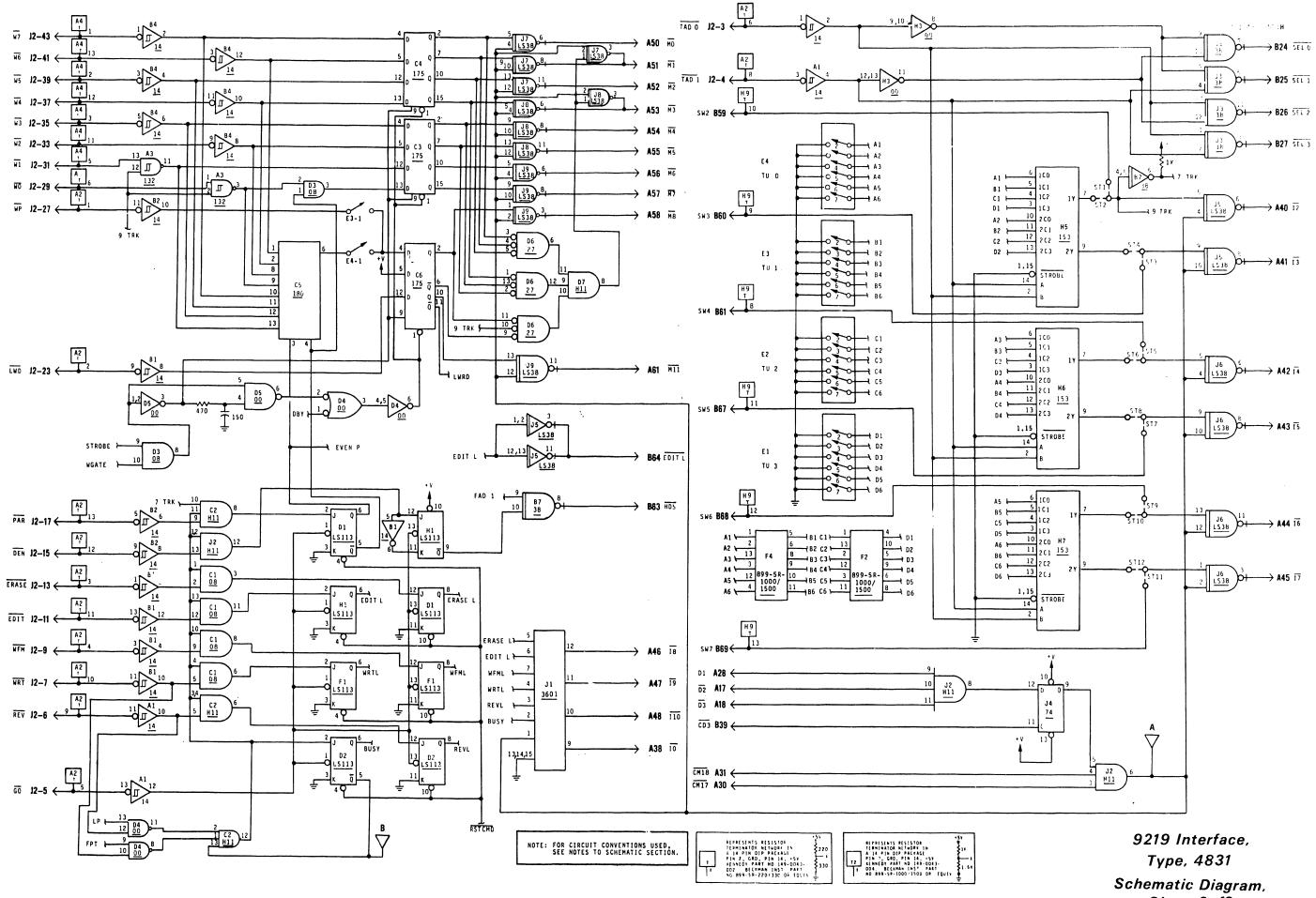

The interface board adapts the Model 9219 to the Pertec controller. All read and write data, computer commands, and tape transport status signals pass through this board. Most tape transport status signals enter the interface board from the masterboard, while write data and computer commands are input on interface board connector J2. Interface board connector J1 outputs read data and transport status signals to the controller.

The microprocessor board is connected to the interface board, the tape unit(s) and the controller through the masterboard. It is capable of driving and selecting tape decks, outputting commands to tape decks and reading status from tape decks. (In normal configurations the interface board selects tape transports, although the microprocessor board may be modified to do this.) In certain applications where responses must be immediate, the microprocessor may be bypassed, or it may look at tape deck signals simultaneously with other formatter boards.

The microprocessor reads and writes at an internally determined data rate which is selectable from 10 to 75 ips in any one of five formats. For seven track tape decks, selectable densities are 200/556 epi or 556/800 epi. For nine track machines, 800 or 1600 epi densities may be selected. The only limitation is that no more than two tape speeds are selectable at 1600 epi. Selectable speeds include: 10 ips, 12.5 ips, 15 ips, 18.75 ips, 25 ips, 37.5 ips, 45 ips, and 75 ips.

Speed selection, density and certain other options are controlled by switches E1 through E4 on the interface board. (See Table 2-6 for IC switch settings).

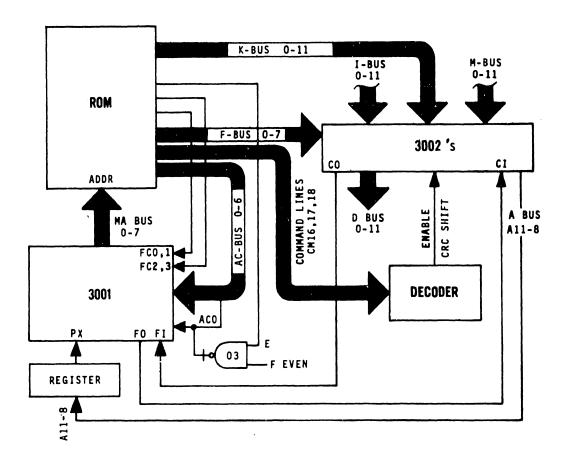

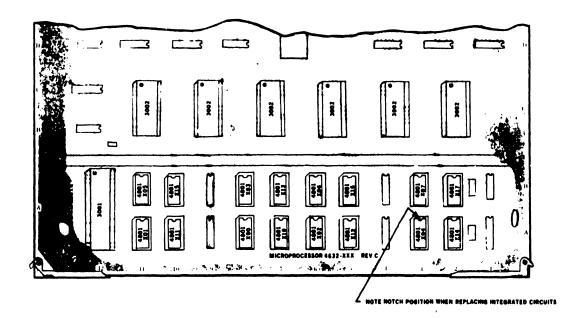

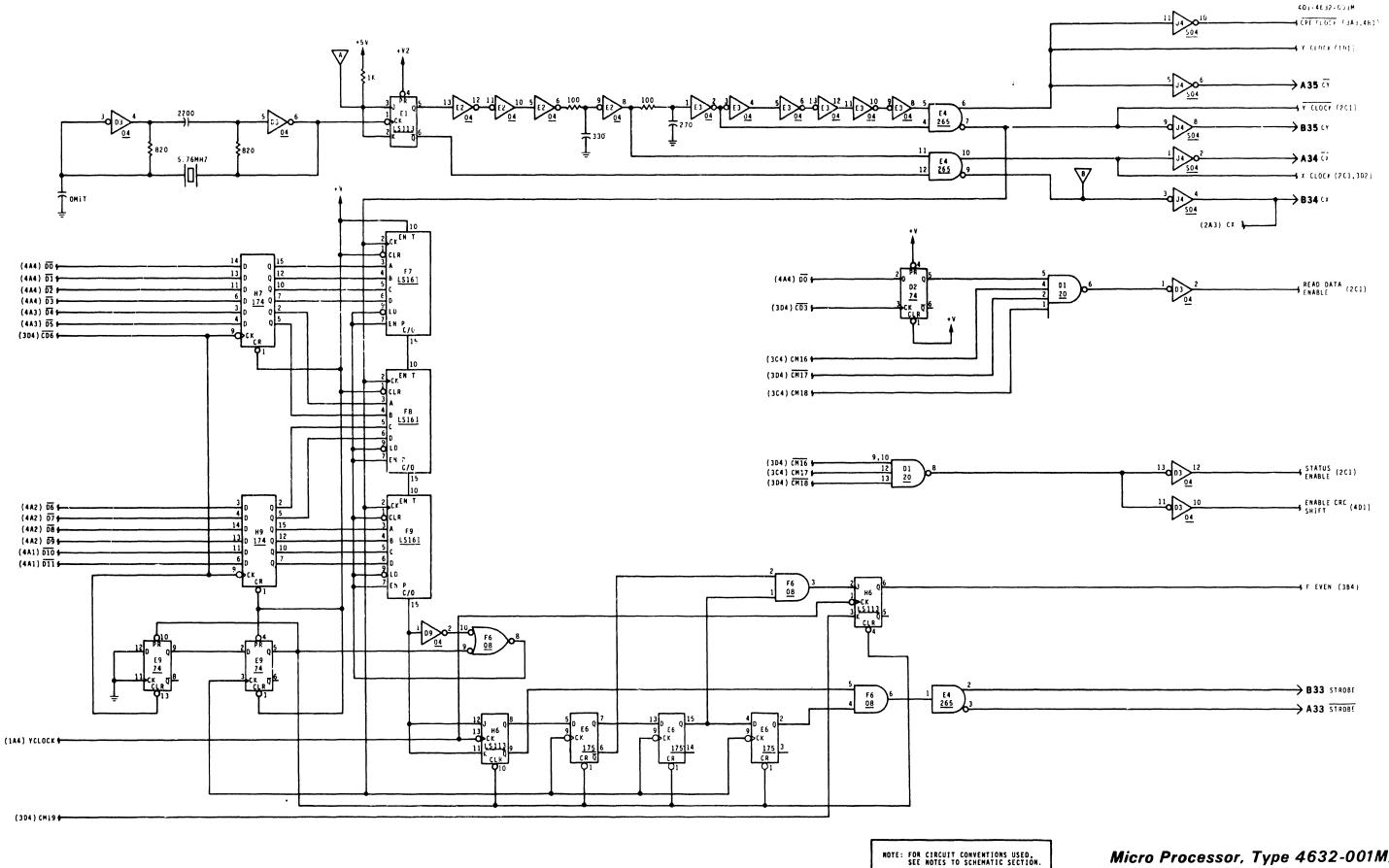

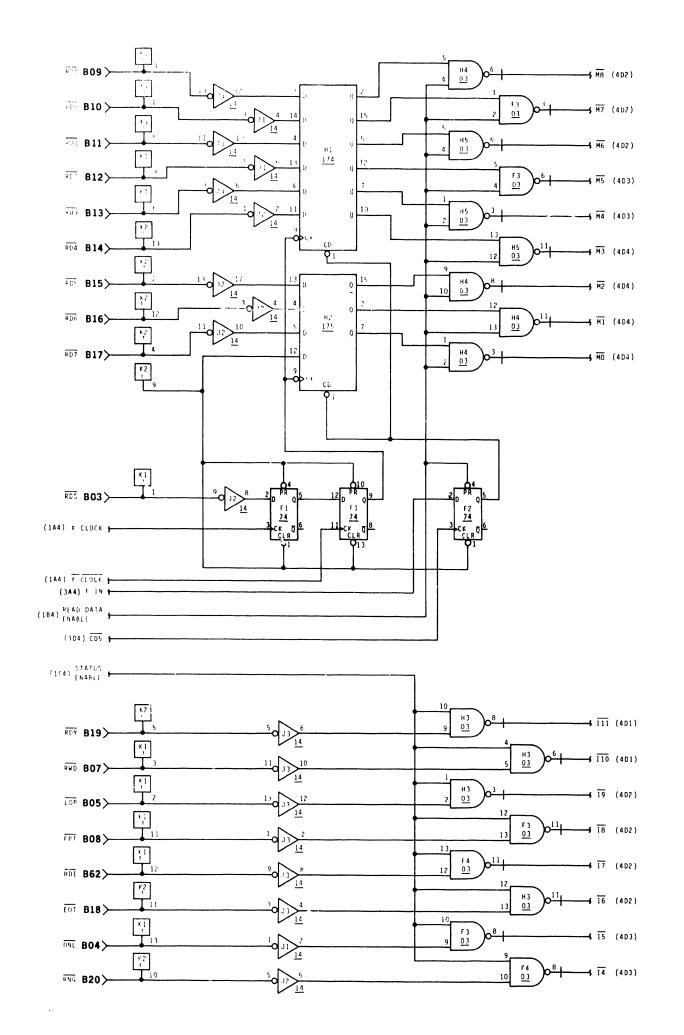

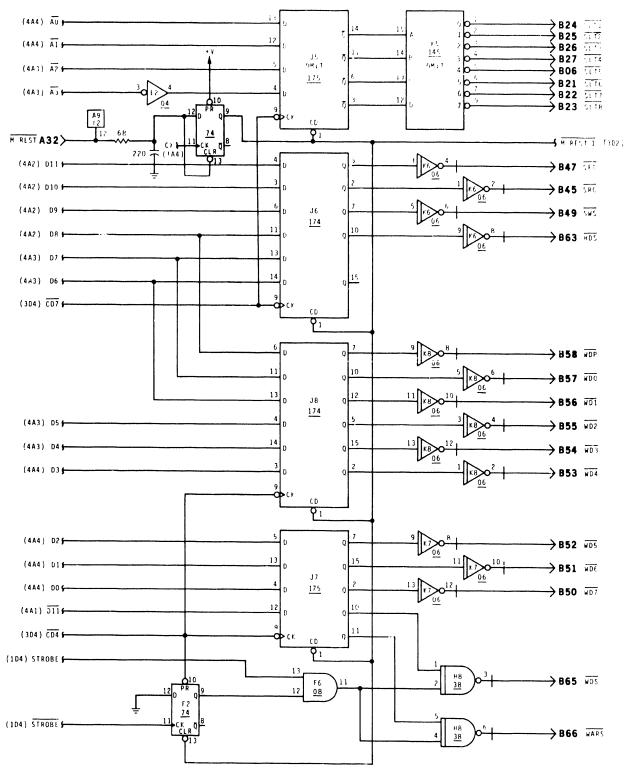

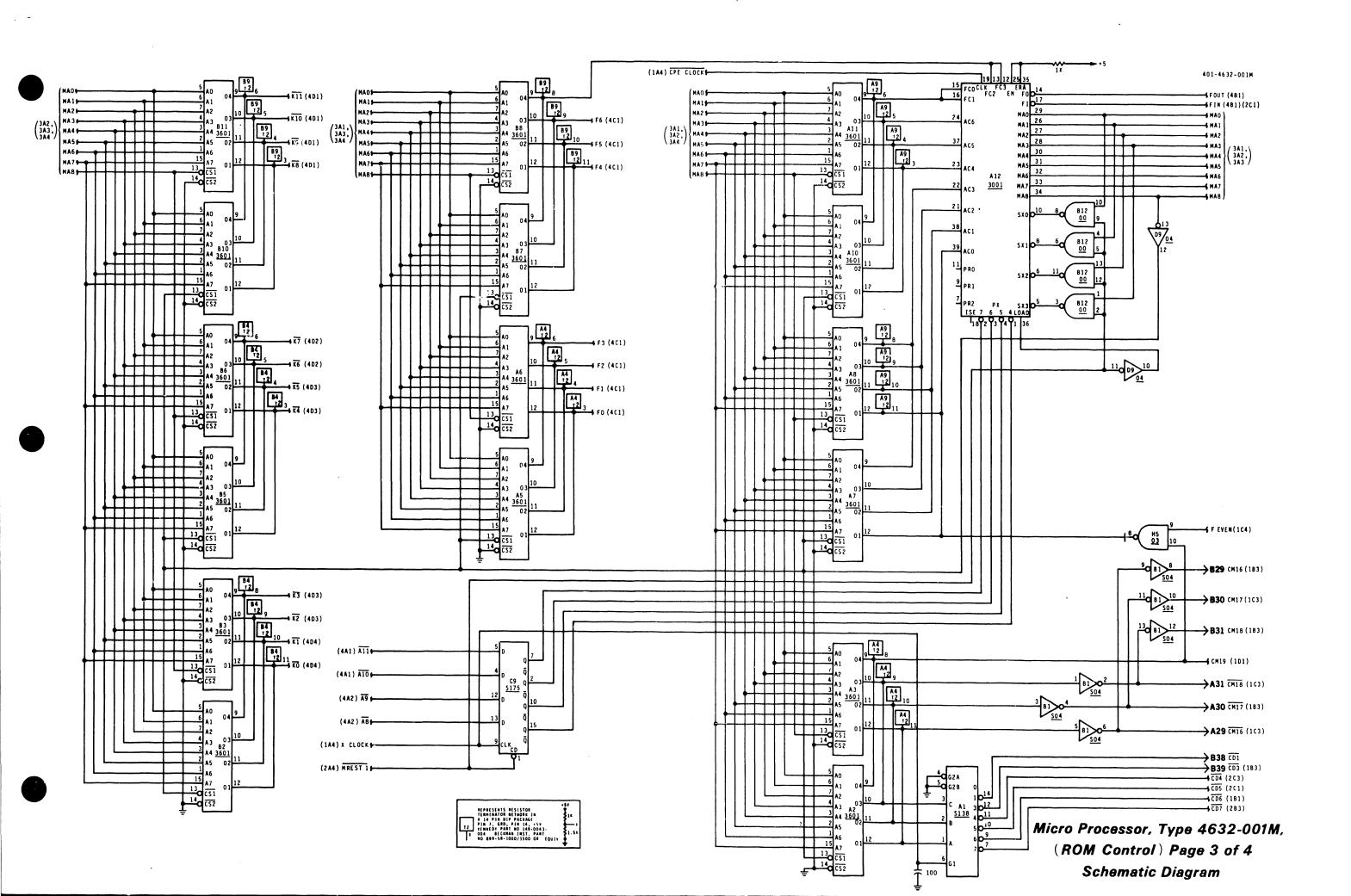

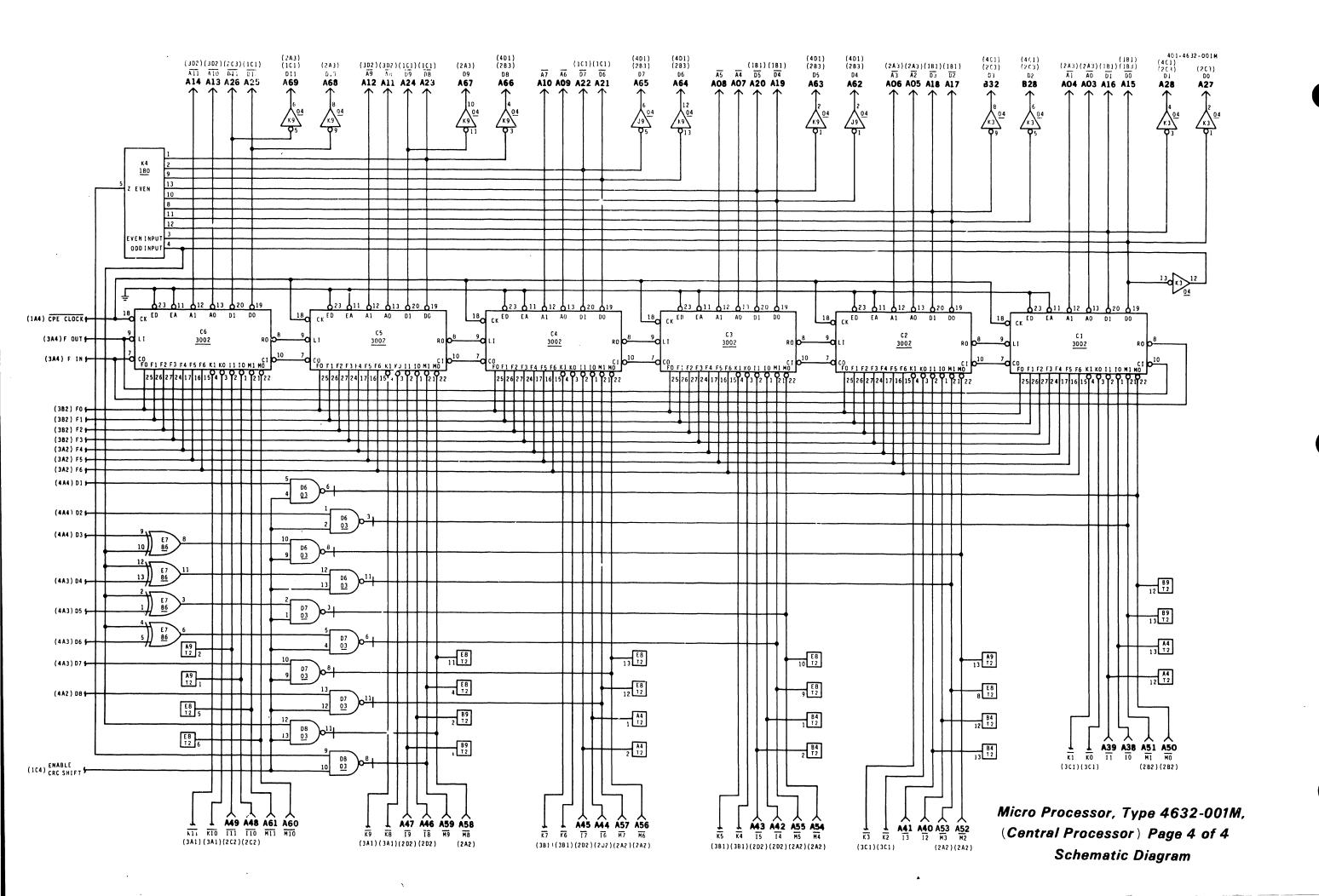

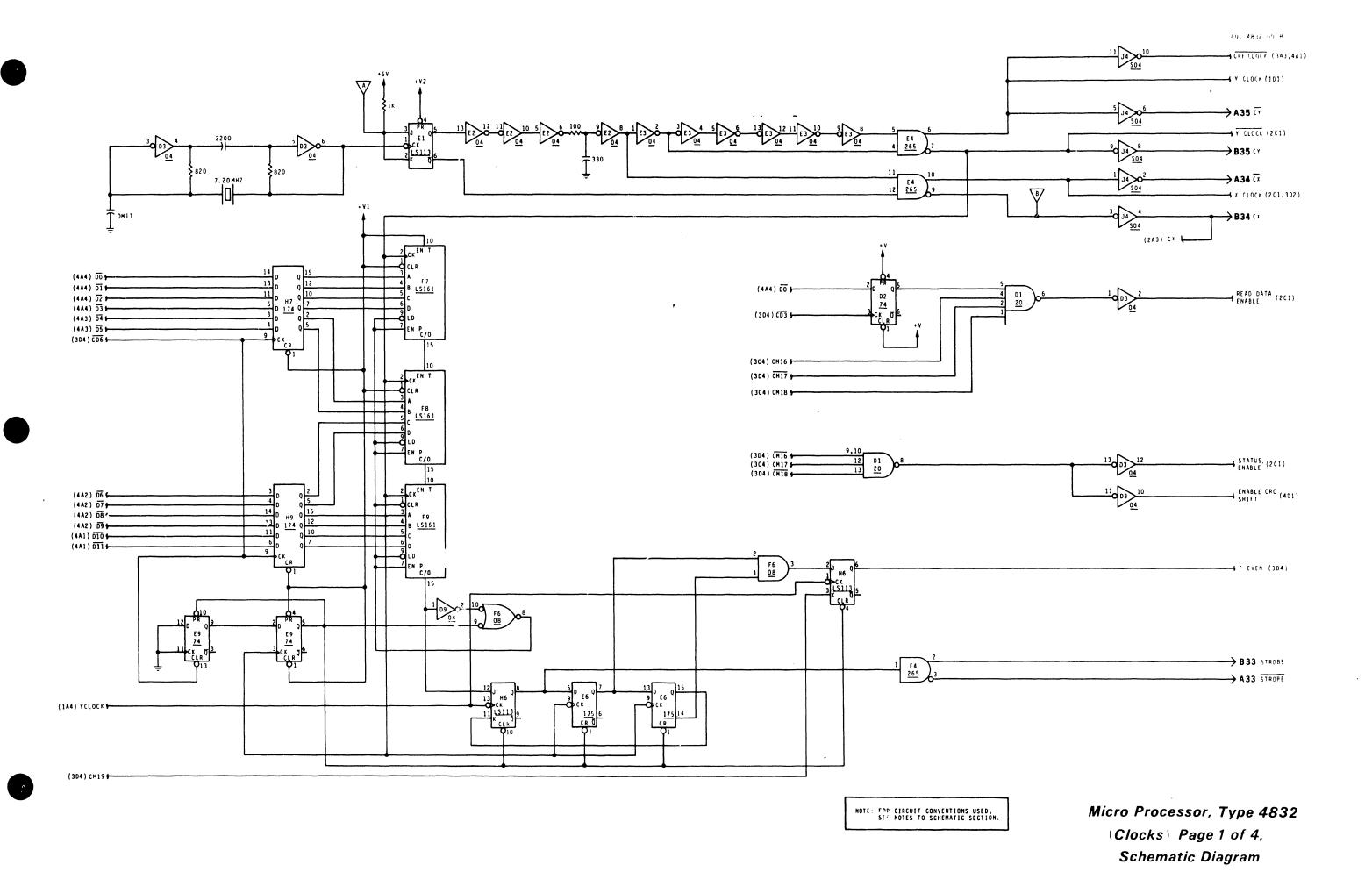

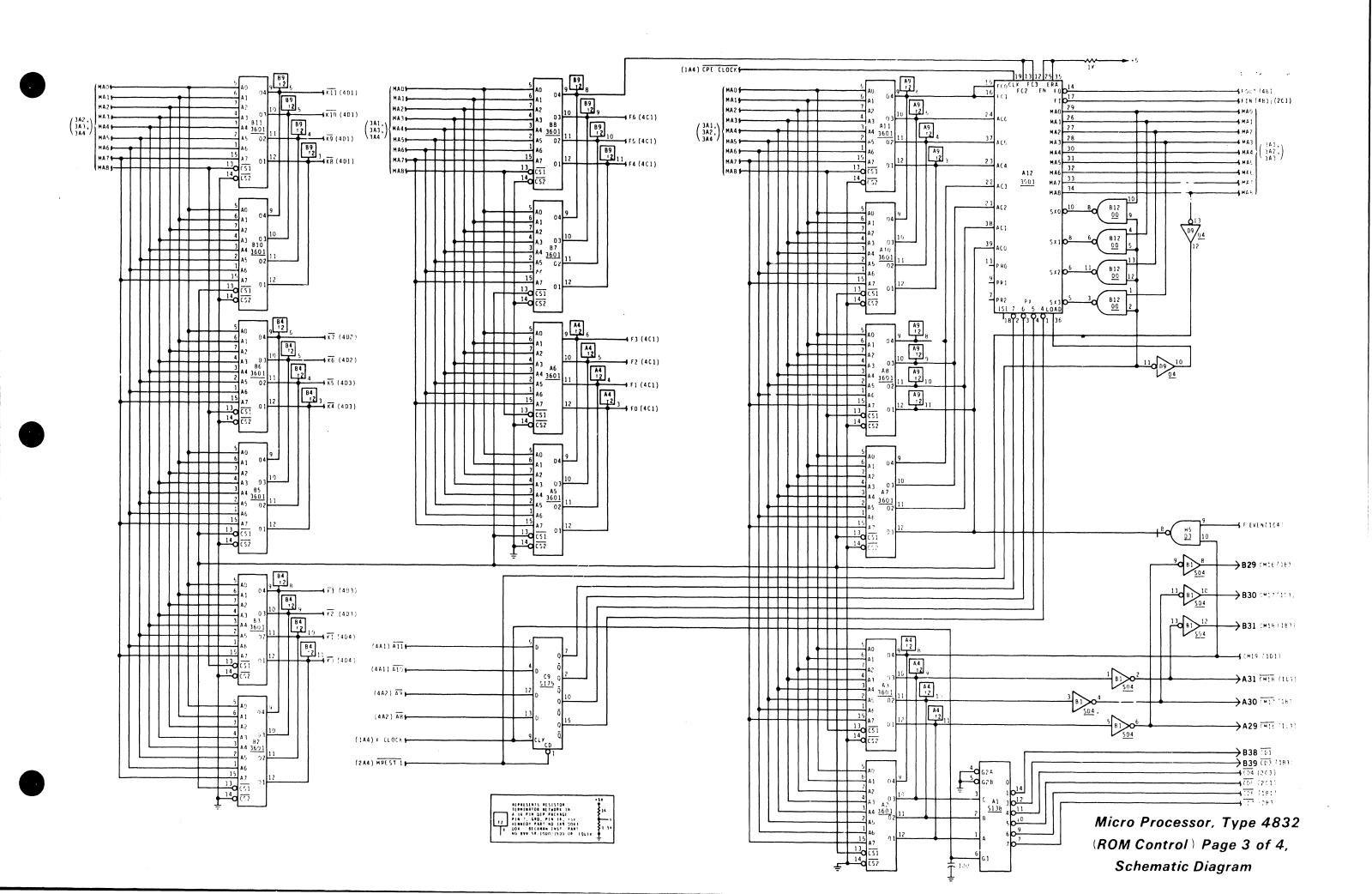

## 3.2 TYPE 4632/4832 MICROPROCESSOR BOARD

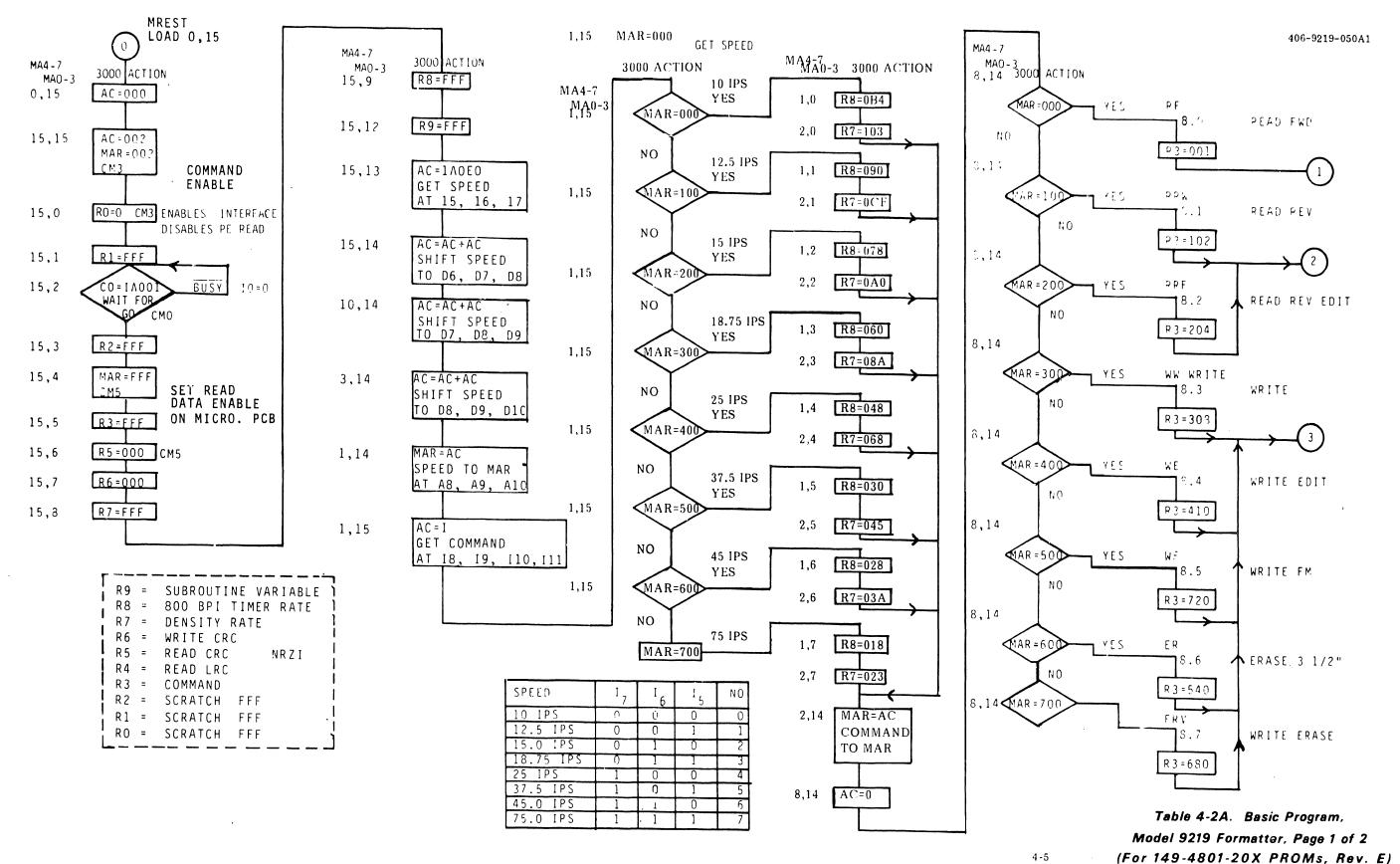

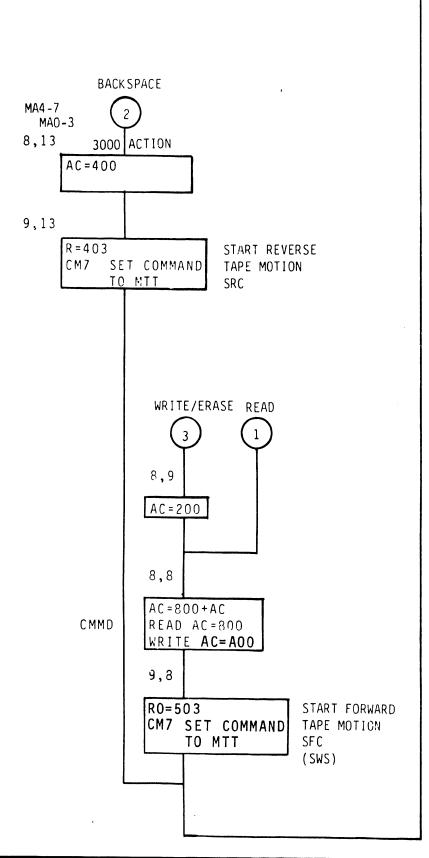

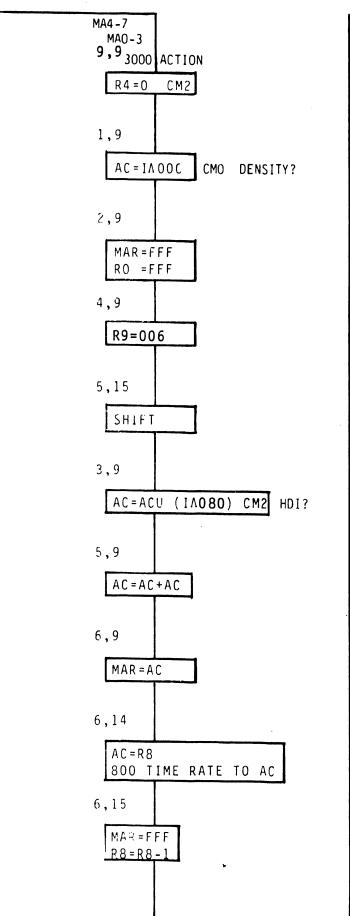

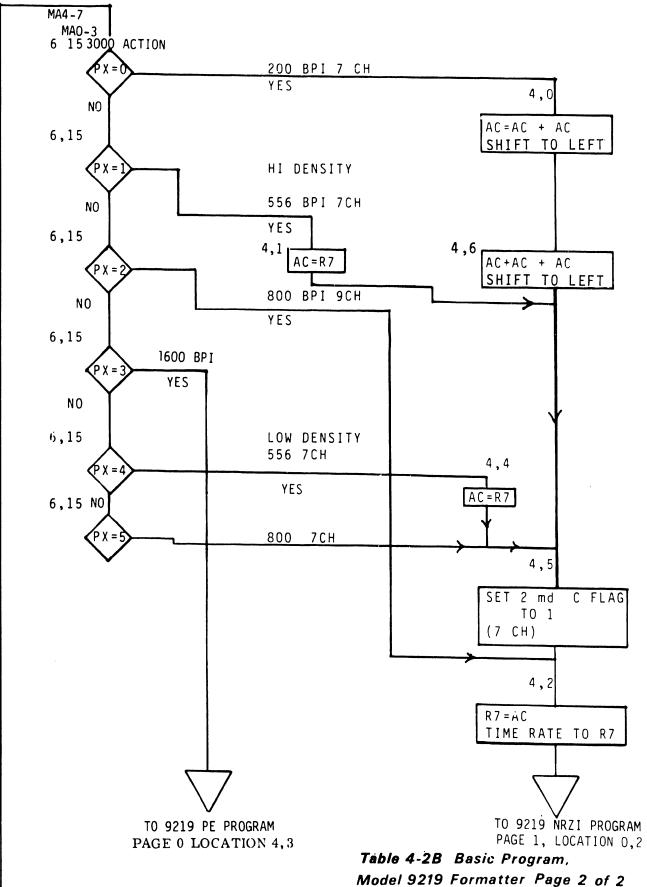

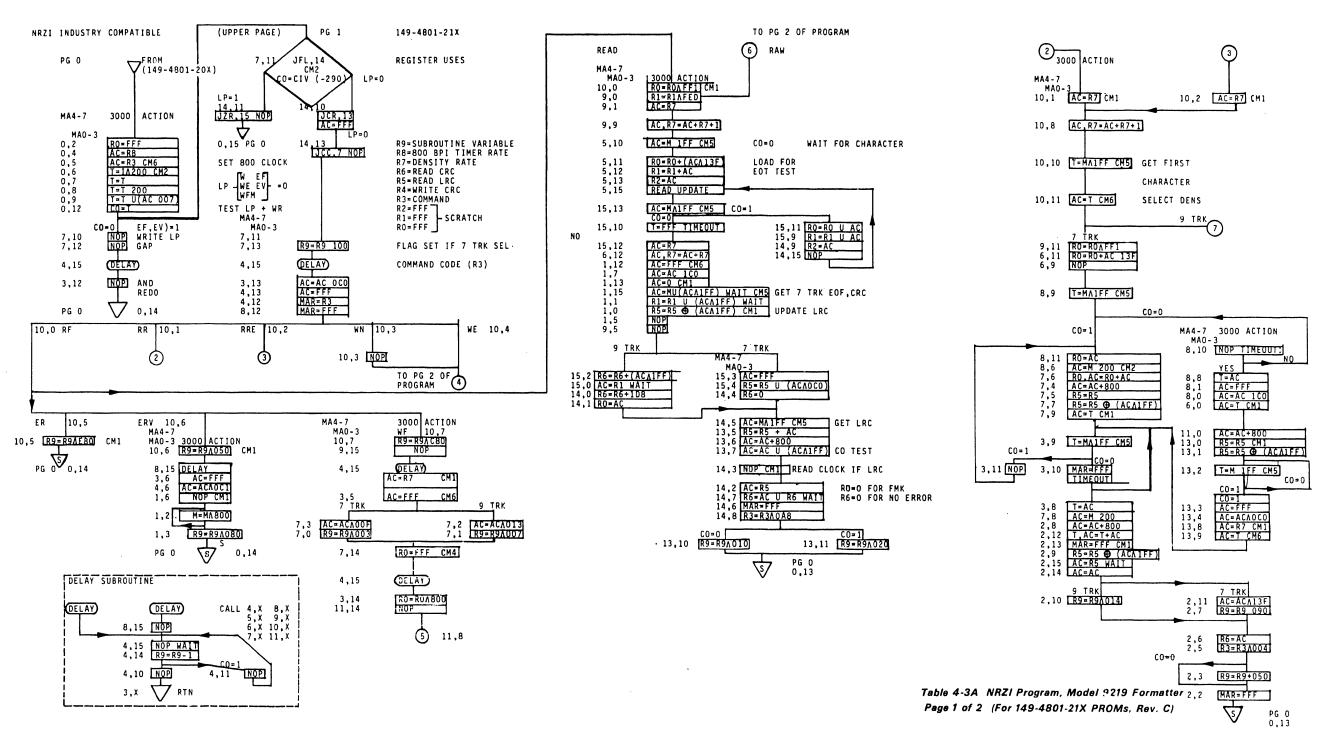

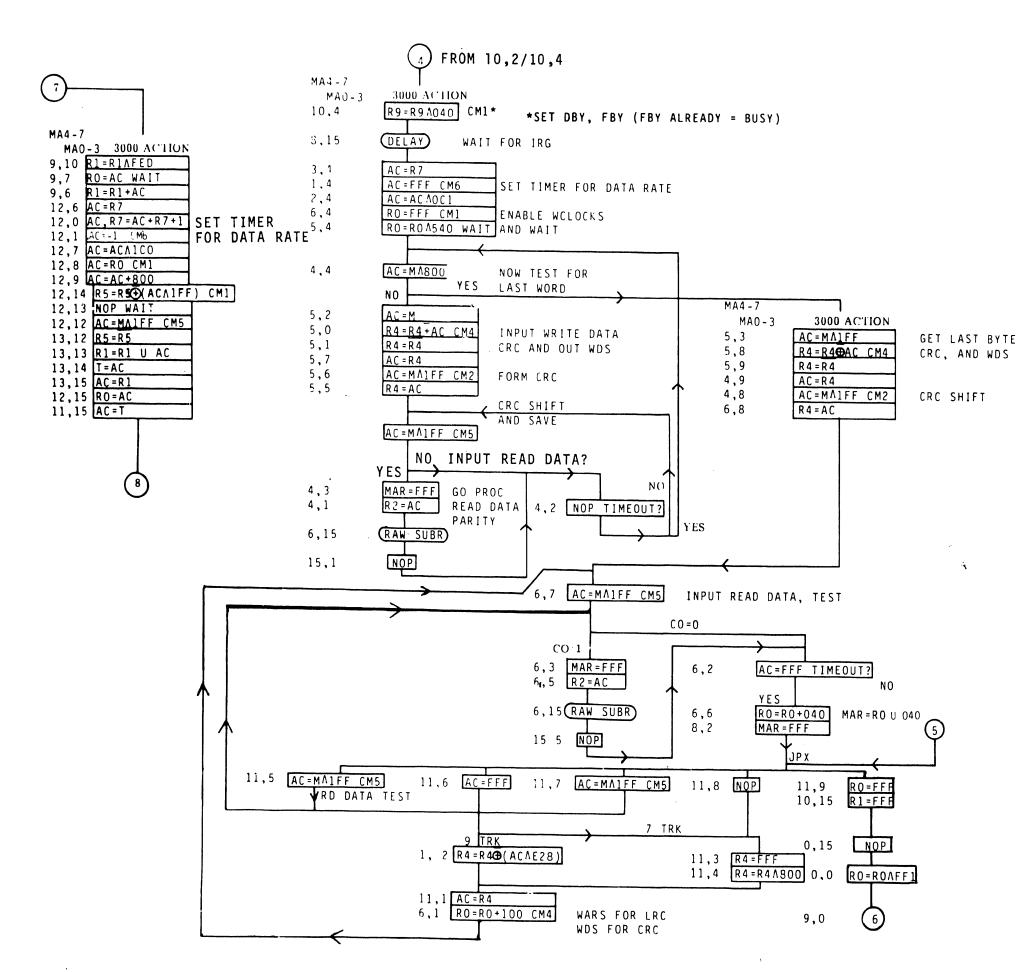

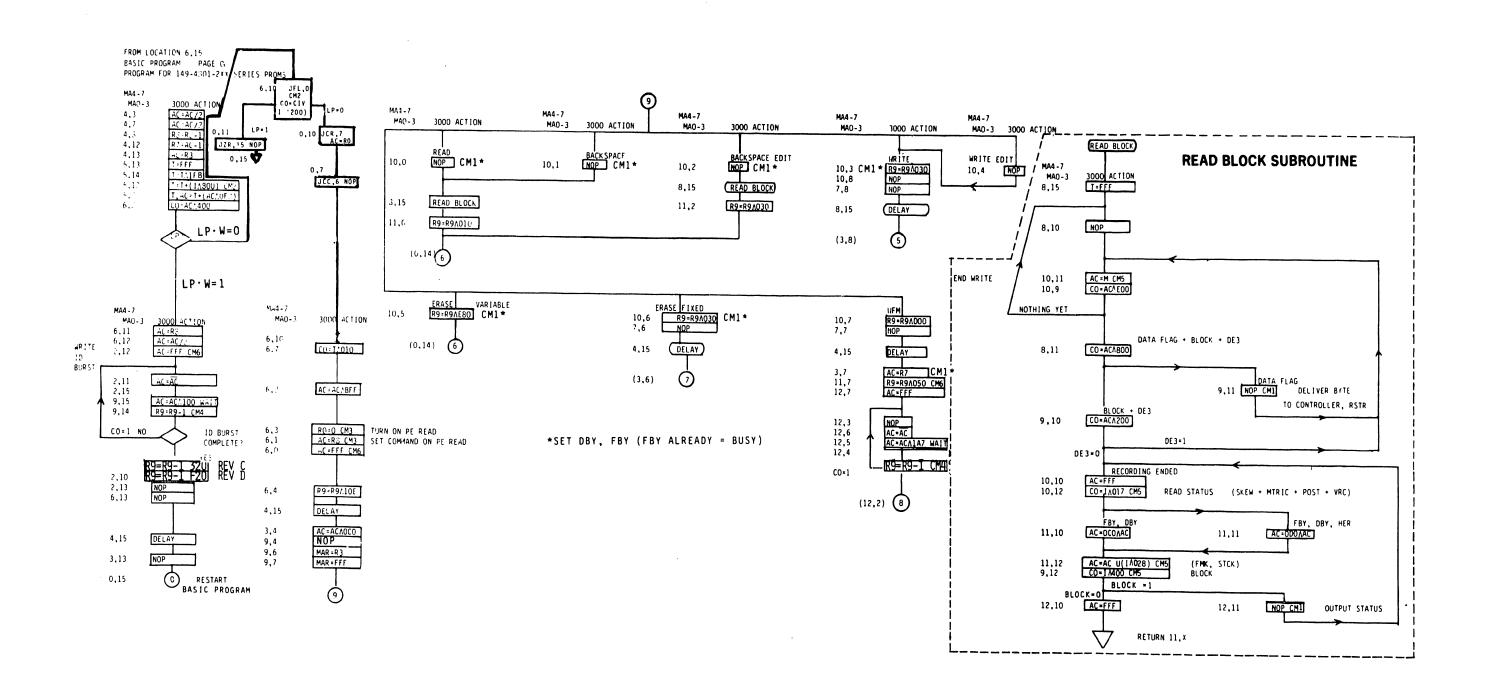

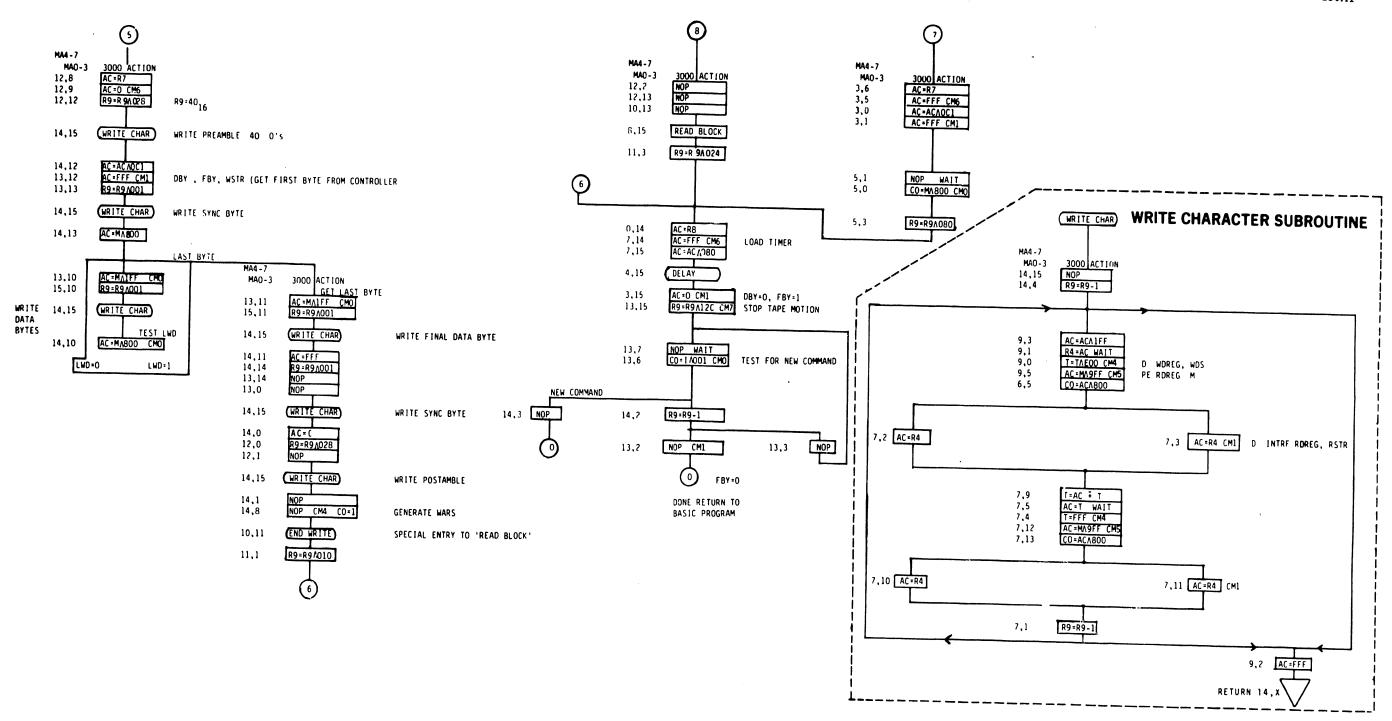

This board is microprogramed to control data, transport command and transport status flow between the selected tape transport and the controller. All inputs and outputs to the microprocessor board are made through the A and B busses of the masterboard. Tables 4-1A and 4-1B in the maintenance section list all masterboard connections. The maintenance section also contains the basic, NRZI, and PE

programs for the formatter. (The program sequence begins on the basic flow chart, then branches to either the NRZI or PE flow chart, depending on formatter type and recording density.)

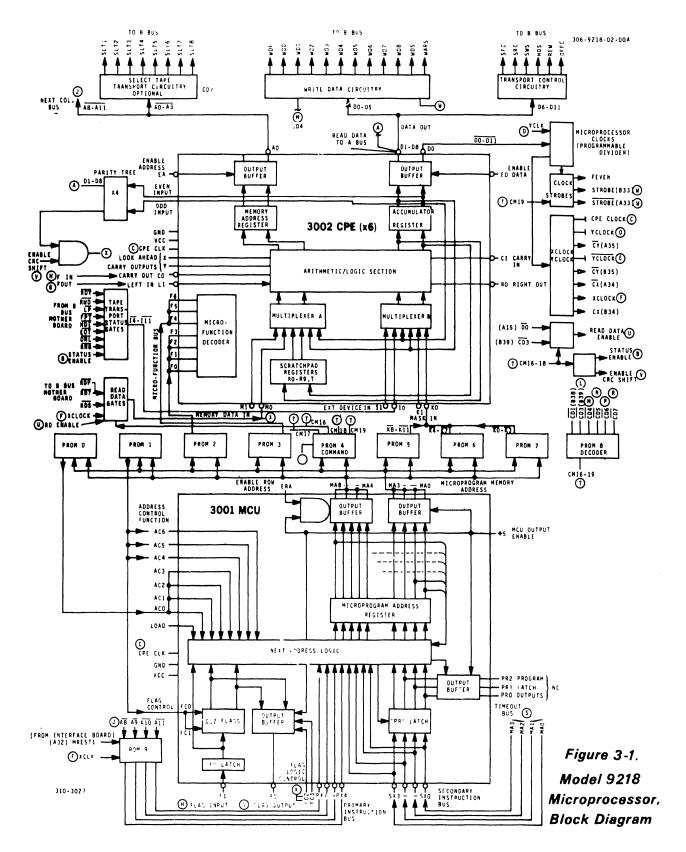

The major functional components of the board include: six bipolar Shottky 3002 Central Processing Elements (CPEs), one 3001 Microprogram Control Unit (MCU) and, depending on formatter application, 8 or 16 3601 Programable Read Only Memories (PROMs). Figure 3-1 is a block diagram showing the interrelationship between these major functional elements.

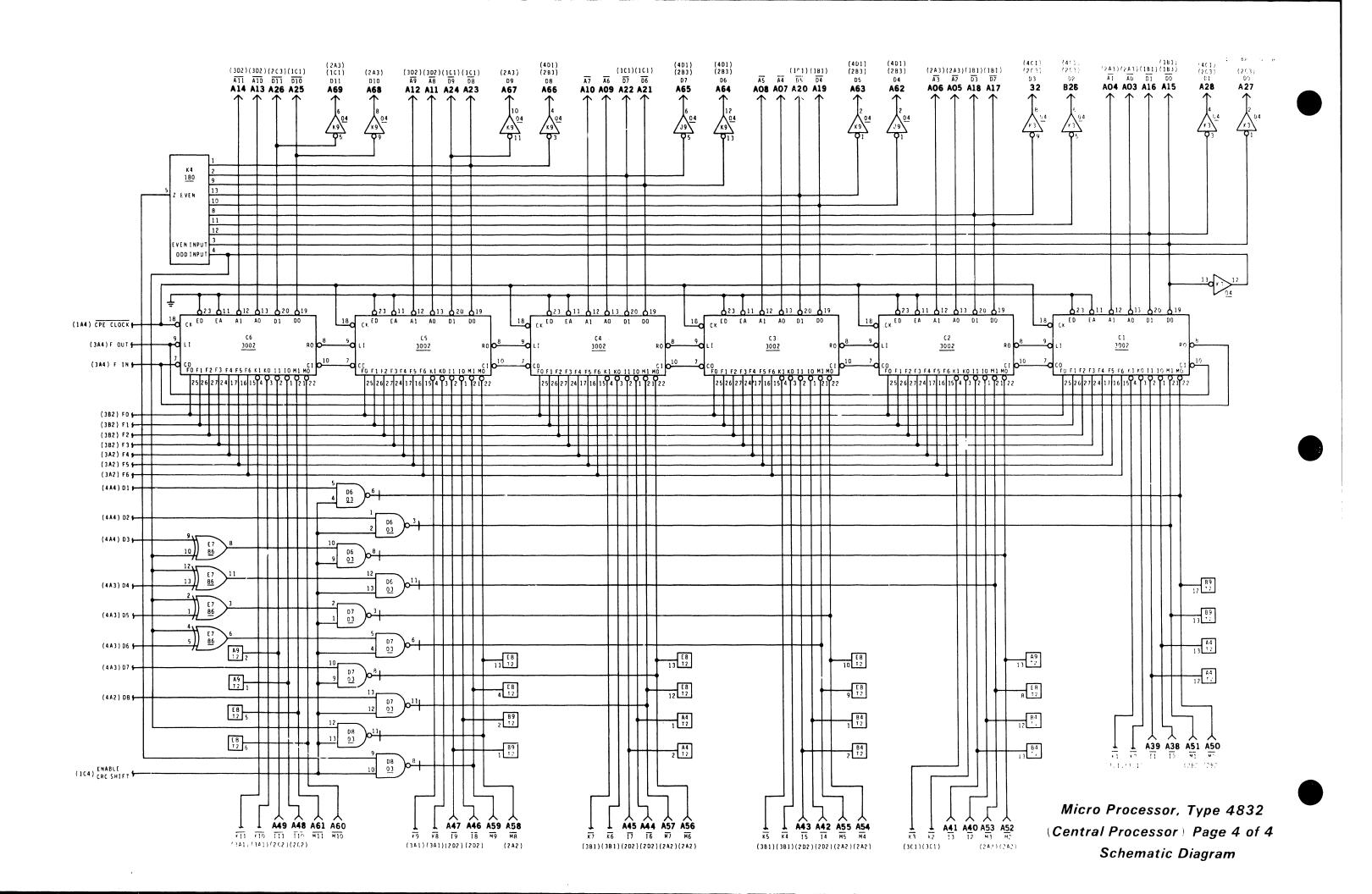

### 3.2.1 The 3002 Central Processing Elements

There are six of these devices per microprocessor board and all of their input control lines are parallel connected. The Central Processing Elements, or CPEs, are controlled by part of a 32 bit microinstruction word which is output from the programable read only memories during microinstruction cycle. (Refer to Figure 3.2.) Seven bits of this microinstruction word are output on bus lines F0-F6, the microfunction bus. The F bus controls tne six CPEs, but its commands can be altered by the 12 bit K, or masking, bus. This bus can modify the F bus commands by selecting or deselecting the Arithmetic Logic Units (ALUs) within the six CPEs. In fact, the K bus expands the number of functions which may be performed by this masking action.

The remaining 13 bits of the 32 bit microinstruction word are routed back to the 3001 Microprogram Control Unit (MCU). The function of these bits will be discussed under the paragraph entitled 3001 Microprogram Control Unit.

Each central processing element has two input busses, designated I and M, and two output busses, termed D and A. The I bus inputs tape transport commands from the computer and tape transport status information from the selected tape drive. The M bus inputs read or write data to the central processing elements. Since data and command signals are multiplexed on these I/O bus lines, an enabling command is output from the CM and CD busses to select the appropriate signals at a particular point in the formatter program. These commands will be discussed shortly.

Output bus lines A8 through A11 make up the Next Column Address Bus. These lines are connected through quad D flip-flop C9 to the PX4-PX7 inputs on the microprogram control unit (MCU). Data on these

Figure 3-1. Microprocessor Block Diagram

lines is tested by the MCU to determine the next column address it will output to the PROMs during a JPX (Jump Instruction) command, which will be explained later. Bus lines A0 through A3 are the tape transport select bus. However, since tape transport selection is normally performed by the controller, these lines are not used in the standard 9219 formatter configuration. Bus lines A4 through A7 are unused.

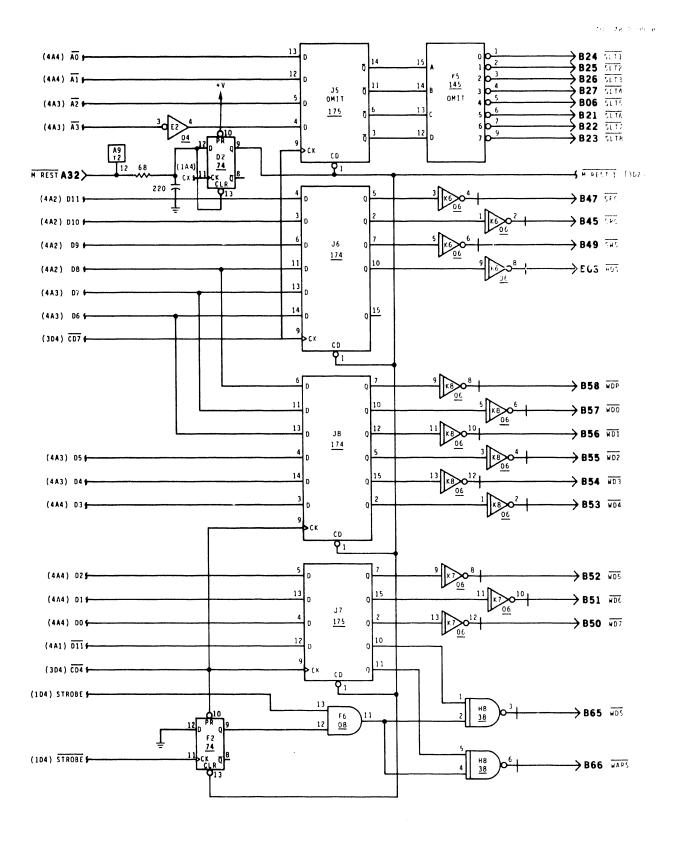

Bus lines D0 through D8 transfer read or write data to the interface. (Write data is clocked out of D latches J7-J8 on the microprocessor to the B bus of the masterboard; read data is transferred through the A bus of the masterboard to the 4831 Interface board.) Bus lines  $\overline{D0}$  through  $\overline{D8}$ , the complements of the D0 through D8 bus lines, load four bit binary counters F7, F8, F9, which determine the read or write data rate. D bus data is also checked for proper parity by Parity Tree IC K4 and exclusive-OR gates E7.

# 3.22 Command Bus CM16, CM17, CM18

As can be seen, read or write data and tape transport status and command signals are applied to common I/O busses at the CPEs. To organize and synchronize read and write data and the tape transport status and command signals, PROM pair 4 has been programed to output commands 0 through 7 in hex code on command lines CM 16, 17 and 18. Line CM 18 outputs the most significant bit; CM 16 outputs the least significant bit. Additionally, during most command times, a corresponding pulse (CD1-7) is given to enable the appropriate D latches AND/OR gates. Commands 0, 1 and 3 select and transfer data to and from the interface. Commands 2,4,5,6,7 and 8 control the operation of the microprocessor board. Table 3.2 illustrates the bits present on the significant bus lines during a given command time.

Command 0 (0 states on CM 16, 17 and 18) places any available write data on M bus lines 0-8. It also places the selected transport's speed, bit density, parity and the FBY line on the I input bus. This is the normal microprocessor situation until another command is issued.

Command 1 transfers read data out of the CPEs to the interface on D bus lines D0-D8. These lines are input to type D flip-flops B8/B9 on the 4831 Interface board, where they are clocked out on each succeeding read data strobe. Command 1 would necessarily be preceded by command 5, which inputs read data into the M bus of the CPEs for processing.

Command 2 places status information from the selected tape transport on the CPE's I input bus. Command 2 also enables ENABLE CRC SHIFT, which transfers the parity of the least significant nine bits contained in the CPE internal accumulators through the  $\overline{D}$  bus onto line 9 of the M input bus. This performs a partial VRC and CRC parity check, reducing the number of instructions required for

oarity checking later. Incidentally, IC K4 checks parity, while the exclusive-OR gates E7 generate the IBM-compatible CRC check character.

Command 3 enables NAND gates F3/H3/H4, applying one read data byte to the M input bus of the CPEs. These NAND gates are connected to the Q outputs of D latches H1/H2, which are clocked by a read data strobe pulse and cleared by a CD5 pulse issued during command 5 time. Thus, CD3 and CD5 must both be true before read data can be input to the central processing elements.

Command 4 parallel-loads write data channels WP through W7 onto CPE output lines D0-D8. It is passed through D latches J7/J8 and out to the tape transport. The WDS and WARS lines are also enabled to insure proper write data timing.

Command 5 transfers one byte of read data onto M input bus lines 0-8 of the CPEs after command 3 is issued. In PE formatters, command 5 also transfers PE read data status information onto I bus lines I0 through III. If a read data character is present during command 5 time, a carryout is generated from the CPE and applied to the F IN input to the 3001 Microprogram Control Unit. This generates CD5 true from PROM pair 4, clearing D latches H1/H2 and enabling the read data bus to respond to the next read clock. If no read characters are present FIN would be false and the D latches would not be cleared. The read bus is not cleared until command 5 occurs and a carryout exists in the microprocessor. However, read data still won't pass to the controller until command 1 has been issued.

Command 6 parallel loads a programable counter with the bit complement of the D bus. The clock defines the read or write data rate. (Refer to ICs H7, H9, F7, F8, F9 et al on the first page of the microprocessor schematic.) This assures even multiples of tape speeds and results in accurate alignment between tape speed and recording density. The cycle time of the programable counter is 6944x The number of (accumulator +1) microsecond. instructions executed per micro-instruction eyele time is defined by the cycle's microinstruction count. This is equal to two times the microinstruction +2. If a hexidecimal 008 were output from the accumulator bus, for example, and command 6 is issued, the number of instructions executed per cycle time would be 2x8+2, or 18. The maximum cycle instruction count is 8192 instructions per cycle time and the minimum eyele instruction count is 4. The 1.02 microsecond STROBE and STROBE pulses are also produced, which are used to develop the WDS and WARS strobe pulses.

In standard formatter configurations, command 7 clocks Hex D flip-flop J6, passing tape transport command(s) available on the A and D busses to the selected tape transport. Commands include: SFC, SRC, SWS, HDS, REW and OFFC. In special formatter configurations, such as buffered tape transports where tape drive selection should be made

### COMMAND 0. 1 (Interface Board Data to Microprocessor Board) I BUS\* 10 9 7 6 2 0 11 DENSITY... 0 BUSY -COMMAND SPEED HIGH COMMAND HEXIDECIMAL CODE 7 - ERASE VAR 6 - ERASE FIXED 5 - WFM 4 - WRITE EDIT 3 - WRITE 2 - BACKSPACE EDIT 1 - BACKSPACE 0 - READ \*When Interface Board is enabled When D11 = 1: (Read Data, Read Strobe, Hard Error to Controller) D BUS 11 10 9 7 6 5 3 2 0 R7 1 X HER RP RO Rı R2 R3 R4 **R**5 R6 When D11 = 0: (Formatter Status to Controller) D BUS <sup>-</sup> 7 10 9 8 6 3 2 0 11 1 x 0 $\mathbf{X}$ Х IDENT FBY DBY $\mathsf{FMK}$ HER CER Х Х COMMAND 2 I BUS 10 9 8 7 6 5 2 0 LDP FPT HDI 0 0 RDY RWD EOT ONL RNG 0 MTU STATUS M BUS (Before Enable) 10 9 7 5 3 11 2 0 1 D4900 D3000 ODD 0 CON PARIT' BIT D0 0 0 D8 D7D2 D1 M BUS (After Enabling) 11 10 9 6 5 3 LWD 0 P 0 0 5 7 2 COMMAND 3 D BUS 11 10 9 6 5 3 2 0 ENB нібн WRT CORR FWD $\mathbf{x}$ X Х X 0 0 READ

When D0 = 1: PE Read Card Enabled When D0 = 0: Interface Card Enabled

ENAB

TO PE CARD

Table 3-1A. Command Time Bus Assignments

ENABLES

INTERFACE

CARD

PE

CARD

# COMMAND 4 (Microprocessor Card) D BUS 11 10 5 WRITE 2 STRB 7 0 U WRITE TOGGLES 0 = WDS 1 • WARS \*(When Emibled) CM5 ON UP CARD (NRZI Mode) M BUS

CM5 ON PE CARD Microprocessor Board \*I BUS (PE Mode) 10 8 6 0 11 9 3 1 OR D3 SKEW BLOCK  $\Gamma M$ ERR

When D11 = 1:

# When D11 = 0:

\*WHEN ENABLED CD3 D0

# COMMAND 6

CD6 on Microprocessor Board Londs Contents of  $\overline{DD}$  -  $\overline{D0}$  into Programable Counter H7/H8/F7/F8/F9.

# COMMAND 7

Outputs Transport Commands to Selected Tape Transport

D BUS

11 10 9 8 7 6 5 4 3 2 1 0

SFC SRC WSW HPS RWC OFFC 0 0 0 0 0 0

Table 3-1B Command Time Bus Assignments

directly from the formatter, command 7 also enables one of eight transport select signals, SLT1 through SLT8. J5 and K5, the ICs from which these signals would be output, are omitted from standard microprocessor boards.

# 3.2.3 Time Out Cycle

The microprocessor's clock circuitry includes a programable divider which enables an interrupt. This interrupt permits the microprocessor to test for a time-out cycle while simultaneously executing the next instruction. If a time out is detected, the processor may be forced to branch, i.e., line ACO will be forced low, and the next location in the memory address register would be an even row or column. Thus the microprocessor can very quickly ascertain whether it should sample the write data registers to determine whether data should be transferred to the formatter, or perform other time-dependent functions.

# 3.2.4 The 3001 Microprogram Control Unit (MCU)

Through its MA address lines, the 3001 chip determines the microinstruction sequence output to central processing elements from programable read only memories. Eleven bits of the microinstruction word output by the PROMs are returned to the 3001 MCU for next address (ACO-AC6) and jump function (FC0-FC3) control. The MA bus lines provide a row and column address to the PROMs, which employ memory matrixes for storing the individual microinstruction word bits. MA0-3 specify the column address; MA4-8 specify the row address. Each PROM matrix can contain up to 32 row addresses and 16 column addresses for a total of 512 microinstruction addresses.

The next address logic in the 3001 MCU makes extensive use of this addressing scheme. For example, from a particular row or address it is possible to jump either unconditionally to any other location in a particular row or column, or conditionally to other specified locations in one operation. For a given address matrix location, there is a fixed subset of microprogram addresses that may be selected as the next address. These are referred to as a jump set and each type of microprogram control unit address control jump function has its associated jump set.

The MCU's jump function logic actually determines the sequence in which microinstruction words are accessed from the microprogram memory by controlling the next address logic within the 3001 MCU. The program memory address is held in the Microprogram Address Register (MAR).

The next address is also influenced by data on bus lines F0-F4. Through flag output line F0, the C and Z flags within the 3001 MCU latch and control the value of the carry and shift inputs to the central

processing elements. Under microprogram control the flag logic simultaneously forces the state of this flag output line to 1 or 0 or the value of the C and Z flags in the MCU.

# 3.2.5 The PROMs

Depending on whether it's a NRZI or NRZI/PE application, there are 8 or 16 socketconnected 3601 PROMs in the microprocessor. They are bipolar Shottky with a 50 nsec access time. Each PROM is 4 x 256, or 256 locations of 4 bits each, and each PROM is specifically programed for use in the Model 9219. The 256 bit locations require lines of addressing (MA bus lines 0-8). The PROMS are paired and parallelconnected. The outputs are common and the chips are wired to have common addresses which are alternately enabled or disabled so that only one chip of a pair operates at any given time. arrangement can provide up to 512, 32 bit programing words for use in the formatter. However, in applications requiring 256 or less program words, NRZI-only machines for example, one set of PROMs may be omitted. The PROMs output a 32 bit wide microinstruction word during one microinstruction cycle. Here is a breakdown of PROM functions:

# PROMS 0 AND 1 (ICs A7, A8, A10, A11)

Output the microinstruction bits which help define the next instruction to the output from the 3001 MCU. These are input on lines AC0-AC6 of the 3001 chip (A12). PROM 0 contains the least significant bits (A0-A3); PROM 1 contains the most significant bits (A4-A6). PROM 1 also outputs FC0-FC1, which control the flags influencing the MCU's next address logic. A true condition on this line results in a conditional branch in the program.

# PROM 2 (ICs A5, A6)

Contains the least significant bits of the CPE's microfunction bus. These bits are found on lines F0-F3.

# PROM 3 (IC's B7, B8)

Outputs the most significant microfunctions which are on lines F4-F6. PROM 3 also contains a flag control which sets an outgoing earry fed to the 3001 microprocessor. This is F IN, which is transmitted on A12, line 17. FC 3 (A12, pins 12 and 13) controls the holding of an internal storage state in the 3001 chip.

# PROM 4 (ICs A2, A3)

Outputs the command bus (CM16, 17 and 18). It also contains CM19 which controls the timing interrupt bit. When true, the interrupt count will be tested to determine whether a timeout has occurred. If it has, AC0 will be forced to 0, causing an unconditional program branch.

PROM 5 (ICs, B10, B11)

Outputs the most significant four bits of the K (masking) bus.

PROM 6 (ICs B5, B6)

Outputs the middle four bits of the K bus.

PROM 7 (ICs B2, B3)

Outputs the least significant four bits of the K bus.

# 3.3 THE INTERFACE BOARD

All signal flow between the computer, the tape transports and the microprocessor board is processed through this card. The two pages of the interface card schematic can be divided into several functional blocks -- Tape Speed/Density Select Switch, Tape Transport Status Gates, Read Data Logic, Address Select Gates, Write Data Gates, and Command Logic, etc.

# 3.3.1 Tape Speed/Density Select Switches

Tape speed and density as well as certain options are controlled by means of E1 through E4 on the interface board. Tape unit 0 is controlled by E4; tape unit 1 is controlled by E3, etc.

The options are selectable by switches S1 on E1 through E4. Switches S1 on ICs E1 and E2 determine whether formatter 0 or 1 is addressed. The positions of E3-1 and E4-1 determine whether internal or external parity is written on tape. Switches S2 through S7 on E1 through E4 supply tape unit commands and status signals to and from the individual tape units. Switch positions of S2 through S7 are directed to the the microprocessor on corresponding I bus lines I2 through I7. Switch S2 on E1 through E4 is turned ON to select a 7 track tape unit; OFF to select a 9 track tape unit.

Switch S3 selects between 556/800 cpi and 200/556 cpi tape densities for 7 track tape units.

Switch S4 is reserved for PE applications and selects between a preset high or low tape speed. Since the PE board can only operate at two speeds, the formatter must be set up so that only two tape speeds are selectable at 1600 cpi. NRZ1 units have no such limitations.

Switches 5 through 7 can be set to various binary combinations for tape speed selection. Tape speeds possible are: 10 ips, 12.5 ips, 15 ips, 18.75 ips, 25 ips, 37.5 ips, 45 ips and 75 ips.

# 3.3.2 Tape Transport Status Gates

Tape transport status signals are input to the interface board on the B bus of the motherboard; then gated with FORMATTER ADDRESS and directed to the controller at interface board jack J1. Formatter Address 1 (FAD 1) must be selected (i.e., E2-1 ON/E1-1 OFF) to enable the NAND gates controlling the tape transport status signals. These signals are: High Density Indicator, File Protect, End of Tape, Load Point, Rewind, On Line and Ready.

# 3.3.3 Read Data Logic

Read data channels P through 7 are assigned to the D output bus of the microprocessor and directed to D latches B8 and B9 on the interface board. They are clocked out to the computer during command 1 (CD1) time when pulses from D11 fire one shot C7. (This one shot also provides the necessary timing delay for the read strobe (RSTR) which is output at J1-31.)

The read data of the D bus is also directed to D latch B5, which outputs any available CER and HER read error signals, as well as IDENT/CCG during command 1 time.

CHECK CHARACTER GATE is set true by a NRZI formatter when the read information contains a CRCC or LRCC check character. The HARD ERROR true signal can either be a pulse or a level. NAND gate B7 will pass a HER true pulse during the read strobe when there is a vertical parity error.

DATA BUSY false will clear D latches B9 and B8 to stop read data transmission when tape speed starts to decelerate. Similarly, INITIALIZE true clears D latch B5.

# 3.3.4 Address Select

The states of controller signals TAD0 and TAD1 determine which transport is selected. The selected tape deck is addressed through the B bus of the formatter motherboard (B24 through B27). Here is a list of the TAD0-TAD1 combinations with their corresponding addresses:

| TAD0 | TAD1 | ADDRESS |

|------|------|---------|

| 0    | 0    | SLT0    |

| 0    | 1    | SLT1    |

| 1    | 1    | SLT2    |

| 1    | 1    | SLT3    |

| (MSB)<br>J1-1 | J1-2<br>BUSY | J1-3<br>REVL | J1-4<br>WRTL | J1-7<br>WFML | J1-6<br>EDITL | (LSB)<br>J1-5<br>ERASEL | Defined<br>Output | Default<br>Output | Output<br>Code |

|---------------|--------------|--------------|--------------|--------------|---------------|-------------------------|-------------------|-------------------|----------------|

| 1             | 1            | 0            | 0            | 0            | 0             | 0                       | RF                |                   | 7              |

| 1             | 1            | 0            | 0            | 0            | 0             | 1                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | 0            | 1             | 0                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | 0            | 1             | 1                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | - 1          | 0             | 0                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | 1            | 0             | 1                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | 1            | 1             | 0                       |                   | RF                | 7              |

| 1             | 1            | 0            | 0            | 1            | 1             | 1                       |                   | RF                | 7              |

| 1             | 1            | 0            | 1            | 0            | 0             | 0                       | WRT               |                   | 4              |

| 1             | 1            | 0            | 1            | 0            | 0             | . 1                     | ERV               |                   | 0              |

| 1             | 1            | 0            | 1            | 0            | 1             | 0                       | WRTE              |                   | 3              |

| 1             | 1            | 0            | 1            | 0            | 1             | 1                       |                   | ERV               | 0              |

| 1             | 1            | 0            | 1            | 1            | 0             | Ú                       | WFM               |                   | 2              |

| 1             | 1            | 0            | 1            | 1            | 1             | 1                       | ERF               |                   | 1              |

| 1             | 1            | 0            | 1            | 1            | 1             | 0                       |                   | WFM               | 2              |

| 1             | 1            | 0            | 1            | 1            | 1             | 1                       |                   | ERF               | 1              |

| 1             | 1            | 1            | 0            | 0            | 0             | 0                       | RR                |                   | 6              |

| 1             | 1            | 1            | O            | 0            | 0             | 1                       |                   | RR                | 6              |

| 1             | 1            | 1            | 0            | 0            | ' 1           | 0                       | RRE               |                   | 5              |

| 1             | 1            | 1            | 0            | 0            | 1             | 1                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 0            | 1            | 0             | 0                       |                   | RR                | ` 6            |

| 1             | 1            | i            | 0            | 1            | 0             | 1                       |                   | RR                | 6              |

| 1             | 1            | 1            | 0            | 1            | 1             | 0                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 0            | 1            | 1             | 1                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 1            | 0            | J             | 0                       |                   | RR                | 6              |

| 1             | 1            | 1            | 1            | 0            | 0             | 1                       |                   | RR                | 6              |

| 1             | 1            | 1            | 1            | 0            | 1             | 0                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 1            | 0            | 1             | 1                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 1            | 1            | 0             | 0                       |                   | RR                | 6              |

| 1             | 1            | 1            | 1            | 1            | 0             | 1                       |                   | RR                | 6              |

| 1             | 1            | 1            | 1            | 1            | 1             | 1                       |                   | RRE               | 5              |

| 1             | 1            | 1            | 1            | 1            | 1             | 1                       |                   | RRE               | 5              |

MSB = Most Significant Bit

LSB = Least Significant Bit

Table 3-2. Input/Output Combinations, Command PROM J1, Interface Board

### 3.3.5 Write Data Gates

Write data from the computer is inverted; then applied to quad D flip-flops C3 and C4. The write data is clocked out of the flip-flops on the leading edge of each succeeding write strobe. Data Busy must be false and WRITE GATE must be true to enable write data transmission. (DATA BUSY goes true when read data is output from the D bus of the microprocessor. WRITE GATE goes false when strobe pulses no longer clock J-K flip-flop H4.

# 3.3.6 Command Logic

Computer commands are input at J2-17 of the interface board and gated with load point, file protect and initiate comand signals. LP true, and FPT true will disable the command line AND gates when write or reverse commands are issued. GO false disables the command gates under any condition.

Any available computer command sets its respective J-K flip-flop and is clocked out to J1, a programable read only memory, on the trailing edge of the next GO pulse from the computer.

The command inputs to the PROM are read as two hexidecimal codes which are used to access an output code from the PROM memory. This binary code is output to I bus lines 8, 9, 10, and 0 of the microprocessor. (Table 3-2 lists the various output

actions developed as a result of various computer command combinations. Some of these combinations are illegal and will cause the PROM to access the RUN FORWARD code. The microprocessor samples and tests the output of PROM J1 to determine its own operational sequence.

# 3.4 PHASE ENCODED READ

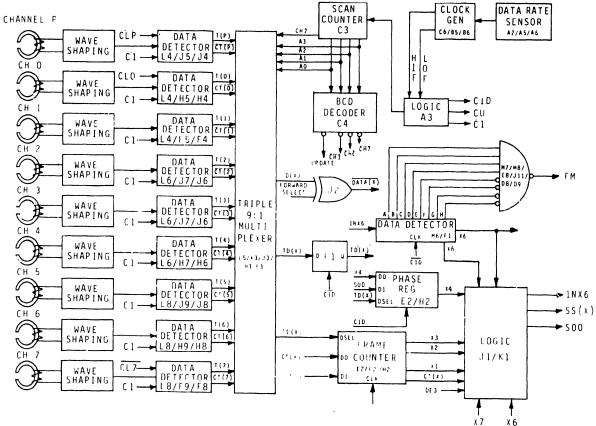

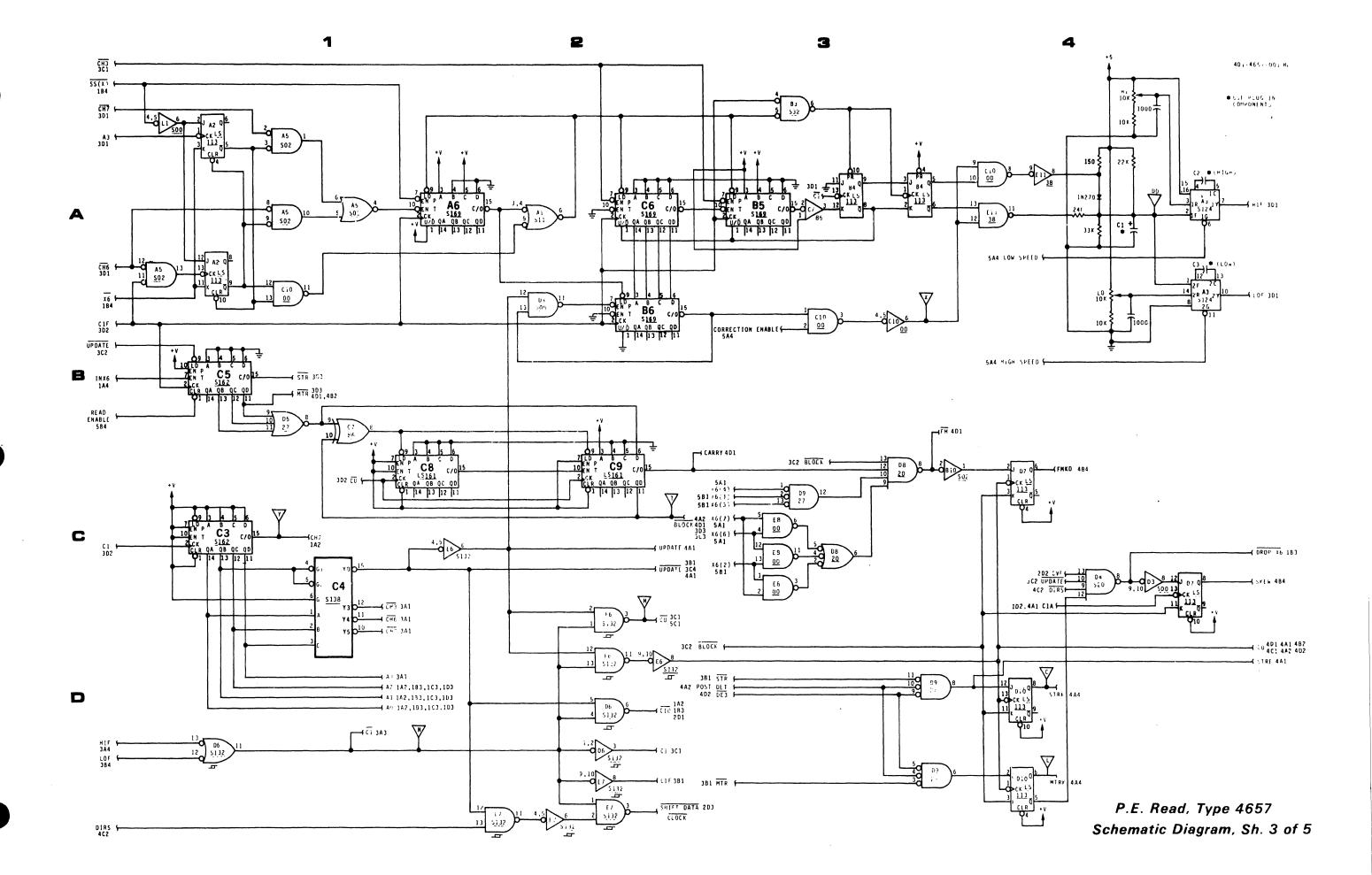

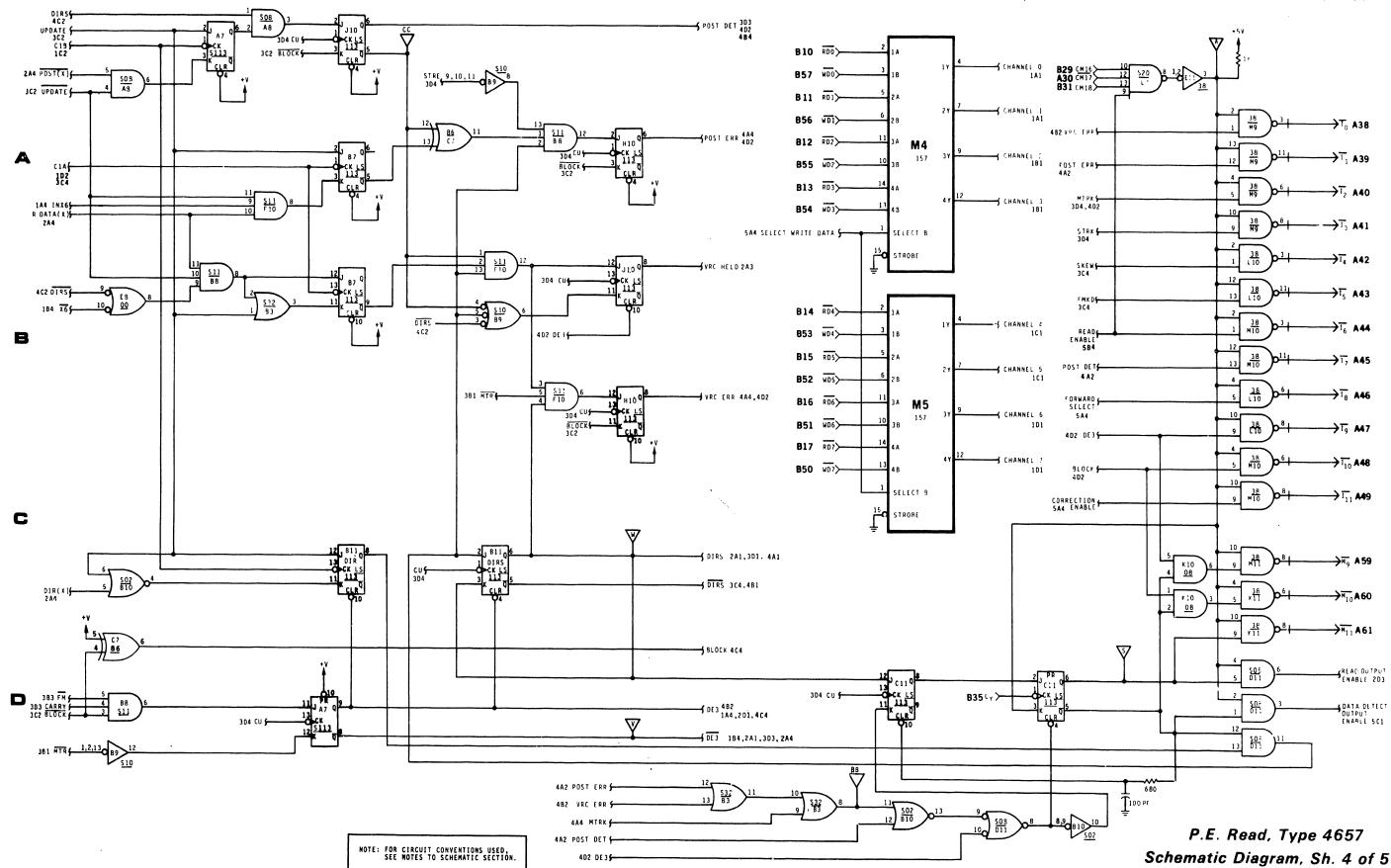

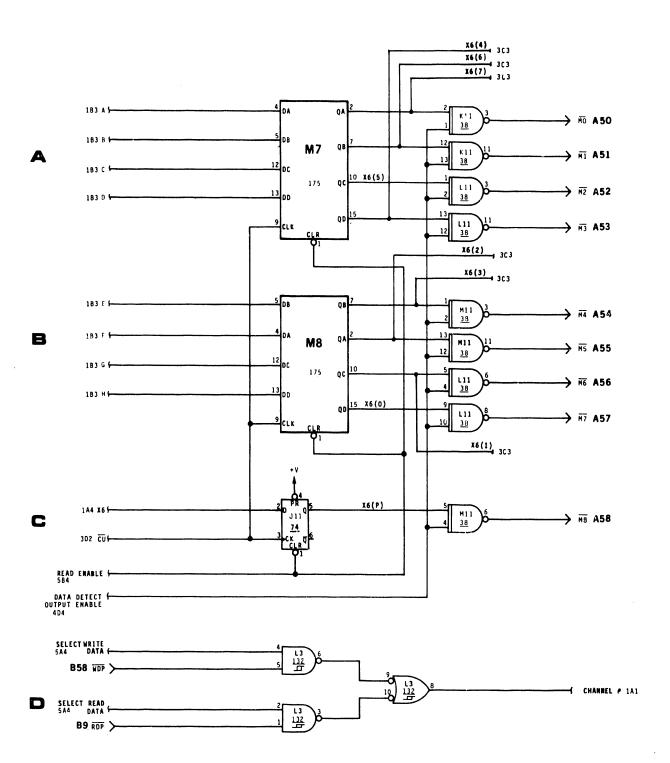

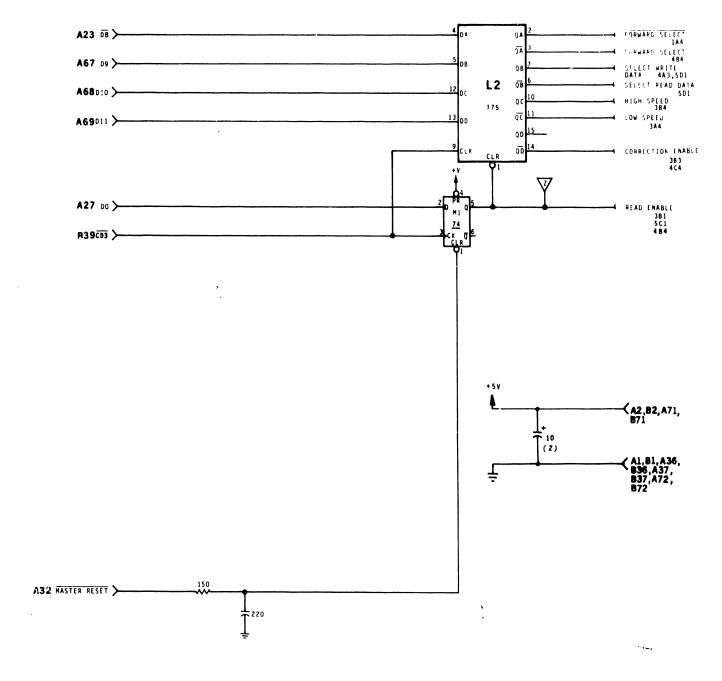

# 3.4.1 INTRODUCTION (See Figure 3-2)

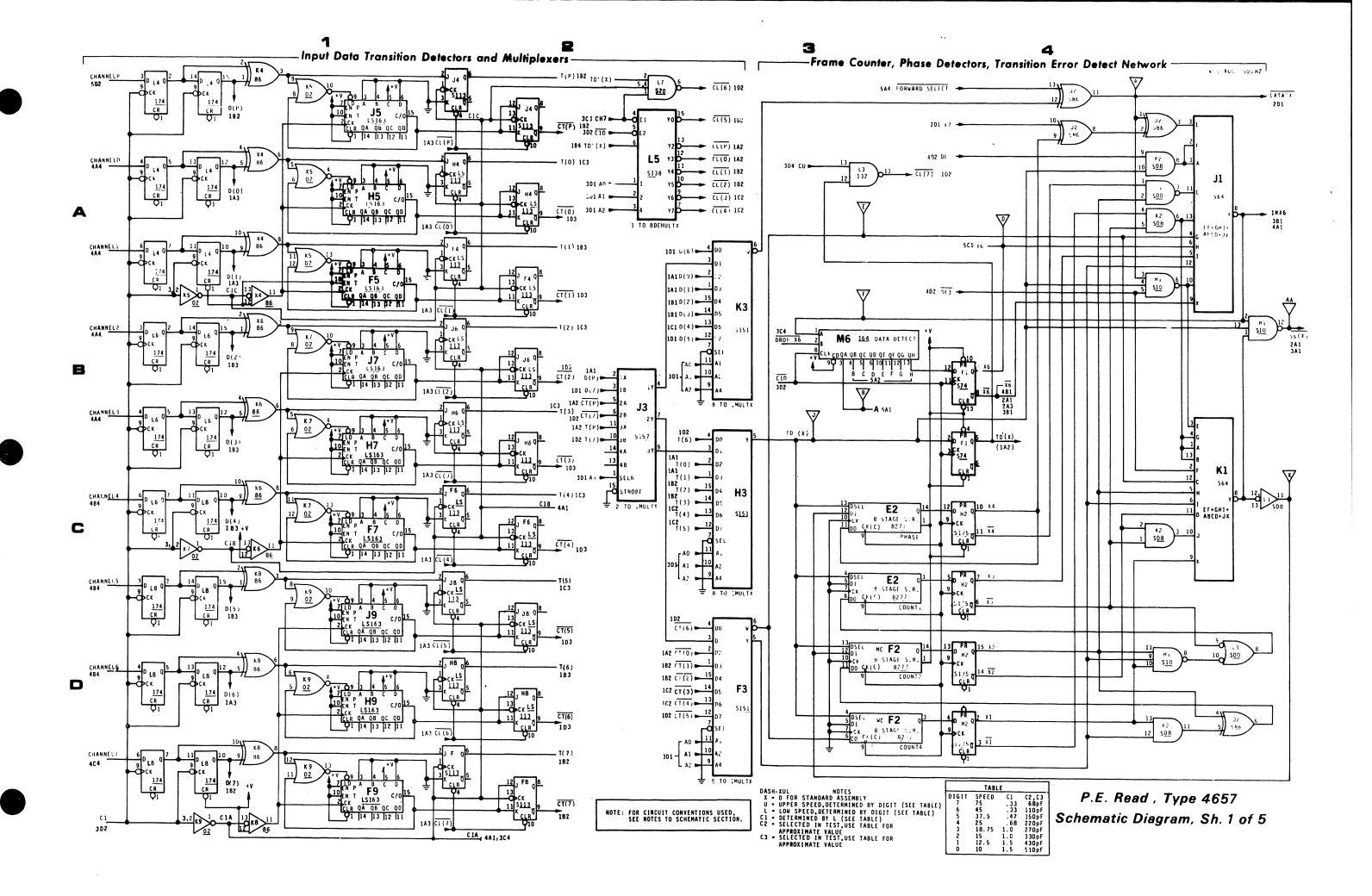

The phase encoded read electronics perform the following functions: detect input data transitions from the transport, decode and deskew read data, generate the read clock, detect any formatting or parity errors, correct single track errors, and detect file marks.

While the detection of input data transitions is performed separately for each channel, the data is multiplexed after the initial detection stages and the functions listed above are performed by a single set of electronics for all nine channels. This is accomplished by scanning the nine channels sequentially, processing one channel at a time. The status of the control circuits is updated (UPDATE true) after each nine-channel scanning. When all functions have been performed the decoded data is demultiplexed by the deskew circuitry and supplied to the M bus of the microprocessor and ultimately to the interface.

110-0143

Figure 3-2. Block Diagram, Type 4657 PE Read Board

The various functions performed by the phase encoded read electronics are described in the following paragraphs. The description is divided into several parts, including the timing circuits, data transition detection, data decoding and deskewing, read clock generation, and read data detection.

# 3.4.2 TRACK ERRORS

The following conditions would cause a track error:

- Crowded transitions, defined as more than one transition occurring within 25 percent of a character frame. One case is the detection of a transition within 25 percent of the character frame since the previous data transition. Alternately a crowded condition is recognized when an interphasetransition (defined as the midpoint of the character frame) is followed by a transition occurring before the 75 percent point of the frame.

- 2. Missing transitions, a condition defined as the absence of a transition within 125 percent of a character frame since the last data transition.

- Inverted transition polarity. This error check samples the polarity of the present input data character, that of the previous data character and the state of the data transition detector.

The parity of these signals should always be odd: otherwise an error is detected. For example, if the present input character is a 1 and the preceding character is also a 1, the interphase detector output should be indicating that the interphase true, transition was detected between the successive 1's. Similarly, if the input character is a 0 and the previous character was a 1, the output of the interphasetransition detector should be false, since no interphase transition should occur between a 1 and a 0. This error check detects spurious transitions caused by noise.

When any of the above conditions is detected, the DATA signal of the respective track is disabled for the remainder of the block, as is the SHIFT SERIAL Ss(X) signal, which shifts the input character into the deskew shift register. If the error occurs on one track only, it is correctable. However, if an error is detected on more than one track, a MULTIPLE TRACK ERROR (MTR) is indicated, inhibiting the DATA ENABLE (DE3) signal, which in turn inhibits the output data lines.

# 3.4.3 READ DETECTION CIRCUITRY 'See Schematic 401-4657-001, Page 3).

Read detection circuitry includes a BCD counter (C5), an eight bit binary counter C8/C9, JK flip-flops

D7, D10 and several logic gates. This circuitry detects proper read circuit operation as a block of information is being read. Whenever READ ENABLE signal goes true to indicate that data reported in a phase encoded format is to be read, the clear on the BCD counter is disabled to permit it to operate during a sampling cycle to count the number of channels on which error-free data has been detected. The signal INX6 indicates whether or not error free data has been detected on a sampling channel. If error free data has been detected on all channels, the BCD counter will count to nine by UPDATE time and the complement of the single track error signal, STR, will go high as the C/O output of the BCD counter goes true on the ninth count. If error-free data is detected on only eight channels as indicated by signal INX6, the BCD counter will only count to eight at the end of a sampling cycle and a logic one single track error signal, STR false, will be generated as the complement of the C/O output of the BCD counter. Output QD will be a logic 1 to indicate a count of 8 and the multiple track error signal, MTR, which is generated as the complement of output QD, will be at logic 0.

In the event that data detected signal INX6 falls on two or more channels, the count will be less than eight at UPDATE time and both multiple track error signal MTR and the single track error signal STR will be generated.

# 3.4.4 INPUT DATA TRANSITION DETECTORS AND MULTIPLEX (See Schematic 401-4657-001, Page 1).

The data lines are input from the B bus of the masterboard; then applied to data input registers M4/M5. Because the data detectors are synchronous systems which operate in response to the master clock pulse signal C1, they are in effect high speed sample data systems which sample the read head data signals (TD X) 48 times during each nominal data frame interval.

The data detectors are sampled at a rate of 256 kHz, which would normally permit a resolution of elapsed time between transitions of no more than 3.9 microseconds, or 1/6.4 of a data frame interval. However, digital timing information provided by the data detector each time it is sampled permits information transitions of a much higher resolution.

Each data detector includes a pair of D input flip-flops, (L4), an exclusive OR gate (K4) an OR gate (K5), a four bit binary counter (J5) and a pair of J-K flips-flops (J4) To understand the operation of the data detector, assume the read data parity (RDP) channel is initially low and has been low for at least 1/4 of a data frame interval period. Flip-flops L4 and the first J4 flip-flop are at a logical zero state; the second J4 flip-flop is at the logical 1 state and counter J5 is counting. Should RDP signal go high, the next low to high transition of clock signal C1 which is generated by the data rate sensor circuitry, sets the first L4 flip-flop. At the following transition

of C1, the second L4 flip-flop is set. During the interval between the setting of flip-flops L4, exclusive OR gate K4 generates an output pulse, setting the second J4 flip-flop. The output pulse from the exclusive OR gate also resets counter J5. The earry output signal from the counter indicates the end of a data frame interval quarter. This earry output pulse toggles the second J4 flip-flop, causing it to output CT(P) true signal. CT(P) signal is then directed to multiplexer J3, where it indicates whether an even or odd number of quarter data frame intervals have elapsed after the latest information transition.

Three 8 input multiplexers receive the three outputs from each data detector. The multiplexers output D(X), TD(X) and CT(X) signals in accordance with the addressing performed by binary coded decimal counter C3. (Lines A0-A3). This same address output is used to address 1 to 8 demultiplexer L5 which is capable of clearing any of the detector J-K flip-flops handling CT signal. C1D true enables the demultiplexer, which will clear the controlling the data channel currently being C1D signal indicates a channel processed. multiplexing sampling interval as opposed to an update multiplexing sampling interval. A TD(X) signal, which indicates the presence or absence of an information transition during the preceding multiplex sampling interval, is also required to enable the multiplexer. When enabled, a clear signal for a given channel is generated during the multiplex sampling interval immediately after the multiplex sampling interval for that channel.

This delay of one clock pulse period insures that the J4 flip-flops are reset as soon as possible to prevent the loss of Information without interfering with the sampling of information during a channel sampling interval. However, counter J5 is reset directly in response to a data transition. Flip-flop J4 is then resynchronized with counter J5 as soon as information is taken.

During a multiplex sampling interval, three separate information signals are sampled. A data signal, D (P), generated by the Q output of the second L4 flip-flop, indicates the current data information state and the T (P) signal, generated by the Q output of the second J4 flip-flop, permits transitions in this flip-flop to be counted for determining quarter data frame interval periods. For multiplexing purposes, master clock signals C1 are divided into ten sequential multiplexing intervals. The time multiplex sampling of the outputs from the data detectors thus occurs at an average of 4.8 sample intervals per data frame interval at 125 ips. Because of counter J5 and the second J4 flip-flop, the relatively slow multiplexing rate is sufficient to insure that information cannot be lost from the data detector.

# 3.4.5 DATA DETECT CIRCUITRY (See Schematic 401-4657-001, Page 1).

M6, the nine bit data detect shift register, is clocked by the clock input data signal,  $\overline{\text{C1D}}$ , to keep track of

whether error-free data has been detected on a given channel. X6 true from type D flip-flop F1 indicates error free data has been detected on a channel corresponding to a current multiplex sampling interval as designated by BCD counter C5. Once an error is detected on a given channel, that channel is disabled by a logical zero in the M6 data detector's storage location for that channel until a block of data has been read successfully. Lines A-H are output to the microprocessor's M bus.

The X6 term in the 1NX6 function permits a logic 1 state to be continued for a channel position once data has been detected unless one of the error conditions is indicated. The TD(X) term indicates that an information transition has been detected by a data detector for a given channel and the data (X) term requires that the information transition be of the logical 0 polarity. X6 and TD(X) permit synchronization of the channel and generation of a logic 1 input to data detector register M6 while a string of zeros is being read from the preamble of a block of information (or postamble when reading backwards).

# 3.4.6 DATA FRAME COUNTER (See Schematic 401-4657-001, Page 1).

The function of the Data Frame Counter is to correlate the asynchronous input data transitions and the synchronous functions of the Format Control Unit. The counter identifies the time of each detected transition with respect to the standard character frame. The timing of the transition is used to distinguish between data transitions and phase-reversal transitions occurring between successive identical characters, and is also used to detect bit crowding or missing bits.

The frame counter (E2, F2 and H2) is a three bit counter with the three bit positions for a given channel arranged vertically in three separate nine bit shift registers. (On the schematic, each shift register is made up on one eight bit shift register with its corrresponding type D flip-flop, which adds the ninth bit. During the course of a multiplex sampling cycle, the three bits which correspond to each channel are shifted from left to right by one bit position for each multiplex sampling interval so that the output signals correspond to a current sampling interval. Within the frame counter, the lowermost nine bit shift register F2 stores the second least significant bit and uppermost nine bit shift register E2 stores the most significant bit. Each of these registers responds to one of two inputs in accordance with an address The transition detected signal, TD(X), is connected to drive the address input so that the D0 inputs are addressed when a transition is not detected and the D1 inputs are addressed during a sampling interval immediately following the detection of an information transition by data detector M6. The D1 inputs of registers F2 are connected to ground while the D1 input of register F2 is connected to the signal SOD. In this way the phase counter for a given channel is preset to count 0 upon detection of a data

information transition and preset to count 010 upon detection of a phase transition. The frame counter is thus resynchronized with the actual occurence of information transitions upon detection of each information transition. The D0 input to the least significant bit register F2 input is responsive to the multiplex signal CT(X). The D0 inputs of registers F2 have their inputs, 1NX2 and 1NX3 connected to respond to conventional counting circuitry to permit the frame counter to be incremented each time signal CT(X) changes states. The outputs from the frame counter are designated X1, X2, and X3 respectively, and indicate the binary count of the number of at least partially elapsed quarter data frame intervals subsequent to a preceding data information transition for a given channel sampling period during its' multiplex sampling interval.

Logic J1, which generates the 1NX6 data detected signal, also generates the phase transition signal to indicate a phase transition. Logic circuitry J1 also generates shift serially signal SS(X) which serves as a clock signal for deskew circuitry. This signal is generated each time an information transition is detected on a currently sampled channel and the transition is not a phase information transition and no errors are detected.

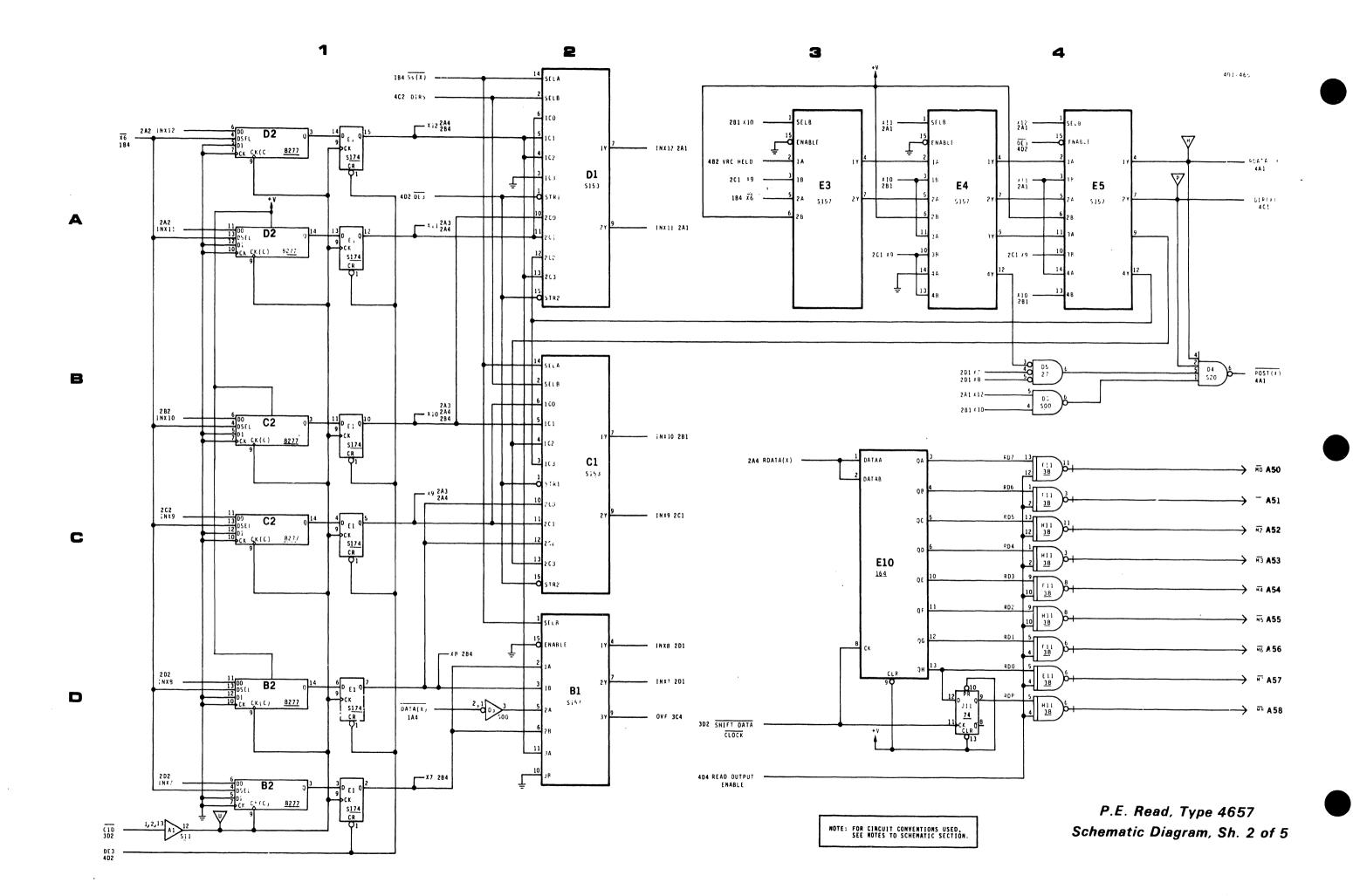

# 3.4.7 DATA DESKEWING CIRCUITRY (See Schematic 401-4657-001, Page 2)

The deskewing circuitry corrects skew variations between the nine input data channels. A maximum of three-character skew can be corrected. In addition, the deskewing circuitry is used to detect the preamble and the postamble, supplying only the valid data to the output with a read clock.

The deskew circuitry consists of six shift registers (B2, C2, D2), and six multiplexers (B1, C1, D1, E3, E4 and E5). Each of the shift registers comprises a stage of the deskew register. The multiplexed input data is shifted into the deskew register by  $\overline{\text{C1D}}$ , whenever a data transition is detected, provided that it is not an interphase transition and that no track error is detected.  $\overline{\text{C1D}}$  shifts the data along the deskew register, supplying the present input character into the first stage, 1NX7, while the contents of the register are shifted one stage up. Until the first 1 bit of the preamble is input into the deskew register the 40 0's of the preamble are ignored by the output.