# PROGRAMMING THE LINC

SECOND EDITION

Computer Systems Laboratory Washington University St. Louis, Missouri

# PROGRAMMING THE LINC Second Edition

## Mary Allen Wilkes and Wesley A. Clark

Computer Systems Laboratory Washington University 724 South Euclid Avenue St. Louis, Missouri 63110

This work was supported by the Division of Research Facilities and Resources of the National Institutes of Health under grant FR-218-01-03, and, in cooperation with the Bio-Sciences Office of the National Aeronautics and Space Administration, under NIH contract PH43-63-540. "Programming the LINC" originally appeared as Section 2 of <u>LINC Volume 16</u>, Programming and Use I, Computer Research Laboratory, Washington University, St. Louis, Missouri, June 1965. First edition: June 1965 Reissue: August 1967 Second edition: January 1969

# Copyright 1969 Washington University

For whom the gong perhaps chimes

# PROGRAMMING THE LINC

## Contents

| 1.  | Introductionl                                                                                                                                                    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.  | Number Systems                                                                                                                                                   |

| 3.  | Simple Instructions                                                                                                                                              |

| 4.  | Shifting                                                                                                                                                         |

| 5,  | LINC Memory and Memory Reference Instructions                                                                                                                    |

| 6.  | The Instruction Location Register 12<br>The JUMP Instruction 14                                                                                                  |

| 7.  | Address Modification and Program "Loops"                                                                                                                         |

| 8.  | Index Class Instructions I                                                                                                                                       |

| 9.  | Special Index Register Instructions29The INDEX AND SKIP Instruction29The SET Instruction31                                                                       |

| 10. | Index Class Instructions II34Double Register Forms34Multiple Length Arithmetic39Multiplication45                                                                 |

| 11. | Half-Word Class Instructions 50                                                                                                                                  |

| 12. | The KEYBOARD Instruction                                                                                                                                         |

| 13. | The LINC Scopes and the Display Instructions                                                                                                                     |

| 14. | Analog Input and the SAMPLE Instruction                                                                                                                          |

| 15. | The Skip Class Instructions 72                                                                                                                                   |

| 16. | The Data Terminal Module and the OPERATE Instruction                                                                                                             |

| 17. | Subroutine Techniques                                                                                                                                            |

| 18. | Magnetic Tape Instructions80Block Transfers and Checking82Group Transfers92Tape Motion and the MOVE TOWARD BLOCK Instruction94Tape Format98Tape Motion Timing101 |

,

#### Contents

# Index of Programming Examples

| 1.  | Simple Sequence of Instructions                        | 13   |

|-----|--------------------------------------------------------|------|

| 2.  | Simple Sequence Using the JUMP Instruction             | 15   |

| 3.  | Summing a Set of Numbers Using Address Modification    | 18   |

| Ц.  | Packing a Set of Numbers                               | 20   |

| 5.  | Indirect Addressing                                    | 23   |

| 6.  | Indexing to Clear a Set of Registers                   | 25   |

| 7.  | Memory Scanning                                        | 26   |

| 8.  | Summing Sets of Numbers Term by Term                   | 27   |

| 9.  | Index Registers Used as Counters                       | 30   |

| 10. | Indexing and Counting to Clear a Set of Registers      | 30   |

| 11. | Setting Initial Index Register Values                  | .3:3 |

| 12. | Scanning for Values Exceeding a Threshold              | 37   |

| 13. | Summing Sets of Double Length Numbers Term by Term     | 44   |

| 14, | Multiplying a Set of Fractions by a Constant           | 48   |

| 15. | Multiplication Retaining 22-bit Products               | 49   |

| 16. | Filling Half-Word Table from the Keyboard              | 55   |

| 17. | Selective Filling of Half-Word Table from the Keyboard | 56   |

| 18. | Horizontal Line Scope Display                          | 58   |

| 19. | Curve Display of a Table of Numbers                    | 59   |

| 20. | Character Display of the Letter A                      | 62   |

| 21. | Character Display of the Letter A Using DSC            | 64   |

| 22. | Displaying a Row of Characters                         | 65   |

| 23. | Simple Sample and Display                              | 68   |

| 24. | Moving Window Display Under Knob Control               | 69   |

| 25. | Histogram Display of Sampled Data                      | 71   |

| 26. | Counting Samples Exceeding a Threshold                 | 74   |

| 27. | Simple Sample and Display with Keyboard Control        | 75   |

| 28. | Simple Check of an Entire Tape                         | 88   |

| 29. | Dividing Large Programs Between Tape and Memory        | 90   |

| 30. | Collecting Data and Storing on Tape                    | 91   |

| 31. | Tape and Memory Exchange with Group Transfer           | 94   |

| 32. | Block Search Subroutine                                | 100  |

| 33• | Write and Check with Fewest Reversals                  | 103  |

| 34. | Indexing Across Memory Boundaries Appendix I:          | 3    |

# Page Index of LINC Instructions

| ADA                  | •••••                                    | 21,   | I <b>I-</b> 5  |

|----------------------|------------------------------------------|-------|----------------|

| ADD                  | •••••                                    | 11,   | II <b>-</b> 3  |

| ADM                  | •••••                                    | 26,   | II <b>-</b> 6  |

| APO                  |                                          | 73,   | II-4           |

| ATR                  |                                          | 6,    | II-l           |

| AZE                  |                                          | 17,   | II <b>-</b> 4  |

| BCL                  |                                          | 26,   | II-7           |

| BCO                  | •••••                                    | 28,   | II <b>-</b> 7  |

| BSE                  |                                          | 28,   | II-7           |

| CHK                  |                                          | 87,   | II-15          |

| CLR                  | • • • • • • • • • • • • • • • •          | 5,    | II-l           |

| COM                  | ·<br>• • • • • • • • • • • • • • • • • • | 6,    | II-l           |

| DIS                  |                                          | 57,   | II-11          |

| DSC                  |                                          | 63,   | II-8           |

| ENI                  |                                          | • • • | III <b>-</b> 5 |

| $\operatorname{HLT}$ |                                          | 13,   | II-l           |

| IBZ                  |                                          | 98,   | II-4           |

| JMP                  | •••••                                    | 14,   | I <b>I-</b> 3  |

| KBD                  |                                          | 54,   | II <b>-</b> 12 |

| KST                  |                                          | 74,   | II-4           |

| LAM                  |                                          | 39,   | II-6           |

| LDA                  |                                          | 23,   | II <b>-</b> 5  |

| LDH                  | •••••                                    | 50,   | <b>II-</b> 9   |

| LŞW                  |                                          | •••   | I <b>I-</b> 12 |

| LZE                  |                                          | 73,   | II-4           |

| MSC                  | 13                                       |       | II-l           |

| MTB                  | •••••                                    | 96,   | II <b>-</b> 14 |

| MUL                  |                                          | 45,   | <b>II-</b> 6   |

| NOP                  |                                          | • • • | II-l           |

7

| OPR                                                                |                                                                                                     | II <b>-</b> 12                                                                  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| OVF                                                                |                                                                                                     | III <b>-</b> 5                                                                  |

| PIN                                                                |                                                                                                     | III <b>-</b> 5                                                                  |

| RCG                                                                |                                                                                                     | II-14                                                                           |

| RDC                                                                | 86,                                                                                                 | II <b>-</b> 13                                                                  |

| RDE                                                                |                                                                                                     | II <b>-</b> 14                                                                  |

| ROL                                                                |                                                                                                     | II <b>-</b> 2                                                                   |

| ROR                                                                | 8,                                                                                                  | II <b>-</b> 2                                                                   |

| RSW                                                                |                                                                                                     | <b>II-</b> 12                                                                   |

| RTA                                                                |                                                                                                     | II-l                                                                            |

| SAE                                                                | 25,                                                                                                 | II-7                                                                            |

| SAM                                                                | 66,                                                                                                 | II-10                                                                           |

| SCR                                                                | 8,                                                                                                  | <b>II-</b> 2                                                                    |

| SET                                                                |                                                                                                     | II-10                                                                           |

|                                                                    |                                                                                                     |                                                                                 |

| SHD                                                                |                                                                                                     | <b>II-</b> 9                                                                    |

| SHD<br>SKP                                                         |                                                                                                     | -                                                                               |

|                                                                    |                                                                                                     | II-4                                                                            |

| SKP                                                                |                                                                                                     | II-4<br>II-4                                                                    |

| SKP<br>SNS                                                         |                                                                                                     | II-4<br>II-4<br>II-7                                                            |

| SKP<br>SNS<br>SRO                                                  |                                                                                                     | II-4<br>II-4<br>II-7<br>II-5                                                    |

| SKP<br>SNS<br>SRO<br>STA                                           |                                                                                                     | II-4<br>II-4<br>II-7<br>II-5<br>II-3                                            |

| SKP<br>SNS<br>SRO<br>STA<br>STC                                    |                                                                                                     | II-4<br>II-4<br>II-7<br>II-5<br>II-3<br>II-9                                    |

| SKP<br>SNS<br>SRO<br>STA<br>STC<br>STH                             |                                                                                                     | II-4<br>II-7<br>II-5<br>II-3<br>II-9<br>II-4                                    |

| SKP<br>SNS<br>SRO<br>STA<br>STC<br>STH<br>SXL                      |                                                                                                     | II-4<br>II-7<br>II-5<br>II-3<br>II-9<br>II-4<br>II-15                           |

| SKP<br>SNS<br>SRO<br>STA<br>STC<br>STH<br>SXL<br>WCG               |                                                                                                     | II-4<br>II-7<br>II-5<br>II-3<br>II-9<br>II-4<br>II-15<br>II-15                  |

| SKP<br>SNS<br>SRO<br>STA<br>STC<br>STH<br>SXL<br>WCG<br>WRC        |                                                                                                     | II-4<br>II-7<br>II-7<br>II-5<br>II-3<br>II-9<br>II-4<br>II-15<br>II-15<br>II-15 |

| SKP<br>SNS<br>SRO<br>STA<br>STC<br>STH<br>SXL<br>WCG<br>WRC<br>WRI | 72,         73,         61,         23,         10,         51,         72,         89,         85, | II-4<br>II-7<br>II-7<br>II-5<br>II-3<br>II-9<br>II-4<br>II-15<br>II-15<br>II-15 |

#### PROGRAMMING THE LINC

#### 1. Introduction

The LINC (Laboratory Instrument Computer) is a stored-program binarycoded digital computer designed to operate in the laboratory environment as a research tool. The following description is intended to serve as a general introduction to basic programming concepts and techniques, and specifically as an introduction to LINC programming.

The "classic" LINC,<sup>1</sup> the basis of this document, has found variation in manufacture in the form of the LINC-8 and the micro-LINC. Other variations may yet appear. The fundamental programming techniques, however, are the same for all varieties, and references to "the LINC" in the following can generally be read without respect to variant. A summary on <u>LINC Variants</u> is provided in Appendix IV. It especially affects Chapter 16, and all questions of instruction execution times.

Like most digital computers, the LINC operates by manipulating binary numbers held in various <u>registers</u> (storage devices for numbers), under the control of a program of <u>instructions</u> which are themselves coded as binary numbers and stored in other registers. LINC instructions generally fall into types or classes, the instructions of a class having certain similarities. In this description, however, instructions are introduced as they are relevant to the discussion; reference to Chart I is therefore recommended when class characteristics are described. Furthermore, not all LINC instructions are described here in detail, specifically those resulting from modifications to the computer as covered in Appendix III. Therefore, this document should be read in conjunction with the LINC Order Code Summary, Appendices II and III-6.

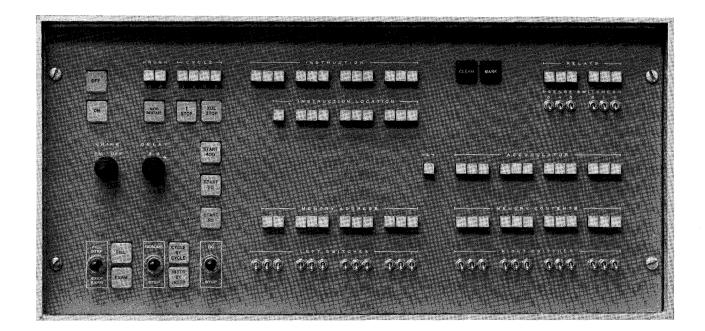

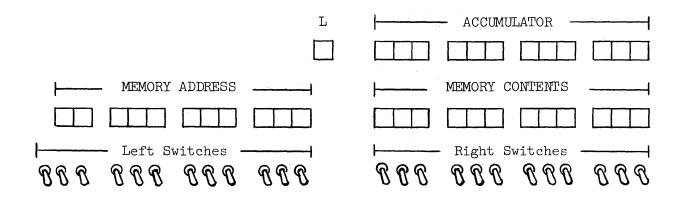

The best way to begin is to consider only a few of the registers and switches which are shown on the LINC Control Console:<sup>2</sup> the ACCUMULATOR (ACC) which is a register of 12 lights, the LINK BIT (L), the LEFT and RIGHT SWITCHES, which are rows of 12 toggle switches each, and one lever switch labeled "DO." The number systems and operation of several of the instructions can be understood in terms of these few elements.

## 2. Number Systems

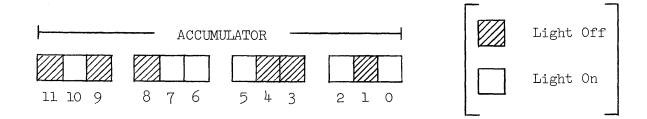

The elements (bits) of each register or row of toggle switches are to be thought of as numbered from right to left starting with zero. This will serve to identify the elements and to relate them to the numerical value of the binary integer held in the register. We shall use "C(ACC)" to denote "the contents of the Accumulator register," etc. If the Accumulator is illuminated thus

then the binary number stored in the Accumulator is

C(ACC) = 010 011 100 101 (binary)

which has the decimal value

$C(ACC) = 2^{10} + 2^7 + 2^6 + 2^5 + 2^2 + 2^0$ = 1024 + 128 + 64 + 32 + 4 + 1 = 1253 (decimal)

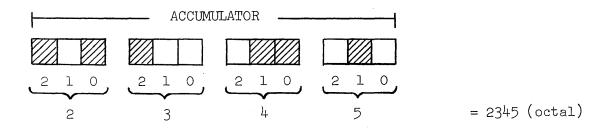

We can also view this as an <u>octal</u> number by considering each group of three bits in turn. In this example, grouping and factoring proceed as follows:

$$C(ACC) = (2^{10}) + (2^{7}+2^{6}) + (2^{5}) + (2^{2}+2^{0})$$

=  $(2^{1})\cdot 2^{9} + (2^{1}+2^{0})\cdot 2^{6} + (2^{2})\cdot 2^{3} + (2^{2}+2^{0})\cdot 2^{0}$

=  $(2)\cdot 8^{3} + (3)\cdot 8^{2} + (4)\cdot 8^{1} + (5)\cdot 8^{0}$

=  $2 \qquad 3 \qquad 4 \qquad 5$

=  $2345 \quad (octal)$

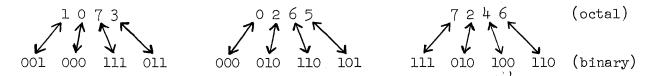

To put this more simply, each octal digit can be treated as an independent 3-bit binary number whose value, (0, 1, ..., 7), can be obtained from the weights  $2^2$ ,  $2^1$ , and  $2^0$ :

This ease of representation (the eight possible combinations within a group are easily perceived and remembered) is the principal reason for using octal numbers. The octal system can be viewed simply as a convenient notational system for representing binary numbers. Of course, octal numbers can also be manipulated arithmetically.

The translation from one system to the other is easily accomplished in either direction. Here are some examples:

Sometimes it is useful to view the contents of a register as a <u>signed</u> <u>number</u>. One of the bits must be reserved for the sign of the number. The left-most bit is therefore identified as the SIGN BIT (0 for +, 1 for -). To change the sign of a binary number, we <u>complement</u> the number (replace all ZEROS by ONES and vice-versa).<sup>3</sup> Examples:

000 000 000 011 = +3 111 111 111 100 = -3 011 111 111 111 = +3777 100 000 000 000 = -3777

The largest positive and negative octal integers in the l2-bit signed-number system.

We say that the pair of binary numbers lollllllloll and OlOOOOOOllOO are ones' complements of each other, (in octal these are 5763 and 2014), and will denote the complement of the number N by  $\overline{N}$ . Note that the sum of each binary digit and its complement is the number 1, and that the sum of each octal digit and its complement is the number 7. Note also that there are two representations of the number zero:

> 000 000 000 000 = +0 111 111 111 111 = -0

Note finally that the sum of any binary number and its complement is always a zero of the second kind, "minus zero," in this system.

#### 3. Simple Instructions

The LINC instructions themselves are encoded as binary numbers and held in various registers. The simplest of these instructions, namely those which operate only on the Accumulator, will be described first with reference to the Left Switches.

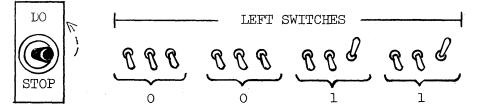

Raising the DO lever (DO means "do toggle instruction") causes the LINC to execute the instruction whose binary code number is held in the Left Switches. The LINC will then halt. For example, if we set the Left Switches to the code number for the instruction "CLEAR," which happens to be OOll (octal), and then momentarily raise the DO lever, the Accumulator lights will all go out and so will the Link Bit light, so that C(ACC) = 0, and C(L) = 0. In setting a switch, "up" corresponds to "one."

Left Switches set to OOll (octal), the code number for "CLEAR."

6 COM ATR RTA RSW

Tersely: If C(Left Switches) = 0011 (octal), then DO has the effect  $0 \rightarrow C(ACC)$  and  $0 \rightarrow C(L)$ . (Read "zero replaces the contents of the Accumulator," etc.).

CLEAR (or CLR) is an instruction of the class known as Miscellaneous instructions. A second Miscellaneous Class instruction, COMPLEMENT (or COM), with the code number OO17 (octal), directs the LINC to complement the contents of the Accumulator and therefore has the effect  $\overline{C(ACC)} \rightarrow C(ACC)$ . (Read: "the complement of the contents of the Accumulator replaces the contents of the Accumulator.")

Two other instructions of this class transfer information between the Accumulator and the Relay Register. The Relay Register, displayed on the upper right corner of the Control Console, operates 6 relays which can be used to control or run external equipment. An instruction with the code OOl4 (octal), called ACCUMULATOR TO RELAY, ATR, directs the LINC to copy the contents of the right <u>half</u> of the Accumulator, i.e., the right-most 6 bits, into the Relay Register. The Accumulator itself is not changed when the instruction is executed. Another instruction, called RELAY TO ACCUMULATOR, RTA, with the octal code OOl5, causes the LINC to clear the Accumulator and then copy the contents of the Relay Register into the right half of the Accumulator. In this case the Relay Register is not changed and the left half of the Accumulator is left cleared (i.e., containing zeros).

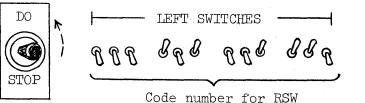

Another instruction called RIGHT SWITCHES, RSW, with the code number 0516 (octal), directs the LINC to copy the contents of the Right Switches into the Accumulator. By setting the Left Switches to 0516, the Right Switches to whatever value we want to put in the Accumulator, and then momentarily raising the DO lever, we can change the contents of the Accumulator to any new value we like. The drawing shows how the switches should be set to put the number 6451 (octal) into the Accumulator:

Code number for RSW instruction = 0516

1-- RIGHT SWITCHES  $\mathcal{P}\mathcal{P}^{\mathcal{Y}} \mathcal{P}^{\mathcal{Y}}$ & R &

$6451 \rightarrow C(ACC)$  when D0 lever is raised

## 4. Shifting

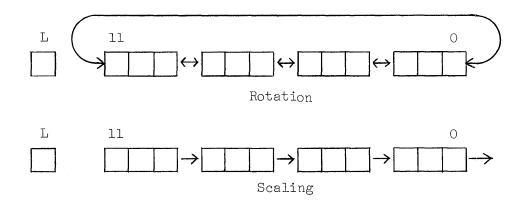

After a number has been put into the Accumulator it can be repositioned or "shifted," to the right or left. There are two ways of shifting: <u>rotation</u>, in which the end-elements of the Accumulator are connected together so as to form a closed ring, and <u>scaling</u>, in which the end-elements are not so connected.

#### Examples of shifts of one place:

|        |     | ct of<br>ght l |     | •   |     |     | ect o<br>right |     |   | <u> </u> |           |

|--------|-----|----------------|-----|-----|-----|-----|----------------|-----|---|----------|-----------|

| before | 000 | 000            | 011 | 001 | 000 | 000 | 011            | 001 | = | +25      | (decimal) |

| after  | 100 | 000            | 001 | 100 | 000 | 000 | 001            | 100 | = | +12      |           |

|        |     |                |     |     |     |     |                |     |   |          | <i>,</i>  |

| before | 111 | 111            | 100 | 110 | 111 | 111 | 100            | 110 | Ξ | -25      | (decimal) |

| after  | 011 | 111            | 110 | 011 | 111 | 111 | 110            | 011 | = | -12      |           |

Note that, in scaling, bits are lost to the right, which amounts to an error of "rounding off"; the original sign is preserved in the Sign Bit and replicated in the bit positions to the right of the Sign Bit. This has the effect of reducing the size of the number by powers of two (analogous to moving the decimal point in decimal calculations). 7

8 ROR ROL SCR

> The LINC has three instructions, called the Shift Class instructions, which shift the contents of the Accumulator; these are: ROTATE RIGHT, ROTATE LEFT, and SCALE RIGHT. Unlike the simple instructions we have considered so far, the code number for a Shift Class instruction includes a variable element which specifies the number of places to shift. For example, we write "ROL n," which means "rotate the contents of the Accumulator n places to the left," where n can be any number from O through 17 (octal).

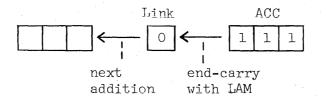

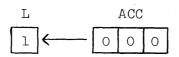

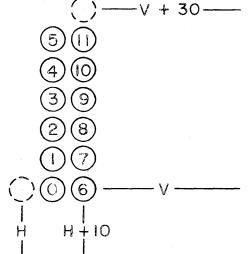

As a further variation of the Shift Class instructions, the Link Bit can be adjoined to the Accumulator during rotation to form a 13-bit ring as shown below, or to bit 0 of the Accumulator during scaling to preserve the low order bit scaled out of the Accumulator:

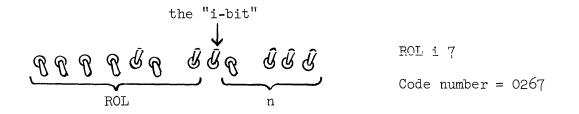

The code number of a Shift Class instruction, e.g., ROTATE LEFT, therefore includes the number of places to shift and an indication of whether or not to include the Link Bit. We use the full expression <u>ROL i n</u>, which has the octal coding:

ROL in 0240 + 20i + n number of places to shift (n = 0, 1, ..., 17)

so that, for example, ROTATE ACC LEFT 3 PLACES has the code number 0243, and ROTATE ACC WITH LINK LEFT 7 PLACES has the code number 0267. Note the

correspondence between the code terms and bit-positions of the binary-coded instruction as it appears, for example, in the Left Switches:

Similar coding is used with ROTATE RIGHT, ROR i n, 300 + 20i + n, and SCALE RIGHT, SCR i n, 340 + 20i + n.

#### 5. LINC Memory and Memory Reference Instructions

Before we can proceed to other instructions it is necessary to introduce the LINC Memory. This Memory is to be regarded as a set of 1024 (decimal) registers\* each holding 12-bit binary numbers in the manner of the Accumulator. These memory registers are numbered 0, 1, ..., 1023 (decimal), or 0, 1, ..., 1777 (octal), and we shall speak of "the contents of register 3," C(3), "the contents of register X," C(X), etc., referring to "3" and "X" as <u>Memory</u> Addresses.

The Memory actually consists of a remotely-located array of magnetic storage elements with related electronics, but for introductory purposes we can view it in terms of two registers of lights, namely the MEMORY ADDRESS register and the MEMORY CONTENTS register:

\*See Appendix I for a discussion of the LINC as a "double memory" machine.

By using these two registers in conjunction with the Left Switches it is possible to find out what values the memory registers contain. If, for example, we are interested in the contents of register 3, we may set the Left Switches to the memory address 0003 and then push the button labeled EXAM. We will see 0003 in the Memory Address register, and the contents of register 3 will appear in the Memory Contents register. By setting the Left Switches to a memory address and pushing EXAM, we can examine the contents of any register in the LINC Memory.

The contents of any selected memory register may be changed by using both the Left and Right Switches and the pushbutton marked FILL. If, for example, we want the memory register whose address is 700 to contain -1 (i.e., 7776 octal) we again set the memory address, 0700, in the Left Switches. We set the Right Switches to the value 7776 and push the FILL button. A 0700 will appear in the Memory Address register and 7776 will appear in the Memory Contents register, indicating that the contents of register 700 are now 7776. Whatever value register 700 may have contained before FILL was pushed is lost, and the new value has taken its place. In this way any register in the LINC Memory can be filled with a new number.

None of the LINC instructions makes explicit reference to the Memory Address register or Memory Contents register; rather, in referring to memory register X, an instruction may direct the LINC implicitly to put the address X into the Memory Address register and the contents of register X, C(X), into the Memory Contents register.

#### The STORE-CLEAR Instruction

Now we can describe the first of the memory reference instructions, STORE-CLEAR X, STC X, which has the code number 4000 + X, where  $0 \le X \le 1777$  (octal). (From now on we will use only octal numbers for addresses.) Execution of STC X has two effects: 1) the contents of the Accumulator are copied into memory register X, C(ACC)  $\rightarrow$  C(X), and 2) the Accumulator is then cleared,  $0 \rightarrow C(ACC)$ . (The Link Bit is not cleared.) Thus, for example, if C(ACC) = 0503 and C(671) = 2345, and we set the code

10 STC number for STC 671, i.e., 4671, in the Left Switches, then raising the DO lever will put 0 into the Accumulator and 0503 into register 671. The original contents of register 671 are lost.

It will be clear, now, that the Memory can be filled with new numbers at any time either by using the FILL pushbutton and the switches, or by loading the Accumulator from the Right Switches with the RSW instruction and the DO lever and then storing the Accumulator contents with the STC X instruction and the DO lever.

The ADD Instruction and Binary Addition

STC is one of three Full Address Class instructions. Another instruction in this class, ADD X, has the code number 2000 + X where  $0 \le X \le 1777$ . Execution of ADD X has the effect of adding the contents of memory register X to the contents of the Accumulator, i.e.,  $C(X) + C(ACC) \rightarrow C(ACC)$ . If the Accumulator is first cleared, ADD X will, of course, have the effect of merely copying into the Accumulator the contents of memory register X, i.e.,  $C(X) \rightarrow C(ACC)$ . In any case, the contents of memory register X are unaffected by the instruction.

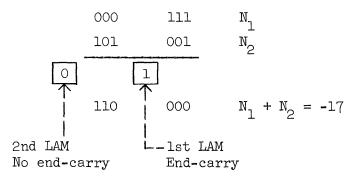

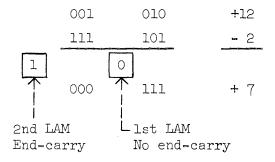

The addition itself takes place in the binary system,<sup>3</sup> within the limitations of the l2-bit registers. The basic rules for binary addition are simple: 0 + 0 = 0; 1 + 0 = 1; 1 + 1 = 10 (i.e., "zero, with one to carry"). A carry arising from the left-most column ("end-carry") is brought around and added into the right-most column ("end-around carry"). Some examples (begin at the right-most column as in decimal addition):

| 001       | 111        | 010      | 001      |                    | 111       | 100 | 010 | 011             |                    |

|-----------|------------|----------|----------|--------------------|-----------|-----|-----|-----------------|--------------------|

| 000       | 010        | 111      | 001      |                    | 001       | 010 | 010 | 000             |                    |

| 11<br>010 | 111<br>010 | 1<br>001 | 1<br>010 | (Carries)<br>(Sum) | 11<br>000 | 110 |     |                 | (Carries)          |

|           |            |          |          |                    |           |     |     | $\rightarrow 1$ | (End-around carry) |

|           |            |          |          |                    | 000       | 110 | 100 | 11<br>100       | (Carries)<br>(Sum) |

The reader should try some examples of his own, and incidentally verify the fact that adding a number to itself with end-around carry is equivalent to

rotating left one place. With signed-integer interpretation, some other examples are:

|     |            |     |          | = +5<br>= -3 |         |     |     |     | = -5<br>= -3 |           |

|-----|------------|-----|----------|--------------|---------|-----|-----|-----|--------------|-----------|

| 111 | 111<br>000 | 111 |          |              | 111 111 |     |     |     |              |           |

| 000 | 000        | 000 | 1<br>010 | = +2         | 111     | 111 | 110 | 111 | = -8         | (decimal) |

It can be seen that subtraction of the number N is accomplished by addition of the complement of N,  $\overline{N}$ . Of course, if either the sum or difference is too large for the Accumulator to hold, the result of the addition may not be quite the number we would like to have. For example, adding 1 to the largest positive integer in this system (+3777, octal) results in the largest negative integer (-3777, octal). This is sometimes called "overflowing the capacity of the Accumulator." \*

#### 6. The Instruction Location Register

It is clear that the code numbers of a series of different instructions can be stored in consecutive memory registers. The LINC is designed to execute such a "stored program" of instructions by fetching and carrying out each instruction in sequence, using a special 10-bit register called the INSTRUCTION LOCATION register, (IL), to hold the address of the next instruction to be executed. Using the FILL pushbutton and the Left and

\* See Appendix III.

12

13 HLT

Right Switches already discussed, we can, for example, put the code numbers for a series of instructions into memory registers  $20-2^4$  which will divide by 8 the number held in memory register 30 and store the result in memory register 31:

|         | Memory<br>Address | Memory Cor | ntents | Effect                                                             |

|---------|-------------------|------------|--------|--------------------------------------------------------------------|

| Start   | → 20              | CLR        | 0011   | Clear the Accumulator.                                             |

|         | 21                | ADD 30     | 2030   | Add the contents of register 30 to                                 |

|         | 22                | SCR 3      | 0343   | the Accumulator.<br>Scale C(ACC) right 3 places to<br>divide by 8. |

|         | 23                | STC 31     | 4031   | Store in register 31.                                              |

|         | 24                | HLT        | 0000   | Halt the computer.                                                 |

|         | •                 | ۰          | •      |                                                                    |

|         | •                 | •          | •      |                                                                    |

|         | •                 | •          | •      |                                                                    |

|         | 30                | N          | N      | Number to be divided by $8.$                                       |

| :<br>:: | 31                | L→N/8      | N/8    | Result.                                                            |

|         |                   |            |        |                                                                    |

Example 1. Simple Sequence of Instructions,

We can use the FILL pushbutton and the Left and Right Switches to put the code numbers for the instructions into memory registers 20 - 24 and the number to be divided into register 30. Pushing the console button labeled START 20 directs the LINC to begin executing instructions at memory register 20. That is, the value 20 replaces the contents of the Instruction Location register. As each instruction of the stored program is executed, the Instruction Location register is increased by 1,  $C(IL) + 1 \rightarrow C(IL)$ . When the Instruction Location register contains 24, the computer encounters the instruction HLT, code 0000, which halts the machine. To run the program again we merely push the START 20 pushbutton. (The code numbers for the instructions will stay in memory registers 20 - 24 unless they are deliberately changed.) The JUMP Instruction

The last Full Address instruction, JUMP to X, JMP X, with the code number 6000 + X, has the effect of setting the Instruction Location register to the value X;  $X \rightarrow C(IL)$ . That is, the LINC, instead of increasing the contents of the Instruction Location register by one and executing the next instruction in sequence, is directed by the JMP instruction to get its next instruction from memory register X. In the above example having a JUMP to 20 instruction, code 6020, in memory register 24 (in place of HLT) would cause the computer to repeat the program endlessly. If the program were started with the START 20 pushbutton, the Instruction Location register would hold the succession of values: 20, 21, 22, 23, 24, 20, 21, etc. (Later we will introduce instructions which increase C(IL) by extra amounts, causing it to "skip.")

JMP X has one further effect: if JMP 20, 6020, is held in memory register 24, then its execution causes the code for "JMP 25" to replace the contents of register 0; i.e.,  $6025 \rightarrow C(0)$ . More generally, if JMP X is in any memory register "p,"  $0 \le p \le 1777$ , then its execution causes "JMP p+1"  $\rightarrow C(0)$ .

| Memory<br>Address | Memory C   | ontents    | Effect                                     |

|-------------------|------------|------------|--------------------------------------------|

| 0                 | JMP p+1    | 6000 + p+1 |                                            |

| o                 | 0          | ٥          |                                            |

| 9                 | . 0        | ø          |                                            |

| → p               | JMP X      | 6000 + X   | $X \to C(IL)$ , and "JMP p+1" $\to C(O)$ . |

| p+1               | •          | o          |                                            |

| ٥                 | o          | •          |                                            |

| ۰                 | •          | ٥          |                                            |

| Х                 | <b>→</b> - |            | Next instruction.                          |

|                   | 1          |            |                                            |

This "JMP p+1" code replaces the contents of register 0 every time a JMP X instruction is executed unless X = 0, in which case the contents of 0 are unchanged. The use of memory register 0 in this way is relevant to a programming technique involving "subroutines" which will be described later.

14 JMP The following programming example illustrates many of the features described so far. It finds one-fourth of the difference between two numbers  $N_1$  and  $N_2$ , which are located in registers 201 and 202, and leaves the result in register 203 and in the Accumulator. After filling consecutive memory registers 175 through 210 with the appropriate code and data numbers, the program must be started at memory register 175. Since there is no "START 175" button on the console, this is done by setting the Right Switches to 0175 and pushing the console button labeled START RS (Start Right Switches).

| Memory<br>Address  | Memory Co       | ontents                             | Effect                                                                           |

|--------------------|-----------------|-------------------------------------|----------------------------------------------------------------------------------|

| <u>Start</u> ▶ 175 | CLR             | 0011                                | $0 \rightarrow C(ACC)$ .                                                         |

| 176                | ADD 201         | 2201                                | $N_1 \rightarrow C(ACC)$ .                                                       |

| 177                | COM             | 0017                                | Forms -N1.                                                                       |

| 200                | JMP 204         | 6204                                | Jumps around data; $204 \rightarrow C(IL)$ ,<br>and JMP 201 $\rightarrow C(0)$ . |

| 201                | Nl              | Nl                                  |                                                                                  |

| 202                | N2              | N <sub>2</sub>                      | >Data and result.                                                                |

| 203                | $(N_2 - N_1)/4$ | (N <sub>2</sub> -N <sub>1</sub> )/4 |                                                                                  |

| 204                | ADD 202         | 2202                                | $\left( N_{2} - N_{1} \right) \rightarrow C(ACC).$                               |

| 205                | SCR 2           | 0342                                | Divides by 4.                                                                    |

| 206                | STC 203         | 4203                                | Stores result in 203; $C(ACC) \rightarrow C(203); O \rightarrow C(ACC).$         |

| 207                | ADD 203         | 2203                                | Recovers result in ACC.                                                          |

| 210                | НІЛ             | 0000                                | Halts the LINC.                                                                  |

Example 2. Simple Sequence Using the JUMP Instruction.

In executing this program, the Instruction Location register holds the succession of numbers: 175, 176, 177, 200, 204, 205, 206, 207, 210.

15

# 7. Address Modification and Program "Loops"

Frequently a program of instructions must deal with a large set of numbers rather than just one or two. Suppose, for example, that we want to add together 100 (octal) numbers and that the numbers are stored in the memory in registers 1000 through 1077. We want to put the sum in memory register 1100. We could, of course, write out all the instructions necessary to do this,

| Memory<br>Address | Memory Conte | ents | Effect                                      |  |  |  |

|-------------------|--------------|------|---------------------------------------------|--|--|--|

| → 20              | CLR          | 0011 | $0 \rightarrow C(ACC); 0 \rightarrow C(L).$ |  |  |  |

| 21                | ADD 1000     | 3000 | Add 1st number.                             |  |  |  |

| 22                | ADD 1001     | 3001 | Add 2nd number.                             |  |  |  |

| 23                | ADD 1002     | 3002 | Add 3rd number.                             |  |  |  |

| 24                | ADD 1003     | 3003 | Add 4th number.                             |  |  |  |

|                   | etc.         | etc. | etc.                                        |  |  |  |

|                   |              |      |                                             |  |  |  |

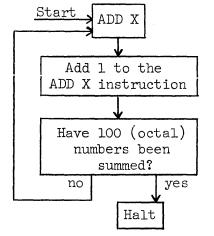

but it is easy to see that the program will be more than 100 (octal) registers long. A more complex, but considerably shorter, program can be written using a programming technique known as "address modification." Instead of writing 100 (octal) ADD X instructions, we write only <u>one</u> ADD X instruction, which we repeat 100 (octal) times, modifying the X part of the ADD X instruction each time it is repeated. In this case the computer first executes an ADD 1000 instruction; the program then adds one to the ADD instruction itself and restores it, so that it is now ADD 1001. The program then jumps back to the location containing the ADD instruction and the computer repeats the entire process, this time executing an ADD 1001 instruction. In short, the program is written so that it changes its own instructions while it is running.

The process might be diagrammed:

This technique introduces the additional problem of deciding when all 100 numbers have been summed and halting the computer. In this context we introduce a new instruction ACCUMULATOR ZERO, AZE, code 0450. This is one of a class of instructions known as the Skip instructions; it directs the LINC to skip the instruction in the next memory register when C(ACC) = either positive or negative zero (0000 or 7777, octal). If  $C(ACC) \neq 0$ , the computer does not skip. For example, if C(ACC) = 7777, and we write:

| Memory<br>Address | Memory Contents |      |  |  |  |  |

|-------------------|-----------------|------|--|--|--|--|

| → p               | AZE             | 0450 |  |  |  |  |

| p+1               | -               | -    |  |  |  |  |

| p+2               |                 | -    |  |  |  |  |

| 1                 |                 | 1    |  |  |  |  |

the computer will take the next instruction from p+2. That is, when the AZE instruction in register p is executed, p+2 will replace the contents of the Instruction Location register, and the computer will skip the instruction at p+1. If  $C(ACC) \neq 0$ , then p+1  $\rightarrow C(IL)$  and the computer executes the next instruction in sequence as usual.

The following example sums the numbers in memory registers 1000 through 1077 and puts the sum into memory register 1100, using address modification and the AZE instruction to decide when to halt the computer. (Square brackets indicate registers whose contents change while the program is running.)

|      | Memory<br>Address | Memory Cont               | ents             | Effect                                                                                                                 |

|------|-------------------|---------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| -    | 10                | ADD 1000                  | 3000             |                                                                                                                        |

|      | 11                | 1                         | 0001             | Constants used by program.                                                                                             |

|      | 12                | -(ADD 1100)               | 4677             |                                                                                                                        |

|      | •                 | ð                         |                  |                                                                                                                        |

| Star | •<br>+ •          | •                         | с<br>0           |                                                                                                                        |

| Duar | <u> </u> 20       | CLR                       | 0011             | Code for ADD 1000 $\rightarrow$ C(25).                                                                                 |

|      | 21                | ADD 10                    | 2010             | $\begin{array}{c} \text{Code for ADD 1000} \rightarrow \text{C(2)},\\ \text{O} \rightarrow \text{C(ACC)}. \end{array}$ |

|      | 22                | STC 25                    | 4025             |                                                                                                                        |

|      | 23                | STC 1100                  | 5100             | $0 \rightarrow C(1100)$ , for accumulating sum.                                                                        |

|      | 24                | $\rightarrow$ CLR         | 0011             | Clear ACC and add $C(X)$ to $C(ACC)$ .                                                                                 |

|      | 25                | [ADD X]                   | [2000+X]         |                                                                                                                        |

|      | 26                | ADD 1100                  | 3100             | Sum so far + $C(ACC) \rightarrow C(ACC)$ .                                                                             |

|      | 27                | STC 1100                  | 5100             | Sum so far $\rightarrow$ C(1100).                                                                                      |

|      | 30                | ADD 25                    | 2025             | "ADD X instruction in register 25"<br>$\rightarrow$ C(ACC). Add 1 to C(ACC)                                            |

|      | 31                | ADD 11                    | 2011             | and replace in register 25.                                                                                            |

|      | 32                | STC 25                    | 4025             |                                                                                                                        |

|      | 33                | ADD 25                    | 2025             | $\int C(25) + C(12) \rightarrow C(ACC). \text{ If } C(25)$                                                             |

|      | 34                | ADD 12                    | 2012             | <pre>&gt; = "ADD 1100," then C(ACC) = 7777.</pre>                                                                      |

|      | 35                | AZE                       | 0450             | Skip to register 37 if $C(ACC) = 7777$ .                                                                               |

|      | 36                | JMP 24                    | 6024             | If not, return and add next number.                                                                                    |

|      | 37                | HLT $\leftarrow - \dashv$ | 0000             | When $C(ACC) = 7777$ , all numbers have                                                                                |

|      | • .               | o                         | •                | been summed. Halt the computer,                                                                                        |

|      | •                 | 0                         | °                |                                                                                                                        |

|      | 1000              | Nl                        | Nl               |                                                                                                                        |

|      | 1001              | N2                        | N <sub>2</sub>   |                                                                                                                        |

|      | •                 | •                         | •                | Numbers to be summed.                                                                                                  |

|      |                   | 0<br>77                   |                  |                                                                                                                        |

|      | 1076              | N <sub>77</sub>           | N <sub>77</sub>  |                                                                                                                        |

|      | 1077              | N <sub>100</sub>          | N <sub>100</sub> | Υ<br>Υ                                                                                                                 |

|      | 1100              | [Sum]                     | [Sum]            | 1                                                                                                                      |

Example 3. Summing a Set of Numbers Using Address Modification.

The instructions at locations 20 - 22 initially set the contents of memory register 25 to the code for ADD 1000. At the end of the program, register 25 will contain 3100, the code for ADD 1100. Adding (in registers 33 and 34) C(25) to C(12), which contains the complement of the code for ADD 1100, results in the sum 7777 only when the program has finished summing all 100 (octal) numbers. This repeating sequence of instructions is called a "loop," and instructions such as AZE can be used to control the number of times a loop is repeated. In this example the instructions in locations 24 through 36 will be executed 100 (octal) times before the computer halts.

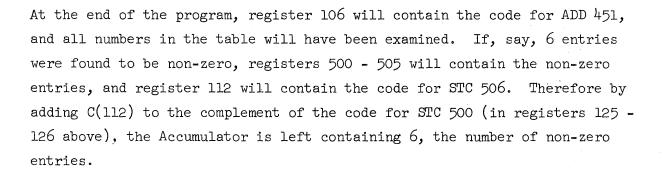

The following program scans the contents of memory registers 400 through 450 looking for registers which do not contain zero. Any non-zero entry is moved to a new table beginning at location 500; this has the effect of "packing" the numbers so that no register in the new table contains zero. When the program halts, the Accumulator contains the number of non-zero entries.

| Memory     |                       |          | 1                                                                                              |  |  |

|------------|-----------------------|----------|------------------------------------------------------------------------------------------------|--|--|

| Address    | Memory Conte          | ents     | Effect                                                                                         |  |  |

| 4          | ADD 400               | 2400     |                                                                                                |  |  |

| 5          | STC 500               | 4500     |                                                                                                |  |  |

| 6          | • 1                   | 0001     | $\rangle$ Constants used by the program.                                                       |  |  |

| 7          | -(ADD 451)            | 5326     |                                                                                                |  |  |

| . 10       | -(STC 500)            | 3277     | J                                                                                              |  |  |

| •          | •                     | •        |                                                                                                |  |  |

| Start, 100 | CLR                   | 0011     |                                                                                                |  |  |

| 101        | ADD 4                 | 2004     | Code for ADD 400 $\rightarrow$ C(106).                                                         |  |  |

| 102        | STC 106               | 4106     |                                                                                                |  |  |

| 103        | ADD 5                 | 2005     | Code for STC 500 $\rightarrow$ C(112).                                                         |  |  |

| 104        | STC 112               | 4112     | $\left\{ \begin{array}{c} code \ \text{ior sic } joo \rightarrow c(112). \end{array} \right\}$ |  |  |

| 105        | $\longrightarrow$ CLR | 0011     |                                                                                                |  |  |

| 106        | [ADD 400]             | [2000+X] | $C(X) \rightarrow C(ACC).$                                                                     |  |  |

| 107        | <u>AZE</u>            | 0450     | If C(ACC) = zero, skip to<br>location 111.                                                     |  |  |

| 110        | JMP 112               | 6112     | $C(ACC) \neq 0$ , therefore JMP                                                                |  |  |

| 111        | JMP 116 ¢ -           | 6116     | to location 112.<br>C(ACC) = 0, therefore JMP<br>to location 116.                              |  |  |

| 112        | ↓[STC 500]            | [4000+X] | Store non-zero entry in new table                                                              |  |  |

| 113        | ADD 6                 | 2006     |                                                                                                |  |  |

| 114        | ADD 112               | 2112     | Add 1 to the STC instruction<br>in register 112.                                               |  |  |

| 115        | STC 112               | 4112     |                                                                                                |  |  |

| 116        | $\rightarrow$ ADD 6   | 2006     |                                                                                                |  |  |

| 117        | ADD 106               | 2106     | Add 1 to the ADD instruction<br>in register 106.                                               |  |  |

| 120        | STC 106               | 4106     | l J                                                                                            |  |  |

| 121        | ADD 106               | 2106     | $C(106) + C(7) \rightarrow C(ACC). $ If                                                        |  |  |

| 122        | ADD 7                 | 2007     | C(106) = ADD 451, then<br>C(ACC) = $7777$ .                                                    |  |  |

| 123        | AZE                   | 0450     | If $C(ACC) = 7777$ , skip to                                                                   |  |  |

| 124        | JMP 105               | 6105     | location 125.<br>If not, return to examine next<br>number.                                     |  |  |

| 125        | ADD 112 -             | 2112     | If $C(ACC) = 7777$ , then number                                                               |  |  |

| 126        | ADD 10                | 2010     | of non-zero entries $\rightarrow$ C(ACC) and computer halts.                                   |  |  |

| 127        | ніл                   | 0000     | and computer narts.                                                                            |  |  |

|            |                       | l        | 1                                                                                              |  |  |

Example 4. Packing a Set of Numbers.

÷.,

#### 8. Index Class Instructions I

Indirect Addressing

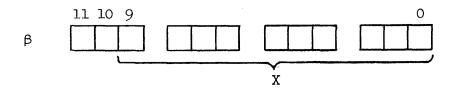

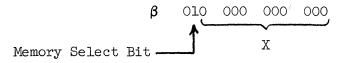

The largest class of LINC instructions, the Index Class, addresses the memory in a somewhat involved manner. The instructions ADD X, STC X, and JMP X are called Full Address instructions because the 10-bit address X,  $0 \le X \le 1777$ , can address directly any register in the 2000 (octal) register memory. The Index Class instructions, however, have only 4 bits reserved for an address, and can therefore address only memory registers 1 through 17 (octal). The instruction ADD TO ACCUMULATOR, ADA i  $\beta$ , octal code 1100 + 201 +  $\beta$ , is typical of the Index Class:

ADA i

$$\beta$$

ADA i  $\beta$

ADA i  $\beta$

ADA i  $\leq \beta \leq 17$

Memory register  $\beta$  should be thought of as containing a memory address, X, in the right-most 10 bits,

and we speak of  $X(\beta)$ , meaning the right 10-bit address part of register  $\beta$ . The left-most bit can have any value whatever, and, for the present, bit 10 must be zero.\* In addressing memory register  $\beta$ , an Index Class instruction tells the computer where to find the memory <u>address</u> to be used in executing the instruction. This is sometimes called "indirect" addressing.

For example, if we want to add the value 35 to the contents of the Accumulator, and 35 is held in memory register 270, we can use the ADA instruction in the following manner:

|   | Memory<br>Address                       | Memory Contents |                 | Effect                                |

|---|-----------------------------------------|-----------------|-----------------|---------------------------------------|

| 1 | (B)                                     | >0270           | 0270            | Address of register containing 35.    |

|   | · ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` |                 | 0<br>0<br>0     |                                       |

|   | 0270 K                                  | 0035            | 0035            |                                       |

|   | 0<br>0<br>9                             |                 | 0<br>0<br>0     |                                       |

|   | → p                                     | ADAB            | 1100 <b>+</b> β | $C(270) + C(ACC) \rightarrow C(ACC).$ |

|   | с<br>0<br>8                             | ₽<br>●<br>○     | 8 ;<br>0 ;<br>0 |                                       |

Note that the ADA instruction does not tell the computer directly where to find the number 35; it tells the computer instead where to find the <u>address</u> of the memory register which contains 35. By using memory registers 1 through 17 in this way, the Index Class instructions can refer to any register in the memory.

Two other Index Class instructions, LOAD ACCUMULATOR, LDA i  $\beta$ , and STORE ACCUMULATOR, STA i  $\beta$ , are used in the following program which adds the contents of memory register 100 to the contents of register 101 and stores the result in 102. The LDA i  $\beta$  instruction, code 1000 + 20i +  $\beta$ , clears the Accumulator and copies into it the contents of the specified memory register. STA i  $\beta$ , code 1040 + 20i +  $\beta$ , stores the contents of the Accumulator in the specified memory register; it does not, however, clear the Accumulator. Addition with ADA uses 12-bit end-around carry arithmetic.

|      | Memory<br>Address | Memory Co                         | ontents | Effect                                                              |

|------|-------------------|-----------------------------------|---------|---------------------------------------------------------------------|

| Star | 10                | X,                                | 0100    | Address of N <sub>1</sub> .                                         |

|      | 11                | X <sub>2</sub>                    | 0101    | Address of N <sub>2</sub> .                                         |

|      | 12                | x <sub>3</sub>                    | 0102    | Address of $(\bar{N}_1 + N_2)$ .                                    |

|      | ۰<br>د            |                                   | •       |                                                                     |

|      | art. 30           | LDA 10                            | 1010    | $N_1$ , i.e., C(100), $\rightarrow$ C(ACC).                         |

|      | 31                | ADA 11                            | 1111    | $\mathbb{N}_{2}^{+}$ , i.e., C(101), + C(ACC) $\rightarrow$ C(ACC). |

|      | 32                | STA 12                            | 1052    | $\tilde{N_1 + N_2} \rightarrow C(102).$                             |

|      | 33                | HLT                               | 0000    |                                                                     |

|      | •                 | 5                                 | •       |                                                                     |

|      | 100               | N                                 | 2.00k   |                                                                     |

|      | 101               | N                                 | ×       |                                                                     |

|      | 102               | [N <sub>1</sub> +N <sub>2</sub> ] | [-]     |                                                                     |

|      | 1                 |                                   | 1       |                                                                     |

# Example 5. Indirect Addressing.

#### Index Registers and Indexing

When "i" is used with an Index Class instruction, that is, when i = 1, the computer is directed to add 1 to the X part of memory register  $\beta$  before it is used to address the memory. This process is called "indexing," and registers 1 through 17 are frequently referred to as Index Registers. In the example below, -6 is loaded into the Accumulator after Index Register  $\beta$ is indexed from 1432 to 1433 by the LDA i  $\beta$  instruction.

| Memory<br>Address | Memory Contents |               | Effect                                                                           |

|-------------------|-----------------|---------------|----------------------------------------------------------------------------------|

| β                 | [x]             | [1432]        | Address minus l of register                                                      |

| :                 | :               | :             | containing 7771.                                                                 |

| → p<br>:          | LDA i β         | 1020 + β<br>: | X + 1, i.e., 1433, $\rightarrow$ C( $\beta$ ), and C(1433) $\rightarrow$ C(ACC). |

| 1432              | -               | -             |                                                                                  |

| 1433              | -6              | 7771          |                                                                                  |

When the LDA i  $\beta$  instruction is executed, the value  $X(\beta) + 1$  replaces the address part of register  $\beta$  (the left-most 2 bits of register  $\beta$  are unaffected). This new value, 1433, is now used to address the memory. Note that if the LDA instruction at p were repeated, it would deal with the contents of register 1434, then 1435, etc. The utility of Index Registers in scanning tables of numbers should be obvious.

Indexing involves only 10-bit numbers, and <u>does not involve end-around</u> <u>carry</u>. Therefore the address "following" 1777 is 0000. (The same kind of indexing takes place in the Instruction Location register, which "counts" from 1777 to 0000.) The following example using indexing introduces another Index Class instruction, SKIP IF ACCUMULATOR EQUALS, SAE i  $\beta$ , code 1440 + 20i +  $\beta$ . This instruction causes the LINC to skip one register in the sequence of programmed instructions when the contents of the Accumulator exactly match the contents of the specified memory register. If there is no match, the computer goes to the next instruction in sequence as usual. The program example clears (stores 0000 in) the set of memory registers 1400 through 1777; the SAE instruction is used to decide whether the last 0000 has been stored.

| _    | Memory<br>Address | Memory Cor   | ntents        | Effect                                                                                                         |

|------|-------------------|--------------|---------------|----------------------------------------------------------------------------------------------------------------|

|      | 3                 | [X]          | [1377]        | Initial Address minus 1 for the STA instruction.                                                               |

|      | 4                 | 356          | 0356          | Address of test number.                                                                                        |

| a.   | •<br>•<br>•       | •            | 0<br>0<br>0   |                                                                                                                |

| Star | t<br>→ 350        | <b>→</b> CLR | 0011          | Clear the Accumulator.                                                                                         |

|      | 351               | STA i 3      | 1063          | <pre>Index the contents of register 3;<br/>store C(ACC) in the memory<br/>register whose address = X(3).</pre> |

|      | 352               | ADD 3        | 2003          | $C(3) \rightarrow C(ACC).$                                                                                     |

|      | 353               | SAE 4        | 1444          | Skip to 0355 if $C(ACC) \equiv C(356)$ .                                                                       |

|      | 354               | JMP 350      | 6 <u>3</u> 50 | If not, return to store 0000 in next register.                                                                 |

|      | 355               | HLT <- 1     | 0000          | Halt the computer.                                                                                             |

|      | 356               | 1777         | 1777          |                                                                                                                |

Example 6. Indexing to Clear a Set of Registers.

When the program halts at register 355, register 3 will contain 1777. The SAE instruction is used here (as the AZE instruction was used in earlier examples) to decide when to stop the computer. The instructions in registers 350 through 354, the "loop," will be executed 400 (octal) times before the program halts. Zero is first stored in register 1400, next in 1401, etc. 25 SAE Another program scans the memory to see if a particular number, Q, appears in any memory register O through 1777. Q is to be set in the Right Switches, and the address of any register containing Q is to be left in the Accumulator.

| Memory<br>Address | Memory Con             | tents  | Effect                                                                           |

|-------------------|------------------------|--------|----------------------------------------------------------------------------------|

| 17<br>Stort       | [X]                    | [-]    | Address of register whose contents<br>are to be compared with Right<br>Switches. |

| Start 20          | RSW                    | 0516   | $C(RS) \rightarrow C(ACC).$                                                      |

| 21                | $\rightarrow SAE i 17$ | 1477   | Index register 17, and compare C(ACC) with C(X).                                 |

| 22                | JMP 21                 | 6021 · | If not equal, return for next test.                                              |

| 23                | $CLR \leftarrow$       | 0011   | If equal, clear ACC, copy address                                                |

| 24                | ADD 17                 | 2017   | of register containing Q into                                                    |

| 25                | HLT                    | 0000   | ACC, and halt.                                                                   |

Example 7. Memory Scanning.

If no memory register 0 through 1777 contains the number Q, the program will run endlessly. The location of the first register to be tested depends on the initial contents of Index Register 17.

An Index Class instruction, ADD TO MEMORY, ADM i  $\beta$ , code 1140 + 20i +  $\beta$ , adds the contents of the specified memory register to C(ACC), using 12-bit end-around carry arithmetic (as ADD or ADA). The result is left, however, not only in the Accumulator but in the specified memory register as well. The BIT CLEAR instruction, BCL i  $\beta$ , code 1540 + 20i +  $\beta$ , is one of three Index Class instructions which performs a so-called "logical" operation. BCL is used to clear selected bits of the Accumulator. For every bit of the specified memory register which contains 1, the corresponding bit of the Accumulator is set to 0.

In the following program two sets of numbers are summed term by term. The first set of numbers, each 6 bits long, is in registers 500 - 577, bits 0 through 5; bits 6 through 11 contain unwanted information. The second set of numbers is in registers 600 - 677, and the sums replace the contents of registers 600 - 677.

| Memory<br>Address | Memory Con                    | tents       | Effect                                                                         |

|-------------------|-------------------------------|-------------|--------------------------------------------------------------------------------|

| 3                 | [x <sub>1</sub> ]             | [0477]      | Initial address minus 1 of first set.                                          |

| ) <sub>4</sub>    | 0410                          | 0410        | Address of BCL pattern.                                                        |

| 5                 | [x <sub>2</sub> ]             | [0577]      | Initial address minus 1 of second set.                                         |

| 6                 | 0411                          | 0411        | Address of test number for halting.                                            |

| •<br>•<br>•       | •<br>•<br>•                   | 8<br>0<br>• |                                                                                |

| Start 400         | LDA i 3                       | 1023        | Index X(3) and load number from first set into ACC.                            |

| 401               | BCL 4                         | 1544        | Clear the left 6 bits of the ACC.                                              |

| 402               | ADM i 5                       | 1165        | Index X(5); Add number from<br>second set to C(ACC), and<br>replace in memory. |

| 403               | CLR                           | 0011        |                                                                                |

| ¥0¥               | ADD 3                         | 2003        | Check to see if finished.                                                      |

| 405               | SAE_6_                        | 1446        |                                                                                |

| 406               | JMP 400                       | 6400        | C(3) ≠ C(411), i.e., ≠ 0577.                                                   |

| 407               | $\mathrm{HLT} \leftarrow - -$ | 0,000       | C(3) = 0577; halt the program.                                                 |

| 410               | 7700                          | 7700        | BCL pattern for clearing left half of ACC.                                     |

| 411               | 0577                          | 0577        | Test number for halting.                                                       |

Example 8. Summing Sets of Numbers Term by Term,

28 BSE BCO

Logic Instructions

The three logic instructions, BCL i  $\beta$ , BSE i  $\beta$ , and BCO i  $\beta$ , are best understood by studying the following examples. These instructions affect only the Accumulator; the memory register M containing the bit pattern is unchanged.

BCL i  $\beta$  BIT CLEAR code: 1540 + 20i +  $\beta$

Clear corresponding bits of the Accumulator:

If C(M) = 010 101 010 101 and C(ACC) = 111 111 000 000 then C(ACC) = 101 010 000 000

BSE i  $\beta$  BIT SET code: 1600 + 20i +  $\beta$

Set to ONE corresponding bits of the Accumulator:

If C(M) = 010 101 010 101 and C(ACC) = 111 111 000 000 then C(ACC) = 111 111 010 101

BCO i  $\beta$  BIT COMPLEMENT code: 1640 + 20i +  $\beta$

Complement corresponding bits of the Accumulator:

If C(M) = 010 101 010 101 and C(ACC) = 111 111 000 000 then C(ACC) = 101 010 010 101

These instructions have a variety of applications, some of which will be demonstrated later.

#### 9. Special Index Register Instructions

Before continuing with the Index Class, two special instructions which facilitate programming with the Index Class instructions will be introduced. These instructions do not use the Index Registers to hold memory addresses; rather they deal directly with the Index Registers and are used to change or examine the contents of an Index Register.

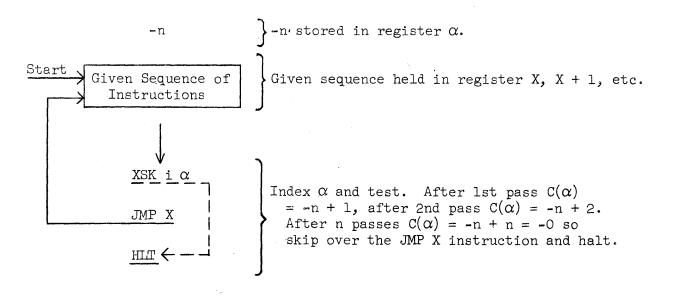

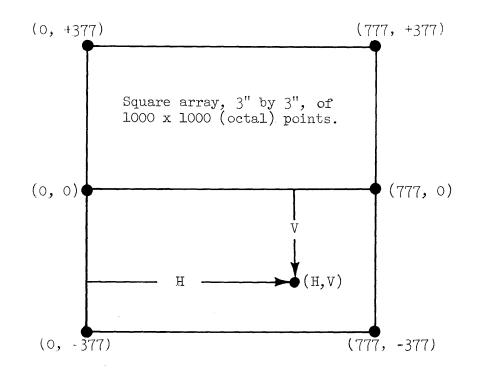

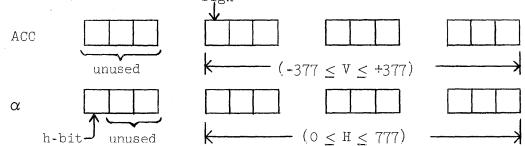

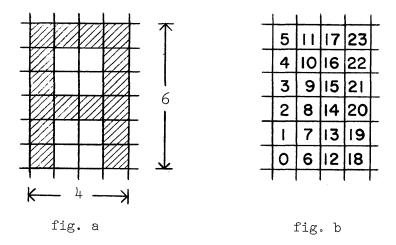

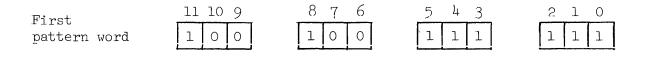

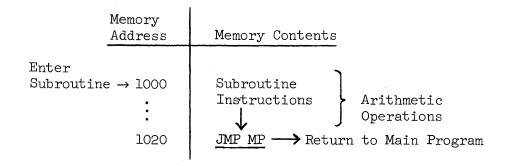

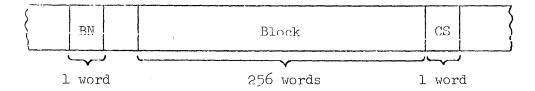

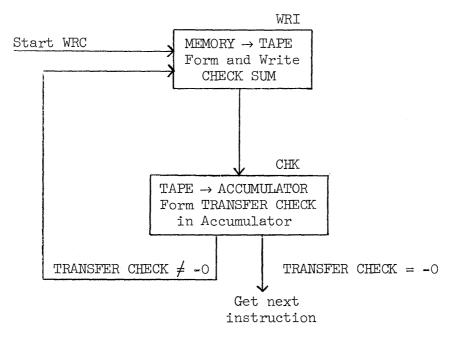

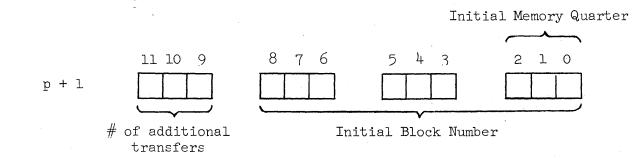

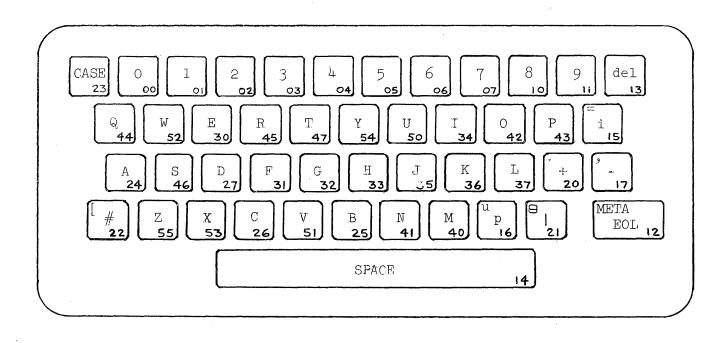

## The INDEX AND SKIP Instruction