# 4. Spot Programmer's Model

# 4.1 Memory Map

The following figure outlines the memory map of the WebTV™ system.

Figure 4-1 WebTV<sup>TM</sup> Memory Map

# 4.2 Registers

There are several registers located in the control space of SPOT (FIDO). These registers are oulined below. The 3-leter prefix before the register name indicates which unit within SPOT the register actually resides. The registers can be referred to with or without these 3-letter prefixes. NOTE: ALL REGISTERS ARE ONLY ACCESSIBLE AS ALIGNED WORDS (32-BITS).

Table 4-1 SPOT Registers

| Address                      | Register Name | Meaning                                | R/W           |

|------------------------------|---------------|----------------------------------------|---------------|

| 0x0400_0000                  | BUS_CHIPID    | SPOT chip ID                           | R-onl         |

| 0x0400_0004                  | BUS_CHPCNTL   | SPOT chip control register             | R/W           |

| 0x0400_0008                  | BUS_INTSTAT   | Interrupt status register              | R-onl         |

| 0x0400_000C                  | BUS_INTEN_S   | Interrupt enable register - set        | R/W           |

| 0x0400_0010                  | BUS_ERRSTAT   | Error status register                  | R-onl         |

| 0x0400_0014                  | BUS_ERREN_S   | Error enable register                  | R/W           |

| 0x0400_0018                  | BUS_ERRADDR   | Error address register                 | R-only        |

| 0x0400_001C                  | BUS_FENADDR1  | Fence lower bound 1 register           | R/W           |

| 0x0400_0020                  | BUS_FENMASK1  | Fence upper bound 1 register           | R/W           |

| 0x0400_0024                  | BUS_FENADDR2  | Fence lower bound 2 register           | R/W           |

| 0x0400_0028                  | BUS_FENMASK2  | Fence upper bound 2 register           | R/W           |

| 0x0400_002C -<br>0x0400_0108 | reserved      | reserved for future use w/i busUnit    | NA NA         |

| 0x0400_0108                  | BUS_INTSTAT_C | Interrupt status register - clear      | W and         |

| 0x0400_010C                  | BUS_INTEN C   | Interrupt-status-register - clear      | W-only        |

| 0x0400_0110                  | BUS_ERRSTAT_C | Error status register - clear          | W-only        |

| 0x0400_0114                  | BUS_ERREN C   | Error enable register - clear          | W-only        |

| 0x0400_0118                  | BUS_WDREG_C   | Reset watchdog register                | W-only        |

| 0x0400_0120 -<br>0x0400_0FFF | reserved      | reserved for future use                | W-only<br>NA  |

| 0x0400_1000                  | ROM_SYSCONF   | System Configuratrion                  | R-only        |

| 0x0400_1004                  | ROM_CNTL0     | ROM control register for Bank 0        | R/W           |

| 0x0400_1008                  | ROM_CNTL1     | ROM control register for Bank 1        | R/W           |

| 0x0400_1008 -<br>0x0400_1FFF | reserved      | reserved for future use                | NA NA         |

| 0x0400_2000                  | AUD_CSTART    | Audio DMA current buffer start address | R-only        |

| 0x0400_2004                  | AUD_CSIZE     | Audio DMA current buffer size          | -             |

| 0x0400_2008                  | AUD_CCONFIG   | Audio current channel configuration    | R-only<br>R/W |

| 0x0400_200C                  | AUD_CCNT      | Audio DMA current buffer index         | R-only        |

| 0x0400_2010                  | AUD_NSTART.   | Audio DMA next buffer start address    | R/W           |

| 0x0400_2014                  | AUD_NSIZE     | Audio DMA next buffer size             | R/W           |

| 0x0400_2018                  | AUD_NCONFIG   | Audio next channel configuration       | R/W           |

| x0400_201C                   | AUD_DMACNTL   | Audio DMA engine control               | R/W           |

| x0400_2020 -<br>x0400_2FFF   | reserved      | reserved for future use                | NA NA         |

| )x0400_3000                  | VID_CSTART    | Video DMA current buffer start address | R-only        |

| )x0400_3004                  | VID_CSIZE     |                                        |               |

| x0400_3008                   | VID_CCNT      | Video DMA current buffer index         | R-only        |

| x0400_300C                   | VID_NSTART    | Video DMA next buffer start address    |               |

| x0400_3010                   | VID_NSIZE     | Video DMA next buffer size             | R/W           |

| x0400_3014                   | VID_DMACNTL   | Video DMA engine control               | R/W           |

| _ |   |   |   |  |

|---|---|---|---|--|

|   | 3 | 5 | 5 |  |

| 0x0400_3018                  | VID_FCNTL                                    | Video general function control         | R/W        |

|------------------------------|----------------------------------------------|----------------------------------------|------------|

| 0x0400_301C                  | VID_BLNKCOL                                  | Blank color register                   | R/W        |

| 0x0400_3020                  | VID_HSTART Horizontal start of active pixels |                                        | R/W        |

| 0x0400_3024                  | VID_HSIZE                                    | Horizontal size of active pixels       | R/W        |

| 0x0400_3028                  | VID_VSTART                                   | Vertical start of active pixels        | R/W        |

| 0x0400_302c                  | VID_VSIZE                                    | Vertical size of active pixels         | R/W        |

| 0x0400_3030                  | VID_HINTLINE                                 | Horizontal line to interrupt on        | R/W        |

| 0x0400_3034                  | VID_CLINE                                    | Current line the vidUnit is displaying | R-on!      |

| 0x0400_3038                  | VID_INTSTAT                                  | Video interrupt status                 | R-onl      |

| 0x0400_303c                  | VID_INTEN_S                                  | Video interrupt enable - set           | R/W        |

| 0x0400_3040 -<br>0x0400_3130 | reserved                                     | reserved for future use w/i vidUnit    | NA NA      |

| 0x0400_3138                  | VID_INTSTAT_C                                | Video interrupt status - clear         | W-onl      |

| 0x0400_313c                  | VID_INTEN_C                                  | Video interrupt enable - clear         | W-on!      |

| 0x0400_3040 -<br>0x0400_3FFF | reserved                                     | reserved for future use                | NA.        |

| 0x0400_4000                  | DEV_IRDATA                                   | IR receiver data                       | R-onl      |

| 0x0400_4004                  | DEV_LED                                      | LED control register                   | R/W        |

| 0x0400_4008                  | DEV_IDCNTL                                   | ID chip control and data reigster      | R/W        |

| 0x0400_400c                  | DEV_NVCNTL                                   | NVRAM control and data register        | R/W        |

| 0x0400_4010                  | DEV_SCCNTL                                   | SmartCard control and data register    | R/W        |

| 0x0400_4014                  | DEV_EXTTIME                                  | External timing control register       | R/W        |

| 0x0400_4018 -<br>0x0400_401c | reserved                                     | reserved for future use                | NA         |

| 0x0400_4020 -<br>0x0400_403c | DEV_KBD0 -<br>DEV_KBD7                       | Keyboard registers (8)                 | R/W        |

| 0x0400_4040 -<br>0x0400_405c | DEV_MOD0 -<br>DEV_MOD7                       | Modem registers (8)                    | R/W        |

| 0x0400_403c -<br>0x0400_4FFF | reserved                                     | reserved for future use                | NA .       |

| 0x0400_5000                  | MEM_CNTL                                     | Memory control register                | R/W        |

| 0x0400_5004                  | MEM_REFCNT                                   |                                        |            |

| 0x0400_5008                  | MEM_DATA Memory data register                |                                        | R/W<br>R/W |

| 0x0400_500c                  | MEM_CMD Memory command register              |                                        | W-only     |

| 0x0400_5010                  | MEM_TIMING Memory Timing Register            |                                        | R/W        |

| 0x0400_5014 -<br>0x047F_FFFF | reserved                                     | reserved for future use                | NA NA      |

# 4.2.1 busUnit Registers

# 4.2.1.1 BUS\_CHIPID Register

This register can be read by software to determine the ID of the SPOT chip. All WebTV ASICS will have this register defined at the same location.

Table 4-2 BUS\_CHIPID Bit Definition

| Bits   | Symbol       | Meaning                                                                                                   |

|--------|--------------|-----------------------------------------------------------------------------------------------------------|

| 31:24  | CHIPID[7:0]  | Chip identification. See Appendix B for encoding                                                          |

| 23: 20 | CHIPREV[3:0] | Revision of silicon. Set to 0x0 in SPOT initially and increments on each revision.                        |

| 19: 16 | CHIPFAB[3:0] | Manufacturer of silicon. See Appendix B for encoding. SPOT will be done with ChipExpress initially (0x0). |

| 15:0   | RESERVED     | Reserved for future use.                                                                                  |

## 42.1.2 BUS\_CHPCNTL Register

This register controls variouis global chip functions such as reset watchdog timer, audio clock dividers, and time-out counts.

Table 4-3 BUS\_CHPCNTL Bit Definition

| Bits  | Symbol         | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:30 | WDENAB         | Writing a special sequence to this field will enable and disable the reset watchdog timer in the busUnit. To enable the watchdog counter, software must write the following sequence: 0b00 -> 0b01 -> 0b10 -> 0b11. To disable the watchdog counter, software must write the following sequence: 0b11-> 0b10 -> 0b01 -> 0b00. After reset this field will read back as 0b00. This watchdog timer will reset the system if 64 VSYNC's have elapsed before software writes the BUS_WDREC to reset the counter. |

| 29:26 | AUDCLKDIV[3:0] | Audio clock dividor. See table below for encoding. After reset, this field is set to 0x0.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 25:16 | RESERVED       | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15:0  | TOCOUNT[15:0]  | Timeout count value. This value in this field is compared against the time out counter. When the time out counter reaches this value an error ack is returned to the CPU on reads. On reset, this field is set to 0xFFFF.                                                                                                                                                                                                                                                                                    |

Table 4-4 AUDCLKDIV Encoding

| AUDCLKDIV[3:0]                          | Encoding                          |  |

|-----------------------------------------|-----------------------------------|--|

| 060000                                  | External clock source being used. |  |

| 060001                                  | Divide AUD_XTALI by I for AUD_CLK |  |

| 060010                                  | Divide AUD_XTALI by 2 for AUD_CLK |  |

| 060011                                  | Divide AUD_XTALI by 3 for AUD_CLK |  |

| 060100                                  | Divide AUD_XTALI by 4 for AUD_CLK |  |

| 0b0101 Divide AUD_XTALI by 5 for AUD_CL |                                   |  |

| 0b0110 Divide AUD_XTALI by 6 for AUD_C  |                                   |  |

| 0b0111 - 0b1111 Reserved for future use |                                   |  |

## 4.2.1.3 BUS\_INTSTAT Register

Spot Programmer's Model

This register provides most of the status of any interrupt generated from SPOT. Whenever an interrupt is detected by the enable being set and a device interrupting, SPOT will assert the CPU\_INT\_N signal and keep it asserted until the source of the interrupt is disabled.

Table 4-5

BUS\_INTSTAT Bit Definition

| Bits     | Symbol   | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:8     | RESERVED | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 7 VIDINT |          | When this bit is set to '1', a vidUnit interrupt has occurred due to any of the video interrupts occurring. The real video source needs to be obtained by reading the VID_INTSTAT register in the vidUnit. Clearing the interrupt is done by writing a '1' to the corresponding bit in the BUS_INTSTAT_C register. A clear must also be done to one of the bits in the VID_INTSTAT_C register for the interrupt to be completely cleared. |  |

| 6        | DEVKBD   | When this bit is set to 'l', a devUnit interrupt has occurred due to the external keyboard controller chip asserting its interrupt line Clearing the interrupt is done by writing a 'l' to the corresponding bit in the BUS_INTSTAT_C register.                                                                                                                                                                                           |  |

| 5        | DEVMOD   | When this bit is set to 'l', a devUnit interrupt has occurred due to the external modem controller chip asserting its interrupt line Clearing the interrupt is done by writing a 'l' to the corresponding bit in the BUS_INTSTAT_C register                                                                                                                                                                                               |  |

| 4        | DEVIR    | When this bit is set to 'l', a devUnit interrupt has occurred due to an IR interface data transfer being completed and ready for reading. Clearing the interrupt is done by writing a 'l' to the corresponding bit in the BUS_INTSTAT_C register.                                                                                                                                                                                         |  |

| 3        | DEVSMC   | When this bit is set to 'l', a devUnit interrupt has occurred due to a SmartCard being inserted Clearing the interrupt is done by writing a 'l' to the corresponding bit in the BUS_INTSTAT_C register.                                                                                                                                                                                                                                   |  |

| 2        | AUDDMA   | When this bit is set to '1', an audUnit interrupt has occurred due to the DMA completing. Clearing the interrupt is done by writing a '1' to the corresponding bit in the BUS_INTSTAT_C register.                                                                                                                                                                                                                                         |  |

| 1.0      | RESERVED | Reserved for future use. These bit s will read back as $\sigma$                                                                                                                                                                                                                                                                                                                                                                           |  |

## 4.2.1.4 BUS\_INTEN Register

This register (register pair) is used to enable and disable the global interrupts in the chip.

Table 4-6 BUS\_ INTEN Bit Definition

| Bits | Symbol                                                                                                                                                                                                                             | Meaning                                                                                                                                                                                                                                                                                               |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:8 | RESERVED                                                                                                                                                                                                                           | Reserved for future use.                                                                                                                                                                                                                                                                              |  |

| 7    | VIDEN                                                                                                                                                                                                                              | When '1', this bit enables video interrupts to pass through and be seen by the CPU. When '0', video interrups are disabled. Software must write a '1 to BUS_INTEN_S location to set the bit and write a '1' to the BUS_INTEN_C location to clear the bit. This bit is set to '0 after reset.          |  |

| 6    | DEVKBDEN                                                                                                                                                                                                                           | When '1', this bit enables keyboard interrupts to pass through and be seen by the CPU. When '0', keyboard interrups are disabled. Software must write a '1 to BUS_INTEN_S location to set the bit and write a '1' to the BUS_INTEN_C location to clear the bit. This bit is set to '0 after reset.    |  |

| 5    | DEVMODEN                                                                                                                                                                                                                           | When '1', this bit enables modem interrupts to pass through and be seen by the CPU. When '0', modem interrupts are disabled. Software must write a '1 to BUS_INTEN_S location to set the bit and write a '1' to the BUS_INTEN_C location to clear the bit. This bit is set to '0 after reset.         |  |

| 4    | DEVIREN  When '1', this bit enables IR interrupts and be seen by the CPU. When '0', IR disabled. Software must write a '1 to E location to set the bit and write a '1' to BUS_INTEN_C location to clear the bit to '0 after reset. |                                                                                                                                                                                                                                                                                                       |  |

| 3    | DEVSMCEN                                                                                                                                                                                                                           | When '1', this bit enables SmartCard interrupts to pass through and be seen by the CPU. When '0', SmartCard interrupts are disabled. Software must write a '1 to BUS_INTEN_S location to set the bit and write a '1' to the BUS_INTEN_C location to clear the bit. This bit is set to '0 after reset. |  |

| 2    | AUDDMAEN                                                                                                                                                                                                                           | When '1', this bit enables audio DMA interrupts to pass through and be seen by the CPU. When '0', audio DMA interrupts are disabled. Software must write a '1 to BUS_INTEN_S location to set the bit and write a '1' to the BUS_INTEN_C location to clear the bit. This bit is set to '0 after reset. |  |

| 1:0  | RESERVED                                                                                                                                                                                                                           | Reserved for future use.                                                                                                                                                                                                                                                                              |  |

## 4.2.1.5 BUS\_ERRSTAT Register

Spot Programmer's Model

This register (register pair) is used to get the status of the most recent error which occurred in the system. Note that internal DMA transactions which are sent to a non-present expansion device will completely hang the system. It is up to software to ensure this does not happen or upon detection of a DMA transaction which has not completed after a ridiculously long time to reset the system via the watchdog timer. This sort of error will not be detected and flagged in the hardware.

Copyright © 1995 Artemis Research Inc. All Rights Reserved. Confidential and Proprietary-Artemis Research Inc.

Table 4-7

BUS\_ERRSTAT Bit Definition

| Blts | Symbol                                                                                                                                                                                                | Meaning                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:5 | RESERVED                                                                                                                                                                                              | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                           |

| 6    | ack was due to a read fence check violation<br>fence register set 1 taking place in the system<br>reset, this bit is '0'. After detection, this bit in<br>cleared by writing a '1' to the BUS_ERRSTA' | When '1', this bit indicates that the most recent error ack was due to a read fence check violation between fence register set 1 taking place in the system. After reset, this bit is '0'. After detection, this bit must be cleared by writing a '1' to the BUS_ERRSTAT_C register in order to enable another error.                                                                                              |

| 5    | FIWRITE                                                                                                                                                                                               | When '1', this bit indicates that the most recent error ack was due to a write fence check violation between fence register set 1 taking place in the system. After reset, this bit is '0'. After detection, this bit must be cleared by writing a '1' to the BUS_ERRSTAT_C register in order to enable another error.                                                                                             |

| 4    | F2READ                                                                                                                                                                                                | When '1', this bit indicates that the most recent error ack was due to a read fence check violation between fence register set 2 taking place in the system. After reset, this bit is '0'. After detection, this bit must be cleared by writing a '1' to the BUS_ERRSTAT_C register in order to enable another error.                                                                                              |

| 3    | F2WRITE                                                                                                                                                                                               | When '1', this bit indicates that the most recent error ack was due to a write fence check violation betweer fence register set 2 taking place in the system. After reset, this bit is '0'. After detection, this bit must be cleared by writing a '1' to the BUS_ERRSTAT_C register in order to enable another error.                                                                                             |

| 2    | TIMEOUT                                                                                                                                                                                               | When '1', this bit indicates that the most recent error ack was due to a timeout taking place in the system. Read timeouts are synchronous, write timeouts are asynchronous. The write timeouts are flagged in conjunction with the BUS_INTSTAT register. After reset, this bit is '0'. After detection, this bit must be cleared by writing a '1' to the BUS_ERRSTAT_C register in order to enable another error. |

| 1    | RESERVED                                                                                                                                                                                              | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                           |

| 0    | 0 OW When 'I', this bit indicates that another before the first could be serviced by the                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### 42.1.6 BUS\_ERREN Register

This register (register pair) is used to enable the various error-checking mechanisms in hardware.

Table 4-8 BUS\_ERREN Bit Definition

| Bits | Symbol   | Meaning                                                                                                      |

|------|----------|--------------------------------------------------------------------------------------------------------------|

| 31:5 | RESERVED | Reserved for future use.                                                                                     |

| 6    | FIRDEN   | When '1', this bit indicates read errors on fence register set 1 are enabled. After reset, this bit is '0'.  |

| 5    | FIWREN   | When '1', this bit indicates write errors on fence register set 1 are enabled. After reset, this bit is '0'. |

| 4    | F2RDEN   | When '1', this bit indicates read errors on fence register set 1 are enabled. After reset, this bit is '0'.  |

| 3    | F2WREN   | When '1', this bit indicates write errors on fence register set 2 are enabled. After reset, this bit is '0'. |

| 2    | TIMEEN   | When '1', this bit indicates tiem-outs on the bus are enabled. After reset, this bit is '0'.                 |

| 1:0  | RESERVED | Reserved for future use.                                                                                     |

#### 42.1.7 BUS\_ERRADDR Register

Spot Programmer's Model

This register is used to flag the address which encountered an error.

Table 4-9 BUS\_ERRADDR Bit Definition

| Bits | Symbol     | Meaning                                                                                                                                      |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | ADDR[31:0] | This field captures the most recent address which caused the error flagged in the BUS_ERRSTAT register. After reset this field is undefined. |

#### 4.2.1.8 BUS\_WDREG\_C Register

Software must whack this register before 64 VSYNC's elapse once the watchdog counter is enabled or else the system will hard reset.

Table 4-10 BUS\_WDREG\_C Bit Definition

| Bits | Bits Symbol Meanin |                                                                                                                                              |

|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | RESERVED           | Reserved for future use.                                                                                                                     |

| 0    | WDCLEAR            | Reserved for future use:  Writing a '1' to this field resets the watchdog counter Writing a '0' has no effect. This register cannot be read. |

## 4.2.1.9 BUS\_FENADDR1 Register

This register is used to hold the address value of the lower bounds on a fence check reigster pair. Note that only main memory address space is checked.

Table 4-11 BUS\_ FENADDR1 Bit Definition

| Bits  | Symbol     | Meaning .                                                                                                                                                                                                                                                                  |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RESERVED   | Reserved for future use.                                                                                                                                                                                                                                                   |

| 23:5  | ADDR[23:5] | This field contains the address of the lower bound which the busUnit checks all main memory CPU accesses against for register set 1. After reset, this register is undefined and must be initialized prior to enabling fence checking or unpredictable results will occur. |

#### 42.1.10 BUS\_FENMASK1 Register

This register is used to hold the mask for FENADDR1.

Table 4-12 BUS\_ FENMASK1 Bit Definition

| Bits  | Symbol     | Meaning                                                                                  |

|-------|------------|------------------------------------------------------------------------------------------|

| 31:24 | RESERVED   | Reserved for future use.                                                                 |

| 23:5  | MASK[23:5] | Fence check equation:                                                                    |

|       |            | ~l(addr[31:24], addr[23:21]^fenAddr[23:21],<br>(addr[20:5]^fenAddr[20:5])&fenMask[23:5]) |

#### 42.1.11 BUS\_FENADDR2 Register

This register is used to hold the address value of the lower bounds on a fence check reigster pair. Note that only main memory address space is checked.

Table 4-13 BUS\_ FENADDR2 Bit Definition

| Bits  | Symbol     | Meaning                                                                                                                                                                                                                                                                 |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RESERVED   | Reserved for future use.                                                                                                                                                                                                                                                |

| 23:5  | ADDR[23:5] | This field contains the address of the lower bound which the busUnit checks all main memory CPU accesses against for register set 2. After reset, this register is undefined and must be initialized prior to enabling fence checking or unpredictable results w occur. |

#### 42.1.12 BUS\_FENMASK2 Register

This register is used to hold the mask for FENADDR2.

#### Table 4-14 BUS\_ FENMASK2 Bit Definition

| Bits  | Symbol     | Meaning                                                                                                      |

|-------|------------|--------------------------------------------------------------------------------------------------------------|

| 31;24 | RESERVED   | Reserved for future use.                                                                                     |

| 23:5  | MASK[23:5] | Fence check equation: ~[(addr[31:24], addr[23:21]^fenAddr[23:21], (addr[20:5])^fenAddr[20:5])&fenMask[23:5]) |

#### 4.2.2 romUnit Register

## 4.2.2.1 ROM\_SYSCONFIG Register

Spot Programmer's Model

This register is used to flag system configuration information to both software as well as hardware. Some of these bits are used to program the SPOT chip directly. Most are used so software can configure the hardware properly. This register is actually the ROM\_DATA[31:0] bus value which is captured when reset goes away. Software is expected to figure out the system (CPU) clock frequency by using veritcal interrupts and the NTSC bit.

| Bits   | Symbol         | Meaning                                                                                                                                                                                                                                                                                                                                        |

|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Symbol         |                                                                                                                                                                                                                                                                                                                                                |

| 31     | ROMTYP0        | When '1', this bit means there is mask ROM present<br>in the system for Bank 0 ROM space. If '0', then<br>Flash ROM is present.                                                                                                                                                                                                                |

| 30     | ROMMODE0       | When '1', this bit means the memory devices in ROM Bank 0 support page mode. When '0', no page mode us supported.                                                                                                                                                                                                                              |

| 29: 28 | ROMSPD0[1:0]   | This field indicates the speed of the ROM present in bank 0 of ROM space. See tables below for encoding.                                                                                                                                                                                                                                       |

| 27     | ROMTYPI        | When '1', this bit means there is mask ROM present<br>in the system for Bank 1 ROM space. If '0', then<br>Flash ROM is present.                                                                                                                                                                                                                |

| 26     | ROMMODEI       | When '1', this bit means the memory devices in ROM Bank 1 support page mode. When '0', no page mode us supported.                                                                                                                                                                                                                              |

| 25: 24 | ROMSPD1[1:0]   | This field indicates the speed of the ROM present in bank 1 of ROM space. See tables below for encoding.                                                                                                                                                                                                                                       |

| 23: 22 | MEMSPD[1:0]    | This field indicates the speed of the memory present in the system. See tables below for encoding.                                                                                                                                                                                                                                             |

| 21:20  | MEMVEND[1:0]   | This field indicates the particular SGRAM present in the system. Note that vendors canot be intermixed. See tables below for encoding.                                                                                                                                                                                                         |

| 19: 18 | AUDDACTYP[1:0] | This field indicates the type of audio DAC present in the system. See tables below for encoding.                                                                                                                                                                                                                                               |

| 17     | AUDDACMODE     | A '1' in this field indicates the clock for the audio DAC originates external to the SPOT chip, and the AUD_CLK pin is configured as an input. A '0' indicates the AUDCLKDIV field of the BUS_CHPCNTL register is used to control by what value SPOT uses to divide the AUD_XTALI input by in order to then drive the AUD_CLK pin on the chip. |

| 16     | VIDCLKSRC      | A '0' in this field indicates the clock for the video encoder originates external to the SPOT chip, and the VID_PIXCLK and VID_PIX2XCLK pins are configured as inputs. A '1' indicates the video clocks originate from the SPOT chip. They are divided down from the VID_4XXTALI input.                                                        |

| 15:14  | CPUMULT[1:0]   | This field indicates the clock multiplier which should<br>be programmed into the CPU upon reset. During reset<br>these values are sent to the CPU so it can configure<br>its internal PLL to use the clock multiplier outlined in<br>the table below.                                                                                          |

| 13     | CPUBUFF        | When '1', this field tells the SPOT CPU reset logic to configure the CPU's output buffers to 50% strength. A '0' indicates to configure to 83%. NOTE: double-check.                                                                                                                                                                            |

| 12     | RESERVED       | Reserved for future use.                                                                                                                                                                                                                                                                                                                       |

| 11     | NTSC           | A 'I' in this field indicates the system is configured fo<br>NTSC mode, and a 12.27MHz pixel clock A '0'<br>indicates PAL mode and a 14.75MHz pixel clock.                                                                                                                                                                                     |

| 10:8   | RESERVED       | Reserved for future use.                                                                                                                                                                                                                                                                                                                       |

| 7:4    | BRDREV[3:0]    | This field indicates the revision of the board type. The revision field starts at 0b1111 and counts down.                                                                                                                                                                                                                                      |

| S | P | O' | T | Chi | p S | pecification | - | Rev | 0.5 |  |

|---|---|----|---|-----|-----|--------------|---|-----|-----|--|

|---|---|----|---|-----|-----|--------------|---|-----|-----|--|

44

| 3:2 |          | This field indicates the board type. See tables below for encoding. |

|-----|----------|---------------------------------------------------------------------|

| 1:0 | RESERVED | Reserved for future use                                             |

Following are the encoding tables of the fields in the previous table.

Table 4-16 ROMSPDx Encoding

| ROMSPDx[1:0] | Encoding (Initial Access/Page Access) |

|--------------|---------------------------------------|

| 0600         | 200ns/100ns                           |

| 0601         | 100ns/50ns                            |

| 0b10         | 90ns/45ns                             |

| 0611         | 120ns/60ns                            |

Table 4-17 MEMSPD Encoding

| MEMSPD[1:0] | Encoding     |

|-------------|--------------|

| 0600        | 100MHz parts |

| 0601        | 66MHz parts  |

| 0610        | 77MHz parts  |

| 0611        | 83MHz parts  |

#### MEMVEND Encoding

| MEMVEND[1:0] | Encoding  |

|--------------|-----------|

| 0600         | Other     |

| 0601         | Samsung   |

| 0ь10         | · Fujitsu |

| 0611         | NEC       |

Table 4-18 AUDDACTYP Encoding

| AUDDACTYP[1:0] | Encoding .    |

|----------------|---------------|

| 0b00 - 0b10    | reserved      |

| . Ob11         | AKM 4310/4309 |

#### CPUMULT Encoding

| CPUMULT[1:0] | Encoding                 |

|--------------|--------------------------|

| 0600         | CPU clock = 5X bus clock |

| 0601         | CPU clock = 4X bus clock |

| 0610         | CPU clock = 2X bus clock |

| 0b11         | CPU clock = 3X bus clock |

Table 4-19 BRDTYP Encoding

| BRDTYP [1:0] | Encoding         |

|--------------|------------------|

| 0600 - 0601  | reserved         |

| 0ь10         | Trial-type board |

| 0611         | FCS board        |

## 4222 ROM\_CNTL0 Register

This register is used to program the state machine which accesses the ROM bank 0 parts in the system. Software should set this register after querying the ROM\_SYSCONFIG register.

# SPOT Chip Specification - Rev 0.5

46

#### Table 4-20 ROM\_CNTL0 Bit Definition

| Bits  | Symbol        | Meaning                                                                                                                                                                                                                                                              |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | ROMPAGE       | When 'I', this bit indicates ROM bank contains page-<br>mode ROMs. If '0', the romUnit state machine<br>decoding ROM bank will use INITWAIT field for all<br>accesses. After reset, this bit is '0'.                                                                 |

| 30:29 | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 28:24 | PAGEWAIT[4:0] | This field indicates how many clock cycles the state machine controlling ROM bank should wait between page mode accesses before latching data. After reset, this field contains 0b11111.                                                                             |

| 23:21 | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 20:16 | INITWAIT[4:0] | This field indicates how many clock cycles the state machine controlling ROM bank should wait on the initial access before latching data. After reset, this field contains 0b11111.                                                                                  |

| 15    | RESERVED      | Reserved for future use.                                                                                                                                                                                                                                             |

| 14:12 | CEDEL[2:0]    | This field indicates how many clock cycles the state machine controlling ROM bank should deassert CE for between accesses. After reset, this field contains 0b111.                                                                                                   |

| 11:10 | RESERVED      | Reserved for future use.,                                                                                                                                                                                                                                            |

| 9:8   | WEDEL[1:0]    | This field indicates how many clock cycles the state machine controlling ROM bank should wait after ROM_CE_N's assertion to assert ROM_WE_N. After reset, this field contains 0b11.                                                                                  |

| 7:4   | RESERVED      | Reserved for future use.                                                                                                                                                                                                                                             |

| 3:0   | WETIME0[3:0]  | This field indicates how many clock cycles the state machine controlling ROM bank should assert ROM_WE_N for during a write to bank. After reset, this field contains 0b1111. Note that software should never program WEDELx + WETIMEx to be greater than INITWAITx. |

## 4.2.2.3 ROM\_CNTL1 Register

Spot Programmer's Model

This register is used to program the state machine which accesses the ROM bank 1 parts in the system. Software should set this register after querying the ROM\_SYSCONFIG register.

| Bits  | Symbol        | Meaning                                                                                                                                                                                                                                                              |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | ROMPAGE       | When '1', this bit indicates ROM bank contains page-<br>mode ROMs. If '0', the romUnit state machine<br>decoding ROM bank will use INITWAIT field for all<br>accesses. After reset, this bit is '0'.                                                                 |

| 30:29 | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 28:24 | PAGEWAIT[4:0] | This field indicates how many clock cycles the state machine controlling ROM bank should wait between page mode accesses before latching data. After reset this field contains 0b11111.                                                                              |

| 23:21 | RESERVED      | Reserved for future use.                                                                                                                                                                                                                                             |

| 20:16 | INITWAIT[4:0] | This field indicates how many clock cycles the state machine controlling ROM bank should wait on the initial access before latching data. After reset, this field contains 0b11111.                                                                                  |

| 15    | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 14:12 | CEDEL[2:0]    | This field indicates how many clock cycles the state machine controlling ROM bank should deassert CE for between accesses. After reset, this field contains 0b111.                                                                                                   |

| 11:10 | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 9:8   | WEDEL[1:0]    | This field indicates how many clock cycles the state machine controlling ROM bank should wait after ROM_CE_N's assertion to assert ROM_WE_N. After reset, this field contains 0b11.                                                                                  |

| 7:4   | RESERVED      | Reserved for future use                                                                                                                                                                                                                                              |

| 3:0   | WETIME0[3:0]  | This field indicates how many clock cycles the state machine controlling ROM bank should assert ROM_WE N for during a write to bank. After reset, this field contains 0b1111. Note that software should never program WEDELx + WETIMEx to be greater than INITWAITx. |

#### 4.2.3 audUnit Registers

#### 4.2.3.1 AUD\_CSTART Register

This register is used to set and view the starting byte address of the currently executing DMA transfer.

Table 4-22 AUD\_CSTART Bit Definition

| Bits  | Symbol      | Meaning                                                                               |

|-------|-------------|---------------------------------------------------------------------------------------|

| 31:26 | RESERVED    | Reserved for future use,                                                              |

| 25:0  | CADDR[25:0] | This field reflects the value of the starting address of the current DMA transaction. |

# 4232 AUD\_CSIZE Register

This register is used to set and view the size of the curently executing DMA transfer. Note that audio DMA transfers can only be up to 64KB.

# SPOT Chip Specification - Rev 0.5

48

## Copyright © 1995 Artemis Research Inc. All Rights Reserved. Confidential and Proprietary—Artemis Research Inc.

# Spot Programmer's Model

Hardware Engineering

Table 4-23 AUD\_C

AUD\_CSIZE Bit Definition

| Bits   | Symbol      | Meaning                                                                   |

|--------|-------------|---------------------------------------------------------------------------|

| 31:16  | RESERVED    | Reserved for future use.                                                  |

| 15:0 - | CSIZE[15:0] | This field reflects the value of the size of the current DMA transaction. |

## 4233 AUD\_CCONFIG Register

This register is used to control the sample sizes and mono vs. stereo in the currently executing audio DMA channel.

Table 4-24

AUD\_CCONFIG Bit Definition

| Bits | Symbol   | Meaning                                                                                                                                                        |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:2 | RESERVED | Reserved for future use.                                                                                                                                       |

| 1    | 8BIT     | When '1', this bit indicates the audio samples should<br>be 8-bit. When '0', 16-bit samples are used. After<br>reset, this bit is undefined.                   |

| 0    | MONO     | When '1', this bit indicates mono samples should be used. When '0', stereo samples are being used in the audio DMA channel. After reset, this bit is undefined |

#### 4.2.3.4 AUD\_CCNT Register

This register is used to to view the (byte) count of the curently executing DMA transfer

Table 4-25 AUD\_CCNT Bit Definition

| Bits   | Symbol     | Meaning                                                                                                                                                             |

|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31; 16 | RESERVED   | Reserved for future use.                                                                                                                                            |

| 15:0   | CCNT[15:0] | This field reflects the value of the index count of the current DMA transaction. Software can determine how far along the DMA transfer is by reading this register. |

## 4235 AUD\_NSTART Register

This register is used to read and write the starting address of the next DMA transfer.

Table 4-26 AUD\_NSTART Bit Definition

| Bits  | Symbol      | Meaning                                                                            |

|-------|-------------|------------------------------------------------------------------------------------|

| 30:26 | RESERVED    | Reserved for future use.                                                           |

| 25:0  | NADDR[25:0] | This field reflects the value of the starting address of the next DMA transaction. |

#### 4.2.3.6 AUD\_NSIZE Register

This register is used to to read and write the size of the next DMA transfer.

Table 4-27 AUD\_NSIZE Bit Definition

| Bits  | Symbol      | Meaning                                                                |

|-------|-------------|------------------------------------------------------------------------|

| 31:16 | RESERVED    | Reserved for future use.                                               |

| 15:0  | NSIZE[15:0] | This field reflects the value of the size of the next DMA transaction. |

#### 4.23.7 AUD\_NCONFIG Register

This register is used to control the sample sizes and mono vs. stereo in the "next" executing audio DMA channel.

Table 4-28 AUD\_NCONFIG Bit Definition

| Bits | Symbol   | Meaning                                                                                                                                                              |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:2 | RESERVED | Reserved for future use.                                                                                                                                             |

| 1    | 8BIT     | When '1', this bit indicates the audio samples should<br>be 8-bit. When '0', 16-bit samples are used. After<br>reset, this bit is undefined.                         |

| ()   | MONO     | When '1', this bit indicates mono samples should be<br>used. When '0', stereo samples are being used in the<br>audio DMA channel. After reset, this bit is undefined |

#### 4.2.3.8 AUD\_DMACNTL Register

This register is used to control the audio DMA channel.

Table 4-29 AUD\_DMACNTL Bit Definition

| Bits | Symbol   | Meaning                                                                                                                                                                                                                                    |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:3 | RESERVED | Reserved for future use.                                                                                                                                                                                                                   |

| 2    | DMAEN    | When 'I', this bit indicates the DMA channel is enabled. When '0', the DMA channel is disabled.  After reset this bit is '0'. A '1' to '0' transition on this bit will flush the current DMA transaction (i.e. the channel will be reset). |

| 1    | NV       | When '1', this bit indicates the NSTART and NSIZE registers are valid. Software should first set up the "next" registers, then enable the NV bit, and finally set the DMAEN bit in order to start the DMA channel                          |

| 0    | NVF      | When 'I', this bit indicates the NV should stay valid<br>forever. This allows software to have a continuous<br>loop on a buffer such as an audio sample.                                                                                   |

#### 4.2.4 vidUnit Registers

#### 4.2.4.1 vidUnit Programming Overview

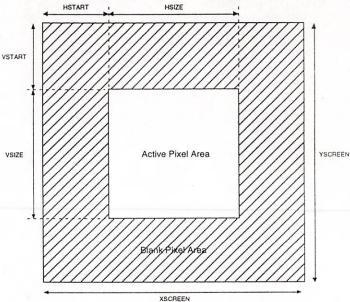

The vidUnit in SPOT can drive both interlace and non-interlace NTSC or PAL displays. There are several registers which control the various features of the vidUnit plus control the actual frame being displayed on the screen. Both the horizontal and veritical resolution of the video display are programmable. The picture below outlines several vidUnit parameters which are key to understanding how the video display operates.

#### SPOT Chip Specification - Rev 0.5

50

Copyright © 1995 Artemis Research Inc. All Rights Reserved. Confidential and Proprietary-Artemis Research Inc.

# Figure 4-1 Video Display Overview

The vidUnit is basically a DMA engine which reads the frame buffer from main memory and displays to the screen. A TV has a resolution of 'X' pixels by 'Y' lines. For NTSC, X=640 and Y=480, but not all of these pixels are visible since they are in the blank time or in the overscan region of the TV. SPOT allows software to position the active window anywhere onto the overall X and Y coordinates of the TV such that all pixels will be guaranteed to be visible. This is done by programming the HSTART, HSIZE, VSTART, and VSIZE registers in SPOT. As long as the DMA size is set exactly to the size of the active pixel area, the vidUnit will continuously display the frame buffer to the TV each field (for interlace) or each frame (for non-interlace).

There is a definite sequence of events software must follow in order to enable video. The rules are outlined below:

#### Non-Interlace Video

Spot Programmer's Model

- 1) Set up the DMA registers VID\_NSTART and VID\_NSIZE. NSIZE must be set to: (HSIZE\*VSIZE)\*2

- Set the NV and NVF bits of the VID\_DMACNTL register. Make sure the INTERLACEEN bit of this register is set to '0'.

- 3) Set the DMAEN bit of the VID\_DMACNTL register

- 4) Set the HSTART, HSIZE, VSTART, and VSIZE registers. HSTART must be a multiple of '2'. HSIZE must be a multiple of 8 pixels (4 words). Make sure enough time has elapsed to allow the DMA engine to pre-load the video pixel buffer. This will be approximately 100 system clock cycles.

Table 4-36 VID\_DMACNTL Bit Definition

| Bits | Symbol         | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:4 | RESERVED       | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3    | DMAINTERLACEEN | When '1', this bit indicates the DMA channel will<br>support interlaced video depending on the value of<br>HSIZE and VSIZE. When '0', the DMA channel<br>supports non-interlace mode. After reset this bit is '0'.                                                                                                                                                                                                                                                                                                                 |

| 2    | DMAEN          | When '1', this bit indicates the DMA channel is enabled. When '0', the DMA channel is disabled. After reset this bit is '0'. A '1' to '0' transition on this bit will flush the current DMA transaction (i.e. the channel will be reset).                                                                                                                                                                                                                                                                                          |

| 1    | NV             | When '1', this bit indicates the NSTART and NSIZE registers are valid. Software should first set up the "next" registers, then enable the NV bit, and finally set the DMAEN bit in order to start the DMA channel. When shutting down DMA, SW must first turn off the display and wait for 2 VSYNC's to elapse before then shutting down DMA. For SPOT1, this bit really has no meaning as far as chaining is concerned. Once video has been enabled, the DMA engine will continue reloading regardless of the NV or NVF bits. :-) |

| 0    | NVF            | When 'I', this bit indicates the NV should stay valid<br>forever. This allows software to have a continuous<br>loop on a buffer such as a video frame.                                                                                                                                                                                                                                                                                                                                                                             |

## 42.4.9 VID\_FCNTL Register

This register is used to control miscellaneous modes of the video DMA channel.

# Table 4-37 VID\_FCNTL Bit Definition

| Bits | Symbol     | Meaning                                                                                                                                                                                                                                                                                                                                                                  |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RESERVED   | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                 |

| 7    | UVSELSWAP  | When '1', this bit indicates that the vidUnit will<br>support YCbYCr pixel format when using a Bt851<br>video encoder in the system. When '0', YCrYCb<br>format is supported for this video encoder.                                                                                                                                                                     |

| 6    | CRCBINVERT | When '1', this bit indicates that the vidUnit should<br>invert the MSB of Cr and Cb values coming from<br>memory before passing on to the video encoder. After<br>reset this bit is '0'.                                                                                                                                                                                 |

| 5    | FIDO       | When '1', this bit indicates the vidUnit should be in "FIDO" mode. After reset this bit is '0'. FIDO mode is TBD. (Beth will fill in here).                                                                                                                                                                                                                              |

| 4    | GAMMA      | When 'l', this bit indicates gamma correction should<br>be done to all pixels passing through the unit. A '0'<br>disables gamma correction.                                                                                                                                                                                                                              |

| 3    | BLNKCOLEN  | When '1', this bit indicates the blank color register<br>should be enabled on the output during "blank" times<br>instead of just asserting the VID_BLANK signal and<br>getting black output. After reset this bit is '0'.                                                                                                                                                |

| 2    | INTERLACE  | When '1', this bit indicates the vidUnit is configured for interlace mode. This bit is also reflected out on the VID_CNTL[0] signal of the chip. This signal should be connected to the INTERLACE pin on the video encoder. After reset, this bit is '0'.                                                                                                                |

| 1    | PAL        | When '1', this bit indicates the vidUnit is configured for PAL mode. This bit is also reflected out on the VID_CNTL[1] signal of the chip. This signal should be connected to the PAL pin on the video encoder. After reset, this bit is initialized with the value of the inverted bit in the ROM_SYSCONFIG register. It can be overwritten after reset with any value. |

| 0    | VIDENAB    | When '1', this bit indicates the video subsystem should start displaying screens. Video is is either disabled or the color values contained in the VID_BLNKCOL register are displated during pixel times if BLNKCOLEN is '1' when VIDENAB is '0'. The DMA channel needs to be set up prior to the VIDENAB bit being set. After reset this bit is '0'.                    |

## 4.2.4.10 VID\_BLNKCOL Register

SPOT Chip Specification - Rev 0.5

Spot Programmer's Model

This register is used to set the default color value to be displayed if this feature is enabled.

54

Table 4-38 VID\_BLNKCOL Bit Definition

| Bits   | Symbol   | Meaning                                                     |

|--------|----------|-------------------------------------------------------------|

| 31:24  | RESERVED | Reserved for future use.                                    |

| 23: 16 | YCOL     | Y value to be displayed for each pixel during blank times.  |

| 15:8   | CRCOL    | Cr value to be displayed for each pixel during blank times. |

| 7:0    | CBCOL    | Cb value to be displayed for each pixel during blank times. |

#### 42.4.11 VID\_HSTART Register

This register is used to set the horizontal starting position of active pixels on the screen. The value in this register plus the values in the HSIZE, VSTART, and VSIZE need to match the appropriate DMA buffer size that software must set up (i.e. hardware does not check that all values jive).

Table 4-39 VID\_HSTART Bit Definition

| Bits  | Symbol      | Meaning                                                                                                                                                                                                                                                                                    |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:10 | RESERVED    | Reserved for future use,                                                                                                                                                                                                                                                                   |

| 9:0   | HSTART[9:0] | This field reflects the horizontal starting pixel out of the possible 640 (NTSC) or 768 (PAL). Must start on an even boundary (i.e. multiple of '2'). Note that this value counts '0'. Thus, if '2' is put in this register then the active display will start on the 3rd pixel (0, 1, 2). |

## 4.2.4.12 VID\_HSIZE Register

This register is used to set the horizontal pixel size of the screen.

Table 4-40 VID\_HSIZE Bit Definition

| Bits  | Symbol     | Meaning                                                                                                                                                                                                                                                                                                |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|