# WESTERN DIGITAL MCP-1600 MICROPROCESSOR SYSTEM

# MCP-1600 MICROPROCESSOR USERS MANUAL

3128 RED HILL AVENUE P.O. BOX 2180 NEWPORT BEACH, CALIFORNIA 92663 TELEPHONE: 714-557-3550 TWX: 910-595-1139

# TABLE OF CONTENTS

| Paragraph | TABLE OF CONTENTS                             | Page  |

|-----------|-----------------------------------------------|-------|

|           | SECTION I, GENERAL SYSTEM CONFIGURATION       |       |

| 1,1       | General                                       | . 1-1 |

| 1.2       | Unique Features of the MCP1600                |       |

| 1.3       | Areas of Application                          |       |

| 1.4       | Block Diagram                                 |       |

| 1.7       | SECTION II, SYSTEM COMPONENTS                 | . 1-2 |

| 0.4       |                                               | 0.1   |

| 2.1       | General                                       | . 2-1 |

| 2.2       | Registers                                     | . 2-1 |

| 2.3       | Instruction Address Generation                |       |

| 2.4       | Microinstruction Bus                          |       |

| 2.5       | Data Access                                   | . 2-4 |

| 2.6       | Microinstruction Storage                      | . 2-5 |

|           | SECTION III, CPU OPERATIONS                   |       |

| 3.1       | General                                       | . 3-1 |

| 3.2       | CPU Operations                                | . 3-2 |

| 3.3       | Control Lines                                 |       |

| 3.3.1     | Register Load                                 |       |

| 3.3.2     | Load Flags                                    |       |

| 3.3.3     | Load High Byte                                |       |

| 3.3.4     | Load Lo Byte                                  |       |

| 3.3.5     |                                               |       |

|           | Modify Lo                                     |       |

| 3.3.6     | Modify Hi                                     |       |

| 3.3.7     | JXX                                           |       |

| 3.3.8     | Load Literal                                  |       |

| 3.3.9     | Double/Single                                 |       |

| 3.3.10    | Load TR                                       | . 3-8 |

|           | SECTION IV, PROGRAMMABLE TRANSLATION ARRAY    |       |

| 4.1       | General                                       | . 4-1 |

| 4.2       | PTA Components                                |       |

| 4.2.1     | Location Counter                              | . 4-2 |

| 4.2.2     | Array #1                                      | . 4-2 |

| 4.2.3     | Array #2                                      | . 4-3 |

| 4.2.4     | Array #3                                      | . 4-6 |

| 4.2.5     | Array #4                                      |       |

| 4.2.6     | Translation State Register                    |       |

| 4.2.7     | Translation Register                          |       |

| 4.3       | Programmable Translation Array Operations     |       |

|           | SECTION V, MICROINSTRUCTIONS                  |       |

| 5.1       | Instruction Repertoire                        | F. 1  |

|           | · · · · · · · · · · · · · · · · · · ·         |       |

| 5.2       | Instruction Types                             |       |

| 5.3       | MCP 1600 Micro-Instruction Set                |       |

| 5.3.1     | Table of Microinstructions                    |       |

| 5.3.2     | Summary of Micro-Instruction and Status Flags | . 5-8 |

|           | SECTION VI, MICROINSTRUCTION BUS OPERATION    |       |

| 6.1       | General                                       |       |

| 6.2       | Micro-Instruction Bus Operation               |       |

| 6.3       | Micro-Instruction Bus Element Description     | . 6-2 |

# TABLE OF CONTENTS (con't.)

| F | aragraph                                                                                              |                                 |             | Page                                                                                                                      |

|---|-------------------------------------------------------------------------------------------------------|---------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                       | SECTION VI, (con't.)            |             |                                                                                                                           |

|   | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.3.7<br>6.4<br>6.5                             | MIB00 - MIB10                   |             | . 6-3<br>. 6-3<br>. 6-3<br>. 6-3<br>. 6-4<br>. 6-4                                                                        |

|   | 6.6                                                                                                   | Micro-Instruction ROM           |             |                                                                                                                           |

|   |                                                                                                       |                                 |             |                                                                                                                           |

|   |                                                                                                       | SECTION VII, DATA ACCESS        | <b>&gt;</b> |                                                                                                                           |

|   | 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.2.5 7.3 7.4 7.5 7.5.1 7.5.2 7.5.3 7.6 7.6.1 7.6.1.1 7.6.1.2 7.6.1.3 | Read Instructions               |             | . 7-1<br>. 7-3<br>. 7-4<br>. 7-6<br>. 7-9<br>. 7-11<br>. 7-12<br>. 7-13<br>. 7-13<br>. 7-13<br>. 7-13<br>. 7-14<br>. 7-14 |

|   |                                                                                                       | SECTION VIII, ELECTRICAL SPECIF |             |                                                                                                                           |

|   | 8.1<br>8.2<br>8.3<br>8.4                                                                              | General                         |             | . 8-1<br>. 8-6                                                                                                            |

|   |                                                                                                       | SECTION IX, PIN ASSIGNMEN       | ITS         |                                                                                                                           |

|   | 9.1                                                                                                   | General                         |             | . 9-1                                                                                                                     |

|   |                                                                                                       |                                 |             |                                                                                                                           |

# **ILLUSTRATIONS**

| Figure No.             |                                             | Page No. |

|------------------------|---------------------------------------------|----------|

| 1-1                    | MCP1600 Microprocessor Block Diagram        | . 1-2    |

| 1-2                    | Simple Microprocessor System                | . 1-3    |

| 2-1                    | Register File                               |          |

| 3-1                    | Ø1 Data Paths                               |          |

| 3-2                    | Ø2 Data Paths                               |          |

| 3-3                    | Ø3 Data Paths                               |          |

| 3-4                    | Ø4 Data Paths                               |          |

| 3-5                    | Ø4 Data Paths, Second Cycle                 |          |

| 3-6                    | Major Control Lines                         |          |

| 4-1                    | PTA Component Interconnections              |          |

| 4-2                    | Array #1 Organization                       |          |

| 4-3                    | Typical Gate - Array #1                     |          |

| 4-4                    | Array #1 Data Specification                 |          |

| 4-5                    | Array #2 Organization                       |          |

| 4-6                    | Array #2 Gate and Interconnect Structure    |          |

| 4-7                    | Data Specification                          |          |

| 4-8                    | Array #3 Interrupt Organization             |          |

| 4-9                    | Array #3 Translation Register Organization  |          |

| 4-10                   | Typical Gate of Array #3                    |          |

| 4-11                   | Array #4 Organization.                      |          |

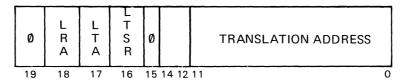

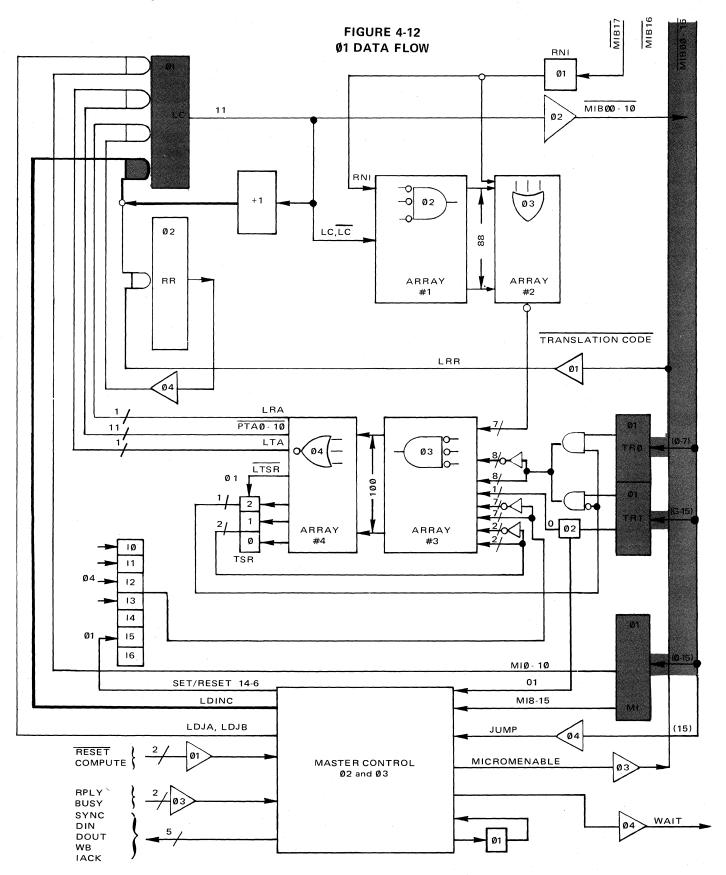

| 4-12                   | Ø1 Data Flow                                |          |

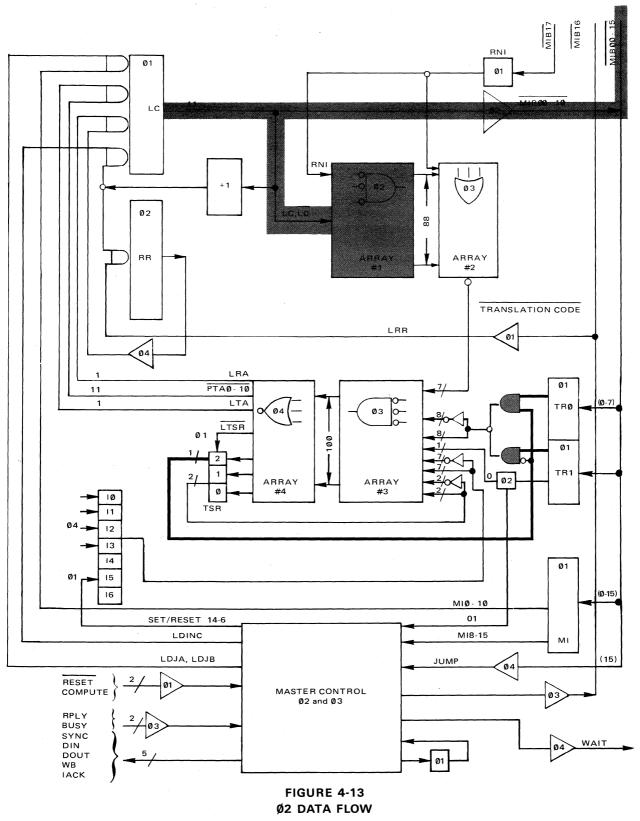

| 4-13                   | Ø2 Data Flow                                |          |

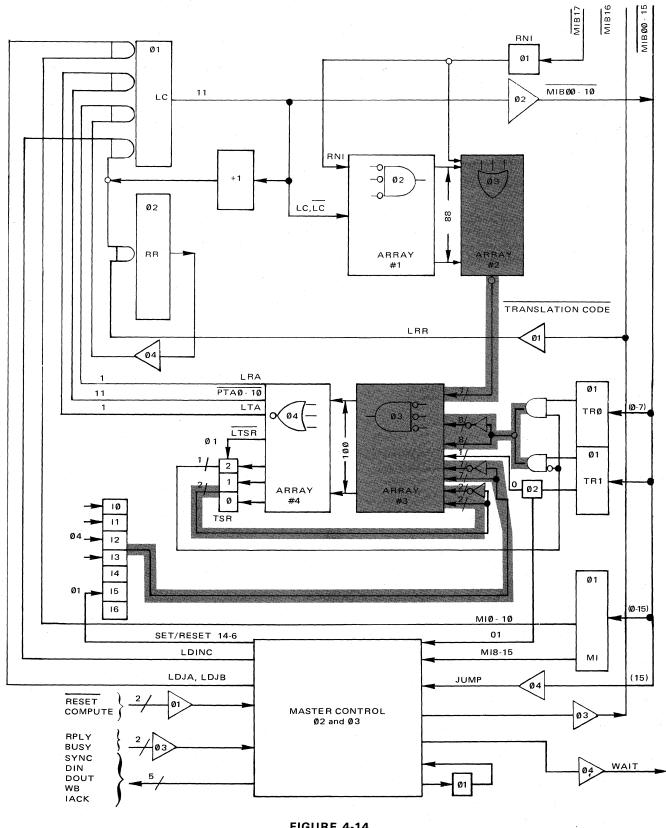

| 4-14                   | Ø3 Data Flow                                |          |

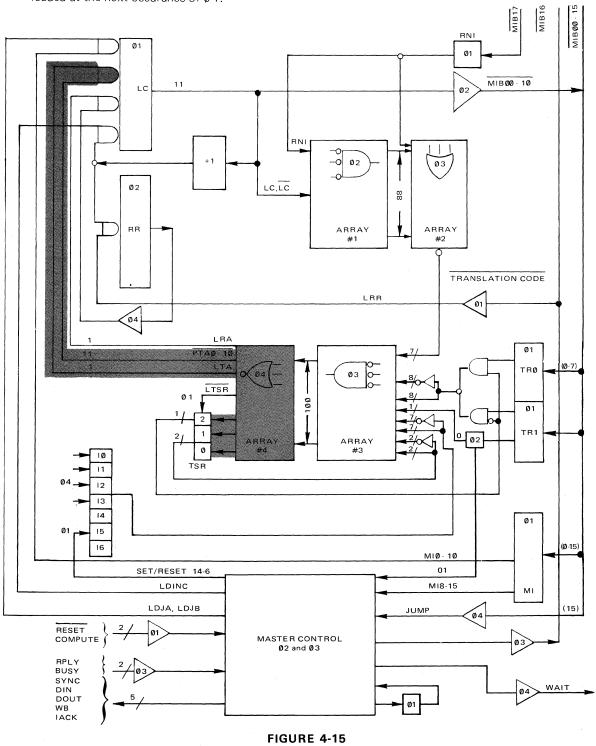

| 4-15                   | Ø4 Data Flow                                |          |

| 6-1                    | System Interconnections, Microprocessor Set |          |

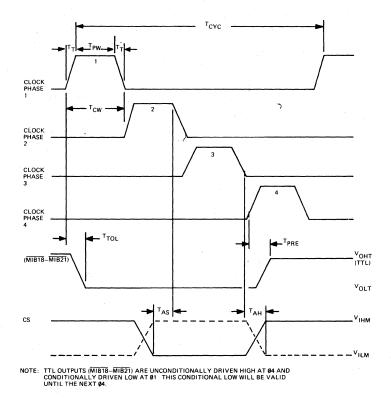

| 6-2                    | TTL Output Timing, CP1631B                  |          |

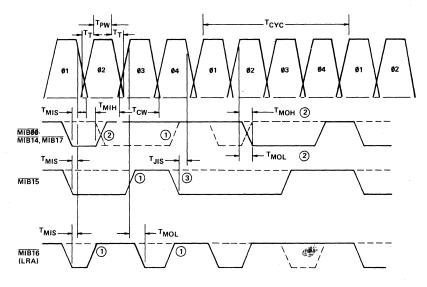

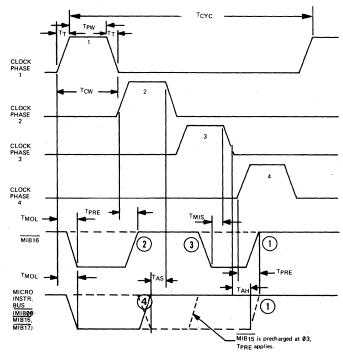

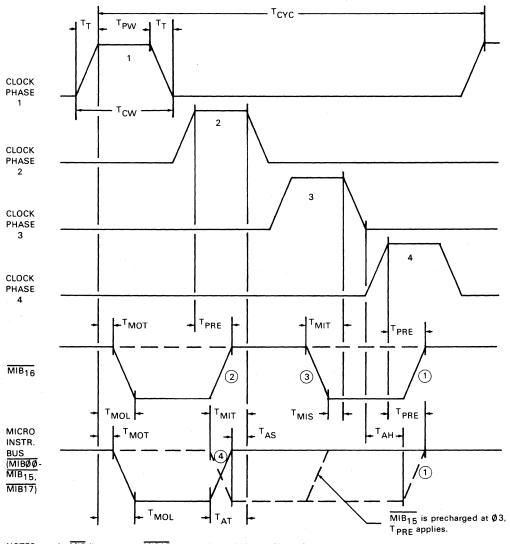

| 6-3                    | Microinstruction Bus Timing                 |          |

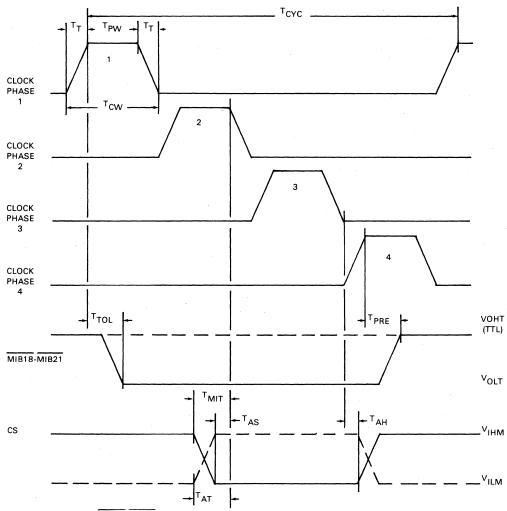

| 6-4                    | Control Chip Microinstruction Bus Timing    |          |

| 6-5                    | Microinstruction Bus Timing, CP1631B        |          |

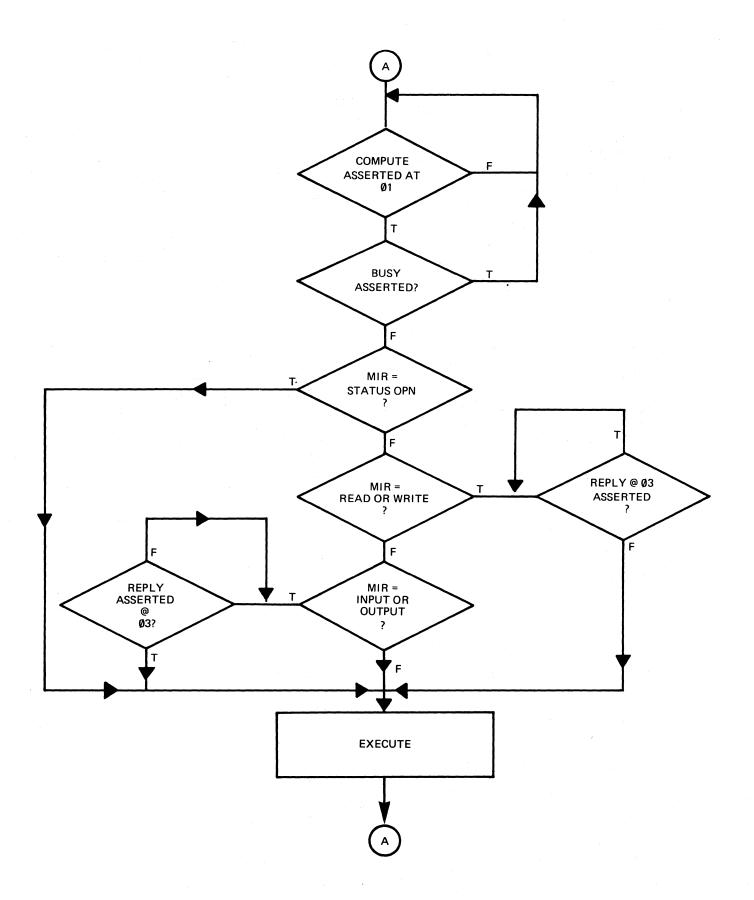

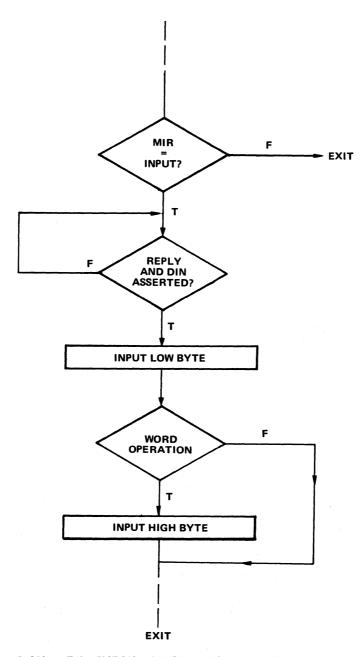

| 7-1                    | I/O Instruction Condition Testing           |          |

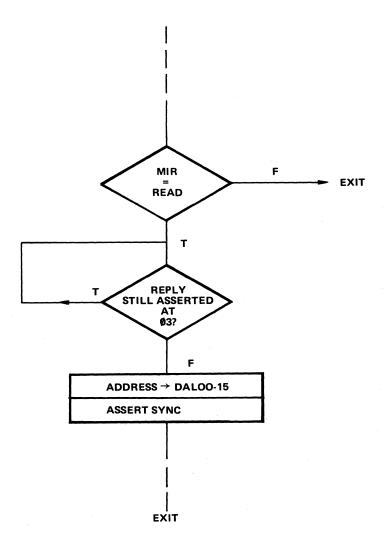

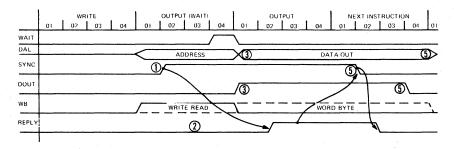

| 7-1                    | Execution of Read Instruction               |          |

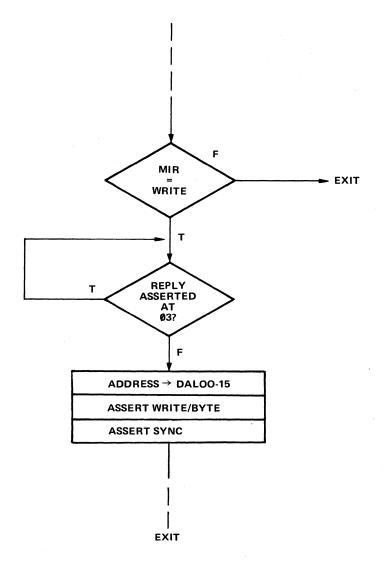

| 7-3                    | Execution of Write Instruction              |          |

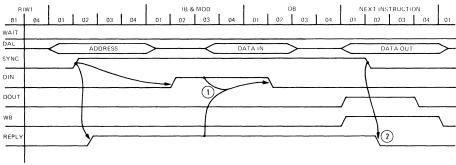

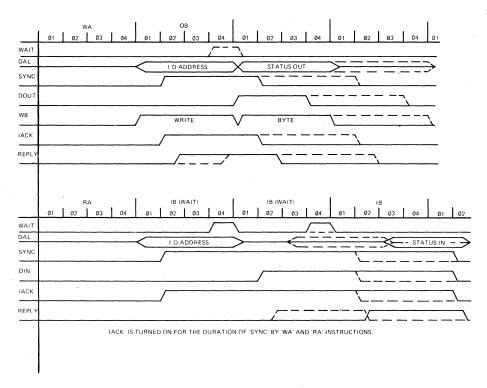

| 7-3<br>7-4             | Execution of Input Instruction              |          |

| 7- <del>4</del><br>7-5 | Execution of Output Instruction             |          |

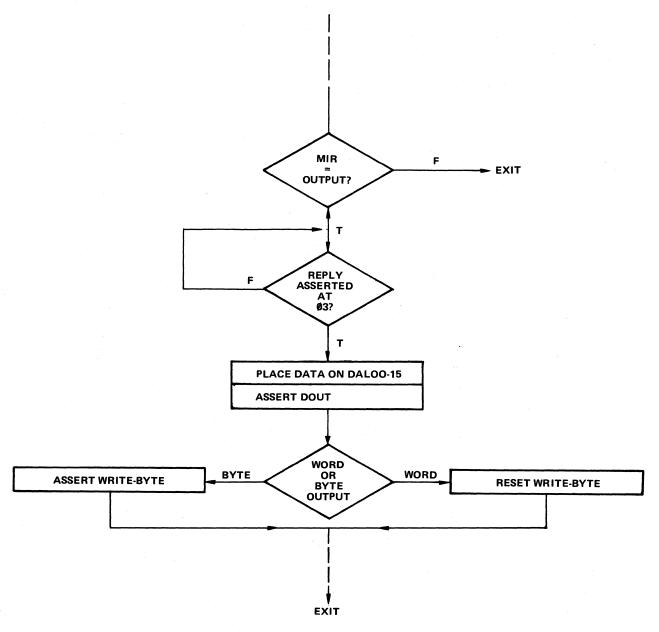

| 7-5<br>7-6             | Write/Output Sequence                       |          |

| 7-0<br>7-7             | Read/Input Sequence                         |          |

| 7-7<br>7-8             | Read/Modify/Write Sequence                  |          |

| 7-9                    | Interrupt Acknowledge Sequence              |          |

| 8-1                    |                                             |          |

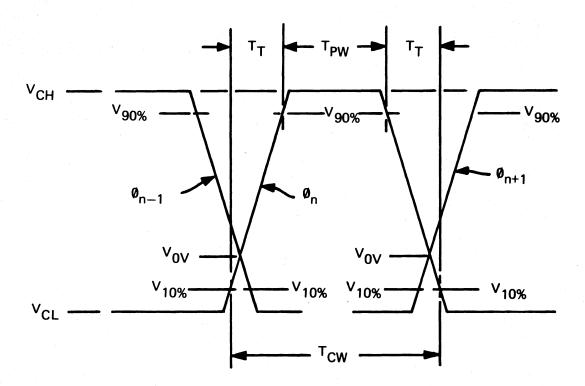

| 8-2                    | MCP16ØØ Clock Diagram                       | -        |

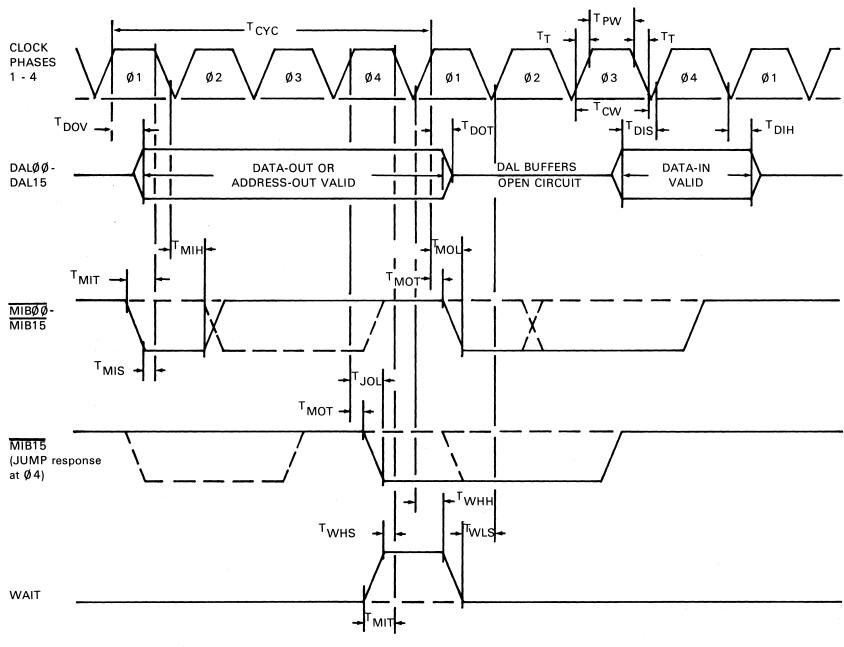

| 8-3                    | 1611 Interface Timing                       |          |

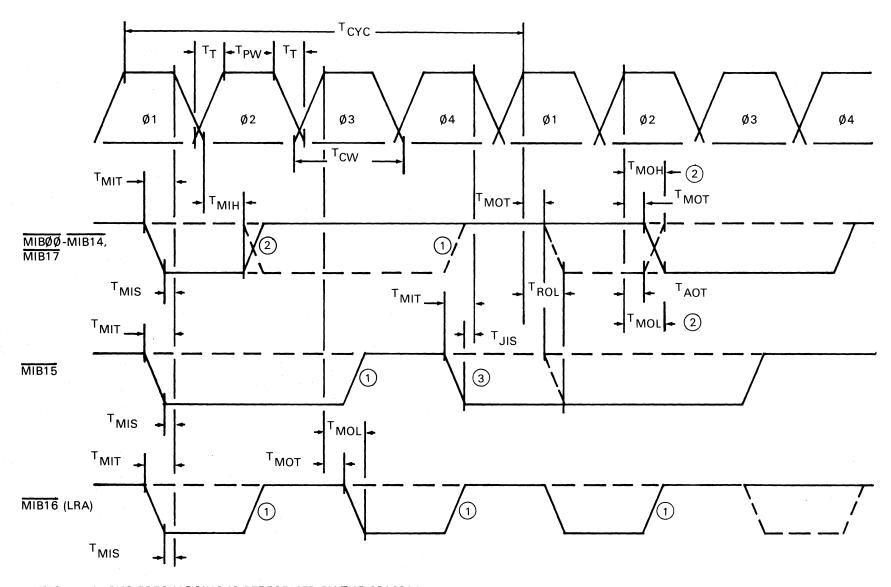

| 8-4                    | 1621 MIB Timing                             |          |

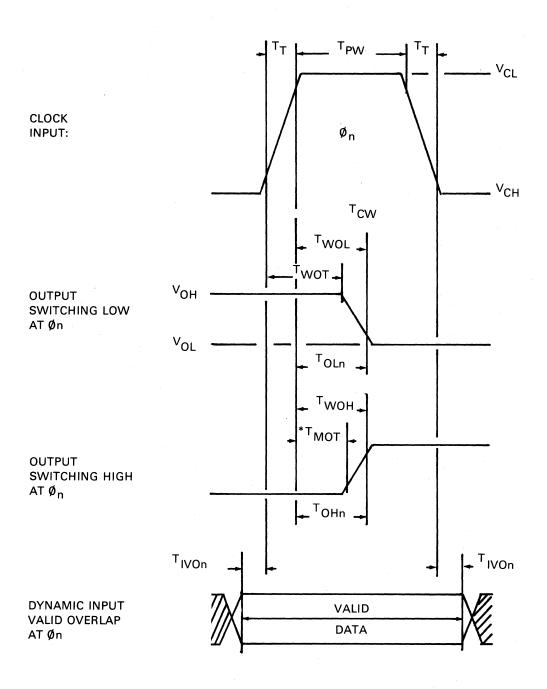

| 8-5                    | 1621 Control Signals Timing                 | -        |

| 8-6                    | 1631 MIB Timing                             |          |

| 9-1                    | 1631 TTL Timing                             |          |

| 9-1<br>9-2             |                                             |          |

| 9-2<br>9-3             | CP1631B Microm Chip Pin Assignments         |          |

| 9-J                    | CP1631B Microm Chip Pin Assignments         | . 9-1    |

| ,                      | TABLES                                      |          |

| Table No.              |                                             | Page No. |

| 4-1                    | Translation State Code Outputs, 4 of 7      | 15       |

| 4-1<br>4-2             | Translation State Code Outputs, 4 of 7      |          |

| 6-1                    | Microbus Timing                             |          |

| 5 1                    |                                             | 02       |

#### **PREFACE**

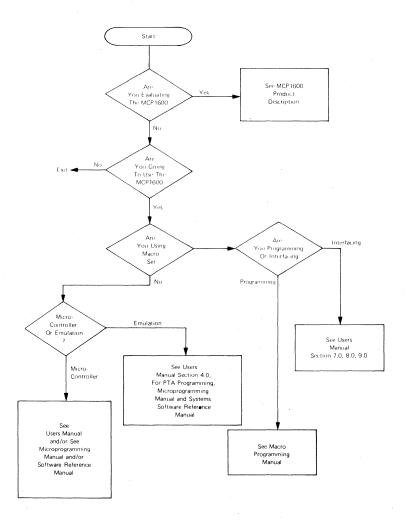

#### **USING THIS MANUAL**

This manual is intended to be used by those who need a detailed description of the internal operation of the MCP1600 Microprocessor Set. Users in this category are usually those who are implementing their own microcode structures and thus require a detailed knowledge of the machine.

- Sections 2,3,4 and 5 are of interest to the overall system architect

- Section 6 is of interest to the sophisticated user who will attempt to hookup to the MIB

- Section 7,8, and 9 are of interest to the interface designer

If you are not sure of your need for information, the attached flowchart may be of assistance. Contact a WDC Applications Engineer Representative for any additional information.

This is a preliminary specification with tentative device parameters and may be subject to change after final product characterization is completed.

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change said circuitry at any time without notice.

#### SECTION I

#### **GENERAL SYSTEM CONFIGURATION**

#### 1.1 GENERAL

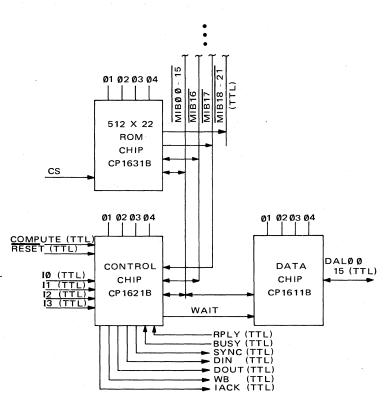

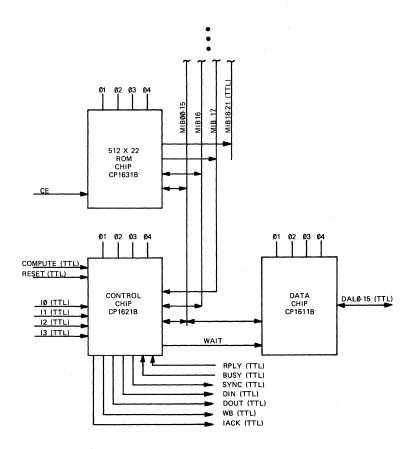

The Western Digital MCP1600 microprocessor is an 8-bit microprogrammable computer implemented with 3 MOS/LSI chips using WDC's N-channel silicon gate process. The chip set consists of the CP1611B Data chip, the CP1621B Control Chip, and the CP1631B microinstruction ROM (MICROM) chip.

These chips are interconnected by the 22 bit Microinstruction Bus (MIB) which provides bi-directional communication between the chips for addresses and instructions. A Data Access Bus provides a 16 bit port for communicating with other system components such as memory and I/O.

The list below describes the pertinent aspects of the set:

- 8-bit Internal Organization

- 16-bit Data Access Port to Memory and I/O

- 26 Registers

- Extensive Microinstruction Set Including Decimal Operations

- Single and Double Byte Operations

- Micro and Macro Level Condition Flags

- 512 Word x 22-bit Control ROM

- Control ROM Expandable to 2048 words

- Micro Level Subroutine Capability

- Programmable Translation Array for Macroinstruction Interpretation

- Four External Interrupts and Three Internal Interrupts

- External Instruction Set

- Power Supplies +12V, +5V, and -5V

- 3.3 MHZ Four Phase Clock (Also available in 2.75 and 2.2. MHz versions)

- TTL Compatible 3 State Interface

The MCP1600 Microprocessor Set is easily interfaced to a variety of applications through many of the standard product offerings of Western Digital and other semi-conductor companies.

## 1.2 UNIQUE FEATURES OF THE MCP1600

The MCP1600 has two uncommon and usable features that set it apart from the standard run of MOS microprocessors.

- The MCP1600 is 'a vertically microprogrammable processor.

- The MCP1600 has a programmable translation array which quickly and automatically generates the jump vectors required for emulation and macroinstruction applications.

The unusual feature of being able to decode macroinstruction quickly and automatically sets the MCP1600 apart from other devices in the microprocessor market.

Unlike other offerings in the MOS microprocessor marketplace, the MCP1600 can be applied to problems that demand speed for their solution. The combination of speed (maximum 3.3 MHz instruction rate) and high density (thus great processing power) brings the economic advantages of MOS to bear upon problems which previously could only be attached by bipolar microprocessors or special logic designs.

Careful review of the contents of this manual will stimulate the imaginative user to think of many applications to which these unique features can apply significant advantage.

#### 1.3 AREAS OF APPLICATION

One of the unique attributes of the MCP1600 is its ability to be sensitive to data. The Program-mable Translation Array provides this ability by allowing the address of the next instruction fetched

to be determined by data, if desired. This makes the MCP1600 highly suitable to areas of application that require a substantial amount of data decoding. Such application might be:

- The emulation of an existing computer's instruction set.

- The invention of a new, application oriented instruction set.

- The construction of a macro-instruction processor

- The construction of a data driven processor

Another of the attributes of the MCP1600 is its ability to quickly process data in a sophisticated manner. The availability of a rich instruction set coupled with speed and a variety of registers make the MCP1600 especially applicable to problems that require great quickness. Applications such as:

- Communications Multiplexing

- Host computer front ends

- Medium Speed Peripheral Device Control

can readily be attacked by the MCP 1600.

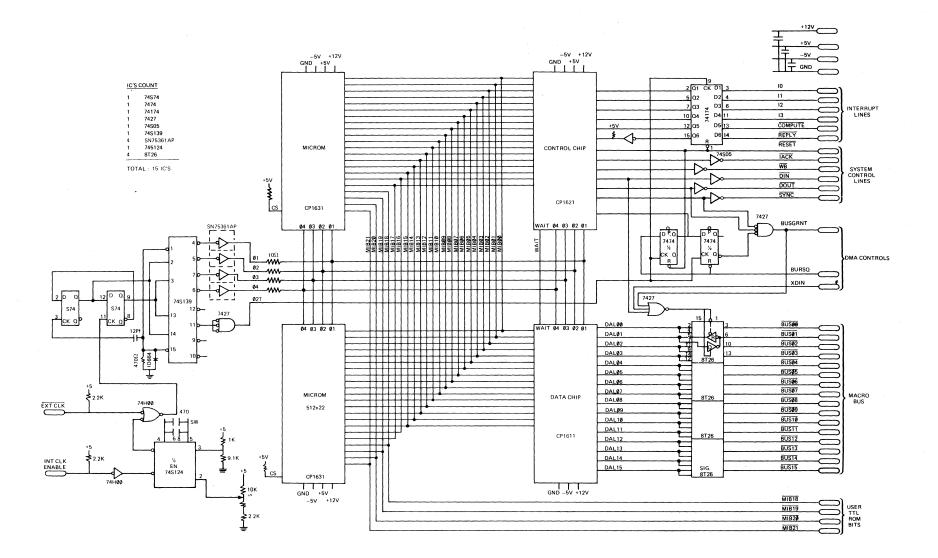

The MCP1600 provides still another advantage to the system designer. It is truly easy to interface. Including the processor set and all other logic a microcontroller can be implemented with as few as 15 parts. Figure 1-2 shows such a system.

Specific application notes detailing ideas relevant the application of the MCP1600 to the above mentioned areas are available from your Western Digital sales representative.

#### 1.4 BLOCK DIAGRAM

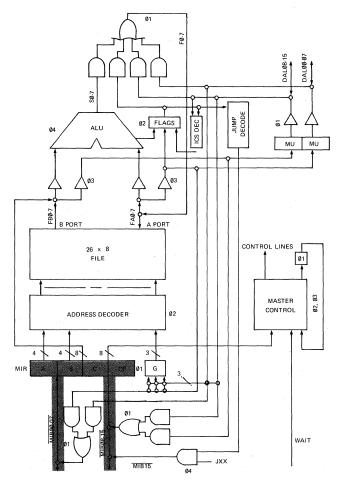

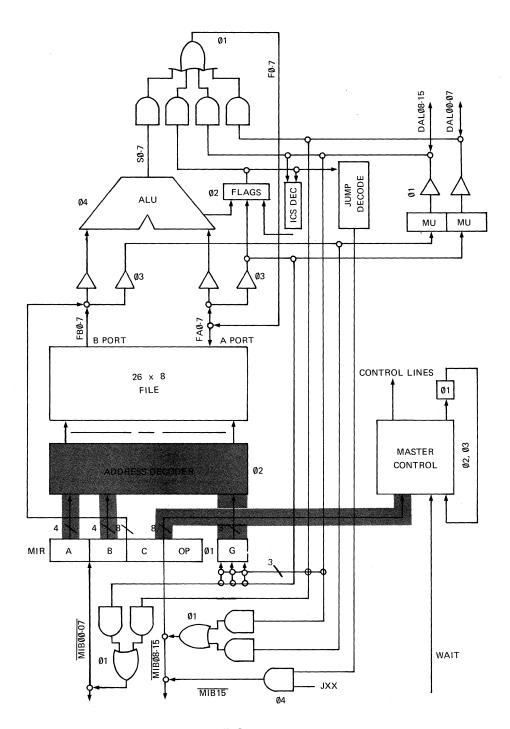

Figure 1-1 describes the interconnection of the required components of the MCP1600 microprocessor set. The DATA CHIP, (CP1611B) contains the arithmetic logic unit, the microinstructions decode and the register file. Additionally, it contains paths to control the operation of the processor.

The CONTROL CHIP (CP1621B) contains the program translation array, portions of the control circuitry to control operation of the processor set, the microinstruction counter and the I/O control system.

The MICROM CHIP (CP1631B) contains the microinstruction ROM. The MP1600 microprocessor set may be expanded up to four MICROMs giving the user a total of 2,048 22 bit microinstructions. The simple system illustrated in Figure 1-2 shows all of the functional components needed to make a working microprocessor. Note that, in addition to the three parts comprising the Microprocessor Set, twelve other available standard TTL parts are required. These parts serve to:

- Generate the clocks

- Latch and gate input signals

- Latch and gate output signals

This is to be contrasted with some other commercially available microprocessors which may require as many as 50 other parts to implement a system of equivalent capability.

FIGURE 1-1 MCP1600 MICROPROCESSOR BLOCK DIAGRAM

#### SECTION II

#### SYSTEM COMPONENTS

#### 2.1 GENERAL

This section describes the main functional components of the MCP1600 system. The reader should be aware that the system is physically partitioned into three kinds of devices. He should be more interested and aware of the logical partitioning of the system, which encompasses five areas:

- Processing and data handling. This is generally handled on the CP1611B Data Chip.

- Next Instruction Address Generation. This is generally handled on the CP1621B Control Chip.

- Microinstruction Storage. These are contained on one or more CP1631B Microinstruction ROMs,

- Microinstruction Bus. This bus connects the three types of devices together and provides a path for the microinstructions to flow from the microinstruction ROM to both the Control and the Data Chip.

- Data Access Bus. This bus provides access from the MCP1600 microprocessor set to the outside world. Lines comprising this data access bus come from all three of the chip types. Lines containing the address and data come from the Data Chip, control lines defining the state of the data access come from the Control Chip and user programmable control lines come from the Microinstruction ROM.

While not strictly a logic component, the clocking scheme should be noted here.

The MCP1600 operates on a four phase clock system. While there are some variations, the general use of each phase period is:

- Ø1 Instruction Access

- Ø2 Data Access

- Ø3 Execution

- Ø4 Data Update

The clocking scheme can be more easily understood by reference to section III and section VIII.

This section will describe the functional components that make up these partition areas.

## 2.2 REGISTERS

This section will describe data handling registers in the MCP1600 set of interest to the system designer.

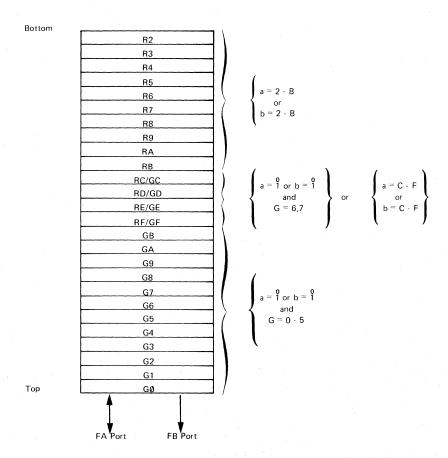

Register File. The Register File consists of 26, 8 bit registers which provide RAM data storage for the MCP1600 processor set. The register file has 2 output ports and 1 input port. Fourteen of the registers of the file can be directly addressed by the A and/or B register designators of a microinstruction. Additionally, the 16 top-most registers of the register file may be considered as register pairs and can be addressed by the G register (see below) to permit operation on full words of data. The Register File is on the Data Chip.

The A and the B output ports of the register file feed into the ALU.

G register. The G register is a pointer register on the Data Chip that describes the currently accessed linked consecutive pair of registers in the register file. Figure 2-1 describes the interaction between the G register and the register file. Note that, when the G register is being used, access to the register file is from the top down. This is opposed to the access to the register file when only the A and B fields are being used as designators, in which case it is from the bottom up. This register is loaded by IW and LGL instructions. "Input Word" instruction loads the G Register from the DAL bus as specified by the "b" field of the instruction. "Load G Low" instruction loads the G Register Ra.

The first (or lowest) 14 registers of the Register File are addressable only from the MIR register. The top 12 registers are addressable only from the G-Register. The middle 4 registers

are addressable from either the G or the MIR registers. Figure 2.1 describes the addressing conventions of this file. It is helpful to note that if the a or b fields of the MIR are 1 or 0, then this enables G-Register addressing.

#### Some Examples

Assume G = 4, a = 0, b = B

Then one operand (A Port) will be from G'8'

The other operand (B Port) will be from R'B'

- Assume

$$G = 0$$

,  $a = 7$ ,  $b = 1$

Then one operand (A Port) will be from R'7'

The other operand (B Port) will be from G'1'

- Assume

$$G = 6$$

,  $a = 1$ ,  $b = 0$

Then one operand (A Port) will be from  $G'D'$

The other operand (B Port) will be from  $G'C'$

#### REGISTER FILE ADDRESSING MODES

FIGURE 2-1 REGISTER FILE

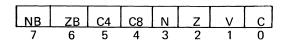

ALU Status Bits. The ALU provides 4 status bit outputs which reflect the result of each 8 bit operation. The ZB and NB bits

are updated after every ALU operation. C4 and C8 are updated for Arithmetic or Shift operations. These bits may be tested

by Jump but their primary function is to pass result data from the first cycle of a word instruction to the second cycle.

The available status bits are:

- ZB: Set if the result of a Byte or Word operation is zero; cleared otherwise.

- NB: Set if the high-order bit of a Byte or Word operation is a one; cleared otherwise (except for SRW and SRWC).

- C4: Set if Carry Out of Position 3 is a one; cleared otherwise. Updated only on Arithmetic operations. This status bit is used mainly for decimal arithmetic corrections.

- C8: Set if Carry Out of Position 7 is a one; cleared otherwise. (Note that this status bit is not set to borrow for subtract as is the case with the C Flag.) Also set if the shifted off bit of a Shift operation is a one; cleared otherwise.

- Condition Flags. The Condition Flags consists of 4 latches which can reflect the status of the previous ALU results. The updating of these flags can be selectively enabled or disabled at the discretion of the microprogrammer. The condition flags are updated with odd-numbered instruction opcodes in the range of 80-EF.

- Z Flag: Set if the result of a Byte or Word operation is zero, cleared otherwise.

- N Flag: Set if the high-order bit of the result of Byte or Word operation is (except for SRW and SRWC) is a one; cleared othewise. (Note that this is the complement of the sign of the result if overflow occurs.)

- C Flag: Monitors the carry, borrow and shifted off bits as follows:

- Add and Increment: Set if there is a carry from the most significant bit of the Byte or Word result;

cleared otherwise.

Subtract and

Decrement: Set if there is a borrow (complement of carry) from the most significant bit of the

Byte or Word result; cleared otherwise.

Shift: Set if the bit shifted off in a left or right shift is a one; cleared otherwise.

The C Flag is not affected for operations (other than those listed above) even if the other flags are updated.

V Flag: Set if there is an arithmetic overflow on Arithmetic operations. Cleared if there is no overflow and on Non-arithmetic operations. On Add operations overflow occurs when the sign of the two operands are the same and the sign of the result is different. On Subtract operations overflow occurs when the signs of the two operands are different and the sign of the result is different from the operand in Ra (V=C7 ⊕ C8).

The format of the ALU status and flag register word is shown below:

MIR Register. The 16 bit MIR register holds the least significant 16 bits of the 22 bit microinstruction currently being executed. The MIR register is loaded every Ø1 unless the currently executing microinstruction is of the 2 cycle variety. In this case the register is not clocked on the second occurrence of Ø1.

#### 2.3 INSTRUCTION ADDRESS GENERATION

This section describes the register and arrays used in generating the next microinstruction address.

- Location Counter Register. The Location Counter (LC) is an 11 bit register which holds the address

of the next microinstruction to be accessed. Under normal conditions, the LC is incremented by

one after each access of a microinstruction. The LC can be altered by other than one by execution

of a Jump instruction or a Return from Sub-routine (RFS) instruction or by invoking a PTA translation.

- Return Register. The Return Register (RR) holds an 11 bit address and permits a subroutine depth

of one in the microprogram. When a subroutine jump is indicated (MIB 16 = 1) the return register

stores the incremented contents of the LC. Contents of the Return Register can be transferred to the LC under

the control of a RFS (Return From Subroutine).

- Translation Register. The Translation Register (TR) is a 16 bit register which holds the data

presently being input to the PTA. Data on the Microinstruction Bus (MIB) is used to load the Translation Register. Note that only the upper or lower half of the Translation Register can be fed into

Array 3 at one time.

- Translation Arrays. There are four arrays on the control chip that control the generation of the next microinstruction address. They generate new inputs into the LC register, as a function of the LC register contents, the contents of the translation register, interrupts, and other miscellaneous inputs. The detailed operation of these arrays is discussed in Section 4, PROGRAMMED TRANSLATION ARRAY OPERATIONS.

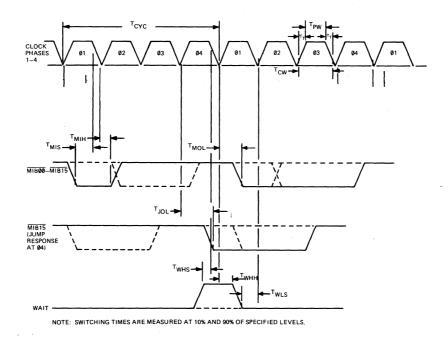

#### 2.4 MICROINSTRUCTION BUS

The Microinstruction Bus serves to interconnect the three required parts of the MCP1600 Microprocessor set. The bus is organized into 4 distinct sections:

- MIB00 MIB15 carry proper microinstruction data from the microinstruction ROM chip to both the

control chip and the data chip. These lines may also carry data between the data chip and the control chip under certain conditions.

- MIB16 controls the subroutine jump operation. When MIB16 is set on a jump instruction, it causes the incremented contents of the LC register to be placed into the Return Register.

- MIB17, if set, causes the PTA on the Control Chip to perform a Read Next Instruction translation.

- MIB18 MIB21 are TTL level outputs that can be programmed by the user as his needs dictate.

They are not used by the MCP1600 Microprocessor set to control its operations. They are provided for the convenience of the user in order that he may interface to the MIB bus or control devices directly from the microprogram level.

#### 2.5 DATA ACCESS BUS

The Data Access consists of three sections:

- DAL00 DAL15 carry address and data between the data chip and the outside world.

- Outside Control Lines. There are five TTL level Outgoing Control Lines that inform the outside world of the present state of the MCP1600 set. These signals include Sync, Input Instruction, Output Instruction, Interrupt Acknowledge, and Write-Byte.

- Incoming Control Lines. There are 8 TTL level Incoming Control Lines. These incoming control lines inform the MCP1600 Microprocessor set of the state of affairs in the outside world. There are four interrupt lines, a Compute line, a Reset line, a Reply line and a Busy line.

With these lines, the MCP1600 can control a wide variety of peripheral devices.

# 2.6 MICROINSTRUCTION STORAGE

#### MICROM

The microinstruction ROM is a 512 X 22 -bit word, high speed ROM which stores the instructions of the microprogram. The transfer of addresses into the chip and the microinstruction out of the chip are performed over the MIB. Address is received from push-pull drivers in the Control Chip on  $\emptyset$ 2. The decoding takes place on  $\emptyset$ 3. On  $\emptyset$ 4 the selected microinstruction is internally accessed and the MIB is precharged. The accessed microinstruction is placed on MIB15-MIB $\emptyset$  for transfer to the Data Chip and Control Chip during  $\emptyset$ 1.

#### SECTION III

#### **CPU OPERATIONS**

#### 3.1 GENERAL

This section describes the internal workings of the Data Chip, the CPU of the MCP1600 system. Its purpose is to provide the designer with a background understanding to enable him to more effectively interface with the Micro Instruction Bus and the Data Access.

The description of the MCP1600 Processor must proceed from the knowledge that there are two important and distinct partitions to the processor. The first partition, called the Data Chip, provides classical stored program processing. The Data Chip consists of:

- A register file

- An arithmetic logic unit

- A Microinstruction register

- A register file address decoder

- A control signal generation function

- Condition flags

- Jump decoding

- Input/Output gating

The data chip is responsible for data manipulation as a result of instruction execution.

The second partition, the Control Chip, generates address data that directs the accessing of the next microinstruction to be executed. This address generation mechanism provides the MCP1600 with its unique emulation capabilities. While the Data Chip is executing the presently fetched microinstruction, the Control Chip is performing a transformation upon the presently executing macroinstruction to determine the address from which to fetch the next microinstruction to be executed.

The description of the processor proceeds by first outlining the operation of the Data Chip (CPU) and then in the following section outlining the operation of the Control Chip. It is important to note that the two chips are not synchronized except by a common clock and the fact that the contents of the MI register on the Control Chip and the contents of the MIR register on the Data Chip are the same. One control line is passed between the Data Chip and the Control Chip.

#### 3.2 CPU OPERATIONS

We start the CPU operation description by first assuming that the machine has been properly reset and has just entered the compute mode. The Control Chip will cause microinstruction to be fetched from the MICROM to be placed on the MIB bus. (See Figure 3-1) Assuming that the clock is now on the leading edge of Ø 1, the contents of the MIB bus are gated into the MIR register on the Data Chip and the MI register on the Control Chip.

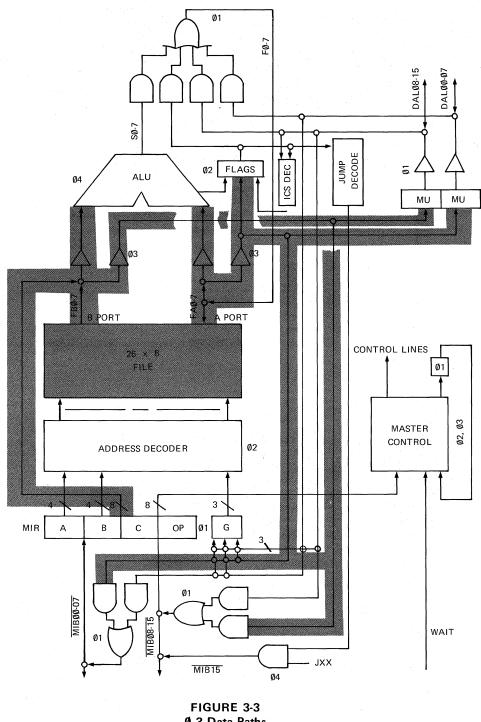

FIGURE 3-1 Ø1 DATA PATHS

At the end of  $\emptyset$  1 (trailing edge of the clock), the contents of the MIR register have settled. The contents on the MIR register are held fixed until the next occurance of  $\emptyset$  1 (four phase times).

At the beginning of Ø2, the contents of the MIR register are presented to the various different functions of the CPU. The A and B fields are presented to the address decoder, as is the G register. The contents of the MIR register's C field and OP field are presented to the master control function of the Data Chip. During Ø2 and Ø3 the master control function decodes the C field and generates signals which control the gating of data to the various functions of the Data Chip. Also during Ø2 the address decoder is interpreting the contents of the A field and the B field and accessing the appropriate register in the register file. Also during Ø2 the condition codes reflecting the result of the last ALU operation become valid. They are presented to the FLAGS register which retains them for examination on the next occurance of Ø4. Figure 3-2 illustrates Ø2 data paths.

FIGURE 3-2 Ø 2 Data Paths

Phase 3 is the register access phase. During Ø 3 data is presented to the ALU by the A and the B output ports of the register file. Data may also be presented to the ALU B port by means of the literal path from the MIR register. Note the literal path (whose contents are the C and B field of the MIR) bypasses the address decoding logic and the register file. Also during Ø 3 the contents of the A and B register file output ports may be presented to the Data Access on line DALOO --DAL15. Also during this phase time the contents of the register file A port may be presented to the flag register. Finally, during this phase time, the contents of the register files A and B ports may be presented to the gating which controls access to the MIB bus. Figure 3-3 illustrates Ø 3 data paths.

Ø 3 Data Paths

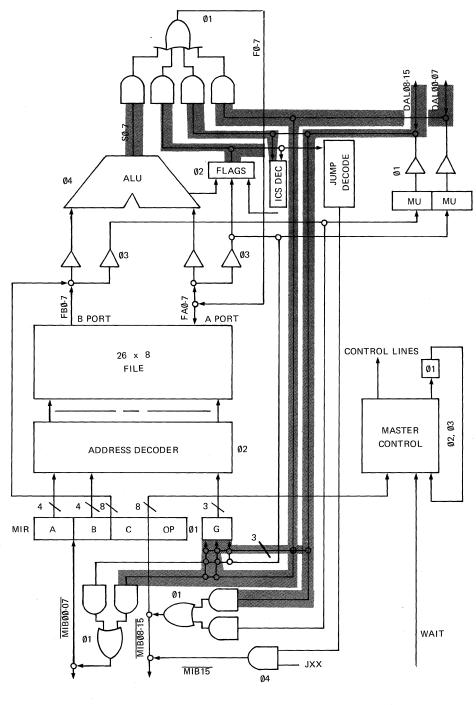

During Ø 4 the output of the ALU becomes valid. Also during Ø 4, input to the ALU may occur from the data bus. That is, data presented on lines DALOO--DAL15 may be presented to the gating structure which controls the output of the ALU. Finally, during Ø4, the data available from the Data Access may be presented to the gating structure that controls access to the MIB bus. Figure 3-4 illustrates the Ø 4 data paths. Note that, during Ø 4 the jump control takes place. If the jump decoder indicates that all the proper jump conditions are met and if JXX is asserted, then MIB15 will cause the Control Chip to effect a jump on the next clock cycle.

FIGURE 3-4 Ø 4 Data Paths

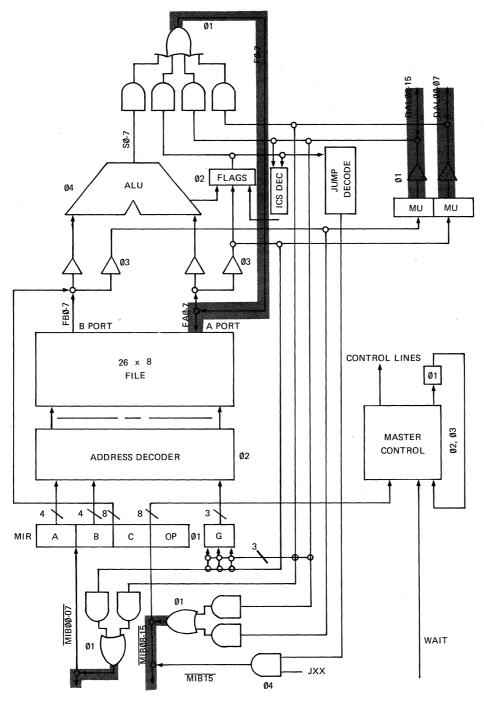

As the next Ø 1 clock occurs to start the next cycle of the instruction/execution, the data that was presented to the gating structure that controls access to the A input port of the register file is gated or not gated, depending upon a signal from the Master Control, into the register file. Figure 3-5 illustrates this path. If the instruction contained in the MIR register is one that requires only one clock cycle for execution, then a new instruction is fetched from the MICROM according to the address generated by the Control Chip and execution begins as in Figure 3-1.

If however, the instruction requires two cycles for execution, things proceed differently. At the beginning of  $\emptyset$  1 of the second cycle, the contents of the MIR are preserved, no new data is gated in. The low order bits of both the 'A' and 'B' fields are complemented to access adjacent slots in the register file to those previously addressed in the first cycle. Also during this phase, the CPU may output data to the MIB bus. Figure 3-5 illustrates this path.

Other than these exceptions, two cycle instructions proceed as do one cycle instructions.

FIGURE 3-5 Ø1 Data Paths Second Cycle

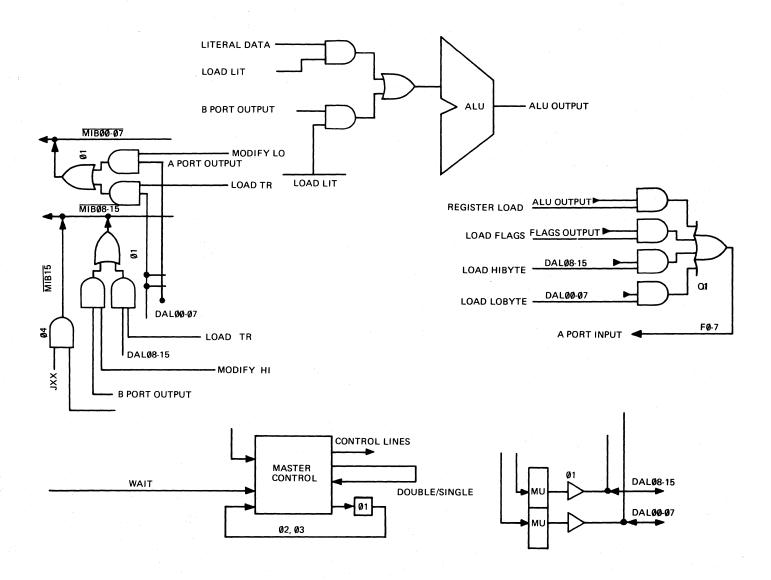

#### 3.3 CONTROL LINES

During Ø 2 and Ø 3 the Master Control function is decoding the new contents of the MIR register in order to generate signals to control the data transfers described above. These control signals are generated on the basis of the contents of the C and OP fields of the MIR register. All of the control lines generated by the Master Control function are not described here because some of them serve timing and sequencing functions that are not necessary to the understanding of the CPU operation and how it affects the Data Access and Microinstruction Bus. However, there are several control lines which the designer may find helpful to understand. They are shown in the attached diagram, Figure 3-6, and, in order, they are:

#### 3.3.1 REGISTER LOAD

This control line determines whether or not the output of the ALU will be gated back into the register file input port. It is invoked by register to register format instructions.

#### 3.3.2 LOAD FLAGS

This line controls whether or not the output of the FLAGS register will be gated into the register file input port. It is generated by the Load Flags and Copy Flags instruction.

#### 3.3.3 LOAD HI BYTE

This control line determines whether or not the contents of the DAL08-15 will be gated into the register file input port. This line is controlled primarily by the Input class of instructions.

#### 3.3.4 LOAD LO BYTE

This control line determines whether the contents of DAL-07 will be gated into the register file input port. It is generated by input class instructions. Note that this signal and preceeding signal are generated by the specification in the B field of the appropriate input instruction. Note also that one can input the low order byte, the hi order byte, or both bytes. This latter case is an Input Word Instruction.

#### 3.3.5 MODIFY LO

This control line is invoked by the Modify instruction and causes the output of the A register file port to be gated on to the low order 7 bits of the microinstruction bus. This control line is also invoked by the Load Translation Register instruction.

#### 3.3.6 MODIFY HI

This control line is the high order analog of the previously described control line.

#### 3.3.7 JXX

This control line is invoked by the jump instruction. It is made hi during the first phase four of the jump instruction, if the jump instructions have been met. It causes the contents of the MI register on the control chip to be placed into the LC register.

#### 3.3.8 LOAD LIT

This instruction controls the multiplexer which selects the B input to the ALU. The ALU B input port may be fed from either the literal field of the MIR register or the B port output of the register file. This control signal is set by the literal class of instructions and causes the B input to the ALU to be selected from the literal path.

# 3.3.9 DOUBLE/SINGLE

This control line is generated by the Master Control for use by itself. It is invoked by instructions that require two cycles for execution. In the main, it controls whether or not a new instruction is gated into the MIR register at the next occurance of  $\emptyset$  1.

#### 3.3.10 LOAD TR

This control line is invoked by the Input Word instruction if either bits 4 or 5 of the B field are set. These bits being set will cause the data on the Data Access to be placed into the translation register on the Control Chip. It is in this fashion that new macroinstructions are fetched from the user memory for decoding.

FIGURE 3-6

MAJOR CONTROL LINES

#### **SECTION IV**

# PROGRAMMABLE TRANSLATION ARRAY (PTA)

#### 4.1 GENERAL

This section describes the operation of the MCP1600 Microprocessor set's most unique feature, the Programmable Translation Array. The Programmable Translation array serves to generate new micro-instruction fetch addresses as a function of several parameters. These parameters are those which are normally considered during the decode of a macroinstruction. While the Programmable Translation Array was designed specifically to eliminate most of the over head of macroinstruction translation, it is useful for other purposes. One could, for instance, conceive of a data driven processor that would determine the next operation to be performed on a data structure as a function of the present data and the present operation. The uses of the Programmable Translation Array are limited only by the system designer's imagination.

Briefly, the Programmable Translation Array consists of eight elements. They are:

- Location Counter.

- Array 1

- Array 2

- Array 3

- Translation Register

- Array 4

- Translation State Register

- Return Register

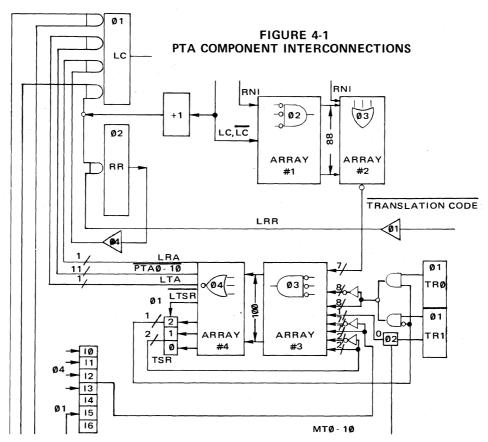

These elements give the capability of calculating microinstruction addresses other than sequentially, or as specified by a jump instruction. Figure 4-1 depicts their interconnection. The mapping (or new Location Counter value) that the PTA generates, when invoked, is a function of the value of the Location Counter, the contents of the Translation Register, the interrupts, and the state of the RNI line.

# 4.2 PTA COMPONENTS

This section will describe the components of the Programmable Translation Array and their functions.

# 4.2.1 LOCATION COUNTER

It is the function of the Location Counter to hold the address of the next microinstruction. The Location Counter is 11 bits wide and has outputs to MIB00—MIB10 and to Array #1. It has inputs from the Master Control function, Array #4 and the Return Register. There is also and input to the Location Counter from an incrementer.

#### 4.2.2 ARRAY #1

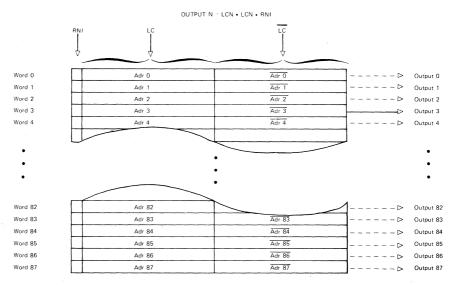

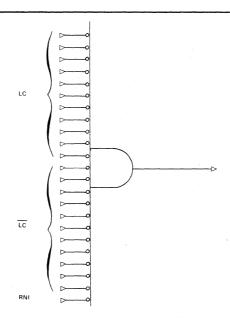

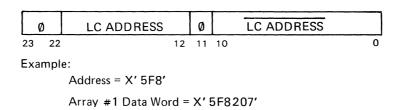

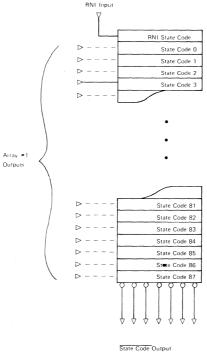

Array #1 is an 88 element array of active low input AND gates with 23 inputs. There are 11 true inputs and 11 complemented inputs from the Location Counter and the RNI bit (MIB17). Figure 4-2 illustrates the organization of Array #1. Figure 4-3 illustrates the concept, as opposed to implementation of a typical gate, one of 88, that make up Array #1. The outputs of these gates make up the bulk of the inputs of Array #2.

FIGURE 4-2 ARRAY #1 ORGANIZATION

FIGURE 4-3 TYPICAL GATE - ARRAY #1

The purpose of Array #1 is to perform a selection function. When the inputs to Array #1 match one (or more) of the word values (addresses) the output associated with that word is asserted. This array is programmed with 6 hexidecimal digits as shown in Figure 4-4. Transistors are placed in the array for 1 bits in the data specification. To program a group of addresses the bits of the address to be left out are specified as Ø bits for the true and complement address inputs. This produces a 'DON'T CARE' effect for those bits and the result will always be a match. This lets the user match on modulo address.

The RNI line serves to inhibit the output of array #1. The reason for this is described later.

FIGURE 4-4 ARRAY #1 DATA SPECIFICATION

#### 4.2.3 ARRAY #2

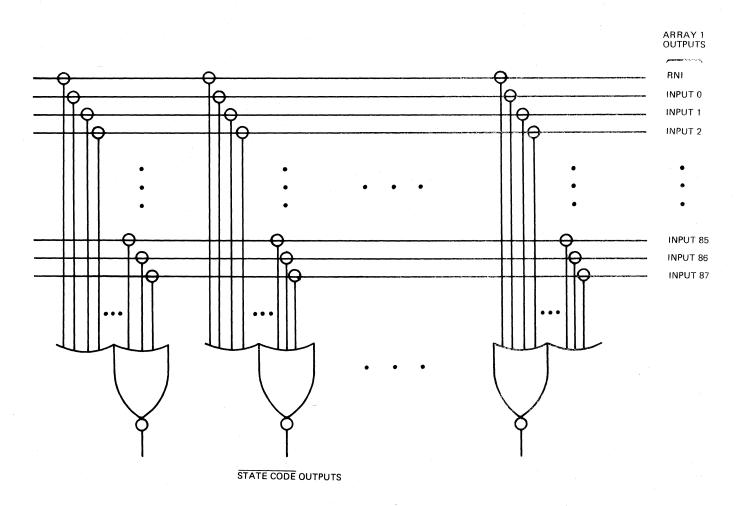

Array #2 is an ORed array whose outputs are negated. The array has 89 inputs, 88 from Array #1 and one from MIB17, the RNI line. The seven outputs from Array #2 represent a translation state code and become inputs into array #3.

Figure 4-5 illustrates the organization of Array #2. Figure 4-6 illustrates in some detail, the conceptual structure of the gate and interconnect structure of Array #2. The small circles present where the lines would normally cross represent connections that can or cannot be made. It is via the making or not making of the connections with transistors that this array is programmed.

FIGURE 4-5 ARRAY #2 ORGANIZATION

FIGURE 4-6

ARRAY #2 GATE AND INTERCONNECT STURCTURE

Array #2 is driven by the inputs from Array #1. When one or more outputs of Array #1 are asserted, Array #2 will make the corresponding word available as its outputs.

The purpose of Arrays #1 and #2 is to provide a mapping between the present value of the Location Counter and a preselected set of translation state codes.

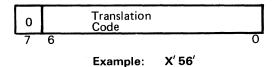

Due to electrical considerations, there are restrictions placed on the configuration of Array #2. Normally this array is programmed in a 4 of 7 code (4 of 7 outputs may be selected to be high, the other 3 must be low), or more ideally, to reduce capacitive loading, a 5 of 7 code. The tables below describe the various state code outputs available in both the 4 of 7 and the 5 of 7 schemes.

| ØF | 2D | 3C | 56 | 69 |  |

|----|----|----|----|----|--|

| 17 | 2E | 47 | 59 | 6A |  |

| 1B | 33 | 4B | 5A | 6C |  |

| 1D | 35 | 4D | 5C | 71 |  |

| 1E | 36 | 4E | 63 | 72 |  |

| 27 | 39 | 53 | 65 | 74 |  |

| 2B | 3A | 55 | 66 | 78 |  |

| 1F | 3D | <b>5</b> B | 6B | 75 |

|----|----|------------|----|----|

| 2F | 3E | 5D         | 6D | 76 |

| 37 | 4F | 5E         | 6E | 79 |

| 3B | 57 | 67         | 73 | 7A |

|    |    |            |    | 7C |

Table 4-1 Translation State Code Outputs -- 4 of 7 Table 4-2 Translation State Code Outputs -- 5 of 7

The outputs of Array #2 represent some of the inputs to Array #3.

The RNI line (MIB17) deserves mention at this point. It is the purpose of the RNI line to force a particular user defined state code from the mapping represented by Arrays #1 and #2. This state code will be independent of the contents of the Location Counter.

Accordingly, RNI inhibits the outputs of Array #1 and invokes that state code selected by the user in Array #2 and makes it present at the output of Array #2.

The programming of Array #2 is illustrated in Figure 4-7 below. Transistors are put in the arrays for zero bits as per the data specifications.

FIGURE 4-7 DATA SPECIFICATION

#### 4.2.4 ARRAY #3

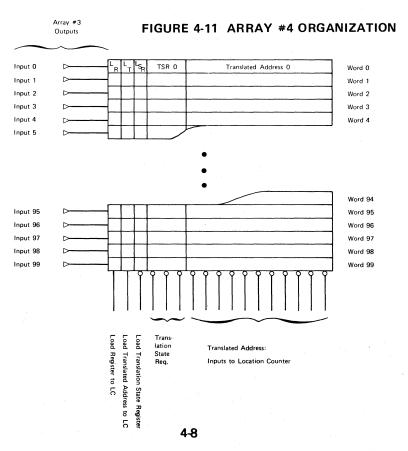

Array #3 consists of 100 active low input AND gates, and has 42 inputs. In contrast to Arrays #1 and #2, the inputs come from a variety of sources. The inputs to this array constitute a direct interface to the real world at the macromachine level, as one of the inputs is the translation register. The inputs to Array #3 are:

- Seven from Array #2. (Translation Code)

- Sixteen from the Translation register. Eight are true data and eight are complemented data.

- Fourteen inputs from the interrupt latches. Again, both true and complemented data are present

- Two from the translation state register. Again, both true and complemented data are used.

- One input, called the Q signal, not generally usable.

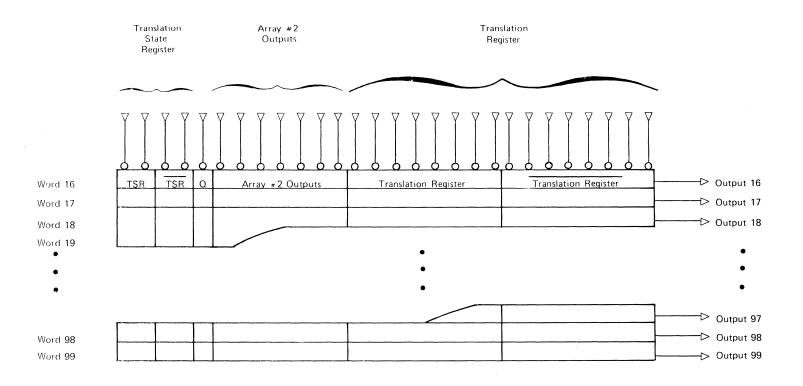

It is worth noting, that, while there are 42 inputs in Array #3, they are not all present at the same time. The array is broken into two partitions. The first partition consists of words 0 through 15, and has as its inputs, the 14 bits from the interrupt latches. The second partition of the array, words 16 through 99 have, in these same slots, the 16 bits of inputs from the Translation Register.

The Figure 4-8 illustrates the structure of the first partition of the array. Figure 4-9 illustrates the second partition of the array. Figure 4-10 shows a conceptual picture of a typical gate in the array.

FIGURE 4-8 ARRAY #3 INTERRUPT ORGANIZATION

FIGURE 4-9 ARRAY #3 TRANSLATION REGISTER ORGANIZATION

FIGURE 4-10 TYPICAL GATE OF ARRAY #3

Array #3, being an ANDed array, will try to match the configuration of its inputs against one of the words that make up the array. If it finds a match, the output associated with that word will be asserted.

Array #3 is programmed with true data as eight hexadecimal digits. DON'T CAREs, which always result in matches, are created by placing both true and complemented bits to zero. Below is a data specification for the programming of Array #3.

NOTE:  $Q = (\overline{TR14} \cdot \overline{TR13} \cdot \overline{TR12}) + (\overline{TR14} \cdot \overline{TR13} \cdot \overline{TR12})$

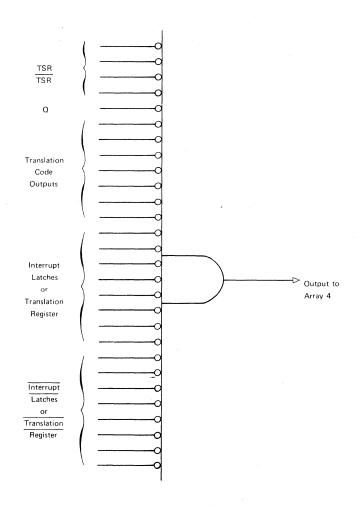

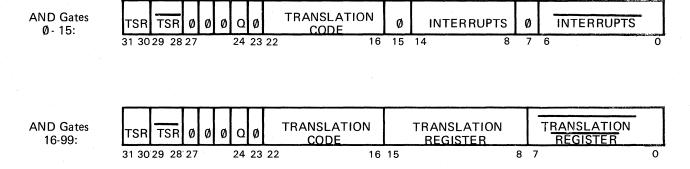

#### 4.2.5 ARRAY #4

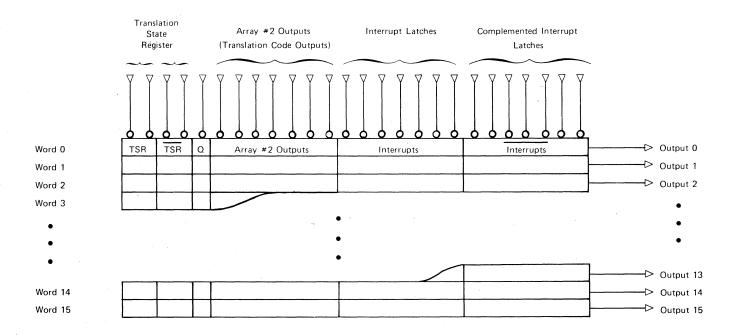

Array #4 is a NORed array with 100 inputs which come from Array #3. The outputs generated by Array #4 include address data to be fed into the Location Counter, data to be fed into the Translation State Register, and three control lines. Two control lines determine whether the Location Counter will be loaded from the Return Register or the output of the translation array. The third control line determines whether or not the value presented to the Translation State Register will in fact be loaded into the Translation State Register. Figure 4-11 illustrates the organization of this array. Note that not all the outputs are complemented. The two control signals LRA and LTA are true data.

Array #4 will determine if any of its inputs are active. If they are, the word associated with the active input is placed on the output lines.

The array is programmed into terms of true data. Five hexadecimal digits are used to program each word. Transistors are placed in the array for 1 bits in the data specification. More than one active AND gate in Array 3 causes the outputs to OR.

#### 4.2.6 TRANSLATION STATE REGISTER

The Translation State Register serves two functions. One is to determine whether the Hi or the Lo order byte of the Translation Register is to be selected for input to Array #3; The other is to provide a four state feedback as an input of Array #3. The loading of the Translation State Register is controlled by an output (LTSR) of Array #4.

#### 4.2.7 TRANSLATION REGISTER

The Translation Register holds the data presently serving as input to the Programmable Translation Array. It receives its inputs from the MicroInstruction Bus (MIB00 - MIB15) as a result of an LTR or IW instruction. Because of the fact that its output destination is 8 bits wide, only half of the Translation Register can be examined at any one time. The Translation State Register controls which half of the Translation Register is gated into the input of Array #3, its destination. It serves as a feedback term of information to the second half of the word.

Bit 2 of the TSR controls the selection of translation input from the TR. When this bit is a zero the upper byte of the TR is selected; when it is a one the lower byte is selected. TSR2 does not serve as an input to Array #3.

#### 4.3 PROGRAMMABLE TRANSLATION ARRAY OPERATIONS

This section describes the operation of the Programmable Translation Array. The operation is based on the description of the components in the preceding section that make up the Programmable Translation Array. The Programmable Translation Array operates as a loop. The beginning and end points of the loop can be considered as the Location Counter.

This loop is completed within one machine cycle. It is helpful to remember that the main components of the loop are:

- The Location Counter

- Arrays #1 and #2, which taken together perform a mapping of the Location Counter to a translation code

- The translation register, which holds the macroinstruction undergoing the translation process.

- Arrays #3 and #4, which take the translation code and the macroinstruction presently undergoing translation and map them into an address.

This newly generated address can then point to the beginning of a macroroutine to interpret the macro-instruction presently accessed.

The following description can be best followed by reference to the attached diagrams which depict the flow of data in the Programmable Translation Array as a function of phase time clocks.

The operation of the Programmable Translation Array begins at  $\emptyset$  1. During  $\emptyset$  1 the location counter is loaded with its new value. The new value can come from any one of four sources. They are:

- From Array #4 of the Programmable Translation Array

- From the MI register

- From the incrementer

- From the Return Register

Figure 4-12 assumes, for the purposes of instruction, that the Location Counter is loaded from the incrementer. Concurrently, with the loading of the Location Counter at Ø 1, the Translation Register is also being loaded if either a LTR or an IW instruction was executed.

At the beginning of Ø2, (See Figure 4-13) the contents of the Location Counter are clocked out to the MIB bus (MIB00 - 10) and to Array #1. Both the true and complemented forms of the Location Counter are input to Array #1. Also input is the RNI line. Array #1 takes the input data word and determines whether or not it has a match. If it has a match, then the appropriate output is set at the end of Ø2. If there is no match, the translation proceeds no farther because no outputs are set.

At the beginning of  $\emptyset$  3, (See Figure 4-14), Array #2 samples the outputs from Array #1 and determines whether any are active. If there is a match, then the translation code is generated and fed to Array #3, also during  $\emptyset$  3.

FIGURE 4-14 Ø3 DATA FLOW

During  $\emptyset$  3, the contents of the selected byte of the Translation Register are fed to Array #3 along with the contents of the interrupt register, the Translation State Register, and the Q bit. During the later portions of  $\emptyset$  3, Array #3 determines if there is a match and, if a match is found, at the end of  $\emptyset$  3 an output is generated.

This output is fed into Array #4 at the beginning of  $\emptyset$  4. (See Figure 4-15). During  $\emptyset$ 4, Array #4 determines whether there is an active input to it. If there is an active input, the contents of the word associated with the input are sent out at the end of  $\emptyset$  4. The Array #4 word may or may not cause the Translation State Register to be loaded, and may or may not cause the Location Counter to be loaded at the next occurance of  $\emptyset$  1.

**Ø4 DATA FLOW** 4-13

#### SECTION V

#### MICRO INSTRUCTIONS

#### 5.1 INSTRUCTION REPERTOIRE

This section contains descriptions of the microinstructions. With each description is a diagram showing the format of the instruction and its operation code, given in hexadecimal. Above each diagram is the instruction mnemonic operation code, the argument needed by the assembler, and the name of the instruction. Under each diagram is a description of the command and its timing in clock cycles. It should be noted that the descriptions of the instructions are rather perfunctory. For a more thorough description of the instructions from a programmer's standpoint, the user is invited to review the MCP1600 MICRO PROGRAMMER'S MANUAL.

The purpose of this section then is to outline the structure of the instruction set as an aid to understanding the events on the two processor busses.

While the formats presented here describe 16 bits of the instruction word, be aware that the word is, in fact, 22 bits wide. The portion of the instruction described here control the operation of the processor. The other 6 bits are:

- bits 16 and 17 are involved with control of the Location Counter. Bit 16 determines whether or not the contents of the Return Register will be loaded into the Location Counter. Bit 17 determines whether or not a Read Next Instruction translation will be invoked.

These two options are available on all instructions.

- bits 18 through 21 have nothing to do with control of the MCP1600 system. They are available for the user to program as TTL levels. These bits are available on all instructions.

# 5.2 INSTRUCTION TYPES

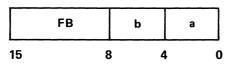

All of the MCP1600 microinstructions are 22 bits long. Of the 22 bits, the 16 least significant effect the operation of the CPU. The purposes of the other 6 bits are covered in either the Programmed Translation Array description or the Micro Instruction Bus description.

The instructions for the MCP1600 are divided into four classes as follows:

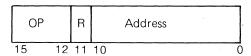

# JUMP FORMAT

This format provides an 11-bit Control ROM address. It causes an unconditional jump to any location in the permissable MICROM address space by always asserting the jump control line (JXX on the Data Chip or MIB 15 on the Micro Instruction Bus). The unconditional jump instruction is the only one that utilizes this format.

Unconditional jump instructions always take two clock cycles; one to decode the instruction, the second to load the Location Counter on the Control Chip.

A special case of this format is the Return From Subroutine instruction, covered later.

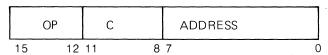

# CONDITIONAL JUMP FORMAT

This format provides a Jump address within a page. This instruction is substantially the same as the Unconditional Jump format, with exception of the reduced address space. It is also a two cycle instruction, with the jump decision (based upon the contents of the C Field) being made by the jump

decode logic on the Data Chip during the first cycle. This decision is communicated to the Control Chip via MIB15 (JXX on the Data Chip). During the second cycle the jump is affected.

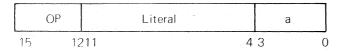

#### LITERAL FORMAT

This format provides 8-bit literal data. The "a" field usually specifies a file register. These instructions invoke the 'literal path' to fetch data around the register file for the 'b' input to the ALU. All of these instructions execute in one clock cycle.

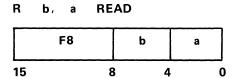

#### REGISTER FORMAT

This format is by far the predominant one. In it, 'b' and 'a' are register file designators. Generally, depending upon the operation, there can be two meanings to the register designators:

as, for instance, in a shift or move instruction

as, for instance, in an arithmetic instruction.

'b' and 'a' can specify either a single byte data quantum or a word (double byte) data quantum. In this latter case, the designators usually point to the even addressed member of a register pair. While they may both point to an odd addressed pair, note carefully the instructions description for the effect.

If the designators apply to a word data quantum, the instruction takes two cycles to execute. The following sections describe MCP1600 instructions by classes of function.

#### 5.3 MCP 1600 MICRO-INSTRUCTION SET

The following micro-instructions are contained in the MCP 1600. The symbology used is listed in the table below:

| Symbols      | Meaning                                                           |

|--------------|-------------------------------------------------------------------|

|              | is transferred to                                                 |

| ( )          | contents of location or register                                  |

| $\wedge$     | Logic Product (AND)                                               |

|              | Inclusive "or"                                                    |

| <b>→</b>     | Exclusive "or"                                                    |

| Rx: Ry       | Forms extended register Ry = LSB, Rx = MSB                        |

| Ra           | The register specified by the micro-instruction "a" field         |

| Rb           | The register specified by the micro-instruction "b" field         |

| Flag Setting | Designates no category                                            |

| X            | Don't care condition                                              |

| Ø            | Flag cleared (set to $\emptyset$ )                                |

| 1            | Flag set                                                          |

| ·            | Flag not affected                                                 |

| *            | Set according to function (see flag description in Section 5.3.2) |

|              |                                                                   |

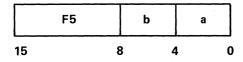

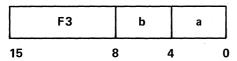

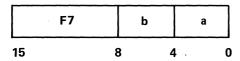

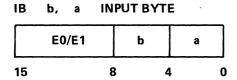

## 5.3.1 TABLE OF MICRO-INSTRUCTIONS

| Instruction                     | OP Code | Mnemonic          | Microcycles | Description of Operation                                                                                                                        |

|---------------------------------|---------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump                            | Ø(Ø)    | JMP               | 2           | (MIR1Ø-ØØ)+(LC) Jump unconditionally<br>to microm location specified by MIR1Ø-ØØ                                                                |

| Return from Subroutine          | Ø(1)    | RFS               | 2           | (RR)+(LC) Restore return address from subroutines                                                                                               |

| Jump if ZB False                | 1Ø      | J <b>Z</b> BF     | 2           | If ZB = Ø, (MIR Ø7-ØØ)→(LC7-Ø) jump<br>conditionally within microm page                                                                         |

| Jump if <del>Z</del> B True     | 11      | J <del>Z</del> BT | 2           | If <del>Z</del> B=1, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                         |

| Jump if C8 False                | 12      | JC8F              | 2           | If C8=Ø, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                     |

| Jump if C8 True                 | 13      | JC8T              | 2           | If C8=1, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                     |

| Jump if ICS False               | 14      | JIF               | 2           | If ICS=Ø, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                                    |

| Jump if ICS True                | 15      | JIT               | 2           | If ICS=1, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                    |

| Jump if NB False                | 16      | JNBF              | 2           | If NB=Ø, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                                     |

| Jump if NB True                 | 17      | JNBT              | 2           | If NB-1, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                     |

| Jump if Z False                 | 18      | J <del>Z</del> F  | 2           | If <del>Z</del> =Ø, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                          |

| Jump if ₹ True                  | 19      | J <del>Z</del> T  | 2           | If <del>Z</del> =1, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                          |

| Jump if C False                 | 1A      | JCF               | 2           | If C=Ø, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                      |

| Jump if C True                  | 1B      | JCT               | 2           | If C=1, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                                      |

| Jump if V False                 | 1C      | JVF               | 2           | If V=Ø, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                      |

| Jump if V True                  | 1D      | JVT               | 2           | If V=1, (MIRØ7-ØØ)→(LC7-Ø)                                                                                                                      |

| Jump if N False                 | 1E      | JNF               | 2           | If N=Ø, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                                      |

| Jump if N True                  | 1F      | JNT               | 2           | If N=1, (MIRØ7-ØØ)+(LC7-Ø)                                                                                                                      |

| Add Literal                     | 2       | AL                | 1           | (Ra)+Literal+Ra the 8 bit constant is added to Ra                                                                                               |

| Compare Literal                 | 3 .     | CL                | · 1         | (Ra)-Literal. The 8 bit result of the literal is compared against Ra and the approprate flags set.                                              |

| And Literal                     | 4       | NL                | 1           | (Ra)∧ Literal + (Ra) The 8 bit result of a logical product of Ra and the literal are coded into Ra.                                             |

| Test Literal                    | 5       | TL                | 1           | (Ra) Λ Literal The 8 bit result of the logical product of Ra and the literal set condition Flags. The contents of Ra are unaffected.            |

| Load Literal                    | 6       | LL                | . 1         | Literal+(Ra). The 8 bit literal is                                                                                                              |

|                                 | 7.0     | 0.1               |             | loaded into Ra.                                                                                                                                 |

| Reset Interrupts                | 7Ø      | RI                |             | The three software interrupts I4, I5, and I6 are reset as indicated in the instruction's b field.                                               |

| Set Interrupts                  | 71      | SI                | 1           | The three software interrupts I4, I5, and I6 are set as indicated in the instruction's b field.                                                 |

| Copy Condition Flags            | 72      | CCF               | 1           | Flags•(Ra) The four condition flags and four ALU status flags are loaded in Ra                                                                  |

| Load Condition Flags            | 73      | LCF               | 1           | (Ra)→Flags. The contents of Ra are transferred to the ALU status flags unconditionally and to the condition flags under control of the b field. |

| Reset TSR                       | 74      | RTSR              | 1           | Ø+(TSR). The three TSR bits in the control chip are reset.                                                                                      |

| Load G Low                      | 75      | LGL               | 1           | (Ra) 2-Ø +(G). The three least significant bits of Ra are loaded into the G register.                                                           |

| Conditionally Increment<br>Byte | 76      | CIB               | 1           | If C8 is set, (Ra)+I → (Ra)                                                                                                                     |

| Conditionally Decrement<br>Byte | 77      | CDB               | , 1         | If C8 is set, (Ra)-I $\rightarrow$ (Ra)                                                                                                         |

| Instruction (              | OP Code | Mnemonic | Microcycles | Description of Operation                                                                                                                                                              |

|----------------------------|---------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Move Byte                  | 80/81   | MB       | 1           | (Rb)+(Ra). The 8 bit contents of Rb are transferred to Ra. Rb is unaffected.                                                                                                          |

| Move Word                  | 82/83   | MW       | 2 ,         | (Rb)+(Ra). The 16 bit contents of Rb+I:Rb are transferred to Ra+1:Ra. Rb+I and Rb are unaffected.                                                                                     |

| Conditionally Move Byte    | 84/85   | CMB      | 1           | (Rb)+(Ra), if C=I. The 8 bit contents of Rb are transferred to Ra if the carry flag is set from a previous operation.                                                                 |

| Conditionally Move Word    | 86/87   | CMW      | 2           | (Rb)+(Ra), if C=I. The 16 bit contents of Rb+I:Rb are transferred into Ra+I: Ra if the carry flag is set from a previous operation.                                                   |

| Shift Left Byte with Carry | 88/89   | SLBC     | 1           | (Rbm)+(Ram+I), (carry) + (Raφ). The 8 bit contents of Rb are shifted left one bit and loaded into Ra. The contents of the carry flag is inserted into the vacated low position of Ra. |

| Shift Left Word with Carry | 8A/8B   | SLWC     | 2           | (Rbm)+(Ram+I), (carry)+(Ra Ø). The 16<br>bit contents of Rb+I:Rb are shifted left                                                                                                     |

|                            |         |          |             | one bit and loaded into Ra+I:Ra. The contents of the carry flag is inserted into the vacated low position of Ra.                                                                      |

| Shift Left Byte            | 8C/8D   | SLB      | 1           | (Rbm)+(Ram+I) The 8 bit contents of Rb are shifted left one bit and loaded into Ra.                                                                                                   |

| Increment Byte by 1        | 90/91   | ICBI     | 1           | (Rb)+I+(Ra). The 8 bit contents of Rb are incremented by one and the result is transferred to Ra.                                                                                     |

| Increment Word by 1        | 92/93   | ICWI     | 2           | (Rb)+I+(Ra). The 16 bit contents of Rb+I:Rb are incremented by one and the result                                                                                                     |

| Increment Byte by 2        | 94/95   | ICB2     | 1           | transferred to Ra+I:Ra. (Rb)+2+(Ra). The 8 bit contents of Rb are incremented by two and the result transferred to Ra.                                                                |

| Increment Word by 2        | 96/97   | ICW2     | 2           | (Rb)+2+(Ra). The 16 bit contents of Rb+I:Rb are incremented by two and the result transferred to Ra+I:Ra.                                                                             |

| Twos Complement Byte       | 98/99   | TCB      | 1           | (Rb)+I+Ra. The 8 bit contents of Rb are two's complemented and transferred to Ra.                                                                                                     |

| Twos Complement Word       | 9A/9B   | TCW      | 2           | (Rb)+I+Ra. The 16 bit contents of Rb+I<br>Rb are two's complemented and transferred<br>to Ra+I:Ra.                                                                                    |

| Ones Complement Byte       | 9C/9D   | OCB      | 1           | (Rb)+Ra. The 8 bit contents of Rb are one's complemented and transferred to Ra.                                                                                                       |

| One's Complement Word      | 9E/9F   | OCW      | 2           | (Rb)+Ra. The 16 bit contents of Rb+I: Rb are one's complemented and transferred to Ra+I:Ra.                                                                                           |

| Add Byte                   | AØ/AI   | АВ       | 1           | (Rb)+(Ra)+(Ra). The 8 bit contents of Rb are added to Ra and loaded into Ra.                                                                                                          |

| Add Word                   | A2/A3   | AW       | 2           | (Rb)+(Ra)+(Ra). The 16 bit contents of Rb+I:Rb are added to Ra+I:Ra and loaded into Ra+I:Ra.                                                                                          |

| Conditionally Add Byte     | A4/A5   | САВ      | . 1         | (Rb)+(Ra)+(Ra), if C=I. The 8 bit contents of Rb are added to Ra and the result is transferred to Ra if the carry flag is set from a previous operation.                              |

| Conditionally Add Word     | A6/A7   | CAW      | 2           | (Rb)+(Ra)+(Ra), if C=I. The 16 bit contents<br>of Rb+1:Rb are added to Ra+I:Ra and<br>the result is transferred to Ra+I;Ra if<br>the carry flag is set from a previous                |

| Add Byte with Carry        | A8/A9   | ABC      | 1           | operation.  (Rb)+(Ra)+C+(Ra). The 8 bit sum of the contents of Rb plus the carry flag are added to Ra and the result is transferred to Ra.                                            |

| Instruction                                          | OP Code      | Mnemonic | Microcycles | Description of Operation                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------|--------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add Word with Carry                                  | AA/AB        | AWC      | 2           | (Rb)+(Ra)+C+(Ra). The 16 bit sum of the contents of Rb+1:Rb plus the carry flag are added to Ra+1:Ra and the result is transferred to Ra+1:Ra.                                                                                                                                                                                                                                           |

| Conditionally Add Digits                             | AC           | CAD      | 1           | (Rb) <sub>3-0</sub> +(Ra) <sub>3-0</sub> +(Ra) <sub>3-0</sub> , if C4=0<br>(Rb) <sub>7-4</sub> +(Ra) <sub>7-0</sub> +(Ra) <sub>7-4</sub> , if C8=0<br>The 4 least significant and/or 4 most significant<br>bits of Rb are added to their corresponding<br>bits in Ra if C4 or C8 are reset respectively<br>from a previous operation. This allows for<br>decimal arithmetic corrections. |

| Conditionally Add Word<br>on Indirect Condition Stat | AE/AF<br>tus | CAWI     | 2           | (Rb)+(Ra)+(Ra), if ICS=I. The 16 bit contents of Rb+I:Rb are added to Ra+I:Ra and the results transferred to Ra+I:Ra if the ICS code is set from a prior operation. This instruction allows address displacement addition on Branch conditions.                                                                                                                                          |

| Subtract Byte                                        | BØ/BI        | SB       | 1           | (Ra)-(Rb)+(Ra). The 8 bit contents of Rb are subtracted from Ra and the result loaded into Ra.                                                                                                                                                                                                                                                                                           |

| Subtract Word                                        | B2/B3        | s SW     | 2           | (Ra)-(Rb)-(Ra). The 16 bit contents of Rb+1:Rb are subtracted from Ra+1:Ra and the results loaded into Ra+1:Ra.                                                                                                                                                                                                                                                                          |

| Compare Byte                                         | B4/B5        | СВ       | 1           | (Ra)-(Rb). The 8 bit difference between the contents of Ra and Rb is used to set the status flags at all times and the condition flags if OP code B5 is selected Registers Ra and Rb are not changed.                                                                                                                                                                                    |

| Compare Word                                         | B6/B7        | CW       | 2           | (Ra)-(Rb). The 16 bit difference between the contents of Ra+I:Ra and Rb+I:Rb are used to set the status flags at all times and the condition flags if OP Code B7 is selected. Registers Ra+I:Ra and Rb+I:Rb are not changed.                                                                                                                                                             |