Caviar AC160/AC2120 Technical Reference Manual

# WESTERN DIGITAL

#### Copyright © 1993 Western Digital Corporation All Rights Reserved

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change specifications at any time without notice.

Western Digital, AutoSwitch, and Paradise are registered trademarks and CacheFlow, Caviar, FIT Lab, Hyperseek, Interarchitecture, PinScan, Piranha, SAM, Tidbit, and TrueShade are trademarks of Western Digital Corporation.

Other marks may be mentioned herein that belong to other companies.

#### Western Digital Corporation

Western Digital Plaza, 8105 Irvine Center Drive, Irvine, CA 92718

For Service and Literature, call: (714) 932-4900

# CONTENTS

| 1.0 | DESCRI   | PTIONS A       | ND FEATURES                      |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 1  |

|-----|----------|----------------|----------------------------------|--------------|--------|------|-------|------|-----|---|---|---|---|---|---|---|---|---|---|----|

|     | 1.1      | GENERA         | L DESCRIPTION                    |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 1  |

|     | 1.2      | ADVANO         | CED PRODUCT FE                   | ATURES       | •      | •    |       | •    | •   | • | • |   | • | • | • |   | • | • | • | 2  |

| 2.0 | SPECIFI  | CATIONS        | MANCE SPECIFIC                   |              |        |      |       | •    |     |   |   |   |   |   |   |   |   |   |   | 5  |

|     | 2.1      | PERFOR         | MANCE SPECIFIC                   | CATIONS      |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 5  |

|     | 2.2      | PHYSICA        | L SPECIFICATIO                   | NS           |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 6  |

|     |          | 2.2.1          | Physical Dimen                   | sions .      |        |      |       |      |     |   |   |   |   |   |   |   |   | _ |   | 7  |

|     |          | 2.2.2          | Weight .                         |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 7  |

|     |          | 2.2.3          | Mechanical Spe                   | ecifications |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 8  |

|     | 2.3      | ELECTRI        | CAL SPECIFICATI                  |              |        |      |       |      |     |   |   |   | • |   | • |   |   |   | • | 9  |

|     |          | 2.3.1          | Typical Current                  | And Power    | Dis    | sip  | atio  | n    |     |   |   |   |   |   |   |   |   |   |   | 9  |

|     |          | 2.3.2          | Power Manager                    | ment - Driv  | e S    | pinr | ina   |      |     |   |   |   |   |   |   |   |   |   |   | 9  |

|     |          | 2.3.3          | Power Manager                    | ment - Driv  | e N    | ot S | bin   | ninc |     |   |   |   |   |   |   |   |   |   |   | 10 |

|     |          | 2.3.4          | Ripple .                         |              |        |      | г<br> |      | · . |   |   |   |   |   |   |   |   |   |   | 10 |

|     |          | 2.3.5          | Ripple<br>Power Connecto         | ors and Cat  | oles   |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 11 |

|     | 2.4      | ENVIRON        | MENTAL SPECI                     | FICATIONS    | ,<br>, |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 12 |

|     |          | 2.4.1          | Shock and Vibra                  | ation .      |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 12 |

|     |          | 2.4.2          | Temperature an                   | d Humidity   | •      |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 12 |

|     |          | 2.4.3          | Atmospheric Pro                  |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     |          | 2.4.4          | Acoustics                        |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     | 2.5      | AGENCY         | APPROVALS                        |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     | 2.6      | Reliabil       | ITY SPECIFICATI                  | ON.          |        | •    |       |      |     | • |   |   | • | • |   |   |   |   |   | 13 |

| 3.0 | DDINICIE |                |                                  |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   | 10 |

| 3.0 | 3.1      |                |                                  |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     | 3.1      |                |                                  | hastar Diel  |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     |          | 3.1.1<br>3.1.2 | WD42C22 Wind                     |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     |          |                | Buffer RAM                       |              | •      | •    | • •   | •    | •   | • | • | · | • | ٠ | · | · | • | • | • | 10 |

|     |          | 3.1.3<br>3.1.4 | WD60C11 Serve                    |              | ſ      | ·    |       | •    | •   | • | • | • | • | • | · | · | • | • | • | 10 |

|     |          | 3.1.4<br>21 F  | WD10C23 Data                     | Sebararo     |        |      | •••   | •    | ·   | • | · | · | · | • | · | · | • | • | · | 10 |

|     |          | 3.1.5<br>3.1.6 | Microprocessor<br>Pulse Detector | RUIVI and    | HAN    | Λ    | •     | •    | •   | • | · | • | • | • | • | · | · | · | · | 10 |

|     |          | J.I.D          | Pulse Detector                   | · · ·        | •      | •    | •••   | •    | •   | • | · | • | • | • | • | • | • | • | · | 10 |

|     |          | 3.1.7          | Spindle Motor E                  | Jriver .     | ·      | ·    | • •   | •    | •   | • | · | · | • | • | · | · | • | • | · | 17 |

|     |          |                | Actuator Driver                  |              | •      | •    | • •   | •    | •   | • | · | · | • | • | · | · | · | • | · | 17 |

|     |          | 3.1.9          | Gate Array Fusio                 |              |        |      |       |      |     |   |   |   |   |   |   |   |   |   |   |    |

|     |          | 3.1.10         | Frequency Synth                  | nesizer      | •      | •    |       | •    | •   | • | • | · | • | • | • | • | • | • | • | 17 |

|     | 3.2        | HEAD D         | ISK ASSEMBLY                   | (HDA)                                  |       |      |     |     |      | •   |     |   |   |   |   |   |   | • | • | . 20 |

|-----|------------|----------------|--------------------------------|----------------------------------------|-------|------|-----|-----|------|-----|-----|---|---|---|---|---|---|---|---|------|

|     |            | 3.2.1          | Base/Cover As                  | sembly                                 |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 20 |

|     |            | 3.2.2          | Spindle Motor                  |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 3.2.3          | Disk Stack As                  | sembly                                 |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 21 |

|     |            | 3.2.4          | Headstack Ass                  | sembly                                 |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 21 |

|     |            | 3.2.5          | Voice Coil Ass                 | embly                                  |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 21 |

|     |            | 3.2.6          | Air Filtration S               | ystem                                  |       |      |     |     | •    | •   |     |   |   |   |   |   | • |   |   | . 22 |

| 4.0 |            | רבה מסחו       | DUCT FEATURES                  | -<br>-                                 |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | 22   |

| 4.0 | 4.1        | CACHEF         |                                | •••••••••••••••••••••••••••••••••••••• |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.1        | 4.1.1          | Purpose of Ca                  |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 4.1.1          | Benefits of Ca                 |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 4.1.Z<br>4.1.3 |                                |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 4.1.3<br>4.1.4 | CacheFlow Op                   |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 4.1.4          | Sequential Mo<br>Repetitive Mo | do .                                   | •     | •    | •   | •   | •    | •   | • • | • | • | • | · | · | · | · | · | . 24 |

|     | 4.2        |                | MANAGEMEN                      | UC .<br>TANIDE(                        | אוסר  | лт   | •   | •   | •    | •   | • • | • | • | · | • | • | • | • | • | . 24 |

|     | 4.2        |                | CTERISTICS                     |                                        | ואוחנ | AI   |     |     |      |     |     |   |   |   |   |   |   |   |   | 26   |

|     |            | 4.2.1          |                                |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 4.2.1          | Defect Manag<br>Format Charac  | toriotico                              | •     | ·    | •   | •   | •    | •   | ••• | • | · | • | • | • | • | • | • | . 20 |

|     | 4.3        |                |                                |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.3<br>4.4 | TRANSL         |                                | · · ·                                  |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.4<br>4.5 |                | RIVE OPTION                    |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.5<br>4.6 |                | CONSERVATION                   |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.0<br>4.7 |                | MPATIBILITY                    |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.7<br>4.8 | BLOCK N        |                                | · · ·                                  |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.0<br>4.9 |                | RECORDING                      | · · ·                                  |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     | 4.9        | LUNED          |                                | •••                                    | •     | •    | ·   | •   | •    | • • | •   | • | • | • | • | • | • | • | · | . 30 |

| 5.0 | HOST IN    | TERFACE        | AND AT COM                     | MAND SI                                | ΞT    |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 31 |

|     | 5.1        | J2 PIN A       | SSIGNMENTS                     |                                        |       |      |     |     |      |     | •   | • |   |   |   |   |   |   |   | . 31 |

|     | 5.2        | HOST IN        | ITERFACE REGI                  | STERS                                  |       |      |     |     |      |     | •   |   |   |   |   |   |   |   |   | . 34 |

|     |            | 5.2.1          | Register Addre                 | ess Map                                |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 34 |

|     |            | 5.2.2          | Data Register                  |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 34 |

|     |            | 5.2.3          | Error Register                 |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

|     |            | 5.2.4          | Write Precomp                  | pensation                              | n Reg | gist | er  |     |      |     | •   |   |   |   |   |   |   |   |   | . 37 |

|     |            | 5.2.5          | Sector Count F                 | legister                               |       |      |     |     |      |     | •   |   |   |   |   |   |   |   |   | . 37 |

|     |            | 5.2.6          | Sector Numbe                   | r Registe                              | r     |      |     |     |      |     | •   |   |   |   |   |   |   |   |   | . 37 |

|     |            | 5.2.7          | Cylinder Low A                 | And Cylin                              | der l | Hig  | h R | egi | stei | rs  |     |   |   |   |   |   |   |   |   | . 38 |

|     |            | 5.2.8          | SDH Register                   |                                        |       |      |     | -   |      |     |     |   |   |   |   |   |   |   |   | . 39 |

|     |            | 5.2.9          | Status Registe                 |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 40 |

|     |            | 5.2.10         | Command Reg                    |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 41 |

|     |            | 5.2.11         | Alternate Stat                 |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 41 |

|     |            | 5.2.12         | Fixed Disk Con                 | •                                      |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 41 |

|     |            | 5.2.13         | <b>Digital Input R</b>         |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 42 |

|     | 5.3        |                | AC160/AC2120                   |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   | . 43 |

|     |            |                |                                |                                        |       |      |     |     |      |     |     |   |   |   |   |   |   |   |   |      |

# Western Digital Corporation

|            |     | 5.3.1             | Recalibrate (1XH)                         |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 44        |

|------------|-----|-------------------|-------------------------------------------|---------|-----|----|-----|-----|---|---|---|---|---|---|---|---|---|---|---|-----------|

|            |     | 5.3.2             |                                           | • •     |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 45        |

|            |     | 5.3.3             | Read Sector (2XH)                         |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            |     | 5.3.4             | Write Sector (30H)                        |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            |     | 5.3.5             | Format Track (50H)                        |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 48        |

|            |     | 5.3.6             | Read Verify (40H)                         |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 49        |

|            |     | 5.3.7             | Execute Diagnostics                       | (90H)   |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 50        |

|            |     | 5.3.8             | Set Drive Parameter                       | s (91H) | )   |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 51        |

|            |     | 5.3.9             | Write DMA (CAH)                           |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 52        |

|            |     | 5.3.10            | Read DMA (C8H)                            |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            |     | 5.3.11            | Read Multiple (C4H)                       |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 54        |

|            |     | 5.3.12            | Write Multiple (C5H                       | ) .     |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 55        |

|            |     | 5.3.13            | Set Multiple (C6H)                        |         |     | •  |     |     |   |   |   |   |   |   |   |   |   |   |   | 56        |

|            |     | 5.3.14            | Standby Immediate                         | (EOH)   |     | •  |     |     |   |   |   |   |   |   |   |   |   |   |   | 57        |

|            |     | 5.3.15            | Idle Immediate (E1H                       | ) .     |     |    |     |     |   |   |   |   |   |   |   | • |   |   |   | 58        |

|            |     | 5.3.16            | Standby (E2)                              |         |     |    | •   |     |   |   |   |   |   |   |   | • |   |   |   | 59        |

|            |     | 5.3.17            | Idle (E3H)                                |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            |     | 5.3.18            | Read Buffer (E4H)                         |         |     | •  |     |     |   |   |   |   |   |   |   |   |   |   |   | 61        |

|            |     | 5.3.19            | Check Power Mode                          | (E5)    |     |    | •   |     |   |   |   |   |   |   |   |   |   |   |   | 62        |

|            |     | 5.3.20            | Sleep (E6)                                |         |     |    | •   |     |   |   |   |   |   |   |   |   |   |   |   | 63        |

|            |     | 5.3.21            | Write Buffer (E8H)                        |         |     |    | •   |     |   |   |   |   |   |   |   |   |   |   |   | 64        |

|            |     | 5.3.22            | Identify Drive (ECH)                      |         |     |    | •   |     |   |   |   |   |   |   |   |   |   |   |   | 65        |

|            |     | 5.3.23            | Set Buffer Mode (EF                       | H)      |     |    |     |     | • |   |   |   |   |   |   |   |   |   |   | 67        |

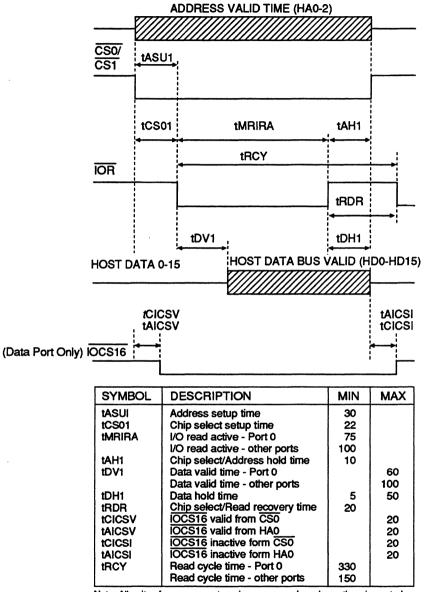

|            | 5.4 | HOST IN           | TERFACE READ TIMI                         | NG      |     |    | •   |     |   | • |   |   |   |   |   |   |   |   | • | 68        |

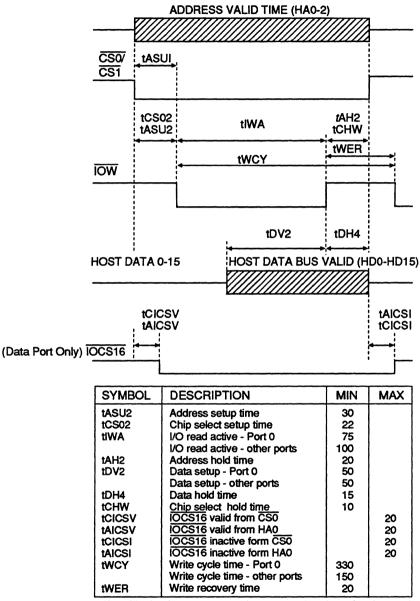

|            | 5.5 | HOST IN           | Iterface read timi<br>Iterface write tim  | ING     |     |    | •   |     |   |   |   |   |   |   |   |   |   |   | • | 69        |

|            | 5.6 | ERROR F           | Reporting                                 |         |     | •  | • • |     |   |   |   |   |   |   |   |   |   |   |   | 70        |

| <b>C</b> 0 |     |                   |                                           | 250     |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 74        |

| 6.0        |     |                   | ND SETUP PROCEDU                          | 152     | ·   | •  | • • | ••• | • | • | • | · | • | • | • | • | · | • | • | / <br>71  |

|            | 6.1 | UNPACK            |                                           | <br>•   | •   | ·  | •   | • • | · | • | • | · | · | • | • | · | · | • | • | 71        |

|            |     | 6.1.1             | Handling Precaution                       | S .<br> | • : |    | •   | ••• | • | • | • | · | • | • | · | · | · | • | · |           |

|            |     | 6.1.2<br>6.1.3    | Inspection of Shippin                     | ig con  |     |    |     | • • | · | • | • | · | · | • | • | · | · | • | · | /  <br>71 |

|            |     | 6.1.3             | Removal From Shipp                        | ing col |     | me |     | ••• | · | · | • | • | • | • | • | • | • | • | • | / I<br>72 |

|            |     | 6.1. <del>4</del> | Removal From Antist<br>Moving Precautions |         | y   |    | • • | ••• | · | • | • | · | · | • | • | · | · | • | • | 12<br>72  |

|            | 6.2 |                   | ING RESTRICTIONS                          |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            | 0.2 | 6.2.1             |                                           | · ·     |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            |     | 6.2.1             | Screw Size Limitatio                      |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 72        |

|            | 6.3 |                   | ATION CONFIGURATI                         |         |     |    |     | -   |   | • |   |   |   |   |   |   |   |   |   | 73        |

|            | 0.3 | 6.3.1             | Determining Your Co                       |         |     |    |     |     |   | • |   |   |   |   |   |   |   |   |   | 73        |

|            |     | 6.3.2             | Dual Installations                        |         |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 73        |

|            |     |                   |                                           | •••     |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   | 73        |

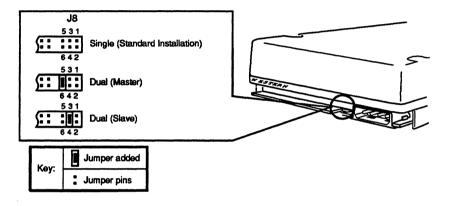

|            | 64  | 6.3.3             | Jumper Settings                           | <br>VE  |     |    |     |     |   |   |   |   |   |   |   |   |   |   |   |           |

|            | 6.4 |                   | ING THE CAVIAR DRI                        |         |     |    |     |     |   | • |   |   |   |   |   |   |   |   |   | 75        |

|            |     | 6.4.1             | Mounting the Drive                        |         |     |    |     |     |   | • |   |   |   |   |   |   |   |   |   | 75<br>75  |

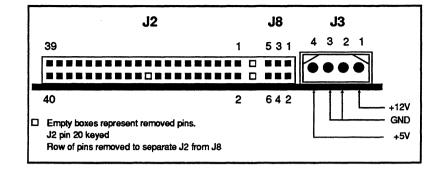

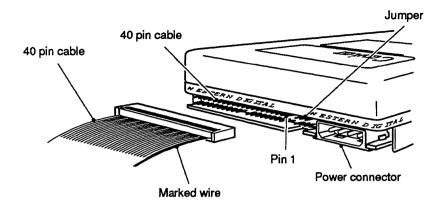

|            |     | 6.4.2             | Cabling and Installat                     | ion Ste | eps |    | • • | •   | • | • | • | • | • | • | • | • | • | • | • | 75        |

|      | 6.5<br>6.6 |           | ing the<br>Rocedur |         |       |        |       |       |     |     |    |    |     |   |   |   |   |   |   |   |   |   |    |

|------|------------|-----------|--------------------|---------|-------|--------|-------|-------|-----|-----|----|----|-----|---|---|---|---|---|---|---|---|---|----|

|      | 0.0        | 6.6.1     | Preparing          | g the ( | Cavia | ar Dri | ve f  | or Us | se  |     | •  |    |     | • |   |   | • |   |   |   | • |   | 79 |

|      |            | 6.6.2     | Selecting          |         |       |        |       |       |     |     |    |    |     |   |   |   |   |   |   |   |   |   |    |

|      |            | 6.6.3     | Partition          |         |       |        |       |       |     |     |    |    |     |   |   |   |   |   |   |   |   |   |    |

|      |            | 6.6.4     | High-lev           |         |       |        |       |       |     |     |    |    |     |   |   |   |   |   |   |   |   |   |    |

|      |            | 6.6.5     | Booting            |         |       |        |       |       |     |     |    |    |     |   |   |   |   |   |   |   |   |   |    |

|      |            | 6.6.6     | Preparing          | g the ( | Cavia | ar Dri | ve fo | or a  | Nov | ell | Ne | tw | ork |   | • |   |   | • | • |   | • | • | 82 |

| 7.0  | MAINTE     | NANCE     |                    |         |       |        | •     |       | •   | •   |    | •  |     | • | • |   |   | • | • | • | • | • | 83 |

| 8.0  | WESTER     | IN DIGITA | l drive i          | JTILIT  | Υ.    |        | •     |       | •   |     | •  | •  | •   | • | • | • | • | • | • | • | • | • | 85 |

| 9.0  | TROUBLI    | eshootii  | NG.                |         |       | •      | •     |       | •   |     |    | •  |     | • | • |   | • |   | • |   |   |   | 87 |

| 10.0 | GLOSSA     | RY.       |                    |         |       | •      | •     |       |     | •   |    |    | •   | • | • | • |   |   |   |   |   |   | 89 |

# **FIGURES**

| Figure 2-1. | Caviar AC160/AC2120 Mounting Dimensions        | 8 |

|-------------|------------------------------------------------|---|

| Figure 2-2. | +12V Current Draw During Spin Up (Master Mode) | 0 |

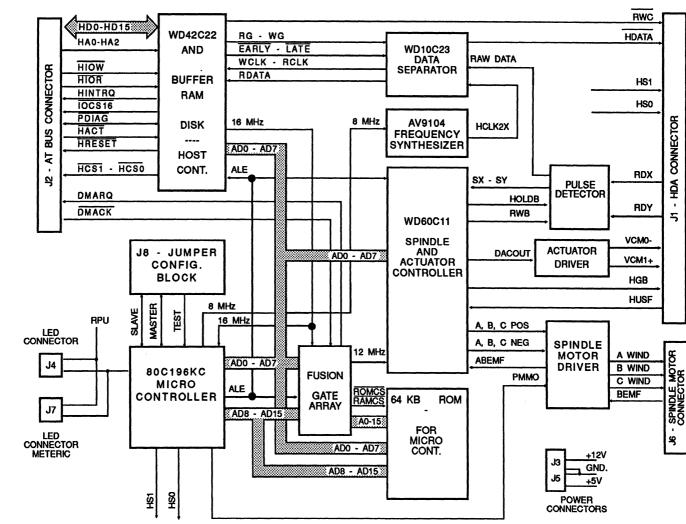

| Figure 3-1. | Caviar Block Diagram                           | 8 |

| Figure 3-2. | Mechanical Exploded View AC2120                |   |

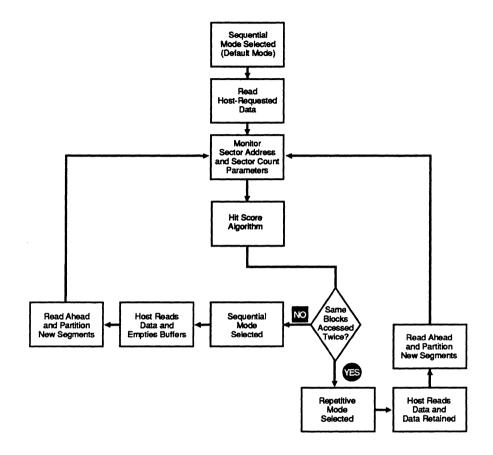

| Figure 4-1. | CacheFlow                                      |   |

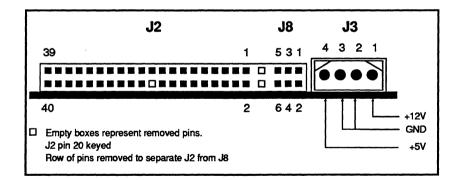

| Figure 5-1. | Standard Factory Connectors                    |   |

| Figure 5-2. | Host Interface Read Timing                     |   |

| Figure 5-3. | Host Interface Write Timing                    |   |

| Figure 6-1. | Jumper Settings                                |   |

|             | Standard Factory Connectors                    |   |

| Figure 6-3. | Caviar Connector Locations                     |   |

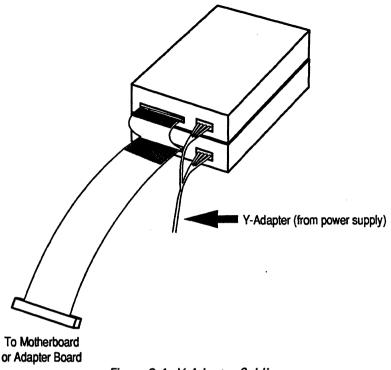

| Figure 6-4. | Y-Adapter Cabling                              |   |

# **TABLES**

| Table 5-1. | J2 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5-2. | Task File Map         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         < |

| Table 5-3. | Standard Command Opcodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 5-4. | Identify Drive Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 5-5. | Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 6-1. | Drive Table Parameters         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .  |

#### **Radio Frequency Interference Statement**

This Western Digital product has been verified to comply with the limits for a Class B computing device pursuant to Part 15, subpart B, of FCC rules. This does not guarantee that interference will not occur in individual installations.

Western Digital is not responsible for any television, radio, or other interference caused by unauthorized modifications of this product.

If interference problems do occur, please consult the system equipment owner's manual for suggestions. Some of these suggestions include the relocation of the computer system away from the television or radio, or placing the computer AC power connection on a different circuit or outlet.

This digital apparatus does not exceed the Class B limits for radio noise for digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications.

Western Digital Corporation

# **1.0 DESCRIPTIONS AND FEATURES**

### **1.1 GENERAL DESCRIPTION**

The Caviar series of Western Digital intelligent drives provides 62/125 megabytes of formatted storage in a 3.5-inch form factor and low profile 1-inch height. Designed for use in AT-compatible systems, Caviar is the premier storage solution that achieves unsurpassed reliability and optimum performance.

Caviar features CacheFlow, Western Digital's exclusive multi-segmented adaptive disk caching system, which dynamically partitions the 32-KByte buffer and adapts during disk operations to the optimum caching mode to dramatically enhance read performance. To meet the demands of high performance 80386, 80386SX, 80486 and 80486SX systems, Caviar has an average seek time of less than 15 milliseconds.

Caviar drives are preformatted (low-level) and defects are mapped out before shipment. Additional Caviar features include:

- Linear logical/physical address translation

- Automatic head parking

- Embedded servo control data on each track

- DMA and Block Mode data transfers

- Cache Flow

- Power Conservation

- 56-bit error correction code

Western Digital offers reliable, cost-effective storage solutions by integrating design and manufacturing into a process known as interarchitecture. Critical computer functions, including storage, intelligent drive control, core logic, video and communication functions are integrated into a variety of platform-specific solutions. Designers in each arena work closely with each other, developing solutions with a first-hand knowledge of all the components that interact in the platform. This interaction between component designers means Western Digital can guarantee compatibility and build in exclusive functionality.

### **1.2 ADVANCED PRODUCT FEATURES**

### CacheFlow

Designed exclusively by Western Digital to minimize disk-seeking operations and rotational latency delays, CacheFlow is the industry's first adaptive, multi-segmented disk caching system. CacheFlow constantly evaluates not only the size of the data request but the type of data request, that is, whether the application is sequential, random, or repetitive. CacheFlow then dynamically partitions the Caviar's 32-KByte (optional 64-KByte) RAM buffer into equal-sized segments and selects the appropriate caching mode for optimum system performance.

### **Power Conservation**

The Caviar supports the ATA Power management command set. This command set allows the host to reduce the power consumption of the drive by issuing a variety of power management commands. In addition the Caviar provides a vendor-unique power saving feature which results in a substantial saving of average power consumption while the drive is spinning at its rated speed.

### DMA

ATA compatible DMA Read and DMA Write commands are supported in systems implementing EISA type B DMA. DMA data transfers provide significant improvements in data transfer rates and CPU bandwidth over conventional PIO data transfers. The system CPU is freed up allowing it to accomplish other tasks while the Caviar drive transfers data directly with the system memory.

### Zoned Recording

The AC160/AC2120 drives employ Zoned Recording to increase the data density on the outer tracks of the drive. The outermost tracks contain 20% more sectors than the innermost tracks, thereby increasing the total capacity of the drive.

### **Block Mode**

ATA compatible Read Multiple and Write Multiple commands are supported. The maximum blocking factor for the Caviar drive with 32 KB of CacheFlow buffer is eight sectors. Block mode increases overall data transfer rates by transferring more data between system interrupts.

#### Automatic Head Parking

Head parking is automatic with the Caviar series of intelligent drives. On power down, the heads retract to a safe, non-data landing zone and lock into position, improving data integrity and resistance to shock.

### **Advanced Defect Management**

The Caviar is preformatted (low level) at the factory and comes with a full complement of defect management functions. Extensively tested during the manufacturing process, media defects found during intelligent burn in are mapped out with Western Digital's high performance defect management technique. No modifications are required before installation.

### **Embedded Sector Servo Control**

The Caviar features an embedded sector servo as the means of providing feedback information to the head position servo system. The embedded information precedes each data sector and provides position updates on a sector by sector basis. This high sampling rate supports the servo bandwidth required for fast access times as well as highly accurate head positioning.

The Caviar records servo data on every sector for precise head positioning.

### **Dual Drive Operation**

The Caviar supports dual drive operation by a means of a "daisy chain" cable assembly and configuration options for master or slave drive designation.

### Intelligent Drive

The Caviar does not require a slot-mounted controller card. The hard disk has the controller circuitry and 40-pin ATA IDE connector attached directly to the drive.

### Universal Data Translation

The Caviar provides a linear disk address translator to convert logical sector addresses to physical sector addresses which provides for easy installation and compatibility with numerous drive types.

### Error Recovery

Caviar uses a 56-bit Error Correction Code (ECC) for automatic detection and correction of errors in the data field.

### **Guaranteed Compatibility**

Western Digital performs extensive testing in its Functional Integrity Testing Labs (FIT Lab.) to ensure compatibility with AT-compatible computers and standard operating systems.

. -

## 2.0 SPECIFICATIONS

### 2.1 PERFORMANCE SPECIFICATIONS

| Average Seek *             | Sub-15 Milliseconds              |

|----------------------------|----------------------------------|

| Track-to-Track Seek        | 6 Milliseconds                   |

| Maximum Seek               | 28 Milliseconds                  |

| Index Pulse Period         | 16.67 Milliseconds               |

| Average Latency            | 8.34 Milliseconds                |

| Rotational Speed           | 3605 Revolutions/min.            |

| Controller Overhead        | 0.3 Milliseconds average         |

| Data Transfer Rate         | -                                |

| - Buffer to Disk           | Zone 1 = 15.375 Mbits/second     |

|                            | Zone 2 = 12.5 Mbits/second       |

| - Buffer to Host **        | 6.0 MBytes/second                |

| Interleave                 | 1:1                              |

| Buffer Size                | 32-KByte Static RAM (64-KByte    |

|                            | optional)                        |

| Error Rate - Recoverable   | <1 in 10 <sup>10</sup> bits read |

| Error Rate - Unrecoverable | <1 in 10 <sup>12</sup> bits read |

| Spindle Start Time         | 5 seconds typical,               |

| -                          | 15 seconds maximum               |

| Spindle Stop Time          | 6 seconds                        |

| Start/Stop Cycles          | 10,000 cycles minimum            |

| • •                        | ·                                |

- "Average Seek" is determined by dividing the total time required to seek between all possible ordered pairs of track addresses by the total number of all ordered pairs.

- \* \* "Data Transfer Rate from the Buffer to the Host" is based on the sustained transfer of buffered data in MBytes per second.

### 2.2 PHYSICAL SPECIFICATIONS

| Physical<br>Specifications                                                                                                                           | Caviar AC160                                     | Caviar AC2120                            |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| Recommended Setup<br>Parameters *                                                                                                                    | 1024 x 7 x 17<br>(Cyl x Hd x SPT)                | 872 x 8 x 35<br>(Cyl x Hd x SPT)         |  |  |  |  |  |  |

| Formatted Capacity                                                                                                                                   | 62.4 MBytes                                      | 125 MBytes                               |  |  |  |  |  |  |

| Interface                                                                                                                                            | 40-pin PC/AT IDE                                 | 40-pin PC/AT IDE                         |  |  |  |  |  |  |

| Actuator Type                                                                                                                                        | Rotary Voice Coil                                | Rotary Voice Coil                        |  |  |  |  |  |  |

| Number of Disks                                                                                                                                      | 1                                                | 2                                        |  |  |  |  |  |  |

| Data Surfaces                                                                                                                                        | 2                                                | 4                                        |  |  |  |  |  |  |

| Number of Heads (Hd)                                                                                                                                 | 2                                                | 4                                        |  |  |  |  |  |  |

| Number of Cylinders (Cyl)                                                                                                                            | Zone 1 = 970<br>Zone 2 = 379                     | Zone 1 = 970<br>Zone 2 = 379             |  |  |  |  |  |  |

| Average Track Density                                                                                                                                | 1712 TPI                                         | 1712 TPI                                 |  |  |  |  |  |  |

| Formatted Cylinder<br>Capacity (Bytes)                                                                                                               | Zone 1 = 48,640<br>Zone 2 = 40,448               | Z1 = 97,280<br>Z2 = 80,896               |  |  |  |  |  |  |

| Bytes per Sector                                                                                                                                     | 512                                              | 512                                      |  |  |  |  |  |  |

| User Sectors per Drive                                                                                                                               | 122,091                                          | 244,182                                  |  |  |  |  |  |  |

| Physical Sectors<br>per Track (SPT)                                                                                                                  | Z1 = 48<br>Z2 = 40                               | Z1 = 48<br>Z2 = 40                       |  |  |  |  |  |  |

| User Sectors per<br>Cylinder                                                                                                                         | Z1 = (2 x 48) - 1 = 95<br>Z2 = (2 x 40) - 1 = 79 | (4 x 48) - 2 = 190<br>(4 x 40) - 2 = 158 |  |  |  |  |  |  |

| Servo Type                                                                                                                                           | Embedded                                         | Embedded                                 |  |  |  |  |  |  |

| Recording Method                                                                                                                                     | 2,7 RLL                                          | 2,7 RLL                                  |  |  |  |  |  |  |

| Recording Density                                                                                                                                    | 33,666 BPI                                       | 33,666 BPI                               |  |  |  |  |  |  |

| Flux Density 22,444 FCI 22,444 FCI                                                                                                                   |                                                  |                                          |  |  |  |  |  |  |

| ECC                                                                                                                                                  | 56 bit                                           | 56 bit                                   |  |  |  |  |  |  |

| Head Park**                                                                                                                                          | Automatic Head<br>Parking                        | Automatic Head<br>Parking                |  |  |  |  |  |  |

| BPI - Bits Per InchRLL - Run Length LimitedFCI - Flux Changes Per InchSPT - Sectors Per TrackIDE - Integrated Drive ElectronicsTPI - Tracks Per Inch |                                                  |                                          |  |  |  |  |  |  |

### Western Digital Corporation

- \* Do not exceed the maximum sector capacity (122,091 sectors for Caviar AC160 and 244,182 sectors for Caviar AC2120) when specifying the number of cylinders, heads and sectors per track. Exceeding the specified limits results in the drive parking, spinning down and the disk controller returning an ID NOT FOUND error to the host.

- \*\* Seeking to a sector greater than or equal to maximum cylinder, parks the read/write heads and spins down the drive. Turning the system power off causes the Caviar to perform an automatic head park operation.

### 2.2.1 Physical Dimensions

| Height | 1.00 inch (+0.02)   |

|--------|---------------------|

| Length | 5.75 inches (+0.02) |

| Width  | 4.00 inches (+0.02) |

### 2.2.2 Weight

| Weight 1.12 Pounds (.508 grams) |

|---------------------------------|

|---------------------------------|

### 2.2.3 Mechanical Specifications

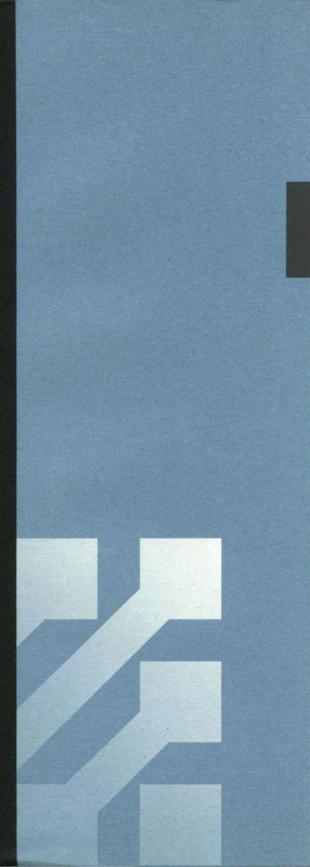

Figure 2-1 shows the mounting dimensions and locations of the screw holes for the Caviar intelligent drive.

Figure 2-1. Caviar AC160/AC2120 Mounting Dimensions

### 2.3 ELECTRICAL SPECIFICATIONS

| Operating Mode | Current,            | Power, Average      |        |

|----------------|---------------------|---------------------|--------|

|                | 12 VDC ±5%          | 5 VDC ±5%           |        |

| Read           | .24 A               | .30 A               | 4.38 W |

| Write          | .24 A               | .30 A               | 4.38 W |

| Random Seek    | .28 A               | .30 A               | 4.86 W |

| Spin up        | .60 A<br>.80 A Max. | .30 A<br>.35 A Max. | 8.70 W |

#### 2.3.1 Nominal Current Requirements and Power Dissipation

#### 2.3.2 Power Management - Drive Spinning

(No media access/no active command)

| Operating Mode | Current,   | Power, Average |        |  |  |  |  |

|----------------|------------|----------------|--------|--|--|--|--|

|                | 12 VDC ±5% | 5 VDC ±5%      |        |  |  |  |  |

| ldle           | .18 A      | .14 A          | 2.86 W |  |  |  |  |

NOTE: IDLE - Power saving mode entered after expiration of the inactivity timer. The contribution due to this power saving mode is dependent on the inactivity time interval which can be user specified via the drive configuration data. No power saving can occur if the period(s) of command inactivity do not exceed the length of the inactivity timer interval. The percentage of time in this mode varies depending on the specific usage of the drive. Please refer to Section 4.6 for details on the Idle mode operation in a power management context.

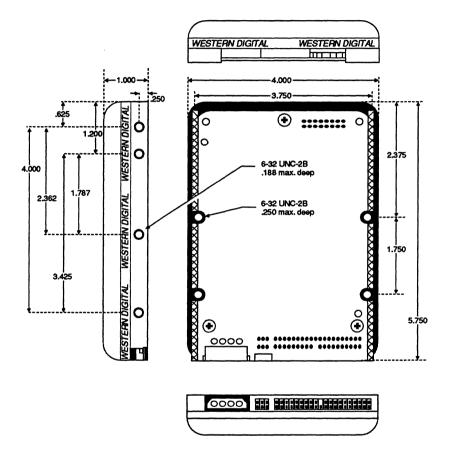

Figure 2-2. Typical +12V Current Draw During Spin Up (Master Mode)

#### 2.3.3 Power Management - Drive Not Spinning

| Operating Mode | Current Average |       | Power, Typical |

|----------------|-----------------|-------|----------------|

|                | 12 VDC          | 5 VDC |                |

| Standby        | .04 A           | .16 A | 1.28 W         |

| Sleep          | .04 A           | .16 A | 1.28 W         |

### 2.3.4 Ripple

| Ripple | Maximum               | Frequency |

|--------|-----------------------|-----------|

| 12 VDC | 200 mV (peak-to-peak) | 0-20 MHz  |

| 5 VDC  | 100 mV (peak-to-peak) | 0-20 MHz  |

### Western Digital Corporation

### 2.3.5 Power Connectors and Cables

| Power Connector        | 4-pin MOLEX (P/N 15-24-4041 or equivalent)                              |

|------------------------|-------------------------------------------------------------------------|

| Mating Connector       | Body (AMP 1-480424-0 or equivalent)<br>Pins (AMP 60619-4 or equivalent) |

| Power Cable Wire Gauge | 18 AWG                                                                  |

### 2.4 ENVIRONMENTAL SPECIFICATIONS

### 2.4.1 Shock and Vibration

| Shock                         |                                                                                          |

|-------------------------------|------------------------------------------------------------------------------------------|

| Operating                     | 10Gs                                                                                     |

| Non-operating                 | 75Gs                                                                                     |

| Note: Half-sine v<br>maximum, | vave of 11 ms duration, two half-sine waves per second , with no non-recoverable errors. |

| Vibration                     |                                                                                          |

| Operating                     | 5-17 Hz, 0.034" (double amplitude)<br>17-400 Hz, 0.75G (Peak)                            |

| Non-Operating                 | 5-20 Hz, 0.195" (double amplitude)<br>20-500 Hz, 4G (Peak)                               |

| Sweep Rate                    | Half-octave/minute                                                                       |

### 2.4.2 Temperature and Humidity

| Temperature                                                                                                          |                                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Operating                                                                                                            | 5°C to 50°C                                                                         |  |

| Non-Operating                                                                                                        | 10°C/hour Max. Thermal Gradient<br>-40°C to 60°C<br>20°C/hour Max. Thermal Gradient |  |

| Note: The system environment must allow sufficient air flow to maintain<br>the casting temperature at or below 55°C. |                                                                                     |  |

| <b>Relative Humid</b>                                                                                                | ity                                                                                 |  |

| Operating                                                                                                            | 8% to 80% RH non-condensing                                                         |  |

| Maximum We                                                                                                           | et Bulb 26°C                                                                        |  |

| Non-operating                                                                                                        | 5% to 95% RH non-condensing                                                         |  |

| Maximum We                                                                                                           | et Bulb 26°C                                                                        |  |

### 2.4.3 Atmospheric Pressure

| Altitude - Operating     | -1000 to 10,000 feet |  |

|--------------------------|----------------------|--|

| Altitude - Non-Operating | -1000 to 40,000 feet |  |

### 2.4.4 Acoustics

| Max. sound power level per ISO | 7779.5 *          |

|--------------------------------|-------------------|

| ldle Mode                      | 40 dBA at 1 meter |

| Seek Mode                      | 43 dBA at 1 meter |

\* The maximum difference between adjacent octave bands is 12 db (no pure tones).

### 2.5 AGENCY APPROVALS

The Caviar meets the standards of the following regulatory agencies:

**Underwriters Laboratories**

UL-Standard 1950, Standard for Safety, Information Processing and Business Equipment; File Number - E101559

Federal Communication Commission

Verified to comply with FCC Rules for Radiated and Conducted Emission, Part 15, Subpart B, for Class B Equipment

Canadian Standards Association

CSA-Standard C22.2, No.950 - M89 Information Processing and Business Equipment; File Number LR 68850

**TUV Essen Laboratories**

IEC 950 (EN 60 950) Safety of Information Technology Equipment Including Electrical Business Equipment

### 2.6 RELIABILITY SPECIFICATION

| 100,000 Predicted Hours |

|-------------------------|

| 10 Minutes typical      |

| Five Years              |

| Two Years               |

|                         |

# 3.0 PRINCIPLES OF OPERATION

This section describes the principles of operation of the Caviar from the following viewpoints:

- Drive Electronics

- Head Disk Assembly (HDA)

### **3.1 DRIVE ELECTRONICS**

Caviar's intelligence resides in the specialized electronic components mounted on the four-layer printed circuit board assembly. The Caviar consists of the following drive electronic components:

- WD42C22C Winchester Disk Controller

- Buffer RAM

- WD60C11 Servo Controller

- WD10C23 Data Separator

- Microprocessor ROM and RAM

- Pulse detector

- Spindle Motor Driver

- Actuator Driver

- Gate Array Fusion II

- Frequency Synthesizer

### 3.1.1 WD42C22C Winchester Disk Controller

The WD42C22C integrates a high performance, low cost Winchester formatter/controller, CRC/ECC generator/checker, host interface and buffer manager into a single, 84-pin QPFP device. The controller/formatter encodes and decodes data to and from the WD10C23 data separator. The CRC/ECC generator/checker calculates ECC for the data field. The host interface directly connects to the host system bus via internal 12 mA drivers. The buffer manager controls the buffer RAM and handles the arbitration between the host interface and drive controller.

### 3.1.2 Buffer RAM

A 32-KByte (optional 64-KByte) static RAM buffer enhances data throughput by buffering sector data between the Caviar and the AT system bus. The RAM only buffers read/write data and ECC information. The buffer is accessed by two

channels, each having a separate 15-bit address and byte-count register. The channels operate simultaneously, accepting read and write operations from two data paths.

### 3.1.3 WD60C11 Servo Controller

The WD60C11 provides servo discrimination, track address capture and measures servo burst amplitudes. A servo burst is a momentary servo pattern used in embedded servo control implementations, usually positioned between sectors. The WD60C11 also provides spindle motor control.

### 3.1.4 WD10C23 Data Separator

The WD10C23 handles the sensitive read/write signals between the WD42C22C and the read channel circuitry at a rate of 15 megabits-per-second for Zone 1 and 12 megabits-per-second for Zone 2. Read data refers to previously written data, with phase, frequency and write splice noise. The WD10C23 removes the noise and sends clean digital read signals to the WD42C22C. The WD10C23 conditions write data to be recorded on the drive. Data to and from the WD42C22C is precisely clocked to the WD10C23.

### 3.1.5 Microprocessor ROM and RAM

A 16-bit microprocessor controls and coordinates the activity of the HDA and the WD42C22C. The microprocessor receives and sends command or status information over an internal multiplexed address/data bus. The microprocessor monitors spindle and actuator activity until the WD42C22C asserts the microprocessor's interrupt line. The WD42C22C asserts the interrupt when the host writes to the Command Register or at the end of either a host or disk transfer. The microprocessor uses 64 KBytes of external ROM and 2/8 KBytes of external static RAM. Firmware controlling all these functions, including the adaptive multi-segmented cache, resides in the microprocessor ROM.

### 3.1.6 Pulse Detector

The pulse detector amplifies and qualifies the RLL-encoded signals from the preamplifier on the flex circuit. Pulse qualification in read mode is accomplished using level qualifications of differentiated input zero crossings. An AGC amplifier compensates for variations in head preamp output levels, presenting a constant input level to the pulse qualification circuitry.

In write mode, the circuitry is disabled. The AGC gain stage input impedance switches to a lower level to allow fast settling of the input coupling capacitors during a write-to-read transition.

### 3.1.7 Spindle Motor Driver

A three-phase spindle motor driver is employed. The driver is controlled by the WD60C11 Servo Controller.

### 3.1.8 Actuator Driver

The actuator driver provides precision placement of the read/write heads by means of the voice coil motor. A digital-to-analog converter in the WD60C11 controls this H-bridge driver.

### 3.1.9 Gate Array Fusion II

This IC performs the memory and I/O decode functions necessary for interface of the VSLI devices to the microprocessor. This device also provides for control of "expanded I/O" devices. The design uses a 74LS387 latch in the expanded I/O address space to provide additional output ports. The gate array also divides a 48MHz oscillator to provide 40/60% duty cycle 12 MHz and 16 MHz clocks which are provided as the sole clock source for the drive. The DMA and IOCS16 control are provided by this device as well.

### 3.1.10 Frequency Synthesizer

The AV9104-14 Frequency Synthesizer uses the 12 MHz clock output from the Fusion IC to generate the clock for the data separator. The Caviar drive uses two zones, one at 12.5 MHz and the other at 15.375 MHz. The firmware selects the output clock frequency to maintain a fairly uniform bit density across the media.

Figure 3-1. Caviar Block Diagram

18

Caviar ACI 60/AC2120 Technical Reference Manual

Figure 3-2. Mechanical Exploded View AC2120

### 3.2 HEAD DISK ASSEMBLY (HDA)

The functional parts of the HDA are mounted to a die-cast housing with a sealed cover. The assembly provides exact mechanical relationships between the spindle, headstack and voice coil through precise machined dimensions on the housing. A clean environment is also maintained within the HDA enclosure.

The HDA consists of the following mechanical subassemblies;

- Base/Cover assembly

- Spindle motor

- Disk stack assembly

- Headstack assembly

- Voice coil assembly

- Air filtration system

#### 3.2.1 Base/Cover Assembly

The single-piece cast base provides a mounting platform for the components of the assembly. The base/cover assembly has machined mounting surfaces for the spindle motor, voice coil and pivot. To ensure a Class 100 environment within the HDA, a tape seal is wrapped around the base and cover castings.

#### 3.2.2 Spindle Motor

The spindle motor assembly consists of a brushless three-phase motor, spindle bearing assembly, disk mounting hub and a ferrofluid magnetic seal. The entire spindle motor assembly is completely enclosed in the HDA and bolted to the base casting. The motor rotates the spindle shaft at approximately 3600 RPM.

Proprietary spindle electronics sense motor speed and angular position by monitoring the spindle motor's back electromotive force (BEMF). Using BEMF sensing, instead of the Conventional Hall effect or inductive motor position sensors, lowers the power consumption and increases reliability. Motor driver circuits dynamically brake the spindle during motor spin down.

#### 3.2.3 Disk Stack Assembly

The disk stack assembly consists of disks, disk spacers and a disk clamp. In the Caviar AC2120, two disks and one spacer are placed on the hub and clamped into place. The Caviar AC160 has one disk and a spacer.

The platters of the Caviar drives are thin inflexible aluminum disks. Each disk is plated with a layer of nickel, followed by the magnetic media coating. A thin film of carbon overcoat protects the magnetic material against wear and abrasion from the read/write heads. The final lubricant layer provides additional protection between the read/write heads and media during take-offs and landings.

### 3.2.4 Headstack Assembly

The headstack assembly consists of the following mechanical subassemblies:

- Read/write heads

- Actuator arm

- Flex Circuit

#### **Read/Write Heads**

Read/Write heads consist of thin film slider mounted on a Whitney class suspension system. The Caviar actuator is statically balanced above the pivot center.

#### Actuator Arm Assembly

This assembly is servo-controlled and derives position information from the sector servo data embedded in all disk tracks.

#### Flex Circuit

The head conductors are flex cables routed through the flex circuit assembly inside the HDA. The flex circuit assembly transfers signals between the read/ write heads and the voice coil actuator motor. A preamplifier IC, located on the flex circuit, maximizes the read/write heads' signal strength while minimizing noise.

### 3.2.5 Voice Coil Assembly

The voice coil assembly consists of an upper and lower magnetic plate, a flat rotary coil, a bidirectional crash stop and a pivot bearing.

The pivot assembly fits in the actuator block bore.

### **3.2.6** Air Filtration System

It is absolutely essential that air circulating within the drive be free of particles. The HDA is assembled in a Class 100 purified air environment, then sealed with tape. To retain this clean environment, the Caviar is equipped with two filters. One filter, the recirculating filter, cleans air within the HDA. The recirculating filter traps any particles which may be generated during head landings or take-offs. Mounting the recirculating filter next to the disk places the filter in the direction of the air flow. This strategic placement of the filter allows the rotating disks to act as an air pump forcing air through the recirculating filter. A second filter, the breather filter, cleans any external air entering the HDA. The breather filter also equalizes the internal and external air pressure. The breather filter is located on the bottom of the HDA.

# 4.0 ADVANCED PRODUCT FEATURES

Western Digital's Caviar series of intelligent drives provides a choice of data storage capacities for the AT and compatibles with a full complement of advanced product features. This section describes the following Caviar advanced product features:

- CacheFlow

- Defect management and format characteristics

- Error recovery process

- Translation

- Dual drive option

- Power Conservation

- DMA Capability

- Zoned Recording

- Block Mode

### 4.1 CACHEFLOW

CacheFlow is the industry's first adaptive multi-segmented disk caching system.

### 4.1.1 Purpose of CacheFlow

CacheFlow was designed by Western Digital to minimize disk seeking operations and the overhead due to rotational latency delays. CacheFlow constantly evaluates not only the size of the data request but the type of data request, that is, whether the application is sequential, random or repetitive. CacheFlow then dynamically partitions the Caviar's 32-KByte (optional 64-KByte) RAM buffer into segments and selects the appropriate caching mode for optimum system performance.

### 4.1.2 Benefits of CacheFlow

In a typical application, most host requests are for sequential data. CacheFlow's adaptive design enables the Caviar to eliminate unnecessary disk seeking operations by immediately implementing the Sequential mode once the data has been analyzed. Applications such as Core Test or other benchmark utilities, on the other hand, request the same data over and over again. CacheFlow provides a similar performance edge by switching to the Repetitive mode of operation.

### 4.1.3 CacheFlow Operation

Sequential mode is the default mode of operation for CacheFlow. The Caviar initially partitions the 32-KByte (optional 64-KByte) cache buffer into four caching segments. As seeking operations begin, CacheFlow monitors the data's logical sector address and sector count parameters. CacheFlow then uses a simple hit score algorithm to either increase or decrease the segment size for optimal performance.

CacheFlow switches from Sequential Mode to Repetitive Mode during read operations if the same block is accessed twice. Both modes read ahead after the host-requested data has been read. By storing read-ahead data in the sector buffers, the cache hit score can be significantly improved.

CacheFlow transfers host write data immediately to the sector buffer. A write operation does not affect the buffer's cache segments since write data is not cached. Only the sectors that are written are purged from the cache buffer.

### 4.1.4 Sequential Mode

The Sequential Caching Mode is the standard read-ahead cache. After reading all of the host-requested data into the segment(s), CacheFlow continues to read ahead until the cache is full. After the host reads the requested data from the cache, a new cache beginning is established following the last sector buffer returned to the host. Based on the hit score algorithm, sequential mode adapts the number and size of segments to optimize segment performance.

The default mode of four cache segments provides optimum cache performance. A larger number of segments may limit cache effectiveness because the segment may not store enough sequential sectors. A smaller number of segments may limit effectiveness for random reads.

### 4.1.5 Repetitive Mode

The Repetitive Caching Mode resembles a static buffer. If the same blocks are accessed twice, the Repetitive Mode is selected. Repetitive Mode also reads ahead and can override the number of segments to build one large segment with the maximum hit score. Unlike Sequential Mode, however, the sector buffer containing the host-requested data remains valid after the host reads the data.

Figure 4-1. CacheFlow Algorithm

### 4.2 DEFECT MANAGEMENT AND FORMAT CHARACTERISTICS

### 4.2.1 Defect Management

Every Caviar undergoes factory-level intelligent burn in, which thoroughly tests for and maps out defective sectors on the media before the drive leaves the manufacturing facility. Following the factory tests, a primary defect list is created. The list contains the cylinder, head and sector numbers for all defects. The purpose of the spare sector/track map is to manage the reallocation of spare sectors and tracks after they have been assigned.

### 4.2.2 Format Characteristics

The Caviar is shipped from the factory preformatted (low level) with all defects mapped out.

In order to be compatible with existing industry standard defect management utility programs, the Caviar supports logical format. When the host issues the Format Track command, the Caviar performs a logical version of this command in response to the host's interleave table request for good and bad sector marking or assign/unassign the sector to/from an alternate sector.

If the host issues the Format Track Command during normal operating modes, the data fields of the specified track are filled with a data pattern of all zeros. The interleave table identifies any bad sectors on a given track. The interleave table must contain an appropriate number of data bytes. There are two bytes per sector for each entry in the interleave table. The first byte marks the sector as good or bad. The first byte is set to OOH to indicate a good sector or to 80H to indicate a bad sector or to 20H to unassign the alternate sector or to 40H to assign the sector to an alternate location. The second byte designates the logical sector ID number.

### 4.3 ERROR RECOVERY

The Caviar has two means of error recovery:

- Read/Write Retry Procedure

- Extended Read Retry Procedure

The Caviar's retry procedures are implemented for the following errors:

- ID Not Found (IDNF)

- Data Address Mark Not Found (DAMNF)

- Error Correction Code (ECC)

The host may explicitly enable/disable retries in the Read, Write and Read Verify Commands. All other commands and the controller's internal disk read and write operations are always performed with retries enabled. If retries are disabled, the Caviar will not perform any disk controller retry operations and will immediately set the appropriate bit in the Error Register.

The Read/Write Retry Procedure will perform up to ten basic retry operations to succeed in reading or writing a specified sector. If recovery is achieved, the Caviar continues executing the command. For a write operation, if these retries fail to validate the ID fields on a specified track, then an IDNF error is reported to the Caviar's Error Register and the command is terminated.

For a read operation, the Caviar will perform the Extended Read Retry Procedure to recover the data. The Extended Read Retry Procedure employs up to sixteen combinations of early/late window shifts and positive/negative track offsets to recover read data. This procedure is used for the IDNF, DAMNF and ECC errors. If the retry operation is successful, the Caviar clears any existing window shift or track offset before continuing with the command. If the retry operation failed, the Caviar reports the appropriate error to the Error Register, with the exception of an ECC error. In the case of an ECC error, the drive performs up to eight retries to obtain two consecutive matching syndromes. If matching syndromes are found, and the error spans eleven bits or less, the data is corrected, the CORR bit is set in the host's status register and the command continues. If two consecutive matching syndromes are not found, or if the error spans more than eleven bits, the Caviar reports an ECC (uncorrectable) error to the Error Register.

### 4.4 TRANSLATION

The Caviar implements linear address translation. The translation mode and translated drive configurations are selected by using the Set Drive Parameters command to issue head and sector/track counts to the translator. Caviar supports universal translation, therefore, any valid combination of cylinder, head and SPT can be assigned to the drive, as long as the total number of sectors is not greater than the physical limits. The product of the cylinder, head and sectors/track counts must be equal to or less than the maximum number of sectors available to the user. The maximum number of sectors per drive for the Caviar AC160 and the AC2120 are 122,091 and 244,182 respectively. Each sector consists of 512 bytes.

The minimum value for any translation parameter is one. The maximum value for any translation parameter is as follows:

| Sectors/Track   | 255  |

|-----------------|------|

| Heads           | 16   |

| Cylinders/drive | 2048 |

The values in the Sector Count Register and the SDH Register determine the Sectors Per Track (SPT) and heads. Regardless of the values of the SPT and the heads, Caviar will always be in the translation mode. Refer to section 2.2 for the recommended setup parameters.

### 4.5 DUAL DRIVE OPTION

The Caviar supports ATA dual drive operations by means of configuration options for master or slave drive designation. A jumper must be placed in the drive's option area for both master and slave configurations. Connection to the host is implemented by means of a daisy-chain cable assembly. These configurations are described in section 6.

The SDH Register contains the master/slave select bit for the Caviar. The  $\overline{\text{DASP}}$  signal is a time-multiplexed indicator of Drive Active or Slave Present on the Caviar's I/O interface. At reset, this signal is an output from the slave drive and an input to the master drive, showing that a slave drive is present. For all times other than reset,  $\overline{\text{DASP}}$  is asserted at the beginning of command processing and released upon completion of the command. If the master drive option has been configured, the Caviar will not respond to commands or show drive status on the interface when the slave bit is selected in the SDH Register.

# 4.6 POWER CONSERVATION

Power saving takes two forms. One is Automatic Power Reduction (APR) that occurs when the drive is idle. The idle state is entered automatically whenever the drive completes command execution and another command is not received from the host computer. The other form is host computer controlled power saving that is realized by commanding the drive to park the heads and stop the spindle. The drive command set includes the industry standard ATA command set power save commands that are used to initiate the park and spin down functions.