WICAT

System 150

(mapped)

Hardware Reference Manual

# July 1982

WICAT SYSTEMS INCORPORATED

Orem, Utah

187-055-201 A

# Copyright Statement

Copyright (c) 1982 by WICAT Systems Incorporated All Rights Reserved Printed in the United States of America

Receipt of this manual must not be construed as any kind of commitment, on the part of WICAT Systems Incorporated, regarding delivery or ownership of items manufactured by WICAT.

This manual is subject to change without notice. A system software subscription entitles you to receive all bulletins and revised editions of manuals pertaining to your WICAT system. Call WICAT Systems's main office for information on this service.

The equipment described in this manual generates, uses, WARNING: and can radiate radio frequency energy, and if not installed in accordance with instructions provided in the hardware documentation for the equipment, may interfere with radio communications. Furthermore, the equipment has been tested and found to comply with the limits for a Class A computing device pursuant to subpart J, Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when the equipment is operated in a commercial environment. Operation of the equipment (described in this manual) in а residential area is likely to cause Where the equipment will be used in a interference. residential area, it is the user's responsibility to ensure that any interference is corrected.

Revision History

First Printing July 1982

# The Purpose of This Manual

This document provides the technical information users will need should they want to modify System 150 (mapped) PC boards to interface with peripheral devices that are not supplied by WICAT Systems Inc.

Furthermore, WICAT Systems Inc. assumes no responsibility for difficulties arising from the use of equipment not manufactured by WICAT.

# Intended Audience

Field service technicians, OEM representatives, and maintenance personnel on Systems 150 (mapped). Readers must be knowledgable in electronics, and familiar with the basic terminology of computer science.

ŝ

ſ .

| 1.1     | INTRODUCTION                                  |

|---------|-----------------------------------------------|

| 1.2     | DEFINITION AND FEATURES                       |

| 1.3     | SYSTEM CONFIGURATION                          |

| 1.4     | BOARD CONFIGURATION                           |

| 1.5     | BOARD INTERACTION                             |

| 1.5.1   | Explanation Of Bus Structure 1-6              |

| 1.5.2   | Bus Control                                   |

| 1.6     | SYSTEM DATA FLOW                              |

| 1.6.1   | Central Processing Unit (CPU) 1-9             |

| 1.6.2   | Memory                                        |

| 1.6.3   | CRT                                           |

| 1.6.4   | Storage • • • • • • • • • • • • • • • • • • • |

| 1.6.5   | Peripherals                                   |

| 1.6.5.1 | Serial Interfaces 1-10                        |

| 1.6.5.2 | Parallel Interface 1-10                       |

| 1.6.5.3 | Battery-backed Clock 1-10                     |

| 1.6.5.4 | Graphics Circuitry (Optional) 1-10            |

| 1.6.5.5 | Videodisc Controller (Optional) 1-10          |

| 1.6.5.6 | IEEE 488 Interface (Optional) 1-11            |

# CHAPTER 2 CPU BOARD

| 2.1     | INTRODUCTION                            |

|---------|-----------------------------------------|

| 2.2     | DEFINITION AND FEATURES                 |

| 2.3     | CPU BOARD CONFIGURATION                 |

| 2.3.1   | The MULTIBUS Interface                  |

| 2.3.2   | On Board ROM                            |

| 2.3.3   | Interrupt Circuitry                     |

| 2.3.4   | Bus Arbitration Circuitry 2-5           |

| 2.3.5   | Memory Mapping Registers                |

| 2.4     | PROCESSOR CIRCUITRY                     |

| 2.4.1   | Address Bus                             |

| 2.4.2   | Data Bus                                |

| 2.4.3   | Synchronous Bus Control                 |

| 2.4.3.1 | Command Lines (MRDC/, MWTC/, IOWC/, And |

|         | IORC/)                                  |

| 2.4.3.2 | Transfer Acknowledge Line (XACK/) 2-12  |

| 2.4.4   | MG68000 Bus Control                     |

| 2.4.5   | Bus Arbitration Control                 |

| 2.4.5.1 | Single Device Arbitration 2-13          |

| 2.4.5.2 | Multi-Device Arbitration                |

| 2.4.6   | Interrupt Control                       |

| 2.4.7   | System Control                          |

| 2.4.8   | MC68000 Peripheral Control              |

| 2.4.9   | Processor Status                        |

| 2.5     | MEMORY MAP                              |

| 2.6     | ERROR CONTROL                           |

| 2.6.1   | Address Errors                          |

| 2.6.2   | The Error Register                      |

.

| 2.7   | ON BOARD PERIPHERALS AND MEMORY                | 2-24 |

|-------|------------------------------------------------|------|

| 2.7.1 | Memory Mapping Flag And The Error Register     | 2-24 |

| 2.7.2 | On Board Memory                                | 2-24 |

| 2.8   | ADDRESS DECODE                                 | 2-27 |

| 2.8.1 | On Board Device Selection                      | 2-27 |

| 2.8.2 | CPU Board Address Decoding • • • • • • • • • • | 2-27 |

| 2.8.3 | EPROM Configuration Firmware                   | 2-28 |

| 2.9   | PAL EQUATIONS                                  | 2-31 |

# CHAPTER 3 I/O BOARD

| 3.1   | INTRODUCTION                                        |

|-------|-----------------------------------------------------|

| 3.2   | DEFINITION AND FEATURES                             |

| 3.3   | I/O BOARD CONFIGURATION                             |

| 3.3.1 | The Serial Interface                                |

| 3.3.2 | The Real-Time Clock                                 |

| 3.3.3 | The Interval Timers                                 |

| 3.3.4 | The Parallel Port                                   |

| 3.3.5 | The Parallel Port Direction And LED Register 3-7    |

| 3.3.6 | The Select/Configuration Switches • • • • • • • 3-9 |

| 3.3.7 | IEEE 488 Multibus                                   |

# CHAPTER 4 MEMORY MODULE

| 4.1      | INTRODUCTION                               | ٠ | • | • | • | • | ٠ | • | ٠ | 4-1          |

|----------|--------------------------------------------|---|---|---|---|---|---|---|---|--------------|

| 4.2      | DEFINITION AND FEATURES                    | • | • | • | • | • | • | • | • | 4-1          |

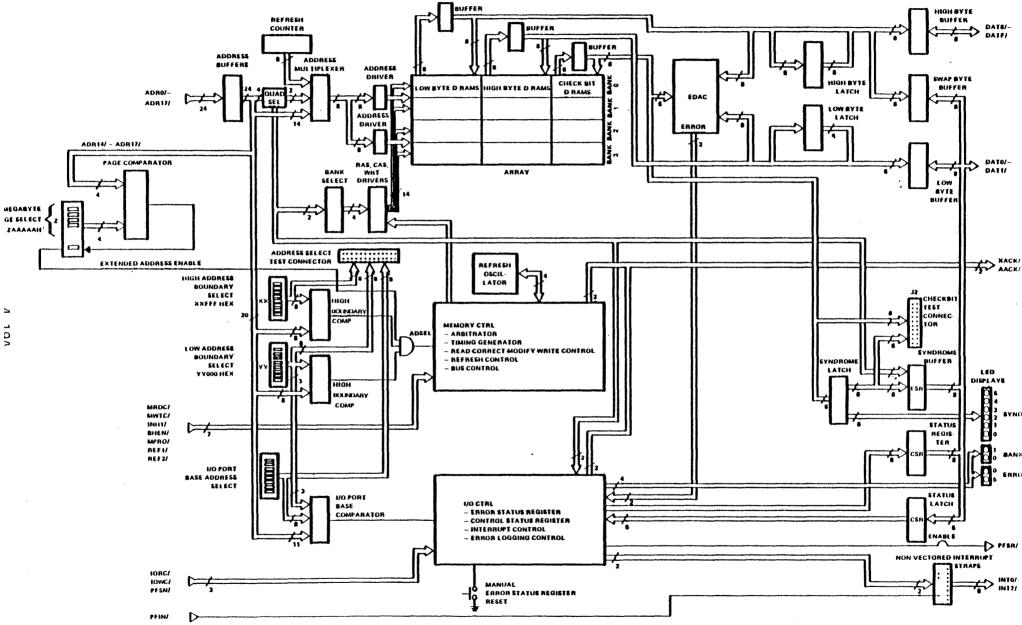

| 4.3      | MEMORY MODULE SIGNALS                      |   | • | • | • | • | • | • | • | 4-3          |

| 4.3.1    | Advanced Acknowledge (AACK/)               |   |   |   |   |   |   |   |   |              |

| 4.4      | ELECTRICAL CHARACTERISTICS                 |   |   |   |   |   |   |   |   |              |

| 4.4.1    | EDAC • • • • • • • • • • • • • • • • • • • |   |   |   |   |   |   |   |   |              |

| 4.4.2    |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.2.1  |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.2.1. |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.2.2  |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.2.3  | Error Status Register                      |   |   |   |   |   |   |   |   |              |

| 4.4.2.4  |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.2.5  | Error Status LEDs                          |   |   |   |   |   |   |   |   |              |

| 4.4.3    |                                            |   |   |   |   |   |   |   |   |              |

| 4.4.3.1  |                                            |   |   |   |   |   |   |   |   | 4-10         |

| 4.4.3.1. | 0                                          |   |   |   |   |   |   |   |   | 4-10         |

| 4.4.3.1. | 5                                          |   |   |   |   |   |   |   |   | 4-10         |

| 4.4.3.1. | 5                                          |   |   |   |   |   |   |   |   | 4-11         |

| 4.4.3.1. |                                            |   |   |   |   |   |   |   |   | 4-11         |

| 4.4.3.2  | · · ·                                      |   |   |   |   |   |   |   |   | 4-11         |

| 4.4.3.3  |                                            | - |   |   |   |   |   |   |   | 4-12         |

| 4.4.3.4  |                                            |   |   |   |   |   |   |   |   | 4-12         |

| 4.4.3.5  |                                            |   |   |   |   |   |   |   |   | <b>↓</b> −12 |

|          | TESTABILITY                                |   |   |   |   |   |   |   |   | 4-13         |

| 4.5.1    |                                            |   |   |   |   |   |   |   |   | <b>-13</b>   |

| 4.5.2    | Address Testing                            |   |   |   |   |   |   |   |   | ÷-13         |

| 4        | Address restring • • • • • • • •           | ٠ | ٠ | • | ٠ | ٠ |   | ٠ | 4 | +-10         |

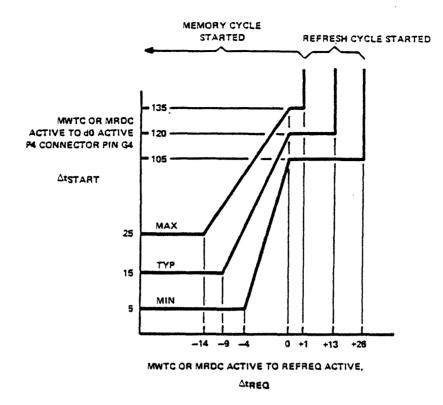

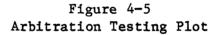

| 4.5.3 | Testing Arbitration 4                           | -14 |

|-------|-------------------------------------------------|-----|

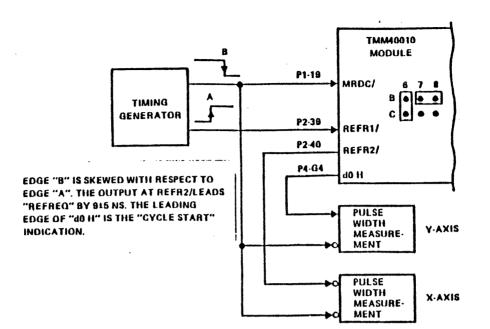

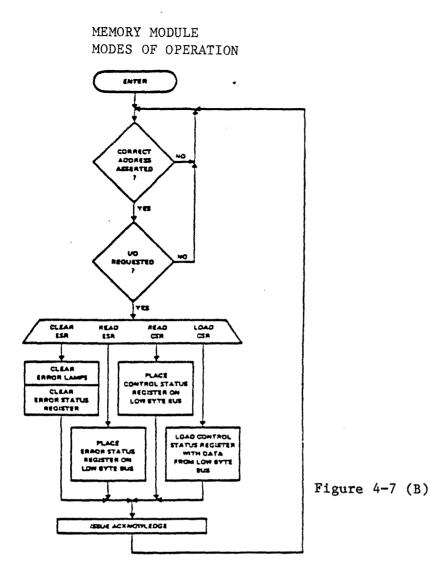

| 4.6   | MODES OF OPERATION 4                            | -16 |

| 4.6.1 | Read Operations 4                               | -19 |

| 4.6.2 | Write Operations 4                              | -19 |

| 4.6.3 | Byte Swap • • • • • • • • • • • • • • • • • • 4 | -20 |

| 4.6.4 | Refresh                                         | -20 |

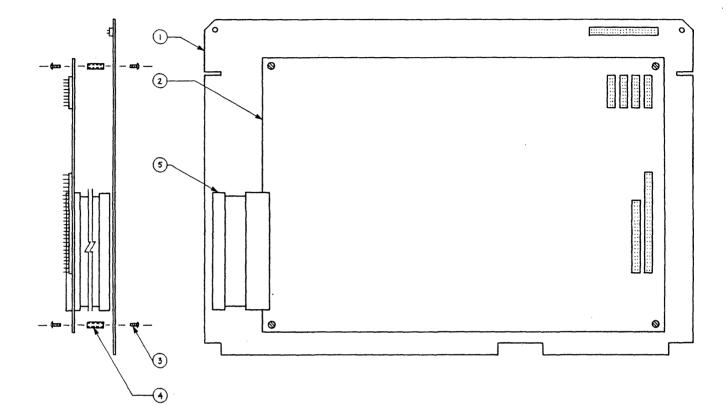

| 4.7   | CONFIGURING THE MEMORY MODULE 4                 | -20 |

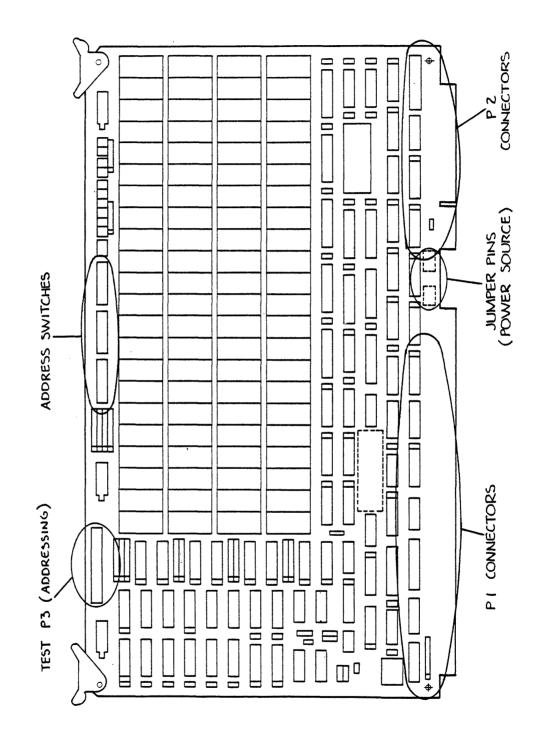

| 4.8   | LOCATION OF ADDRESS SWITCHES 4                  | -20 |

| 4.8.1 | Starting Address 4                              | -21 |

| 4.8.2 | Ending Address 4                                | -21 |

| 4.8.3 | Enabling Extended Address Lines • • • • • • 4   | -22 |

| 4.8.4 | Setting Address For Extended Lines 4            | -22 |

| 4.8.5 | I/O Port Address 4                              | -23 |

CHAPTER 5 WD1000 AND COUPLER/FLOPPY BOARD SET

| 5.1      | INTRODUCTION                                         | -1 |

|----------|------------------------------------------------------|----|

| 5.2      | DEFINITION AND FEATURES                              | -1 |

| 5.3      | WD1000 AND COUPLER/FLOPPY BOARD SET CONFIGURATION 5- | -2 |

| 5.4      | COUPLER/FLOPPY CIRCUITRY AREAS                       | -4 |

| 5.4.1    | WD1000 Coupler/DMA Controller 5-                     | -5 |

| 5.4.1.1  | Synchronous State Machine 5-                         | •5 |

| 5.4.1.2  | Address Decode                                       | -6 |

| 5.4.1.3  | DMA Address Register/Counter 5-                      | -6 |

| 5.4.1.4  | Bus Arbitration 5-                                   | -6 |

| 5.4.1.5  |                                                      |    |

| 5.4.2    | Two-mode Operation Of Coupler 5-                     | -6 |

| 5.4.2.1  | Register Interface 5-                                |    |

| 5.4.2.2  | -                                                    |    |

| 5.4.3    |                                                      |    |

| 5.4.3.1  |                                                      |    |

| 5.4.3.2  |                                                      |    |

| 5.5      | WD1000 BOARD CONFIGURATION                           |    |

| 5.6      | BOARD SET ELECTRICAL DATA                            |    |

| 5.7      | MECHANICAL DATA                                      |    |

| 5.8      | ENVIRONMENTAL DATA                                   |    |

| 5.9      | SOFTWARE INTERFACE DATA                              |    |

| 5.10     | BASE ADDRESS                                         | 12 |

| 5.11     | WINCHESTER REGISTERS                                 | 2  |

| 5.12     | FLOPPY REGISTERS                                     | 13 |

| 5.12.1   | Description Of Floppy Registers 5-1                  | 3  |

| 5.12.1.1 |                                                      |    |

| 5.12.1.2 |                                                      | 3  |

| 5.12.1.3 |                                                      |    |

| 5.12.1.4 |                                                      |    |

| 5.12.1.5 |                                                      | 4  |

| 5.13     | SIGNAL DEFINITIONS                                   |    |

.

APPENDIX A I/O BOARD JUMPER PIN LOCATIONS BY PORT

APPENDIX B JUMPER PIN INPUT/OUTPUT SIGNALS

APPENDIX C WICAT DIAGNOSTIC MONITOR (DIAMOND)

| C.1      |                                                 |

|----------|-------------------------------------------------|

|          | INTRODUCTION                                    |

|          | LITERALS                                        |

| C.2.1    | Integer Literals                                |

| C.2.2    | String Literals                                 |

|          | SYNTAX                                          |

| C.3.1    | The Stack • • • • • • • • • • • • • • • • • • • |

| C.3.2    | Variables In Fixed Locations                    |

| C.3.3    | Reverse-polish Notation                         |

| C.3.4    | Addresses Versus Contents                       |

| C.3.4.1  | @ • • • • • • • • • • • • • • • • • • •         |

| C.3.4.2  | @W                                              |

| C.3.4.3  | @L                                              |

| C.3.4.4  |                                                 |

| C.3.4.5  | !W                                              |

| C.3.4.6  | !L                                              |

| C.3.4.7  |                                                 |

|          | FIXED POINT OPERATORS                           |

| C.4.1    |                                                 |

| C.4.1.1  |                                                 |

| C.4.1.2  | .!ABS                                           |

| C.4.1.3  | NOT                                             |

| C.4.1.4  |                                                 |

| C.4.1.5  | .12/                                            |

| C.4.1.6  | .!1+                                            |

| C.4.1.7  | .!!                                             |

|          |                                                 |

| C.4.1.8  | EQZ                                             |

| C.4.1.9  | NEZ                                             |

| C.4.1.10 |                                                 |

| C.4.1.11 |                                                 |

| C.4.1.12 |                                                 |

| C.4.1.13 |                                                 |

| C.4.1.14 |                                                 |

| C.4.1.15 |                                                 |

| C.4.1.16 |                                                 |

| C.4.1.17 |                                                 |

| C.4.2    | BINARY OPERATORS                                |

| C.4.2.1  |                                                 |

| C.4.2.2  |                                                 |

| C.4.2.3  | * • • • • • • • • • • • • • • • • • • •         |

| C.4.2.4  | / • • • • • • • • • • • • • • • • • • •         |

| C.4.2.5  | /U                                              |

| C.4.2.6  | MAX                                             |

| C.4.2.7  | MIN                                             |

| C.4.2.8  | AND                                             |

|          |                                                 |

~

| C.4.2.9  | OR           | • •  | ٠    | • •    | • •  | ٠   | ٠     | • •      | •  | • • | • | • | ٠ | • | • | C-37          |

|----------|--------------|------|------|--------|------|-----|-------|----------|----|-----|---|---|---|---|---|---------------|

| C.4.2.10 | XOR .        | • •  | •    | • •    | • •  | •   | •     | • •      | •  | •   | • | • | • | ٠ | • | C-38          |

| C.4.2.11 | EQ           |      | •    |        |      |     | •     | • •      | •  | • • | • | • | • | • | • | C-39          |

| C.4.2.12 | NE           |      | •    |        |      |     |       |          | •  | • • | • | • | • |   | • | <b>C-4</b> 0  |

| C.4.2.13 | LT.          |      |      |        |      |     |       |          |    |     |   | • |   | • |   | C-41          |

| C.4.2.14 | LE           |      |      |        |      |     |       |          | •  |     |   | · |   | Ţ |   | C-42          |

| C.4.2.15 | GE           | •••  | •    | •••    | •••  | •   | •     | •••      | •  | • • | • | • | • | • | • | C-43          |

| C.4.2.15 | GI           | • •  | •    | • •    | • •  | •   | •     | • •      | ٠  | • • | • | • | • | • | • | C-44          |

| C.4.2.17 |              | • •  | •    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | • | ٠ | • | ٠ | C-44<br>C-45  |

|          | LSL .        | • •  | ٠    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | • | ٠ | • | • |               |

| C.4.2.18 | LSR .        | • •  | •    | • •    | • •  | ٠   | -     | • •      | ٠  | • • | • | • | ٠ | • | • | C-46          |

| C.4.2.19 | ASL .        | • •  | •    | • •    | • •  | ٠   | •     | • •      | •  | • • | • | ٠ | ٠ | • | ٠ | C-47          |

| C.4.2.20 | ASR .        | • •  | ٠    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | ٠ | ٠ | ٠ | • | C-48          |

|          | tack Ope     | erat | ors  | ٠      | • •  | •   | •     | • •      | ٠  | • • | • | ٠ | ٠ | ٠ | • | C-49          |

| C.4.3.1  | DUP .        | • •  | •    | • •    | • •  | ٠   | •     | • •      | •  | • • | • | ٠ | • | • | • | C-50          |

| C.4.3.2  | OVER .       |      |      |        | • •  | •   | •     | • •      | •  |     | • | • | • | • | • | C-51          |

| C.4.3.3  | 20VER        | • •  | •    |        | • •  |     | •     | • •      | •  |     |   | • | • | • | • | C-52          |

| C.4.3.4  | <b>30VER</b> |      | •    |        |      |     |       |          |    |     |   | • |   | • |   | C-53          |

| C.4.3.5  | UNDER        |      | •    |        |      | •   | •     |          |    |     |   |   |   |   | • | C-54          |

| C.4.3.6  | 2UNDER       |      | •    |        |      |     |       | •••      |    |     |   |   |   |   |   | C-55          |

| C.4.3.7  | <b>A</b>     |      |      |        |      |     |       |          |    |     |   |   |   |   |   | C-56          |

| C.4.3.8  | DROP .       |      | •    |        |      | •   |       |          |    |     |   |   |   |   |   | C-57          |

| C.4.3.9  | SWAP .       | •••  | •    | • •    | • •  | •   | •     | •••      | •  | • • | • | • | • | • | • | C-58          |

| C.4.3.10 | 2SWAP        | • •  | •    | • •    | • •  | •   | •     | • •      | •  | • • | • | • | • | ٠ | • | C-59          |

| C.4.3.11 |              | • •  | ٠    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | • | • | ٠ | ٠ | C-60          |

|          | FLIP .       | • •  | •    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | ٠ | ٠ | ٠ | ٠ |               |

| C.4.3.12 | +ROT .       | • •  | ٠    | • •    | • •  | ٠   | •     | • •      | ٠  | • • | • | ٠ | ٠ | • | ٠ | C-61          |

| C.4.3.13 | -ROT .       | • •  | ٠    | • •    | • •  | ٠   | ٠     | • •      | ٠  | • • | • | ٠ | ٠ | ٠ | ٠ | C-62          |

|          | /O WORDS     | · ·  | ٠    | • •    | • •  | ٠   | •     | ••       | ٠  | • • | • | ٠ | ٠ | • | • | C-63          |

| C.4.4.1  | TYO .        | • •  | ٠    | • •    | • •  | •   | •     | • •      | ٠  | • • | • | ٠ | ٠ | ٠ | ٠ | C-64          |

| C.4.4.2  | CR           | • •  | •    | • •    | • •  | ٠   | •     | ••       | ٠  | • • | • | ٠ | ٠ | • | • | C <b>-</b> 65 |

| C.4.4.3  | SPACE        | • •  | ٠    | • •    |      | •   | •     | • •      | •  | • • | • | ٠ |   | • | • | C-66          |

| C.4.4.4  | SPACES       | • •  | •    | • •    | • •  | •   | •     | • •      | •  |     | • | • | • | • | • | C-67          |

| C.4.4.5  | TYI .        |      | •    |        |      | •   | •     | • •      |    |     | • | • |   | • | • | C-68          |

| C.4.4.6  | =            |      | •    |        |      |     | •     |          | •  |     |   | • | • | • | • | C-69          |

| C.4.4.7  | .1? .        |      |      |        |      |     |       |          |    |     |   |   |   |   |   | C-69          |

| C.4.4.8  | TYPE .       |      |      |        |      |     |       |          |    |     |   |   |   |   |   | C-70          |

|          | ORDS WHI     | СН   | CHAI | NGE    | THE  | CI  | IRRI  | ENT      | R۵ | אדת |   |   |   | • |   | C-71          |

| C.4.5.1  | .!-1<-       |      |      |        |      |     |       |          |    |     |   |   | • | • | • | C-72          |

| C.4.5.2  | •!+!         |      |      |        |      |     |       |          |    |     |   |   |   |   |   | C-72          |

|          |              |      |      |        |      |     |       |          |    |     |   |   |   |   |   |               |

| C.4.5.3  | .!1+!        |      |      |        |      |     |       |          |    |     |   |   |   |   |   | C-72          |

| C.4.5.4  | .!1-!        |      |      |        | • •  |     |       |          |    |     |   |   |   |   |   | C-72          |

| C.4.5.5  | .!MOVE       |      | -    |        | • •  |     |       |          | -  |     |   |   | - | - |   | C-72          |

| C.4.5.6  | .!XCHG       |      | ٠    |        | • •  | -   | -     |          |    |     | - |   | - | - | - | C-72          |

| C.4.5.7  | .!MVBY]      |      | •    | • •    | • •  | -   | -     |          |    |     | - |   | - | - | - | C-72          |

|          | ON DEFIN     | IITI | ONS  | •      |      |     |       | ••       |    |     |   |   |   |   | • | C-72          |

| C.6 ITE  | RATION       | • •  | •    | • •    | • •  | ٠   | •     | ••       | •  | • • | • | • | • | • | • | C-74          |

| C.6.1 N  | ( )          | •    | •    | • •    | • •  | ٠   | •     | • •      | •  | • • |   | • | • | • | • | C-75          |

|          | EGIN         |      | D    |        | • •  | •   | •     | • •      | •  |     |   | • | • | • |   | C-76          |

|          | EGIN         |      |      | . RI   | EPEA | т   | •     | • •      | •  |     |   |   | • | • | • | C-77          |

|          | 0 LOOPS      |      | •    |        |      |     | -     | ••       |    |     |   | - | - |   | • | C-78          |

| C.6.4.1  | EXIT ar      |      |      |        |      |     |       | •••      |    | • • |   |   |   | • |   | C-80          |

|          | ONDITION     |      |      |        | •••  | -   |       |          |    | • • | - | - |   | - |   | C-82          |

|          | NG DIAMO     |      |      |        |      | EYF | 30 41 | מא<br>מא | -  | ••• | - | - |   | - | - | C-83          |

| J., 001  |              |      |      | لب به. |      |     |       |          | •  | • • | • | • | • | • | • |               |

.

| C.8      | NESTING DEPTH AND CONTINUATION LINES C-8                                            |

|----------|-------------------------------------------------------------------------------------|

| C.8.1    | Postponing Execution C-8.                                                           |

| C.9      | REPEATING THE LAST COMMAND LINE C-80                                                |

| C.10     | DEFINING CONSTANTS, VARIABLES, AND ARRAYS C-8                                       |

| C.10.1   | CONSTANTS                                                                           |

| C.10.2   | VARIABLES                                                                           |

| C.10.3   | ARRAYS                                                                              |

| C.10.3.1 | 1 REFERENCING ARRAY ELEMENTS C-83                                                   |

| C.11     | THE DICTIONARY $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $C-9$ |

| C.12     | STRING HANDLING                                                                     |

| C.13     | NUMBER OUTPUT CONVERSION                                                            |

| C.14     | FORGET                                                                              |

| C.15     | DEBUGGING TECHNIQUES                                                                |

x · · ·

·

•

# CHAPTER 1

# SYSTEM OVERVIEW

# 1.1 INTRODUCTION

This chapter serves as an overview of the WICAT System 150 (mapped) computer system. The information contained herein is for use by field service technicians.

#### **1.2 DEFINITION AND FEATURES**

The WICAT System 150 (mapped) is a 68000-based microcomputer system with mainframe capabilities. A single desk-top unit (with detachable keyboard) contains:

- Central Processing Unit (CPU) (Section 1.6.1)

- Memory (Section 1.6.2)

- CRT (terminal screen) (Section 1.6.3)

- Storage and storage backup (Section 1.6.4)

- Several standard and optional peripherals (Section 1.6.5)

# 1.3 SYSTEM CONFIGURATION

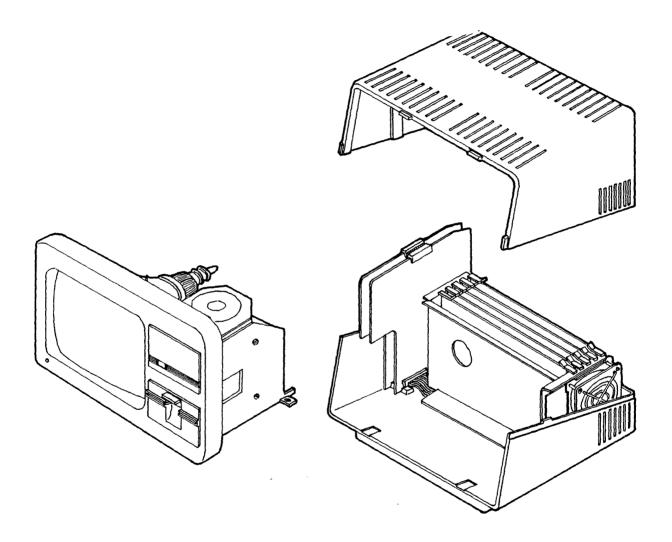

Refer to Figure 1-1.

The PC boards are held in place by the card cage located directly behind the CRT. At the base of the card cage is the motherboard containing six slots into which the boards are inserted.

The standard 150 multiuser configuration leaves two slots empty, but

SYSTEM OVERVIEW SYSTEM CONFIGURATION

è

upon request these slots can be used for two additional memory boards, or one additional memory board and a videodisc controller board.

To the left side of the card cage (with the CRT nearest you) and running perpendicular to the card cage are the graphics terminal boards (connected to each other by a ribbon cable) or a non-graphics terminal board.

To the right side of the CRT are located the Winchester disk and floppy disk drives.

The System 150 has a detachable keyboard connected to the terminal by a coiled cable.

Figure 1-1 System 150 Multiuser (Exploded View)

# WARNING

When removing the WD1000/Coupler Board, please exercise extreme caution to avoid damaging the end of the CRT.

1.4 BOARD CONFIGURATION

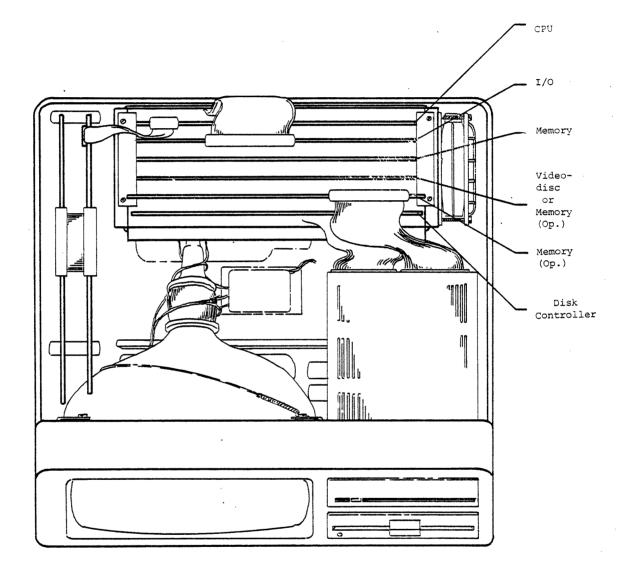

Refer to Figure 1-2.

The standard CPU chassis contains the following boards. (Indicated in parentheses immediately following the board name are later chapters that give detailed explanations):

- CPU (Chapter 2)

- I/O (Chapter 3)

- Memory Board (Chapter 4)

- WD 1000 and WD1000 Coupler/Floppy Disk Controller (Chapter 5)

Figure 1-2 Placement of Boards in CPU Chassis

# 1.5 BOARD INTERACTION

The **bus structure** amounts to a common group of circuit paths over which input and output signals are routed. This structure enables communication between the CPU board and the other PC boards.

# 1.5.1 Explanation Of Bus Structure

The PC boards and the CPU board are interconnected by the backplane, or motherboard, in the base of the chassis. The CPU board handles bus control.

There are three types of buses: address buses, which consist of all the signals needed to define any of the possible memory or I/O locations in the system; data buses, which handle all communication of instructions and data; and control buses, which are used by the CPU to direct the action of the other elements in the system.

# 1.5.2 Bus Control

The MC68000 microprocessor allocates CPU time for requesting processes and devices. The basic theory of allocation is simple. First, the CPU receives a request signal for bus use. Second, based on internally defined priorities, the request is either granted immediately or delayed until previous or higher priority requests are processed. Finally, when the request is granted, the requesting bus device returns an acknowledgement signal to the CPU and the cycle continues.

Once a device or process has been granted bus use, it is called the "Bus Master". (WICAT systems currently allow only one bus master at a time.) A device called the "slave" then receives or transmits data from or to the bus master.

# 1.6 SYSTEM DATA FLOW

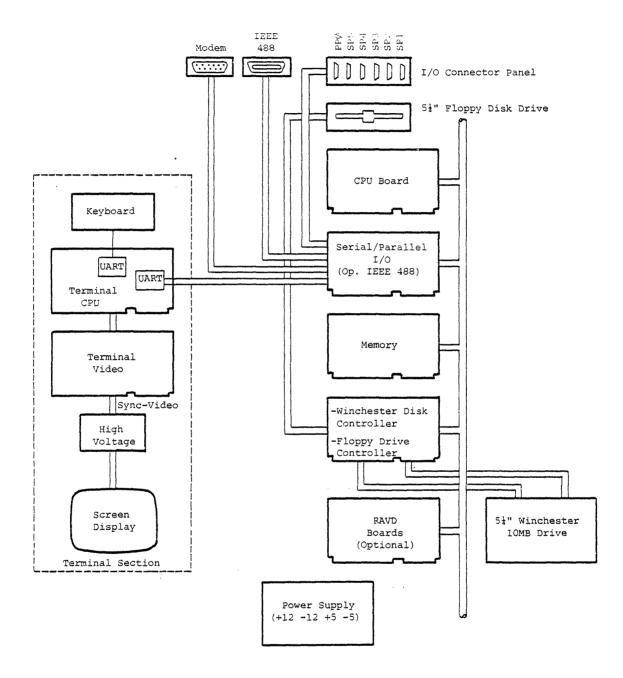

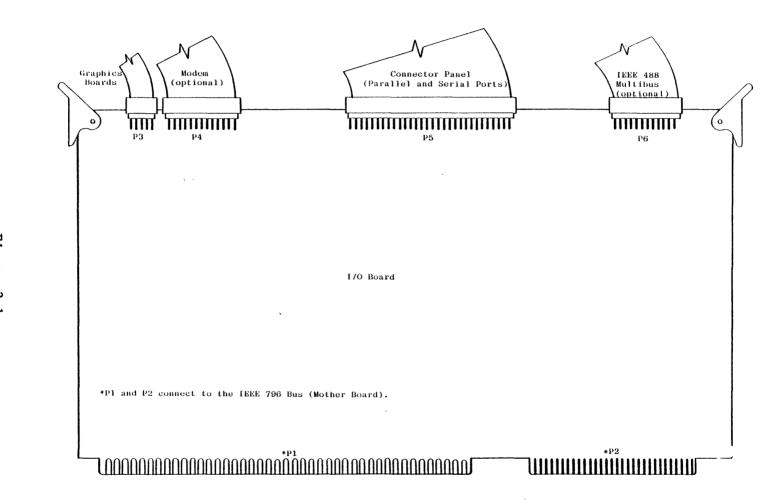

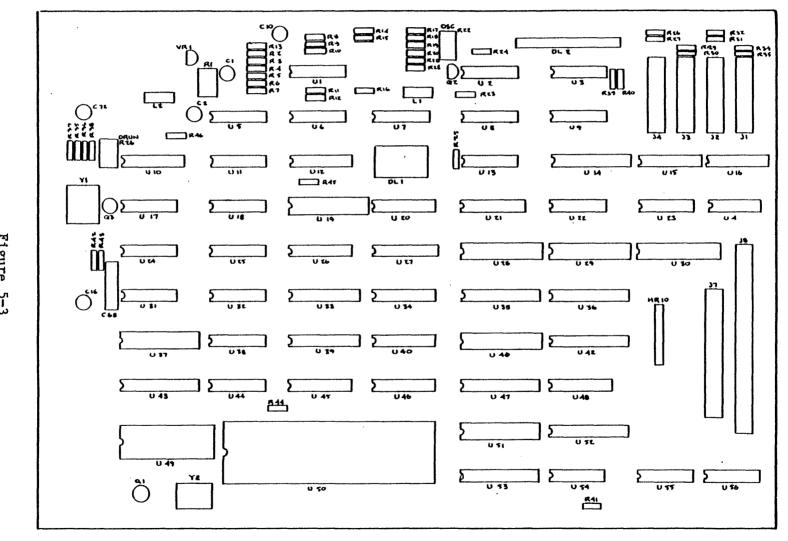

As shown in Figure 1-3, information is input to the System 150 through the keyboard. A serial link transfers the data to the terminal CPU, located on one of the boards perpendicular to the card cage (see Figure 1-1). The CPU is connected to the Pl connector on the I/Oboard by a ribbon connector.

The I/O board now acts as a liaison between the terminal section of

the System 150 and the other system boards. It sends data to the other boards as required through the circuitry of the IEEE 796 bus. Connector P5 connects the additional serial and parallel ports on the I/O board to the connector panel at the back of the chassis.

The I/O board has two other connectors (P4 and P6) that can be connected to peripheral devices. Connector P4 is configured as a full-handshake modem port and connector P6 is used for the optional IEEE 488 (GPIB) bus interface. See Figure 3-1 for connector locations on the I/O board.

The disk controller board controls the Winchester disk drive and the floppy disk drive.

The memory board on all standard 150's handles temporary data storage.

SYSTEM OVERVIEW SYSTEM DATA FLOW

Figure 1-3 System 150 Multiuser Data Flow Chart

# 1.6.1 Central Processing Unit (CPU)

The processor for the System 150 (mapped) is the Motorola 68000 microprocessor that runs at 8 megahertz (MHz) and executes approximately one million instructions per second. Thirty-two bit internal registers support 32-bit data operations.

See Chapter 2 for more information on the CPU.

## 1.6.2 Memory

The System 150 (mapped) is equipped with a single memory board containing 256 Kilobytes (Kbytes) of Dynamic Random Access Memory (DRAM) that is expandable to 512 Kbytes by fully populating the board. Two additional memory boards may be inserted into the chassis increasing the available memory space to 1.5 megabytes (Mb).

See Chapter 4 for more information.

# 1.6.3 CRT

The CRT has a resolution of  $300 \times 400$  pixels, allowing medium-resolution graphics when using the graphics option. Each character is 7 X 9 pixels.

#### 1.6.4 Storage

Mass storage includes a 10 Mb 5-1/4 inch Winchester disk drive and a 5-1/4 inch floppy disk drive for backup and file portability purposes.

#### 1.6.5 Peripherals

The standard and optional peripherals available on the System 150 (mapped) are:

- 5 RS232 serial interfaces (Section 1.6.5.1)

- 16-bit parallel interface (Section 1.6.5.2)

- Battery-backed clock (Section 1.6.5.3)

# SYSTEM OVERVIEW SYSTEM DATA FLOW

- Graphics circuitry (optional) (Section 1.6.5.4)

- Videodisc controller (optional) (Section 1.6.5.5)

- IEEE 488 interface (optional) (1.6.5.6)

# 1.6.5.1 Serial Interfaces -

These interfaces are used as input/output ports for various peripheral devices such as printers, terminals, etc. The interfaces are located on the I/O board (see Chapter 3) and conform to the standard RS232C to ensure asynchronous data transfers.

# 1.6.5.2 Parallel Interface -

This is a 16-bit parallel port organized as two 8-bit bi-directional ports and set up to act as a standard Centronics interface.

#### 1.6.5.3 Battery-backed Clock -

This clock, located on the I/O board, is a real time calendar clock for the system. It continues to keep time, in the event of a system failure or power-down, with power supplied by an on-board battery.

# 1.6.5.4 Graphics Circuitry (Optional) -

Two graphics boards located perpendicularly to the CRT allow system graphics to be available as an option.

#### 1.6.5.5 Videodisc Controller (Optional) -

To make the System 150 (mapped) compatible with a videodisc player, a printed circuit (PC) board configured for videodisc control is inserted into the first of the available slots in the chassis (see Figure 1-2).

This option allows the System 150 to interface with a videodisc player's parallel control port.

1.6.5.6 IEEE 488 Interface (Optional) -

Additional components on the I/O board (see Chapter 3 and Figure 3-1) make up this option. The IEEE 488 interface is a standard General Purpose Interface Bus (GPIB), allowing the use of other external peripherals.

# CHAPTER 2

# CPU BOARD

# 2.1 INTRODUCTION

This chapter explains the components of the CPU board and focuses on the operations performed by the microprocessor.

# 2.2 DEFINITION AND FEATURES

The CPU board handles the central processing of the System 150 (mapped) and controls all bus use requests. The key component on the board is the Motorola 68000 microprocessor. The CPU board has the following features:

- Memory map (Section 2.5)

- Error control (Section 2.6)

- On board peripherals and memory (Section 2.7)

- Address decoding (Section 2.8)

1.1

2.3 CPU BOARD CONFIGURATION

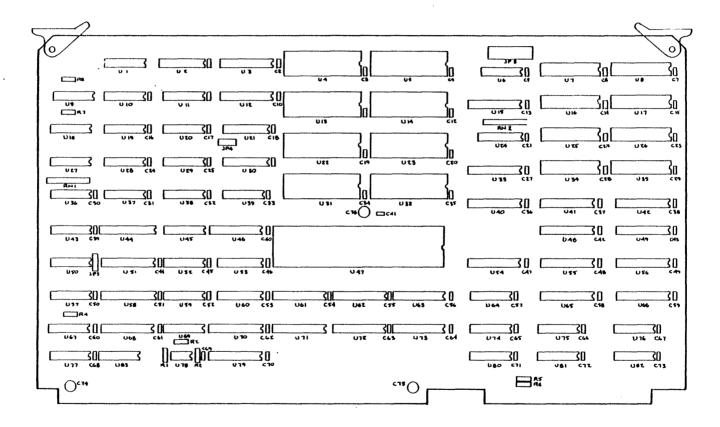

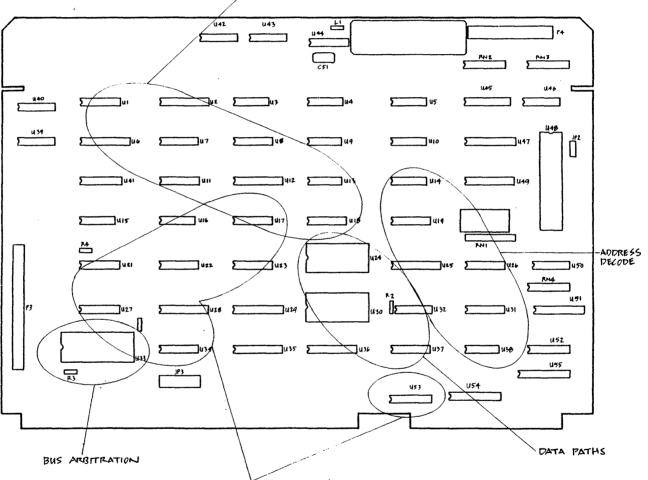

Refer to Figure 2-1.

The CPU board comprises five main areas of circuitry:

# CPU BOARD CPU BOARD CONFIGURATION

- Multibus Interface (Section 2.2.1)

- On-board ROM (Section 2.2.2)

- Interrupt Circuitry (Section 2.2.3)

- Bus Arbitration Circuitry (Section 2.2.4)

- Memory Mapping Registers (Section 2.2.5)

Figure 2-1 CPU Board Circuitry

CPU BOARD CPU BOARD CONFIGURATION

2-3

CPU BOARD CPU BOARD CONFIGURATION

The circuitry of the CPU board is divided into two principal functions: the CPU bus-associated functions and some system I/O functions. The connectors are the system bus proper. They contain paths and connections for the system data, address, and control.

# 2.3.1 The MULTIBUS Interface

The MC68000 microprocessor and the INTEL Multibus are incompatible because the Microprocessor defines the lower byte of the data bus as odd and the upper byte of the data bus as even; this data byte definition is reversed on the Multibus. An interface in the form of **byte swap buffer** ensures that odd and even single-byte transfers always take place on the low order data lines. Thus, the CPU board conforms to the INTEL MULTIBUS standard for both eight- and sixteen-bit systems. Word transfers use the full set of sixteen data lines.

# CAUTION

When writing a byte to a peripheral device the least significant address bit must be complemented or inverted by the software because of the MC68000 to MULTIBUS incompatibilities.

# 2.3.2 On Board ROM

The CPU board can support up to 64K bytes of on board Read Only Memory (ROM). ROM address decoding is done through a 74S288 PROM. ROM sizes of 2K X 8, 4K X 8, or 8K X 8 can be accommodated by changing two jumpers and the address decode PROM. The CPU board accepts 2K X 8 EPROMs as standard. The CPU board will accept the other two types of EPROMs if you change the jumpers as specified in Figure 2-2.

2-4

# EPROM SIZE 4K X 8

| Jumper | • | IN/OUT |

|--------|---|--------|

| JP1    | А | OUT    |

|        | В | IN     |

| JP2    | A | IN     |

|        | В | OUT    |

# EPROM SIZE 8K X 8

| Jumper | • | IN/OUT |

|--------|---|--------|

| JP1    | А | OUT    |

|        | В | IN     |

| JP2    | А | OUT    |

|        | В | IN     |

# Figure 2-2 Jumper Configuration for Larger EPROMs

# 2.3.3 Interrupt Circuitry

The CPU board supports seven levels of interrupts, INTO/ through INT6/, with INTO/ having the highest priority. INTO/ is the only nonmaskable interrupt. All interrupts are autovectored to addresses designated by the MC68000. See Section 2.3.5 and the appropriate section of the Motorola's MC68000 l6-Bit Microprocessor User's Manual, January 1980.

# 2.3.4 Bus Arbitration Circuitry

The CPU bus arbitration scheme conforms to the MULTIBUS specification for serial priority bus arbitration. When a MULTIBUS device wants control of the bus it checks its BPRN/ signal. If the BPRN/ signal is low, the Multibus sets its BPRO/ signal high. The high signal disables all lower priority bus requests and sends the MULTIBUS device's request to the CPU. The arbitration sequence is then as follows:

1. The CPU finishes executing the current instruction and sets the BUSY/ line high to tell the requesting device that it can take control of the bus.

# CPU BOARD CPU BOARD CONFIGURATION

- 2. The requesting device then pulls BUSY/ low and takes control of the bus.

- 3. When finished with the bus, the requesting device sets its BPRO/ line low, then sets the BUSY/ line high.

- 4. If no bus requests are pending, the CPU regains control of the bus.

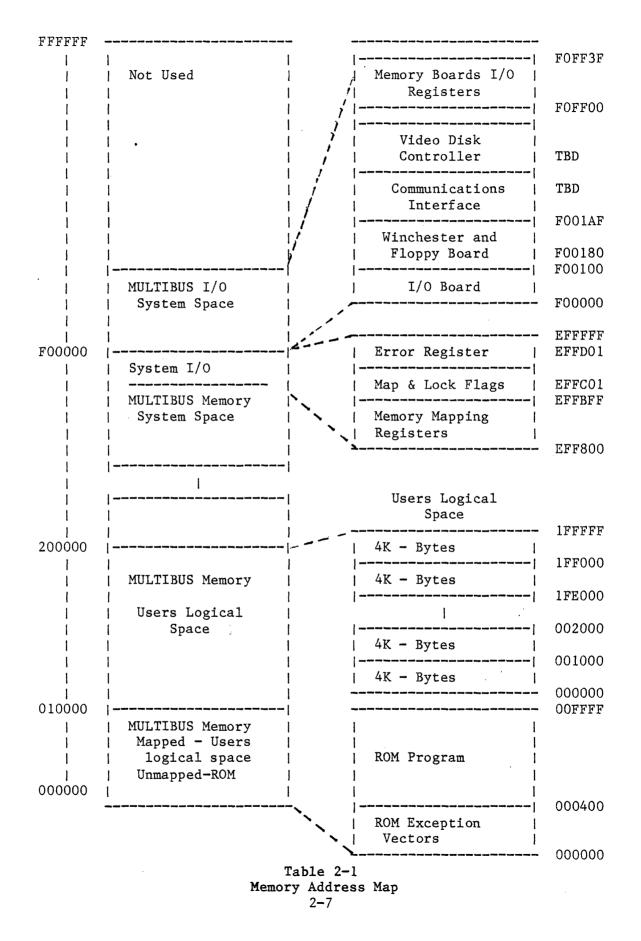

All bus arbitration signals are synchronized with the falling edge of BCLK. Table 2-1 is an address map.

CPU BOARD CPU BOARD CONFIGURATION

# 2.3.5 Memory Mapping Registers

lk of high speed static RAM at address EFF800-EFFBFF on the CPU board is available for memory mapping. Address lines A12-A20 are the inputs to the RAMs. The data lines out of the RAMs become the new lines A12-A23. The mapping function is enabled by writing an 80 to EFFC01 and disabled by writing a 00 to EFFC01. This sets and clears a bit addressable latch U2 on the CPU board.

# 2.4 PROCESSOR CIRCUITRY

The CPU board contains the Motorola MC68000 Microprocessor, which directs control, logic, and arithmetic operations required of the **SYSTEM 150 (mapped)**. The processor circuitry is comprised of the microprocessor, its associated buffers, system clocks; and, bus error, interrupt, and arbitration logic.

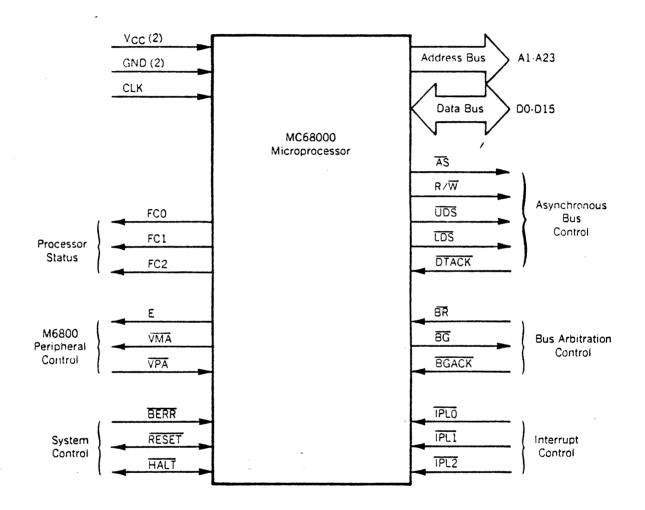

Input and output signals of the microprocessor fall into the groups shown in Figure 2-3.

Figure 2-3 Input and Output Signals

CPU BOARD PROCESSOR CIRCUITRY

#### 2.4.1 Address Bus

The microprocessor uses a 23-bit address bus to select one of eight two-byte megawords. The lower 11 address lines are directly buffered onto the bus connector. Normally, the upper 12 lines are routed directly from the 68000 to the bus connector.

However, the upper 12 lines may be treated as a logical address and the bus transaction may be steered by the mapping registers into a physical location when the processor is in user state, or in supervisor state with memory mapping flag set and the address is less than one megaword (= two megabytes).

The address bus is asserted LOW at the bus connector and is the logical inversion of the address bus at the microprocessor. The address lines from the CPU board are put into a high impedance state when another master controls the bus.

# 2.4.2 Data Bus

The MC68000 uses a 16-bit data bus to transfer programs or data. The data bus is buffered at the bus connector.

The most significant data bits (D8-15) are the odd bytes, and the least significant bits (D0-D7) are the even bytes. When the processor executes a byte operation, the least significant address bit--A0 is determined from the upper and lower data strobes (see Section 2.3.3). This process determines whether the processor will transfer an even or an odd byte.

Operating on a word or an even address boundary will produce a <u>different</u> effect than operating on a byte at the same address. Executing a word instruction on an odd boundary causes an illegal address trap.

You may connect an eight-bit peripheral to the data bus with the byte access option or the word access option.

1. Byte Access Option

The data lines can be connected to the least significant eight data bus lines (DO-17) and all accesses to the peripheral may then be byte or word accesses.

2. Word Access Option

The peripheral data lines can be connected to the most significant eight data bus lines (D8-15) and

all accesses must then be word accesses. A word access will access the odd and the even bytes. A byte instruction may not be used to access the peripheral when connected to the most significant eight data lines.

The data bus is asserted LOW at the bus connector. When another master has control of the bus, the CPU board bus buffers are placed in a high impedance state.

2.4.3 Synchronous Bus Control

# NOTE

The following information regarding bus control concerns the 796 bus.

Five control signals listed here coordinate data transfer on a synchronous bus.

- 1. Memory Read Control (MRDC/)

- 2. Memory Write Control (MWTC/)

- 3. I/O Read Control (IORC/)

- 4. I/O Write Control (IOWC/)

- 5. Transfer Acknowledge (XACK/)

2.4.3.1 Command Lines (MRDC/, MWTC/, IOWC/, And IORC/) -

These command lines are communication links between the bus masters and bus slaves. There are four command lines for memory and I/O reads and writes. An active command line indicates to the slave that the address lines are carrying a valid address, and that the slave should perform the specified operation. CPU BOARD PROCESSOR CIRCUITRY

2.4.3.2 Transfer Acknowledge Line (XACK/) -

This line is the slave's acknowledgement of the master's command. XACK/ indicates to the master that the requested action is complete, and that data has been placed on or accepted from the data lines.

2.4.4 MG68000 Bus Control

# Address Strobe (AS L)

AS L is a control signal asserted when the address on the bus is stable and considered valid. It will remain asserted until Data Transfer ACKnowledge (DTACK L) is asserted in response. If the addressed device is not attached or occupied, the level of the Bus ERRor line changes from high to low. The Error Control Circuitry disables AS L before it reaches the bus connector if:

- a. an access violation occurs in the current cycle.

- b. a parity error occurs in the previous cycle.

#### Data Transfer ACKnowledge (DTACK)

The device currently being addressed asserts DTACK when that device is ready to terminate the bus transaction. DTACK is negated in response to the negation of Address Strobe.

# Upper and Lower Data Strobe (UDS L and LDS L)

The CPU uses UDS L and LDS L to select one or both of the bytes from the word currently being addressed by the address bus.

# Read/Write (R/W)

R/W determines the direction of the data transfer. When LOW, data are moving TO memory. When HIGH, data are moving away FROM memory.

# 2.4.5 Bus Arbitration Control

# 2.4.5.1 Single Device Arbitration -

The MC68000 uses three lines to arbitrate bus use among devices:

- 1. Bus Request (BR L) an input signal that can be driven by any number of devices wired-OR devices.

- 2. Bus Grant (BG L) an output signal indicating that the requesting device may use the bus after the current bus transaction finishes.

- 3. Bus Grant ACKnowledge (BGACK L) when asserted at the end of the bus cycle, BGACK L allows the requesting device to become bus master under three conditions:

- a. Address strobe and DTACK are negated

- b. No other device is using the bus

- c. The bus request is negated

# 2.4.5.2 Multi-Device Arbitration -

Three MSI logic devices on the CPU board automatically prioritize bus requests and grants. On the left (or I/O) connector are eight bus request lines (BRO-7) and eight corresponding bus grant lines (BGO-7). BR7 has the highest priority.

Requests for bus use are prioritized depending on the bus request line used for input. The number of the highest request is latched onto the falling edge of bus grant from the processor. The outputs of this latch then drive the inputs to a three-to-eight line decoder that selects the highest priority bus grant line. Thus, a device simply asserts its bus request line and waits until its bus grant line is asserted. When the device recognizes its bus grant, it waits until the end of the current bus cycle to verify that BGACK is not asserted. After the verification the device asserts BGACK, negates its bus request, and becomes bus master.

If more than one bus request is pending, the arbitration logic selects the bus grant corresponding to the highest priority bus request. After the device with the highest priority has become bus master, the arbitration logic will select the bus grant corresponding to the bus request with the next highest priority. CPU BOARD PROCESSOR CIRCUITRY

When the current bus master is through with the bus, the next device immediately takes control. The arbitration logic then selects the next device with the highest priority. Thus, the arbitration logic manipulates the queu according to device priority.

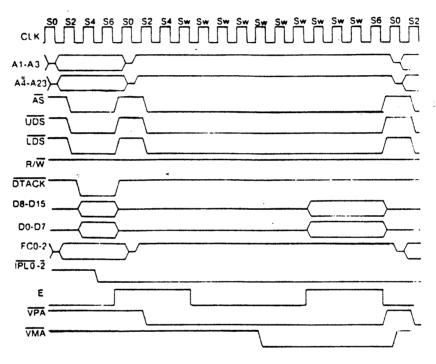

## 2.4.6 Interrupt Control

The MC68000 supports seven interrupt levels. Level seven is nonmaskable and is the highest priority.

Interrupts are actually a subset of a more general class of operations called exceptions. Interrupts are either autovectored or nonautovectored but the CPU board circuitry simplifies the interrupt process on autovectored interrupts:

- a. autovectored The processor generates the interrupt vector number internally, as a function of the interrupt level.

- b. nonautovectored The processor reads the interrupt vector number from the interrupting device.

In each case the processor executes an interrupt acknowledge sequence. During this sequence, the function codes indicate an interrupt acknowledge cycle, the address lines A4-23 are set to 1's, and the interrupt level is placed on address lines A1-3. If Valid Peripheral Address, VPA L, (2.3.7.[b]) is asserted during this bus cycle, the interrupt will be interpreted as autovectored, in which case the bus cycle emulates a MC6800 cycle. No DTACK will be expected and the transaction will terminate after approximately 1 microsecond. The interrupting device need not respond because the processor generates its own interrupt vector number based on the level of the interrupt.

If VPA is not asserted during the interrupt acknowledge sequence, the interrupt is considered nonautovectored, and the interrupting device responds with a vector number on data bus lines DO-7 (odd byte). The upper byte is ignored. This transfer takes place just as a normal read operation does. The interrupting device asserts DTACK when the data have been placed on the bus. This number is then multiplied by four to obtain the address of the interrupt vector. Figure 2-4 is a photographic recording of signal activity during an autovectored interrupt sequence.

Normal Cycles ----- Autovector Operation -----

Figure 2-4 Signal Activity During an Autovectored Interrupt Sequence CPU BOARD PROCESSOR CIRCUITRY

After the interrupt vector number is obtained, either by internal generation or by external read, the processor saves the status and return address on the system stack and then uses the vector number to access the interrupt vector (interrupt handler routine address) from memory. The processor then continues execution at the interrupt handler routine.

Eighteen wire-wrap pins on the high end of the left (I/0) connecter (location M9) are arranged in six equivalent groups. Each group configures the type of interrupt for levels one through six. Level seven is reserved for the error control circuitry as described in section 2.5. Level six is the leftmost group and level one is the rightmost group of pins, as viewed from the connector edge of the board.

Jumpering the center pin of any group to the pin above it (away from the connector) defines that interrupt level to be autovectored. Jumpering to the pin below it (toward the connector), defines it as nonautovectored.

The example in **Figure 2-2** shows levels six, five, and two defined as autovectored, and levels four, three, and one defined as nonautovectored. The system leaves the factory with all levels defined as autovectored.

If an interrupt level has been defined as autovectored, VPA will be automatically asserted during an interrupt acknowledge bus cycle. If the level is defined as nonautovectored, VPA will not be asserted during interrupt acknowledge.

#### NOTE

IF VPA IS ASSERTED during the interrupt acknowledge bus cycle, the processor still executes an autovectored interrupt sequence even if the interrupt level is jumpered to be nonautovectored. An device connected to a interrupting nonautovectored interrupt level may still cause an autovectored sequence by VPA asserting during interrupt acknowledge.

2-16

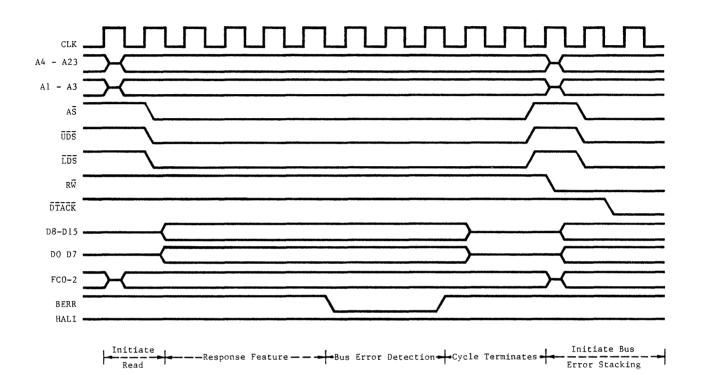

2.4.7 System Control

System control comprises three lines, RESET (RESET L), HALT (HALT L), and Bus ERRor (BERR L). RESET and HALT are bidirectional. On power-up and during manual reset conditions, both the RESET and HALT lines are driven as inputs for a minimum of 200 mSec. In no other case is HALT or RESET driven as an input. The processor asserts RESET while executing a reset instruction and asserts HALT when the processor is halted.

A high-to-low transition on the Bus ERRor line tells the processor that a specified time has elapsed without a DTACK response to the assertion of Address Strobe. The DIS CPU implements the Bus ERRor timer with a presettable counter. This counter is clocked at 4 MegaHertz, but is normally held in the clear (all zeroes) condition.

When Address Strobe is asserted, the counter is allowed to begin. After 16 clock cycles, the ripple carry output causes the assertion of Bus ERRor. If, however, DTACK is asserted before the 16 counts can occur, the counter is stopped, and the negation of Address Strobe will again hold the counter in the clear state. The 16 counts with a clock cycle time of 250 nS provides a bus error time out of 4.0 uS. This value is nonadjustable.

Figure 2-5 is a record of a bus error sequence.

When an access or parity error occurs, address strobe is not asserted on the bus. Although the processor expects a DTACK, it receives none. Normally, the bus error timer times out after 4.0 uS and causes the assertion of Bus ERRor.

Because this causes an erroneous bus trap, the circuitry can detect a bus error time out resulting from the blocking of the address strobe. In this case, Bus ERRor is not asserted and the bus error timer overflow latches the error conditions and generates a DTACK so that the processor can finish its bus cycle.

2-17

CPU BOARD PROCESSOR CIRCUITRY

Figure 2-5 Bus Error Sequence

#### 2.4.8 MC68000 Peripheral Control

The MC68000 provides three lines for interfacing MC6800 peripheral devices:

- a. Enable (E)- a clock signal that synchronizes transactions between the processor and MC6800 type peripherals. The clock period is ten times the system clock (10 x 125nS = 1.25uS) and has a 60/40 duty cycle (6 clocks low, 4 clocks high).

- b. Valid Peripheral Address (VPA L) asserted by the peripheral device when it recognizes its address on the address bus. VPA L is also used to distinguish between auto and nonautovectored interrupts during an interrupt acknowledge sequence.

- c. Valid Memory Address (VMA L) asserted by the processor in response to the assertion of VPA L during an MC6800 peripheral data transfer.

E and VMA L are buffered onto the bus. VPA L is a shared tri-state input to the CPU board.

#### 2.4.9 Processor Status

The values of the function code lines (FCO-2) determine the status of each MC68000 bus cycle. See Figure 2-6 for these values.

| FC2                       | FC1                                 | FCO | Cycle Type            |

|---------------------------|-------------------------------------|-----|-----------------------|

| و بين هيد جب حيد جب يب جب | یس افاد که بربه برب وی خود خود بربه |     |                       |

| 0                         | 0                                   | 0   | (Undefined, Reserved) |

| 0                         | 0                                   | 1   | User Data             |

| 0                         | . 1                                 | 0   | User Program          |

| 0                         | 1                                   | 1   | (Undefined, Reserved) |

| 1                         | 0                                   | 0   | (Undefined, Reserved) |

| 1                         | 0                                   | 1   | Supervisor Data       |

| 1                         | 1                                   | 0   | Supervisor Program    |

| 1                         | 1                                   | 1   | Interrupt Acknowledge |

Figure 2-6 Function Code Line Values CPU BOARD PROCESSOR CIRCUITRY

As seen in the Figure 2-6, whenever FC2 is zero, the processor is in user mode. The memory mapping logic uses FC2 to determine when to map the processor address. The interrupt acknowledge condition is decoded on the CPU board and buffered, along with the values of the function codes, out onto the bus.

#### 2.5 MEMORY MAP

If mapping occurs the original upper three addresss bits (A21-23) are zeroes (users are confined to a one-megaword address space). The next nine address bits (A12-20) will be used to access one of 512 locations of the memory mapping registers. These registers are 16 bits wide, containing 12 bits of new address and three bits of access control information. One bit is not used. Each register location within the memory map represents a 2K word segment of logical space, representing one megaword of memory in all.

When a memory map register is accessed, the 12 bits of new address information replace the original upper 12 address bits. This scheme allows the system to map any of the user's 512 2K word segments into any of the system's 4096 2K word segments. In reality, only the lower 14 megabytes are reserved for routine memory functions. The upper two megabytes are reserved for system and I/O space.

The three bits of access control information interact with the function codes representing the state of the processor and the Memory Mapping Flag to check for access errors as described in chapter four. Figure 2-7 shows the memory mapping register format.

| D15         | D14 | D13 | D12 | D11 - DO                                                     |                                                                                                          |

|-------------|-----|-----|-----|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Not<br>Used | 1/0 | 1/Ø | 1/0 | Physical Segment Number                                      |                                                                                                          |

|             |     |     |     | Ø: Segment N<br>1: Segment N<br>Ø: Segment N<br>1: Segment N | Write Protected<br>Not Protected<br>Number Invalid<br>Number Valid<br>Not Resident<br>Resident in Memory |

Figure 2-7 Memory Mapping Register Format

CPU BOARD MEMORY MAP

The memory map is accessible as read/write memory beginning at location EFF800 (hex).

#### 2.6 ERROR CONTROL

The CPU board error control circuitry monitors the address for address violations. When an error occurs, the error type is latched, and a level seven interrupt is generated.

#### 2.6.1 Address Errors

An illegal condition on the address bus causes an address error. Nonmapped addresses are inherently legal except for a word access on a byte boundary, so that an access error can only occur when the map is active. Four address errors are associated with using the memory map:

- access violation occurs when you try to access outside of user space, defined as 000000 - 1FFFFF (2 MegaBytes).

- write violation occurs when you try to write to a segment that is write protected.

- 3. invalid segment occurs when you try to access a nonallocated segment.

- 4. **nonresident segment -** occurs when you try to access a nonresident segment.

Conditions 2, 3, and 4 above result directly from the access control information stored for each segment in the memory mapping registers.

#### 2.6.2 The Error Register

All error conditions are sampled at the assertion of XACK/ at the end of a bus cycle. There is no danger, however, that an address error will cause erroneous data transfers since the error condition blocked the assertion of address strobe on the bus. In this case the bus error timer will time out asserting XACK/ (thereby latching the error condition).

If an error condition exists, the error register, which holds the values of the error conditions as sampled at the assertion of DTACK, is disabled from further change until it has been read by the CPU. Also, a level 7 autovectored interrupt is generated and held until it

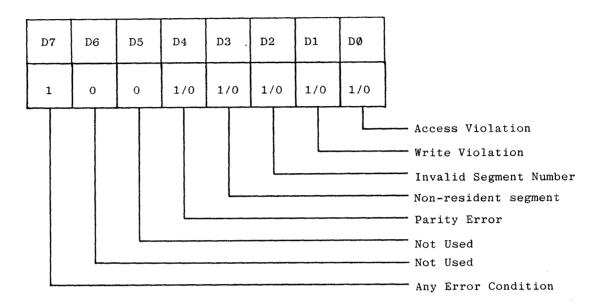

is reset by the reading of the error register. The contents of the error register are defined in the diagram below:

## Figure 2-8 Error Register

The error condition flags (bits DO-D4) are active high, i.e., a one indicates that an error occurred. Register bit D7 will be a zero if an error condition is active. Register bits D5 and D6 are always zeroes.

The error conditions are latched at the assertion of XACK/ only if an error is detected at that time. When the error register is read, the level seven interrupt is reset but the contents of the error register remain intact. They will not change until another error is detected and latched.

CPU BOARD ON BOARD PERIPHERALS AND MEMORY

## 2.7 ON BOARD PERIPHERALS AND MEMORY

The on board peripheral/memory address and data busses are sourced from the connector on the backplane and thus accessible to any device currently controlling the bus. The single exception to this rule is that another device cannot access the memory mapping registers.

## 2.7.1 Memory Mapping Flag And The Error Register

Two other devices may be considered on board peripherals: the Memory Mapping Flag and the Error register.

If the processor is in supervisor state and the processor address bus is carrying an address below 2 MegaBytes, then the value of the Memory Mapping Flag will determine whether the address will be mapped. The address will be mapped if the value of the flag is a one. It will not be mapped if it is a zero. The Memory Mapping Flag is set by writing 80 to location EFFCO1. This is an even byte address. It may be reset by writing 00 to the same location. The value of the flag may not be read and is automatically reset to zero when the processor begins an interrupt acknowledge bus cycle, and when the system is reset.

The Error Register is a read-only byte location in memory. Its contents represent the error conditions present when the last address or parity error occurred. An error generates a level seven interrupt. Reading the Error Register (address = EFFD01) clears the interrupt.

#### 2.7.2 On Board Memory

Sockets for 8 UV-EPROMs, either 2Kx8, 4Kx8, or 8Kx8 allow for 16K, 32K, or 64K bytes of ROM. The CPU board supports the memory board and any other part that conforms to these standards. In addition, the board also supports either the memory board standards by selecting the appropriate jump options. The memory type select jumpers are located between C7 and C8 on the CPU board. It consists of six pins arranged in three rows of two columns and two jump connections. (See Figure 2-9 for the various jumper configurations.)

2-24

,

|               | JP1          | JP2 |   |          |           |

|---------------|--------------|-----|---|----------|-----------|

| 0             |              |     |   |          |           |

| Configuration | 0            | 0   |   | to Bus C | onnectors |

| for TMS 2516. | 1            | 1   | А |          |           |

|               | о            | 0   |   |          | 1         |

|               |              |     | В |          | Í         |

|               | о            | 0   |   |          | v         |

|               | 0            | U   |   |          | •         |

|               |              |     |   |          |           |

|               |              |     |   |          |           |

| Configuration | 0            | 0   |   |          |           |

| for TMS 2532  |              | 1   | A |          |           |

|               | 0            | 0   |   |          |           |

|               | 1            |     | В |          |           |

|               | o<br>o       | 0   |   |          |           |

|               | -            | -   |   |          |           |

|               |              |     |   |          |           |

| Comfiguration | •            | •   |   |          |           |

| Configuration | 0            | 0   |   |          |           |

| for TMS 2564. |              |     | A |          |           |

|               | 0            | 0   |   |          |           |

|               | I            | 1   | В |          |           |

|               | 0            | 0   |   |          |           |

|               | 0 <b>-</b> - | -   |   |          |           |

|               | 0            | 0   |   |          |           |

Figure 2-9 Jumper Configurations

The ROM is configured to reside in the lower 16K (or 32K or 64K) bytes of system memory. Figure 2-10 shows the board placement.

ŝ

٠

,

## CPU BOARD ON BOARD PERIPHERALS AND MEMORY

.

|   | Even Bytes<br>(D8-D15)<br>5 | Odd Bytes<br>(DO-D7)<br>6 7 |

|---|-----------------------------|-----------------------------|

| A | <br>  ROMO  <br>  even      | <br>  ROMO  <br>  odd       |

| В |                             | ROM1  <br>  odd  <br>       |

| С | ROM2  <br>  even  <br>      | ROM2  <br>  odd             |

| D | ROM3  <br>  even            | ROM3  <br>  odd             |

| E | II                          | II                          |

| [ OK- 4K) | [ 4K <b>-</b> 8K)  | [ 8K-12K) | [12K <b>-</b> 16K) | 2Kx8's |

|-----------|--------------------|-----------|--------------------|--------|

| [ OK- 8K) | [ 8K-16K)          | [16K-24K) | [24K-32K)          | 4Kx8's |

| [ OK-16K) | [16K <b>-</b> 32K) | [32K-48K) | [48K <b>-</b> 64K) | 8Kx8's |

To Bus Connectors

| | V

Figure 2-10 ROM Configuration

.

-

#### 2.8 ADDRESS DECODE

The address decode logic decodes the value of the address bus and drives select lines for the on board peripherals and memory as well as general purpose I/O device and buffer select lines.

## 2.8.1 On Board Device Selection

The on board device selects are generated as the outputs of a 74154, 4 to 16 line decoder. The decoder is enabled when the address EOOBxx (x = don't care) appears on the address bus. The next to the least significant hex digit determines which on board device is being selected, while the least significant hex digit is reserved for register selection within the device itself. This scheme allows for a maximum of 16 on board peripherals. Currently only seven of these select lines are used. DTACK is asserted whenever EOOBxx appears on the address bus.

The memory mapping registers are selected whenever E00Cxx - E00Fxx appears on the address bus, providing for 1K bytes (512 registers) of memory map. DTACK is asserted whenever the map is selected as an I/O device.

The on board ROM is selected whenever OOxxxx appears on the address bus. This allows for a maximum of 64K bytes of ROM; 32K bytes are now implementable. DTACK is asserted whenever this area of memory is addressed.

#### 2.8.2 CPU Board Address Decoding

The following summarizes the CPU board address decoding:

CPU BOARD ADDRESS DECODE

On Board Peripherals/Memory -

Read Only Memory: 000000 - 003FFF (2Kx8's) (standard) 000000 - 007FFF (4Kx8's) 000000 - 00FFFF (8kx8's)

Clock/Timer: TBD

Memory Mapping Flag: EFFC01

Error Register: EFFD01

Memory Mapping Registers: EFF800 - EFFBFF

Off Board Memory -

RAM/ROM: 020000 - EFF7FF

I/O and Off Board Space -

F00000 - F0FFFF

## 2.8.3 EPROM Configuration Firmware

One 74S288 PROM on the CPU board must be programmed according to the EPROM configuration for your System 150. Tabulated below is the firmware programming for the three EPROM configurations possible with the CPU board. Standard configuration is  $2K \ge 8$  EPROMS. Use the nonstandard PROM programs (Tables 2-3 and 2-4) only after the EPROMS on the CPU board have been updated to the size indicated above the tables. All address and data information is in hexadecimal.

| Data               | Address                                                                                                                                                                                                                                                                                                                                                    | Data                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •••• OE            | 10                                                                                                                                                                                                                                                                                                                                                         | •••• OF                                                                                                                                                                                                                                                                                                                                                                         |

| ••• OB             | 12                                                                                                                                                                                                                                                                                                                                                         | •••• OF                                                                                                                                                                                                                                                                                                                                                                         |

| ••• OF             | 14                                                                                                                                                                                                                                                                                                                                                         | ••••• OF<br>•••• OF                                                                                                                                                                                                                                                                                                                                                             |

| •••• OF<br>••• OF  | 15<br>  16                                                                                                                                                                                                                                                                                                                                                 | •••• OF<br>•••• OF                                                                                                                                                                                                                                                                                                                                                              |

| •••• OF<br>•••• OF | 17<br>  18                                                                                                                                                                                                                                                                                                                                                 | ••••• OF<br>•••• OF                                                                                                                                                                                                                                                                                                                                                             |

| •••• OF<br>••• OF  | 19<br>  1A                                                                                                                                                                                                                                                                                                                                                 | •••• OF<br>•••• OF                                                                                                                                                                                                                                                                                                                                                              |

| ••• OF             | 1 1B                                                                                                                                                                                                                                                                                                                                                       | •••• OF                                                                                                                                                                                                                                                                                                                                                                         |

| ••• OF             | 1D                                                                                                                                                                                                                                                                                                                                                         | •••• OF                                                                                                                                                                                                                                                                                                                                                                         |

| ••• OF             | 1 IF                                                                                                                                                                                                                                                                                                                                                       | ••••• OF                                                                                                                                                                                                                                                                                                                                                                        |

|                    | <ul> <li>OD</li> <li>OB</li> <li>OF</li> </ul> | OD               11          OB               12          OF               13          OF               14          OF               14          OF               15          OF               16          OF               17          OF               18          OF               18          OF               IB          OF               ID          OF               ID |

Table 2-2 2K X 8 EPROMS (standard)

.

ş

| Address | Data   | 1 | Address | Data    |

|---------|--------|---|---------|---------|

| _       | •      | 1 |         |         |

| 0 ••••• | ••• OE | 1 | 10      | •••• OF |

| 1       | ••• OE | 1 | 11      | •••• OF |

| 2       | ••• OD | 1 | 12      | •••• OF |

| 3       | ••• OD | I | 13      | •••• OF |

| 4       | ••• OB | 1 | 14      | •••• OF |

| 5       | ••• 07 | i | 15      | OF      |

| 6       | ••• 07 | 1 | 16      | •••• OF |

| 7       | ••• OF | 1 | 17      | •••• OF |

| 8       | ••• OF | I | 18      | •••• OF |

| 9       | ••• OF | I | 19      | •••• OF |

| Α       | ••• OF | 1 | 1A      | •••• OF |

| В       | ••• OF | 1 | 1B      | •••• OF |

| С       | ••• OF | 1 | 1C      | OF      |

| D       | ••• OF | 1 | 1D      | •••• OF |

| Ε       | ••• OF | 1 | 1E      | •••• OF |

| F       | ••• OF | 1 | 1F      | OF      |

4K X 8 EPROMS

Table 2-3 4K X 8 EPROMS

-

.

.

| Address | Data        | - <b></b> | Address              | Data   |

|---------|-------------|-----------|----------------------|--------|

|         |             | i         |                      |        |

| 0       | •••• OE     |           | 10                   | ••• OF |

| 1       | •••• OE     | 1         | 11                   | ••• OF |

| 2       | •••• OE     | i         | 12                   | ••• OF |

| 3       | •••• OE     | l         | 13                   | ••• OF |

| 4       | •••• OD     | i         | 14                   | ••• OF |

| 5       | •••• OD     | i         | 15                   | ••• OF |

| 6       | •••• OD     |           | 16                   | ••• OF |

| 7       | 0.0         | 1         | 17                   | 07     |

| 8       | •••• OB     |           | 18                   | ••• 0F |

| 9       | •••• OB     | ,<br>I    | 10                   | ••• 0F |

| A       | 0B          | t t       | 1A                   | ••• 0F |

| В       | 0B          | 1         | 1B                   | ••• 0F |

| C       | 07          | 1         | 1C                   | ••• 0F |

| D       | 07          | 1         | 10                   | ••• 0F |

| Ε       | 07          | 1         | 15 •••••<br>1E ••••• | ••• OF |

| E       | 07          | 1         |                      | ••• OF |

| £ ••••• | •••• 0/<br> |           | 1F                   | ••• VF |

Table 2-4 8K X 8 EPROMS

## 2.9 PAL EQUATIONS

Uncommitted logic space in the chips is configured as per the following equations: PAL10L8 PAL DESIGN SPECIFICTION P/N 318-021-001 CONTROL SIGNAL GENERATOR - POSTITON G2, S150 MMU CPU BOARD

SYSIO PA8 PA9 PA10 /PA0;/MWTC /MRDC /BHEN /CBUSY GND SEL UHALF ERRSEL FLGSEL IOXACK LBYTE SWBYTE HBYTE LHALF VCC

LHALF = /PAO +BHEN

UHALF = PAO +BHEN

.

LBYTE = SEL\*BHEN +SEL\*/PAO

SWBYTE = SEL\*/BHEN\*PAO

2-31

CPU BOARD PAL EQUATIONS

- HBYTE = SEL\*BHEN

- IOXACK = SYSIO\*MRDC\*CBUSY +SYSIO\*MWTC\*CBUSY

- ERRSEL = SYSIO\*MRDC\*PA10\*/PA9\*PA8\*/PA0

- FLGSEL = SYSIO\*MWTC\*CBUSY\*PA10\*/PA9\*/PA8\*/PA0

## DESCRIPTION:

This chip generates the byte control lines for the onboard I/0 which includes the ROM, the flag register, the error register, and the mape registers.

PAL12H6 PAL DESIGN SPECIFICATION P/N 318-022-001 ERROR AND VAS GENERATOR - POSTITON B4, S150 MMU CPU BOARD

NRS NVS SWP /AS RW FC2 /MAPPED MAPFLG PIN9 GND PIN11 PIN12 PIN13 AV WV SNV SNR VADD USP VCC

- VADD = MAPPED\*/NRS\*/NVS\*RW\*AS +MAPPED\*/NRS\*/NVS\*/SWP\*AS +FC2\*/MAPFLG\*AS +FC2\*AS\*/USP

- AV = /FC2\*/USP

- SNV = NVS\*MAPPED

- WV = SWP\*/RW\*MAPPED

- SNR = NRS\*MAPPED

#### DESCRIPTION:

This PAL generates the Valid Address Strobe and the error flags.

## CHAPTER 3

## I/O BOARD

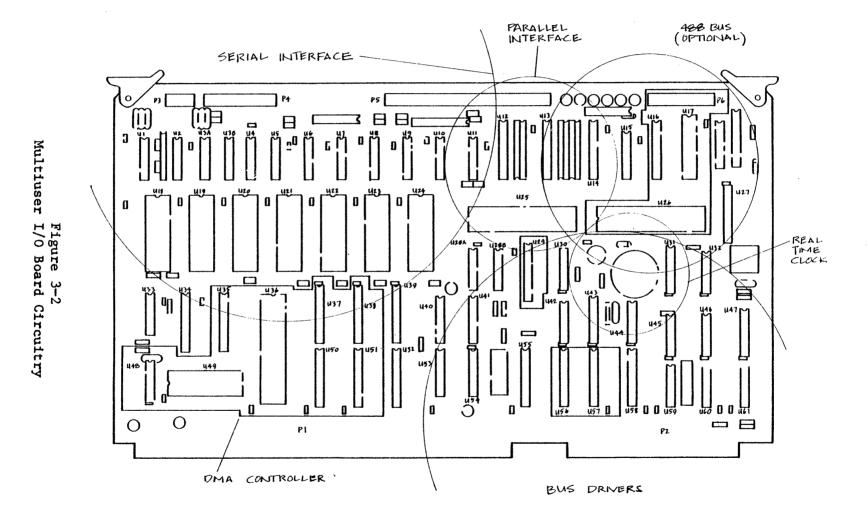

## 3.1 INTRODUCTION

This chapter deals with the physical and logical aspects of the I/0 board. Some of the items discussed are: I/0 board configuration, the serial interface, the parallel port, etc.

## 3.2 DEFINITION AND FEATURES