## XEBEC 432 LAKESIDE DRIVE SUNNYVALE, CALIFORNIA 94086 (408) 733-4200

## S1410A 5.25 INCH WINCHESTER DISK CONTROLLER

OWNER'S MANUAL

DOCUMENT #104478

REVISION B FEBRUARY, 1984

© XEBEC SYSTEMS, INCORPORATED 1984

DOCUMENT CONTROL

## PREFACE

This manual contains technical information on the S1410A 5.25 Inch Winchester Disk Controller. New features have been added to the S1410A over the original S1410. The following is a list of additions:

- 1. Write Precompensation is selectable at 0, 5, and 10 nanosecs. See Section 4.5.3.13 (Initialize Drive Characteristics).

- 2. Drives that have Imbedded Servo at index now operate on the S1410A. See Sections 4.5.1 (Control Byte) and 4.5.3.5 (Format Drive).

- 3. All non-buffered step options have been removed except the 3.0 millisec. See Section 4.5.1 (Control Byte).

- 4. Drives that have more than 8 heads and use the Reduced Write Current signal as head select 23 now operate on the S1410A. See Section 4.1.4.3 (Head Select Signals).

- 5. Two new commands have been added: Read Verify (Section 4.5.3.10) and Retry Statistics (Section 4.5.3.25).

- 6. During disk read operations, the S1410A operates different from the S1410 when reporting corectable errors (type 1, error code 8) to the host. See Sections 4.5.3.9 (Read) and 4.5.3.10 (Read Verify).

- 7. The sector format for the 256 byte sector size of the S1410A is not compatable with the S1410. See Section 4.6 (Sector Format).

- 8. The S1410A contains four new mounting holes, in addition to the four mounting holes on the original S1410. See Section 2.3 (Physical Requirements).

- 9. A Right Angle Power Connector (P1) is used on the S1410A. (The mating connectors and pins as used for the S1410 remain the same.)

- Hardware has been added to provide for extra signals for the removeable cartridge Winchester Drives. (Firmware options will be available at a later date).

## CONTENTS

## INTRODUCTION

|                          |                                           |                                                                                                                                                                                                                                             | Page                                                                             |

|--------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1.2                      | 1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5 | IPTION TONAL ORGANIZATION Host Interface Processor State Machine                                                                                                                                                                            | 1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                              |

|                          |                                           | SPECIFICATIONS                                                                                                                                                                                                                              |                                                                                  |

| 2.2<br>2.3<br>2.4<br>2.5 | ENVIRO                                    | RICAL<br>CAL SPECIFICATIONS<br>DNMENTAL REQUIREMENTS                                                                                                                                                                                        | 5<br>5<br>5<br>6<br>6<br>8                                                       |

|                          |                                           | BOARD SET-UP                                                                                                                                                                                                                                |                                                                                  |

| 3.2<br>3.3<br>3.4<br>3.5 | CONNE                                     |                                                                                                                                                                                                                                             | 12<br>12<br>12<br>13<br>13                                                       |

|                          |                                           | THEORY OF OPERATION                                                                                                                                                                                                                         |                                                                                  |

| 4.1                      |                                           | SASI Conventions SASI Names and Abbreviations SASI Signal Definitions Drive Control Signals Reduced Write Current Write Select Gate Head Select Signals Step Direction In Drive Select 0, Drive Select 1 Drive Output Signals Seek Complete | 17<br>17<br>17<br>18<br>24<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>27<br>27 |

## **CONTENTS (CONTINUED)**

## THEORY OF OPERATION (CONTINUED)

|     | 4.1.5.5        | Ready                                                 | 27               |

|-----|----------------|-------------------------------------------------------|------------------|

|     | 4.1.5.6        | Select Status                                         | 28               |

|     | 4.1.6          | Drive Data Transfer Signals                           | 28               |

|     | 4.1.6.1        | MFM Write Data                                        | 28               |

|     | 4.1.6.2        | MFM Read Data                                         | 28               |

| 4.2 | BASIC O        | PERATING CONFIGURATION                                | 29               |

| 4.3 |                | ED DESCRIPTION                                        | 29               |

|     | 4.3.1          | Controller Selection                                  | 29               |

|     | 4.3.2          | Command Mode                                          | 32               |

|     | 4.3.3          | Data Transfer                                         | 32               |

|     | 4.3.3.1        | Data Transfer to Host                                 | 32               |

|     | 4.3.3.2        | Data Transfer From Host                               | 33               |

|     |                |                                                       | 33               |

| 4.4 | PROGR <i>A</i> | AMMING INFORMATION                                    | 36               |

| 4.5 | COMMA          | NDS                                                   | 36               |

|     | 4.5.1          | Control Byte                                          | 37               |

|     | 4.5.2          | Logical Address (High, Middle, and Low)               | 39               |

|     | 4.5.3          |                                                       | 39               |

|     | 4.5.3.1        | Test Drive Ready (Class 0, Opcode 00)                 | 39               |

|     | 4.5.3.2        |                                                       | 41               |

|     | 4.5.3.3        |                                                       | 41               |

|     | 4.5.3.4        |                                                       | 41               |

|     | 4.5.3.5        |                                                       | 51               |

|     | 4.5.3.6        |                                                       | 53               |

|     |                | Format Track (Class 0, Opcode 06)                     | 55               |

|     |                | Format Bad Track (Class 0, Opcode 07)                 | 56               |

|     |                | Read (Class 0, Opcode 08)                             | 57<br>50         |

|     |                | Read Verify (Class 0, Opcode 09)                      | 58<br>50         |

|     |                | Write (Class 0, Opcode 0A)                            | 59               |

|     |                | Seek (Class 0, Opcode 0B)                             | 60               |

|     | 4.5.3.13       | Initialize Drive Characteristics (Class 0, Opcode 0C) | 61               |

|     | 4.5.3.14       | Read ECC Burst Error Length (Class 0, Opcode 0D)      | 64               |

|     |                | Format Alternate Track (Class 0, Opcode 0E)           | 6 <i>5</i><br>67 |

|     | 4.5.3.16       | Write Sector Buffer (Class 0, Opcode 0F)              | 68               |

|     |                | Read Sector Buffer (Class 0, Opcode 10)               | 69               |

|     |                | RAM Diagnostic (Class 7, Opcode 00)                   | 69               |

|     |                | Reserved (Class 7, Opcode 01)                         | 69               |

|     |                | Reserved (Class 7, Opcode 02)                         | 69               |

|     | 4.5.3.21       | Drive Diagnostic (Class 7, Opcode 03)                 | 71               |

|     |                | Controller Internal Diagnostic (Class 7, Opcode 04)   | 71               |

|     |                | Read Long (Class 7, Opcode 05)                        | 73               |

|     |                | Write Long (Class 7, Opcode 06)                       | 73               |

|     | 4.5.3.25       | Retry Statistics (Class 7, Opcode 07)                 | / 3              |

## CONTENTS (CONTINUED)

## THEORY OF OPERATION (CONTINUED)

| 4.6  | SECTOR FORMAT                                      | 75  |

|------|----------------------------------------------------|-----|

| 4.7  | EXECUTION OF DIAGNOSTICS                           | 80  |

| 4.8  | ERROR CORRECTION PHILOSPHY                         | 81  |

| 4.9  | ALTERNATE TRACK ASSIGNMENT AND HANDLING            | 82  |

| 4.10 | OVERLAPPING SEEKS WITH BUFFER STEP DRIVES          | 84  |

| 4.11 | SECTOR INTERLEAVING                                | 85  |

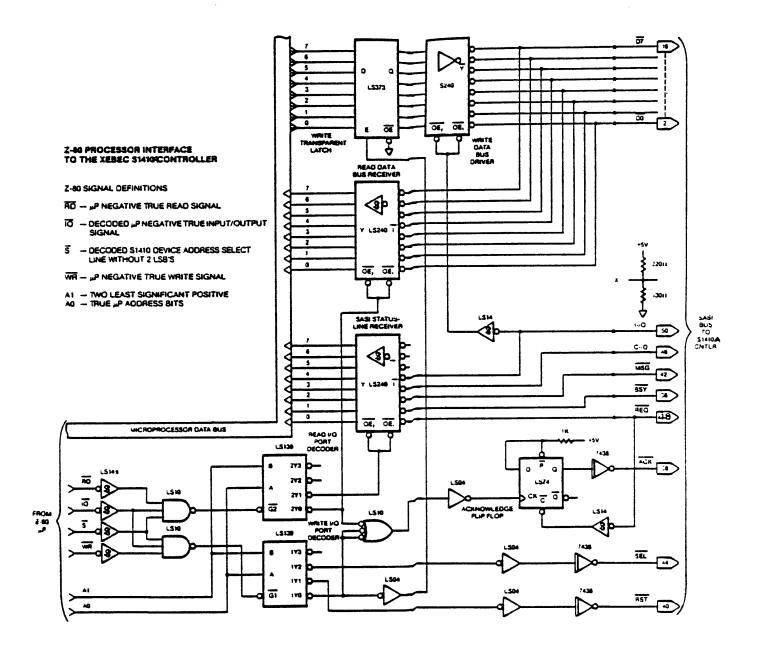

|      | APPENDIX A                                         | 87  |

|      | SAMPLE HARDWARE INTERFACE AND PROGRAMMING EXAMPLES | FOF |

|      | A Z-80 BASED MICROPROCESSOR TO INTERFACE TO THE    |     |

|      | XEBEC S1410A CONTROLLER                            |     |

|      | APPENDIX B                                         | 96  |

|      | S1410A FIRMWARE OPTIONS                            |     |

## LIST OF FIGURES

| <b>Figure</b> | Page | <u>Description</u>                                               |

|---------------|------|------------------------------------------------------------------|

| 1-1           | 3    | Picture of S1410A Disk Controller.                               |

| 1-2           | 4    | S1410A Controller functional organization.                       |

| 2-1           | 7    | Controller board dimensions.                                     |

| 3-1           | 14   | Connector and jumper locations.                                  |

| 3-2           | 15   | Operating setups.                                                |

| 4-1           | 30   | Basic operating configuration.                                   |

| 4-2           | 31   | Controller select timing.                                        |

| 4-3           | 34   | Data transfer to host, timing.                                   |

| 4_4           | 35   | Data transfer from host to controller, timing.                   |

| 4-5           | 36   | Device control block (DCB), format.                              |

| 4-6           | 37   | Completion Status Bytes.                                         |

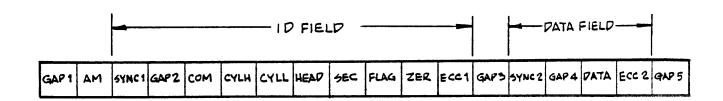

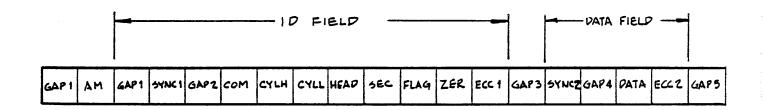

| 4-7           | 78   | Sector format for 256 byte sectors.                              |

| 4-8           | 79   | Sector format for 512 byte sectors.                              |

| 4-9           | 86   | <ul> <li>Track format example of 32 sectors-per-track</li> </ul> |

|               |      | with an interleave factor of 5.                                  |

## LIST OF TABLES

| <u>Table</u> | Page | Description                                           |

|--------------|------|-------------------------------------------------------|

| 2-1          | 5    | . Controller electrical requirements.                 |

| 2-2          | 6    | . Controller board specifications.                    |

| 2-3          | 6    | • Environmental limits•                               |

| 2-4          | 6    | · Controller mating connectors·                       |

| 2-5          | 8    | . Connector J1, control signals, pin assignments.     |

| 2-6          | 9    | . Connector J2 and J3 data signal pin assignments.    |

| 2-7          | 10   | . Connector P2 host interface pin assignments.        |

| 2-8          | 11   | . Connector P1, power supply, pin assignments.        |

| 3-1          | 12   | . Jumper locations.                                   |

| 4-1          | 18   | . Host bus status signals.                            |

| 4-2          | 20   | . Summary of host bus status signals.                 |

| 4-3          | 21   | . Controller-host adapter handshaking.                |

| 4-4          | 22   | . Host bus control signals.                           |

| 4-5          | 23   | . Host bus data signals.                              |

| 4-6          | 44   | . Type 0 error codes, disk drive.                     |

| 4-7          | 46   | . Type 1 error codes, controller.                     |

| 4-8          | 49   | . Type 2 and 3 error codes command and miscellaneous. |

| 4-9          | 76   | . Sector field description for 256 byte sectors.      |

| 4-10         | 77   | • Sector field description for 512 byte sectors•      |

## CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

The Xebec S1410A Disk Controller can control the operation of up to two 5%-inch Winchester disk drives that have the industry standard Seagate interface, including those drives with index servo area. This means that the S1410A Controller can operate with a large and growing class of 5%-inch Winchester disk drives.

#### 1.2 DESCRIPTION

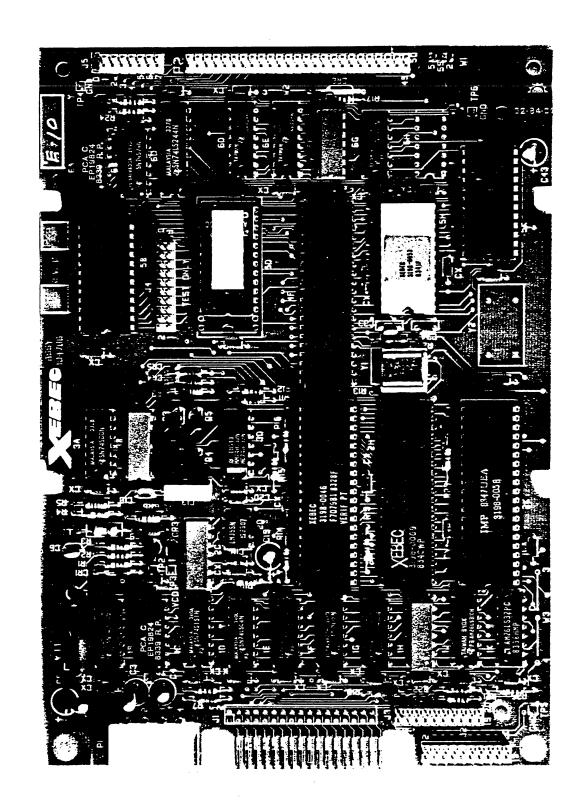

The S1410A Controller, shown in Figure 1-1, is packaged on a compact printed circuit board whose dimensions are 5-3/4 by 8 inches. The board with this popular form factor mounts easily on many 5%-inch drives. If not mounted directly on the drive, the controller takes up very little space in a typical drive enclosure. Because the controller uses the Shugart Associates System Interface (SASI), it does not require special or complex design considerations in order to communicate with popular host buses. The following list highlights the operating and design features of the controller.

- Interlocked data transfer through the Shugart Associates System Interface (SASI).

- Microprocessor-based architecture (patent pending).

- Full-sector buffer, (256 or 512 bytes).

- Hardware 32-bit ECC polynomial with 11-bit burst correction.

- Field-proven data separator.

- Defacto Industry Standard (ST-506/412) disk interface.

- Automatic retries during disk access.

- Internal Diagnostics.

- Automatic burst error detection and correction.

- Separate sector format for ID and data fields with individual ECC fields for both the ID and data fields.

- High level command set.

- Variable Interleave.

#### 1.3 FUNCTIONAL ORGANIZATION

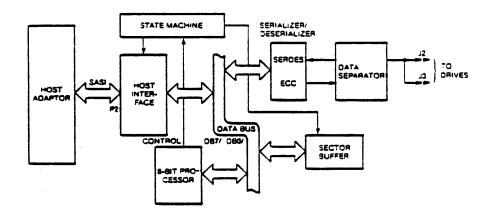

The simplified block diagram in Figure 1-2 shows the functional organization of the Controller. Only the major areas are shown.

#### 1.3.1 Host Interface

The host interface connects the internal data bus to the host adapter; the state machine controls the movement of data and commands through the host interface.

#### 1.3.2 Processor

The eight-bit processor is the intelligence of the controller; it monitors and controls the operation of the controller.

#### 1.3.3 State Machine

The state machine controls and synchronizes the operation of the host adapter, SERDES, and sector buffer.

#### **1.3.4 SERDES**

The serializer/deserializer (SERDES) converts parallel data from the internal data bus to serial data for transfer to a selected disk drive. It converts serial data from the selected disk drive to parallel data which it places on the internal data bus.

#### 1.3.5 Data Separator

The data separator converts serial NRZ data to MFM for transfer to the selected disk drive. It converts MFM data coming from the selected disk drive to serial NRZ data for the SERDES.

#### 1.3.6 Sector Buffer

The sector buffer stages data transfers between the disk and the host to prevent data overruns.

FIGURE 1-1 S1410A DISK CONTROLLER

FIGURE 1-2 S1410A CONTROLLER, FUNCTIONAL ORGANIZATION

# CHAPTER 2 SPECIFICATIONS

#### 2.1 GENERAL

This chapter contains the overall specifications for the Controller. These specifications are meant to guide the user in placing the controller into operation. Some of the specifications indicate limits; the user must adhere to these in order to operate the controller successfully.

#### 2.2 ELECTRICAL

Table 2-1 lists the electrical requirements of the controller.

## TABLE 2-1 CONTROLLER ELECTRICAL REQUIREMENTS

NOTE: All measurements are made on the controller printed circuit board at the power connector P1.

| Voltage   | Range            |     | <u>urrent</u> |

|-----------|------------------|-----|---------------|

| +5.0 Vdc  | 4.75 to 5.25 Vdc | 1.3 | Amp. Max.     |

|           |                  | 1.0 | Amp. Typ.     |

| +12.0 Vdc | 10.8 to 13.2 Vdc | 6.0 | ma. Max.      |

|           |                  | 3.0 | ma. Typ.      |

NOTE: The maximum conducted power supply ripple must not exceed 200 mv peak to peak from 0.1 to 25 mHz.

## 2.3 PHYSICAL SPECIFICATIONS

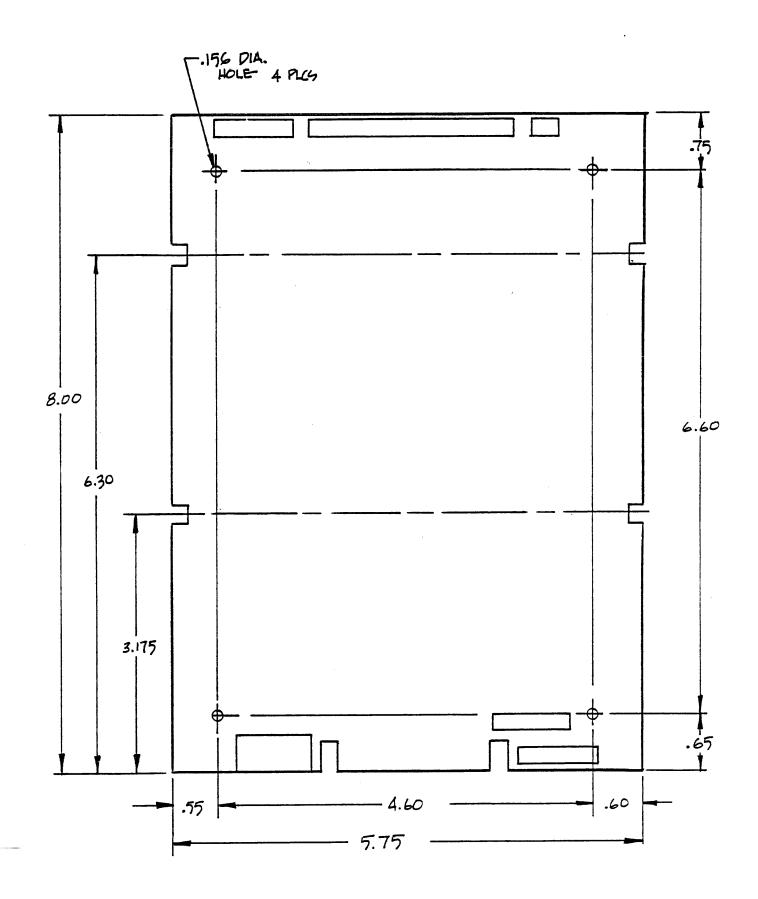

Table 2-2 lists the specifications of the controller board and Figure 2-1 illustrates the dimensions of the board.

TABLE 2-2 CONTROLLER BOARD SPECIFICATIONS

| <u>Item</u>                  | Measurement        |

|------------------------------|--------------------|

| Width (W)                    | <b>5.75</b> inches |

| Length (L)                   | 8.00 inches        |

| Height (H)                   | .75 inches         |

| (Board thickness, components |                    |

| and lead protrusion)         |                    |

| Weight                       | 7.5 ounces         |

## 2.4 ENVIRONMENTAL REQUIREMENTS

The controller will operate under the environmental conditions listed in Table 2-3. The controller does not normally require fans in standard operating environments where airflow is not restricted.

**TABLE 2-3 ENVIRONMENTAL LIMITS**

| <u>Item</u>       | <u>Measurement</u>              |

|-------------------|---------------------------------|

| Temperature       | 0 to 50 degrees Celsius         |

| Relative Humidity | 10 to 95 percent non-condensing |

| Altitude          | Sea level to 10,000 feet        |

#### 2.5 CONNECTORS

Table 2-4 lists the Controller mating connectors.

TABLE 2-4 CONTROLLER MATING CONNECTORS

| Designation | <u>Function</u>          | Type/Source (or equivalent) |

|-------------|--------------------------|-----------------------------|

| J1          | Drive control signals    | 3M 3463-0001                |

| J2, J3      | Drive data signals       | 3M 3421-7000                |

| J4          | Test connector           | Not applicable              |

| J5          | Controller select number | Not applicable              |

| P1          | Power supply             | AMP 1-480424-0 (housing)    |

|             |                          | AMP 350078-4 (pins)         |

| P2          | Host interface           | 3M 3425-7000                |

NOTE: The user must not connect a cable to connector J4 or J5.

FIGURE 2-1 CONTROLLER BOARD DIMENSIONS

#### 2.6 CONNECTOR PIN ASSIGNMENTS

Tables 2-5 through 2-8 list the pin assignments of the connectors on the controller board. The tables identify the signals on the pins. The connector P2 signals are defined in Chapter 4, Theory of Operation.

TABLE 2-5

CONNECTOR J1, CONTROL SIGNALS, PIN ASSIGNMENTS

| Signal Pin | Ground Return | Signal Name                                   |

|------------|---------------|-----------------------------------------------|

| 2          | 1             | Reduced Write Current/                        |

|            |               | Head Select 2 <sup>3</sup> /-Change Cartridge |

| 4          | 3             | Head Select 2 <sup>2</sup>                    |

| 6          | 5             | Write Select Gate                             |

| 8          | 7             | Seek Complete                                 |

| 10         | 9             | Track 00                                      |

| 12         | 11            | Write Fault                                   |

| 14         | 13            | Head Select 20                                |

| 16         | 15            | Spare / -Sector                               |

| 18         | 17            | Head Select 2 <sup>1</sup>                    |

| 20         | 19            | Index                                         |

| 22         | 21            | Ready                                         |

| 24         | 23            | Step                                          |

| 26         | 25            | Drive Select 1                                |

| 28         | 27            | Drive Select 2                                |

| 30         | 29            | Reserved                                      |

| 32         | 31            | Reserved                                      |

| 34         | 33            | Direction In                                  |

TABLE 2-6

CONNECTORS J2 and J3, SIGNALS, PIN ASSIGNMENTS

| Signal Pin | Ground Return | Signal Name                |

|------------|---------------|----------------------------|

| 1          | 2             | Drive Selected             |

| 3          | 4             | Spare / -Recalibrate       |

| 5          | . 6           | Spare / -Write protected   |

| 7          | 8             | Reserved                   |

| 9          | 10            | Spare / -Cartridge Changed |

| 11         | 12            | Ground (GND)               |

| 13         |               | MFM Write Data+            |

| 14         |               | MFM Write Data-            |

| 15         | 16            | Ground (GND)               |

| 17         |               | MFM Read Data+             |

| 18         |               | MFM Read Data-             |

| 20         | 19            | Ground (GND)               |

TABLE 2-7

CONNECTOR P2, HOST INTERFACE, PIN ASSIGNMENTS

| Signal Pin | Ground Return | Signal Name |

|------------|---------------|-------------|

| 2          | 1             | DATA0-      |

| 4          | 3             | DATAI-      |

| 6          | 5             | DATA2-      |

| 8          | 7             | DATA3-      |

| 10         | 9             | DATA4-      |

| 12         | 11            | DATA5-      |

| 14         | 13            | DATA6-      |

| 16         | 15            | DATA7-      |

| 18         | 17            | Spare       |

| 20         | 19            | Spare       |

| 22         | 21            | Spare       |

| 24         | 23            | Spare       |

| 26         | 25            | Reserved    |

| 28         | 27            | Spare       |

| 30         | 29            | Spare       |

| 32         | 31            | Spare       |

| 34         | 33            | Spare       |

| 36         | 35            | BUSY-       |

| 38         | 37            | ACK-        |

| 40         | 39            | RST-        |

| 42         | 41            | MSG-        |

| 44         | 43            | SEL-        |

| 46         | 45            | C-/D        |

| 48         | 47            | REQ-        |

| 50         | 49            | I-/0        |

|            |               |             |

TABLE 2-8

CONNECTOR P1, POWER SUPPLY, PIN ASSIGNMENTS

| Pin Number | <u>Voltage</u> |  |

|------------|----------------|--|

| 1          | +12 Vdc        |  |

| 2          | Ground return  |  |

| 3          | Ground return  |  |

| 4          | +5 Vdc         |  |

# CHAPTER 3 BOARD SETUP

#### 3.1 GENERAL

This chapter contains the information for setting up and installing the controller before placing it in operation. These preparatory steps require the proper placement of jumpers, mounting the controller in its operating environment, and properly connecting the cables. In addition, the user has the option of using more than one controller with the host adapter in his system. Instructions for connecting multiple controllers appear later in the chapter.

#### 3.2 BOARD SETUP

Setting up the Controller for operation requires checking that the factory-installed jumpers are according the listing in Table 3-1. Figure 3-1 shows the locations of the jumpers on the Controller.

#### TABLE 3-1 JUMPER LOCATIONS

| Designation | <u>Function</u>     | Connection and Result    |

|-------------|---------------------|--------------------------|

| <b>W</b> 1  | Selects sector size | SS to 2: 256-byte sector |

|             |                     | 32 Sectors/Track         |

|             |                     | SS to 5: 512-byte sector |

|             |                     | 17 Sectors/Track         |

#### 3.3 MOUNTING CONTROLLER

The controller board has eight mounting locations. The four mounting holes match those of the original S1410, while the four sloted mounting locations allow for easy mounting on the drive. The controller should be mounted to receive convection air flow.

#### 3.4 CONNECTING CABLES

Before the controller can be placed in operation, the cables to the drive and host must be connected. These cables are listed below:

- J1 Control Cable (controller to last drive): maximum 20 feet

- J2 Data Cable: maximum 20 feet

- J3 Data Cable: maximum 20 feet (optional second drive)

- Pl Power Cable

- P2 Host Interface Cable: maximum 15 feet

NOTE: Do not attempt to connect a cable to connector J4 or J5. Connector J4 is for factory test only. Connector J5 sets the controller SASI address.

Figure 3-1 shows the connector locations.

#### 3.5 MULTIPLE CONTROLLERS

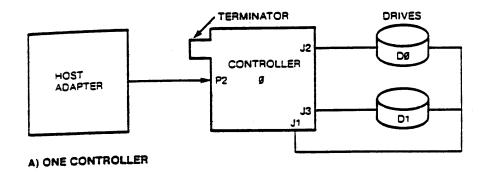

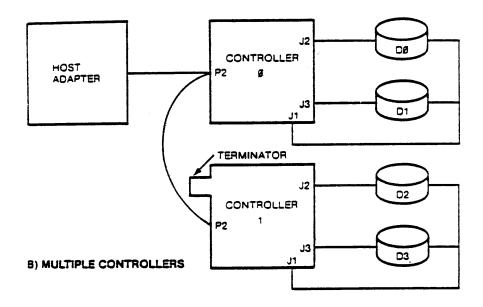

A separate Controller is required for each additional pair of drives. Figure 3-2 shows two operating setups; (A) using one Controller and (B) using two Controllers. Notice the terminator (resistor pack) in both drawings. The terminator is at position 6F on the board. When multiple Controllers are used, the terminator must be installed only in the last board in the daisy chain.

FIGURE 3-2 OPERATING SETUPS

#### 3.6 ADDRESS JUMPER GROUP

The Controller supports one of eight unique device addresses. When more than one controller is used in a system, the address jumper on the controller must be changed. Figure 3-1 shows the address jumper group (J5) located next to the connector P2. It also shows that terminal (pad) 0 is connected. This is the factory-installed jumper, and it sets the controller's address to 0.

In order to change this address, the factory-installed jumper must be removed from postion zero and connected between terminals at a different selected address. The position of this jumper corresponds to the bit position on the SASI bus that must be set, when the select strobe is issued, to select this controller. Each controller attached to a SASI bus must use a dfferent SASI address.

# CHAPTER 4 THEORY OF OPERATION

#### 4.1 GENERAL

This chapter discusses the theory of operation of the S1410A Controller and lays down the guidelines that will enable the user to use the controller successfully.

### 4.1.1 SASI Conventions

Signals or lines can be active in either a high or low state. The terms signal, signal lines, and lines mean the same thing. A low state is equivalent to a voltage level of 0.8 volts or less, and a high state is equivalent to a voltage level of 2.4 volts or more. Some texts use the term 'asserted' to mean active. In this manual, only the term active is used; if the term 'asserted' appears, it is only for reference.

### 4.1.2 SASI Names and Abbreviations

A dash (-), or the lack of one, indicates the active state of a signal. The active state of a signal is that state which is required for a given operation. When a dash is appended to end of a signal name, the signal is active when it is low. When no dash appears at the end of a signal name, the signal is active when it is high. Some signal lines have two so-called active (or significant) states. When the level on the line is high, a particular operation takes place. When the level on the line is low, a different operation takes place. The following examples show the use of these conventions.

- BUSY- The signal BUSY- is active when it is at a low level because it has the dash appended.

- BUSY The signal BUSY is active at a high level because it does not have the dash appended.

C-/D The line C-/D (command-/data) has a dual purpose. The dash after the C indicates that when this line is at a low level, command mode is indicted and when it is at a high level, data mode is indicated.

Other designations used to define signal lines are listed below.

Drv Driver

Rcvr Receiver

OC Open collector

Tri-State Line has three states: high, low, high impedance

220/330 Line termination: 220 Ohms to source voltage/330

Ohms to ground.

## 4.1.3 SASI Signal Definitions

The following tables list and define the signals that appear on the SASI Bus lines between the host adapter and the controller.

#### TABLE 4-1 HOST BUS STATUS SIGNALS

| NAME | DRV/RCVR | DEFINITION                                 |

|------|----------|--------------------------------------------|

| I-/O | Drv OC   | Input-/Output: The controller drives this  |

|      |          | line. A low level on this line indicates   |

|      |          | that the controller is driving the data in |

|      |          | on the host bus. A high level on this line |

|      |          | indicates that the host adapter is driving |

|      |          | the data out on the host bus. The host     |

|      |          | adapter monitors this line and uses it to  |

|      |          | enable and disable its data bus drivers.   |

|      |          | This signal is qualified by signal REQ     |

## TABLE 4-1 HOST BUS STATUS SIGNALS (Continued)

| C-/D  | Drv OC | Command-/Data: This signal line indicates whether the information on the data bus consists of command or data bytes. A low means command bytes; a high means data bytes. This signal is qualified by signal REQ                                                                       |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSY- | Drv OC | Busy: The controller generates this active low signal in response to the SEL-signal and the address bit (DB0- to DB7-) from the host adapter. The busy signal informs the host adapter the controller is present and ready to conduct transactions on the host bus.                   |

| MSG-  | Drv OC | Message: The controller sends this active low signal to the host adapter to indicate that the current command has been completed. When MSG- is active, the I-/O signal line is always low so that the controller can drive the bus data lines. This signal is qualified by signal REQ |

## TABLE 4-2 SUMMARY OF HOST BUS STATUS SIGNALS

| <u>I-/0</u> | <u>C-/D</u> | MSG- | DEFINITION                                                                 |

|-------------|-------------|------|----------------------------------------------------------------------------|

| High        | Low         | High | The controller receives command bytes from the host                        |

|             |             |      | adapter (All Commands).                                                    |

| High        | High        | High | The controller receives data bytes from the host adapter.                  |

|             |             |      | Write Data                                                                 |

|             |             |      | Drive initialize Data                                                      |

|             |             |      | Write Buffer Data                                                          |

|             |             |      | Format Alternate Track Data                                                |

|             |             |      | Write Long Data                                                            |

| Low         | High        | High | The controller sends data bytes to the host adapter.                       |

|             |             |      | Read Data                                                                  |

|             |             |      | Request Sense Data                                                         |

|             |             |      | Read ECC Burst Error Data                                                  |

|             |             |      | Read Sector Buffer Data                                                    |

|             |             |      | Read Long Data                                                             |

|             |             |      | Retry Statistics Data                                                      |

| Low         | Low         | High | The controller sends error status byte to the host adapter                 |

|             |             | _    | (All Commands).                                                            |

| Low         | Low         | Low  | The controller sends message byte to host which informs                    |

|             |             |      | the host adapter that it has completed the current command (All Commands). |

|             |             |      |                                                                            |

TABLE 4-3 CONTROLLER-HOST ADAPTER HANDSHAKING

| <u>NAME</u> | <u>DRV/RCVR</u> | DEFINITION                                |

|-------------|-----------------|-------------------------------------------|

| REQ-        | Drv OC          | Request: The controller sends this        |

|             |                 | active low signal to the host adapter for |

|             |                 | each byte transferred across the          |

|             |                 | interface. This signal qualifies signals  |

|             |                 | I-/O, C-/D and MSG                        |

| ACK-        | Rcvr, 220/330   | Acknowledge: The host adapter             |

|             |                 | generates this active low signal in       |

|             |                 | response to the REQ- signal from the      |

|             |                 | controller when the host is ready to      |

|             |                 | receive or transmit a byte of data. In    |

|             |                 | order to complete the handshake, the      |

|             |                 | host adapter must send an acknowledge     |

|             |                 | (ACK-) in response to each request        |

| 4           |                 | (REQ-) from the controller.               |

#### TABLE 4-4 HOST BUS CONTROL SIGNALS

NAME DRV/RCVR

RST- Rcvr, 220/330

DEFINITION

Reset: The host adapter sends this active low signal to the controller to force the controller to the idle state. After RST- has become active, any controller status is cleared. RST- also causes the deactivation of all signals to the drives. Select should not be issued for 20 microseconds after a reset pulse. The time requirements for the RST-signal are as follows:

Minimum

Maximum

100 nsec.

None

SEL- Rcvr, 220/330

Select: The host adapter sends this active low signal to the controller to initiate a command transaction. BUSYmust be in the inactive state at the beginning of the select process. Along with SEL-, the host adapter must also send an address bit to select the controller (DB0- for controller 0). The data bus must be stable 100 nsec before SEL- is active, and remain stable for 100 SELnsec after is deactivated. Minimum select pulse width is 100 nsec, there is no maximum, as long as the data bus remains stable during select. SELshould not be issued for 25 microseconds after a reset.

## TABLE 4-5 HOST BUS DATA SIGNAL

NAME

DB7- to DB0-

DRV/RCVR

Tri-State, 220/330

DEFINITION

These are the eight data bits (lines) of the host bus (DB0 = LSB).

Each line is also used as address bits to select a controller in systems using multiple controllers (see Chapter 3). The normal connection is to DBO- which is the address of controller 0. Any other connection requires moving the jumper connection at J5.

The following list shows the bit assignments.

| DB0- | Controller 0 |

|------|--------------|

| DB1- | Controller 1 |

| DB2- | Controller 2 |

| DB3- | Controller 3 |

| DB4- | Controller 4 |

| DB5- | Controller 5 |

| DB6- | Controller 6 |

| DB7- | Controller 7 |

## 4.1.4 Drive Control Input Signals

The control input signals are of two kinds: those to be multiplexed in a multiple drive system and those that do the multiplexing. The control input signals to be multiplexed are: Reduced Write Current, Write Gate, Head Select Line 0, Head Select Line 1, Head Select Line 2, Step, and Direction. The signal to do the multiplexing is Drive Select 0 and Drive Select 1.

The input lines have the following electrical specifications as measured at the drive.

True: 0.0 volt D.C. to 0.4 volt D.C. @I=40 milliamperes, maximum

False: 2.5 volts D.C. to 5.25 volts D.C. @IL=250 microamperes, maximum

All input lines share a 220/330 ohm resistor pack for line termination. Only the last drive in the chain should have the resistor pack installed.

NOTE: Refer to drive specifications for detailed information of these line.

#### 4.1.4.1 Reduced Write Current

When active, this line, together with Write Gate, causes the write circuitry to write on the disk with a lower write current. This line is set active at the cylinder specified in the initialize command.

#### 4.1.4.2 Write Select Gate

The active state of this signal or logical zero level enables write data to be written on the disk. The inactive state of this signal enables the data to be transferred from the drive. In addition, the inactive state enables the step pulse to step the read/write actuator. MFM write data is sent to the drive within 400 nsec after write is active.

## 4.1.4.3 Head Select Signals 2, 0, 12, 2, 3

These four lines provide for the selection of each read/write head in a binary coded sequence. Head Select Line 20 is the least significant line. When all Head Select Lines are false, Head 0 is selected. If drive initialize is for greater than 8 heads, reduce Write Current line is used as Head Select 2<sup>3</sup>.

## 4.1.4.4 Step

This interface line is a control signal that causes the read/write head to move with the direction of motion defined by the Direction In line.

The access motion is initiated at the logical true-to-logical false transition or the trailing edge of this signal pulse. Change in the Direction In line is made at least 5.0 microseconds before the leading edge of the step pulse.

The minimum pluse width is 5.0 microseconds.

#### 4.1.4.5 Direction In

This signal defines the direction of motion of the read/write head when the Step line is pulsed. An open circuit or logical false defines the direction as "out". If a pulse is applied to the Step line, the read/write heads move away from the center of the disk. If this line is logical true, the direction is defined as "in", and the read/write heads move in toward the center of the disk. The direction line is set a minimum of 5 nsec before step pulse are issued.

Seek Complete is verified to be true prior to changing directions and the application of additional step pulses.

#### 4.1.4.6 Drive Select 0, Drive Select 1

These control signals enable the selected drive's input receivers and output drivers. When logically false, the output drivers are open circuits or logically false and the input receivers do not acknowledge signals presented to them.

Drive addresses are assigned on the drive. Refer to Drive Manual for drive selection.

NOTE: Only one drive may be selected at a time.

#### 4.1.5 Drive Output Signals

The output control signals are driven with an open collector output stage capable of sinking a maximum of 40 milliamperes in a logical true state with a maximum voltage of 0.4 volt measured at the driver. When the line driver is in the logical false state, the driver transistor is off, and the collector cutoff is a maximum of 250 microamperes.

All output lines are enabled by the respective Drive Select lines.

#### 4.1.5.1 Seek Complete

This line goes true when the read/write heads have settled on the final track at the end of a seek. Reading or writing is not attempted when Seek Complete is false.

#### 4.1.5.2 Track 000

This interface signal indicates a true state only when the drive's read/write heads are positioned at Track 000, the outermost data track.

#### 4.1.5.3 Write Fault

This signal is used to indicate that a condition exists at the drive that could cause improper writing on the disk. When this line is true, further writing is inhibited. This line is edge detected, and cleared on the controller by deselection of the drive.

#### 4.1.5.4 Index

This interface signal is provided by the drive once each revolution (16.7 milliseconds nominal) to indicate the beginning of the track. Normally, this signal is logical false and makes the transition to logical true to indicate Index. This line is edge detected on the logical false to logical true transition. The minimum pulse width is 200 nsecs, with the maximum pluse width less than one revolution of the disk.

## 4.1.5.5 Ready

When true, this interface signal, together with Seek Complete, indicates that the drive is ready to read, write, or seek, and that the I/O signals are valid. When this line is false, all controller-initiated functions are inhibited.

#### 4.1.5.6 Select Status

A status line is provided at the J2,J3 connector to inform the controller of the selection status of the drive. This line is used to determine which port the drive data cable is connected.

#### 4.1.6 Drive Data Transfer Signals

Data lines associated with the transfer of data between the drive and the S1410A are differential in nature and may not be multiplexed. These lines are provided at the J3,J2 connector. Signal levels are defined by the RS-422A specification.

Two pairs of balanced lines are used for the transfer of data: MFM Write Data and MFM Read Data.

#### 4.1.6.1 MFM Write Data

This is a differential pair of lines that defines the flux transition to be written on the track. The transition of the +MFM Write Data line going more positive than the -MFM Write Data line causes a flux reversal on the track if the Write Gate is active. This signal is driven to an inactive state (+MFM Write Data more negative then -MFM Write Data) by the S1410A when in a read mode. Write Gate is inactive.

The delay from the leading edge of Write Gate to the Write Data pulse is 400 nanoseconds maximum.

#### 4.1.6.2 MFM Read Data

The data recovered by reading a prerecorded track is transmitted to the S1410A via the differential pair of MFM Read Data lines. The transition of the +MFM Read Data lines going more positive then the -MFM Read Data line represents a flux reversal on the track of the selected head. This line is edge detected, minimum active pulse width is 50 nsec, maximum active pulse width is 150 nsec.

#### 4.2 BASIC OPERATING CONFIGURATION

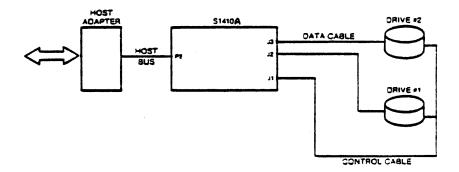

The basic operating configuration consists of a host adapter, S1410A Controller, and a Winchester disk drive with an industry standard Seagate interface. Figure 4-1 shows the basic setup. Also shown is an additional, optional drive; the controller can control a maximum of two drives.

The host can be one of a number of computer systems; the host adapter is an interface between the host's bus and the controller.

#### 4.3 DETAILED DESCRIPTION (HANDSHAKING AND TIMING)

The following paragraphs describe the interaction between the controller and the host adapter.

#### 4.3.1 Controller Selection

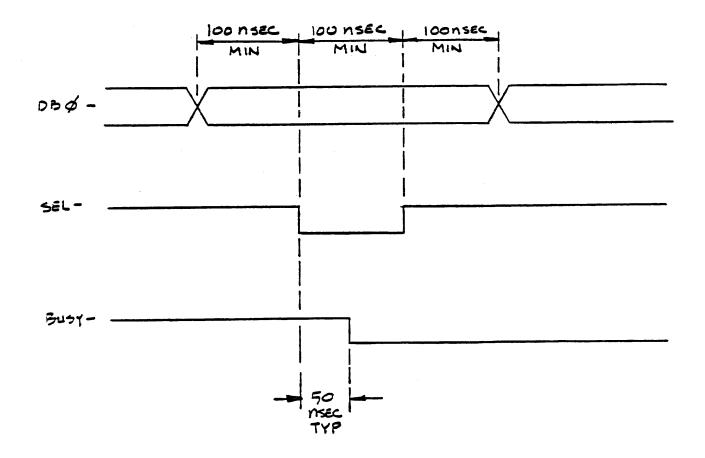

Before the host adapter can begin a transaction, it must select the controller. The host adapter selects the controller by activating the SEL- control signal and the address bit of the controller. Any bit, DBO- through DB7-, can be the address bit in a system with multiple controllers (all controllers leave the factory with DBO- connected to the controller's address logic). For this discussion, the controller's address is 0. Only one controller may be selected at a time. BUSY- must not be active at the start of the selection process.

The timing diagram in Figure 4-2 shows the basic timing requirements. Upon receiving both the SEL- signal and DBO-, the controller activates the BUSY-signal. As shown in the timing diagram, both SEL- and DBO- must be active (low) before the controller can activate the BUSY- signal. The data bus must be stable a minimum of 100 nanoseconds before SEL- is set, and held stable for 100 nanoseconds after SEL- is reset. Do not issue a select for at least 25 microseconds following a controller reset. During the selection process, the host has control of the data bus as signified by the deactivation of the I-/O line. Selection is complete when BUSY-becomes active. The controller then enters the command mode.

FIGURE 4-1 BASIC OPERATING CONFIGURATION

FIGURE 4-2 CONTROLLER SELECT TIMING

### 4.3.2 Command Mode

The controller receives commands from the host adapter using a handshaking sequence. The controller places a low level on the C-/D (command-/data) line to indicate that it wants a command from the host adapter and places a high level on the I-/O line to indicate that the movement of information is from the host adapter out to the controller. The MSG- line is high.

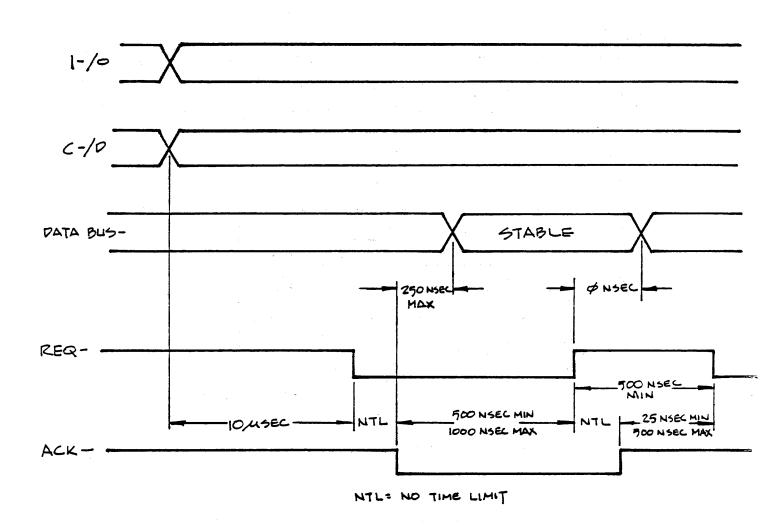

The controller activates the REQ- line within 20 microseconds after signals I-/O, C-/D and MSG- have been placed at high, low and high levels, respectively. The host adapter responds by activating the ACK- signal when a command byte is ready for the controller. The command byte placed on the data bus by the host must be stable within 250 nanoseconds after the ACK- signal is activated. The command byte must be held stable until REQ- is deactivated. The host deactivates ACK- after REQ- goes high. This completes the handshake for the first command byte. There are 6 command bytes, and each succeeding command byte from the host adapter requires the same complete handshake sequence. See Figure 4-4 and Section 4.3.3.2 for data bus, REQ, and ACK- timing. See Table 4-2 for I-/O, C-/D and MSG- definition.

#### 4.3.3 Data Transfer

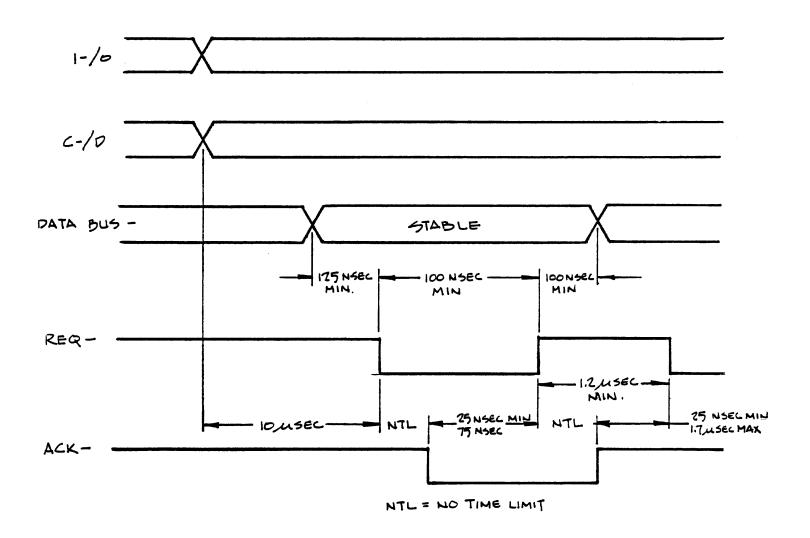

#### 4.3.3.1 Data Transfer to Host

On the transfer of data from the controller to the host, the data is stable on the bus a minimum of 125 nanoseconds before REQ- becomes active. There is no time limit from REQ- active to ACK- active. After the controller receives ACK-, REQ- will become inactive within 25 to 75 nanoseconds. If the controller has more data to send, it will set REQ- active within 1.2 to 1.7 microseconds from REQ- going inactive, if ACK- was set inactive within 1.2 microseconds of REQ- going inactive. The controller can not set REQ- active if ACK- is active. If the controller is ready to set REQ- active, but ACK- is

active, the controller waits for ACK- to go inactive, then sets REQ- active between 25 and 50 nanoseconds later. There is no time limit for the controller waiting for ACK-to go inactive. Refer to Figure 4.3 for timing detail.

#### 4.3.3.2 Data Transfer From Host

Each data byte transferred from host to the controller starts with the REQ- going active. For REQ- to go active, the host must ensure that ACK- is inactive at the beginning of each byte transfer sequence. After REQgoes active, the host sets ACK- active while placing a byte of data on the bus. There is no time limit from the time REQ- goes active to ACK- going active. However, there is a time limit of 250 nanoseconds maximum for the host to place the data byte on the bus referenced from the ACK- edge. When ACK- goes active, the controller sets REQ- inactive within 1000 nanoseconds maximum. The host must not change data on the bus until REQ- goes inactive. There is no hold time for the data when REQgoes inactive. There is no time limit for the host to set ACK- inactive. The controller will not set REQ- active again, for the next byte to transfer, until ACK- goes inactive. If ACK- goes inactive in response to REQ-going inactive, the controller will set REQ- active within 500 nanoseconds, ready to receive the next byte. controller is ready to set REQ- active, but ACK- is active, the controller waits for ACK- to go inactive, then sets REQ- between 25 and 50 nanoseconds later.

### 4.3.4 Status Bytes

Two bytes of status are passed to the host at the end of all commands. The first byte informs the host if any errors occurred during the execution of the command. The second is a zero byte. It signals to the host that the command is complete. Figure 4-3 shows the data bus, REQ- and ACK- timing. See Table 4-2 for I-/O, C-/D and MSG- definition. Figure 4-5a shows the format of these two bytes.

FIGURE 4-3 DATA TRANSFER TO HOST, TIMING

FIGURE 4-4 DATA TRANSFER FROM HOST TIMING

#### 4.4 PROGRAMMING INFORMATION

The following paragraphs discuss communications between the controller and host from the point of view of the command codes that are passed. The host sends commands to the controller through the host adapter. The controller then performs the commands and reports status back to the host.

#### 4.5 COMMANDS

The host sends a six-byte block to the controller to during command mode to specify the operation. This block is the Device Control Block (DCB). Figure 4-5 shows the composition of the DCB. The list that follows Figure 4-5 defines the byte that make up the DCB.

| /                                             | 6     | )                  | 4                                          | 3                                               | 4.                                                                      | 1                                                                                     | U                                                                                          |                                                                                                |

|-----------------------------------------------|-------|--------------------|--------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Con                                           | nmano | i Class            | 5                                          | Opc                                             | code                                                                    |                                                                                       |                                                                                            |                                                                                                |

|                                               |       | LUN                | 1                                          |                                                 | Hig                                                                     | h Ado                                                                                 | iress                                                                                      |                                                                                                |

|                                               | Mid   | dle Ac             | idres                                      | S                                               |                                                                         |                                                                                       |                                                                                            |                                                                                                |

| e 3 Low Address e 4 Interleave or Block Count |       |                    |                                            |                                                 |                                                                         |                                                                                       |                                                                                            |                                                                                                |

|                                               | Inte  | rleave             | or E                                       | Block (                                         | Count                                                                   |                                                                                       |                                                                                            |                                                                                                |

|                                               | Cor   | trol F             | ield                                       |                                                 |                                                                         |                                                                                       |                                                                                            |                                                                                                |

|                                               | Con   | Mid<br>Low<br>Inte | LUN<br>Middle Ac<br>Low Addr<br>Interleave | Command Class  LUN  Middle Address  Low Address | Command Class Ope LUN  Middle Address Low Address Interleave or Block C | Command Class Opcode  LUN Hig  Middle Address  Low Address  Interleave or Block Count | Command Class Opcode  LUN High Add  Middle Address  Low Address  Interleave or Block Count | Command Class Opcode  LUN High Address  Middle Address  Low Address  Interleave or Block Count |

FIGURE 4-5 DEVICE CONTROL BLOCK (DCB), FORMAT

- Byte 0 Bits 7, 6 and 5 identify the class of the command. Bits 4 through 0 contain the opcode of the command.

- Byte 1 Bit 5 identifies the logical unit number (LUN). Bits 4 through 0 contain logical address 2.

- Byte 2 Bits 7 through 0 contain logical address 1.

- Byte 3 Bits 7 through 0 contain logical address 0 (LSB).

- Byte 4 Bits 7 through 0 specify the interleave or sector count.

- Byte 5 Bits 7 through 0 contain the contain the control field.

### Next to Last Status Byte

Bits 0, Set to zero.

2-4,6,7

Bit 1 When set, error occurred during command execution.

Bit 5 Logical unit number of drive, d=0 or 1.

### Last Status Byte

Bits Set to zero.

0 - 7

Figure 4-6 Completion Status Bytes

### 4.5.1 The Control Byte.

Bit 7 - If Bit 7 is set, the Controller will not retry the operation, but reports the error immediately. If Bit 7 is reset, the Controller will retry the operation 3 times, then recalibrate the drive, seek back to the current track, and retry once more. For example, if an ADDRESS MARK (AM) NOT FOUND error occurs, the Controller attempts to reread the same sector 3 times. If the error persists, the Controller recalibrates the drive to track 0, seeks to the target track and rereads for the last time. If the error still persists the Controller aborts the command and reports the error to the host. Set this bit only during the evaluation of a disk drive.

<u>Bit 6</u> - If Bit 6 is set, the Controller will not retry a read of a sector that contains a data error before attempting error correction. If Bit

6 is reset, the Controller will reread the sector before attempting error correction. It is faster and more reliable to read the data again than apply error correction immediately. If the data error is transient in nature, such as noise or electrical interference in the disk heads or read amplifier, noise in cable, or a power supply transient, then another read of the sector will be successful. If the error occurs twice in succession, the error is usually caused by a media defect, so ECC correction is used to recover the data.

#### Bit 5 - Not used.

Bit 4 - If set to one, indicates the disk drive has disk servo information prior to index on each track. The "Imbedded Servo" drives use this servo information to control the rotational speed of the drive and to control position of the read/write head over the track.

<u>Bit 0-3</u> - Bits 0-3 will set the step rate for the disc drive. The following describes the step rates provided.

| DESCRIPTION BITS         |          |          |          |             |  |

|--------------------------|----------|----------|----------|-------------|--|

|                          | <u>3</u> | <u>2</u> | <u>1</u> | <u>o</u>    |  |

| Default 3 msec step rate | 0        | 0        | 0        | 0           |  |

| Reserved                 | 0        | 0        | 0        | 1           |  |

| Reserved                 | 0        | 0        | 1        | 0           |  |

| Reserved                 | 0        | 0        | 1        | 1           |  |

| 200 usec buffered step   | 0        | 1        | 0        | 0           |  |

| 70 usec buffered step    | 0        | 1        | 0        | 1           |  |

| 30 usec buffered step    | 0        | 1        | 1        | 0           |  |

| 15 usec buffered step    | 0        | ı        | i        | 1           |  |

| 12 usec buffered step    | 1        | 0        | 0        | 0           |  |

| Spare (for future use)   | 1<br>1   | 0<br>1   | 0<br>1   | l thru<br>l |  |

### 4.5.2 Logical Addressing

The logical address of the drive is computed by using the following equation:

Logical Address = (CYADR \* HDCYL + HDADR) \* SETRK + SEADR

where:

CYADR Cylinder Address

HDADR Head Address

SEADR Sector Address

HDCYL Number of Heads per Cylinder

SETRK Number of sectors per track

#### 4.5.3 Command Set

The commands fall into eight classes, 0 through 7; only classes 0 and 7 are used. Class 0 command are data, non-data transfer, and status commands. Classes 1 through 6 are reserved. Class 7 are diagnostic commands.

Each command is described below. The description includes its class, opcode, and format. When a slash (/) represents a bit position, the slash means that the value of that bit is not important (a don't-care bit).

### 4.5.3.1 Test Drive Ready (Code 00)

This command selects the drive specified by the Byte 1 of DCB and reads back the status from that drive. If all status bits are in the correct state, the command will not return an error code. If the drive status is not OK, the command will return an error code.

This command is usually used in 2 occasions:

A) When initially powered on, the host should issue this command continuously with appropriate time out loop to insure the drive spins up to speed and comes ready. B) When implementing overlapped seeks. First, issue a seek command to the first drive, then issue another seek command to the second drive. Now keep issuing a TEST DRIVE READY command to each drive until either drive finishes its seek operation. Then continue with the normal READ/WRITE operation on that drive.

The following diagram shows the format of the device control block for this command.

d = drive, 0 or 1

| Bit    | 7 | 6  | 5 | 4 | 4 | 2 | 1 | 0 |

|--------|---|----|---|---|---|---|---|---|

| Byte 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 |

| Byte 1 | 0 | 0  | d | / | / | / | / | / |

| Byte 2 | 1 | /  | / | / | / | / | / | / |

| Byte 3 | 1 | 1. | / | / | / | / | / | / |

| Byte 4 | / | /  | / | / | / | / | / | / |

| Byte 5 | / | /  | / | 1 | / | / | / | / |

At the end of the TEST DRIVE READY command if no error is reported (bit 1 of status byte) then the drive is ready for the next operation. If an error is reported, then a Request Sense Status command must be issued to determine the status of the drive.

## 4.5.3.2 Recalibrate (Code 01)

This command will move the drive arm to the track 00 position. This command should only be used to attempt to correct a drive position error, since it is slower than a direct seek to track 0. Also, if retries are enabled, the Controller will recalibrate automatically in case of error. The difference between this command and a direct seek to track 0 is this command steps the drive one cylinder at a time looking for the signal TRACK 00 from the drive to become active. A direct seek to track 0 is faster because the Controller steps the drive at the programmed step rate.

d = drive, 0 or 1

r = retries

| Bit     | <b>7</b> . | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---------|------------|---|---|---|---|---|---|-----|

| Byte 0  | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 1   |

| Byte 1  | 0          | 0 | d | 1 | 1 | / |   | _/_ |

| Byte 2  | 1          | / | 1 | / | / | / | / | /   |

| Byte 3  | 1          | 1 | 1 | 1 | 1 | 1 | 1 | /   |

| Byte 4  | 1          | 1 |   | 1 | 1 | 1 | 1 | /   |

| Byte 5  | -          | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| Dy Le 7 | L          |   |   |   |   |   |   |     |

# 4.5.3.3 Reserved (Class 0, Opcode 02)

This opcode is not used.

# 4.5.3.4 Request Sense Status (Code 03)

The host must send this command immediately after it detects an error. The command causes the Controller to return four bytes of drive and Controller status; the formats of these four bytes are shown after the DCB. When an error occurs on a multiple sector data transfer, (read or write), the Request Sense Status command

returns the logical address of the failing sector in bytes 1, 2 and 3. If the Request Sense Status command is issued after any of the Format commands or the Check Track Format command, then the logical address returned by the controller points to one sector beyond the last track formatted or checked if there was no error. If there was an error, then the logical address returned points to the track in error.

d = drive, 0 or 1

| Bit    | 7    | 6   | 5   | 4                       | 3     | 2 | 1 | 0 |  |

|--------|------|-----|-----|-------------------------|-------|---|---|---|--|

| Byte 0 | 0    | 0   | 0   | 0                       | 0     | 0 | 1 | 1 |  |

| Byte 1 | 0    | 0   | d   | /                       |       | / |   | / |  |

| Byte 2 | 1    | /   | /   | /                       | /     | / | 1 | 7 |  |

| Byte 3 | 1    | /   | /   | /                       | /     |   | 1 | - |  |

| Byte 4 | 1    | /   | /   |                         | /     | / |   | - |  |

| Byte 5 | 1    | 1   | /   | /                       | /     | / | / | / |  |

|        |      |     | SEN | NSE BYTES               |       |   |   |   |  |

| Bit    | 7    | 6   | 5   | 4                       | 3     | 2 | 1 | 0 |  |

| Byte 0 |      |     | SEE | BELO                    | ow ·  |   |   |   |  |

|        | Bits | 0-3 |     | Error Code              |       |   |   |   |  |

|        | Bits | 4-5 |     | Erro                    | r Typ | е |   |   |  |

|        | Bits | 6   |     | Spare, set to zero      |       |   |   |   |  |

|        | Bits | 7   |     | Address valid, when set |       |   |   |   |  |

The address valid bit in the error code byte (bit 7) is relevant only when the previous command required a logical block address; in which case it is always returned as a one, otherwise it is set to zero. For instance, if a Recalibrate command is followed immediately by a Request Sense Status command, the address valid bit would be returned as zero since this command does not require a logical block address to be passed in its DCB.

| Bit    | 7 _         | 6   | 5      | 4        | 3        | 2     | 1    | 0 |

|--------|-------------|-----|--------|----------|----------|-------|------|---|

|        |             |     |        |          |          |       |      |   |

| Byte 1 | 0           | 0   | d      | <u> </u> | Hig      | h Add | ress |   |

| Byte 2 |             | Mic | idle A | ddress   | <u> </u> |       |      |   |

| Byte 3 | Low Address |     |        |          |          |       |      |   |

| •      |             |     |        |          |          |       |      |   |

d = drive, 0 or 1

This section details the S1410A Error Codes returned in the REQUEST SENSE STATUS command. The cause of the error is given, followed by the most probable source of the error. The error code numbers are given in HEX notation.

# TABLE 4-6 TYPE 0 ERROR CODES, DISK DRIVE

### HEX CODE DEFINITION

No Error Occurred. This code is always returned if no error had occurred during the previous command.

No Index Signal from the Drive. This error occurs during any data transfer or format command if a normal drive select occurs, the drive is ready, but no index signal is detected from the drive within two revolutions of the disk. Possible error causes are:

- Bad Drive

- Control Cable (J1)

- Controller

No Seek Complete Signal from the Drive. This error occurs on non-buffered seek processing if the controller does not receive the Seek Complete Signal from the Drive within one second following the last step pulse. Possible error causes are:

- Bad Drive

- Control Cable (J1)

- Controller

Write Fault Signal Received from the Drive. This error occurs if the controller detects an active write fault signal from the disk drive either at the completion of a sector data transfer or initially after a successful drive select and the drive indicates ready. Possible error causes:

- Drive power supply voltage out of range

- Bad Drive

- Control Cable (J1)

- Unit Cable (J2, J3)

- Controller

# TABLE 4-6 TYPE 0 ERROR CODES, DISK DRIVE (CONTINUED)

| HEX CODE | DEFINITION                                                                  |

|----------|-----------------------------------------------------------------------------|

| 04       | Disk Drive Not Ready. This error occurs if the controller fails             |

|          | to the select the drive, or the drive indicates not ready after             |

|          | selection. Possible error causes:                                           |

|          | <ul> <li>Drive power supply voltages out of range</li> </ul>                |

|          | <ul> <li>Drive not yet up to operating speed following power on</li> </ul>  |

|          | - Bad drive                                                                 |

|          | - Control Cable (J1)                                                        |

|          | - Controller                                                                |

| 05       | Not used                                                                    |

|          |                                                                             |

| 06       | Track 00 Not Found. After stepping the drive 200 more steps                 |

|          | than the number of configured cylinders during a recalibrate                |

|          | command, the Track 00 Signal was not received fron the drive.               |

|          | Possible causes are:                                                        |

|          | <ul> <li>Incorrect drive size initialization (too few cylinders)</li> </ul> |

|          | - Bad Drive                                                                 |

|          | - Control Cable (J1)                                                        |

|          | - Bad controller                                                            |

| 07       | Not used                                                                    |

|          |                                                                             |

| 08       | Disk Drive is Seeking. This code is returned in response to a               |

|          | test drive ready command if the drive had previously been                   |

|          | issued a buffered seek command that has not yet completed.                  |

| 09 to    |                                                                             |

| 0F       | Not used                                                                    |

# TABLE 4-7 TYPE I ERROR CODES, CONTROLLER

ID Field Read Error. During a data transfer or format command, address marks were detected, but the target sector was not found and an ECC error occurred on one or more ID fields. Possible causes are:

- Media Defect on Drive

- Bad Drive (if errors are excessive or continuous)

- Bad controller (if errors are excessive or continuous)

Media defects may be overcome by deleting the defective sectors from system use or assigning an alternate track.

Uncorrectable Data Error in the Data Field. The controller detected a data error that could not be corrected using ECC. Possible causes are:

- Media defect on drive

- Bad drive (if errors are excessive or continuous)

- Bad controller (if errors are excessive or continuous)

Media defects may be overcome by deleting the defective sectors from system use or assigning an alternate track.

Sector Address Mark Not Found. The controller did not detect an address mark (AM) from the drive within its timing window. An address mark is a special recording pattern preceeding the ID field of a sector. The AM is only written at format time. The AM tells the controller where new sectors start. The error may occur during any data transfer or format commands. The error may mean that no address marks were detected on the track, or the target sector address mark was not detected. Possible causes are:

- Media defect on drive

- Drive has not been formatted

- Bad drive

- Bad unit cable (J2, J3)

- Bad controller

Media defects may be overcome by deleting the defective sectors from system use or assigning an alternate track.

# TABLE 4-7 CONTROLLER ERROR CODES (CONTINUED)

| HEX CODE<br>14 | <ul> <li>DEFINITION</li> <li>Target Sector Not Found. The target sector was not located within two revolutions of the disk. Possible causes are: <ul> <li>Media defect on drive.</li> <li>Invalid format (changing sector size from 512 to 256 bytes and not reformatting the drive)</li> </ul> </li> <li>Bad drive</li> <li>Bad controller</li> </ul> |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>16 to    | Seek Error. After a seek, the target disk address did not match the ID address read from the disk. Either the cylinder or head bytes did not match. Possible causes are:  - Incorrect seek option specified in the command - Bad drive (Seek to incorrect cylinder) - Bad control cable (J1) - Bad controller                                          |

| 16 to<br>17    | Not used                                                                                                                                                                                                                                                                                                                                               |

| 17             |                                                                                                                                                                                                                                                                                                                                                        |

| 18             | Correctable Data Error. The controller detected a media error while reading that was corrected by ECC. This error code informs the host software that error correction has taken place.                                                                                                                                                                |

| 19             | Track is Flagged Bad. The last data transfer command encountered a track that had been flagged defective using the Format Bad Track Command. Host software is responsible for insuring that deleted tracks are never accessed.                                                                                                                         |

| 1A             | Format Error. During execution of a check track command, the controller detected an unformatted track, the wrong interleave on disk, or an ID ECC error on at least one sector.                                                                                                                                                                        |

| 1B             | Not used                                                                                                                                                                                                                                                                                                                                               |

# TABLE 4-7 CONTROLLER ERROR CODES (CONTINUED)

### HEX CODE DEFINITION

IC Controlle

Controller Detected a Direct Access to an Alternate Track. A track that has the alternate track flag set in the ID has been directly accessed by the host, instead of coming from the defective track that that is assigned to this alternate track. Host software is responsible for insuring that the alternate track area is not directly accessed.

The Designated Alternate Track is already assigned to another Defective Track, or is flagged as a Bad Track. Host software has attempted to assign an alternate track to replace a defective track, but the alternate had previously been assigned to a defective track, or has been previously formatted as a bad track. If an alternate track is no longer needed, the host software must reformat the track using the FORMAT TRACK command before attempting to reassign the track again.

Assigned Alternate Track Not Found. A defective track has been assigned an alternate track, but the alternate track does not have the alternate track bit set in the ID field. This may be caused by reformatting the alternate track with the format track command without reprocessing the defective track.

The Alternate and Defective Track Addresses point to the same track. Host software has attempted to assign a defective track to itself. That is not allowed in this alternate track scheme.

TABLE 4-8 TYPES 2 AND 3 ERROR CODES, COMMAND AND MISCELLANEOUS

| HEX CODE<br>20 | <u>DEFINITION</u> Invalid Command: The controller has received an invalid command from the host.                                                                                                 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|