| 4.1. | Hardware     |                  |                           | 2  |

|------|--------------|------------------|---------------------------|----|

|      | 4.1.1        | Memory on DCM    | board                     | 2  |

|      | 4.1.2        | Memory on MEB    |                           | 5  |

|      |              | 4.1.2.1          | Memory Controller Chip    | 6  |

|      |              | 4.1.2.2          | Backplane Interface       | 7  |

| 4.2. | Theory of Op | erations         |                           | 10 |

|      | 4.2.1        | Read             |                           | 10 |

|      | 4.2.2        | Write            |                           | 10 |

|      | 4.2.3        | Refresh          |                           | 11 |

| 4.3. | Programmer   | Interface        |                           | 11 |

|      | 4.3.1        | Status Registers |                           | 11 |

|      | 4.3.2        | Memory Timing    |                           | 13 |

|      | 4.3.3        | Functions        |                           | 14 |

|      |              | 4.3.3.1          | Full and Page Mode Access | 14 |

|      |              | 4.3.3.2          | Row and Column Addressing | 14 |

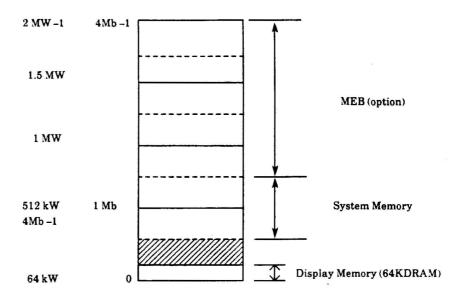

The display memory, the system memory, and the expansion memory (option) are included in the memory subsystem.

Memory for Daybreak is packaged in 512 Kbyte blocks. Each of the three memory segments requires a memory controller. Each memory controller includes a refresh controller.

The system and expansion memory has three ports: one for the Mesa processor, one for the I/O subsystem, and one for the Refresh controller. These three devices operate independently except when competing for the same memory segment. Display memory has an additional display controller port. The refresh controller is responsible for refreshing the DRAM chips in its block of real memory.

Each port of the memory subsystem employs a protocol suited to the corresponding device. Each device initiates a memory request whenever necessary. The request results in a memory cycle when the currently active and higher-priority requests have been satisfied.

The memory controller chip receives memory request signals from outside ports (ports A, B, and C), sets priorities, and generates proper control signals to perform memory operations. It also has circuitry to initiate refresh of the dynamic RAMs so that data is maintained.

The memory controller runs four types of cycles:

- display. Display cycles are quadword read. DRAM nibble mode operation allows the display controller to use all the available memory bandwidth.

- IOP bus. Memory cycles are: read word, write word, write high byte, and write low byte.

- Mesa Processor. Memory cycles are: read word and write word.

- · Refresh.

#### 4.1 Hardware

Memory on the Display Control and Memory (DCM) is 3 x 256 KW, and memory on the Memory Expansion Board (MEB) is 5 x 256 KW. Both are multi-ported memory banks with an internal refresh port. Normal word access cycle time is 312.5 ns/16-bit word; read access cycle time is 718 ns/64-bit nibble.

Figure 4.1 illustrates the memory units.

Figure 4.1. Memory units

#### 4.1.1 Memory on DCM Board

The DCM board contains both display memory and system memory.

The display memory is the first 64 KW of 256 KW real memory contained on the DCM board. Display memory can be 64 KW or 256 kW. It is a 3-ported memory bank with an internal refresh port, controlled by a gate array chip, the Memory Control Chip (MCC).

Figure 4.2 illustrates the pins and signals of the Memory Control Chip (MCC) gate array. Note: Italicized signals are not required for Display memory operation.

|           |     | 2           |       | 200  | ١           |     |         |        |

|-----------|-----|-------------|-------|------|-------------|-----|---------|--------|

| DOPE0     |     | 1           | P1P68 | P68  | 68          |     | PEINT'  |        |

| ERRCLK"   |     | 2           | P2    | P67  | 67          |     |         |        |

| DOPE1     |     | 3           | P3    | P66  | 66          |     |         |        |

| A/BHEB'   |     | 4           | P4    | P65  | 65          |     |         |        |

| A/A.00B'  |     | 5           | P5    | P64  | 64          |     | WTHB    |        |

| A/RESETB1 |     | 6           | P6    | P63  | 63          |     | WTLB    |        |

| RFREQDIS' |     | 7           | P7    | P62  | 62          |     | WRITE   |        |

|           | GND | 8           | P8    | P61  | 61          | VCC |         |        |

|           | VCC | 9           | P9    | P60  | 60          | GND |         |        |

|           | GND | 10          | P10   | P59  | 59          |     | DOCLK   |        |

| C/A.20    | GND | 11          | P11   | P58  | 58          |     |         |        |

| B/A.20    |     | 12          | P12   | P57  | 57          |     | PCEN'   |        |

| A/MA.20   |     | 13          | P13   | P56  | 56          |     | PBEN'   |        |

| C/A.191   |     | 14          | P14   | P55  | 55          |     | PAEN'   |        |

| B/A.19    |     | 15          | P15   | P54  | 54          |     | B/ALEB  |        |

| A/MA.19   |     | 16          | P16   | P53  | 53          |     | B/MEMRE | EFL'   |

| A.20      |     | 17          | P17   | P52  | 52          |     | REFS2   |        |

| A.19      |     | 18          | P18   | P51  | 51          | GND | A/PROC  | ,      |

| RAS0T     |     | 19          | P19   | P50  | 50          |     | PBAH'   |        |

| RAS1T     |     | _20         | P20   | P49  | 49          |     | C/MEMRI | CF'    |

| RAS2T     |     | 21          | P21   | P48  | 48          |     | A/MEMRI | EF'    |

| RAS3T     |     | 22          | P22   | P47  | 47          |     | PAAH'   |        |

| CAS1T     |     | 23          | P23   | P46  | 46          |     | A/MRDBL | ,      |

| CAS0T     |     | 24          | P24   | P45  | 45          |     | A/MWTBI | ,      |

|           | VCC | 25          | P25   | P44  | 44          |     | GND     |        |

|           | GND | 26          | P26   | P43  | 43          | VCC |         |        |

|           | GND | 27          | P27   | P42  | 42          |     | RAWCLK  | В      |

| COLT'     |     | 28          | P28   | P41  | 41          | GND | C/NIBBI | LE'    |

| ROWT'     |     | 29          | P29   | P40  | 40          | GND | C/MRD'  |        |

| C/XACK'   |     | 30          | P30   | P39  | 39          |     | HIGH1   | C/MWT' |

| B/READYL  | .,  | 31          | P31   | P38  | 38          |     | B/MRD'  |        |

| A/READYL  |     | 32          | P32   | P37  | 37          |     | B/MWT'  |        |

| PCRDEN'   |     | 33          | P33   | P36  | 36          |     | A/ALEB  |        |

| PBRDEN'   |     | 34          | P34   | P35  | 35          |     | PARDEN' |        |

| - DIWELL  |     | U- <b>T</b> | . 04  | 1 00 | <del></del> |     |         |        |

\*Refresh Control Signal REFS2 is inserted at MCC pins 51 (A/PROC') and 52 (C/MEMREF') to delay IOP and/or display requests going to the Arbiter during a refresh operation.

Figure 4.2. DCM memory controller chip

Memory

REFS2\*

Table 4.1 describes the signals illustrated in Figure 4.2.

Table 4.1. Memory Control Chip (Display) Signal Description

| Signal                               | Function                                                                                           |                               |                   |                                                                     |                                                                                      |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------|-------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| A/A.00B'                             | With A/BHEB' identifies port A memory operation, as follows:                                       |                               |                   |                                                                     |                                                                                      |  |

| A/BHEB'                              | <u>A/A.00B'</u><br>0                                                                               | A/BHEI                        | <u>B'</u>         | Memory Op<br>Word                                                   | eration                                                                              |  |

|                                      | 0<br>1                                                                                             | 1 0                           |                   | High byte only<br>Low byte only                                     |                                                                                      |  |

|                                      | i                                                                                                  | 1                             |                   | Not 1                                                               |                                                                                      |  |

| A.19:20                              | With A.21 selects mem                                                                              | ory location                  | on, as            | follows:                                                            |                                                                                      |  |

|                                      | (A;B/A;C/A) (A;l<br>A.21<br>0<br>0<br>0                                                            | B/A;C/A)<br>20<br>0<br>0<br>1 | 19<br>0<br>1<br>0 | Memory<br>Selected<br>0 - 255 KW<br>256 - 511 KW<br>512 - 767 KW    | Remark Display memory Bank 1, system memory Bank 2, system memory                    |  |

|                                      | 0<br>1<br>1<br>1                                                                                   | 1<br>0<br>0<br>1              | 1<br>0<br>1<br>0  | 768 - 1023 KW<br>1024 - 1279 KW<br>1080 - 1535 KW<br>1536 - 1791 KW | Bank 1, MEB memory<br>Bank 2, MEB memory<br>Bank 3, MEB memory<br>Bank 4, MEB memory |  |

|                                      | 1                                                                                                  | 1                             | 1                 | 1792 - 2047 KW                                                      | Bank 5, MEB memory                                                                   |  |

| A/ALEB<br>B/ALEB                     | Address latch enable signal for port A and port B                                                  |                               |                   |                                                                     |                                                                                      |  |

| A/MA.19:20<br>B/A.19:20<br>C/A.19:20 | Generate A.19-20, as described above. The prefix identifies the corresponding port.                |                               |                   |                                                                     |                                                                                      |  |

| A/MEMREF'<br>B/MEMREFB'<br>C/MEMREF' | Indicate that a memory operation is being requested. The prefix identifies the corresponding port. |                               |                   |                                                                     |                                                                                      |  |

| A/MRDBL'<br>B/MRD'<br>C/MRD'         | Memory read operation. The prefix identifies the corresponding port.                               |                               |                   |                                                                     |                                                                                      |  |

| A/MWTBL'<br>B/MWT'<br>C/MWT'         | Memory write operation. The prefix identifies the corresponding port.                              |                               |                   |                                                                     |                                                                                      |  |

| A/PROC'                              | Not used.                                                                                          |                               | X 385             |                                                                     |                                                                                      |  |

| A/READYL<br>B/READYL                 | Indicates port readiness.                                                                          |                               |                   |                                                                     |                                                                                      |  |

| A/RESETB1'                           | General reset.                                                                                     |                               |                   |                                                                     |                                                                                      |  |

| CAS0T<br>CAS1T                       | CAS (column address s                                                                              | trobe) ena                    | ble fo            | or RAM. CAS1T is r                                                  | ot used.                                                                             |  |

| C/NIBBLE'                            | Indicates port C nibble                                                                            | mode ope                      | ratio             | n.                                                                  |                                                                                      |  |

| COLT'                                | Not used.                                                                                          |                               |                   |                                                                     |                                                                                      |  |

| C/XACK'                              | Transfer acknowledge                                                                               | for port C.                   |                   |                                                                     |                                                                                      |  |

| DOCLK                                | Data Out clock.                                                                                    |                               |                   |                                                                     | ,                                                                                    |  |

- more -

Table 4.1. Memory Control Chip (Display) Signal Description (continued)

| Signal                        | Function                                                                    |

|-------------------------------|-----------------------------------------------------------------------------|

| DOPE0-1                       | Data Out parity error for low and high byte.                                |

| нісні                         | Input high.                                                                 |

| LOCK                          | Not used.                                                                   |

| PAAH'<br>PBAH'                | Indicates valid memory address by the corresponding port.                   |

| PAEN'<br>PBEN'<br>PCEN'       | Identifies the port now being serviced by memory.                           |

| PARDEN'<br>PBRDEN'<br>PCRDEN' | Enables read operation for corresponding port.                              |

| PEINT'                        | Indicates that a parity error was encountered during memory read operation. |

| RAS0T-3T                      | RAS (row address strobe) enable for RAM.                                    |

| RAWCLKB                       | System clock.                                                               |

| RFREQDIS'                     | Disables refresh circuit for dynamic RAM.                                   |

| ROWT'                         | Not used.                                                                   |

| WRITE                         | Not used.                                                                   |

| WTHB<br>WTLB                  | Enables memory write operation to high and/or low byte.                     |

# 4.1.2 Memory on MEB

The Memory Expansion Board is a 10.9 inch by 16 inch 165-pin board populated with 256K DRAMs. Figure 4.3 illustrates the board layout.

Memory 4 - 3

Figure 4.3. Memory Expansion Board (MEB) layout

## 4.1.2.1

# **Memory Controller**

Chip

A 68-pin gate array, MCC, acts as memory controller on the MEB. Figure 4.4 illustrates pins and signals for the MEB memory controller chip (MCC). Refer to the preceding table for description of signals.

· 6 Memory

|                                         |       |    |     |           | 1        |            |

|-----------------------------------------|-------|----|-----|-----------|----------|------------|

| DOPE0                                   |       | 1  | P1  | P68       | 68       | PEINT'.S   |

| ERRCLK'                                 |       | 2  | P2  | P67       | 67       |            |

| DOPE1                                   |       | 3  | P3  | P66       | 66       |            |

| A/BHEB'                                 |       | 4  | P4  | P65       | 65       |            |

| A/A.00B'                                |       | 5  | P5  | P64       | 64       | WTHB.S     |

| A/RESETB2                               |       | 6  | P6  | P63       | 63       | WTLB.S     |

| RFREQDIS'                               |       | 7  | P7  | P62       | 62_      |            |

|                                         | GND   | 8  | P8  | P61       | 61       | VCC        |

|                                         | VCC   | 9  | P9  | P60       | 60       | GND        |

|                                         | GND   | 10 | P10 | P59       | 59       | DOCLK      |

|                                         | GND   | 11 | P11 | P58       | 58       |            |

|                                         | GND   | 12 | P12 | P57       | 57       |            |

|                                         | GND   | 13 | P13 | P56       | 56       | PBEN'      |

|                                         | GND   | 14 | P14 | P55       | 55       | PAEN'      |

|                                         | GND   | 15 | P15 | P54       | 54       | B/ALEB     |

|                                         | GND   | 16 | P16 | P53       | 53       | B/MEMREFL' |

|                                         |       | 17 | P17 | P52       | 52       | REFS2      |

|                                         |       | 18 | P18 | P51       | 51       | REFS2      |

| RASOT*                                  |       | 19 | P19 | P50       | 50       | PBAH'      |

| *************************************** |       | 20 | P20 | P49       | 49       | HIGH3      |

|                                         |       | 21 | P21 | P48       | 48       | A/MEMREF'  |

|                                         |       | 22 | P22 | P47       | 47       | PAAH'      |

|                                         |       | 23 | P23 | P46       | 46       | A/MRDB'    |

| CASOT                                   |       | 24 | P24 | P45       | 45       | A/MWTB'    |

|                                         | VCC   | 25 | P25 | P44       | 44       | GND        |

|                                         | GND   | 26 | P26 | P43       | 43       | VCC        |

|                                         | GND   | 27 | P27 | P42       | 42       | RAWCLKB    |

|                                         | ····· | 28 | P28 | P41       | 41       | HIGH3      |

|                                         |       | 29 | P29 | P40       | 40       | HIGH3      |

|                                         |       | 30 | P30 | P39       | 39       | HIGH3      |

| B/READYL                                |       | 31 | P31 | P38       | 38       | B/MRD'     |

|                                         |       | 32 | P32 | P37       | 37       | B/MWT'     |

|                                         |       | 33 | P33 | P36       | 36       | A/ALEB     |

| PBRDEN'                                 |       | 34 | P34 | P35       | 35       | PARDEN'    |

|                                         |       |    |     | or can be | <b> </b> |            |

Figure 4.4. MEB memory controller chip

## 4.1.2.2 Backplane Interface

Table 4.2 lists the MEB interface to the backplane.

Table 4.2. MEB Backplane Pin Assignment (Front View)

| Outmost | Inmost |

|---------|--------|

|         |        |

| ) 80186 Bus                                                              |                     |                      |             |              |

|--------------------------------------------------------------------------|---------------------|----------------------|-------------|--------------|

| Spare-1 J1.001                                                           | GND                 | J1.002               | Spare-2     | J1.003       |

| A/AD.07 (bi) J1.004                                                      | A/DT/R'(i)          | J1.005               | A/AD.15 (bi | ) J1.006     |

| A/AD.06 (bi) J1.007                                                      | A/DEN' (i)          | J1.008               | A/AD.14 (bi | ) J1.009     |

| A/AD.05 (bi) J1.010                                                      | GND                 | J1.011               | A/AD.13 (bi | ) J1.012     |

| A/AD.04 (bi) J1.013                                                      | A/MemRdy (o)        | J1.014               | A/AD.12 (bi |              |

| A/AD.03 (bi) J1.016                                                      | A/ALE'              | J1.017               | A/AD.11 (bi | ) J1.018     |

| A/AD.02 (bi) J1.019                                                      | A/IOPMemWr'(        | i) J1.020            | A/AD.10 (bi | ) J1.021     |

| A/AD.01 (bi) J1.022                                                      | Spare-3             | J1.023               | A/AD.09 (b) | ) J1.024     |

| A/AD.00 (bi) J1.025                                                      | GND                 | J1.026               | A/AD.08 (b) | ) J1.027     |

| GND J1.028                                                               | A/CLK(i)            | J1.029               | VCC         | J1.030       |

| 1.031 GND                                                                | J1.032 G            | ND                   | J1.033      | GND          |

| 1.034 A/AA.19*                                                           |                     | /S.2'                | J1.036      | A/AA.23*     |

| 1.037 A/AA.18*                                                           | <del></del>         | /S.1'                | J1.039      | A/AA.22*     |

| 1.040 A/AA.17*                                                           |                     | .S.0'                | J1.042      | A/AA.21*     |

| 1.043 A/AA.16*                                                           |                     | /BHE'                | J1.045      | A/AA.20*     |

| 1.046 A/EPROMCs'*                                                        |                     | ND                   | J1.048 (i)  | A/IOR'       |

| 1.049 Reserved-0                                                         |                     | /LocRamCS**          | J1.051      | Spare-4      |

| 1.052 A/IOPLock'*                                                        |                     | ND                   | J1.054 (i)  | A/IOW'       |

| 1.055 A/PCHldToArb                                                       |                     | /IOPMemRd'           | J1.057 (i)  | Spare-5      |

| 1.058 -5V                                                                |                     | V                    | J1.060      | -5V          |

|                                                                          |                     | 2) MPB-              | DCM         |              |

| GND J1.061                                                               | GND                 | J1.062               | GND         | J1.06        |

| A/IORdy* J1.064                                                          | A/MA.23 (i)         | J1.065               | A/MA.22 (i) | J1.06        |

| Spare-7 J1.067                                                           | A/MA.21 (i)         | J1.068               | A/MA.20 (i) | J1.06        |

| SpareID* J1.070                                                          | A/MA.19 (i)         | J1.071               | A/MA.18 (i) | J1.07        |

|                                                                          | A/MA.17(i)          | J1.074               | A/AA.16B (  | i) J1.07     |

| DBRK/DAISY'* J1.073                                                      | A/MA.17(I)          | 41.074               |             |              |

| DBRK/DAISY** J1.073 A/PEINT* (0) J1.076                                  | GND                 | J1.074<br>J1.077     | MPB-DCM-    |              |

|                                                                          |                     | J1.077               | MPB-DCM-    | sparel J1.07 |

| A/PEINT' (o) J1.076                                                      | GND                 | J1.077               |             | sparel J1.07 |

| A/PEINT* (o) J1.076<br>A/MEBIntr** J1.079                                | GND                 | J1.077               |             |              |

| A/PEINT (₀) J1.076<br>A/MEBIntr J1.079<br>A/VRETINT J1.082               | GND                 | J1.077               |             | spare1 J1.07 |

| A/PEINT (0) J1.076<br>A/MEBIntr J1.079<br>A/VRETINT J1.082<br>GND J1.085 | GND<br>MPB-DCM-spai | J1.077<br>re2 J1.080 | 3) M        | spare1 J1.07 |

<sup>\*</sup> Not used

- more -

Table 4.2. MEB Backplane Pin Assignment (continued)

| <u>Ou</u>                                                    | tmost                      |                                                                                            |                                                                                                  | Ī                                                                                  | nmost                                                                                                  |

|--------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 4) IOP-Mesa                                                  | a                          |                                                                                            |                                                                                                  | 3) MesaBus (co                                                                     | ontinued)                                                                                              |

| J1.091                                                       | GND                        | J1.092                                                                                     | GND                                                                                              | J1.093                                                                             | GND                                                                                                    |

| J1.094                                                       | A/IOPIntMP**               | J1.095                                                                                     | CSWREN*                                                                                          | J1.096 (o)                                                                         | A/MEMS'                                                                                                |

| J1.097                                                       | A/MPIntIOP*                | J1.098                                                                                     | CSLOAD/SHIFT**                                                                                   | J1.099 (i)                                                                         | B/Lock'                                                                                                |

| J1.100                                                       | A/IOPRdNIA*                | J1.101                                                                                     | CSBUFFEREN*                                                                                      | J1.102                                                                             | B/IOR'*                                                                                                |

| J1.103                                                       | A/Halt'*                   | J1.104                                                                                     | CSDATAIN*                                                                                        | J1.105 (i)                                                                         | B/MemRef*                                                                                              |

| J1.106                                                       | IOP-S-spare1               | J1.107                                                                                     | CSSHIFTCLK*                                                                                      | J1.108                                                                             | B/IOW**                                                                                                |

| J1.109                                                       | A/ResetMPB'*               | J1.110                                                                                     | CSDATOUT*                                                                                        | J1.111 (o)                                                                         | B/Rdy                                                                                                  |

| J1.112                                                       | VCC                        | J1.113                                                                                     | VCC                                                                                              | J1.114                                                                             | VCC                                                                                                    |

| J1.115                                                       | VCC                        | J1.116                                                                                     | VCC                                                                                              | J1.117 (i)                                                                         | VCC                                                                                                    |

| J1.118                                                       | VCC                        | J1.119                                                                                     | VCC                                                                                              | J1.120                                                                             | VCC                                                                                                    |

| GND GND INTDIS' B/A.23 (i B/A.21 (i B/A.20 (i B/A.19 (i -12V | J1.136<br>J1.139<br>J1.142 | GND<br>GND<br>B/A.18 (i)<br>B/A.17 (i)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi) | J1.122<br>J1.125<br>J1.128<br>J1.131<br>J1.134<br>J1.137<br>J1.140<br>J1.143<br>J1.146<br>J1.149 | GND GND B/ALE' (0) Dawn-Mp-sp B/D.11 (bi) B/D.10 (bi) B/D.09 (bi) B/D.08 (bi) -12V | J1.123<br>J1.126<br>J1.129<br>J1.132<br>pare3 J1.135<br>J1.138<br>J1.141<br>J1.144<br>J1.147<br>J1.150 |

| J1.151<br>J1.154 (bi)<br>J1.157 (bi)                         | GND<br>B/D.07<br>B/D.05    | J1.152<br>J1.155 (bi)<br>J1.158                                                            | GND<br>B/D.12<br>GND                                                                             | J1.153<br>J1.156 (bi)<br>J1.159 (bi)                                               | GND<br>B/D.06<br>B/D.04                                                                                |

| J1.160 (bi) J1.163 (bi)                                      | B/D.03<br>B/D.01           | J1.161 (i)<br>J1.164                                                                       | A/Reset'<br>GND                                                                                  | J1.162 (bi) J1.165 (bi)                                                            | B/D.02<br>B/D.00                                                                                       |

| VALUE (DI)                                                   | <u> </u>                   | 81.10 <del>4</del>                                                                         |                                                                                                  | 91.100 (DI)                                                                        | D/D.VV                                                                                                 |

# 4.2 Theory of Operations

The Mesa processor, 80186, display controller, and memory operate at independent speeds. These subsystems are logically joined by the synchronous memory arbiter within the memory controller gate array chip (MCC) on each board. The arbiter grants memory access according to the following priority: refresh, display control, IOP, and Mesa processor. When memory is not busy, the arbiter grants access to the first requesting device. Otherwise, arbitration is performed during the DRAM RAS precharge time.

IOP and Mesa Processor memory requests are initiated by bus transactions. At the 80186 bus port (port A), the memory controller responds to mapped address bits MA23-17 and not to A17-20. At the Mesa bus port (port B), all signals are synchronized with the Mesa processor.

For refresh, the memory controller counts down from the 16 MHz input clock and requests refresh cycles when necessary.

When a memory cycle is granted, the memory controller is started. The memory controller multiplexes the addresses, controls memory timing, delivers data, and starts the IOP arbiter when memory is again available. DRAM strobes are generated from shift registers in the MCC gate array chip.

The memory controller generates and checks byte parity. If the IOP has accessed memory, then a parity error interrupts the IOP. If the Mesa processor has accessed memory, then a parity error traps the Mesa processor.

The MCC synchronously generates RAS, CAS, and other control signals.

The following subsections provide a summary of system memory functions as viewed from the central processor.

#### 4.2.1 Read

A read operation is started upon receipt of a MemRef and valid memory address from the selected port. The selected port address is multiplexed to form the Row/Column DRAM address. The RAS/CAS clocks are initiated. Read data is placed on the selected port bus within 250 ns after the start of the cycle.

#### 4.2.2 Write

A Write operation is started in the same manner as a Read operation. Write data is multiplexed from the selected port and routed to the DRAM array. Byte parity is generated and sent to the parity DRAMs. The Write operation is completed when the MCC controller issues the 62 ns write clock.

#### 4.2.3 Refresh

The memory controller gate arrays contain circuitry for memory refresh. The MCC generates a refresh sycle by issuing a CAS-before-RAS clock sequence. The refresh time circuit within the MCC determines the refresh interval (minimum of 256 cycles in 2 ms). The RAM device contains the refresh address counter and performs the refresh cycle operation.

# 4.3 Programmer Interface

This section describes the memory status registers and typical process timing.

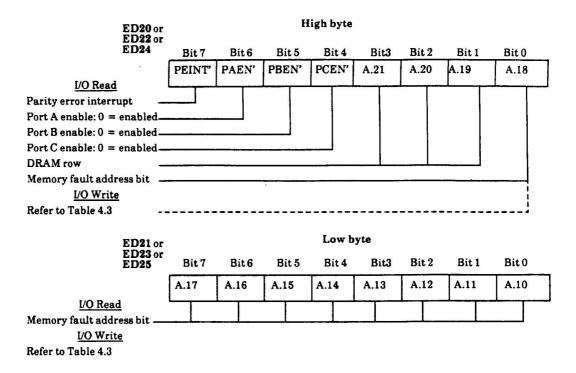

Figure 4.5 illustrates the IOP I/O address map for memory.

| For DCM |                                               |                                                                       |              |  |  |  |

|---------|-----------------------------------------------|-----------------------------------------------------------------------|--------------|--|--|--|

|         | I/O Read                                      | I/OWrite                                                              | ď            |  |  |  |

| ED20    | Memory Status Register<br>(MSR) for<br>MCC #1 | Write parity mode for MCC #1  Clear parity interrupt in MSR of MCC #1 | ED20<br>ED21 |  |  |  |

| ED22    | Memory Status Register (MSR) for              | Write parity mode for MCC #2                                          | ED22         |  |  |  |

| ED23    | MCC #2                                        | Clear parity interrupt in MSR of MCC #2                               | ED23         |  |  |  |

| -            | I/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | or MEB  I/OWrite                        | _    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| ED24         | to to the productive of the state of the sta | Write parity mode for MCC #1            | ED24 |

|              | (MSR) for<br>MCC #3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Clear parity interrupt in MSR of MCC #3 |      |

| ED25<br>ED26 | Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ED25<br>ED26                            |      |

|              | (Not yet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t implemented)                          |      |

| ED27         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                      |      |

Figure 4.5. IOP I/O address map for memory

#### 4.3.1 Status Registers

A Memory Control Chip (MCC) controls a unit of memory space. Each MCC has an associated memory status register.

In each unit of memory, the 16-bit, read/write status register, readable at any time by the IOP, logs the following information: Port

A, B, or C selected; the row of 256 Kbit DRAM devices accessed; and the memory page address of a fault.

Figure 4.6 illustrates the register.

Figure 4.6. Memory status register

When a memory error condition is detected, the faulty memory address is logged into the memory status register of the corresponding MCC. The memory status register can be accessed by the I/O read operation.

The I/O write operation has two functions: defining parity mode and clearing parity error interrupts. Table 4.3 lists the address map locations on the MEB for these functions.

Table 4.3. I/O Write Operation Locations

| Hex Address          | Data bit 0 = | <u>Function</u>                                                               |

|----------------------|--------------|-------------------------------------------------------------------------------|

| ED20                 | 0<br>1       | MCC #1 is odd parity mode MCC #1 is even parity mode                          |

| ED22                 | 0<br>1       | MCC #2 is odd parity mode MCC #2 is even parity mode                          |

| ED24                 | 0            | MCC #3 is odd parity mode MCC #3 is even parity mode                          |

| ED21<br>ED23<br>ED25 |              | Clear PEINT' for MCC #1<br>Clear PEINT' for MCC #2<br>Clear PEINT' for MCC #3 |

When a parity error is detected, the status register is frozen until read by an IOP status read. Parity defaults to odd parity at system reset. Normal mode parity is odd; special mode parity is even. A special I/O write to a memory bank causes bad parity to be written into memory until changed back to the normal default parity mode. This feature checks the parity checker and the parity-check interrupt to the IOP.

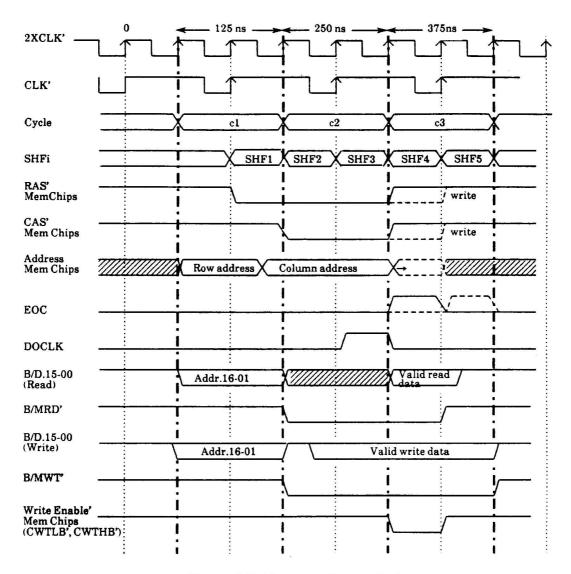

## 4.3.2 Memory Timing

Figure 4.7 illustrates typical processor timing.

Figure 4.7. Memory reference timing

The high order memory address must be valid on the address buses early enough that the proper bank is selected and address lines valid for RAS' (row address strobe). The row address bits are latched in the

DRAM by the RAS' signal. The CAS' (column address strobe) signal occurs 62 ns after the RAS' signal and latches the column address in the memory chips. Data becomes valid at the output of the chips at a maximum of 150 ns after RAS' or 75 ns after CAS', whichever is later.

To be written into memory, data must be supplied within two clocks from RAS'.

#### 4.3.3 Functions

Memory functions support full and nibble mode access as well as row and column addressing.

# 4.3.3.1 Full and Nibble Mode Access

The display port supports both full and nibble mode accesses. The full access cycle time is 312 ns; the page mode access time is 687 ns (Quadword). A nibble mode access occurs when the RAS"signal goes low and the CAS' signal cycles several times.

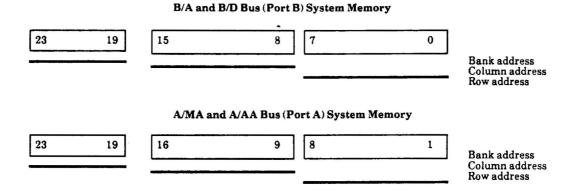

# 4.3.3.2 Row and Column Addressing

Figure 4.8 illustrates how row and column bits are derived from the port address bus.

Figure 4.8. Row and column addressing

.

4 - 14