# Dorado Hardware Marmal.

by E.R. Fiala

contributions to the manual by

R. Bates, D. Boggs, B. Lampson, K. Pier, and C. Thacker

other help by

- D. Clark, W. Crowther, W. Haugeland, G. McDaniel,

- S. Ornstein, and E. Taft

#### 3 October 1979

The document describes the architecture and hardware design of the Dorado comprises at a level appropriate for programming. At this time three prototype machines are being used for firmware and software development, and production has seemmenced for most hardware subsections.

This release of the manual is substantially revised from the 14 February 1979 release. There are new chapters on the Disk, Ethernet, and Display controllers and the Junk 10' chapter has been replaced by an 'Other IO and Event Counters' chapter. There are many other charges, particularly in the 'Memory Section' and 'Instruction Fetch Unit' chapters.

JA JE GO

Palo Alto Research Center Computer Sciences Latter story 3333 Coyote Hill Rd. Palo Alto California 94304)4

This document is for internal X-rox use only... \* -

# **Table of Contents**

| 1.   | Introduction                                  | 1   |

|------|-----------------------------------------------|-----|

| 2.   | Overview                                      | 2   |

| 2.1  | Control                                       | 2   |

| 2.2  | Data Paths                                    | 2   |

| 2.3  | Registers and Memories                        | 2   |

| 2.4  | Timing                                        | 5   |

| 2.5  | Instruction Fields                            | 7   |

| 2.6  | Notation                                      | 8   |

| 3.   | Processor Section                             | 9   |

| 3.1  | RM and STK Memories, Stkp and RBase Registers | ·   |

| 3.2  | Cnt Register                                  | 1.1 |

| 3.3  | Q Register                                    | 11  |

| 3.4  | T Register                                    | 11  |

| 3.5  | BSEL: B Multiplexor Select                    | 12  |

| 3.6  | ASEL: A Source/Destination Control            | 14  |

| 3.7  | ALUF, ALU Operations                          | 16  |

| 3.8  | LC: Load Control for RM and T                 | 18  |

| 3.9  | FF: Special Function                          | 18  |

| 3.10 | Multiply and Divide                           | 22  |

| 3.11 | Shifter                                       | 22  |

| 3.12 | Hold and Task Simulator                       | 24  |

| 4.   | Control Section                               | 25  |

| 4.1  | Tasks                                         | 25  |

| 4.2  | Task Switching                                | 25  |

| 4.3  | Next Address Generation                       | 26  |

| 4.4  | Conditional Branches                          | 28  |

| 4.5  | Subroutines and the Link Register             | 29  |

| 4.6  | Dispatches                                    | 30  |

| 4.7  | IFU Addressing                                | 31  |

| 4.8  | IM and TPC Access                             | 32  |

| 4.9  | Hold                                          | 33  |

| 4.8  | Program Control of the DMux                   | 33  |

| 5.   | Memory Section                                | 35  |

| 5.1  | Memory Addressing                             | 35  |

| 5.2  | Processor Memory References                   | 36  |

| 5.3  | IFIT References                               | 40  |

| 5.4  | Memory Timing and Hold                    | 40 |

|------|-------------------------------------------|----|

| 5.5  | The Map                                   | 43 |

| 5.6  | An Automatic Storage Management Algorithm | 47 |

| 5.7  | Mesa Map Primitives                       | 48 |

| 5.8  | The Pipe                                  | 50 |

| 5.9  | Faults and Errors                         | 52 |

| 5.10 | Storage                                   | 56 |

| 5.11 | The Cache                                 | 57 |

| 5.12 | Initialization                            | 58 |

| 5.13 | Testing                                   | 60 |

| 6.   | Instruction Fetch Unit                    | 63 |

| 6.1  | Overview of Operation                     | 63 |

| 6.2  | The IFUJump Entry Vector                  | 68 |

| 6.3  | Timing Summary                            | 69 |

| 6.4  | Use of MemBX and Duplicate Stk Regions    | 70 |

| 6.5  | Traps                                     | 71 |

| 6.6  | IFU Reset                                 | 73 |

| 6.7  | Rescheduling                              | 73 |

| 6.8  | Breakpoints                               | 74 |

| 6.9  | Reading and Writing IFUM                  | 75 |

| 6.10 | Continuing from Processor Faults          | 75 |

| 6.11 | IFU Testing                               | 77 |

| 6.12 | Details of Pipe Operation                 | 79 |

| 6.13 | Timing Details                            | 80 |

| 7.   | Slow IO                                   | 83 |

| 7.1  | Input/Output Functions                    | 83 |

| 7.2  | IO Opcodes                                | 84 |

| 7.3  | Wakeup, Block, and NEXT                   | 85 |

| 7.4  | SubTasks                                  | 86 |

| 7.5  | Illegal Things IO Tasks Must Not Do       | 86 |

| 8.   | Fast IO                                   | 87 |

| 8.1  | Transport                                 | 87 |

| 8.2  | Wakeups and Microcode                     | 87 |

| 8.3  | Latency                                   | 88 |

| 9.   | Disk Controller                           | 89 |

| 9.1  | Disk Addressing                           | 90 |

| 9.2  | Sector Layout Considerations              | 90 |

| 9.3  | General Firmware Organization             | 92 |

| 9.4  | Task Wakeups                              | 93 |

| 9.5  | Control Register                          | 94 |

| 9.6   | Format RAM                      | 94  |

|-------|---------------------------------|-----|

| 9.7   | Tag Register                    | 95  |

| 9.8   | FIFO Register                   | 97  |

| 9.9   | Muffler Input                   | 97  |

| 9.10  | Error Detection and Correction  | 99  |

| 10.   | Display Controller              | 104 |

| 10.1  | Operational Overview            | 104 |

| 10.2  | Video Data Path                 | 105 |

| 10.3  | Horizontal and Vertical Control | 107 |

| 10.4  | Pixel Clock System              | 110 |

| 10.5  | OIS Seven-Wire Video Interface  | 111 |

| 10.6  | Processor Task Management       | 112 |

| 10.7  | Slow IO Interface               | 114 |

| 10.8  | DDC Initialization Requirements | 116 |

| 10.9  | Speed and Resolution Limits     | 116 |

| 11.   | Ethernet Controller             | 118 |

| 11.1  | Ethernet Packets                | 118 |

| 11.2  | Controller Overview             | 119 |

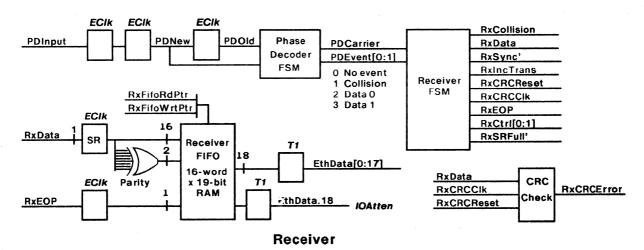

| 11.3  | Receiver                        | 121 |

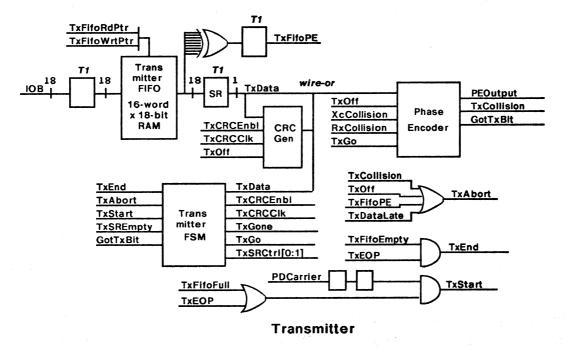

| 11.4  | Transmitter                     | 122 |

| 11.5  | Clocks                          | 123 |

| 11.6  | Task Wakeups                    | 123 |

| 11.7  | Muffler Input                   | 124 |

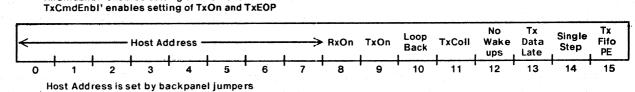

| 11.8  | IOB Registers                   | 125 |

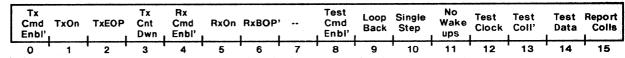

| 11.9  | Control Register                | 125 |

| 11.10 | Status Register                 | 126 |

| 12.   | Other IO and Event Counters     | 127 |

| 12.1  | Junk Task Wakeup                | 127 |

| 12.2  | General IO                      | 127 |

| 12.3  | Event Counters                  | 127 |

| 13.   | Error Handling                  | 130 |

| 13.1  | Processor Errors                | 131 |

| 13.2  | Control Section Errors          | 133 |

| 13.3  | IFU Errors                      | 133 |

| 13.4  | Memory System Errors            | 133 |

| 13.5  | Sources of Failure              | 134 |

| 13.6  | Error Correction                | 134 |

| 14.   | Performance Issues              | 138 |

| 14.1  | General Performance Issues      | 138 |

| 15.  | Glossarv                                | 143 |

|------|-----------------------------------------|-----|

| 14.4 | Cache and Storage Geometry              | 140 |

| 14.3 | Performance Degradation Due to IO Tasks | 139 |

| 14.2 | Cache Efficiency and Miss Wait          | 139 |

# List of Tables

| 1.  | Memories                                | 3    |

|-----|-----------------------------------------|------|

| 2.  | Registers                               | 4    |

| 3.  | Load Timing                             | 6    |

| 4.  | Instruction Fields                      | 7    |

| 5.  | RSTK Decodes for Stack Operations       | 10   |

| 6.  | BSEL Decodes                            | 12   |

| 7.  | ASEL Decodes                            | . 14 |

| 8.  | ALUFM Control Values                    | 16   |

| 9.  | LC Decodes                              | 18   |

| 10. | FF Decodes                              | 19   |

| 11. | ALUF Shift Decodes                      | 23   |

| 12. | Branch Conditions                       | 28   |

| 13. | Reserved Locations in the Microstore    | 32   |

| 14. | Timing of a Dirty Miss                  | 43   |

| 15. | Map Configurations                      | 44   |

| 16. | Fault Indications                       | 53   |

| 17. | IFUM Fields                             | 64   |

| 18. | Operand Sequence for +Id                | 65   |

| 19. | IFU FF Decodes                          | 67   |

| 20. | IO Register Addresses                   | 83   |

| 21. | Task Assignments                        | 84   |

| 22. | T-80 Specifications and Characteristics | 92   |

| 23. | PClock vs. Pixel Clock Period           | 110  |

| 24. | OIS Terminal Microcomputer Messages     | 112  |

| 25. | DDC Muffler Signals                     | 115  |

| 26. | Ethernet Muffler Signals                | 124  |

| 27. | Error-Related Signals                   | 131  |

| 28. | Double Error Incidence vs. Repair Rate  | 137  |

| 29. | Utilization of the Microstore           | 138  |

| 30. | Execution Time vs. Cache Efficiency     | 139  |

| 31. | Cache Geometry vs. LRU Behavior         | 142  |

# List of Figures

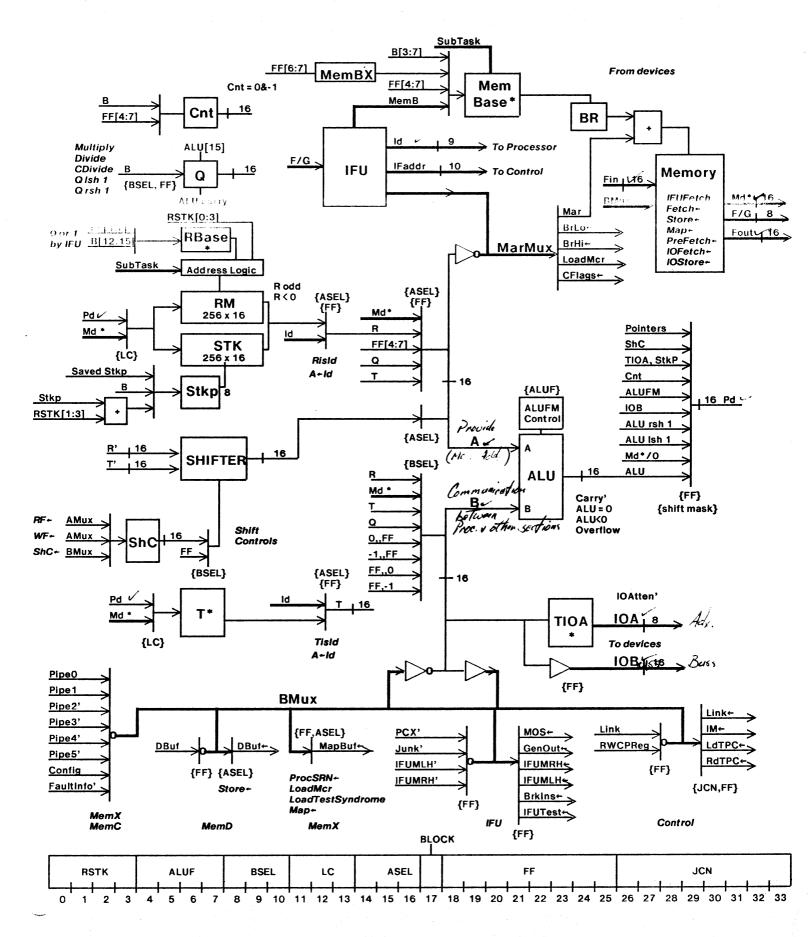

- 1. Dorado: Programmer's View

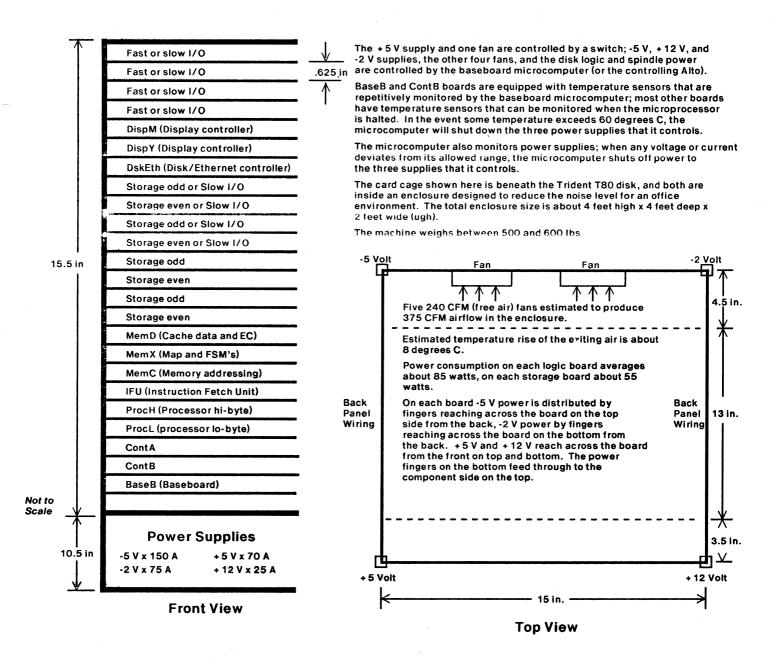

- 2. Card Cage

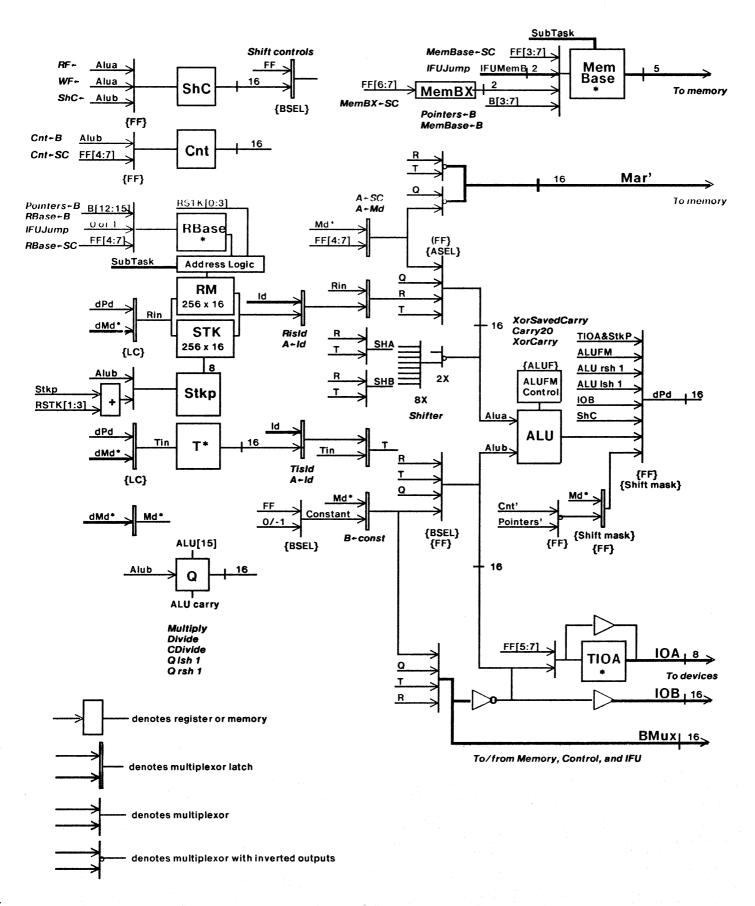

- 3. Processor Hardware View

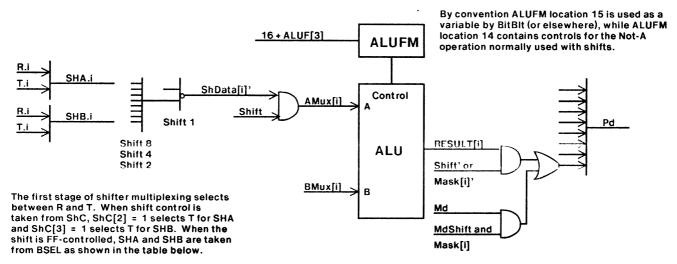

- 4. Shifter

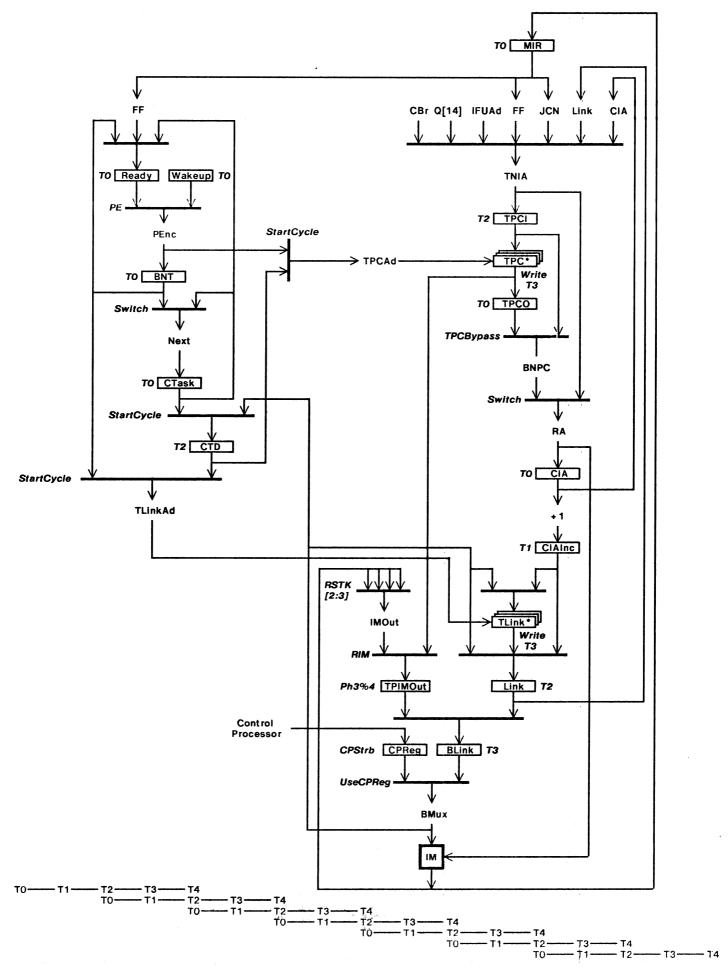

- 5. Control Section

- 6. Next Address Formation

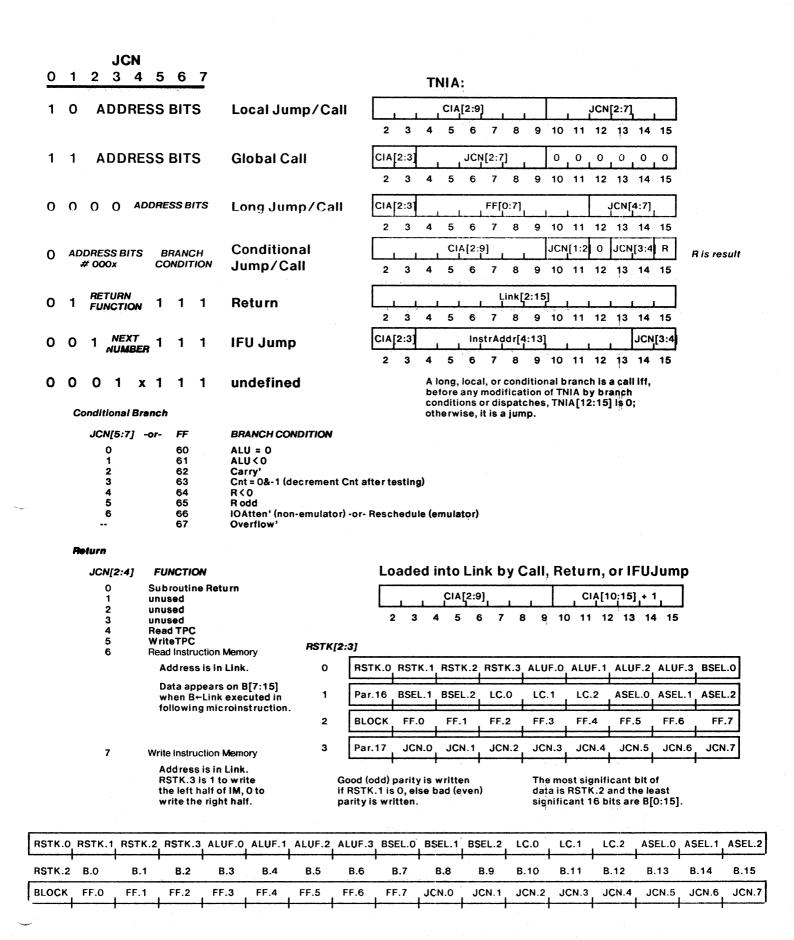

- 7. Instruction Timing

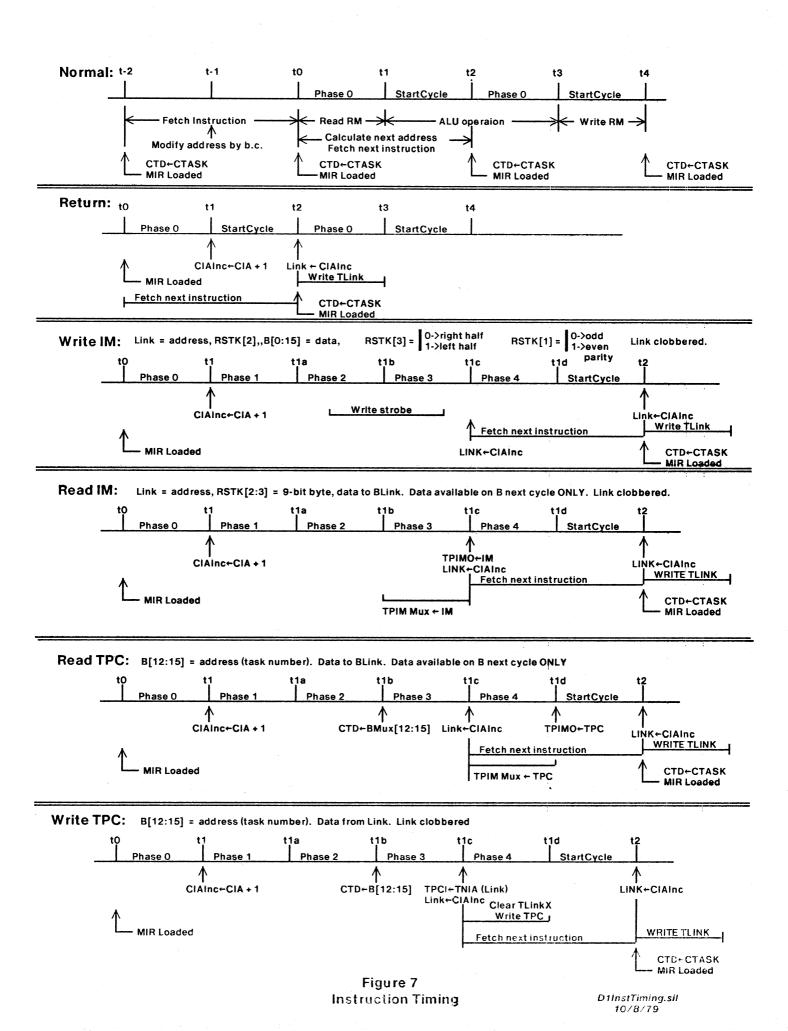

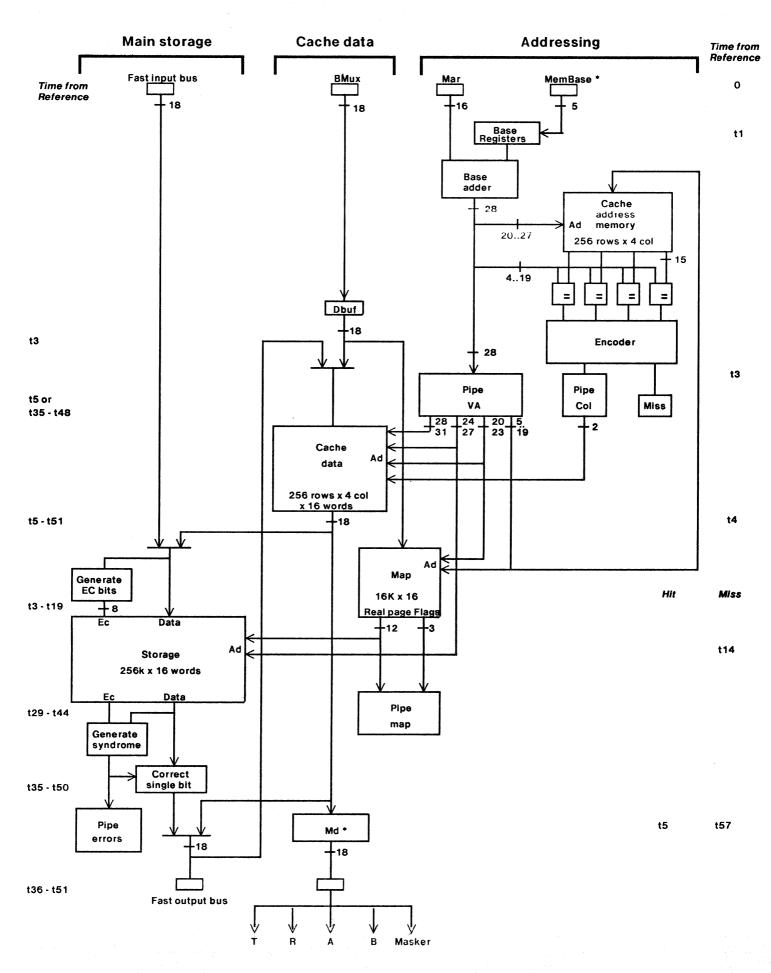

- 8. Overall Structure of the Memory System

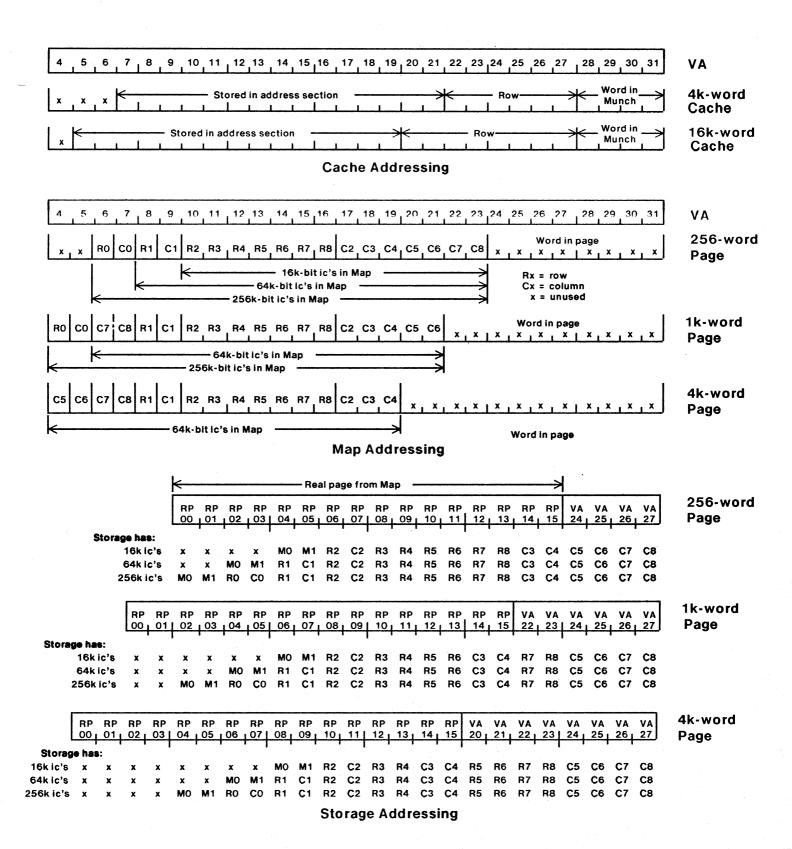

- 9. Cache, Map, and Storage Addressing

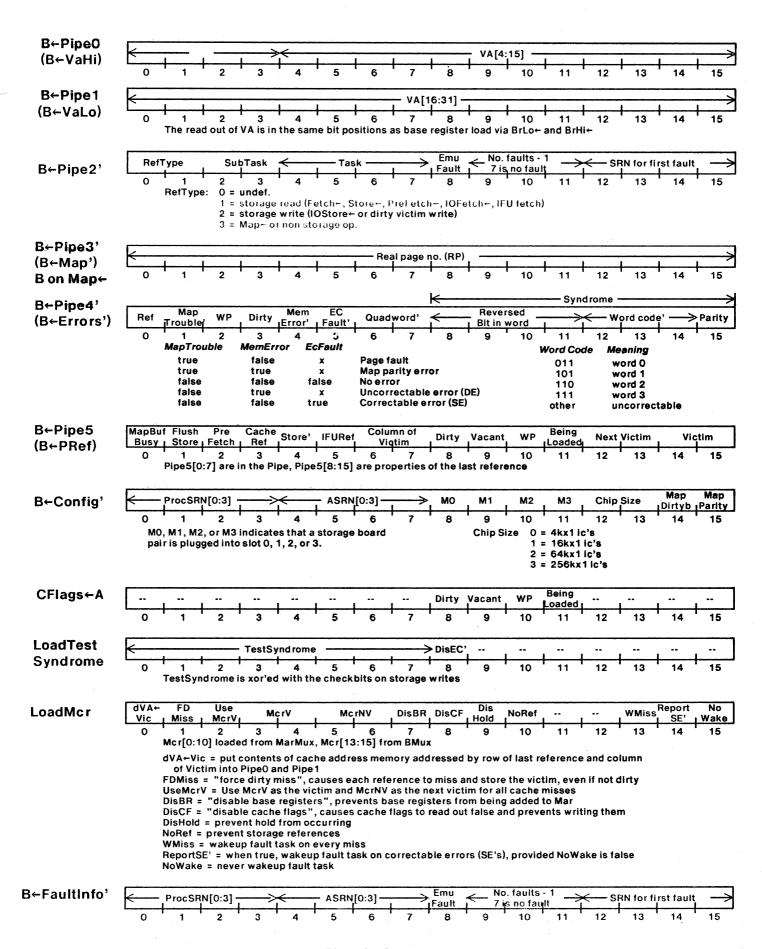

- 10. The Pipe and Other Memory Registers

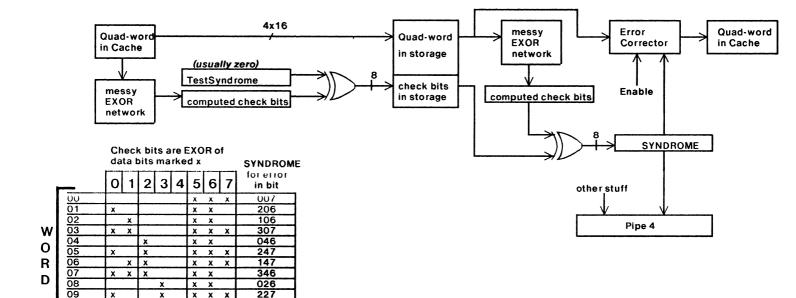

- 11. Error Correction

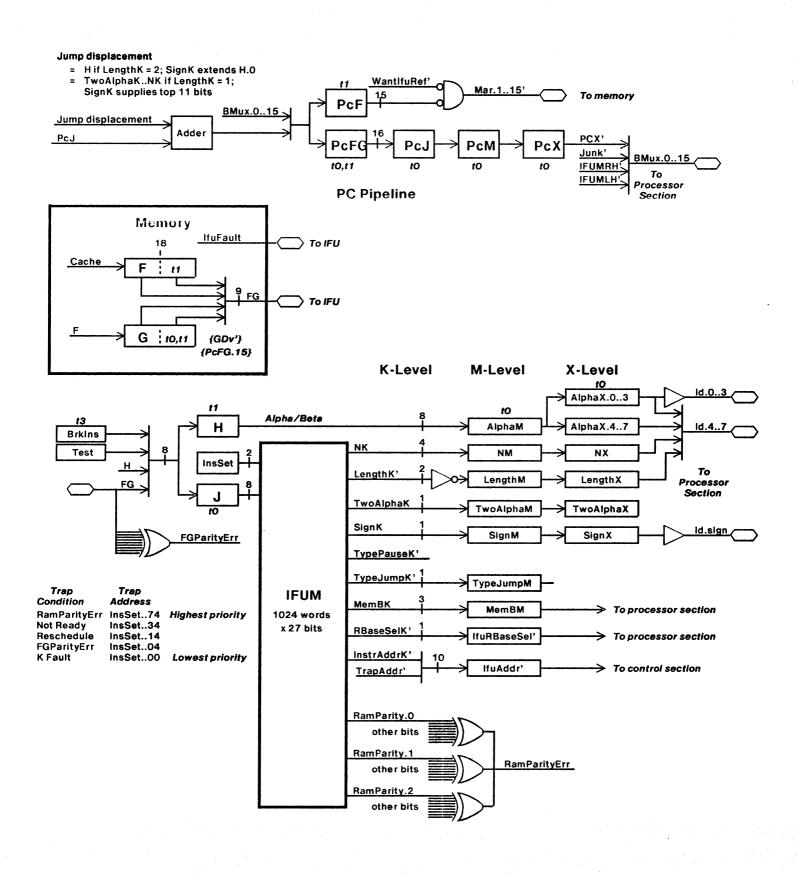

- 12. Instruction Fetch Unit Organization

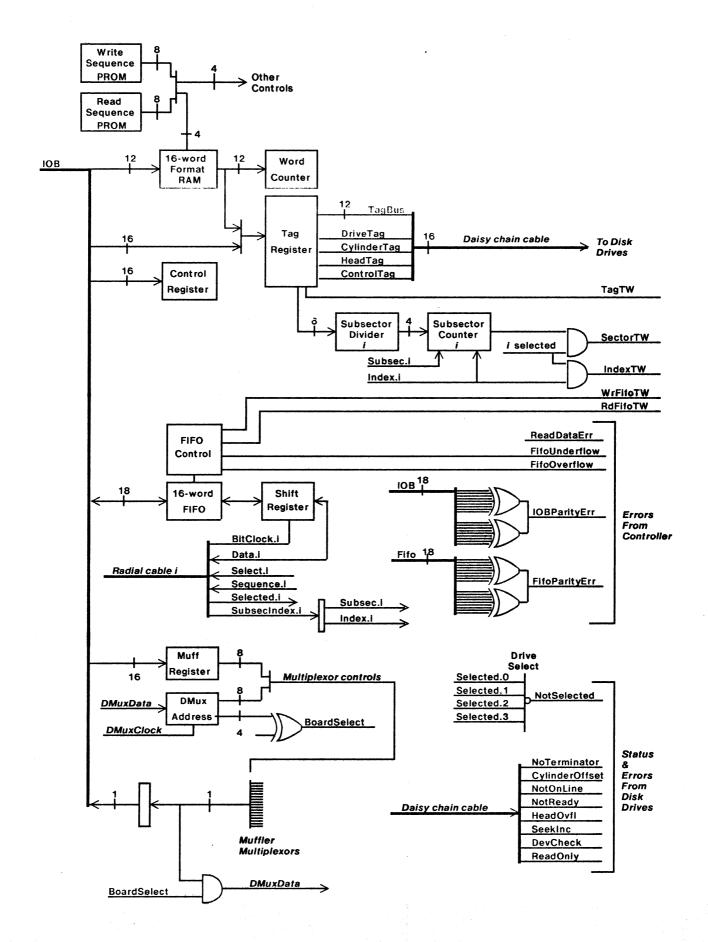

- 13. Disk Controller

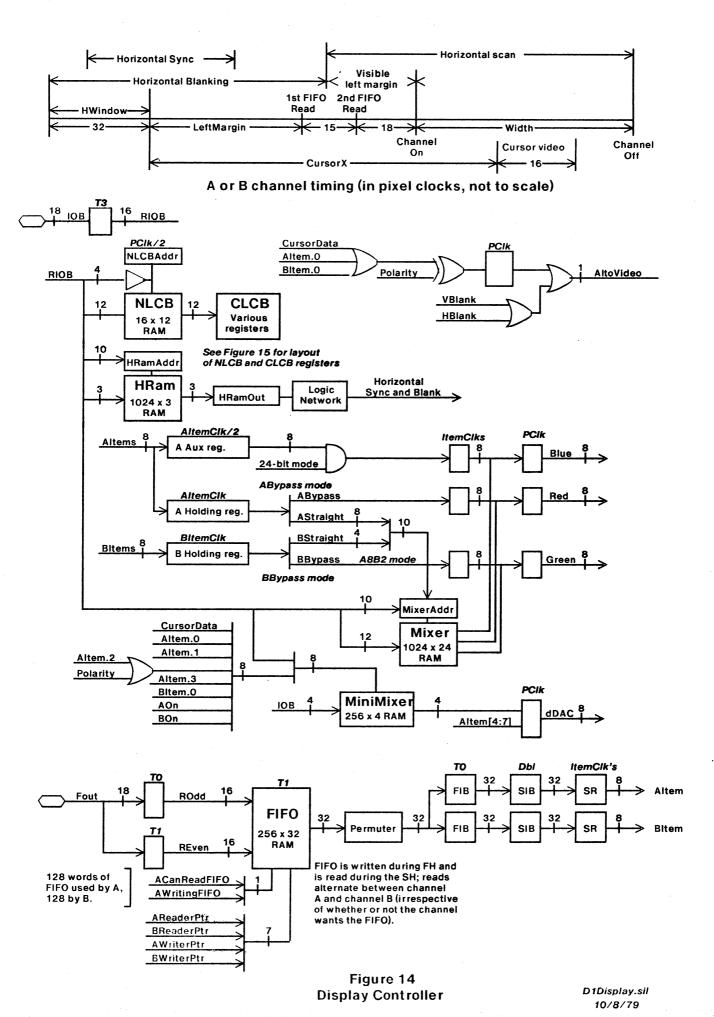

- 14. Display Controller

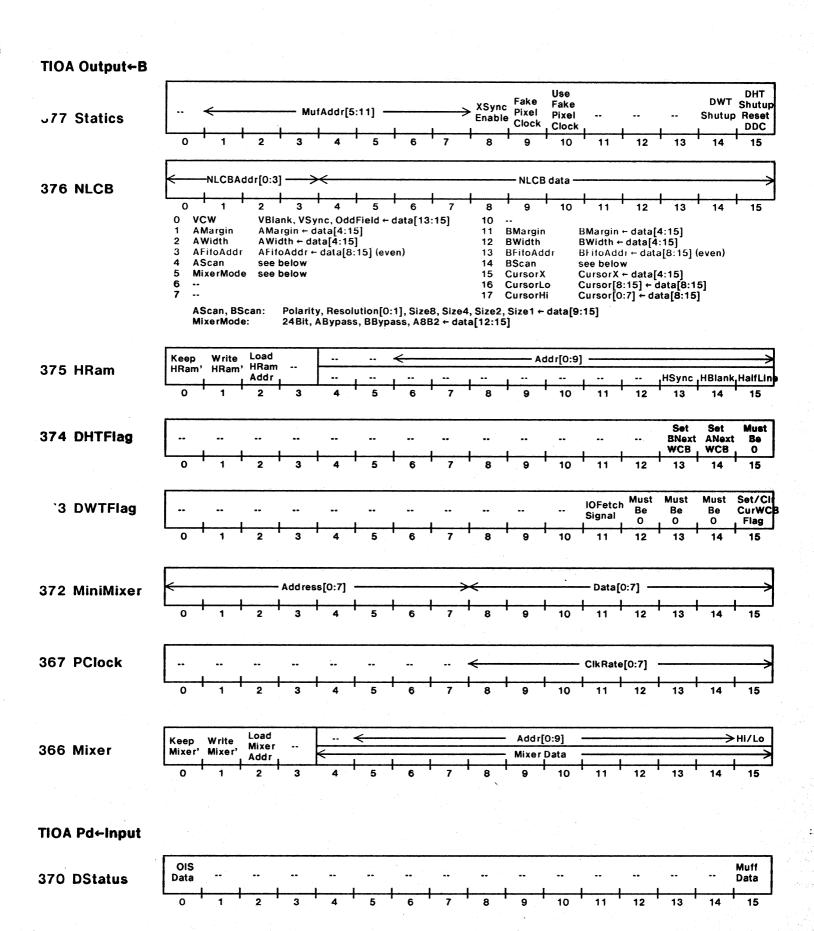

- 15. Display Controller IO Registers

- 16. Ethernet Controller

- 17. Programmers' Crib Sheet

# Introduction

Dorado is a high performance, medium cost microprogrammed computer designed primarily to implement a virtual machine for the Mesa language, as described in "The OIS Processor Principles of Operation," and to provide high storage bandwidth for picture-processing applications. Dorado aims more at word processing than at numerical applications.

The microprocessor has a nominal cycle time of 50 ns, and most Mesa opcodes will execute in one or two cycles; the overall average opcode execution time will be subject to a number of considerations discussed later. Dorado will also achieve respectable performance when implementing virtual machines for the Alto, Interlisp, and Smalltalk programming systems, although simple instructions for these run three to five times slower than Mesa.

Dorado is implemented primarily of MECL-10K integrated circuits; storage boards use MOS and Schottky-TTL components primarily. Backplanes and storage boards are printed circuits; other logic boards are stitchweld in the prototypes and will be multiwire in the production machines. The mainframe is divided into sections called Control, Processor, Instruction Fetch Unit (IFU), and Memory, and peripheral control is accomplished by the Disk, Ethernet, and Display Controller sections, as discussed in chapters of this manual. The main data paths, shown in Figure 1, are 16-bits wide (the word size). The control section is shown in Figure 5. The Baseboard section, used to control the mainframe, is discussed in the "Dorado Debugging Interface" document.

The processor is organized around an Arithmetic and Logic Unit (ALU) whose two inputs are the A and B data paths (Figure 1), and whose output is normally routed to the Pd data path. Inputs to A, B, and Pd include all registers accessible to the programmer. In addition, 16-bit literal constants can be generated on B. B appears on the backplane for communication with the IFU, Control, and Memory sections.

The processor also includes a 32-bit in/16-bit out shifter-masker optimized for field insertion and extraction and with specialized paths for the bit-boundary block transfer (BitBlt) instruction.

An instruction fetch unit (the IFU) operating in parallel with the processor can handle up to four instruction sets with 256 opcodes each.

Emulator and IFU references to main memory are made through a 4k-word high-speed cache. Main storage can be configured in various sizes up to a maximum of 2<sup>20</sup> 16-bit words (i.e., 1,048,576 words) or eventually up to 222 16-bit words when 64k x 1 RAM's become available.

The processor initiates data transfers between main memory and fast input/output devices. 16 16-bit words are then transmitted without disturbing the main data paths of the microprocessor in about 1.4 µs (28 cycles). New requests can be initiated every 8 cycles, so total bandwidth of the memory, 640 mHz, is available for devices with enough buffering.

# Overview

#### Control

Dorado supports up to 16 independent tasks at the microcode level. Each task has its own program counter (TPC), and other commonly-used registers are also replicated on a pertask basis. Tasks are scheduled automatically by the hardware in response to wakeup requests, where task 15 is highest priority, task 0, lowest.

Emulator microcode runs entirely in task 0 (lowest priority); fault conditions normally wakeup task 15, the "fault task" (highest priority). Other tasks are normally paired with io devices that issue wakeup requests when they need service. Task switching, discussed in "Control Section", is in most cases invisible to the programmer, because commonly-used registers are duplicated for each task.

Read the following with Figure 1 in front of you.

#### **Data Paths**

Primary registers and data paths in Dorado are shown in Figure 1. The main data paths are A, B, Pd ("processor data"), Md ("memory data"), Id ("IFU data"), IOA ("io address"), IOB ("io bus"), Fin ("fast input bus"), and Fout ("fast output bus").

"A" is used to supply memory addresses (via the Mar bus on the backplane) and as an ALU input. Several registers inside the processor section source A or receive A as an input, and Id (IFU section) sources A.

B is the other ALU input. B appears on the backplane for communication between the processor and other sections of Dorado. There are numerous external sources and destinations; most internal processor registers load from and source B.

The Pd path has the ALU, IOB, and several seldom-read registers inside the processor as sources; T and RM/STK are its destinations. The ALU input to this path can be shifted left or right one by various functions. Shift-and-mask operations replace any ALU field by zeroes or Md.

The TIOA register sources IOA on the backplane.

Fin and Fout are used for high bandwidth transfers between storage and io devices. Among standard peripherals, only the display controller uses the fast io system (Fout).

# Registers and Memories

Tables 1 and 2 describe registers and memories available to the programmer.

### **Table 1: Memories**

#### **Memory Comments**

IM is a 4096-word x 34-bit (+2 parity) RAM used to store instructions. When written, the address is taken from Link and data from B 16 bits at-a-time (1 extra bit and parity from RSTK field). When read, the address is taken from Link, and data is delivered to Link 9 bits at-a-time. The read or write is controlled by the JCN field and two or three low bits of RSTK.

ALUFM is a 16-word x 6-bit ALU control RAM addressed by the 4-bit ALUF field. Five ALUFM bits specify 16 boolean or 5 arithmetic operations on A and B. One bit is the input carry for arithmetic operations (modifiable by several functions). ALUFM[ALUF] is read onto Pd by the ALUFMEM function or both read onto Pd and loaded from B by the ALUFMRW+ function.

RM is a 256-word x 16-bit (+2 parity) RAM used for general storage by all tasks. The normal address is RBase[0:3], RSTK[0:3]. Data can be read onto A or B and loaded from Pd or Md without using FF. Together with T, RM forms the input to the Shifter.

STK is a 256-word x 16-bit (+2 parity) stack accessible only to the emulator, used instead of RM when the BLOCK bit in the instruction is 1. Its address comes from StkP, modified by -4 to +3 under control of RSTK.

IFUM is a 1024-word x 24-bit (+3 parity) decoding memory containing 256 words for each of four instruction sets. The instruction set can be set by the InsSetOrEvent← function. The low 8 address bits are normally an opcode fetched from the cache, but can be loaded from B by the BrkIns← function to read or write IFUM itself. The IFUMLH← and IFUMRH← functions load, and the B←IFUMLH' and B←IFUMRH' functions read different bits of IFUM. During normal operation IFUM controls decoding of the stream of opcodes and operands fetched from memory relative to BR 31, the code base.

Main storage consists of a 64-row x 4-column x 16-word virtual cache coupled with one to four 256k x 16-bit memory modules (using 16k-bit storage chips). The IFU and processor independently access the cache, with IFU references deferring to the processor. The processor has two dissimilar methods of reference, one primarily to the cache (with "misses" initiating main memory action) and one directly to main memory (invalidating cache hits on writes, using dirty cache hits on reads). Fetch←, Store←, IFetch←, LongFetch←, and PreFetch← are cache references. Md can be loaded into T or RM (LC field), routed onto B (BSEL field), onto A (FF field), or used in a shift-and-mask operation (ASEL and ALUF fields). IOFetch← and IOStore← (ASEL field) initiate a 16-word transfer between an io device and memory without further processor interaction (using Fin or Fout bus). Virtual addresses are transformed to absolute using the Map memory. All references leave information in the Pipe memory.

BR A 32-word x 28-bit base register memory addressed by the MemBase register. The virtual address for any memory reference is BR[MemBase] + Mar. BR is loaded from Mar by the BrLo+ and BrHi+ functions and can be read indirectly onto B via the virtual address left in the Pipe after a memory reference (Pipe0 and Pipe1 functions).

Pipe The 16-entry x 6-word pipe contains trace information left by memory references. This information includes the virtual address, map stuff, single-error and double-error information, cache control stuff, task and subtask. It is automatically loaded during any memory reference and can be read onto B by the Pipe0, Pipe1, ..., Pipe5' functions.

Map The Map is a 16k-word x 19-bit (+parity) memory used to transform virtual addesses to absolute. Addressed by VA[10:23], map entries contain 16 bits of real page, write protect, dirty, and referenced bits. They can be written from B with Map← (ASEL) and read from the Pipe after main storage references.

### Table 2: Registers

# Register Comments \* = task specific

- T\* 16-bit (+2 parity) T sources either A (ASEL field or FA field with memory ops) or B (BSEL field), or the Shifter (ASEL) and loads from either Pd or Md (LC field).

- RBase\* 4-bit RBase,,RSTK field forms addresses for RM. RBase can be loaded from FF[4:7] or from B[12:15] by the RBase+SC, RBase+B, or Pointers+B functions; it is read onto Pd[12:15] by the Pd+Pointers function. RBase is loaded with 0 or 1 when the IFU dispatches to the first instruction for an opcode.

- The emulator uses STK instead of RM when the BLOCK bit is 1. 8-bit StkP holds the address for STK. The RSTK field is interpreted as an adjustment to StkP, which can be modified -4 to +3 in conjunction with testing for overflow and underflow. This mechanism implements the Mesa evaluation stack. StkP can be loaded by the StkP+B function and read onto Pd[8:15] by the +TIOA&StkP function (Stack overflow and underflow indicators are read into Pd[8:9] by the Pd+Pointers function.).

- Q 16-bit Q is used as a shift register by multiply and divide. Q can be read onto A (FF field or FA with Fetch+ or Store+) or B (BSEL field) and loaded from any B source except a constant (BSEL and FF fields). Functions implement Q lsh 1 and Q rsh 1.

- Cnt is a 16-bit counter that can be both decremented and tested for zero by a branch condition.

Cnt can be loaded from FF[4:7] with 1 to 16 or from B (FF field) and can be read onto Pd (FF).

- TIOA\* TIOA is an 8-bit io address register (see "Slow IO") loaded by the TIOA+B function and read onto Pd[0:7] with the Pd+TIOA&StkP function. TIOA[5:7] may also be loaded from FF[5:7].

- ShC 16-bit ShC controls the shifter-masker (see "Shifter"). RF←A, WF←A, and ShC←B functions load ShC in various ways. ShC can be read onto Pd by the Pd←ShC function.

- MemBase\* MemBase is a 5-bit register addressing BR for memory references. The MemBase+n functions load it from FF[3:7]; the MemBaseX+n functions load it from 0,,MemBX[0:1],,FF[6:7]. The IFU loads MemBase with a value between 0 and 3 relative to MemBX or with 34 to 37, as specified in IFUM, prior to executing the first instruction of an opcode. MemBase is read onto Pd[3:7] by the Pd+Pointers function and loaded from B[3:7] by the Pointers+B and MemBase+B functions.

- MemBX is a 2-bit register used like a stack pointer in conjunction with MemBase. The ideas behind this are discussed in "Memory Section".

- Link\* 16-bit Link holds subroutine return addresses, address-modification for dispatches, IM address for IM reads/writes, and data for TPC reads/writes. It can be read onto or loaded from B[0:15] by the B+Link or Link+B, BigBDispatch+B, or BDispatch+B functions, or from CIA+1 by CALLs and RETURNs.

- PC 16-bit PC contains the byte displacement of the next opcode relative to BR 31, the code base. The IFU maintains this register, so only conditional jumps that don't jump and opcodes of type "pause" have to load it with the PCF+B function. The B+PCX' function reads PC.

- TPC \* TPC contains the address of the next instruction for each task. It is addressed from B[12:15] and read/write control is in JCN. Data is read from/written into Link under control of the JCN field of the instruction.

- Mcr Memory control register--disables parts of memory system for initialization and checkout.

### **Timing**

The terminology used in discussing timing is as follows:

clock The 25 ns (nominal) atomic time period of the machine.

cycle The duration of instructions--two clocks or 50 ns except for instructions that read/write IM or TPC.

t<sub>0</sub> The instant at which MIR (MicroInstruction Register) is loaded--the beginning of a cycle.

$t_1$  The next instant after  $t_0$ --always one clock later.

$t_2$  The instant following  $t_1$ -one clock after  $t_1$  except for instructions that read/write IM or TPC. Additional clocks intervening for these special cases, which only affect the control section, are denoted by  $t_{1a}$ ,  $t_{1b}$ , etc.

$t_3$ ,  $t_4$  Subsequent instants for a instruction.  $t_3$  of the previous instruction coincides with  $t_1$  of the current instruction;  $t_4$  with  $t_2$ .

First half cycle

The interval from  $t_0$  to  $t_1$  (or  $t_2$  to  $t_3$ ).

Second half cycle

The interval from  $t_1$  to  $t_2$  (or  $t_3$  to  $t_4$ ).

As implied by this terminology, Dorado initiates a new instruction every cycle. Instructions are pipelined, requiring a total of three cycles for execution. Timing for a typical instruction is shown in Figure 7. At  $t_{.2}$ , the next instruction address is determined and instruction fetch from IM begins; at  $t_{0}$ , the instruction is loaded into MIR from IM. During the first half cycle, the selected register is read from RM or STK, and at  $t_{1}$  is loaded into a register. During the next two clocks ( $t_{1}$ - $t_{3}$ ), addition is performed in the ALU; at  $t_{3}$  the result is loaded into a register for writing into RM/STK or T. During the final clock, RM is written.

Since a new instruction begins before the previous one finishes, paths exist to bypass the register being written if the following instruction specifies it as a source (These paths, inaccessible to the programmer, are not shown in Figure 1).

Most registers load from B at  $t_3$  (i.e., at the mid-clock of the cycle following the load instruction). These may source B in the instruction after they are loaded. The load information and data are pipelined into the next cycle, as described above. Registers loaded at  $t_2$  may be used during the first half-cycle of the following instruction. Usually, this type of register is used for some type of control information, since control registers are normally clocked at  $t_0$  (=  $t_2$  of previous instruction), data-oriented registers at  $t_1$  ( $t_3$  of previous instruction).

Table 3 summarizes the time at which loading takes place and some other information.

Table 3: Load Timing

| Register/    | Task     | Load       | Data             | Load      | Comment                                            |

|--------------|----------|------------|------------------|-----------|----------------------------------------------------|

| Memory       | Specific | Time       | Source           | Control   |                                                    |

| MID*         |          | <b>+</b> 0 | 18.4             | ION       | Microinstriction                                   |

| MIR*         | no       | t0         | IM<br>TNIA DNDC  | JCN       | Microinstruction                                   |

| CIA          | no       | t0         | TNIA,BNPC        | JCN       | Microinstruction address                           |

| ClAinc*      | no       | t1         | CIA              |           |                                                    |

| TPCI*        | no       | t2         | TNIA, CIA        |           |                                                    |

| TPC          | yes      | FHC        | TPCI             | HOLD      | B 11 / 11                                          |

|              |          | t2         | LINK(??)         | JCN,B     | Reading/writing takes 3 cycles                     |

| Link         | yes      | t2         | В                | FF        | Also loaded by CALL, RETURN, and                   |

|              |          |            | _                | 1011      | dispatchesreadout valid t1 to t3                   |

| IM           | no       |            | В                | JCN       | Reading/writing require 3 cycles                   |

| CTASK        | no       | t0         | Next             | Switch    | Current task                                       |

| CTD          | no       | t1         | CTASK            | ·-        | Current task delayed                               |

| Ready        | no       | t0         | PEnc             | Switch    | Task-ready flipflops                               |

| StkP         | no       | t2         | В                | FF        | New value read if it changes in the                |

|              |          |            |                  |           | same instruction                                   |

| RBase        | yes      | t2         | F2               | F1        | RAM writte at t3, bypassed                         |

| Cnt          | no       | t2         | F2               | F1        | Br cond to sub 1 and test                          |

|              |          |            | В                | FF        |                                                    |

| ALUFM        | no       | t2         | В                | FF        | Addressed by ALUF                                  |

|              |          |            |                  |           | The output is valid t1 to t3                       |

| TIOA         | yes      | t2         | В                | FF        | Readout valid till t3                              |

| MemBX        | no       | t2         | F2               | F1        | Readout valid till t3                              |

| MemBase      | yes      | t2         | F2               | F1        | Readout valid till t3                              |

|              |          |            | MemBase xor 1    | FF        |                                                    |

| ShC          | no       | t3         | A,B              | FF        | RF+A, WF+A, ShC+B                                  |

|              |          | t1         | FF               | ASEL,BSEL |                                                    |

| Q            | no       | t3         | В                | FF,BSEL   |                                                    |

|              |          | t3         | ALU[15],,Q[0:14] | FF        | Multiply                                           |

|              |          | t3         | Q[1:15],,ALUcry  | FF        | Divide                                             |

|              |          | t3         | Q                | FF        | Q rsh 1, Q Ish 1                                   |

| RM           | no       | SHC        | Pd,Md            | LC,RSTK   | Bypassed                                           |

| STK          | no       | SHC        | Pd,Md            | LC,RSTK   | Bypassed                                           |

| Т            | yes      | SHC        | Pd,Md            | LC,FF     | Bypassed                                           |

| IFUM         | no       | SHC        | В                | FF        | IFUMLH+/IFUMRH+                                    |

| Brkins       | no       | t2         | В                | FF        |                                                    |

| PC*          | no       | t3         | В                | FF        | Level F PC loaded, level X read                    |

| Br           | no       | t2         | A                | FF        | BrLo←/BrHi←, ←Pipe0, ←Pipe1                        |

| MapBuf*      | no       | FHC        | В                | ASEL, FA  | Written on Map←, TestSyndrome←,                    |

|              |          |            | _                | ,         | ProcSRN←, LoadMcr                                  |

| DBuf         | no       | FHC        | В                | ASEL, FA  | Written on Store←                                  |

| Md           | yes      | t5         | cache            |           | Bypassed                                           |

| CFlags       | no       | t2         | Mar              | FF        | For debugging, initialization                      |

| Mcr          | no       | t3         | Mar, MapBuf      | FF        | For debugging, initialization                      |

| Asrn         | no       | t2         | Asrn             | ••        | Addresses the pipe for ring refs                   |

| ProcSRN      | no       | t3         | MapBuf           | FF        | Addresses the pipe for Pipe0 to Pipe5              |

| TestSyndrome |          | t3         | MapBuf           | FF        | For debugging error correction                     |

| Pipe0        | no       | t3         | Br, etc.         | ASEL, FA  | Written on ref., B←Pipe0                           |

| Pipe1        | no       | t3         | Br, etc.         | ASEL, FA  | Written on ref., B←Pipe1                           |

| Pipe2        |          | t3         | etc.             | ASEL, FA  | Written on ref., B←Pipe2                           |

| Pipe3        | no       | t14        |                  | ASEL, FA  | Valid after any storage access or Map←             |

| •            | no       |            | map<br>map EC    |           | Valid after any storage access of Map <sup>4</sup> |

| Pipe4        | no       | t14,t48    | map, EC          | ASEL, FA  |                                                    |

| Pipe5        | no       | t3,t4      | cache            | ASEL, FA  | Written on ref., B←Pipe5                           |

<sup>\*</sup>Cannot be read as data by the processor

#### Instruction Fields

The 34-bit instruction is divided into the following fields:

**Table 4: Instruction Fields**

| Field | Size    | Purpose (may have other effects, described below)                                     |

|-------|---------|---------------------------------------------------------------------------------------|

| RSTK  | 4 bits  | Selects RM register to be read and/or written                                         |

| ALUF  | 4 bits  | Selects ALU function or shifter operation                                             |

| BSEL  | 3 bits  | Selects source for B                                                                  |

| LC    | 3 bits  | Controls source and loading of RM and T                                               |

| ASEL  | 3 bits  | Source/destination control for A                                                      |

| BLOCK | 1 bit   | Blocks io task unless wakeup is waiting<br>Selects stack operations for emulator task |

| FF    | 8 bits  | Function $(FA = FF[0:1], FB = FF[2:4], FC = FF[5:7])$                                 |

| JCN   | 8 bits  | Jump control                                                                          |

| P016  | 1 bit   | Odd parity on first word of instruction                                               |

| P1733 | 1 bit   | Odd parity on second word of instruction                                              |

| Total | 34 bits | + 2 parity                                                                            |

The above instruction layout emphasizes compactness at the expense of programming flexibility. The following comments explain some of these tradeoffs

- 1. The RSTK field specifies only four of the eight address bits needed for addressing RM. The other four are taken from the RBase register (loaded by a function). In the emulator task, BLOCK causes STK to be used instead of RM, and RSTK is decoded to cause modifications of StkP.

- 2. ALUF addresses the 16-word ALUFM memory in which 16 of 26-odd useful ALU operations are stored. For the shift operation decode of ASEL, the first three bits of ALUF select the kind of shift, while the ALUFM address is forced to 14 or 15.

- 3. BSEL decodes the most common data sources for B. Less common B sources are selected by FF, and then BSEL encodes one of several destinations for the source.

- 4. ASEL specifies the source and destination for A. The default source is the RM address selected by RSTK. Four ASEL decodes specify the most common memory operations, where the virtual address is BR[MemBase] + A. These decodes consume the two leading bits of FF to specify alternate sources (T or Id) or less frequent memory operations. The remaining four ASEL decodes select alternate sources T, Id, or the shifter, where the shifter decodes work in combination with ALUF, as discussed later.

- 5. LC specifies loading of RM/STK and T from Pd and Md.

- 6. FF is the catch-all field in which operations or data not otherwise specifiable can be encoded. Operations encoded in FF are called "functions". There are five ways FF is used:

- a. To extend the branch address encoded in JCN (long goto, long call).

- b. To form a constant on B as selected by BSEL.

- c. To specify one of 64 common functions and branch conditions while the two leading bits modify the memory reference operation specified in ASEL.

- d. To specify one of 256 functions and branch conditions, some of which use low bits of FF as literal values.

- e. As a shift control value when ASEL decodes to "shift" and BSEL to a constant.

When FF is used as a function, it sometimes modifies the interpretation of other fields in the instruction. For example:

- a. 16 FF decodes modify RM write address bits which would otherwise have come from RSTK or StkP.

- b. 16 FF decodes modify RM write-address bits which would otherwise come from RBase.

- c. 16 FF decodes select less common B sources, causing BSEL to encode a destination rather than a source for B.

- 7. JCN (in conjunction with current address) encodes the next instruction address as follows:

- a. One of 64 global Calls.

- b. One of 60 local Gotos.

- c. One of 4 local Calls.

- d. One of 14 local conditional branches with 7 branch conditions.

- e. One of 16 long Gotos/Calls (use FF field for rest of address).

- f. One of 4 IFU jumps for next opcode (high 10 address bits from IFU).

- g. Return.

- h. TPC read/write.

- i. IM read/write (Use low bits of RSTK also).

- 8. P0 and P1 are odd parity on the left and right halves of IM. When wrong, these give rise to error signals (see "Theory of Operations") which stop the machine after (unfortunately) the instruction with bad parity has been executed. The artifice of deliberately loading both parity bits incorrectly is used to implement breakpoints.

#### **Notation**

The notation used in referring to fields in the instruction is that the left-most bit of the field is denoted as 0. Hence, the fields in the instruction are as follows: RSTK[0:3], ALUF[0:3], BSEL[0:2], LC[0:2], ASEL[0:2], BLOCK[0], FF[0:7], JCN[0:7].

The BLOCK bit is also called StackSelect, for its use in choosing STK instead of RM for the emulator task.

# **Processor Section**

The processor section implements most registers accessible to the programmer and decodes all instruction fields except JCN. The FF field of the instruction is also decoded by the control, memory, IFU, and Junk sections.

Read this chapter with Figure 1 in front of you.

The processor section contains the Q, ShC, Cnt, StkP, and MemBX registers, the T, RBase, MemBase, and TIOA task-specific registers, and the ALUFM, RM, and STK memories. It contains the arithmetic and logic unit (ALU) and the shifter.

The processor communicates with the control, memory, and IFU sections via B; with io devices via the IOB bus. It exports MemBase and Mar to the memory system for addressing, IOA to devices for io addressing, and branch conditions to the control section. It imports Md from the memory system and Id from the IFU.

### RM and STK Memories, StkP and RBase Registers

The RM and STK memories each store 256 words x 16 data bits with odd parity on each byte of data. The STK memory is accessible only to the emulator. Either RM or STK is read at  $t_0$  and latched at  $t_1$ . Data may be routed to A, B, or the shifter, and branch conditions (see "Control") test the sign bit (R<0) and low bit (R odd). Either RM or STK may be written between  $t_3$  and  $t_4$  with data from Md or Pd.

The RM read address is RBase[0:3],,RSTK[0:3]. For io tasks SubTask[0:1] (discussed in "Slow IO") are or'ed with RBase[2:3]. Each task can thus select from 16 RM registers in the block pointed to by RBase.

Normally, this read address is also used for the write part of the instruction (if any). However, two groups of FF decodes discussed below modify the write address.

The RBase+SC function loads RBase with FF[4:7], selecting any block of 16 registers; RBase+B loads RBase from B[12:15]; Pointers+B loads RBase from B[12:15] while also loading MemBase from B[3:7] (Previous RBase value is used for both the read and write portions of the instruction.). The IFU initializes the emulator task's RBase to 0 or 1 before dispatching to the first instruction of an opcode.

In the emulator (task 0), if BLOCK (i.e., StackSelect) is 1, RM is disabled and STK used instead. STK is addressed by the 8-bit StkP register, and RSTK controls the adjustment of StkP; StkP may be decremented or incremented by any value between -4 and +3.

Unadjusted StkP is always the read address and normally the write address, but the ModStkPBeforeW FF decode forces adjusted StkP to be used for the write. STK is divided into four separate regions, each  $100_8$  words long. Valid addresses are 1 to  $77_8$  within each region. That is, StkP[0:1] select the region, stack overflow occurs at the onset of a instruction that would increment StkP[2:7] >  $77_8$ , and underflow occurs when location 0 is either read or written or when StkP[2:7] is decremented below 0.

StkP[2:7] are initialized to 0, denoting the empty stack. A push could do StkP+StkP+1 and

write in one instruction. A pop does StkP+StkP-1, and the item being popped off can be referenced in the same instruction if desired.

Table 5: RSTK Decodes for Stack Operations

```

RSTK[0]

0 = no underflow on StkP = 0 at start or end

1 = underflow when StkP originally 0 or finally 0.

RSTK[1:3]

Meaning

0

no StkP change

StkP+StkP+1

2

StkP+StkP+2

3

StkP+StkP+3

4

StkP+StkP-4

5

StkP+StkP-3

6

StkP+StkP-2

StkP+StkP-1

```

In other words, RSTK[1:3] treated as a signed number are added to StkP[2:7] (StkP[0:1] don't change.). In the emulator, an attempt to underflow or overflow the stack generates the signal StkError:

StkError generates HOLD and wakes up the fault task (task 15) to deal with the situation, so the instruction causing StkError has not been executed when the fault task runs. StkUnd and StkOvf are remembered in flipflops read by the Pd+Pointers function. These get cleared (i.e., recomputed) when the next stack operation is executed by the emulator. The fault task can read them to decide whether stack underflow or overflow action is necessary.

Interpretation of underflow: StkP eq 0 denotes the empty stack. A stack adjustment may occur either by itself or with a read or write stack reference. StkP originally equal 0 underflows if the top of stack is read or written; decrementing StkP below 0 is always an underflow error; StkP equal 0 after modification underflows iff writing at the modified address. Consequently, the assembler sets RSTK[0] equal 1 for a stack reference only when either reading STK and incrementing the pointer or writing at the modified address and decrementing the pointer.

In other words, the microassembler must tell the hardware when to make the StkP equal 0 underflow checks, and it must do this correctly when the ModStkPBeforeW FF decode is used.

StkP is saved at  $t_2$  of an instruction dispatched to by the IFU. The saved value may be reloaded into StkP at  $t_2$  by the RestoreStkP function.

The utility of RestoreStkP will not be known until we decide how to continue from map faults. It will only be useful if opcodes are restarted after servicing map faults. However, we are also arranging for the IFU state, branch conditions, etc. of an interrupted opcode to be readable and reproducible, so that it will be possible to simply continue from the instruction that faulted. RestoreStkP will be useless if the continue-method of restarting is adopted.

Two groups of FF decodes change the RM address for the write portion of an instruction.

The first group of 16 FF decodes forces the write address to come from RBase[0:3],,FF[4:7]. This allows different registers in the same group of 16 to be used for the read and write portions of the instruction, or allows STK[StkP] to be used for the read portion and any of the 16 registers pointed to by RBase in the write portion. Note: SubTask does not affect the write address for these functions.

The second group of 16 FF decodes forces the top four write address bits to come from FF[4:7]. The complete RM write address becomes FF[4:7], RSTK[0:3]. This allows an arbitrary RM address to be written without having to load RBase in a previous instruction. Alternatively, if the i'th register in a group of 16 is read from RM, it permits the i'th register in a different group of 16 to be written in the same instruction. In conjunction with a read of STK, RSTK[0:3] will encode the StkP modification, and whatever RM word this happens to point to will be written (Programmers will have to struggle to use this with a STK read.).

The Risld FF decode causes Id to be substituted for RM/STK in the A, B, or shifter multiplexing.

There are branch conditions to test R[0] (R<0) and R[15] (R odd). These branch conditions are unaffected by the Risld FF decode; actual data from RM/STK is tested.

# **Cnt Register**

The 16-bit Cnt register is provided for use as a loop counter. Since it is not task-specific, io tasks cannot conveniently use it.

Cnt can be decremented and tested for 0 by the Cnt = 0&-1 branch condition; loaded from B[0:15] or from small constants 1 to 16 (FF decodes), and read onto the Pd path (into T or RM/STK) by an FF decode.

#### **Q** Register

The 16-bit Q register is provided primarily for use as a shift register with multiply and divide, but will probably be used more widely by the emulator. Since it is not task-specific, io tasks cannot conveniently use it.

Q can be read onto B (BSEL) or onto A (FF); it can be loaded from B (FF) and when FF specifies an external B source in the memory, ifu, or control sections, it can also be loaded from B (BSEL). Q can be left-shifted or right-shifted one (bringing 0 into the vacant bit) by two FF decodes.

# T Register

The 16-bit T register is the primary register for data manipulation in the processor. Since it is task-specific io tasks do not have to save and restore it. T can be read onto B (BSEL) or A (ASEL); it can be loaded from Pd or Md (LC).

# **BSEL: B Multiplexor Select**

BSEL normally selects the source for B. However, when this selection is overruled by one of the FF decodes for external B sources (an assortment of stuff in the memory, IFU, and control sections), then BSEL may instead encode the destination for B. B sources that originate outside the processor are called "external". FF decodes for other B sources are discussed later (see "Special Function").

The sources selected by BSEL are:

**Table 6: BSEL Decodes**

| BSEL | Primary               | External     |

|------|-----------------------|--------------|

| 0    | Md<br>RM/STK          | <br>         |

| 2    | Т                     |              |

| 3    | Q                     | Q+B *        |

| 4    | 0,,FF                 | Inapplicable |

| 5    | 377 <sub>8</sub> ,,FF | Inapplicable |

| 6    | FF,,0                 | Inapplicable |

| 7    | FF,,377 <sub>8</sub>  | Inapplicable |

\*Note: BSEL decode for Q+B is needed in initializing Dorado from the baseboard or Alto. Because ALUFM contents may be unknown, and data from the Alto is transmitted via the B+Link FF decode, some other field is needed to encode a destination that can then be routed into ALUFM.

The values selected by BSEL = 4-7 are 16-bit constants obtained by concatenating the 8-bit FF field with zeroes or ones. When this is done, normal effects of functions are disabled, so primary and external BMux stuff doesn't apply. In conjunction with a shift operation on A, BSEL = 4 to 7 will cause the shifter controls to come directly from FF rather than from ShC as discussed in "Shifter"; the Q-register sources B when an FF-controlled shift is carried out.

The Tisld and Risld FF decodes may be used with the B←T or B←RM/STK BSEL decodes, respectively, to accomplish B←Id.

The "External" decode of BSEL applies with Link, DBuf, Pipe0-Pipe5, FaultInfo, PCX, DecLo, DecHi, and other functions that source B on the backpanel, as selected by the FF decode. For these external sources, BSEL is interpreted as the destination for B rather than the source.

Note: When the memory or control section sources the external B bus, it is *illegal* to execute A+B or A-B alu operations; these sources are not electrically stable soon enough to permit the extra 10 ns required for carry propagation. But: if you are sure carries will not propagate into the high 8 bits of ALU result, then the hardware is fast enough.

However: Arithmetic is permitted when the IFU sources the external B bus, provided the previous instruction was not one of the slow B sources from the memory or control sections. This permits (Id)-(PCX')-1, common in emulator microcode.

This implies that an io task must never block on an instruction that sources B from a slow external source.

#### Hardware Implementation

The processor's internal version of B, called Alub, is driven by a 4-input multiplexor when sourced from within the processor; in this case an identical multiplexor drives the external bus, called Bmux (High-true). When the B source is external, both of these multiplexors are disabled, and the backpanel Bmux (Low-true) is inverted through a gate onto Alub. The multiplexor arrangement is shown in Figure 3.

The IFU section is on/off of Bmux by t1+6 ns and the processor section is off by t1+7 ns, but the memory and control sections are not on/off until t1+16 ns; hence, a slow Bmux source in the previous instruction prevents Bmux from stabilizing until t1+16 ns of the current instruction, allowing insufficient time to propagate Bmux onto Alub and finish carry propagation. However, because Bmux is gated onto Alub, and the gate shuts off quickly, arithmetic on internal Alub sources is always permissible.

Bmux sources in this manual are given high or low true names that agree with the way signals appear on Alub. For external sources this is inverted with respect to the sense of these signals on Bmux. However, because external sources cannot feed external destinations (no way to encode this in an instruction), the signal inversion is invisible to programmers.

# ASEL: A Source/Destination Control

The AMux drives the A input to the ALU, and is the data source for the read-field (RF+) and write-field (WF+) methods of loading ShC. The shifter also drives A, in which case the AMux is usually disabled.

A copy of the AMux drives the backplane Mar bus on processor memory references. The IFU may also drive Mar, when the processor isn't using it.

The three-bit ASEL field controls the source and destination for A as follows:

Table 7a: ASEL Decodes When FF is ok\*

| ASEL | FF[0:1] | Meaning                                                         |

|------|---------|-----------------------------------------------------------------|

| 0    | 0       | PreFetch←RM/STK                                                 |

|      | 1       | Map+RM/STK (emulator or fault task) -or- IOFetch+RM (ic task)   |

|      | 2       | LongFetch+RM/STK                                                |

|      | 3       | Store+RM/STK                                                    |

| 1    | 0       | DummyRef ←RM/STK                                                |

|      | 1       | Flush+RM/STK (emulator or fault task) -or- IOStore+RM (io task) |

|      | 2       | IFetch+RM/STK                                                   |

|      | 3       | Fetch+RM/STK                                                    |

| 2    | 0       | Store+Md                                                        |

|      | 1       | Store+Id                                                        |

|      | 2       | Store+Q                                                         |

|      | 3       | Store+T                                                         |

| 3    | 0       | Fetch+Md                                                        |

|      | 1       | Fetch+Id                                                        |

|      | 2       | Fetch+Q                                                         |

|      | 3       | Fetch+T                                                         |

| 4    |         | A+RM/STK                                                        |

| 5    |         | A←ldsee "Instruction Fetch Unit"                                |

| 6    |         | A←T                                                             |

| 7    |         | Shift operationsee "Shifter" (uses ALUF)                        |

Table 7b: ASEL Decodes When FF is not ok\*

| ASEL | Meaning                                  |  |  |  |  |

|------|------------------------------------------|--|--|--|--|

| 0    | Store←RM/STK                             |  |  |  |  |

| 1    | Fetch+RM/STK                             |  |  |  |  |

| 2    | Store←T                                  |  |  |  |  |

| 3    | Fetch+T                                  |  |  |  |  |

| 4    | A+RM/STK                                 |  |  |  |  |

| 5    | A←ld                                     |  |  |  |  |

| 6    | A←T                                      |  |  |  |  |

| 7    | Shift operationsee "Shifter" (uses ALUF) |  |  |  |  |

|      |                                          |  |  |  |  |

<sup>\*</sup>FF is ok when not used in a long goto, long call, as a BSEL constant, or in an FF-controlled shift.

When FF is ok and ASEL = 0 to 3, the decoding of FF as a function is forced to be in the range 0 to 63. In other words, FF[0:1], stolen to modify the memory operation on A, do not participate in the FF decode. Hence, only functions 0 to 63 can be used in the same

instruction with a memory reference.

In the above tables, each instance where the source for A is RM/STK can be overruled by one of the 4 FF decodes for A sources or the FF decodes that put FF[4:7] on A. These FF decodes are illegal with the ASEL or ASEL-FF[0:1] values that select ld or T, and the source for A is undefined when this restriction is violated.

The notation "Fetch+A", "Store+A", etc. in the above table is compatible with the microlanguage. These routing expressions mean, for example, that the displacement originating on A is routed onto the Mar bus on the backplane, added to BR[MemBase] in the memory section and loaded into the memory address register. Then the Fetch, Store, etc. is started as detailed in "Memory Section".

ASEL does a pretty thorough job of encoding possible actions on A: Store← and Fetch← references take the address from RM/STK, T, Md, Id, or Q; other references take the address from RM/STK; LongFetch+ takes the low 16 bits of address from RM/STK and high 8 bits from B.

The FF field can be used to select any of the following sources:

FF[4:7] (small constant) RM/STK Q Т Md

These functions are illegal except on shifts (ASEL = 7) or when the source otherwise selected would be RM/STK (ASEL = 0, 1, or 4). On shifts these functions cause the A source to be wire-or'ed with the shifter output (otherwise the A source would be disabled); with references, these functions overrule RM/STK as the source.

#### Hardware Implementation

A is driven by a 4-input multiplexor as shown in Figure 3. A similar arrangement drives Mar, which is disabled except on memory references or when one of the 8 FF decodes that use Mar is executed; the IFU may use Mar when the processor does not. The 4-input multiplexors are usually disabled on shifts, which OR onto A independently.

However, the A multiplexor is not disabled when the source for A is encoded in FF, so it is possible to OR any A input except Id with the (complemented) shifter data--this is useful for BitBlt and other complicated uses of the shifter. Since shifter data on A is low-true, and since the normal ALU operation is NOT A on shifts, the effect of enabling both the shifter and the normal A multiplexor is [Shiftdata and not A].

# **ALUF, ALU Operations**

The 4-bit ALUF field controls the ALU operation. It addresses a RAM (ALUFM) containing control for the MC10181 ALU chips.

ALUFM is 8-bits wide, of which 6 bits are used. ALUFM[0] controls the carry-in for arithmetic ALU operations. It is a "don't care" for the 16 logical ALU operations. The XorSavedCarry function causes the saved carry-out of a previous operation to be xor'ed with this bit. The XorCarry function complements the value from ALUFM. ALUFM[3:7] select the ALU function performed as below. The carry-out (task-specific) changes whenever an arithmetic operation is performed in the ALU unless explicitly disabled by the FreezeBC function (freeze branch conditions).

The Carry20 function forces the bit 12 carry-in to one. Assuming that this carry-in would otherwise have been zero, then this function adds  $20_8$  to the (arithmetic) ALU output. Adding  $20_8$  is expected to be useful because the cache, fast input bus, and fast output bus deal with  $20_8$ -word munches.

The table below shows the logical and (useful) arithmetic ALU operations.

Table 8: ALUFM Control Values (Octal)

| Logic | al                      | Arith  | metic (No Carry) | Arithmetic      | (With Carry) |

|-------|-------------------------|--------|------------------|-----------------|--------------|

| *1    | NOT A                   | *0     | Α                | *0 A+1          |              |

| 3     | (NOT A) OR (NOT B)      | 6      | 2*A              | 6 2*A+1         |              |

| 5     | (NOT A) OR (B)          | *14    | A+B              | *14 A+B+        | 1            |

| 7     | All-ones output         | *22    | A-B-1            | *22 A-B         |              |

| 11    | (NOT A) AND (NOT B)     | *36    | A-1              | 36 A            |              |

| *13   | NOT B                   |        |                  |                 |              |

| 15    | A XNOR B (Assembler ma  | kes "E | QV" and "="      | synonyms for XN | OR)          |

| 17    | A OR (NOT B)            |        |                  |                 |              |

| 21    | (NOT A) AND B           |        |                  |                 |              |

| *23   | A XOR B (Assembler make | es "#' | ' synonym for    | XOR)            |              |

| *25   | В                       |        |                  |                 |              |

| *27   | A OR B                  |        |                  |                 |              |

| 31    | All-zeroes output       |        |                  |                 |              |

| 33    | A AND (NOT B)           |        |                  |                 |              |

| *35   | A AND B                 |        |                  |                 |              |

| 37    | Α                       |        |                  |                 |              |

<sup>\*</sup>System microcode can count on these operations being defined

On a barrel shift (selected by ASEL = 7), the first three ALUFM address bits are forced to 1 (ALUF[0:2] selects the kind of shift in this case). The intent of this arrangement is that ALUFM[ $16_8$ ] selects the "NOT A" ALU operation. Nearly all shifter operations use this ALU function to route shifter output through the ALU. ALUFM[ $17_8$ ] is loaded with assorted controls (i.e., used as a variable) by BitBlt or other opcodes that do more complicated things.

ALUFM can be read onto Pd by the ALUFMEM function, loaded from B by the ALUFMEM+ function, or both loaded from B and read onto Pd by the ALUFMEMRW function.

External B sources from the IFU and internal sources are ready in time for arithmetic, but external sources from the memory and control sections are not (see the earlier section on "BSEL: B Multiplexor Select"). Internal A sources except shifter are ready in time for arithmetic. Unless explicitly disabled by the FreezeBC function, the branch conditions ALU<0, ALU=0, Carry' (ALU carry out'), and Coverflow are available for testing on the control card at  $t_3$ .

The Overflow branch condition, defined as carry-out from bit 0 unequal to carry-out from bit 1, is true iff a signed arithmetic operation yields an incorrect result.

Normally, the ALU is routed directly onto Pd, and Pd is then written into either T or RM/STK. However, several functions route ALU output shifted left or right 1 position onto Pd. The right shifts are:

ALU rsh 1 (0 onto Pd[0])

ALU rcy 1 (ALU[15] onto Pd[0])

ALU arsh 1 (ALU[0] onto Pd[0] preserving the sign)

ALU brsh 1 (ALUcarry onto Pd[0])

Multiply (ALUcarry onto Pd[0]).

#### The left shifts are:

ALU Ish 1 (0 onto Pd[15])

ALU Icy 1 (ALU[0] onto Pd[15])

Divide (Q[0] onto Pd[15])

CDivide (Q[0] onto Pd[15]).

Multiply, Divide, and CDivide have other effects as well discussed later.

*Note:* The barrel shifter discussed in the "Shifter" section also use the Pd multiplexor for masking, so it is illegal to combine barrel shifts and ALU shifts in the same instruction.

Note: ALUKO, ALU = 0, Carry', and Overflow branch conditions test the ALU output of the previous instruction executed by the task and any shifting or masking that takes place in the Pd input multiplexor does not affect the result of these branch conditions.

Note: The value of Carry' and Overflow change only on arithmetic ALU operations. However, ALU+A operation may be either an arithmetic or a logical operation; in order to use XorCarry with ALU+A, we will probably use the arithmetic form of ALU+A, but the consequence of this is that Carry' will change on ALU+A. Programmers will have to be wary of this.

Note: Overflow is implemented correctly only for the A+B, A+B+1, A-B, and A-B-1 operations; other arithmetic ALU operations may modify the branch condition erroneously.

# LC: Load Control for RM and T

This field controls the loading and source selection for the RM/STK memory and T register. The eight combinations are:

Table 9: LC Decodes

| LC | Meaning           |

|----|-------------------|

| 0  | No Action         |

| 1  | T←Pd              |

| 2  | T←Md, RM/STK←Pd   |

| 3  | T←Md              |

| 4  | RM/STK <b>←Md</b> |

| 5  | T←Pd, RM/STK←Md   |

| 6  | RM/STK+Pd         |

| 7  | T+Pd, RM/STK+Pd   |

The only missing combination is T+Md, RM/STK+Md. T+Md, RM/STK+Md can be accomplished by combining an LC value of 5 with the TgetsMd FF decode. It is illegal to use TgetsMd with other LC decodes.

### FF: Special Function

This field is the catch-all for functions not otherwise encoded in the instruction. For consistency with the hardware implementation, the 8-bit FF field is shown below as a two-bit field FA (= FF[0:1]) and two 3-bit fields, FB (= FF[2:4]) and FC (= FF[5:7]). Field values are given in octal.

The FF field is interpreted as a function iff:

(BSEL not selecting a constant) and JCN does not select a "long" goto or call

When ASEL selects one of the memory references, the FF decode is forced to be that of FA = 0 because the FA field specifies the source for A or alternate memory reference in this case.

The decoding assignments have been made with the following considerations:

Functions that source the external BMux are grouped for easy decode of the signal that turns off the processor's B-multiplexors.

Operations that might be useful in conjunction with a memory reference are put in the first 64 decodes (FA = 0) since FA is decoded as zero on memory references.

Functions decoded by different hardware sections are arranged in groups to reduce decoding logic.

0:7

# Table 10a: FF Decodes (FA = 0)

| FB                                                   | FC                                                        | Function                                                                                                                           |

|------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 0-1                                                  |                                                           | A[12:15] ← FF[4:7]                                                                                                                 |

| * The                                                | e 4 A←xx                                                  | decodes below do not disable the AMux, if ASEL selects a shift                                                                     |

| 2                                                    | 0                                                         | A ← RM/STK                                                                                                                         |

| 2                                                    | 1                                                         | A ← T                                                                                                                              |

| 2                                                    | 2                                                         | A ← Md                                                                                                                             |

| 2 3 A ← Q                                            |                                                           | A ← Q                                                                                                                              |

| 2                                                    | 4                                                         | XorCarry (complements ALUFM carry bit)                                                                                             |

| 2 5 XorSavedCarry                                    |                                                           | XorSavedCarry                                                                                                                      |

| 2 6 Carry20 (carry-in to bit 11 of ALU = 1)          |                                                           | · · · · ·                                                                                                                          |

| 2 7 ModStkPBeforeW (Use modified StkP for write addr |                                                           | ModStkPBeforeW (Use modified StkP for write address of STK)                                                                        |

| 3                                                    | 0                                                         |                                                                                                                                    |

| 3                                                    | 1 ReadMap. Modifies action of Map+ (see "Memory Section") |                                                                                                                                    |

| 3                                                    | 2                                                         | Pd ← Input (checks for IOB PE)                                                                                                     |

| 3                                                    | 3                                                         | Pd ← InputNoPE (no check for IOB PE)                                                                                               |

| 3                                                    | 4                                                         | Risld (causes ld to replace RM/STK in A+RM/STK, B+RM/STK, and shifter)                                                             |

| 3                                                    | 5                                                         | Tisld (causes ld to replace T in A+T, B+T, and shifter)                                                                            |

| 3                                                    | 6                                                         | Output + B                                                                                                                         |

| 3                                                    | 7                                                         | FlipMemBase (MemBase ← MemBase xor 1)                                                                                              |

| 4-5                                                  | <br>                                                      | Replace RMaddr[0:3] by RBase[0:3] and RMaddr[4:7] by FF[4:7] for write of RM; Forces RM to be written even if STK was read.        |

| 6                                                    | 0-7                                                       | Branch conditions (see "Control"). In conjunction with an IFU jump in JCN,                                                         |

|                                                      |                                                           | if the condition is true, IFU advance is disabled (see "IFU")                                                                      |

| 7                                                    | 0                                                         | BigBDispatch ← B (256-way dispatch on B[8:15]. See "Control")                                                                      |

| 7                                                    | 1                                                         | BDispatch + B (8-way dispatch on B[13:15]. See "Control")                                                                          |

| 7                                                    | 2                                                         | Multiply (Pd[0:15] ← ALUcarry,,ALU[0:14]; Q[0:15] ← ALU[15],,Q[0:14]; Q[14] OR'ed into TNIA[10] as slow branchsee "Multiply")      |

| 7                                                    | 3                                                         | Q ← B                                                                                                                              |

| 7                                                    | 4                                                         |                                                                                                                                    |

| 7                                                    | 5                                                         | TgetsMd (In conjunction with LC=5, this causes T←Md, RM/STK←Md)                                                                    |

| 7                                                    | 6                                                         | FreezeBC (freezes previous values of ALU and IOAtten' BC's for 1 cycle)                                                            |

| 7                                                    | 7                                                         | Reserved as a no-op                                                                                                                |

|                                                      |                                                           | Table 10b: FF Decodes (FA = 1)                                                                                                     |

| FB                                                   | FC                                                        | Action                                                                                                                             |

| 0                                                    | 0                                                         | PCF ← B. Load PCF and starts fetching instructions                                                                                 |

| 0                                                    | 1                                                         | IFUTest ← B, dismisses junk wakeup, bits used as follows:                                                                          |

|                                                      |                                                           | 0:7 TestFG 8 TestParity 9 TestFault 10 TestMemAck 11 TestMakeF←D 12 TestFH' 13 TestSH' 14 enables testing 15 Disables junk wakeups |

| 0                                                    | 2                                                         | IFUTick                                                                                                                            |

| 0                                                    | 3                                                         | RescheduleNow                                                                                                                      |

| 0                                                    | 4                                                         |                                                                                                                                    |

| 0                                                    | 5                                                         | MemBase+B[3:7]                                                                                                                     |

| 0                                                    | 6                                                         | RBase+B[12:15]                                                                                                                     |

| 0                                                    | 7<br>0: <b>7</b>                                          | Pointers←B (MemBase←B[3:7] and RBase←B[12:15])                                                                                     |

| -                                                    | 0.7                                                       |                                                                                                                                    |

# Table 10c: FF Decodes (FA = 1)

| FB FC          | Action                                                                                                                                                                |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| *The following | g 8 FF decodes drive Mar from A.                                                                                                                                      |  |  |  |

| 2 2            | CFlags ← A' (see Figure 10) (Mar must be stable during prev. instr.)                                                                                                  |  |  |  |

| 2 3            | BrLo ← A. BR[16:31] ← A[0:15]                                                                                                                                         |  |  |  |

| 2 4            | BrHi ← A. BR[4:15] ← A[4:15]                                                                                                                                          |  |  |  |

| 2 5            | LoadTestSyndrome from DBuf (see Figure 10)                                                                                                                            |  |  |  |

| 2 6            | LoadMcr[A,B] (see Figure 10)                                                                                                                                          |  |  |  |

| 2 7            | ProcSRN ← B[12:15]                                                                                                                                                    |  |  |  |

| 3 0            | InsSetorEvent $\leftarrow$ B. If B[0] = 0, then B[4:15] are controls for EventCntA and EventCntB; if B[0] = 1, then B[6:7] are loaded into the IFU's InsSet register. |  |  |  |

| 3 1            | EventCntB + B or equivalently GenOut+B (General output to printer, etc.)                                                                                              |  |  |  |

| 3 2            | Reschedule                                                                                                                                                            |  |  |  |

| 3 3            | NoReschedule                                                                                                                                                          |  |  |  |

|                | setup during previous instruction and not glitch when writing IFUMLH/RHsee IFU section.                                                                               |  |  |  |

| 3 4            | IFUMRH ← B. Packeda←B.5, IFaddr'←B[6:15]                                                                                                                              |  |  |  |