# XVME-678/688

# VMEbus PC/AT Processor Module

P/N 74688-002A

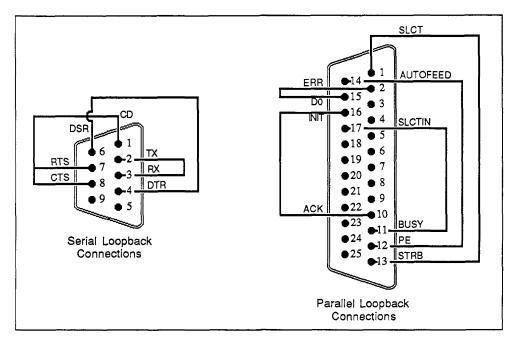

© 1994 XYCOM, INC.

Printed in the United States of America Part Number 74688-002A **XYCOM**750 North Maple Road

Saline, Michigan 48176-1292

734-429-4971 (phone)

734-429-1010 (fax)

# XYCOM REVISION RECORD

| Revision | Description     | Date |

|----------|-----------------|------|

| A        | Manual Released | 7/94 |

# Trademark Information

Brand or product names are registered trademarks of their respective owners.

# Copyright Information

This document is copyrighted by Xycom Incorporated (Xycom) and shall not be reproduced or copied without expressed written authorization from Xycom.

The information contained within this document is subject to change without notice. Xycom does not guarantee the accuracy of the information and makes no commitment toward keeping it up to date.

Address comments concerning this manual to:

Part Number: 74688-002A

# TABLE OF CONTENTS

| CHAPTER |        | TITLE                                                  | PAGE |  |

|---------|--------|--------------------------------------------------------|------|--|

| 1       |        | INTRODUCTION                                           |      |  |

|         | 1.1    | Product Features                                       | 1-1  |  |

|         | 1.2    | Manual Structure                                       | 1-2  |  |

|         | 1.3    | XVME-678/688 Board Operational Description             | 1-3  |  |

|         | 1.3.1  | 80386SX or 486SLC/e Central Processing Unit (CPU)      | 1-4  |  |

|         | 1.3.2  | DRAM                                                   | 1-4  |  |

|         | 1.3.3  | Floppy Drive Controller                                | 1-4  |  |

|         | 1.3.4  | Hard Drive Controller                                  | 1-4  |  |

|         | 1.3.5  | Graphics Controller                                    | 1-5  |  |

|         | 1.3.6  | I/O Ports                                              | 1-5  |  |

|         | 1.3.7  | VMEbus Master Interface                                | 1-5  |  |

|         | 1.3.8  | Keyboard Controller                                    | 1-5  |  |

|         | 1.4    | Specifications                                         | 1-6  |  |

| 2       |        | INSTALLATION                                           |      |  |

|         | 2.1    | Introduction                                           | 2-1  |  |

|         | 2.2    | Jumpers                                                | 2-2  |  |

|         | 2.2.1  | VGÂ Jumpers (J3, J5)                                   | 2-4  |  |

|         | 2.2.2  | EPROM/Flash Jumper (J1)                                | 2-4  |  |

|         | 2.2.3  | IRQ12 Jumper (J8)                                      | 2-4  |  |

|         | 2.2.4  | Battery and Test Jumpers (J2, J4)                      | 2-5  |  |

|         | 2.3    | Switch Settings                                        | 2-5  |  |

|         | 2.4    | Connectors                                             | 2-6  |  |

|         | 2.4.1  | VMEbus P1 Connector                                    | 2-8  |  |

|         | 2.4.2  | VMEbus P2 Connector                                    | 2-9  |  |

| •       | 2.4.3  | Floppy Drive Connector (P4)                            | 2-10 |  |

|         | 2.4.4  | IDE Hard Drive Connector (P5)                          | 2-11 |  |

|         | 2.4.5  | Keyboard Connector (P6)                                | 2-12 |  |

|         | 2.4.6  | Auxiliary Connector (P7)                               | 2-12 |  |

|         | 2.4.7  | COM2 Serial Port Connector (P8)                        | 2-12 |  |

|         | 2.4.8  | COM1 Serial Port Connector (P9)                        | 2-13 |  |

|         | 2.4.9  | VGA Connector (P10)                                    | 2-13 |  |

|         | 2.4.10 | Parallel Port Connector (JK1)                          | 2-14 |  |

|         | 2.4.11 | Speaker Connector (J7)                                 | 2-14 |  |

|         | 2.4.12 | PXT1 Connector                                         | 2-15 |  |

|         | 2.4.13 | PAT1 Connector                                         | 2-16 |  |

|         | 2.5    | Installing the XVME-678/688 into a Backplane           | 2-17 |  |

|         | 2.6    | Adding Extended BIOS                                   | 2-20 |  |

|         | 2.7    | Installing DRAM                                        | 2-22 |  |

|         | 2.8    | Installing an Optional Intel 80387SX Math Co-processor |      |  |

# Table of Contents

| CHAPTER |        | TITLE                                                    | PAGE |

|---------|--------|----------------------------------------------------------|------|

| 3       |        | BIOS SETUP MENUS                                         |      |

|         | 3.1    | Introduction                                             | 3-1  |

|         | 3.2    | Software Control and Initial Setup                       | 3-1  |

|         | 3.3    | BIOS Main Menu                                           | 3-2  |

|         | 3.3.1  | BIOS Setup Menu                                          | 3-3  |

|         | 3.3.2  | VMEbus Master Setup Menu                                 | 3-8  |

|         | 3.3.3  | Solid State Disk Setup Menu                              | 3-11 |

|         | 3.3.4  | Extended BIOS Features Menu                              | 3-13 |

|         | 3.3.5  | System Information Menu                                  | 3-16 |

|         | 3.3.6  | Diagnostics Menu                                         | 3-16 |

|         | 3.3.7  | Format Fixed Disk Menu                                   | 3-23 |

| 4       |        | PROGRAMMING                                              |      |

|         | 4.1    | Introduction                                             | 4-1  |

|         | 4.2    | XVME-678/688 Memory Maps                                 | 4-1  |

|         | 4.2.1  | DRAM                                                     | 4-7  |

|         | 4.2.2  | EPROM                                                    | 4-8  |

|         | 4.3    | Accessing VMEbus Memory Space Using the Real Mode Window | 4-9  |

|         | 4.3.1  | EPROM                                                    | 4-9  |

|         | 4.3.2  | VMEbus IACK Space                                        | 4-9  |

|         | 4.3.3  | VMEbus Short I/O Space                                   | 4-10 |

|         | 4.3.4  | VMEbus Standard Address Space                            | 4-11 |

|         | 4.4    | VMEbus Master Interface                                  | 4-12 |

|         | 4.5    | Shadow RAM Option                                        | 4-14 |

|         | 4.6    | I/O Port Addresses                                       | 4-15 |

|         | 4.6.1  | Control Register 1                                       | 4-17 |

|         | 4.6.2  | Auxiliary Interrupt                                      | 4-18 |

|         | 4.6.3  | Status Register 1                                        | 4-18 |

|         | 4.6.4  | Status Register 2                                        | 4-19 |

|         | 4.6.5  | VMEbus HI Address                                        | 4-19 |

|         | 4.6.6  | Control Register 2                                       | 4-19 |

|         | 4.6.7  | Control Register 3                                       | 4-20 |

|         | 4.6.8  | Control Register 4                                       | 4-20 |

|         | 4.6.9  | Control Register 5                                       | 4-21 |

|         | 4.6.10 | Control Register 6                                       | 4-21 |

|         | 4.7    | Interrupts                                               | 4-22 |

|         | 4.7.1  | Auxiliary Maskable Interrupts (AMIs)                     | 4-22 |

|         | 4.8    | Byte-Swapping                                            | 4-26 |

|         | 4.8.1  | Byte-Ordering Schemes                                    | 4-26 |

|         | 4.8.2  | Address Consistency                                      | 4-27 |

| CHAPTER |       | TITLE                                             | PAGE |  |

|---------|-------|---------------------------------------------------|------|--|

| 4       |       | PROGRAMMING (continued)                           |      |  |

|         | 4.8.3 | Numeric Consistency                               | 4-28 |  |

|         | 4.9   | System Resource Function                          | 4-30 |  |

|         | 4.10  | CMOS RAM                                          | 4-31 |  |

| 5       |       | XVME BIOS FUNCTIONS                               |      |  |

|         | 5.1   | XVME BIOS Functions                               | 5-1  |  |

|         | 5.2   | Miscelleneous Functions                           | 5-4  |  |

|         | 5.2.1 | Identify XVME Model                               | 5-4  |  |

|         | 5.2.2 | Get Real Mode Window Physical Segment             | 5-5  |  |

|         | 5.2.3 | Get LED Configuration                             | 5-6  |  |

|         | 5.2.4 | Set LED Configuration                             | 5-7  |  |

|         | 5.2.5 | Get Flash BIOS Write Configuration                | 5-8  |  |

|         | 5.2.6 | Set Flash BIOS Write Configuration                | 5-9  |  |

|         | 5.3   | Real Mode Window (RMW) Functions                  | 5-10 |  |

|         | 5.3.1 | Get Real Mode Window Configuration                | 5-10 |  |

|         | 5.3.2 | Set Real Mode Window Configuration                | 5-11 |  |

|         | 5.4   | Auxiliary Non-maskable Interrupt (ANMI) Functions | 5-12 |  |

|         | 5.4.1 | Get ANMI Group Configuration                      | 5-12 |  |

|         | 5.4.2 | Set ANMI Group Configuration                      | 5-13 |  |

|         | 5.4.3 | Get ANMI Mask                                     | 5-14 |  |

|         | 5.4.4 | Set ANMI Mask                                     | 5-15 |  |

|         | 5.4.5 | Get ANMI Status                                   | 5-16 |  |

|         | 5.4.6 | Clear ANMI                                        | 5-17 |  |

|         | 5.5   | VMEbus Master Functions                           | 5-18 |  |

|         | 5.5.1 | Get VMEbus Master Configuration                   | 5-18 |  |

|         | 5.5.2 | Set VMEbus Master Configuration                   | 5-19 |  |

|         | 5.5.3 | Get VMEbus Ownership Configuration                | 5-21 |  |

|         | 5.5.4 | Set VMEbus Ownership Configuration                | 5-22 |  |

|         | 5.5.5 | Get VMEbus Ownership Status                       | 5-23 |  |

|         | 5.5.6 | Wait for VMEbus Ownership to be Granted           | 5-24 |  |

|         | 5.6   | VMEbus Interrupt Handler Functions                | 5-25 |  |

|         | 5.6.1 | Get VMEbus Interrupt Group Configuration          | 5-25 |  |

|         | 5.6.2 | Set VMEbus Interrupt Group Configuration          | 5-26 |  |

|         | 5.6.3 | Get VMEbus Interrupt Mask                         | 5-27 |  |

|         | 5.6.4 | Set VMEbus Interrupt Mask                         | 5-28 |  |

|         | 5.6.5 | Enable/Disable Specific VMEbus Interrupts         | 5-30 |  |

|         | 5.6.6 | Get VMEbus Interrupt Status                       | 5-32 |  |

# Table of Contents

| CHAPTER                                                                                     | TITLE                                                                                                                                                                                                                                                                                                                         | PAGE                                                                                              |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 5                                                                                           | XVME BIOS FUNCTIONS (continued)                                                                                                                                                                                                                                                                                               |                                                                                                   |

| 5.6.7<br>5.6.8<br>5.7<br>5.7.1                                                              | Determine Highest Priority Pending VMEbus Inter-<br>Acknowledge VMEbus Interrupt Via Real Mode W<br>VMEbus System Resource Functions<br>Get System Resource Flag                                                                                                                                                              | •                                                                                                 |

|                                                                                             | APPENDICES                                                                                                                                                                                                                                                                                                                    |                                                                                                   |

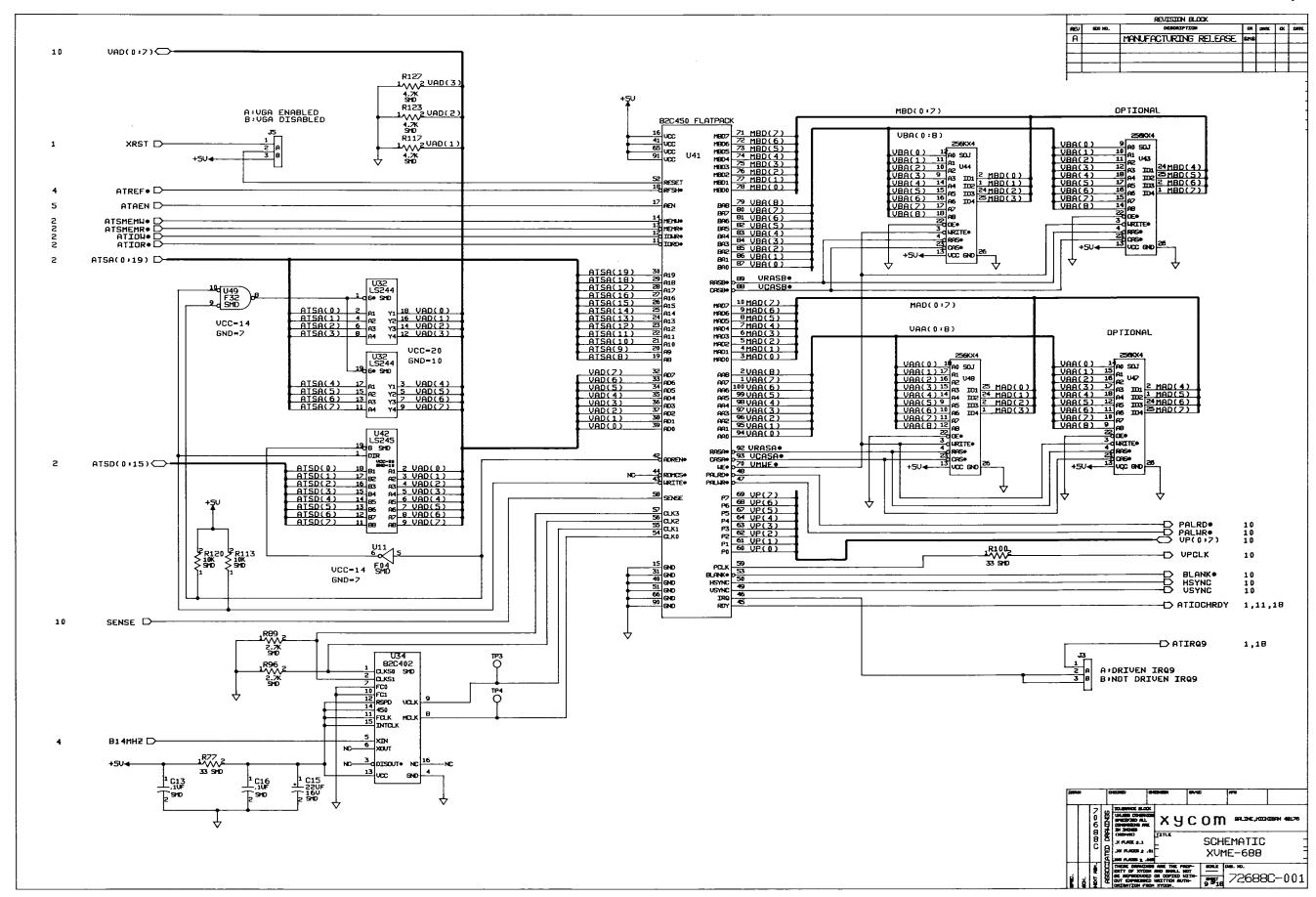

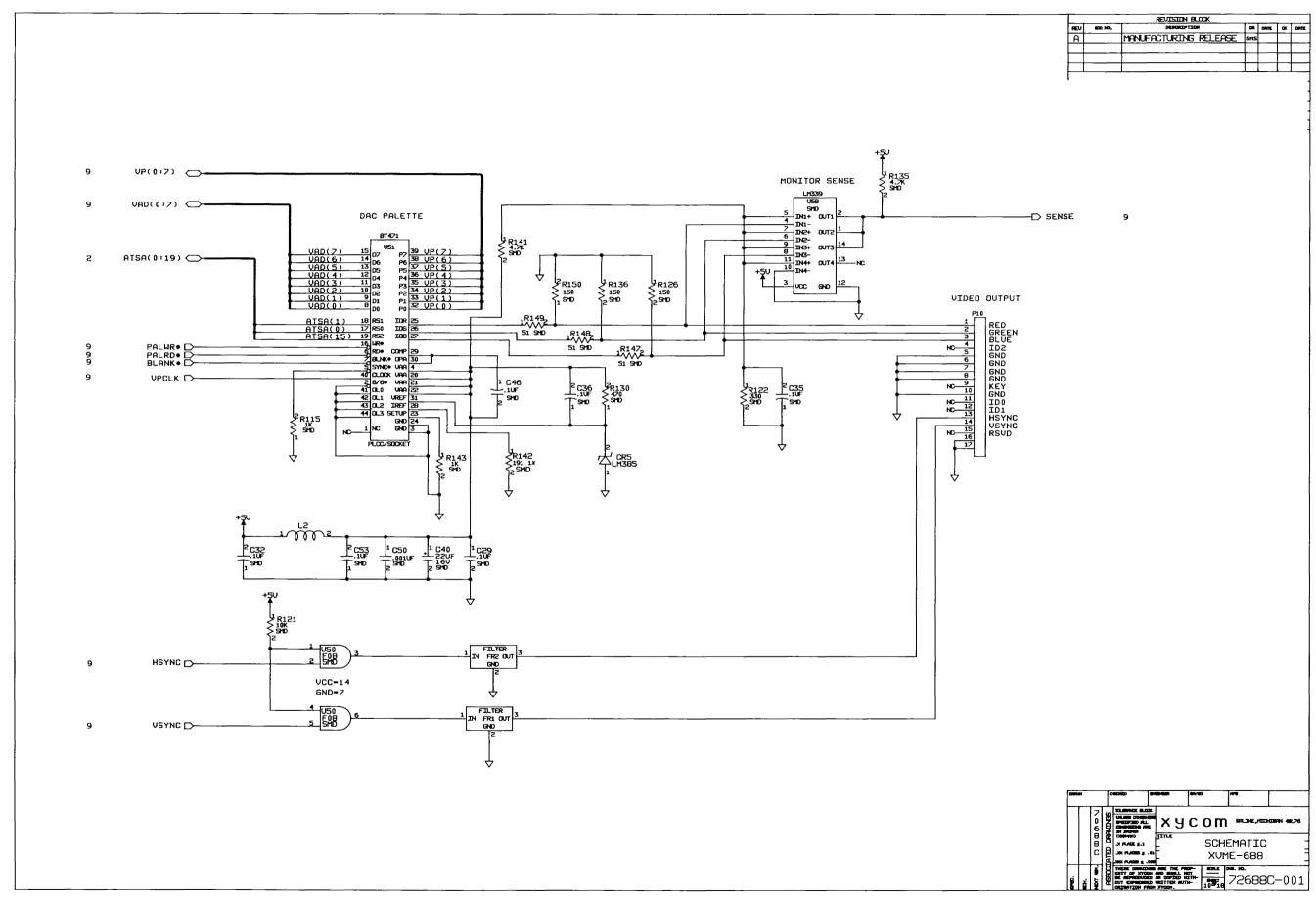

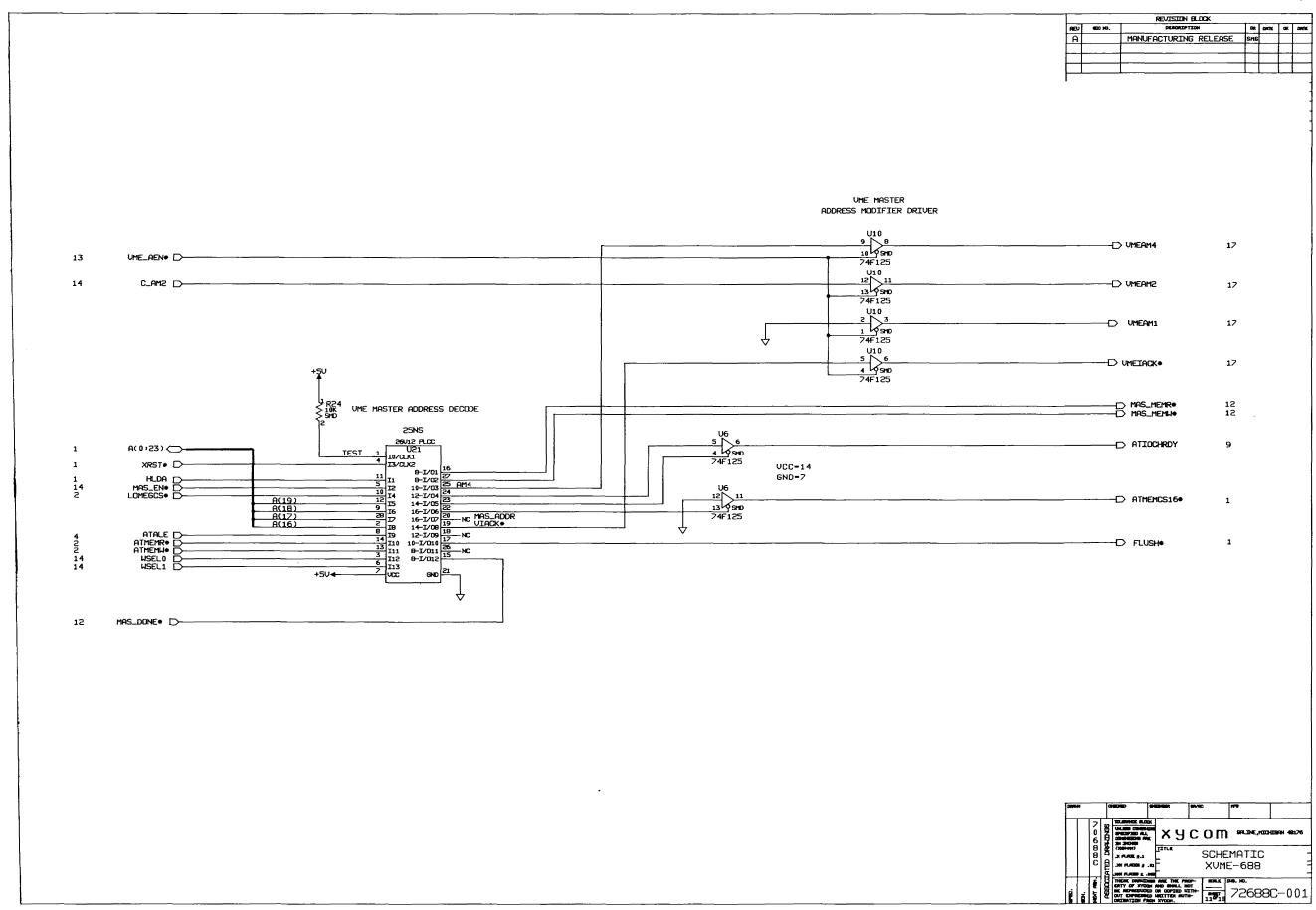

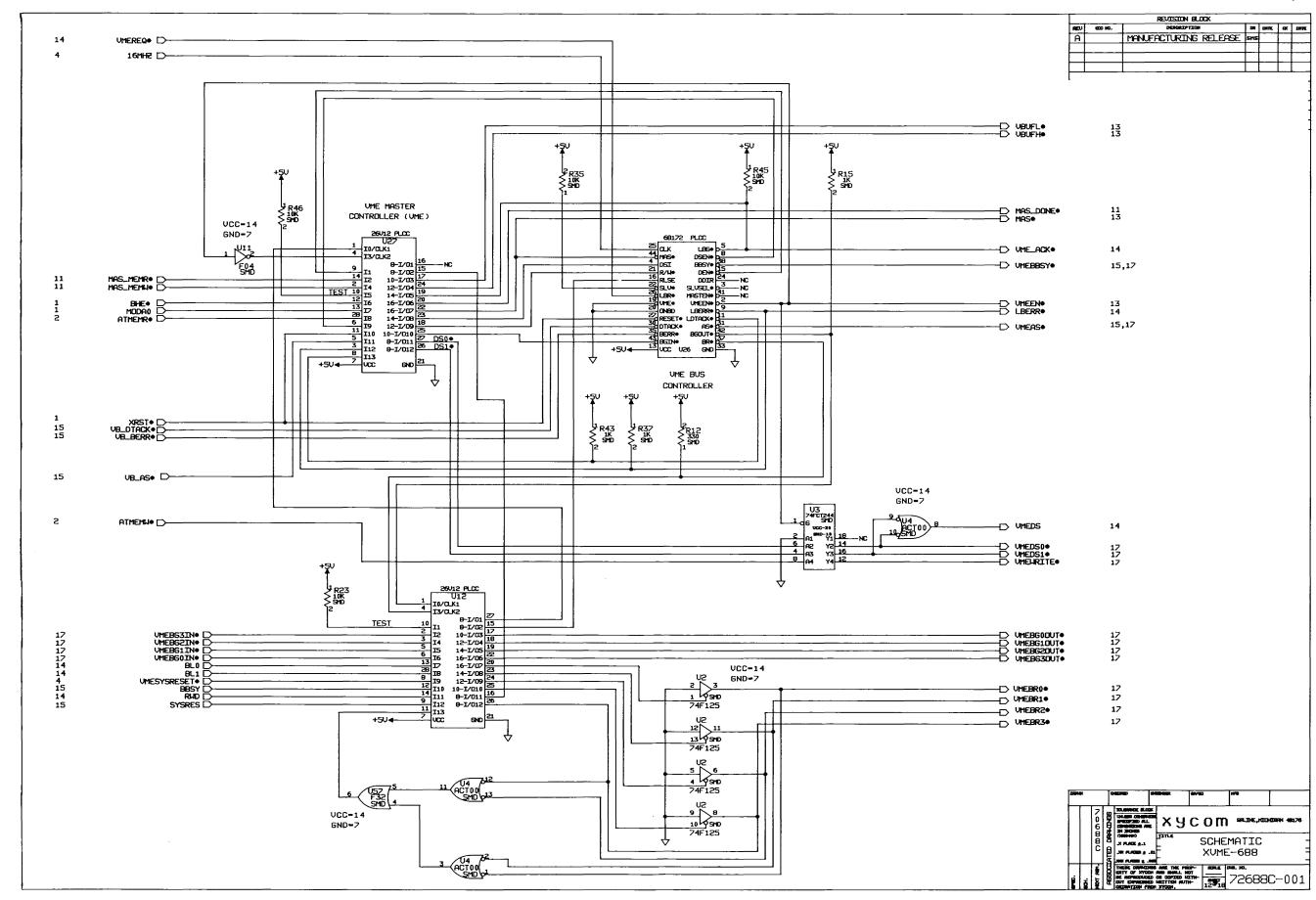

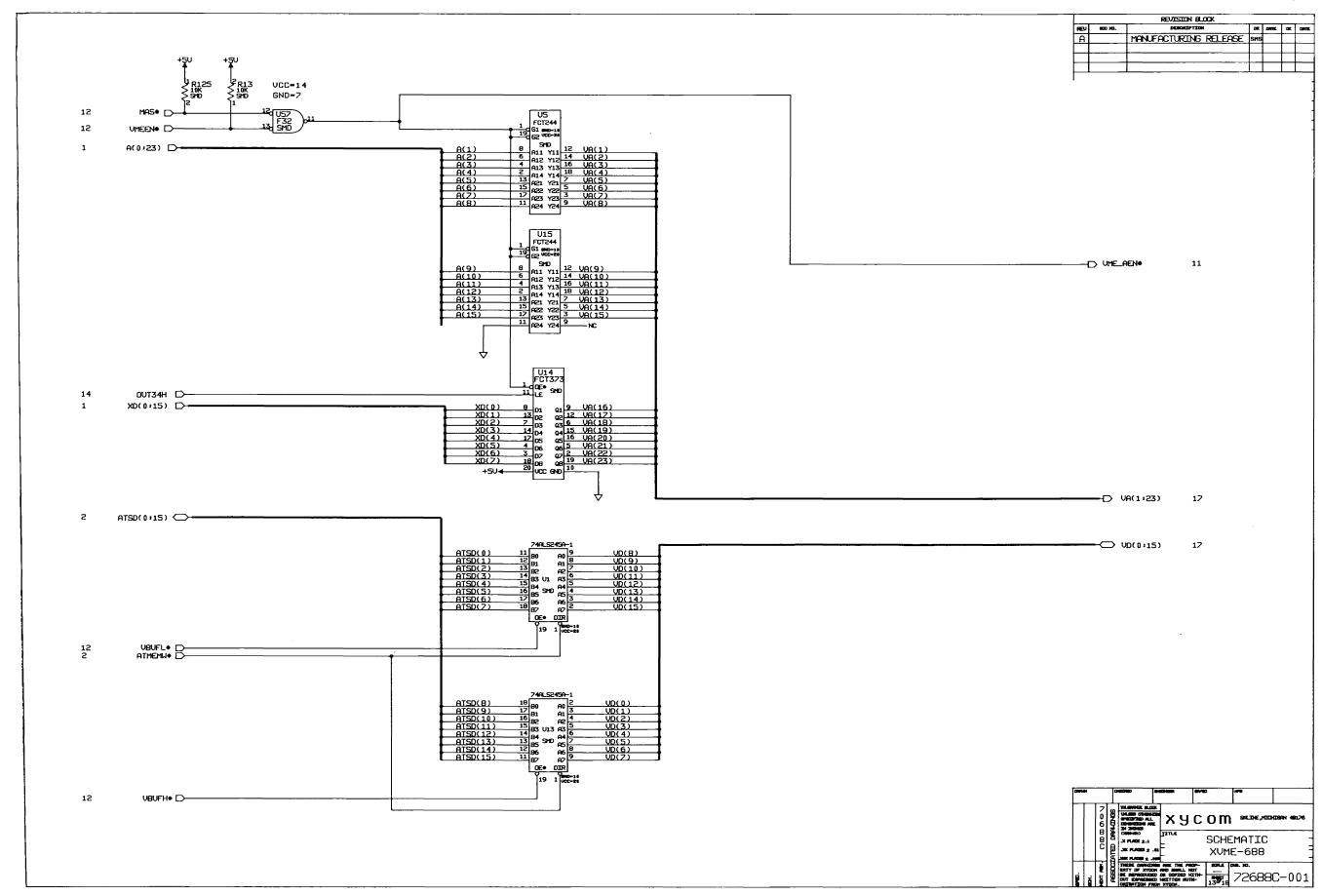

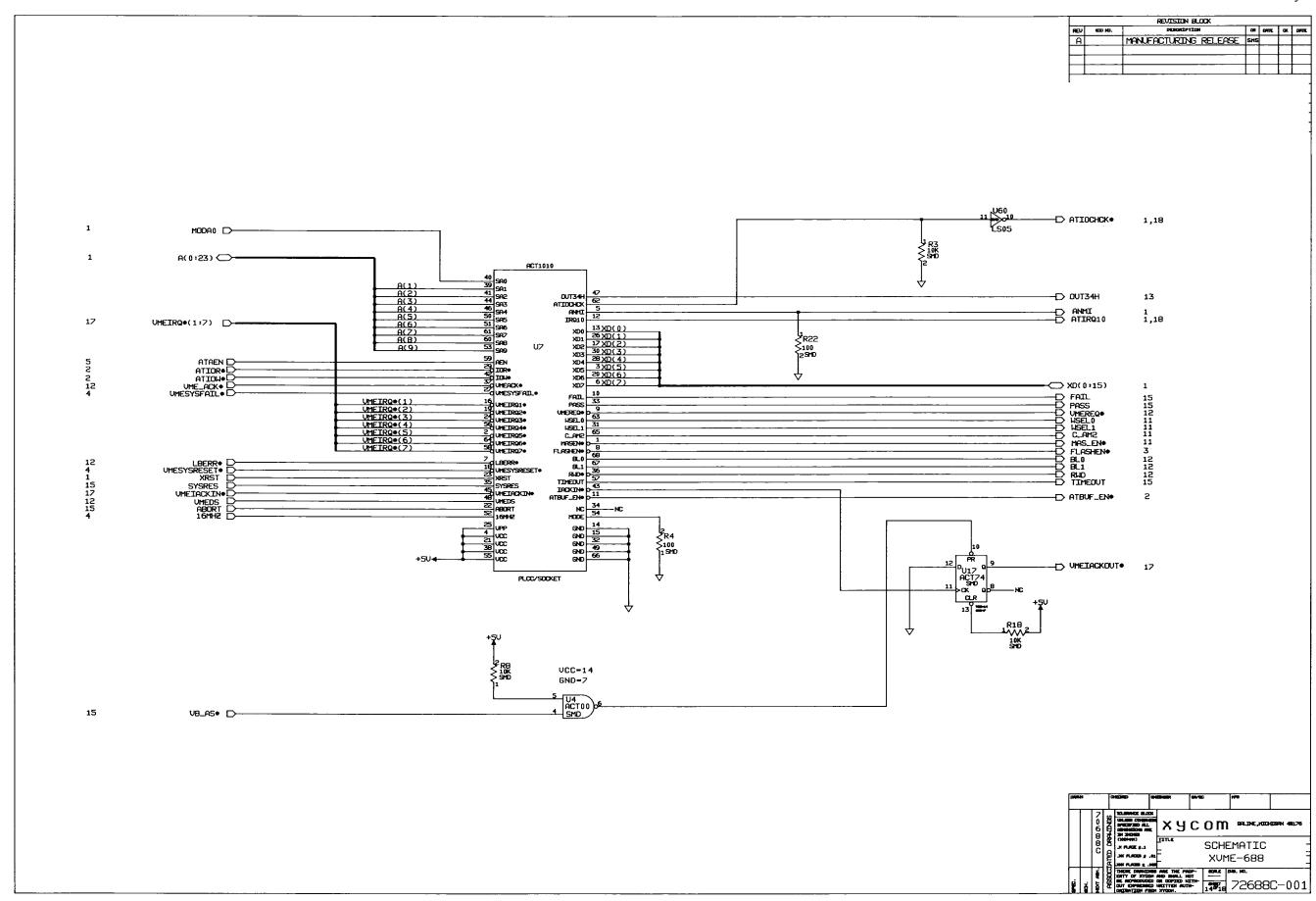

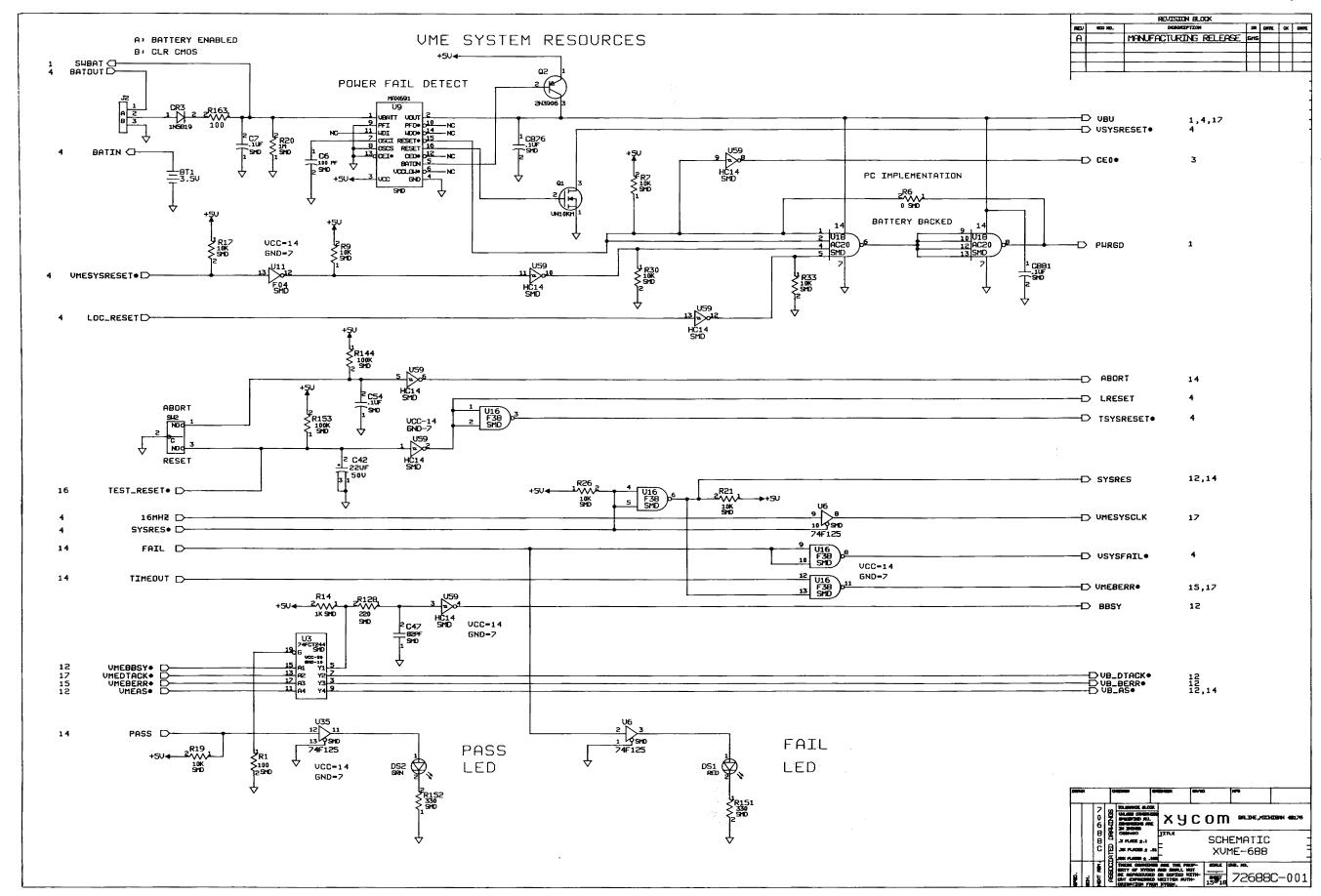

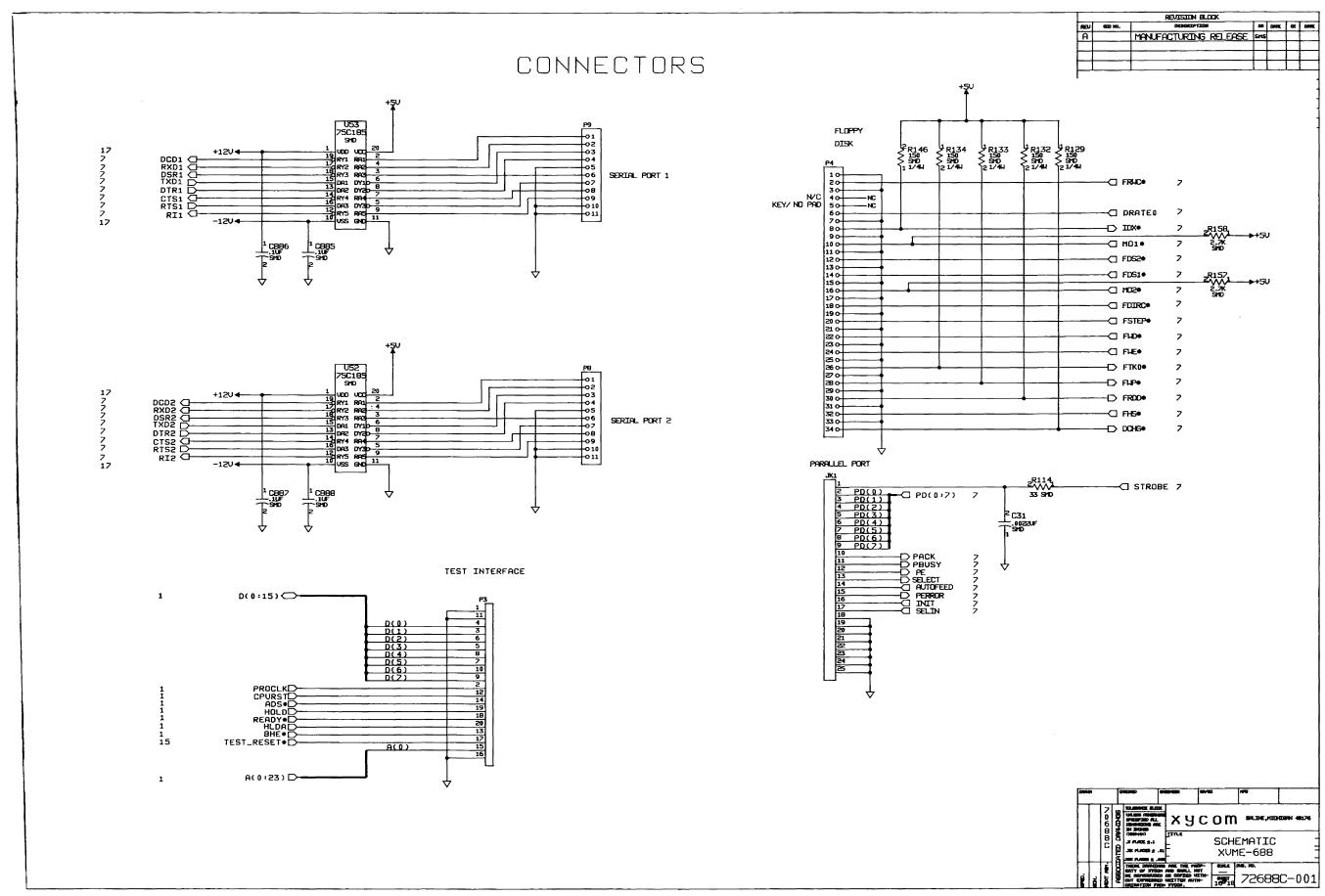

| A<br>B<br>C<br>D                                                                            | VMEbus CONNECTOR/PIN DESCRIPTIONS<br>QUICK REFERENCE GUIDE<br>EXTENDED VGA MODES<br>BLOCK DIAGRAM, ASSEMBLY DRAWING, A                                                                                                                                                                                                        | ND SCHEMATICS                                                                                     |

|                                                                                             | LIST OF FIGURES                                                                                                                                                                                                                                                                                                               |                                                                                                   |

| FIGURE                                                                                      | TITLE                                                                                                                                                                                                                                                                                                                         | PAGE                                                                                              |

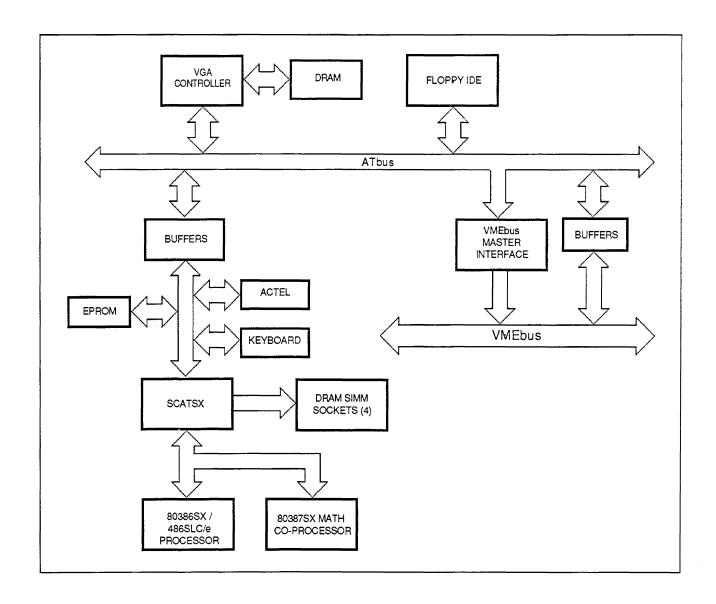

| 1-1                                                                                         | XVME-678/688 Board Block Diagram                                                                                                                                                                                                                                                                                              | 1-3                                                                                               |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5                                                             | XVME-678/688 Jumper and Switch Locations<br>XVME-678/688 Connector Locations<br>XVME-678/688 Board Front Panel<br>DRAM Installation<br>80387SX Math Co-processor Installation                                                                                                                                                 | 2-3<br>2-7<br>2-19<br>2-24<br>2-25                                                                |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13 | Main Setup Menu BIOS Setup Menu VMEbus Master Setup Menu Solid State Disk Setup Menu Extended BIOS Features Menu System Information Menu Advanced Diagnostics Menu Advanced Diagnostics Test Menu Diskette Drive Menu Fixed Disk Menu Parallel Port Test Menu Serial and Parallel Loopback Connections Format Fixed Disk Menu | 3-2<br>3-3<br>3-8<br>3-11<br>3-13<br>3-16<br>3-17<br>3-18<br>3-20<br>3-21<br>3-22<br>3-22<br>3-22 |

| 4-1                                                                                         | 1 Mbyte Memory Map (as seen by the CPU)                                                                                                                                                                                                                                                                                       | 4-2                                                                                               |

# LIST OF FIGURES (continued)

| FIGURE   | PAGE                                       |       |

|----------|--------------------------------------------|-------|

| 4-2      | 2 Mbyte Memory Map (as seen by the CPU)    | 4-3   |

| 4-3      | 4 Mbyte Memory Map (as seen by the CPU)    | 4-4   |

| 4-4      | 10 Mbyte Memory Map (as seen by the CPU)   | 4-5   |

| 4-5      | 16 Mbyte Memory Map (as seen by the CPU)   | 4-6   |

| 4-6      | EPROM Memory Map                           | 4-8   |

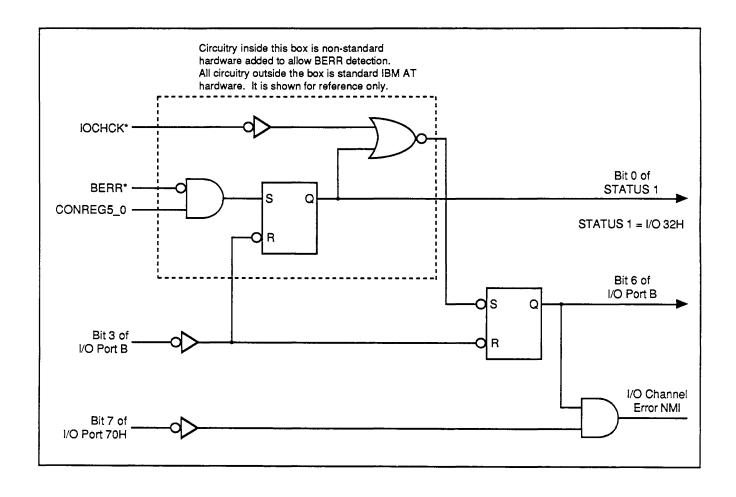

| 4-7      | BERR Mapped Onto IOCHCK*                   | 4-12  |

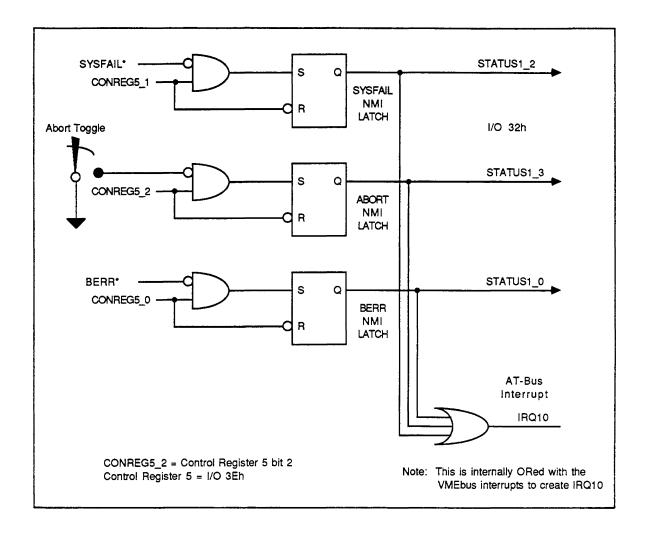

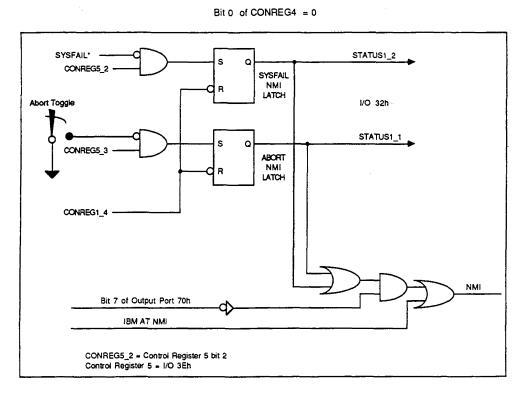

| 4-9      | BERR, SYSFAIL, and ABORT Switch Mapped on  | -     |

| 4-10     | Auxiliary Non-maskable Interrupt Structure | 4-25  |

| 4-11     | Byte-Ordering Schemes                      | 4-26  |

| 4-12     | Maintaining Address Consistency            | 4-27  |

| 4-13     | Maintaining Numeric Consistency            | 4-28  |

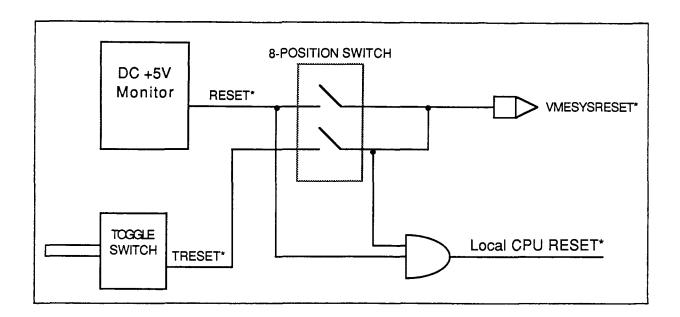

| 4-14     | Reset Structure                            | 4-30  |

|          | LIST OF TABLES                             |       |

| TABLE    | TITLE                                      | PAGE  |

| 11,12,22 | 11122                                      | 11102 |

| 1-1      | XVME-678/688 Module Specifications         | 1-6   |

| 2-1      | XVME-678/688 Jumper Options                | 2-4   |

| 2-2      | XVME-678/688 SW1 Switch Settings           | 2-5   |

| 2-3      | P1 Pinouts                                 | 2-8   |

| 2-4      | P2 Pinouts                                 | 2-9   |

| 2-5      | Floppy Drive Connector                     | 2-10  |

| 2-6      | IDE Hard Drive Connector                   | 2-11  |

| 2-7      | Keyboard Connector                         | 2-12  |

| 2-8      | Auxiliary Connector                        | 2-12  |

| 2-9      | COM2 Serial Port Connector                 | 2-12  |

| 2-10     | COM1 Serial Port Connector                 | 2-13  |

| 2-11     | VGA Connector                              | 2-13  |

| 2-12     | Parallel Port Connector                    | 2-14  |

| 2-13     | Speaker Connector                          | 2-14  |

| 2-14     | PXT1 Pinouts                               | 2-15  |

| 2-15     | PAT1 Pinouts                               | 2-16  |

| 2-16     | Bank and SIMM Size                         | 2-22  |

| 3-1      | Error Codes                                | 3-26  |

| 4-1      | I/O Address Map                            | 4-15  |

| 4-2      | I/O Addresses Unique to the XVME-678/688   | 4-16  |

| 4-3      | CMOS RAM Address Map                       | 4-32  |

#### 1.1 **PRODUCT FEATURES**

The XVME-678/688 VMEbus PC/AT processor modules are designed to combine the high-performance and ruggedized packaging of the VMEbus with the broad application software base of the IBM PC/AT standard. These 6U, double-high modules require a single VMEbus slot, are fully AT-compatible, and support all standard PC/AT software.

The XVME-688 features a low-power CMOS design with an 80386SX processor running at 25 MHz. The XVME-678 features a Cyrix 486SLC/e running at 25 MHz. The 486SLC/e provides an internal 1 Kbyte cache, a 486SX-compatible instruction set, and a 80386SX pin out.

Both modules offer the following features:

- 25 MHz 80386SX microprocessor (XVME-688) or 25 MHz 486SLC/e (XVME-678)

- 0, 1, or 4 Mbytes of DRAM

- -SIMM sockets for memory expansion up to 16 Mbytes DRAM

- -Zero wait state page interleaved DRAM accesses with 60 nsec DRAMs

- Shadow RAM option for System and VGA BIOS

- Super VGA graphics controller with 512 Kbytes of DRAM

- Floppy disk controller

- High-performance IDE hard disk controller

- A socket for an 80387SX math co-processor

- VMEbus master interface

- VMEbus interrupt handler

- Programmable interrupt enable

- Programmable bus request and bus grant levels

- VMEbus slot 1 functions

- Real mode window, allowing VMEbus Short I/O and Standard address space locations to be accessed while processor is in real mode

- Two RS-232C serial communication ports

- Centronics-compatible parallel port

- PS/2-compatible keyboard port

- PS/2 AUX port for PS/2-compatible mouse or trackball

- VMEbus SYSFAIL switch

# 1.2 MANUAL STRUCTURE

The chapters in this manual are organized in the following manner:

- Chapter One Module Description: functional and environmental specifications, module structure, VMEbus compliance information, and block diagram

- Chapter Two Installation: system requirements, jumper and switch settings, connector pinouts, and procedures for installing the XVME-678/688 into a backplane, installing SIMM memory onto the XVME-678/688, adding extended BIOS, and installing the optional math coprocessor

- Chapter Three BIOS Setup Menus: descriptions of menu-driven BIOS utilities

- Chapter Four **Programming**: information required to program the module, including memory maps, I/O maps, and interrupt information

- Appendix A VMEbus Connector/Pin Description: VMEbus signals, connectors, pin numbers and their descriptions

- Appendix B Quick Reference Guide: default jumper settings, tables, and graphs

- Appendix C Extended VGA Modes: information about extended video modes

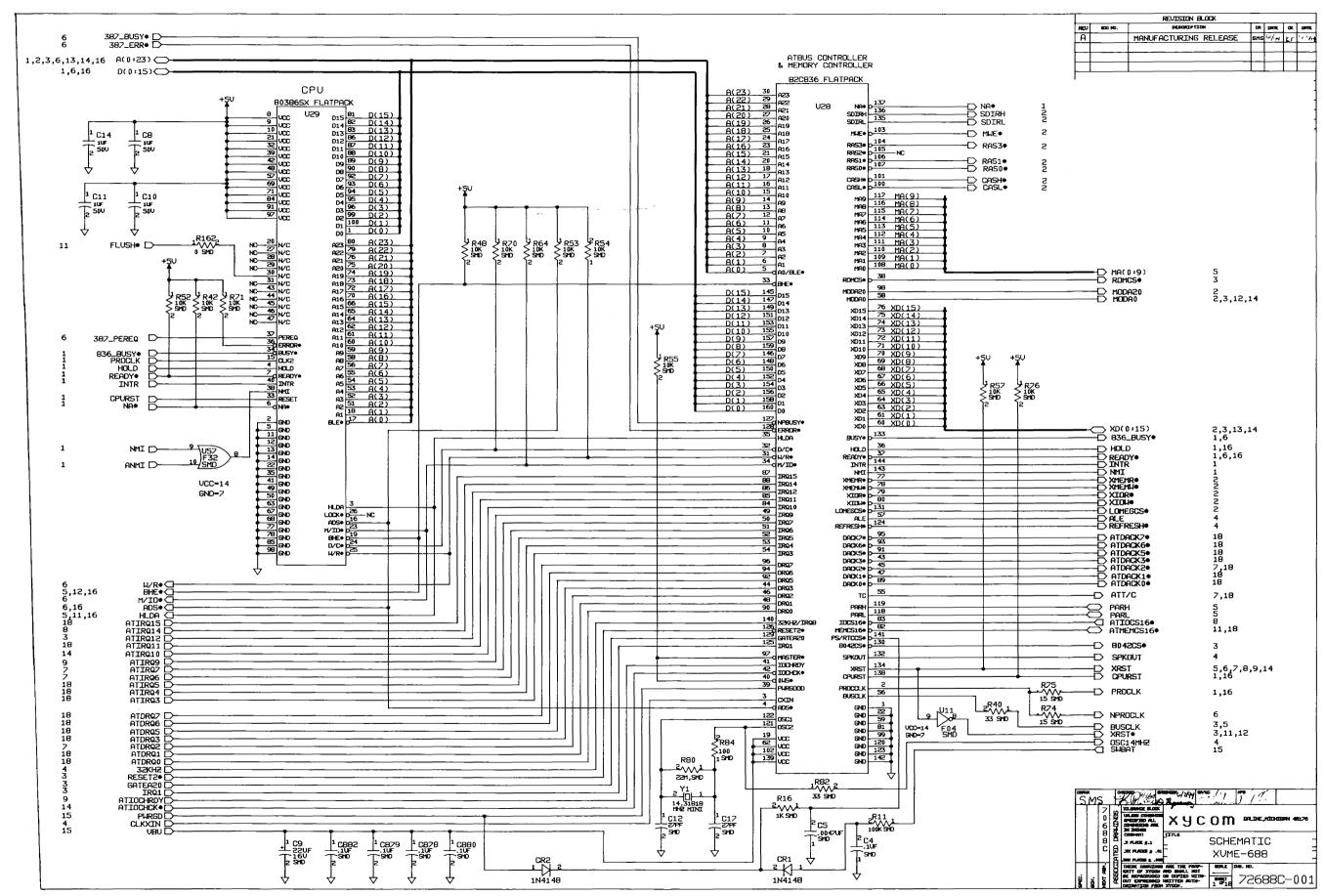

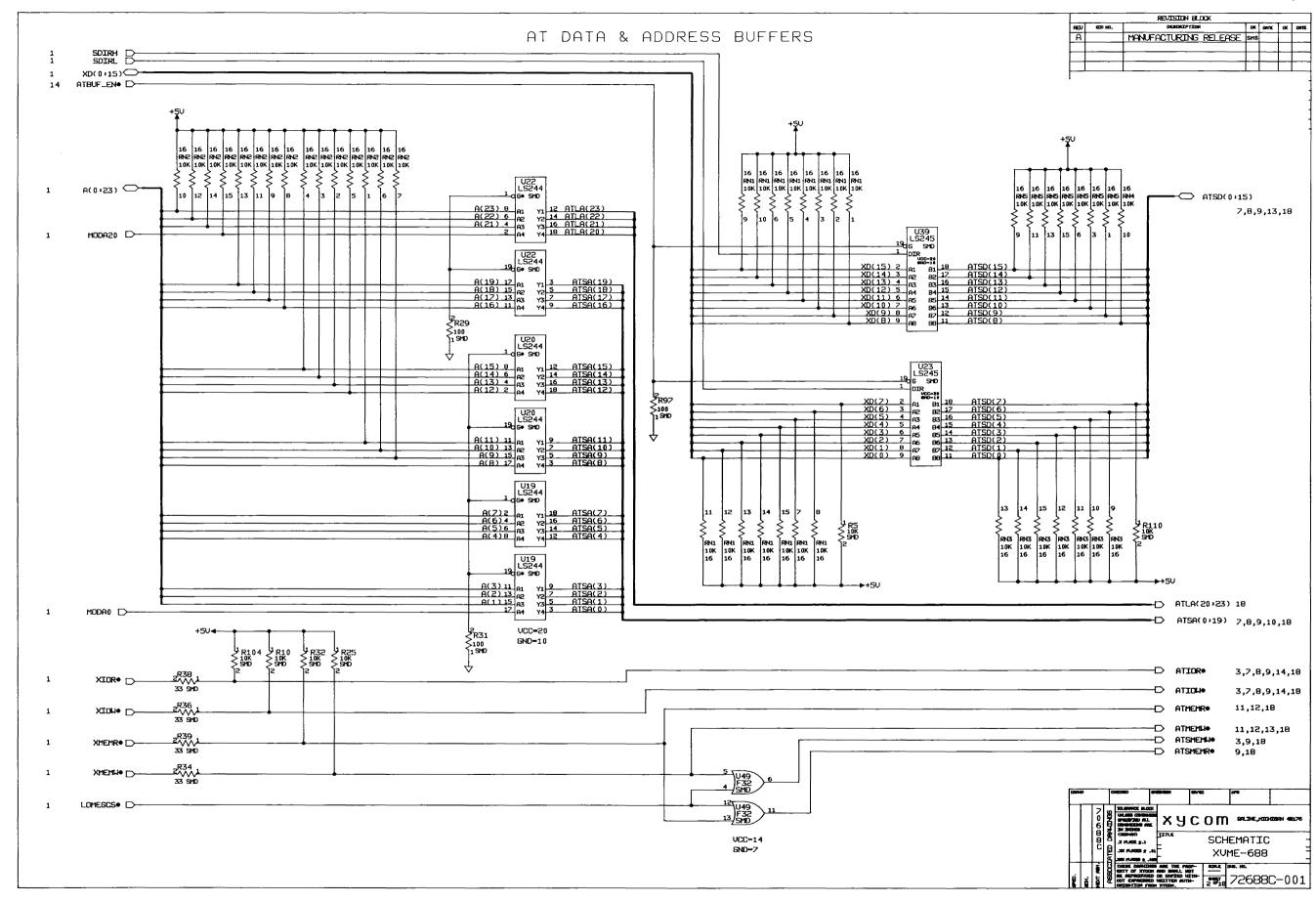

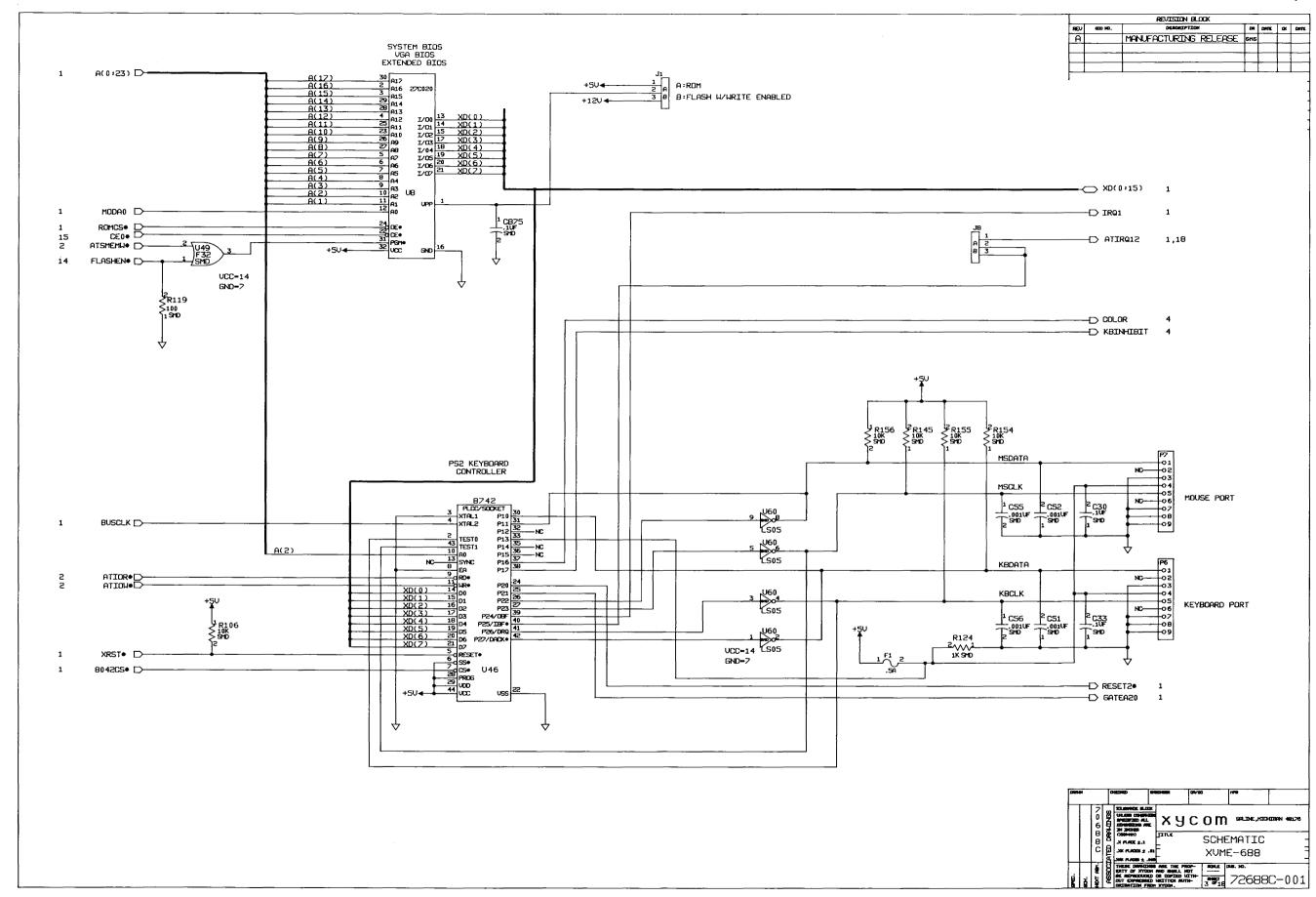

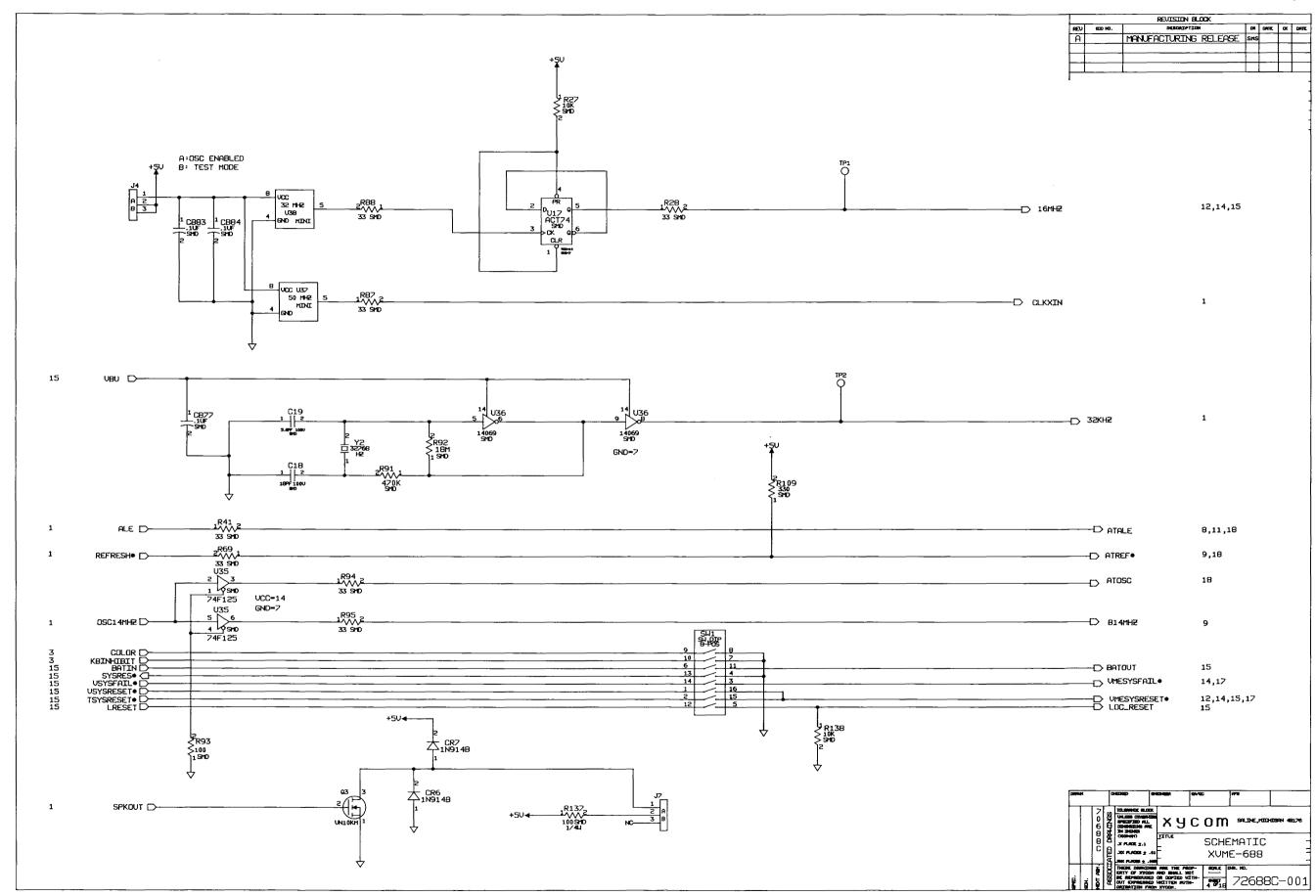

- Appendix D Block Diagrams, Assembly Drawings, and Schematics

# 1.3 XVME-678/688 BOARD OPERATIONAL DESCRIPTION

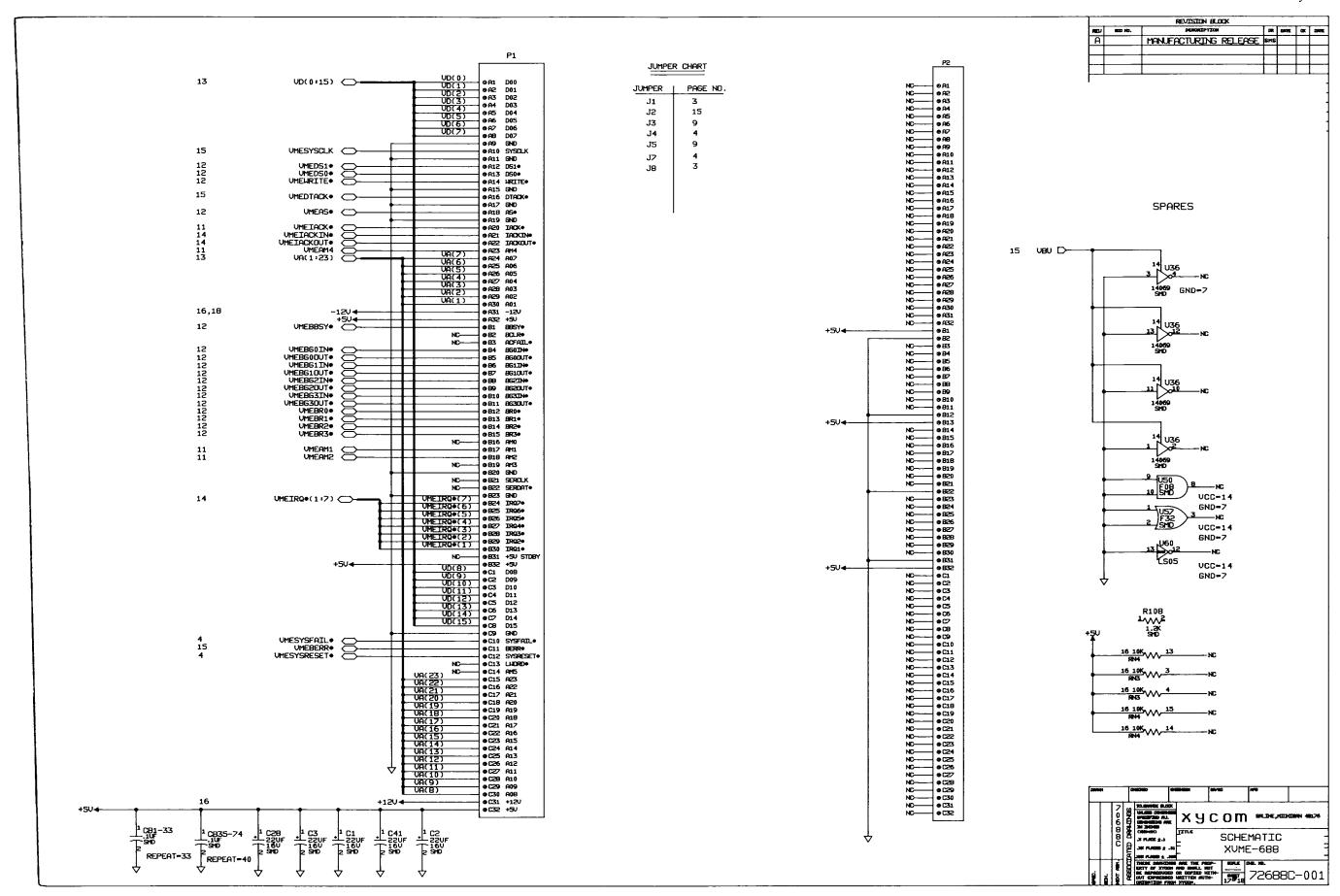

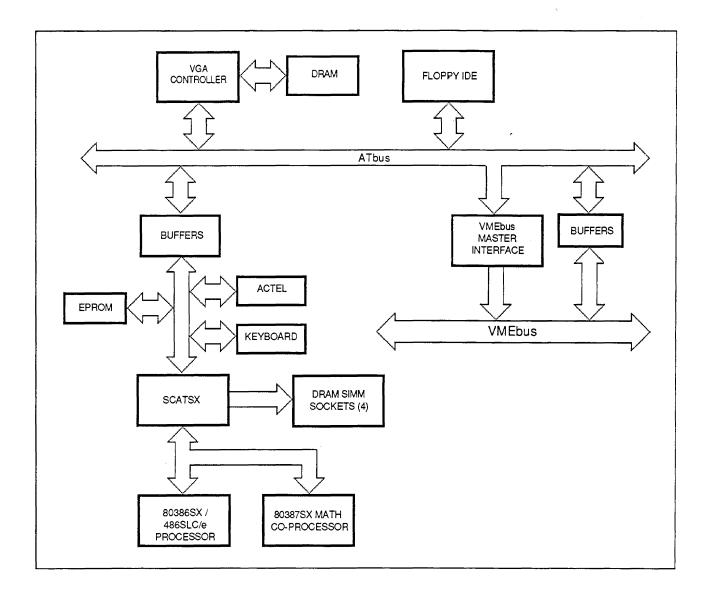

Figure 1-1 shows the logical arrangement of the XVME-678/688 board.

Figure 1-1. XVME-678/688 Board Block Diagram

## 1.3.1 80386SX or 486SLC/e Central Processing Unit (CPU)

The XVME-688 uses an 80386SX microprocessor to provide operational capabilities. The XVME-678 uses a Cyrix 486SLC/e that provides a 486SX-compatible instruction set with a 1 Kbyte internal cache. These 25 MHz CPUs can access up to 16 Mbytes of DRAM.

#### 1.3.2 **DRAM**

The XVME-678/688 uses Dynamic Random Access Memory (DRAM) configured in a page interleave mode with 0 wait-state operation. The 1, 4, and 16 Mbyte versions of the XVME-678/688 are two-way interleaved, while the 2 and 10 Mbyte versions have no interleaving.

The XVME-678/688 comes factory-configured with 0, 1, or 4 Mbytes of DRAM. Additional DRAM can be installed in 2, 10, and 16 Mbyte configurations. Refer to section 2.7 for more information.

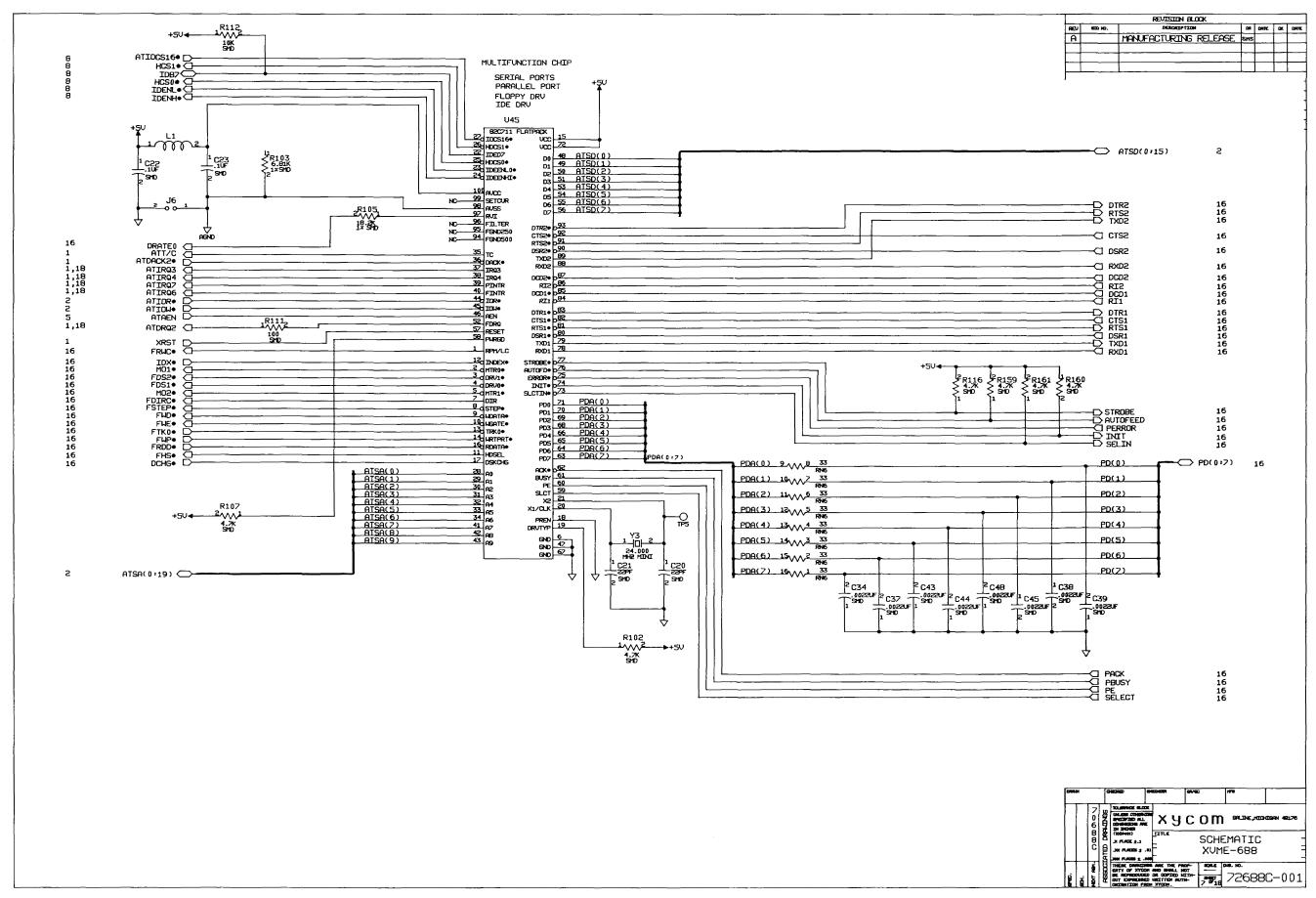

# 1.3.3 Floppy Drive Controller

The XVME-678/688 floppy drive controller can support up to two PC/AT-compatible floppy drives. These drives can be any combination of 360 Kbytes, 720 Kbytes, 1.2 Mbytes, and 1.44 Mbytes.

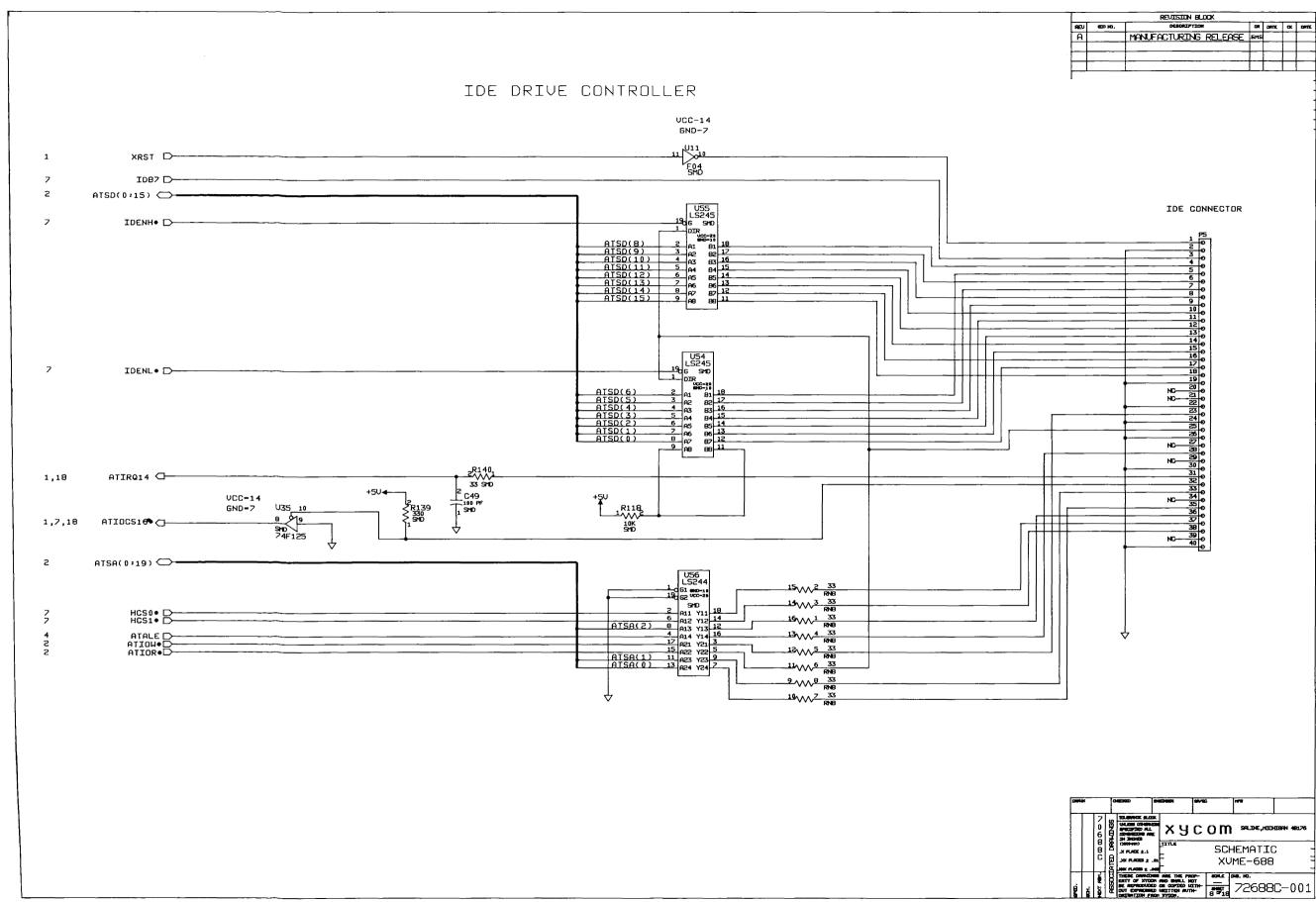

#### 1.3.4 Hard Drive Controller

The XVME-678/688 uses the IDE interface for the hard drive controller. This 16-bit interface provides complete hardware-level compatibility to the IBM PC/AT hard drive controller. Two drives can be connected to the interface by daisy chaining the ribbon cable and setting one drive as the master and one as the slave. (This requires setting jumpers on the drive. Consult your drive manual for more information.)

#### **CAUTION**

The IDE ribbon cable should not exceed 18 inches. Otherwise, errors may occur and data may be corrupted.

Most IDE drives should never be low-level formatted. Check your IDE drive manual for formatting procedures.

### 1.3.5 Graphics Controller

The XVME-678/688 VGA graphics controller supports all IBM VGA, EGA, CGA, and MDA modes to the register level. The VGA adapter supports Super VGA up to 1024 x 768 with 16 colors. The VGA BIOS is 8 bits. Shadowing the BIOS through the BIOS Setup Menu (see Chapter 3 for more information) significantly increases system performance.

The VGA controller supports IBM modes 0-13H (hex) as well as other modes. See Appendix C for a complete list of supported modes.

#### 1.3.6 **I/O Ports**

The XVME-678/688 has two RS-232C serial ports and one IBM PC/AT style Centronics-compatible parallel port. These ports are controlled in the BIOS Setup Menu which allows the ports to be disabled or enabled from software. Interrupts are enabled or disabled by setting bits in I/O registers (refer to Chapter 5).

#### 1.3.7 VMEbus Master Interface

The VMEbus master interface allows the 80386SX CPU to become a master or interrupt handler on the VMEbus. The XVME-678/688 master interface is invoked whenever the 80386SX accesses the VMEbus Standard, Short I/O, or IACK address spaces. All accesses to the VMEbus are through the Real Mode Window.

### 1.3.8 Keyboard Controller

The XVME-678/688 keyboard controller is PS/2 compatible and supports not only the PS/2 keyboard, but also provides an auxiliary input port for a PS/2-compatible mouse, trackball, etc.

# 1.4 **SPECIFICATIONS**

Table 1-1 contains the functional specifications for the XVME-678/688.

Table 1-1. XVME-678/688 Module Specifications

| SPECIFICATION                          | DESCRIPTION                            |

|----------------------------------------|----------------------------------------|

| Mechanical                             |                                        |

| Processor                              |                                        |

| XVME-688                               | 80386SX                                |

| XVME-678                               | 486SLC/e                               |

| Processor Speed                        | 25 MHz                                 |

| AT-bus Speed                           | 10 or 8.33 MHz                         |

| Math Co-processor (optional)           | 80387SX                                |

| Graphics Controller                    | VGA analog output                      |

| Grapmes Controller                     | Max. resolution: 1024 x 768, 16 colors |

| Floppy Disk Interface                  | PC/AT-compatible: supports two         |

| Proppy Disk Interface                  | drives—360 Kbyte, 720 Kbyte, 1.2 Mbyte |

|                                        | and 1.44 Mbyte capacities              |

| Hard Disk Interface                    | IDE controller: supports two drives    |

| PS/2 AUX Port                          | Compatible with PS/2 mouse             |

| Serial Ports (2)                       | RS-232C                                |

| Parallel Port                          | Centronics compatible                  |

| Power Requirements                     | +12 V @ 2 mA max.                      |

| +5 V @ 1.9 A typ., 2.7 A max.          | -12 V @ 1 mA max.                      |

| SIMM Memory Configuration              |                                        |

| SIMM Sites                             | 4                                      |

| Memory Configurations                  | Up to 16* Mbytes                       |

| Memory Accepted                        | 256Kx9, 1Mx9, or 4Mx9                  |

| Memory Speed Required                  | 60 nsec, 0 wait states                 |

|                                        | 80 nsec, 1 wait state                  |

| * 0, 1, and 4 Mbytes of DRAM are avail | lable as factors, configured entires   |

Table 1-1. XVME-678/688 Module Specifications (continued)

| SPECIFICATION  | DESCRIPTION                                            |

|----------------|--------------------------------------------------------|

| Environmental  |                                                        |

| Temperature    |                                                        |

| Operating      | 0° to 65° C (32° to 149°F)                             |

| Non-operating  | -40° to 85°C (-40° to 185°F)                           |

| Humidity       | 5 to 95% RH, non-condensing                            |

| Altitude       |                                                        |

| Operating      | Sea level to 10,000 ft. (3048 m)                       |

| Non-operating  | Sea level to 50,000 ft. (15240 m)                      |

| Vibration      | 5 to 2000 Hz                                           |

| Operating      | .015" peak to peak displacement 2.5 g max acceleration |

| Non-operating  | .030" peak to peak displacement                        |

| rion operating | 5.0 g max acceleration                                 |

| Shock          |                                                        |

| Operating      | 30 g peak acceleration,                                |

|                | 11 msec duration                                       |

| Non-operating  | 50 g peak acceleration,                                |

|                | 11 msec duration                                       |

# **VMEbus**

Complies with VMEbus Specification IEEE 1014 A24/A16:D16/D08(EO) Master R(0-3) Bus Requester Interrupt Handler IH(1)-IH(7) SYSCLK and SYSRESET Driver SGL Arbiter

ROR Option

Form Factor - Double (6U), 233.35 mm x 160 mm (9.2" x 6.3")

#### 2.1 **INTRODUCTION**

This chapter provides the information necessary to configure the XVME-678/688 VMEbus PC/AT Processor Module. It also provides information on installing the XVME-678/688 into a backplane, adding extended BIOS to the XVME-678/688, adding DRAM memory in SIMM sockets, and installing an optional math co-processor.

#### WARNING

If the battery is disabled in your system, please do the following: Upon enabling, your module **must** be powered up for a minimum of 30 seconds. Failure to follow this procedure may result in premature battery failure.

#### WARNING

XVME-678/688 CPU modules with functional revision levels of 4.1 or higher (functional revision levels and part numbers are located on a label on the P1 connector) feature a 16-bit compatible PC/104 expansion site. This PC/104 expansion site requires a new version of the XVME-956 Modular I/O Carrier Module. If the CPU module's functional revision level is 4.1 or higher, use the XVME-956/12 (part number 70956-012). If the functional revision level is less than 4.1, use the XVME-956/2 (part number 70956-002). Do not use the XVME-956/2 on a CPU module with functional revision levels of 4.1 or higher as this may cause damage to both modules.

In addition, the XVME-956/402 SCSI Expansion Module has been updated. The XVME-956/412 must be used with XVME-678/688 modules that have a functional revision level of 4.1 or higher. Use of the XVME-956/402 with the new CPU modules will damage the SCSI Expansion Module and the CPU.

Please contact Xycom's Customer Service Department at 1-800-289-9266 for assistance.

#### **NOTE**

The XVME-678/688 module obtains power from both the VMEbus P1 and P2 backplanes. However, only P1 is necessary for proper operation.

# 2.2 **JUMPERS**

All of the jumpers on the XVME-678/688 are shipped in the correct positions. The unit will function as required with no modifications.

# NOTE

Jumpers only need to be modified when disabling VGA or replacing the BIOS EPROM with Flash RAM devices.

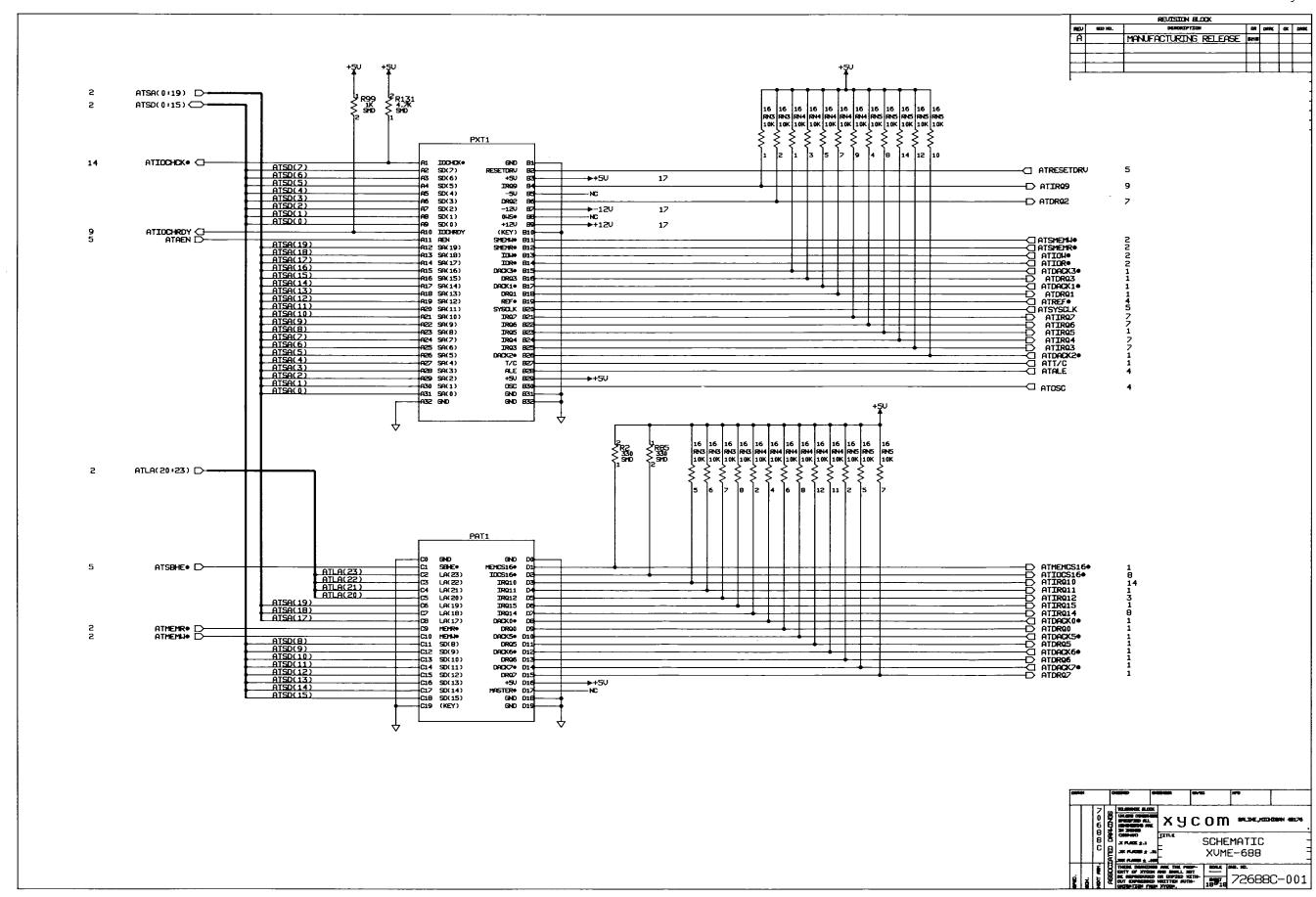

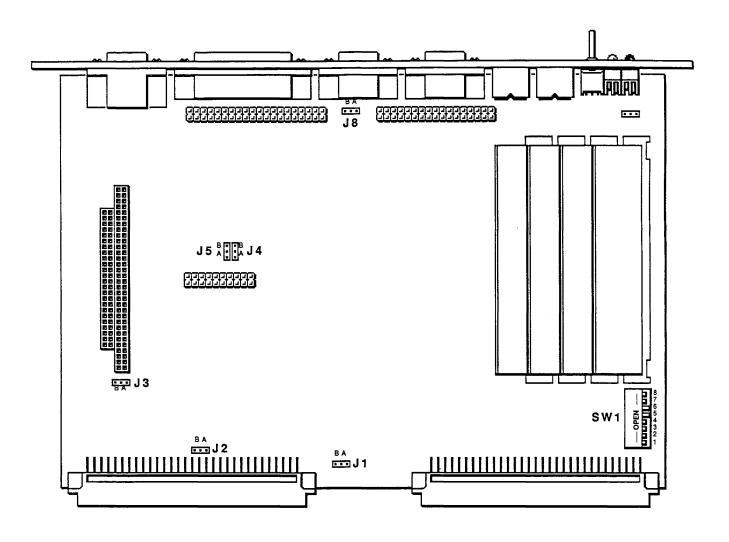

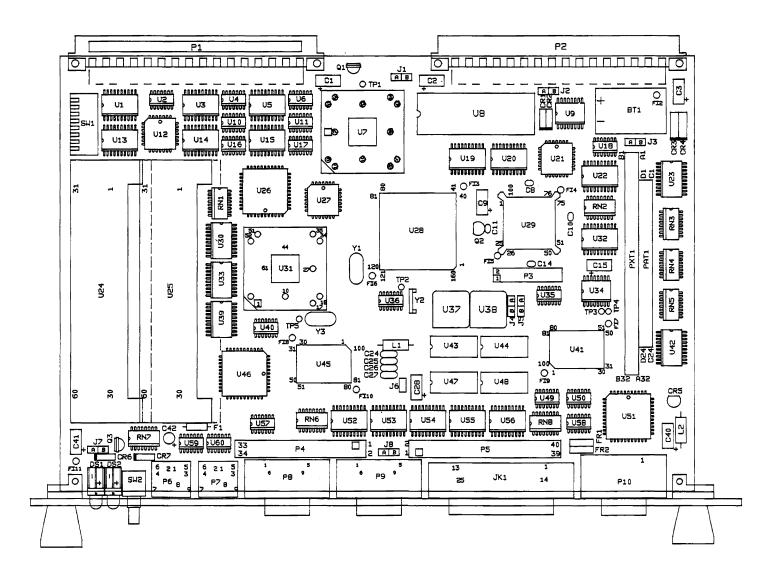

Jumper locations on the XVME-678/688 module are shown in Figure 2-1. The jumpers are described in Table 2-1.

Figure 2-1. XVME-678/688 Jumper and Switch Locations

Table 2-1. XVME-678/688 Jumper Options

| Jumper | Position        | Function                                                                       | Section Reference |

|--------|-----------------|--------------------------------------------------------------------------------|-------------------|

| J1     | A <b>√</b><br>B | Sets EPROM or Flash RAM to non-writable +5V<br>Sets Flash RAM to +12V          | 2.2.2             |

| J2     | A <b>√</b><br>B | Enables battery Disables battery                                               | 2.2.4             |

| J3     | A <b>√</b><br>B | IRQ9 is driven by VGA controller IRQ9 is not driven by the VGA controller      | 2.2.1             |

| J4     | A <b>√</b><br>B | Test jumper that supplies Vcc to OSC Test jumper that disconnects Vcc from OSC | 2.2.4             |

| J5     | A <b>√</b><br>B | Enables VGA<br>Disables VGA                                                    | 2.2.1             |

| 18     | A <b>√</b><br>B | IRQ12 driven for auxiliary port IRQ12 not driven for auxiliary port            | 2.2.3             |

<sup>✓</sup> indicates default settings

# 2.2.1 VGA Jumpers (J3, J5)

Jumper J5 enables the VGA BIOS and Xycom Setup when positioned to A (default) or disables the VGA BIOS and XYCOM Setup when positioned to B.

Jumper J3 should be set to A (default) for IRQ9 to be driven by the VGA, or to B for IRQ9 not to be driven by the VGA.

# 2.2.2 EPROM/Flash Jumper (J1)

Jumper J1 sets EPROM and Flash RAM devices to a non-writable +5V when positioned to A (default). When positioned to B, J1 sets Flash RAM devices to +12V.

# 2.2.3 **IRQ12 Jumper (J8)**

Jumper J8 allows the PS/2 auxiliary port to drive IRQ12 when positioned to A (default). When positioned to B, the PS/2 port does not drive IRQ12.

# 2.2.4 Battery and Test Jumpers (J2, J4)

Jumper J2 enables the XVME-678/688 on-board battery when positioned to A (default), and disables the battery when positioned to B. This jumper should remain positioned to A. To disable the battery, position switch 6 of SW1 to open (see Section 2.3). See WARNING in Section 2.1 regarding a disabled battery.

Jumper J4 is a test jumper that supplies Vcc to OSC. This jumper must always remain positioned to A.

#### 2.3 SWITCH SETTINGS

The XVME-678/688 has one eight-position switch, SW1. This switch allows critical options, which are not software accessible, to be enabled in a common area. Figure 2-1 on page 2-2 shows the switch location. The settings and their functions are shown in the table below.

| Position | Setting                 | Function                                                                                                  |

|----------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| 1        | Open<br>Closed√         | VME SYSRESET* is not driven on the VMEbus at power-up. VME SYSRESET* is driven on the VMEbus at power-up. |

| 2        | Open<br>Closed√         | VME SYSRESET* is not caused by the toggle switch.  VME SYSRESET* is caused by the toggle switch.          |

| 3        | Open <b>√</b><br>Closed | VME SYSFAIL is not driven on the VMEbus. VME SYSFAIL is driven on the VMEbus.                             |

| 4        | Open<br>Closed√         | VME system resource function is disabled. VME system resource function is enabled.                        |

| 5        | Open <b>√</b>           | Not user configurable. Must remain open.                                                                  |

| 6        | Open <b>√</b><br>Closed | Disables the battery. Enables the battery.                                                                |

| 7        | Open <b>√</b><br>Closed | Enables the keyboard.  Disables the keyboard.                                                             |

| 8        | Open <b>√</b><br>Closed | Enables color video. Enables monochrome video.                                                            |

Table 2-2. XVME-678/688 SW1 Switch Settings

<sup>✓</sup> indicates default settings

#### **NOTE**

The battery enable switch (SW6) is shipped in the OPEN position. Close this switch to allow the CMOS configuration to be retained on power-down.

# 2.4 CONNECTORS

The XVME-678/688 has 12 connectors:

- IDE hard drive

- Floppy drive

- Parallel port

- COM1 and COM2 serial ports

- PS/2 AUX port

- VGA

- Keyboard

- Speaker

- VMEbus P1 and P2

- PC/104-compatible expansion site

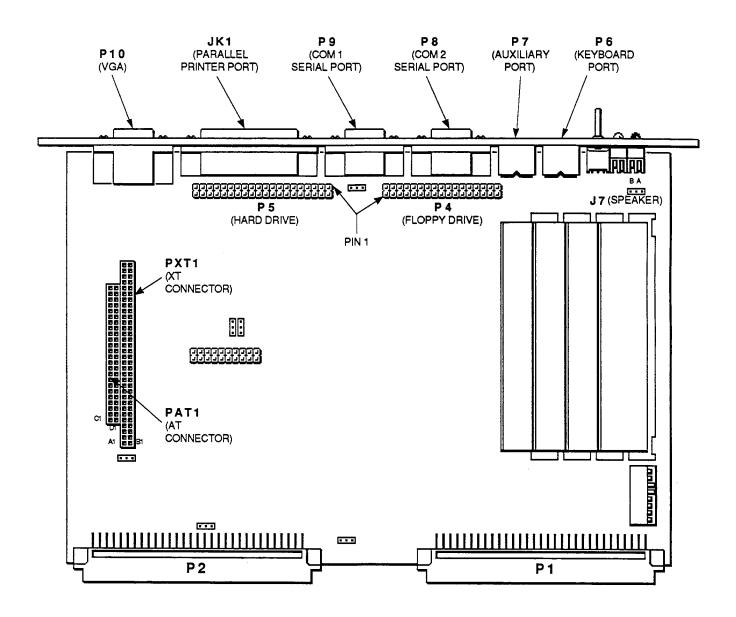

The connectors must be clean, dry, and undamaged at the time of installation. Figure 2-2 on the following page shows the location of the connectors on the board.

# **NOTE**

All connector locations are labeled on the circuit card.

Figure 2-2. XVME-678/688 Connector Locations

# 2.4.1 VMEbus P1 Connector

VMEbus P1 is a 96-pin DIN connector.

Table 2-3. P1 Pinouts

| Table 2-3. F1 Finous |              |              |              |

|----------------------|--------------|--------------|--------------|

| Pin                  | Row A Signal | Row B Signal | Row C Signal |

| 1                    | D0           | BBUSY        | D08          |

| 2                    | D01          | BCLR*        | D09          |

| 2 3                  | D02          | ACFAIL*      | D10          |

| 4                    | D03          | BG0IN*       | D11          |

| 5                    | D04          | BG0OUT*      | D12          |

| 6                    | D05          | BG1IN*       | D13          |

| 7                    | D06          | BG1OUT*      | D14          |

| 8                    | D07          | BG2IN*       | D15          |

| 9                    | GND          | BG2OUT*      | GND          |

| 10                   | SYSCLK       | BG3IN*       | SYSFAIL*     |

| 11                   | GND          | BG3OUT*      | BERR*        |

| 12                   | DS1*         | BR0*         | SYSRESET*    |

| 13                   | DS0*         | BR1*         | LWORD*       |

| 14                   | WRITE*       | BR2*         | AM5          |

| 15                   | GND          | BR3*         | A23          |

| 16                   | DTACK*       | AM0          | A22          |

| 17                   | GND          | AM1          | A21          |

| 18                   | AS*          | AM2          | A20          |

| 19                   | GND          | AM3          | A19          |

| 20                   | IACK*        | GND          | A18          |

| 21                   | IACKIN*      | SERCLK       | A17          |

| 22                   | IACKOUT*     | SERDAT*      | A16          |

| 23                   | AM4          | GND          | A15          |

| 24                   | A07          | IRQ7*        | A14          |

| 25                   | A06          | IRQ6*        | A13          |

| 26                   | A05          | IRQ5*        | A12          |

| 27                   | A04          | IRQ4*        | A11          |

| 28                   | A03          | IRQ3*        | A10          |

| 29                   | A02          | IRQ2*        | A09          |

| 30                   | A01          | IRQ1*        | A08          |

| 31                   | -12V         | +5V STDBY    | +12V         |

| 32                   | +5V          | +5V          | +5V          |

# 2.4.2 VMEbus P2 Connector

VMEbus P2 is a 96-pin DIN connector.

Table 2-4. P2 Pinouts

| Pin | Row A Signal | Row B Signal | Row C Signal |

|-----|--------------|--------------|--------------|

| 1   | N/C          | +5V          | N/C          |

| 2   | N/C          | GND          | N/C          |

| 3   | N/C          | N/C          | N/C          |

| 4   | N/C          | N/C          | N/C          |

| 5   | N/C          | N/C          | N/C          |

| 6   | N/C          | N/C          | N/C          |

| 7   | N/C          | N/C          | N/C          |

| 8   | N/C          | N/C          | N/C          |

| 9   | N/C          | N/C          | N/C          |

| 10  | N/C          | N/C          | N/C          |

| 11  | N/C          | N/C          | N/C          |

| 12  | N/C          | GND          | N/C          |

| 13  | N/C          | +5V          | N/C          |

| 14  | N/C          | N/C          | N/C          |

| 15  | N/C          | N/C          | N/C          |

| 16  | N/C          | N/C          | N/C          |

| 17  | N/C          | N/C          | N/C          |

| 18  | N/C          | N/C          | N/C          |

| 19  | N/C          | N/C          | N/C          |

| 20  | N/C          | N/C          | N/C          |

| 21  | N/C          | N/C          | N/C          |

| 22  | N/C          | GND          | N/C          |

| 23  | N/C          | N/C          | N/C          |

| 24  | N/C          | N/C          | N/C          |

| 25  | N/C          | N/C          | N/C          |

| 26  | N/C          | N/C          | N/C          |

| 27  | N/C          | N/C          | N/C          |

| 28  | N/C          | N/C          | N/C          |

| 29  | N/C          | N/C          | N/C          |

| 30  | N/C          | N/C          | N/C          |

| 31  | N/C          | GND          | N/C          |

| 32  | N/C          | +5V          | N/C          |

# 2.4.3 Floppy Drive Connector (P4)

The floppy drive connector is a 34-pin header located on the board near P8, the COM2 serial port connector. It is the interface and control connection for up to two floppy drives.

Table 2-5. Floppy Drive Connector

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | GND    | 18  | FDIRC* |

| 2   | FRWC*  | 19  | GND    |

| 3   | GND    | 20  | FSTEP* |

| 4   | N/C    | 21  | GND    |

| 5   | KEY    | 22  | FWD*   |

| 6   | N/C    | 23  | GND    |

| 7   | GND    | 24  | FWE*   |

| 8   | IDX*   | 25  | GND    |

| 9   | GND    | 26  | FTK0*  |

| 10  | MO1    | 27  | GND    |

| 11  | GND    | 28  | FWP*   |

| 12  | FDS2   | 29  | GND    |

| 13  | GND    | 30  | FRDD*  |

| 14  | FDS1   | 31  | GND    |

| 15  | GND    | 32  | FHS*   |

| 16  | MO2    | 33  | GND    |

| 17  | GND    | 34  | DCHG*  |

# 2.4.4 **IDE Hard Drive Connector (P5)**

The IDE hard drive connector is a 40-pin header located near JK1, the parallel port. It is the control connector for any hard drive(s) interfaced with the XVME-678/688. The XVME-678/688 can control up to two hard drives from this connector.

Table 2-6. IDE Hard Drive Connector

| Pin | Signal | Pin | Signal    |

|-----|--------|-----|-----------|

| 1   | RESET* | 21  | N/C       |

| 2   | GND    | 22  | GND       |

| 3   | ID87   | 23  | IOW*      |

| 4   | SD8    | 24  | GND       |

| 5   | SD6    | 25  | IOR*      |

| 6   | SD9    | 26  | GND       |

| 7   | SD5    | 27  | N/C       |

| 8   | SD10   | 28  | ALE       |

| 9   | SD4    | 29  | N/C       |

| 10  | SD11   | 30  | GND       |

| 11  | SD3    | 31  | ATIRQ14   |

| 12  | SD12   | 32  | ATIOCS16* |

| 13  | SD2    | 33  | SA1       |

| 14  | SD13   | 34  | N/C       |

| 15  | SD1    | 35  | SA0       |

| 16  | SD14   | 36  | SA2       |

| 17  | SD0    | 37  | HCS0      |

| 18  | SD15   | 38  | HCS1      |

| 19  | GND    | 39  | N/C       |

| 20  | N/C    | 40  | GND       |

# 2.4.5 Keyboard Connector (P6)

P6, a 6-pin MINI DIN connector, serves as the interface point for a keyboard. An interface cable is shipped with the XVME-678/688 so a standard PC/AT keyboard can be used.

| Pin | Signal |  |  |

|-----|--------|--|--|

| 1   | DATA   |  |  |

| 2   | NC     |  |  |

| 3   | GND    |  |  |

| 4   | +5V    |  |  |

| 5   | CLK    |  |  |

| 6   | N/C    |  |  |

Table 2-7. Keyboard Connector

# 2.4.6 Auxiliary Connector (P7)

P7 is a PS/2-compatible, 6-pin MINI DIN connector. This port accepts a PS/2-compatible mouse, track ball, etc.

| Pin | Signal |

|-----|--------|

| 1   | DATA   |

| 2   | NC     |

| 3   | GND    |

| 4   | +5V    |

| 5   | CLK    |

| 6   | N/C    |

Table 2-8. Auxiliary Connector

# 2.4.7 COM2 Serial Port Connector (P8)

The 9-pin D subminiature COM2 serial port connector is located on the module's front panel.

Pin Signal Pin Signal 1 DCD2 6 DSR2 2 RXD2 7 RTS2 3 TXD2 8 CTS2 4 9 DTR2 RI2 5 **GND**

Table 2-9. COM2 Serial Port Connector

# 2.4.8 COM1 Serial Port Connector (P9)

The 9-pin D subminiature COM1 serial port connector, P9, is located on the module's front panel.

Table 2-10. COM1 Serial Port Connector

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | DCD1   | 6   | DSR1   |

| 2   | RXD1   | 7   | RTS1   |

| 3   | TXD1   | 8   | CTS1   |

| 4   | DTR1   | 9   | RI1    |

| 5   | GND    |     |        |

# 2.4.9 VGA Connector (P10)

The VGA connector, P10, is a 15-pin subminiature located at the bottom of the module's front panel.

Table 2-11. VGA Connector

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | RED    | 9   | KEY    |

| 2   | GREEN  | 10  | GND    |

| 3   | BLUE   | 11  | N/C    |

| 4   | N/C    | 12  | N/C    |

| 5   | GND    | 13  | HSYNC  |

| 6   | GND    | 14  | VSYNC  |

| 7   | GND    | 15  | N/C    |

| 88  | GND    |     |        |

# 2.4.10 Parallel Port Connector (JK1)

JK1 is a 25-pin female D subminiature connector located on the module's front panel.

Table 2-12. Parallel Port Connector

| Pin | Signal | Pin | Signal   |

|-----|--------|-----|----------|

| 1   | STROBE | 14  | AUTOFEED |

| 2   | PDOUT0 | 15  | PERROR   |

| 3   | PDOUT1 | 16  | INIT     |

| 4   | PDOUT2 | 17  | SELIN    |

| 5   | PDOUT3 | 18  | GND      |

| 6   | PDOUT4 | 19  | GND      |

| 7   | PDOUT5 | 20  | GND      |

| 8   | PDOUT6 | 21  | GND      |

| 9   | PDOUT7 | 22  | GND      |

| 10  | PACK   | 23  | GND      |

| 11  | PBUSY  | 24  | GND      |

| 12  | PE     | 25  | GND      |

| 13  | SELECT |     |          |

# 2.4.11 Speaker Connector (J7)

J7 is a three-pin header located on the board near the LEDs.

Table 2-13. Speaker Connector

| Pin | Signal |

|-----|--------|

| 1   | SIGNAL |

| 2   | +5V    |

| 3   | N/C    |

# 2.4.12 **PXT1 Connector**

The PC/104-compatible PXT1 is a two-row, 64-pin connector. It allows a single card expansion to XVME-678/688 without an adapter card. This interface incorporates the power that allows plug-in adapters to be free of the need for a P1 or P2 connection.

Table 2-14. PXT1 Pinouts

| Pin | Row A Signal | Row B Signal |

|-----|--------------|--------------|

| 1   | IOCHCHK*     | GND          |

| 2   | SD7          | RESETDRV     |

| 3   | SD6          | +5V          |

| 4   | SD5          | IRQ9         |

| 5   | SD4          | N/C          |

| 6   | SD3          | DRQ2         |

| 7   | SD2          | -12V         |

| 8   | SD1          | N/C          |

| 9   | SD0          | +12V         |

| 10  | IOCHRDY      | KEY          |

| 11  | AEN          | SMEMW*       |

| 12  | SA19         | SMEMR*       |

| 13  | SA18         | IOW*         |

| 14  | SA17         | IOR*         |

| 15  | SA16         | DACK3*       |

| 16  | SA15         | DRQ3         |

| 17  | SA14         | DACK1*       |

| 18  | SA13         | DRQ1         |

| 19  | SA12         | REF*         |

| 20  | SA11         | SYSCLK       |

| 21  | SA10         | IRQ7         |

| 22  | SA9          | IRQ6         |

| 23  | SA8          | IRQ5         |

| 24  | SA7          | IRQ4         |

| 25  | SA6          | IRQ3         |

| 26  | SA5          | DACK2*       |

| 27  | SA4          | T/C          |

| 28  | SA3          | ALE          |

| 29  | SA2          | +5V          |

| 30  | SA1          | OSC          |

| 31  | SA0          | GND          |

| 32  | GND          | GND          |

# 2.4.13 PAT1 Connector

PAT1 is a two-row, 40-pin connector that allows a single card expansion to XVME-678/688 without an adapter card. This interface incorporates the power that allows plug-in adapters to be free of the need for a P1 or P2 connection.

Table 2-15. PAT1 Pinouts

| Pin | Row C Signal | Row D Signal |

|-----|--------------|--------------|

| 0   | GND          | GND          |

| 1   | SBHE*        | MEMCS16*     |

| 2   | LA23         | IOCS16*      |

| 3   | LA22         | IRQ10        |

| 4   | LA21         | IRQ11        |

| 5   | LA20         | IRQ12        |

| 6   | LA19         | IRQ15        |

| 7   | LA18         | IRQ14        |

| 8   | LA17         | DACK0*       |

| 9   | MEMR*        | DRQ0         |

| 10  | MEMW*        | DACK5*       |

| 11  | SD8          | DRQ5         |

| 12  | SD9          | DACK6*       |

| 13  | SD10         | DRQ6         |

| 14  | SD11         | DACK7*       |

| 15  | SD12         | DRQ7         |

| 16  | SD13         | +5V          |

| 17  | SD14         | N/C          |

| 18  | SD15         | GND          |

| 19  | KEY          | GND          |

#### 2.5 INSTALLING THE XVME-678/688 INTO A BACKPLANE

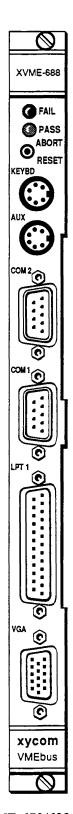

This section provides the information necessary to install the XVME-678/688 PC/AT Processor Module into the VMEbus backplane.

Xycom modules are designed to comply with all physical and electrical VMEbus backplane specifications. The XVME-678/688 is a double-high, single-board VMEbus module. As such, it requires one slot with either just the P1 VMEbus backplane, or with both the P1 and P2 backplanes.

The XVME-955 Hard Disk/Floppy Disk Module, available from Xycom, is ideally suited for use with the XVME-678/688. It combines a high-capacity 3.5" IDE drive and a 3.5" 1.44 Mbyte micro-floppy into a unit that occupies only two double-high VMEbus slots. Ask your Xycom representative for details.

#### WARNING

Do **not** install or remove any boards before turning off the power to the bus and all related external power supplies.

- 1. Disconnect all power supplies to the backplane and/or terminal.

- 2. Make sure the backplane P1 and P2 connectors are accessible.

- 3. Verify all jumper settings.

- 4. If using the Intel 80387SX math co-processor, install it in socket U7 of the XVME-678/688. Refer to Section 2.8 for more detailed diagrams.

- 5. Position SW1 switch 6 to closed to enable the on-board battery.

- 6. Connect the floppy disk cable to P4 on the component side of the XVME-678/688 board. Refer to Figure 2-2 on page 2-6 for the location of P4.

- 7. Connect the IDE hard drive cable to P5 on the component side of the XVME-678/688 module. Refer to Figure 2-2 on page 2-6 for the location of P5.

- 8. Turn **OFF** power to the VMEbus cardcage and disconnect the power cable.

- 9. Make sure the cardcage slot that will hold the XVME-678/688 is clear and accessible. If using the XVME-678/688 in conjunction with the XVME-955 module, make sure that the two cardcage slots to the right of the XVME-678/688 (which will hold the XVME-955) are also clear.

- 10. Install the XVME-678/688 into the cardcage by centering the unit on the plastic guides in the slots (P1 connector facing up) and pushing the boards slowly toward the rear of the chassis until the P1 and P2 connectors engage. The boards should slide freely in the plastic guides.

#### **CAUTION**

Do not use excessive force or pressure to engage the connectors. If the boards do not properly connect with the backplane, remove the module and inspect all connectors and guide slots for possible damage or obstructions.

- 11. Secure the module to the chassis by tightening the machine screw at the top and bottom of each board.

- 12. Connect all remaining peripherals by attaching each interface cable into the appropriate connector on the front of the XVME-678/688 board as follows: VGA cable—VGA, keyboard—KEYBD, serial devices—COM1 and COM2, and parallel device—LPT1. Refer to Figure 2-2 on page 2-6 for locations of these connectors.

Assuming the steps in the previous sections of this chapter have been followed, the power to the VMEbus cardcage can now be turned **ON**.

Figure 2-3. XVME-678/688 Board Front Panel

#### 2.6 ADDING EXTENDED BIOS

The XVME-678/688 has one 256Kx8 EPROM that can represent the entire IBM BIOS range. The device address is the physical address which is viewed from an EPROM programmer such as a Data I/O. The system address is the address the code appears at when plugged into the EPROM site on the XVME-678/688, as addressed by the 80386SX processor.

A diagram of the XVME-678/688 and EPROM programmer addresses is shown below:

| Device Address |                    | System Address |

|----------------|--------------------|----------------|

| 30000-3FFFFF   | System BIOS<br>64K | F0000-FFFFF    |

| 20000-2FFFF    | Diagnostics<br>64K | E0000-0EFFFF   |

| 10000-1FFFF    | User Area<br>64K   | D0000-DFFFF    |

| 08000-0FFFF    | User Area<br>32K   | C8000-CFFFF    |

| 00000-07FFF    | Video BIOS<br>32K  | C0000-C7FFF    |

Adding on-board extended BIOS to the XVME-678/688 involves two major steps: programming the EPROM and setting the Extended BIOS Setup Menu.

# Programming the EPROM

Before beginning, make sure your EPROM programmer supports 2-Mbit devices.

- 1. Remove the 32-pin EPROM from socket U8.

- 2. Place the EPROM into the EPROM programmer's socket.

- 3. Load the EPROM into the RAM of the programmer. Set the starting address at 0H.

- 4. Remove the EPROM from the socket.

#### NOTE

At this point, the data should be stored to a disk to protect the information in case of an error in programming.

- 5. Use a UV light to erase the EPROM.

- 6. Place your extended EPROM programmer RAM starting at location 10000H. The code should not exceed 64 Kbytes.

- 7. Reburn the EPROM with the new code. This places the new extended BIOS in the D000:0000-D000:FFFF block.

#### NOTE

At this point, the data should be stored to a disk to protect the information in case of an error in programming.

8. Place the EPROM back into socket U8 on the XVME-678/688.

# Setting the EPROM Menu

- 1. Power-up the XVME-678/688. After the memory tests, press < Ctrl> < Alt> < S> simultaneously to enter the Extended BIOS Menu.

- 2. Use the arrow keys to highlight Solid State Disk Setup and press < Enter > to select this menu.

- 3. Enable the on-board extended BIOS from D0000-DFFFF and disable the BIOS from E0000-EFFFF.

- 4. Select F10 to save the configuration, and then press  $\langle Esc \rangle$  to exit the menu.

The procedure is now complete.

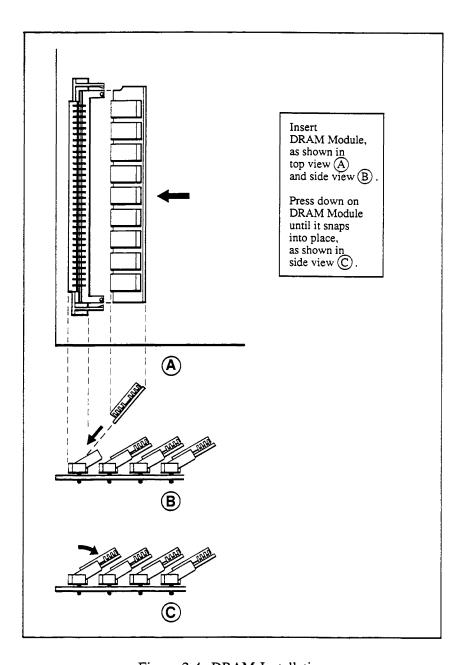

#### 2.7 **INSTALLING DRAM**

The XVME-678/688 has four SIMM sites in which to add memory. Due to the 25 MHz CPU speed, the access time of the DRAM interface is very important. To run at 0 wait states, the SIMMs must have the following access times:

- 60 ns access time for nine chip DRAM SIMMs

- 70 ns access time for three chip DRAM SIMMs

If you opt for 80 ns DRAMs, change the 0 wait state option to 1 wait state in the Setup Menu.

#### **NOTE**

Three-chip memory modules are recommended to meet the VME height specifications.

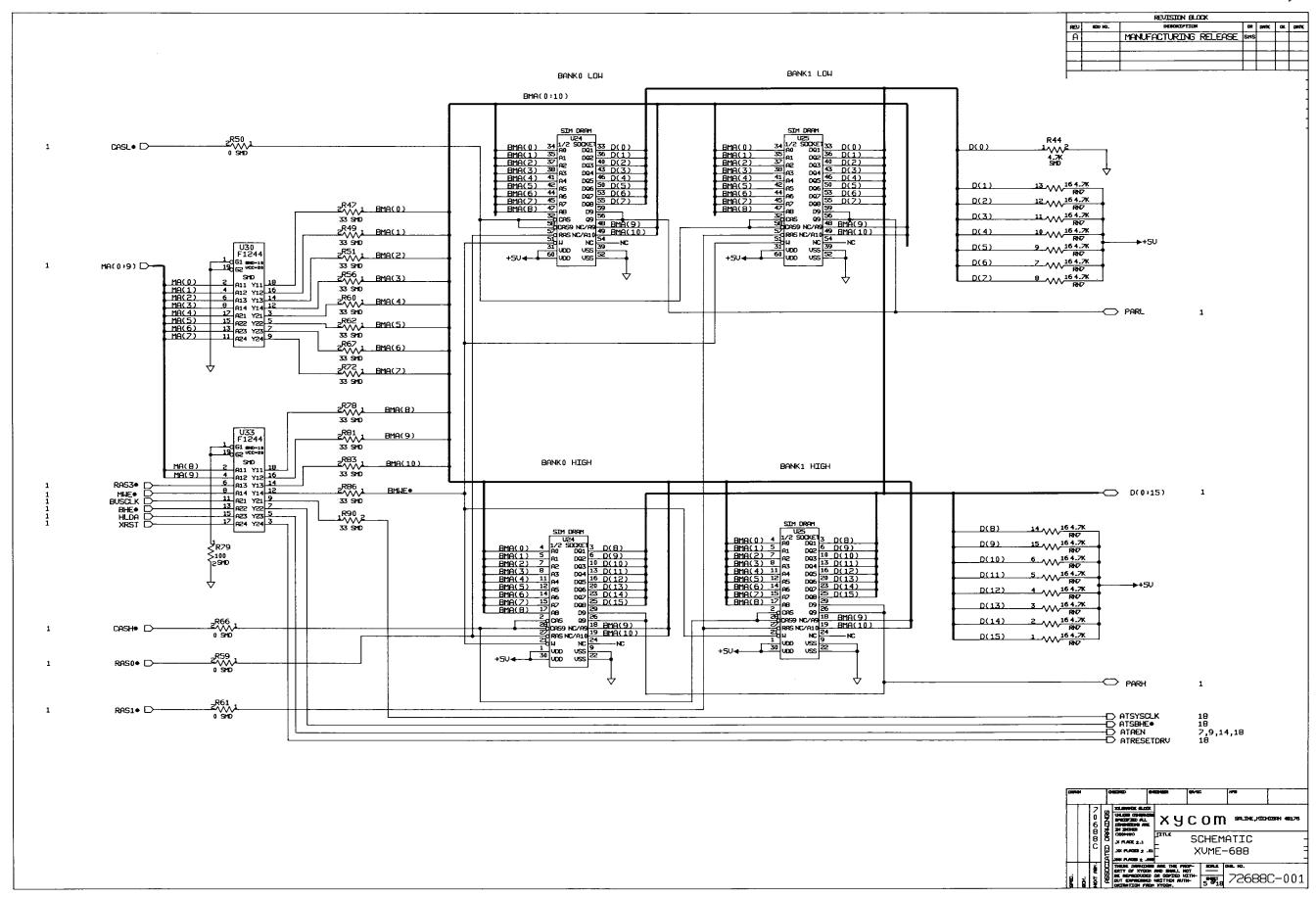

The XVME-678/688 can accommodate 1, 2, 4, 10 or 16 Mbytes of DRAM, mounted on SIMM strips. SIMM strips with 256Kx9, 1Mx9, or 4Mx9 DRAM may be used. The table below lists the combinations needed for the five memory configurations. (The bank location is silk screened on the back of the board.)

| Memory    | Bank 0 low | Bank 0 high | Bank 1 low | Bank 1 high |

|-----------|------------|-------------|------------|-------------|

| 1 Mbyte   | 265Kx9     | 265Kx9      | 256Kx9     | 256Kx9      |

| 2 Mbytes  | 1Mx9       | 1Mx9        | N/A        | N/A         |

| 4 Mbytes  | 1Mx9       | 1Mx9        | 1Mx9       | 1Mx9        |

| 10 Mbytes | 1Mx9       | 1Mx9        | 4Mx9       | 4Mx9        |

| 16 Mbytes | 4Mx9       | 4Mx9        | 4Mx9       | 4Mx9        |

Table 2-16. Bank and SIMM Size

## 1 Mbyte Memory

The 1 Mbyte DRAM is divided into 640 and 384 Kbyte blocks for 80386SX accesses when the Shadow RAM option is not enabled. The 640 Kbyte block resides from 000000-09FFFF; the 384 Kbyte block from 100000-15FFFF. If the shadow RAM option is enabled, the DRAM is reduced to the lower 640 Kbytes of DRAM.

Four 256Kx9 memory SIMMs are needed for the 1 Mbyte configuration.

# 2 Mbytes Memory

The 2 Mbyte version has 1.64 Mbytes of DRAM divided as 640 Kbyte and 1 Mbyte blocks. The additional 384 Kbytes of DRAM are dedicated for Shadow RAM and are not relocatable. Because this configuration uses only two SIMMs, there is no interleaving. This configuration tends to be less optimal for performance than the other memory configurations.

Two 1Mx9 SIMMs are needed for the 2 Mbyte configuration.

# 4 Mbytes Memory

The 4 Mbyte version has 3.64 Mbytes of DRAM divided as 640 Kbyte and 3 Mbyte blocks. The additional 384 Kbytes of DRAM are dedicated for Shadow RAM and are not relocatable.

Four 1Mx9 SIMMs are needed for the 4 Mbyte configuration.

# 10 Mbytes Memory

The 10 Mbyte version has 9.64 Mbytes of DRAM divided as 640 Kbyte and 9 Mbyte blocks. The additional 384 Kbytes of DRAM are dedicated for Shadow RAM and are not relocatable. Because this configuration uses two SIMMs of different sizes, there is no interleaving. This configuration tends to be less optimal for performance than the others.

Two 4Mx9 SIMMs and two 1Mx9 SIMMs are needed for the 10 Mbyte configuration.

# 16 Mbytes Memory

The 16 Mbyte version has 15.64 Mbytes of DRAM divided as 640 Kbyte and 15 Mbyte blocks. The additional 384 Kbytes of DRAM are dedicated for Shadow RAM and are not relocatable.

Four 4Mx9 SIMMs are needed for the 16 Mbyte configuration.

#### Installation Procedure

- 1. Turn off power to the XVME-678/688.

- 2. Refer to Table 2-16 on page 2-21 and select the appropriate type of SIMMs for your memory configuration, and install them into the appropriate banks.

- 3. Refer to Figure 2-4 on the next page. For easiest access to the SIMM sockets, install the strips in the sockets from right to left (referenced with P1 and P2 facing down). Insert the contact edge of the SIMM strip into the socket with the chips on the strip facing up. Be sure the edge of the strip is aligned in the socket. Press down firmly on the strip until it snaps into place.

Figure 2-4. DRAM Installation

To remove a strip, pull gently outward on the two metal tabs on either end of the socket. The strip should loosen in the socket and pop forward slightly for removal.

# **CAUTION**

Do not pull too hard on the metal tabs or they could snap off the socket.

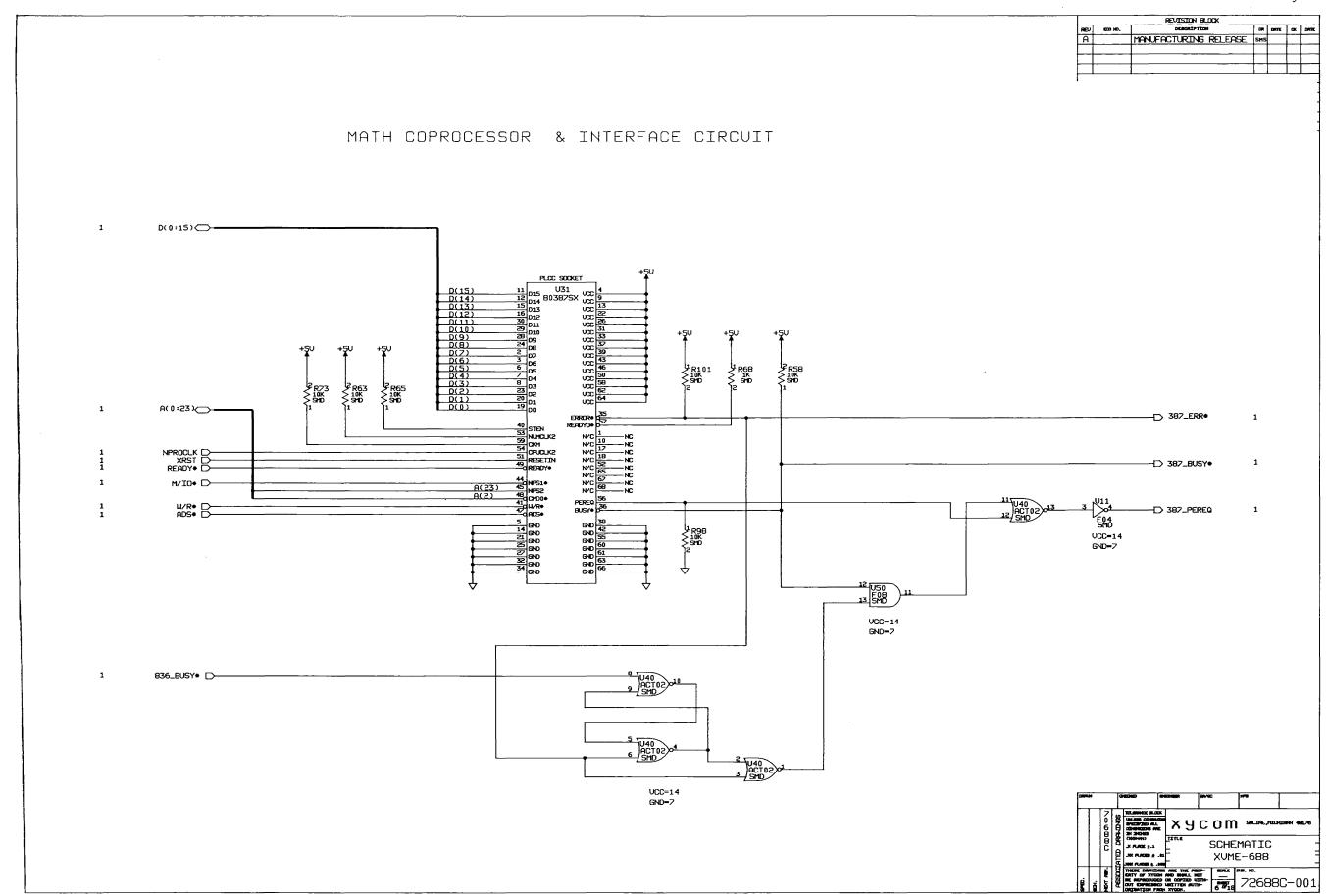

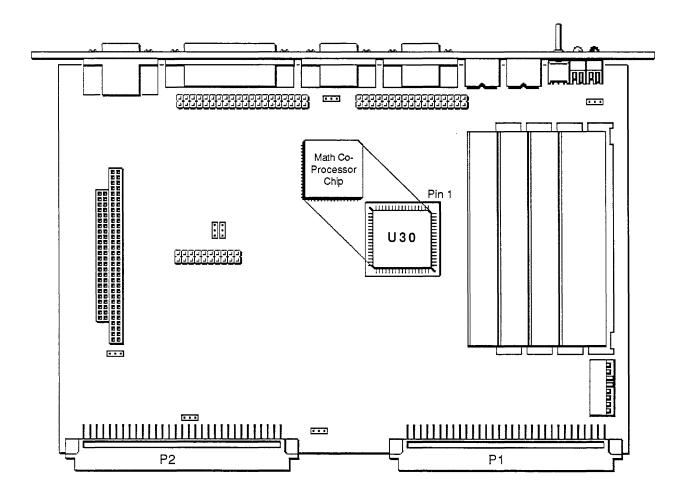

# 2.8 INSTALLING AN OPTIONAL INTEL 80387SX MATH CO-PROCESSOR

With the power to the XVME-678/688 off, install the 80387SX math co-processor into socket U31 of the XVME-678/688, as shown in Figure 2-5. Align pin 1 of the chip with pin 1 of the socket designated for the math co-processor (U7), as shown.

Figure 2-5. 80387SX Math Co-processor Installation

|  |  | \$ |  |

|--|--|----|--|

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

#### 3.1 INTRODUCTION

This chapter contains information on running the BIOS Setup Menus on the XVME-678/688. All pertinent menu instructions are included.

Beyond the standard key codes translated by the BIOS, there are additional function keys that can be used in the BIOS Setup Program:

In addition, the following function keys can be used on the XVME-678 in the BIOS Setup Program if the cache is set to zero.

#### 3.2 SOFTWARE CONTROL AND INITIAL SETUP

The XVME-678/688 is equipped with the Quadtel AT Compatible BIOS System. This BIOS allows easy modification of certain characteristics of the system configuration. The parameters set during the BIOS SETUP program are stored in battery-backed CMOS RAM so that the information is retained during power-down periods. Once the BIOS is set up, it is ready to run any PC/AT software. (Consult the operating system manual for specific applications and instructions.)

Several Xycom extensions were added to the XVME-678/688 BIOS:

- ROM DOS (Solid State Disk) support

- Menus for configuring Xycom value-added features

- XVME BIOS Interrupt functions for access to Xycom's value-added features

During power-up, the XVME-678/688 communicates with devices and checks its hardware configuration against the configuration information stored in the CMOS memory. The red FAIL and green PASS LEDs located on the CPU front panel come on at power-up, and after the processor has successfully completed diagnostics, the FAIL LED goes out. The PASS LED remains on as long as power is on, diagnostics pass, and the processor functions properly. If an error is detected, or parameters need to be defined, the FAIL LED remains on, and the diagnostic program prompts you to go to the SETUP program. Some errors are significant enough to abort start-up.

General instructions for navigating through the screens are described below:

- Arrow keys move the cursor up, down, left, and right. Press < Enter > to validate a selection.

- < Esc > exits the menu. You are prompted to save any changes.

- <F5> selects the previous or smaller value.

- <F6> selects the next higher value.

- <F9> automatically configures the system with the default values. These default values are defined by the system configuration and the values set in the Setup Menu.

# NOTE Disk drives must be configured manually.

• <F10> saves the current configuration. With the exception of time and date, the configuration is not saved until <F10> is pressed.

#### 3.3 **BIOS MAIN MENU**

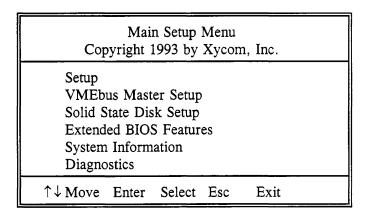

The BIOS Main Menu is presented as the top level in the BIOS setup menu structure. To access the Main Setup Menu, depicted below, press <Ctrl> <Alt> <S> simultaneously after the BIOS has completed the RAM test.

Figure 3-1. Main Setup Menu

# 3.3.1 BIOS Setup Menu

On the Setup Menu, depicted in Figure 3-2 below, the time, date, and setup information contained in the CMOS RAM can be changed. This information is used by the System BIOS for system configuration.

| Ex                                                  | tended BIOS Setup - Copy                          | yright 1989-91 Quadtel C              | orporation                                    |   |

|-----------------------------------------------------|---------------------------------------------------|---------------------------------------|-----------------------------------------------|---|

| Current Date: [01/c<br>Current Time: [00:           | <u>-</u>                                          | Video System:<br>Power-up Speed:      | [EGA / VGA<br>[Fast                           | ] |

| [ 3072]K Exte                                       | em Memory<br>Inded Memory<br>Iow Memory<br>Memory | BIOS Shadow:<br>Wait States:          | [System in RAM] [Video in RAM] [0, All banks] |   |

| Internal COM A:<br>Internal COM B:<br>Internal LPT: | [COM1, 3F8H]<br>[COM2, 2F8H]<br>[LPT1, 378H]      | Internal Floppy:<br>Internal IDE:     | [Enabled ]<br>[Enabled ]                      |   |

| Diskette Drive 1:<br>Fixed Disk 0: Typ              | [rior mounted]                                    | System Memory Cache:<br>AT Bus Speed: |                                               |   |

| ←↑↓→ Move<br>F1 Help<br>Esc Exit                    | F5 Previous Value<br>F6 Next Value                | F9 Automatic<br>F10 Save Con          | Configuration figuration                      |   |

Figure 3-2. BIOS Setup Menu

Each of the options on the Setup Menu are described on the next few pages. Default items are underlined.

## 3.3.1.1 **Date** (01/01/1988 format)

The date entry sets the real time clock for the month, day, and year. The left and right arrow keys and the enter key may be used to move from one field to the next. The numeric keys, 0-9, are used to change the field values. It is not necessary to type zeros in front of numbers.

## 3.3.1.2 **Time** (00:00:00 format)

The time entry sets the real time clock for hours, minutes, and seconds. During the power-up sequence, the time is read from the real time clock and saved in the BIOS system time.

The hour is calculated according to a 24-hour military clock, i.e., 00:00:00 through 23:59:59. The left and right arrow keys and the enter key may be used to move from one field to the next. The numeric keys, 0-9, are used to change the field values. It is not necessary to enter the seconds or type zeros in front of numbers.

# 3.3.1.3 **Setup RAM Configuration**

The RAM on the XVME-678/688 can be partitioned or allocated between system memory, extended memory, shadow memory, and EMS memory. The F9 key is used to automatically resize memory and select default memory values. The default memory configuration is 640 Kbytes system memory, 96 Kbytes shadow memory, 288 Kbytes EMS memory, and 3072 Kbytes or 15360 Kbytes of extended memory, depending on the XVME-678/688 version.

## 3.3.1.4 System Memory

This option should always indicate the size of conventional system memory as 640 Kbytes.

#### 3.3.1.5 Extended Memory

This option sets the amount of extended memory in Kbyte increments. The maximum amount of extended memory is 31 Mbytes (31744 Kbytes).

## 3.3.1.6 Shadow Memory

This field displays the amount of shadow memory in use. The contents of this field are controlled by BIOS shadow selection. Shadow memory is used to copy the system and/or video BIOS into RAM to improve performance. The XVME-678/688 allocates for Shadow RAM in Kbytes, and this number will

be displayed on the menu. This field, which is not editable, is controlled by the BIOS shadow selections (Section 3.3.1.13). It is for reference only.

The default shipping configuration for the XVME-678/688 will have the System BIOS and the Video BIOS shadowed. Shadowing the BIOS increases system performance.

#### NOTE

Shadow RAM is always allocated for BIOS shadow only. Disabling the BIOS shadow option will not increase the amount of system memory.

#### 3.3.1.7 **EMS Memory**

This option is used to set the amount of system memory to be configured as Expanded Memory (EMS). As the amount of EMS memory increases, the amount of extended memory decreases, and vice versa.

## 3.3.1.8 Internal Floppy and IDE (Disabled/Enabled)

These selections enable or disable the internal floppy and IDE hard disk drive controllers.

#### 3.3.1.9 Diskette Drives 0 and 1

Diskette Drive 0 (none/1.44MB, 3½ "/360KB, 5¼ "/1.2MB, 5¼ "/720KB, 3½")

Diskette Drive 1 (none/1.44MB, 3½ "/360KB, 5¼ "/1.2MB, 5¼ "/720KB, 3½")

These fields are used to specify the types of floppy disk drives connected to the PC/AT.

#### 3.3.1.10 Fixed Disk Drives 0 and 1

Fixed Disk 0 (none/1-14/16-45/User) Fixed Disk 1 (none/1-14/16-45/User)

This selection individually configures the disk drives as one of 45 drive types, a user-defined type, or not installed. All 45 drive types are displayed on the screen if F1 is pressed. If the type "User" is selected, several fixed disk parameters must be specified: number of cylinders (CY), heads (HD), sectors per track (ST), landing zone cylinder (LZ), and write precompensation (WP). Consult your fixed disk drive manual for information on any of these parameters.

## **3.3.1.11 Video System**

There are four video adapter choices:

- EGA/VGA (Enhanced Graphics Adapter, Video Graphics Array, or any special video adapter)

- 40 Color (Color Adapter, power-up in 40 column mode)

- 80 Color (Color Adapter, power-up in 80 column mode)

- Monochrome Adapter

This field should not be changed from its default—EGA/VGA. This allows video functions to be controlled by the video BIOS rather than the system BIOS.

# 3.3.1.12 Power-Up Speed

This option determines the CPU speed at boot time. Choices are Fast (25 MHz) and Normal (10 MHz).

# 3.3.1.13 BIOS Shadow (System in RAM/ROM, Video in RAM/ROM)

The System BIOS and the VGA BIOS may be shadowed into DRAM to increase system performance. Shadowing is the process of loading the BIOS from EPROM into DRAM after the power-up. Since the DRAM bus width is 16 bits and the EPROM is only 8 bits, opcode fetches from the DRAM have a significant increase in system performance.

#### 3.3.1.14 Wait States

This sets the number of wait states for memory controlled by the chipset to 0 or 1.

#### NOTE

It is recommended that automatic configuration be used to select the COM and LPT ports. Automatic configuration selects the first logical port address that does not conflict with other communication ports in your system. If the address is select manually, there is the possibility that there will be a conflict with other system devices.

#### 3.3.1.15 Internal COM A and COM B

These selections individually set the port address that will be programmed by the BIOS for each port. There are three options:

- Off

- Default for COM A COM1 (3F8h)

- Default for COM B COM2 (2F8h)

#### **NOTE**

It is recommended that automatic configuration be used to select the COM and LPT ports. Automatic configuration selects the first logical port address that does not conflict with any other communication ports in your system. If the addresses are selected manually, conflicts with other devices in the system may occur.

# 3.3.1.16 Internal LPT (off/<u>LPT1 at 378h</u>/278h/3BCh)

This item selects the port address to be programmed by the BIOS for the internal LPT port. There are four options:

- Off

- LPT1 at 378h

- LPT1 at 278h

- LPT1 at 3BCh

# 3.3.1.17 System Memory Cache (Off/On/N/A)

The system memory cache option—which refers to the XVME-678's 1 Kbyte internal cache on the 486SLC/e—can be enabled or disabled by changing the field to **ON** or **OFF**. If the cache is disabled (**OFF**), the XVME-678 takes longer to perform memory accesses, degrading system performance. The XVME-688 does not support this option, so N/A is the default.

# 3.3.1.18 **AT-bus Speed** (8.33/<u>10 MHz</u>)

The AT-bus speed is software selectable on power-up. Bus speed can be 8 or 10 MHz.

# 3.3.2 VMEbus Master Setup Menu

The VMEbus Master Setup Menu, depicted in Figure 3-3 below, allows configuration of the XVME-678/688 VMEbus master interface, auxiliary non-maskable interrupts (NMIs), and the VMEbus interrupt handler.

| VMEbus Master Setup - Copyright 1993 by Xycom, Incorporated |                    |          |                   |              |  |  |  |

|-------------------------------------------------------------|--------------------|----------|-------------------|--------------|--|--|--|

| VMEbus Master Config                                        | uration:           | System   | Resources         | Disabled     |  |  |  |

| Master Interface                                            | [Disabled]         | VMEb     | us Request Level  | [3]          |  |  |  |

| Master Byte Swapping                                        | N/A                | VMEb     | us BERR Timeout   | N/A          |  |  |  |

| Master Access Mode                                          | [Non-Privileged]   | VMEb     | us Release        | [When done]  |  |  |  |

| Auxiliary NMI Configur                                      | ation:             | VMEb     | us BERR           | [Disabled]   |  |  |  |

| Abort Push Button                                           | [Disabled]         | VMEb     | us SYSFAIL        | [Disabled]   |  |  |  |

|                                                             |                    | VMEb     | us ACFAIL         | N/A          |  |  |  |

| VMEbus Interrupt Hand                                       | ler Configuration: | L1 [Di   | sabled] L2        | 2 [Disabled] |  |  |  |

| L3 [Disabled] L4 [Di                                        | isabled] L5 [D     | isabled] | L6 [Disabled] L7  | [Disabled]   |  |  |  |

|                                                             |                    |          |                   |              |  |  |  |

| $\leftarrow \uparrow \downarrow \rightarrow Move$ F5        | Previous Value     | F10      | Save Configuratio | n            |  |  |  |

| F6                                                          | Next Value         | Esc      | Exit              |              |  |  |  |

Figure 3-3. VMEbus Master Setup Menu

# 3.3.2.1 Master Interface (<u>Disabled</u>/Enabled)

Select Enabled for the system to power-up with the VMEbus master interface enabled. If disabled, the XVME-678/688 cannot access VMEbus memory or perform VMEbus interrupt acknowledge (IACK) cycles.

# 3.3.2.2 Master Byte-Swapping

This feature is not supported (N/A) on the XVME-678/688. It is present on the menu only for compatibility with other XVME PC/AT products—such as the XVME-674/677—that support programmable byte-swapping.

# 3.3.2.3 Master Access Mode (Non-Privileged/Supervisory)

This field allows the choice of Non-privileged or Supervisory accesses for VME master cycles. The access mode selection controls the AM2 signal on the VMEbus when the XVME-678/688 performs VMEbus accesses.

# 3.3.2.4 System Resources (Display Only)

This option displays the state of the SYSRES switch, which determines if the VMEbus system resources are provided by the XVME-678/688 or another VMEbus processor. The system resources are VMEbus Arbiter, BERR timeout, SYSCLK, and IACK daisy chain driver. These resources must be provided by the module installed in VMEbus slot 1.

## 3.3.2.5 VMEbus Request Level (0/1/2/3)

This feature sets which bus request level (0,1,2,3) will be used by the XVME-678/688 when requesting use of the VMEbus. If the XVME-678/688 is providing the system resources, this selection is automatically set to 3.

#### 3.3.2.6 VMEbus BERR Timeout

If system resources are enabled, the length of the VMEbus BERR timeout is 16  $\mu$ s. If system resources are disabled, this option is unavailable.

#### 3.3.2.7 Auxiliary NMI Configuration

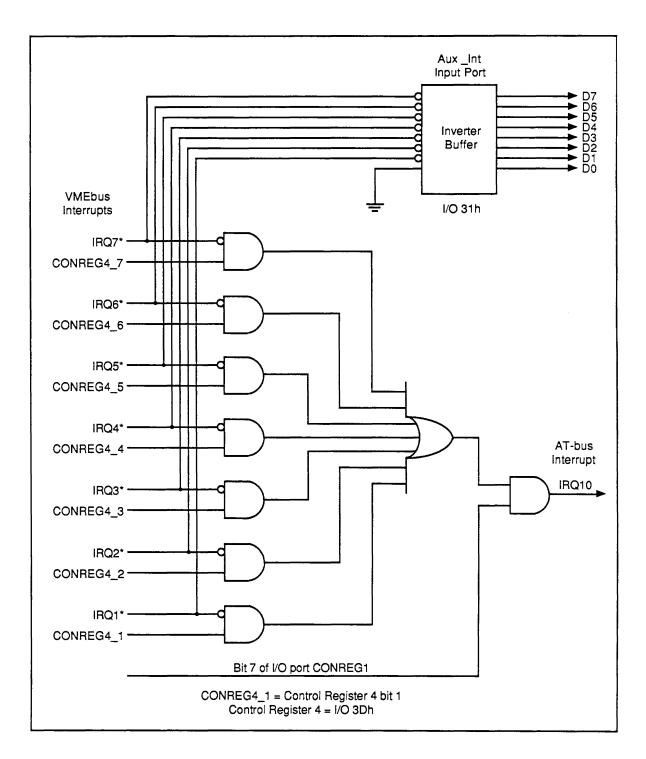

The XVME-678/688 has both individual and group enable bits for the auxiliary non-maskable interrupts (ANMIs) and auxiliary maskable interrupts (AMIs). Individual ANMI and AMI bits are configured by the VMEbus master menu, but the group enable bits are left disabled and must be enabled by software (via XVME BIOS functions 21H and 51H, or by directly setting bit 4 and/or bit 7 of CONREG1—I/O port 30H) before the actual interrupts can be processed. This is because non-maskable interrupts (NMIs) and IRQ10 handlers must be provided by a user application or the operating system, not by the BIOS.

# Chapter 3 - BIOS Setup Program

These options are used to define which of the following ANMIs are enabled at power-up:

- ABORT Switch

- VMEbus BERR

- VMEbus SYSFAIL

- VMEbus ACFAIL

Each ANMI can be enabled or disabled. All are disabled by default.

VMEbus ACFAIL is not available (N/A) on the XVME-678/688. It is listed on the menu only for compatibility with other XVME PC/AT products—such as the XVME-674/677—that support VMEbus ACFAIL.

# 3.3.2.8 VMEbus Interrupt Handler Configuration

This option determines which VMEbus interrupt level AMIs (1-7) can be received by the XVME-678/688. Each of the interrupt levels can be enabled or disabled. All are disabled by default.

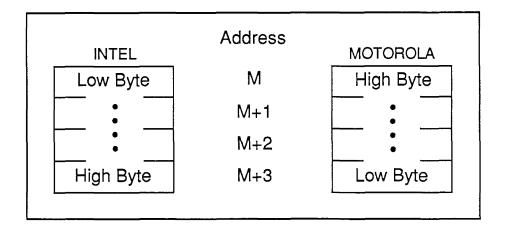

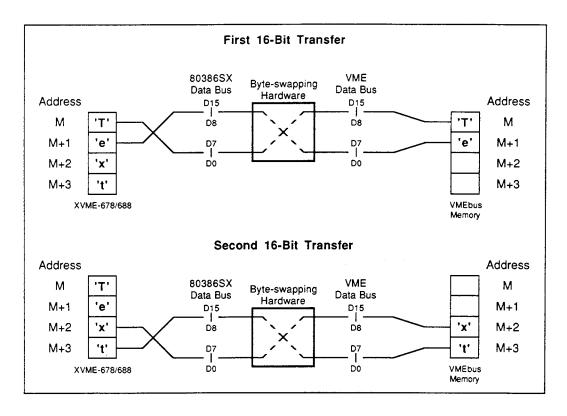

## 3.3.3 Solid State Disk Setup Menu