# Model 721 VMEbus to SCSI Controller User's Manual

166-721-001 Revision A January 22, 1990

Copyright 1990 Xylogics, Inc.

The information in this manual is subject to change without notice, and should not be construed as a commitment by Xylogics. Xylogics assumes no responsibility for any errors that may appear in this document.

# 721 Revision Level History

| Revision         | Description      |

|------------------|------------------|

| Rev. A (1/22/90) | Initial release. |

| List of  | Figures and Tables                                                                           | v  |

|----------|----------------------------------------------------------------------------------------------|----|

| Specific | ations                                                                                       | 1  |

| 1.1.     | General                                                                                      | 1  |

| 1.2.     | Using This Manual                                                                            | 1  |

| 1.3.     | Abbreviations                                                                                | 1  |

| 1.4.     | Design Reliability                                                                           | 3  |

| 1.5.     | Programmable Features                                                                        | 3  |

| 1.6.     | Physical                                                                                     | 3  |

| 1.7.     | Environmental                                                                                | 4  |

| 1.8.     | Electrical                                                                                   | 4  |

| 1.9.     | System-related Specifications                                                                | 4  |

| 1.10.    | SCSI-related Specifications                                                                  | 5  |

| 1.11.    | Floppy Disk Drive-related Specifications (not implemented in this version of the controller) | 6  |

| 1.12.    | VMEbus-related Specifications                                                                | 6  |

| 1.13.    | Software-related Specifications                                                              | 7  |

| 1.13.1.  | Software Interface                                                                           | 7  |

| 1.13.2.  | Software Drivers                                                                             | 8  |

| Installi | ng and Testing the 721                                                                       | 9  |

| 2.1.     | General                                                                                      | 9  |

| 2.2.     | Unpacking and Inspection                                                                     | 9  |

| 2.2.1.   | Inspect the Shipping Carton and the Controller                                               | 9  |

| 2.2.2.   | Contents                                                                                     | 9  |

| 2.2.3.   | Handling Precautions                                                                         | 9  |

| 2.3.     | Configuring the 721                                                                          | 10 |

| 2.3.1.   | Base Address Selection                                                                       | 11 |

| 2.3.2.   | Bus Request and Bus Grant Lines                                                              | 12 |

| 2.3.3.   | P2 Connector                                                                                 | 13 |

| 2.3.4.   | P2 Terminator Power                                                                          | 13 |

| 2.3.5.   | Controller Terminator Power                                                                  | 14 |

| 2.3.6.   | SCSI Timing                                                                                  | 14 |

| 2.3.7.   | Floppy Disk Jumper J3                                                                        | 14 |

| 2.3.8.   | Floppy Disk Jumper J17                                                                       | 15 |

| 2.4.     | EPROM and PAL Part Numbers                                                                   | 15 |

| 2.5.     | Light Emitting Diodes                                                                        | 15 |

| 2.6.     | Board Labels/Revision Control                                                                | 16 |

| 2.7.     | Preparing the Computer System for Installation                                               | 16 |

| 2.7.1.   | Backplane Jumpers                                                                            | 16 |

| 2.7.2.   | Card Cage Slot                                                                               | 16 |

| 2.7.3.  | Power Considerations                                | 17 |

|---------|-----------------------------------------------------|----|

| 2.8.    | Installing the 721                                  | 17 |

| 2.9.    | Cabling the Subsystem                               | 17 |

| 2.9.1.  | Mechanical Restraint                                | 17 |

| 2.9.2.  | SCSI Device Grounds                                 | 17 |

| 2.10.   | Power-up Self Test                                  | 17 |

| 2.11.   | Diagnostics                                         | 18 |

| 2.12.   | Cabling Multiple SCSI Devices                       | 18 |

| 2.12.1. | Terminators                                         | 19 |

| 2.12.2. | Target Select                                       | 20 |

| The 72  | 1 Registers                                         | 21 |

| 3.1.    | General                                             | 21 |

| 3.2.    | IOPB Address Registers                              | 22 |

| 3.3.    | IOPB Address Modifier/Priority IOPB Register        | 22 |

| 3.4.    | Control and Status Register                         | 22 |

| 3.4.1.  | Control Register (Write)                            | 23 |

| 3.4.2.  | Status Register (Read)                              | 24 |

| 3.5.    | Fatal Error Register                                | 26 |

| IOPB I  | Description                                         | 27 |

| 4.1.    | General                                             | 27 |

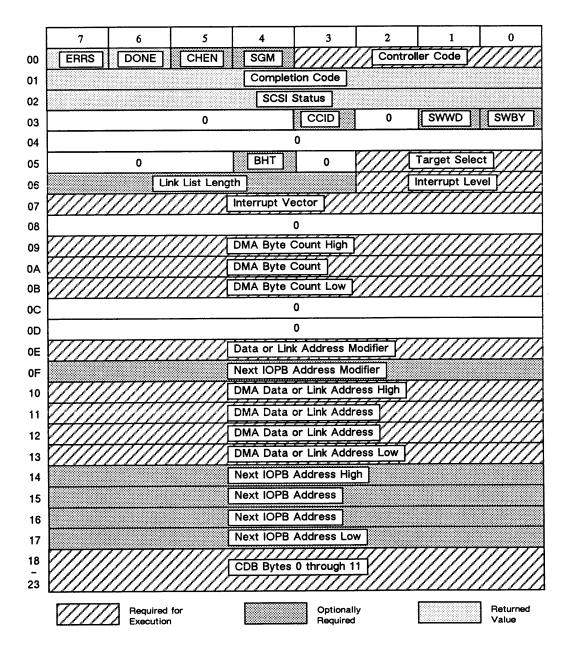

| 4.2.    | Standard IOPB                                       | 27 |

| 4.2.1.  | IOPB Byte 0 (Channel Byte)                          | 28 |

| 4.2.2.  | IOPB Byte 1 (Completion Code)                       | 28 |

| 4.2.3.  | IOPB Byte 2 (SCSI Status)                           | 29 |

| 4.2.4.  | IOPB Byte 3 (Controller Command)                    | 30 |

| 4.2.5.  | IOPB Byte 5 (Target Select)                         | 30 |

| 4.2.6.  | IOPB Byte 6 (Interrupt Level)                       | 31 |

| 4.2.7.  | IOPB Byte 7 (Interrupt Vector)                      | 31 |

| 4.2.8.  | IOPB Bytes 9 through B (DMA Count)                  | 32 |

| 4.2.9.  | IOPB Byte E (Data or Link Address Modifier)         | 32 |

| 4.2.10. | IOPB Byte F (Next IOPB Address Modifier) .          | 32 |

| 4.2.11. | IOPB Bytes 10 through 13 (DMA Data or Link Address) | 33 |

| 4.2.12. | IOPB Bytes 14 through 17                            |    |

|         | (Next IOPB Address)                                 | 33 |

| 4.2.13. | IOPB Bytes 18 through 23 (SCSI CDB)                 | 33 |

| 4.3.    | SCSI Command Descriptor Block                       | 33 |

| 4.3.1.  | Typical Six-byte Command Descriptor Block           | 34 |

| 132     | Typical Ten-byte Command Descriptor Block           | 34 |

| 4.3.3.  | Typical Twelve-byte Command Descriptor Block  | 35 |

|---------|-----------------------------------------------|----|

| 4.3.4.  | CDB Byte 0 (Operation Code)                   | 35 |

| 4.3.5.  | CDB Byte 1 (Logical Unit Number)              | 36 |

| 4.3.6.  | CDB Bytes 2 through 10 (Transfer Information) | 36 |

| 4.3.7.  | CDB Bytes 5, 9, and 13 (Control)              | 36 |

| Comma   | ands                                          | 37 |

| 5.1.    | General                                       | 37 |

| 5.2.    | SCSI Command Codes                            | 37 |

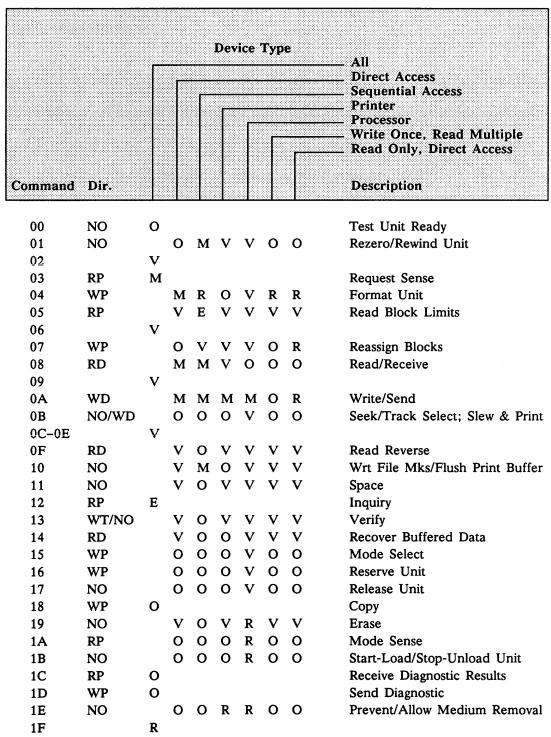

| 5.2.1.  | SCSI Group 0 Command Codes                    | 38 |

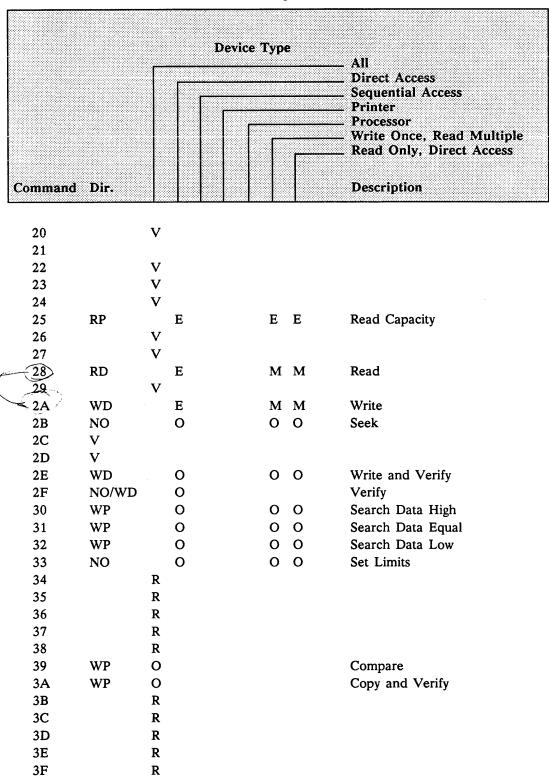

| 5.2.2.  | SCSI Group 1 Command Codes                    | 39 |

| 5.3.    | Command Structure                             | 40 |

| 5.4.    | No Operation                                  | 41 |

| 5.5.    | Read Controller Parameters                    | 42 |

| 5.5.1.  | Read Controller Parameters CDB                | 43 |

| 5.5.2.  | Parameter List                                | 43 |

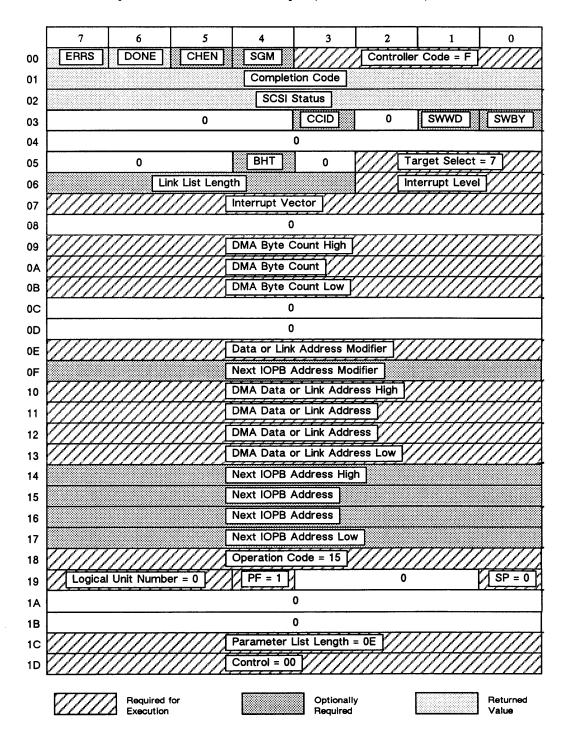

| 5.6.    | Write Controller Parameters                   | 48 |

| 5.6.1.  | Write Controller Parameters CDB               | 49 |

| 5.6.2.  | Parameter List                                | 49 |

| 5.7.    | SCSI Bus Reset                                | 50 |

| Error I | Processing                                    | 51 |

| 6.1.    | General                                       | 51 |

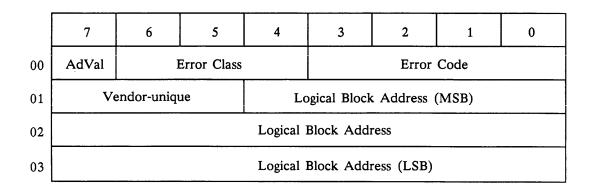

| 6.2.    | SCSI Request Sense Data                       | 51 |

| 6.2.1.  | Sense Key Descriptions                        | 53 |

| 6.3.    | The Completion Code                           | 55 |

| 6.3.1.  | Completion Code Descriptions                  | 56 |

| 6.4.    | Fatal Error Codes                             | 59 |

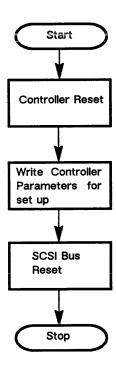

| Progra  | mming Tutorial                                | 61 |

| 7.1.    | General                                       | 61 |

| 7.2.    | Programming the Controller                    | 61 |

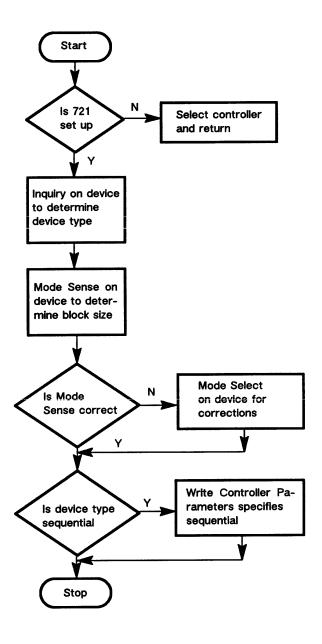

| 7.3.    | Programming the Controller and the Driver     | 62 |

| 7.4.    | Executing a Read or Write Operation           | 63 |

| Special | Functions                                     | 65 |

| 8.1.    | General                                       | 65 |

| 8.2.    | Maintenance Mode                              | 65 |

| 8.2.1.  | Register Use in Maintenance Mode              | 65 |

| 8.2.2.  | Maintenance Mode Protocol                     | 66 |

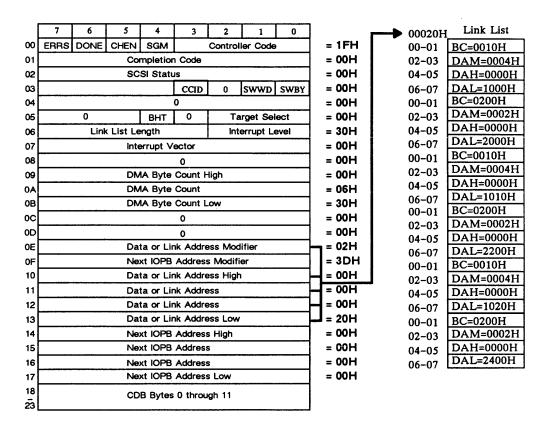

| 8.3.    | Scatter/Gather                                | 66 |

| 8.3.1.  | Scatter/Gather Link List             | 67 |

|---------|--------------------------------------|----|

| 8.3.2.  | Setting Up a Scatter/Gather Transfer | 68 |

| 8.3.3.  | 721 Operation                        | 68 |

| 8.4.    | IOPB DMA Throttle/Throttle Dead Time | 69 |

| 8.5.    | Black Hole Transfers                 | 69 |

| 8.6.    | Block Mode Transfers                 | 70 |

| Interfa | ce Signals                           | 71 |

| 9.1.    | General                              | 71 |

| 9.2.    | VMEbus Interface Signals             | 71 |

| 9.3.    | SCSI Bus Interface Signals           | 75 |

| 9.3.1.  | Single-ended Pin Assignments         | 76 |

| Index   |                                      | 77 |

| Monuc   | I Evaluation Form                    | 81 |

# List of Figures and Tables

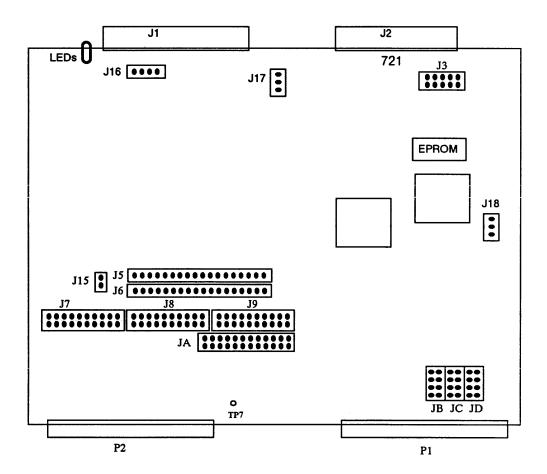

| Figure 2–1. | Approximate Jumper Locations              | 10 |

|-------------|-------------------------------------------|----|

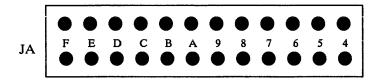

| Figure 2-2. | Jumper Block JA                           | 11 |

| Figure 2-3. | Jumpering the Base Address                | 11 |

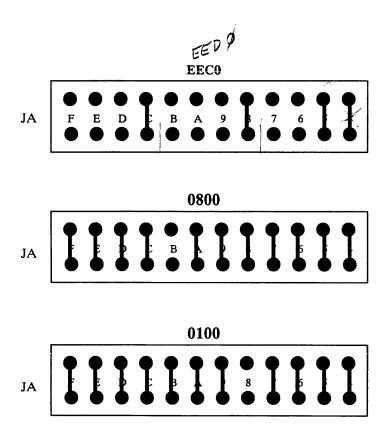

| Figure 2-4. | Jumpers JB, JC, and JD                    | 12 |

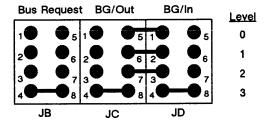

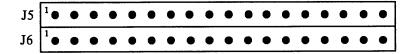

| Figure 2-5. | Jumper Blocks J5 and J6                   | 13 |

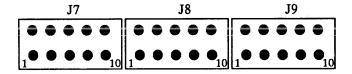

| Figure 2-6. | Jumper Blocks J7, J8, and J9              | 13 |

| Figure 2–7. | Jumper Block J15                          | 13 |

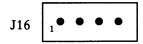

| Figure 2–8. | Jumper Block J16                          | 14 |

| Figure 2–9. | Jumper Block J18                          | 14 |

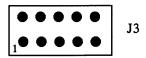

| •           | Jumper Block J3                           | 14 |

| •           | Jumper Block J17                          | 15 |

| •           | Sample Part Number                        | 16 |

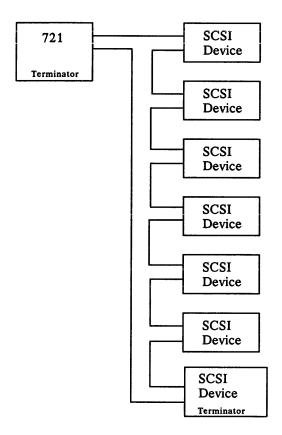

| •           | Single Initiator, Multiple Target         | 18 |

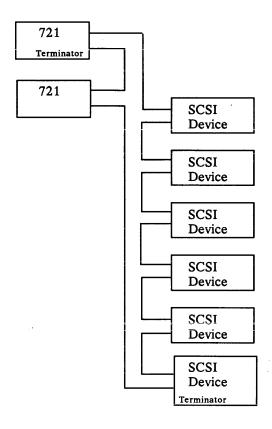

| _           | Multiple Initiators, Multiple Targets     | 19 |

| Figure 3–1. | Register Map                              | 21 |

| Figure 6–1. | Non-extended Sense Data Format            | 51 |

| Figure 6–2. | Extended Sense Data Format                | 52 |

| Figure 7–1. | Initial Controller Values                 | 61 |

| Figure 7–2. | Programming the Controller and the Driver | 62 |

| Figure 7–3. | Read/Write                                | 63 |

| Figure 8–1. | Scatter/Gather Transfers                  | 68 |

| Table 2-1.  | PROM/PAL Part Numbers and Locations       | 15 |

| Table 3–1.  | Register Offsets                          | 21 |

| Table 3-2.  | Fatal Error Codes                         | 26 |

| Table 4–1.  | SCSI Status Codes                         | 29 |

| Table 4–2.  | Group Codes                               | 36 |

| Table 5-1.  | SCSI Group 0 Command Codes                | 38 |

| Table 5-2.  | SCSI Group 1 Command Codes                | 39 |

| Table 5-3.  | Read Controller Parameters List           | 44 |

| Table 5-4.  | AIO Response Times                        | 45 |

| Table 5-5.  | Throttle Values                           | 46 |

| Table 5-6.  | Write Controller Parameters List          | 49 |

| Table 6-1.  | Summary of Completion Codes               | 55 |

| Table 8-1.  | Register Use in Maintenance Mode          | 65 |

| Table 8-2.  | Scatter/Gather Link List                  | 67 |

| Table 8-3.  | Link List Field Values                    | 67 |

| Table 8-4.  | Throttle Dead Time Values                 | 69 |

# **Specifications**

1

# **Specifications**

#### 1.1. General

The Xylogics Model 721 VME to SCSI host adapter controls up to 56 SCSI target devices in any combination. Host software can set the configuration of SCSI targets via the 721 software interface. The 721 provides a single high-performance SCSI port that supports both synchronous and asynchronous transfers; it also offers an optional floppy disk drive port. Data transfers occur between the VMEbus™ and SCSI or between the VMEbus and floppy.

## 1.2. Using This Manual

This manual provides two software reference cards that display the IOPB structure and codes (see inserts). Section 1 describes the 721 specifications, Section 2 provides installation information, Section 3 describes the 721 registers, Section 4 describes the IOPBs, and Section 5 describes the commands. Section 6 describes error processing, Section 7 is a programming tutorial, Section 8 explains the 721's special functions, and Section 9 contains VME and SCSI interface information.

A detailed theory of operation is available on a per customer basis.

#### 1.3. Abbreviations

| AIO  | Add IOPB                 |

|------|--------------------------|

| AIOP | AIO Pending              |

| AIOR | AIO Response Time        |

| AM   | Address Modifier         |

| BDID | Bus Device ID            |

| BHT  | Black Hole Transfer      |

| CC   | Command Code             |

| CCID | Change Controller ID     |

| CDB  | Command Descriptor Block |

VMEbus is a trademark of the VMEbus International Trade Association.

# 1.3. Abbreviations (continued)

CHEN Chain Enable

CRIO Clear Remove IOPB

CRBS Clear Register Busy Semaphore

CRST Controller Reset

DRDY Drive Ready

ERRS Error Summary

FDMAC DMA Controller Chip

FERR Fatal Error

FIFO First In/First Out Buffer

H Notation for hexadecimal values

INTRAM 8031 Internal Random Access Memory

IOPB Input/Output Parameter Block IRAM IOPB Random Access Memory

LED Light Emitting Diode

LSB Least Significant Byte

LSI Large Scale Integration

LUN Logical Unit Number

MMA Maintenance Mode Active

MM Maintenance Mode

MSB Most Significant Byte

NPRM Non-privileged Request Mode

PRIO Priority IOPB Request

RBS Register Busy Semaphore

REGCEL Register Read, Write, and Interrupt

RIO Remove IOPB

ROM Read Only Memory

ROR Release on Request

RSTA Controller Reset Active

RT Register Test

SCSI Small Computer System Interface

SGM Scatter/Gather Mode SPC SCSI Protocol Chip

SWBY Swap Bytes SWWD Swap Words

TDT Throttle Dead Time

TGT Target Select

TMOD Transfer Mode

# 1.4. Design Reliability

The following Xylogics features minimize the likelihood of product failure:

- Design for worst case voltage and temperature

- Extensive evaluation testing

- Low parts count through extensive use of custom LSI

- Buffer parity for continuous error checking

- All components burned-in

- One card in backplane or expansion chassis

- Power-cycling under thermal stress during burn-in

# 1.5. Programmable Features

- Interrupt or polled operations

- DMA parameters

- Drive parameters

# 1.6. Physical

Packaging: The 721 resides on one printed circuit board.

Dimensions: The 721 is a 2 by 2 Eurocard that measures 9.2-inches high by 6.3-inches deep (233.35 mm by 160 mm). The 721 is identical in form-factor to the standard VME (dual high-dual wide) printed circuit board.

Shipping Weight: 3 pounds (1.4 kg).

Connectors: The 721 supports two SCSI bus connector schemes: the VME P2 connector with an external cable adapter and the front panel 50-pin header.

Front Panel: Xylogics offers the 721 with an optional front panel.

#### 1.7. Environmental

The 721 environmental requirements are 0 through 55°C, with a maximum relative humidity of 90% (non-condensing). Air flow across the board must maintain a maximum temperature differential of 7°C to prevent hot spots.

#### 1.8. Electrical

Power: The 721 uses 4.2 amperes at +5 volts DC (VDC).

Tolerance: Power voltage must be within  $\pm 5\%$  (4.75 to 5.25).

Grounding: Common earth ground must be established between the SCSI devices and the CPU chassis, backplane, and expansion cabinets.

# 1.9. System-related Specifications

Data Transfer Modes: The 721 transfers data in word or longword mode. It may use byte transfers to align subsequent transfers on word boundaries.

I/O Addressing Capability: The 721 decodes byte addresses for its on-board registers.

**Data Buffering:** The 721 has a 256 byte FIFO buffer. Data can be put into one end of the FIFO and simultaneously removed at the other end. There are no delays associated with filling and emptying the buffer.

Command Buffer: The 721 reads commands into a separate buffer that holds up to 14 full commands (IOPBs); this minimizes host processor intervention and optimizes controller decode overhead. The 721 can also store an additional 35 IOPB addresses.

Status LEDs: The 721 has two status LEDs. The green LED indicates the controller is active; the yellow LED indicates the on-board diagnostics did not complete successfully or a fatal error occurred.

On-board Diagnostics: The 721 runs an extensive on-board diagnostic routine upon power-up or a bus reset. If an error occurs during this test, the 721 posts the failure in a special error register.

# 1.9. System-related Specifications (continued)

Multiprocessor Support: The 721 has a built-in register control semaphore. This flag allows multiple processors to share the 721 register set.

Scatter/Gather: The 721 supports Scatter Read and Gather Write commands. The controller gathers data from various memory locations and transfers it to the buffer for use in a Write command. It scatters the data out from the SCSI drive to the appropriate memory locations with a Read command. To execute a scatter/gather, software issues a normal Read or Write command along with a DMA list containing a memory address and the number of 16-bit words to transfer to/from that location. The smallest granularity of scatter/gather is one 16-bit word.

**Priority IOPBs:** The 721 executes priority IOPBs over all IOPBs in its command buffer, except for the one in process.

Black Hole Transfers: The 721 may transfer all the DMA data into the same bus address without incrementing the address at each DMA.

Block Mode Transfers: The 721 supports block mode as per the VMEbus Specification. Block mode reduces data transfer times by allowing a DMA device to use one memory address strobe for up to 256 bytes.

# 1.10. SCSI-related Specifications

Small Computer System Interface: Conforms fully to the American National Standard for Information Systems (ANSI) X3.131-1986.

Data Transfer Rate: The 721 supports data transfer rates of up to 3 megabytes per second (MB/s) asynchronously and 5 MB/s synchronously.

Disconnect/Reconnect Facility: The 721 supports targets that can disconnect and reconnect at a later time.

Common Command Set: The 721 supports the SCSI Common Command Set (CCS).

SCSI Channel Controller: The 721 uses the Fujitsu MB87030 LSI SCSI Channel Controller.

SCSI Device Support: The 721 supports all SCSI devices, including magnetic and optical disks, and tape drives.

SCSI Bus Drivers: The 721 supports single-ended drivers and receivers.

# 1.11. Floppy Disk Drive-related Specifications

(not implemented in this version of the controller)

Data Transfer Rate: The 721 supports a floppy disk transfer rate of up to 500K-bits per second or less.

Sector Size: The 721 supports four different sector sizes: 128, 256, 512, and 1024 bytes.

Floppy Controller: The 721 uses the Western Digital 37C65 floppy controller with built-in drivers and receivers.

Number of Floppy Drives: The 721 supports up to two floppy drives in normal or PC/AT mode.

**Drive Types:** The 721 supports 3.5-, 5.25-, and 8-inch drives. The factory configures the 721 with connectors used on 5.25-inch form factor drives.

Drive Formats: The 721 supports IBM, PC/AT, and PC/XT formats.

# 1.12. VMEbus-related Specifications

VME Compliance Number: IEEE P1014/D1.0.

Transfer Mode: Direct Memory Access (DMA).

**DMA Throttle Control:** Each time the 721 becomes bus master, it executes DMA transfers to or from the buffer up to the maximum throttle parameter or the number of bytes/spaces available in the buffer.

**DMA Data Transfer Rate:** The 721 has a maximum transfer rate of 30 MB/s based on 30 nanoseconds (ns) memory response time assuming longword mode transfers.

**DMA Dead Time:** The 721 supports a programmable DMA dead time between throttle bursts. This prevents the 721 from taking over the bus and allows time for other DMA devices to access the bus.

Data Transfer Limit: From 0 to 2<sup>24</sup>-1 bytes.

Bus Compatibility: The 721 is compatible with the standard VMEbus (C.1).

# 1.12. VMEbus-related Specifications (continued)

Addressing Capability: Full 32-bit support. The 721 supports master A32, and slave A16, as per the VMEbus Specification. As a slave, the 721 responds to address modifiers 29H and 2DH. The 721 also supports block transfers.

Data Width: The 721 supports D16 and D32 as per the VMEbus Specification.

Release On Request: The 721 optionally releases the bus at the request of other VMEbus masters.

Release When Done: The 721 releases the bus after each throttle burst.

Bus Request Levels: The 721 supports four bus request levels.

Interrupt Priority: Software programmable interrupt level and vector.

# 1.13. Software-related Specifications

Controller IOPB Length: 36 bytes.

Controller Registers: Seven 8-bit I/O Registers; byte or word addressable. Only eight bits respond during word access.

**Software Control:** Software can program the 721 for use with various SCSI targets, controller parameters, and controller options

**Diagnostic Support:** Comprehensive set of stand-alone diagnostics written in the C language are available.

#### 1.13.1. Software Interface

The software interface includes seven byte-wide registers. The first four bytes comprise the VME Address Register, the fifth byte is the Address Modifier Register, the sixth byte is the Control and Status Register (CSR), and the last byte is the Fatal Error Register (FER). The CSR includes two bits that are very important to IOPB processing: *Add IOPB* (AIO) and *Remove IOPB* (RIO).

#### 1.13.1. Software Interface (continued)

The IOPB is a block of command and status information that includes the bus address and the type of operation. The software driver sets up the IOPB in host memory, sends the IOPB address to the VME Address Registers, and sets AIO. After receiving the IOPB address, the 721 clears AIO, DMAs the IOPB to its IRAM, executes the IOPB and, upon completion or error, updates the IOPB status, DMAs it back and sets RIO. The VME Address Registers point to the completed IOPB. The software driver reads the address and clears RIO. Software may add IOPBs to the queue, providing AIO is clear, by writing the IOPB address to the address registers and setting AIO, regardless of the 721's Busy status.

#### 1.13.2. Software Drivers

Xylogics provides its customers with UNIX™ drivers for a variety of VME-based systems. Currently, Xylogics offers a full device driver and diagnostic support for Sun Microsystems'™ Sun-3 and Sun-4 series machines. Xylogics also provides UNIX System V drivers for a variety of machines. A format utility for these drivers enables formatting, defect management, and feature tuning.

UNIX is a trademark of AT&T Bell Laboratories. Sun Microsystems is a trademark of Sun Microsystems, Inc.

# **Installing and Testing the Controller**

2

# Installing and Testing the 721

#### 2.1. General

This section describes how to unpack, configure, install, and test your 721 controller.

# 2.2. Unpacking and Inspection

#### 2.2.1. Inspect the Shipping Carton and the Controller

Inspect the shipping carton. If it is damaged, do not unpack the unit. Notify Xylogics and the freight carrier immediately. If no damage is visible, carefully unpack the 721. Save the carton and other packing materials for future use.

#### 2.2.2. Contents

The 721 is a single printed circuit board. Optional items include a manual and/or software on a ¼-inch cartridge or ½-inch magnetic tape.

If any items are missing or damaged, please contact Xylogics at one of the following telephone numbers.

United States (Burlington, MA): (617) 272-8140; United Kingdom (Milton Keynes): 44-908-22212.

#### 2.2.3. Handling Precautions

Observing proper handling precautions minimizes the risk of damaging the 721 with electrostatic discharge. When transporting the 721, use an antistatic bag, antistatic bin, or the original shipping carton and packing material. Personnel handling the 721 should observe proper grounding methods including, but not limited to, wrist bands, heel straps, and antistatic mats.

# 2.3. Configuring the 721

You can configure the 721 with several jumper options. The following subsections describe these options.

Figure 2-1. Approximate Jumper Locations

#### 2.3.1. Base Address Selection

Jumper block JA controls the base address. Figure 2-3 shows how to set the jumpers for commonly used base addresses. Inserting a jumper makes the 721 respond to a zero on that address line; removing a jumper makes the 721 respond to a one. The 721 uses bits 1 through 3 to determine which register is being accessed. The 721 is an A16 slave, and responds to address modifier 2DH, and optionally to 29H. Factory setting: EEC0.

Figure 2-2. Jumper Block JA

Figure 2-3. Jumpering the Base Address

#### 2.3.2. Bus Request and Bus Grant Lines

The 721 uses the Bus Request and Bus Grant lines to become bus master. In VMEbus arbitration, there are four Bus Request/Grant levels: 0 through 3. The 721 drives one Bus Request line according to the jumper scheme you choose. The arbiter responds by driving the associated Bus Grant In line (i.e., BG0IN responds to BR0). If the 721 receives a Bus Grant on any of the Bus Grant In lines (BG0IN through BG3IN), and is not requesting the bus on that line, it passes the grant to the appropriate Bus Grant Out line: BG00UT through BG3OUT.

Select a request level by jumpering one Bus Request (BR0 through BR3), one Bus Grant In, and one Bus Grant Out line to match the selected request level. Jumper the remaining Bus Grant In/Out lines so that the incoming signal passes through the board (i.e., jumper BGxIN to BGxOUT, where x represents the remaining grant levels).

For example, Figure 2-3 shows the jumpering scheme for level 3 (the pins are numbered for this example): jumper JB4 to JB8; then jumper JC4 to JC8, and JD4 to JD8. Jumper the remaining grant levels from JC5 to JD1, JC6 to JD2, and JC7 to JD3. Factory configuration: Bus Request Level 3.

Some VME systems only support Bus Request Level 3.

Figure 2-4. Jumpers JB, JC, and JD

#### 2.3.3. P2 Connector

When using the P2 connector, jumper J5n to J6n, where n = 1 to 18. Also, install all jumpers in J7, J8 and J9. Factory setting: all jumpers out.

Do not use the front panel SCSI connector when using the P2 connector.

Figure 2-5. Jumper Blocks J5 and J6

Figure 2-6. Jumper Blocks J7, J8, and J9

#### 2.3.4. P2 Terminator Power

To supply terminator power (TERMPWR) on the P2 bus, install jumper J15. Factory setting: J15 out.

Figure 2-7. Jumper Block J15

#### 2.3.5. Controller Terminator Power

The 721 accepts or generates terminator power, depending on J16's configuration. Factory setting: J16 3-4 in.

To generate terminator power locally to the 721, jumper J16 3-4 in.

To generate terminator power locally and to the SCSI bus, jumper J16 1-2 in and 3-4 in.

To accept terminator power from the SCSI bus, jumper J16 1-2 in.

Figure 2-8. Jumper Block J16

#### 2.3.6. SCSI Timing

To run the SCSI bus at a maximum speed of 4 MHz, jumper J18 2-3 in. To run the SCSI bus at a maximum speed of 5 MHz, jumper J18 1-2 in. Factory setting: J18 2-3 in.

Figure 2-9. Jumper Block J18

#### 2.3.7. Floppy Disk Jumper J3

Jumper J3 determines the floppy drive type (AT or other). Future versions of the controller will implement this feature. Factory setting: all jumpers out.

Figure 2-10. Jumper Block J3

#### 2.3.8. Floppy Disk Jumper J17

Jumper J17 determines the floppy drive type (AT or other). Future versions of the controller will implement this feature. Factory setting: J17 out.

Figure 2-11. Jumper Block J17

# 2.4. EPROM and PAL Part Numbers

Table 2-1. PROM/PAL Part Numbers and Locations

| B / N I     | 7.       | The second   |

|-------------|----------|--------------|

| Part Number | Location | Туре         |

| 181-001-088 | U31      | PAL 1        |

| 181-001-089 | U26      | PAL 2        |

| 181-001-090 | U37      | PAL 3        |

| 180-002-307 | U56      | <b>EPROM</b> |

# 2.5. Light Emitting Diodes

The 721 has two light emitting diodes (LEDs). When the green LED is lit, the 721 is active. During power-up, the yellow LED lights for a moment and then goes off. If it remains on, a fatal error or self test error occurred.

#### 2.6. Board Labels/Revision Control

All Xylogics controllers use revision control labels. They are located on the soldered side of the board. The revision level is important when discussing configuration issues.

Figure 2-12. Sample Part Number

# 2.7. Preparing the Computer System for Installation

The backplane of your system must provide a VMEbus slot for the 721. The slot must be capable of handling a bus master, and the power source must handle the power consumption of the entire system, including the 721.

#### 2.7.1. Backplane Jumpers

Remove any jumpers that short, or cause the Interrupt Acknowledge (IACK IN/OUT) and DMA Grants (BG 0-3 IN/OUT) to bypass the slot in which you are installing the 721.

#### 2.7.2. Card Cage Slot

The card cage must have a slot at the proper DMA priority available for the 721. The 721 uses DMA to transfer data and IOPBs. Placement of the 721 in the DMA priority chain may be critical. The amount of bus bandwidth it uses will be high at times; this may affect other boards in the system. Likewise, other boards may not allow enough time for the 721 to DMA enough data to keep up with the SCSI; consider this when choosing a slot. For example, if the 721 does not get a high enough priority, then its DMA falls behind the SCSI requirements, and the SCSI device must wait for the 721. If the 721 priority is high, it gets enough DMA time, but other boards having smaller buffers may not receive enough data within the allotted DMA time. The priorities must be balanced for your system to work properly.

#### 2.7.3. Power Considerations

The 721 affects the power consumption of the entire computer system. The 721 uses +5 volts (4.75 to 5.25 volts) at 4.2 amps. Make sure the power supplies can handle the entire power load. Readjust the voltages *after* plugging in the 721. A power supply that is just adequate may cause intermittent and unusual problems as it generates noise from occasional overcurrent protection.

# 2.8. Installing the 721

Place the 721 into the computer card cage; make sure it is firmly seated. Be careful not to dislodge any socketed ICs. Situate the SCSI device and connect it to its power source.

# 2.9. Cabling the Subsystem

#### 2.9.1. Mechanical Restraint

Mechanically restraining the SCSI cable at both ends prevents it from accidentally disconnecting. Using pull tabs on the cable greatly reduces connector damage.

#### 2.9.2. SCSI Device Grounds

Install a ground braid wire between the ground terminal on the SCSI device(s) and the computer system ground.

# 2.10. Power-up Self Test

The 721 initiates a self test upon power-up. The yellow LED lights for a moment, and then goes off. If it remains on, the board is not functioning properly or the SCSI cable is backwards. The Fatal Error Register may indicate the nature of the problem. Check the power supply voltage to ensure it is within limits (4.75 to 5.25 volts). Contact Xylogics for further assistance.

# 2.11. Diagnostics

When you run your diagnostics:

- Run a full pass of your diagnostic or determine that the system is working properly

- Cable and test any additional devices

# 2.12. Cabling Multiple SCSI Devices

If you are using multiple devices, make sure the cables are properly connected. Observe the pin l markings on both the cables and the devices (see Figure 2-13 and Figure 2-14).

Figure 2-13. Single Initiator, Multiple Target

# 2.12. Cabling Multiple SCSI Devices (continued)

Figure 2-14. Multiple Initiators, Multiple Targets

#### 2.12.1. Terminators

The SCSI bus requires terminators in the first and last connecting SCSI device. Since the 721 has an on-board terminator, only the last SCSI device on the bus requires a terminator. The 721 offers terminator power as a jumper option (J16) with three configurations: supply terminator power to the SCSI bus, supply terminator power locally, and accept terminator power from the bus (see Section 2.3.5.).

#### 2.12.2. Target Select

In a single initiator, multiple target application, assign each target a unique SCSI identification (ID) number. The 721 accesses targets with ID numbers ranging from 0 through 6. ID number 7 is reserved as the 721 default (see Section 5). Each target can connect up to eight logical units having logical unit numbers that range from 0 through 7.

# **The Controller Registers**

3

# The 721 Registers

# 3.1. General

The 721 programming interface uses seven, one-byte long, I/O registers. These registers have one function when read, and another when written. The bus address jumpers define the register set's base address. Table 3-1 lists the registers and the address offset from the base address. Figure 3-1 illustrates the register map, assuming you use EEC0 as the base address.

Table 3-1. Register Offsets

| Register                                     | Offset |

|----------------------------------------------|--------|

|                                              |        |

| IOPB Address Byte 0 (Least Significant Byte) | 1      |

| IOPB Address Byte 1                          | 3      |

| IOPB Address Byte 2                          | 5      |

| IOPB Address Byte 3 (Most Significant Byte)  | 7      |

| IOPB Address Modifier                        | 9      |

| Control and Status Register                  | В      |

| Fatal Error Register                         | D      |

|      |   | 0 7 | 8 16                  |

|------|---|-----|-----------------------|

| EEC0 | 0 | х   | IOPB Address Byte 0   |

| EEC2 | 2 | х   | IOPB Address Byte 1   |

| EEC4 | 4 | x   | IOPB Address Byte 2   |

| EEC6 | 6 | x   | IOPB Address Byte 3   |

| EEC8 | 8 | х   | IOPB Address Modifier |

| EECA | A | х   | CSR                   |

| EECC | С | х   | FERR                  |

Figure 3-1. Register Map

# 3.2. IOPB Address Registers

The first four registers define the 32-bit address of an IOPB. When you write these registers, the 721 interprets the address of the IOPB ready for execution. When you read them, and Remove IOPB (RIO) is set in the Control and Status Register, the registers point to the IOPB that the 721 just completed (see Section 3.4.).

# 3.3. IOPB Address Modifier/Priority IOPB Register

This register defines the IOPB address modifier. Address modifiers are used for many purposes, such as memory mapping, privilege levels, and addressing range (see the VMEbus Specification).

This register also specifies whether an IOPB has priority over the current set of IOPBs in the 721 command queue. Section 3.4. defines the protocol for reading and writing this register.

|                             | U        | 5 4 3 2 1 0      |

|-----------------------------|----------|------------------|

| Priority<br>IOPB<br>Request | Reserved | Address Modifier |

#### Bit Mnemonic Description

- 7 PRIO Priority IOPB Request: When set, the IOPB, precedes all others, except the one in process, in the command queue.

- 6 Reserved.

- 5-0 AM Address Modifier: Most systems use the standard AM code of 3DH (see the VMEbus Specification).

# 3.4. Control and Status Register

When written, this register provides the host with control of the 721 operation. When read, it provides the host with 721 status information. Section 3.4.1. defines the bits in this register when written; Section 3.4.2. defines the bits when read.

#### 3.4.1. Control Register (Write)

| 7                | 6        | 5              | 4        | 3                   | 2           | 1            | 0            |

|------------------|----------|----------------|----------|---------------------|-------------|--------------|--------------|

| Register<br>Test | Reserved | Maint.<br>Mode | Reserved | Controller<br>Reset | Add<br>IOPB | Clear<br>RIO | Clear<br>RBS |

#### Bit Mnemonic Description

REGISTER Test: In maintenance mode, when RT, MM, and AIO are set, the 721 echoes back the values previously written in all of the registers (except the CSR).

#### 6 Reserved.

5 MM Maintenance Mode: Setting MM and AIO places the 721 in maintenance mode. Maintenance mode supports a different register protocol; use it as a diagnostic tool.

#### 4 Reserved.

3 CRST Controller Reset: When set, the 721 performs a *soft* reset to recover from fatal errors; it reinitializes its IOPB and AIO address storage RAM, cancelling any IOPBs in its queues, and clears the Fatal Error Register and CSR. The 721 does not generate RIOs for cancelled IOPBs.

A controller reset does not affect the SCSI bus, and leaves outstanding SCSI transfers in an indeterminate state. A SCSI bus reset should follow a controller reset.

A Controller Reset takes up to one-half second to complete.

Add IOPB: When set, the 721 executes the IOPB at the address pointed to by the IOPB Address and Address Modifier Registers. As soon as the host sets AIO, the 721 sets AIO Pending (AIOP) in the Status Register indicating the 721 has received AIO, but has not yet processed the new IOPB address. The 721 clears AIOP after internally storing the new address. Setting AIO while AIOP is set violates the register protocol.

## 3.4.1. Control Register (Write) (continued)

#### Bit Mnemonic Description

1 CRIO Clear RIO: The host sets CRIO to clear RIO in the Status Register.

Typically, the host sets CRIO after reading the address of a completed IOPB from the IOPB Address and Modifier Registers. Clearing RIO enables the

721 to update the IOPB Address and Modifier Registers with the address and address modifier of a newly completed IOPB. Clearing RIO, if it is not

set in the Status Register, violates the register protocol.

0 CRBS Clear RBS: The host sets CRBS to clear RBS in the Status Register. Clearing

RBS releases the registers for use by another host. CRBS is relevant only in a

multiprocessor environment.

#### 3.4.2. Status Register (Read)

| 7    | 6              | 5                        | 4        | 3                             | 2              | 1              | 0                                  |

|------|----------------|--------------------------|----------|-------------------------------|----------------|----------------|------------------------------------|

| Busy | Fatal<br>Error | Maint.<br>Mode<br>Active | Reserved | Controller<br>Reset<br>Active | AIO<br>Pending | Remove<br>IOPB | Register<br>Busy<br>Sema-<br>phore |

#### Bit Mnemonic Description

7 BUSY

Busy: The 721 is processing IOPBs. The 721 sets Busy when it clears AIOP to acknowledge the first IOPB address; it clears Busy after completing all the IOPBs with no new ones pending (within 500 microseconds of the host clearing RIO on the last IOPB). The 721 redefines this bit in maintenance mode.

#### 3.4.2. Status Register (Read) (continued)

conditions:

#### Bit Mnemonic Description

- FERR Fatal Error: When set, the 721 detected a fatal hardware error. A fatal error asserts SYSFAIL. Setting CRST clears FERR. The Fatal Error Register holds more specific information. The 721 sets FERR under the following

- Maintenance mode test failure

- Power-up self test failure

- IOPB DMA fatal

- IOPB address alignment error

- Firmware error

- Illegal maintenance mode test number

- 5 MMA Maintenance Mode Active: When set, the 721 is in maintenance mode.

- 4 Reserved.

- 3 RSTA Controller Reset Active: The host set CRST in the Control Register and the 721 is reinitializing.

- 2 AIOP AIO Pending: When set, AIO has been set in the Control Register, but the 721 has not acknowledged its receipt. When clear, AIO may be set again.

- 1 RIO Remove IOPB: The 721 sets RIO after completing an IOPB, and placing the address in the IOPB Address and Address Modifier Registers. After the host reads the address and modifier, it must clear RIO by writing CRIO in the Control Register.

- Register Busy Semaphore: RBS allows multiple hosts to share access to the 721 registers without simultaneous access. RBS is relevant only in a multiprocessor environment.

# 3.5. Fatal Error Register

If a fatal error occurs, the 721 returns the appropriate completion code in this register. Table 3-2 lists the fatal error codes. Section 6.4. describes them. All codes not listed are reserved.

Table 3-2. Fatal Error Codes

| Code       | Description                          |

|------------|--------------------------------------|

| <b>E</b> 1 | IRAM/8031 INTRAM Self Test Failure   |

| E2         | SCSI Cable Installed Backwards       |

| E3         | SPC Register Self Test Failure       |

| E5         | FDMAC Register Self Test Failure     |

| <b>E</b> 6 | REGCEL Self Test Failure             |

| E8         | FIFO Self Test Failure               |

| F1         | IOPB DMA Fatal                       |

| F2         | IOPB Address Alignment Error         |

| F3         | Firmware Error                       |

| F5         | Illegal Maintenance Mode Test Number |

| F6         | Abort Message Rejected               |

| F9         | SCSI Illegal Transfer Phase          |

| FC         | Global Timeout Error                 |

# **IOPB Description**

4

# **IOPB Description**

#### 4.1. General

The Input/Output Parameter Block (IOPB) passes messages between the 721 and host software. Software passes the type of transfer, target address, data address, and count to the 721; the 721 returns the transfer status and possibly the ending addresses upon command completion. Each IOPB includes 24 bytes of controller information, and 6, 10, or 12 bytes of SCSI command descriptor block (CDB).

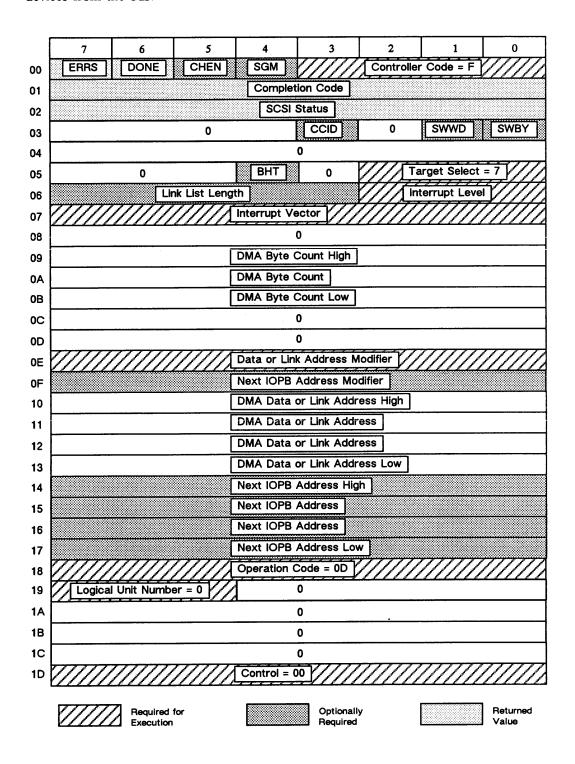

# 4.2. Standard IOPB

The 721 uses the standard 36-byte IOPB for all commands.

|            | _                                                            |                     |          |                                       |                          | 2          | •          | 0      |  |  |

|------------|--------------------------------------------------------------|---------------------|----------|---------------------------------------|--------------------------|------------|------------|--------|--|--|

|            | 7                                                            | 6                   | 5        | 4                                     | 3 2 1 0  Controller Code |            |            |        |  |  |

| 00         | ERRS   DONE   CHEN   SGM   Controller Code   Completion Code |                     |          |                                       |                          |            |            |        |  |  |

| 01         |                                                              |                     |          |                                       |                          |            |            |        |  |  |

| 02         |                                                              |                     |          | SCSI                                  | Status                   |            | 0115115    | 014514 |  |  |

| 03         |                                                              |                     | 0        |                                       | CCID                     | 0          | SWWD       | SWBY   |  |  |

| 04         |                                                              |                     |          | · · · · · · · · · · · · · · · · · · · | 0                        |            |            |        |  |  |

| 05         |                                                              | 0                   |          | BHT                                   | 0                        |            | arget Sele |        |  |  |

| 06         |                                                              | Lini                | List Len | gth                                   |                          | In         | terrupt Le | vel    |  |  |

| .07        |                                                              |                     | In       | terrupt Ve                            | ector                    |            |            |        |  |  |

| 08         |                                                              | 0                   |          |                                       |                          |            |            |        |  |  |

| 09         |                                                              | DMA Byte Count High |          |                                       |                          |            |            |        |  |  |

| 0A         |                                                              |                     | D        | MA Byte (                             | Count                    |            |            |        |  |  |

| <b>₽</b> B |                                                              |                     | D        | MA Byte (                             | Count Low                |            |            |        |  |  |

| 0C         |                                                              |                     |          | 0                                     |                          |            |            |        |  |  |

| 0D         |                                                              |                     |          | 0                                     |                          |            |            |        |  |  |

| 0E         |                                                              |                     | Da       | ata or Link                           | Address                  | Modifier   |            |        |  |  |

| QF.        |                                                              |                     | Ne       | ext IOPB                              | Address M                | lodifier   |            |        |  |  |

| 10         |                                                              |                     | DI       | MA Data o                             | or Link Add              | dress High | 1          |        |  |  |

| 11         |                                                              |                     | DI       | MA Data o                             | or Link Add              | dress      |            |        |  |  |

| 12         |                                                              |                     | DI       | MA Data o                             | or Link Add              | dress      |            |        |  |  |

| ุ13        |                                                              |                     | DI       | MA Data o                             | or Link Add              | dress Low  |            |        |  |  |

| 14         |                                                              |                     | N        | ext IOPB                              | Address H                | igh        |            |        |  |  |

| 15         |                                                              |                     | N        | ext IOPB                              | Address                  |            |            |        |  |  |

| 16         |                                                              |                     | Ne       | ext IOPB                              | Address                  |            |            |        |  |  |

| _17        |                                                              |                     | No       | ext IOPB                              | Address L                | ow         |            |        |  |  |

| 18         |                                                              |                     | C        | DR Rytes                              | 0 through                | 11         |            |        |  |  |

| 23         |                                                              |                     |          | Dy (00                                | - anough                 |            |            |        |  |  |

## 4.2.1. IOPB Byte 0 (Channel Byte)

| 7                | 6    | 5               | 4                          | 3 2 1 0         |

|------------------|------|-----------------|----------------------------|-----------------|

| Error<br>Summary | Done | Chain<br>Enable | Scatter/<br>Gather<br>Mode | Controller Code |

| <u>Bit</u> | Mnemonic | Description                                                                                                                                                                                                                                                                                            |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | ERRS     | <b>Error Summary:</b> ERRS is only valid if <i>Done</i> is set. When set, a hard or soft error occurred during IOPB processing. When clear, the 721 successfully completed the IOPB.                                                                                                                   |

| 6          | DONE     | Done: The 721 sets Done after completing the IOPB.                                                                                                                                                                                                                                                     |

| 5          | CHEN     | Chain Enable: When set, the Next IOPB Address Modifier and Next IOPB Address point to the next chained IOPB. When clear, this IOPB is not chained to another IOPB.                                                                                                                                     |

| 4          | SGM      | Scatter/Gather Mode: When set, the IOPB is either a scatter read or a gather write transfer. A link list describes the number of 16-bit words and the address to which the 721 transfers each section of the data. The link address modifier and the link address specify the link list location. When |

clear, this IOPB specifies the data transfer address. The data is transferred

3-0 CD Controller Code: Always set this field to 0FH.

to/from contiguous memory.

# 4.2.2. IOPB Byte 1 (Completion Code)

After the 721 executes the IOPB, it sets *Done* and posts a completion code in this byte. Completion codes are only valid if *Done* is set. A code of 00H indicates a successful completion; any other value indicates an error occurred (see Section 6.3.).

# 4.2.3. IOPB Byte 2 (SCSI Status)

IOPB Byte 2 is the SCSI Status byte; it is valid only if *Done* is set. The selected target returns this byte after completing each command. It is the last SCSI status that the target returns while running this IOPB or it is an equivalent byte for the floppy drives (see Table 4-1).

Vendor-unique means the American National Standards Institute (ANSI) has not defined the bit, field, or code value. SCSI device manufacturers define these fields.

| 7        | 6 5           | 4 3 2 1     | 0                 |

|----------|---------------|-------------|-------------------|

| Reserved | Vendor-unique | Status Code | Vendor-<br>unique |

Table 4-1. SCSI Status Codes

| Value | Description                     |

|-------|---------------------------------|

| value | Description                     |

| 0000  | Good                            |

| 0001  | Check Condition                 |

| 0010  | Condition Met/Good              |

| 0011  | Reserved                        |

| 0100  | Busy                            |

| 0101  | Reserved                        |

| 0110  | Reserved                        |

| 0111  | Reserved                        |

| 1000  | Intermediate/Good               |

| 1001  | Reserved                        |

| 1010  | Intermediate/Condition Met/Good |

| 1011  | Reserved                        |

| 1100  | Reservation Conflict            |

| 1101  | Reserved                        |

| 1110  | Reserved                        |

| 1111  | Reserved                        |

|       |                                 |

# 4.2.4. IOPB Byte 3 (Controller Command)

| 7 6 5 4  | 3                          | 2        | 1             | 0             |

|----------|----------------------------|----------|---------------|---------------|

| Reserved | Change<br>Controller<br>ID | Reserved | Swap<br>Words | Swap<br>Bytes |

#### Bit Mnemonic Description

7-4

Reserved.

3 CCID

Change Controller ID: When set, you can change the 721 SCSI ID with a Write Controller Parameters command.

2

Reserved.

1 SWWD

Swap Words: When set, the 721 swaps the significance of the two words in a data longword. Swapping does not occur on IOPB transfers, scatter/gather lists, or 721 mode sense/select data, and is independent of setting TMOD. Swap word is not restricted to longword aligned data.

0 SWBY

Swap Bytes: When set, the 721 swaps the significance of the two bytes in a data word. Swapping does not occur on IOPB transfers, scatter/gather lists, or 721 mode sense/select data, and is independent of setting TMOD. Swap Byte transfers are illegal and cause an error if the data address (IOPB Byte 13) is an odd number. Swap bytes is not restricted to word aligned data.

#### 4.2.5. IOPB Byte 5 (Target Select)

| 7 6 5    | 4                         | 3        | 2 1 0         |  |  |

|----------|---------------------------|----------|---------------|--|--|

| Reserved | Black<br>Hole<br>Transfer | Reserved | Target Select |  |  |

#### Bit Mnemonic Description

7-5 Reserved.

## 4.2.5. IOPB Byte 5 (Target Select) (continued)

#### Bit Mnemonic Description

BHT Black Hole Transfer: When set, the 721 does not increment the bus address during a data transfer; IOPB transfers occur normally. When clear, the 721 does increment the bus address.

3 Reserved.

2-0 TGT Target Select: Contains the target device's SCSI bus ID.

## 4.2.6. IOPB Byte 6 (Interrupt Level)

| 7 6 5 4 3        | 2 1 0           |

|------------------|-----------------|

| Link List Length | Interrupt Level |

|                  |                 |

#### Bit Mnemonic Description

- 7-3 LLL Link List Length: Bits 7 through 3 specify the length, in elements, of a link list for Scatter/Gather commands. Each element is an 8-byte block in the link list (see Table 8-2).

- 2-0 INTL Interrupt Level: The 721 uses INTL as the VMEbus interrupt level after completing the IOPB. The 721 does not interrupt if the level is zero.

#### 4.2.7. IOPB Byte 7 (Interrupt Vector)

IOPB Byte 7 determines the interrupt vector that the 721 uses upon command completion. This byte is not valid if the interrupt level is zero.

#### 4.2.8. IOPB Bytes 9 through B (DMA Count)

IOPB Bytes 9 through B are the DMA Count. These bytes specify how many bytes the 721 transfers in a data transfer, Write Controller Parameters, or Read Controller Parameters IOPB. The DMA count must correspond to the transfer length in the CDB.

#### 4.2.9. IOPB Byte E (Data or Link Address Modifier)

| 7 6      | 5 4 3 2 1 0                   |

|----------|-------------------------------|

| Reserved | Data or Link Address Modifier |

Bit Description

7-6 Reserved.

5-0 **Data or Link Address Modifier:** If SGM is set, this field specifies the link list address modifier; if SGM is clear, it specifies the data address modifier.

#### 4.2.10. IOPB Byte F (Next IOPB Address Modifier)

| 7 6      | 5 4 3 2 1 0                |

|----------|----------------------------|

| Reserved | Next IOPB Address Modifier |

#### Bit Mnemonic Description

7-6 Reserved.

5-0 NIAM Next IOPB Address Modifier: This field, along with the Next IOPB Address, points to the next IOPB in the chain. NIAM must contain a valid modifier value if CHEN is set.

# 4.2.11. IOPB Bytes 10 through 13 (DMA Data or Link Address)

IOPB Bytes 10 and 11 are DMA Data Address High; Bytes 12 and 13 are DMA Data Address Low. These bytes comprise the data or SGM link list address pointers. The 721 uses these bytes with the data or link list address modifier to point to the data or linked list address. If SGM is set, this address points to the linked list; if SGM is clear, this address points to the data address. The 721 uses the data address when transferring both data and mode sense or select information to or from host memory.

# 4.2.12. IOPB Bytes 14 through 17 (Next IOPB Address)

IOPB Bytes 14 and 15 are Next IOPB Address High; Bytes 16 and 17 are Next IOPB Address Low. These bytes comprise the Next IOPB Address pointers. The 721 uses these bytes with the Next IOPB Address modifier to point to the next IOPB in the chain (if CHEN is set in Byte 0).

# 4.2.13. IOPB Bytes 18 through 23 (SCSI CDB)

IOPB Bytes 18 through 23 are the SCSI command descriptor block. The 721 passes the CDB to the SCSI target device (see Section 4.3.).

# 4.3. SCSI Command Descriptor Block

IOPB Bytes 18H through 23H comprise the SCSI command descriptor block (CDB). The CDB can be 6-, 10-, or 12-bytes long. The 721 uses the CDB to prepare its data transfer and DMA paths; it sends the complete CDB to the SCSI target. All reserved bits, fields, or bytes must equal zero. For all commands, if there is an invalid parameter in the CDB, the target terminates the command without altering the medium.

Each CDB has an operation code as its first byte, followed by a logical unit number, command parameters (if any), and a control byte. The ANSI X3.131–1986 Specification (pages 51–184) describes the SCSI CDB more fully.

# 4.3.1. Typical Six-byte Command Descriptor Block

The logical block address and the transfer length (specified in blocks or bytes) are not always required and depend on both the command and device type. The CDB transfer length must correspond to the IOPB DMA byte count.

| Offs<br>IOPB = |    | 7                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|-------------------------------------------------|---|---|---|---|---|---|---|

| 18             | 00 | Operation Code                                  |   |   |   |   |   |   |   |

| 19             | 01 | Logical Unit Number Logical Block Address (MSB) |   |   |   |   |   |   |   |

| 1A             | 02 | Logical Block Address                           |   |   |   |   |   |   |   |

| 1 <b>B</b>     | 03 | Logical Block Address (LSB)                     |   |   |   |   |   |   |   |

| 1C             | 04 | Transfer Length                                 |   |   |   |   |   |   |   |

| 1D             | 05 | Control                                         |   |   |   |   |   |   |   |

# 4.3.2. Typical\Ten-byte\ Command Descriptor Block

| Offset<br>IOPB = CDB |    | 7                     | 6                           | 5 | 4       | 3        | 2 | 1 | 0   |

|----------------------|----|-----------------------|-----------------------------|---|---------|----------|---|---|-----|

| 18                   | 00 |                       |                             |   | Operati | ion Code |   |   |     |

| 19                   | 01 | Logic                 | Logical Unit Number 0 RA    |   |         |          |   |   | RAD |

| 1A                   | 02 |                       | Logical Block Address (MSB) |   |         |          |   |   |     |

| 1B                   | 03 |                       | Logical Block Address       |   |         |          |   |   |     |

| 1C                   | 04 |                       | Logical Block Address       |   |         |          |   |   |     |

| 1D                   | 05 |                       | Logical Block Address (LSB) |   |         |          |   |   |     |

| 1E                   | 06 |                       | 0                           |   |         |          |   |   |     |

| 1F                   | 07 |                       | Transfer Length (MSB)       |   |         |          |   |   |     |

| 20                   | 08 | Transfer Length (LSB) |                             |   |         |          |   |   |     |

| 21                   | 09 |                       | Control                     |   |         |          |   |   |     |

# 4.3.3. Typical Twelve-byte Command Descriptor Block

| Offset<br>IOPB = CDB |    | 7     | 6        | 5      | 4       | 3              | 2         | 1    | 0   |  |

|----------------------|----|-------|----------|--------|---------|----------------|-----------|------|-----|--|

| 18                   | 00 |       |          |        |         | Operation Code |           |      |     |  |

| 19                   | 01 | Logic | cal Unit | Number |         | (              | )         |      | RAD |  |

| 1A                   | 02 |       |          |        | Logical | Block A        | ddress (1 | MSB) |     |  |

| 1B                   | 03 |       |          |        | Logical | Block A        | ddress    |      |     |  |

| 1C                   | 04 |       |          |        | Logical | Block A        | ddress    |      |     |  |

| 1D                   | 05 |       |          |        | Logical | Block A        | ddress (  | LSB) |     |  |

| iE                   | 06 |       |          |        |         | 0              |           |      |     |  |

| 1F                   | 07 |       | 0        |        |         |                |           |      |     |  |

| 20                   | 08 |       |          |        |         | 0              |           |      |     |  |

| 21                   | 09 |       |          |        | Transfe | er Length      | (MSB)     |      |     |  |

| 22                   | 0A |       |          |        | Transfe | er Length      | (LSB)     |      |     |  |

| 23                   | 0B |       |          |        | Contro  |                |           |      |     |  |

# 4.3.4. CDB Byte 0 (Operation Code)

The first byte of all CDBs is the operation code.

| 7 6 5      | 4 3 2 1 0    |  |  |  |  |  |

|------------|--------------|--|--|--|--|--|

| Group Code | Command Code |  |  |  |  |  |

|            |              |  |  |  |  |  |

# Bit Mnemonic Description

7-5 GC Group Code: Designates one of eight command groups. The 721 fully supports the mandatory, optional, and extended commands in Groups 0 and 1. Groups 2 through 7 are all vendor-unique or reserved commands. The 721 supports these commands by passing through software requests and transferring data or parameters according to the SCSI bus data phase.

## 4.3.4. CDB Byte 0 (Operation Code) (continued)

#### Bit Mnemonic Description

4-0 CC Command Code: Designates one of 32 commands available in the group.

Table 4-2. Group Codes

| Group | Description            |

|-------|------------------------|

| 0     | 6-byte commands        |

| 1     | 10-byte commands       |

| 2-4   | Reserved               |

| 5     | 12-byte commands       |

| 6-7   | Vendor-unique commands |

## 4.3.5. CDB Byte 1 (Logical Unit Number)

The second byte of all CDBs defines the logical unit number of the peripheral device attached to the selected SCSI target to which the command applies. It also contains other information that is command- and device type-dependent (see Section 5).

#### 4.3.6. CDB Bytes 2 through 10 (Transfer Information)

Six-byte CDBs use Bytes 2 through 4, 10-byte CDBs use Bytes 2 through 8, and 12-byte CDBs use Bytes 2 through 10. These bytes may be reserved, specify the logical block address for a command on a direct access device, or a transfer count on a sequential access device (see Section 5).

#### 4.3.7. CDB Bytes 5, 9, and 13 (Control)

Six-byte CDBs use Byte 5, 10-byte CDBs use Byte 9, and 12-byte CDBs use Byte 13.

# Commands

5

# **Commands**

#### 5.1. General

As an initiator, the 721 supports all SCSI commands for all SCSI devices (see your device manual for specific command information). The 721 also supports five controller-specific commands (see Sections 5.3. through 5.7.).

## 5.2. SCSI Command Codes

Table 5-1 and Table 5-2 list the SCSI Group 0 and Group 1 command codes. The directive (Dir.) column defines all the SCSI commands that transfer data between system memory and the target device. You can also use vendor-unique commands that are not listed since the 721 transfers data according to the SCSI bus requests.

Key to Table 5-1 and Table 5-2:

#### 721 Directive:

NO = No data transfer

RD = Read data from SCSI to system memory

WD = Write data from system memory to SCSI

RP = Read parameters from SCSI to system memory

WP = Write parameters from system memory to SCSI

#### SCSI Command Implementation Levels:

M = Mandatory

O = Optional

R = Reserved

V = Vendor-unique

E = Extended (required for self-configuring software)

#### 5.2.1. SCSI Group 0 Command Codes

Table 5-1. SCSI Group 0 Command Codes

# 5.2.2. SCSI Group 1 Command Codes

Table 5-2. SCSI Group 1 Command Codes

# 5.3. Command Structure

All 721 commands use the same IOPB structure. The following diagram shows which bytes the 721 absolutely requires for command execution, which bytes are optional, and which bytes it returns after execution.

Each IOPB is 36-bytes long. Reserving all 36 bytes in memory maintains IOPB integrity.

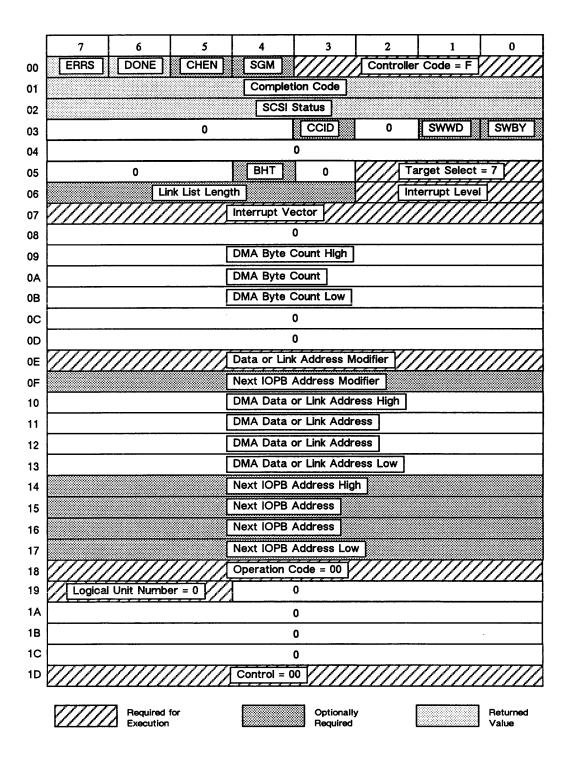

# 5.4. No Operation

This is an implementation of the SCSI Test Unit Ready command. Addressing the 721's target ID (seven) and logical unit zero executes a No Operation (NOP) command.

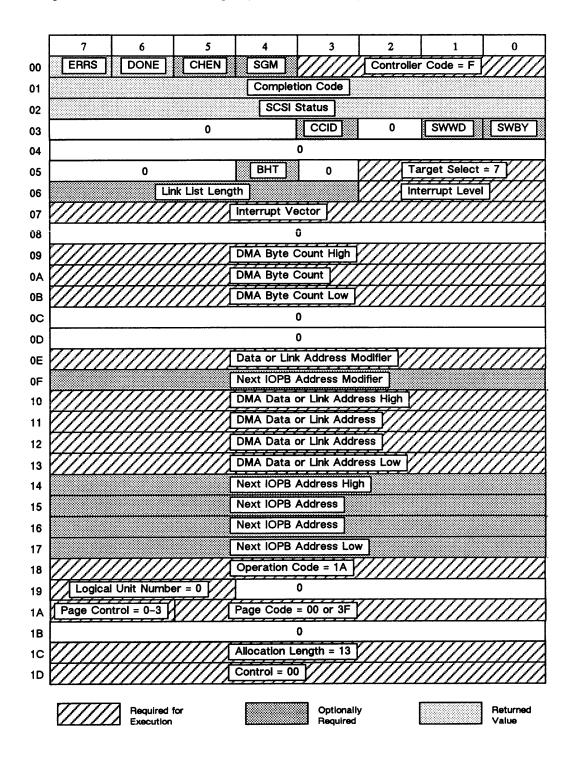

#### 5.5. Read Controller Parameters

This is a vendor-unique implementation of the SCSI Mode Sense command. Addressing the 721's target ID (seven) and logical unit zero executes a Read Controller Parameters command. The parameter list is vendor-unique (see Section 5.5.2.).

#### 5.5.1. Read Controller Parameters CDB

#### 5.5.1.1. Logical Unit Number

Always address the 721 as logical unit zero.

#### 5.5.1.2. Page Control

There are four valid page control values:

- 0H = Report Current Values

- 1H = Report Changeable Values

- 2H = Report Default Values

- 3H = Report Saved Values (same as default)

#### 5.5.1.3. Page Code

There are two valid page code values:

- 00H = Report Page Zero

- 3FH = Report All Pages (returns only page zero)

#### 5.5.1.4. Allocation Length

An allocation length of 13H or greater returns 19 bytes of mode sense data (all the 721's information). An allocation length of less than 13H returns that number of mode sense bytes.

#### 5.5.2. Parameter List

All the values listed in Table 5-3 are expressed in hexadecimal. The X represents a programmable value in the Read Controller Parameters command.

# 5.5.2. Parameter List (continued)

Table 5-3. Read Controller Parameters List

| Byte     | Description Pag                       | e Contro    | l = 0 | 1             | A 2 pt | 7 3 /    |     |

|----------|---------------------------------------|-------------|-------|---------------|--------|----------|-----|

| Header   |                                       |             | 10    | URRE          | JCK"   | FEF-AUCT | 151 |

| 00       | Campa Data Lameth                     |             | 13    | Citr          | 13     | 13       |     |

| 01       | Sense Data Length                     | 12          | 80    | 80            | 80     | 80       |     |

|          | Vendor-unique Medium Type<br>Reserved |             | 00    | 00            | 00     | 00       |     |

| 02       |                                       |             |       |               |        |          |     |

| 03       | Block Descriptor Length               |             | 00    | 00            | 00     | 00       |     |

| Page 0   |                                       |             |       |               |        |          |     |

| 04       | Page Code (Vendor-unique = 0)         | )           | 00    | 00            | 00     | 00       |     |

| 05       | Page Length                           |             | 0D    | 0D            | 0D     | 0D       |     |

| 06       | Controller Parameters                 |             | XX    | FF            | 00     | 00       |     |

| 07       | Throttle Dead Time and ROR            |             | X0    | $\mathbf{D0}$ | 00     | 00       |     |

| 08       | DMA Throttle                          |             | XX    | FF            | 00     | 00       |     |

| 09       | Sequential Device Types               | \           | XX    | FF            | 00     | 00       |     |

| 0A       | Host BDID                             |             | 0X    | 07            | 07     | 07       |     |

| 0B       | Inhibit Probe for Sync                |             | XX    | FF            | 00     | 00       |     |

| 0C-0D    | Reserved                              |             | 00    | 00            | 00     | 00       |     |

| 0E       | EPROM Number High                     |             | NN    | 00            | NN     | NN       |     |

| 0F       | EPROM Number Low                      | V design of | NN    | 00            | NN     | NN       |     |

| 10       | Firmware Release                      |             | NN    | 00            | NN     | NN       |     |

| 11       | Firmware Revision                     | 477         | NN    | 00            | NN     | NN       |     |

| 12       | Firmware Subrevision                  |             | NN    | 00            | NN     | NN       |     |

| 13       | Reserved                              | 1           | 00    | 00            | 00     | 00       |     |

|          |                                       |             |       |               |        |          |     |

| 5.5.2.1. | Controller Parameters                 |             |       |               |        |          |     |

| 7               | 6                | 5                 | 4              | 3                        | 2                                     | 1 0                  |

|-----------------|------------------|-------------------|----------------|--------------------------|---------------------------------------|----------------------|

| Auto-<br>update | Transfer<br>Mode | Disable<br>Timers | SCSI<br>Parity | Enable<br>DMA<br>Timeout | Non-<br>privileged<br>Request<br>Mode | AIO Response<br>Time |

#### 5.5.2.1. Controller Parameters (continued)

#### Bit Mnemonic Description

- AUD Auto-update: When set, the 721 updates the IOPB to the transfer's ending parameters; it updates the DMA count data address after completing the transfer or detecting an error. When clear, the 721 only updates the IOPB if an error occurs. The update includes the DMA count and the final data address plus one transfer. Default: set.

- Transfer Mode: When set, the 721 executes data transfers in longword mode. When clear, it executes transfers in word mode. IOPB transfers are always in word mode. If a transfer starts on an improper address boundary, the 721 transfers a byte and/or a word, as necessary to align boundaries, and continues the transfer in the selected mode. The 721 may end the transfer with a byte and/or a word. Default: clear.

- 5 DT Disable Timers: Setting DT disables global timeouts. Clearing DT enables global timeouts. Default: clear.

- 6 SP SCSI Parity: When set, the SPC checks/generates parity on SCSI data. When clear, the 721 ignores SCSI parity. Default: clear.

- 3 EDT Enable DMA Timeout: When set, the 721 enables an on-board DMA bus error timer. When clear, the 721 relies on the external VMEbus transfer timer. The timeout period is one millisecond. Default: clear.

- NPRM Non-privileged Request Mode: When set, the 721 responds to address modifiers 2DH and 29H. When clear, the 721 only responds to 2DH. The VMEbus Specification describes address modifiers. Default: set.

- 1-0 AIOR AIO Response Time: This is the maximum time from setting AIO to the time the 721 clears it. The shorter the response time, the greater the 721 overhead. Default: 00.

Table 5-4. AIO Response Times

| Value | Time                  |

|-------|-----------------------|

| 00    | 100 microseconds (μs) |

| 01    | 75 μs                 |

| 02    | 62 μs                 |

| 03    | 50 μs                 |

|       |                       |

#### 5.5.2.2. Throttle Dead Time and Release on Request

| 7 6                   | 5        | 4                        | 3 2 1 0  |

|-----------------------|----------|--------------------------|----------|

| Throttle Dead<br>Time | Reserved | Release<br>on<br>Request | Reserved |

#### Bit Mnemonic Description

7-6 TDT Throttle Dead Time: TDT selects one of four minimum time periods that determines the time the 721 remains off the bus between throttle bursts (see Section 8.4.). Default: 00.

#### 5 Reserved.

ROR Release on Request: When set, the 721 releases the bus at the request of other bus masters; otherwise, it continues with the next throttle burst. The 721 monitors the bus request lines and releases Bus Busy only if another bus request is pending. It completes the specified throttle burst before releasing the bus due to a pending request. When clear, the 721 releases the bus at the end of each throttle burst and rearbitrates if more data transfers are pending. Default: clear.

#### 3-0 Reserved.

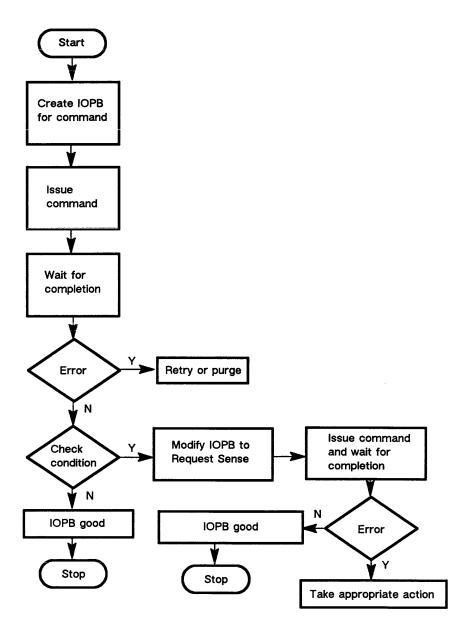

#### 5.5.2.3. DMA Throttle