Applied Microsystems Corporation 11003-118th Place N.E. Kirkland, WA 98033 (206) 823-9911

Toll Free Service: 1-800-426-3925

EM-188 Diagnostic Emulator

# Table of Contents

| Sect | tion 1 - Introduction                          |      |

|------|------------------------------------------------|------|

| 1-1  | System Concept                                 | . 2  |

| 1-2  | Transparency                                   | . 2  |

| 1-3  | Warranty                                       | . 2  |

| 1-4  | General Specifications                         | . 3  |

| Sec  | tion 2 - EM-188 Components                     |      |

| 2-1  | Operator's Station                             | . 6  |

| 2-2  | Emulator Probe                                 | . 6  |

| 2-3  | Keyboard                                       | . 6  |

| 2-4  | Diagnostic EPROM Socket                        | . 6  |

| 2-5  | Display Panel                                  |      |

| 2-6  | Trace Memory                                   | . 6  |

| 2-7  | Back Panel Controls and Connectors             |      |

| 2-8  | RAM Overlay                                    |      |

| 2-9  | Disassembler                                   | . 10 |

| Sec  | tion 3 - Basic Operating Instructions          |      |

| 3-1  | Operating Voltage                              | . 12 |

| 3-2  | Safety Information                             | 12   |

| 3-3  | Connection to Target Equipment                 |      |

| Sec  | tion 4 - EM-188 Functions                      |      |

| 4-1  | Execution Control                              | 16   |

| 4-1  | 4-1.0 RESET Key                                | 16   |

|      | 4-1.0 RESLITREY                                |      |

|      | 4-1.2 RUN BKPT Keyswitch                       |      |

| 1    | 4-1.3 STEP Keyswitch                           | 17   |

|      | 4-1.4 Breakpoint System                        | 19   |

|      | 4-1.5 Trace Memory                             |      |

| 4-2  | Examination and Alteration of CPU Registers    |      |

| 4-3  | Examination and Alteration of Memory Locations | . 23 |

| 4-4  | Examination and Alteration of I/O Ports        | . 24 |

|      | etion 5 - RAM Overlay                          |      |

| 5-1  | Overview                                       | 26   |

| 1    | Controls                                       | 26   |

| 5-2  |                                                | . 20 |

| Sec  | ction 6 - Disassembly                          |      |

| 6-1  | Overview                                       |      |

|      | 6-1.1 Operation Preparation Procedures         |      |

| 6-2  | Format Definition                              | . 31 |

| Sec  | ction 7 - Built-In Diagnostic Functions        |      |

| 7-1  | Group A: Memory Tests                          | . 36 |

| 7-2  | Group B: Oscilloscope Loops                    | . 40 |

| 7-3  | Group C: Memory Load and Dump                  |      |

| 7-4  | Group D: Miscellaneous                         |      |

| 7-5  | Group E: Change Default Parameters             |      |

| 7-6  | Group F: Internal Operations                   | . 47 |

| Sect | ion 8 - User Implemented Code Functions |

|------|-----------------------------------------|

| 8-1  | Overview                                |

| 8-2  | Internal Environment                    |

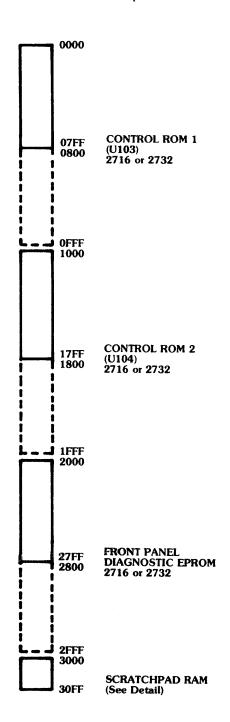

|      | 8-2.1 ROM                               |

|      | 8-2.2 Front Panel EPROM Socket          |

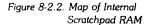

|      | 8-2.3 Scratchpad RAM                    |

|      | 8-2.4 I/O Devices                       |

| 8-3  | Entry to User Code Functions            |

| 8-4  | Introspection Mode                      |

|      | 8-4.1 Code F                            |

| 8-5  | Getting To and From the Target System   |

|      | 8-5.1 Examine and Store                 |

|      | 8-5.2 Pause to Run                      |

|      | 8-5.3 Run to Pause                      |

| •    | 8-5.4 Re-entry Jump                     |

| 8-6  | User Accessible Subroutines             |

| 8-7  | Interrupts                              |

| 8-8  | Code Function Examples                  |

| Sac  | tion 9 - Supplementary Information      |

|      | • •                                     |

| 9-1  | Auxiliary Connector                     |

| 9-2  | Option Switches                         |

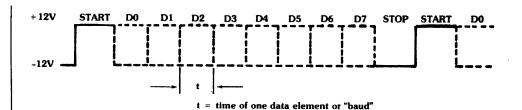

| 9-3  | Serial Interface                        |

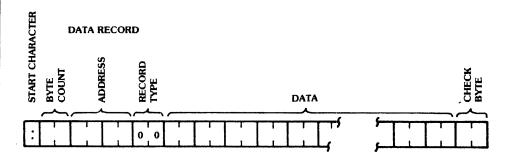

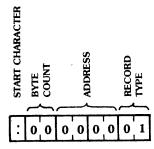

| 9-4  | Upload/Download Protocol                |

| 9-5  | External Breakpoint                     |

| 9-6  | Trace Hold                              |

|      | 9-6.1 Window Mode                       |

|      | 9-6.2 Selective Trace                   |

| 9-7  | Signature Analysis                      |

| 9-8  | Soft Shutdown                           |

# SECTIONN 5

## **INTRODUCTION**

- 1-1 System Concept

- 1-2 Transparency

- 1-3 Warranty

- 1-4 General Specifications

### 1-1 SYSTEM CONCEPT

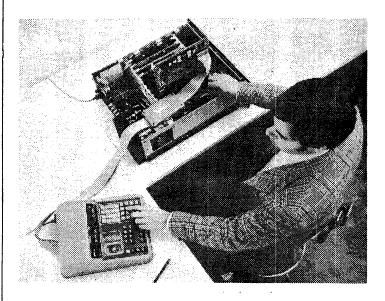

The EM-188 Diagnostic Emulator is a microprocessor test and diagnosis instrument designed to emulate the 8085A or 8085A-1 microprocessors. An alternate cable pod and cable assembly enables the unit to emulate the 8080A, 8080A-1 and 8080A-2 microprocessors. The Diagnostic Emulator consists of an Operator's Station with Keyboard and Display Panel and an Emulator Pod and Cables for connection to the user's system. The EM-188 is fast and easy to use and includes many diagnostic capabilities for troubleshooting problems in the user's system.

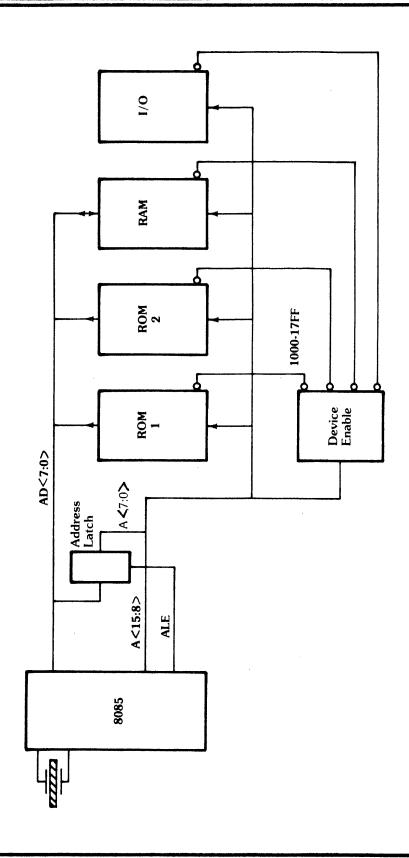

Figure 1-1.1

### 1-2 TRANSPARENCY

The EM-188 Diagnostic Emulator is transparent to the normal operation of the target system in that emulation is in real-time, with no additional processor cycles required as a result of the emulation process. There are no target system addresses or I/O ports needed or used by the EM-188 and there are no programs or other software objects that are required to be in the target address space. As a consequence of this transparancy, the user should not experience difficulties in using the EM-188 Diagnostic Emulator with his system even if there are critical software timing constraints in his system.

### 1-3 WARRANTY

Applied Microsystems Corporation (AMC) warrants that the articles furnished hereunder are free from defects in material and workmanship and perform to applicable published AMC specifications for one year from date of shipment. This warranty is in lieu of any other warranty expressed or implied. In no event will AMC be liable for special or consequential damages as a result of any alleged breach of this warranty provision. The liability of AMC hereunder shall be limited to replacing or repairing, at its option, any defective units which are returned F.O.B. AMC's plant. Equipment or parts which have been subject to abuse, misuse, accident, alteration, neglect, unauthorized repair or installation are not covered by warranty. AMC shall have the right of final determination as to the existence and cause of defect. When items are repaired or replaced, the warranty shall continue in effect for the remainder of the warranty period, or for 90 days following date of shipment by AMC, whichever period is longer.

## 1-4 GENERAL SPECIFICATIONS

### **Input Power**

90 to 140 Vac

60 Hz

less than 50 watts

### **Optional**

180 to 280 Vac

50 Hz

less than 50 watts

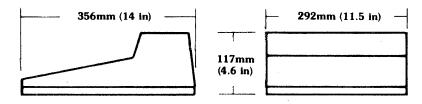

### **Physical**

### **Operator's Station**

Width:

292mm (11.5 inches)

Height:

117 mm (4.6 inches)

Depth:

356 mm (14 inches)

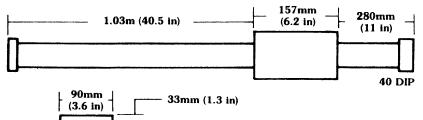

### Target System Connection (Ribbon Cable)

Total Length (including Pod):

1.5M (58 inches)

### **Emulator Cable Pod**

Width:

90mm (3.6 inches)

Depth:

33mm (1.3 inches)

### **Total Weight**

4.5 Kg (11 lbs); Shipping 6.3 Kg (14 lbs)

### **Environmental**

Operating Temperature:  $0^{\circ}$ C to  $40^{\circ}$ C ( $32^{\circ}$ F to  $104^{\circ}$ F) Storage Temperature:  $-40^{\circ}$ C to  $70^{\circ}$ C ( $-40^{\circ}$ F to  $158^{\circ}$ F)

Humidity: 5% to 95% RH non-condensing

### **Operator's Station**

### **Emulator Probe**

# SECIMONN 2

### **EM-188 COMPONENTS**

- 2-1 Operator's Station

- 2-2 Emulator Probe

- 2-3 Keyboard

- 2-4 Diagnostic EPROM Socket

- 2-5 Display Panel

- 2-6 Trace Memory

- 2-7 Back Panel Controls and Connectors

- 2-8 RAM Overlay

- 2-9 Disassembler

### 2-1 OPERATOR'S STATION

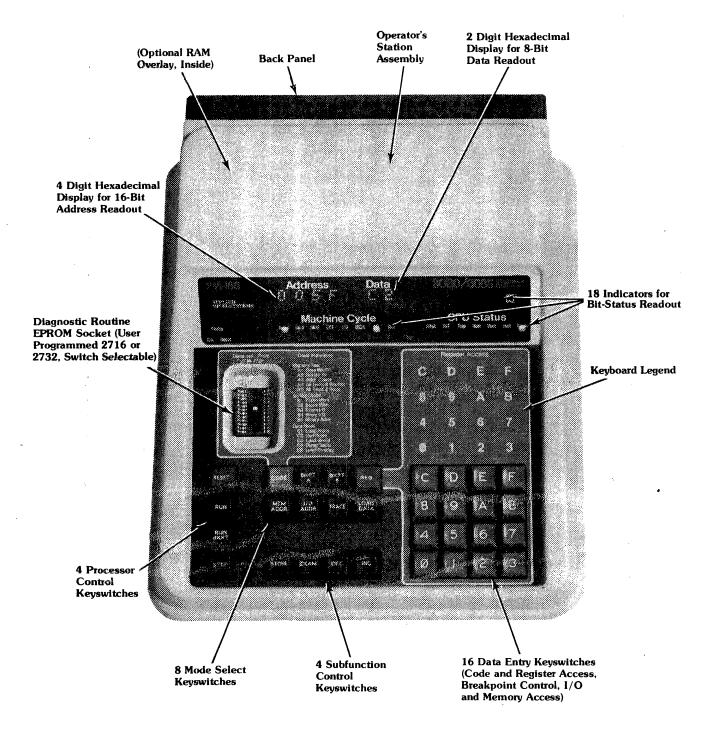

The EM-188 Operator's Station consists of a Keyboard, Display Panel, Diagnostic EPROM Socket, Back Panel Controls and Connectors. It contains most of the system electronics, including the emulation control circuitry, Trace Memory, Breakpoint Comparators, plus control firmware with preprogrammed test routines. A RAM Overlay option may be included. See Figure 2-1.1.

### 2-2 EMULATOR PROBE

Two Emulator Probes are available: The EP-8085 for the 8085A and 8085A-2 microprocessors and the EP-8080 for the 8080A, 8080A-1 and 8080A-2. The Probe contains the CPU and associated circuitry and buffers. It connects to the Operator's Station via 40-inch ribbon cables and to the target system CPU socket via 11-inch ribbon cables and a 40-contact DIP connector.

### 2-3 KEYBOARD

The Keyboard has 32 keyswitches divided into four groupings: Processor Control, Mode Select, Subfunction Control and Data Entry.

# 2-4 DIAGNOSTIC EPROM SOCKET

A low insertion force EPROM socket to accept EPROMs compatible with Intel 2716 or 2732 types (single +5 power supply and Intel pinout). The user may create his own system test and diagnosis routines, program the EPROM with these routines, insert the EPROM into the EM-188 front panel socket and then execute the routines in a convenient manner from the EM-188 Keyboard. See Section 8: USER IMPLEMENTED CODE FUNCTIONS.

### 2-5 DISPLAY PANEL

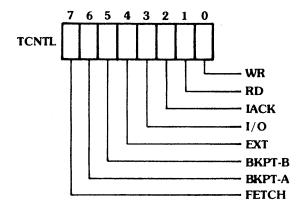

The Display Panel consists of LED dot-matrix address and data displays and of individual LED indicators. Address and data information are displayed in hexadecimal notation. The individual indicator LEDs are divided into five groupings: Fault indicators (CLK, RESET) show loss of system clock or a continuous RESET condition; Machine Cycle indicators (Fetch, BK A, BK B, EXT, I/O, IACK, RD, WR) readout the control bus and other information acquired during target program execution; the microprocessor condition code bits (S, Z, AC, P, CY) are also displayed on these indicators; CPU Status indicators (IENA, INT, Trap, Hold, Wait, Halt, Pause) show the condition of the emulated target system CPU; Breakpoint Enable (BKPT ENA) is illuminated if the Breakpoint System is enabled.

### 2-6 TRACE MEMORY

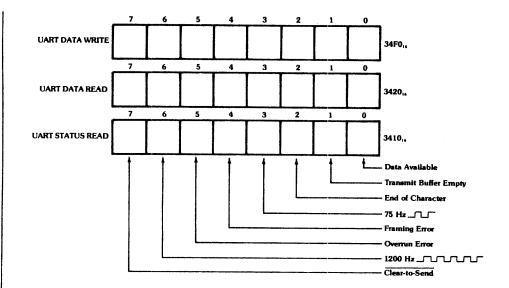

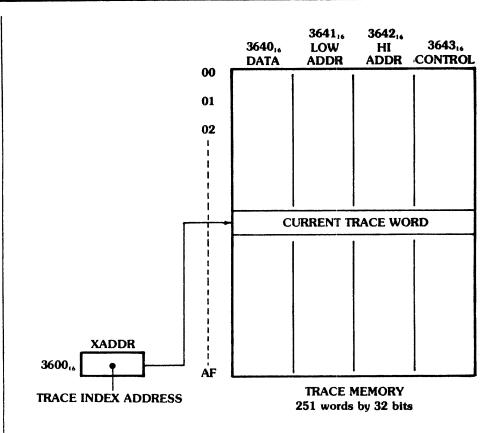

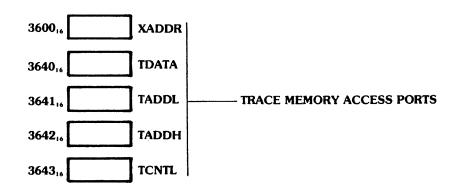

The Trace Memory is a 251-word by 32-bit memory that captures information from each bus cycle of the emulated target system microprocessor. The information recorded is: the 16 address bits, 8 data bits, CPU read and write signals, the type of bus cycle (i.e., op-code Fetch, I/O, or Interrupt Acknowledge) and three possible breakpoint sources - the Breakpoint A Comparator, the Breakpoint B Comparator and the External Breakpoint input.

Figure 2-1.1. Operator's Station

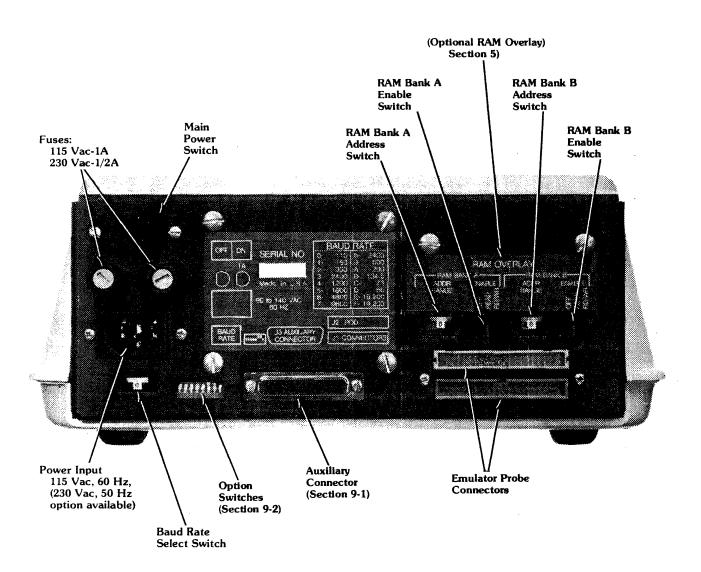

Figure 2-7.1. Back Panel

# 2-7 BACK PANEL CONTROLS AND CONNECTORS

The Back Panel of the EM-188 includes the controls and various connectors used to connect the Diagnostic Emulator with power, the Emulator Probe and other external equipment:

### Main Power Switch

Controls the primary power to the unit.

### **Baud Rate Selector Switch**

A 16-position switch is used to control the transmission rate of serial data flow between the Diagnostic Emulator and peripheral equipment. The baud rate selection options are visible on the Back Panel template shown in Figure 2-7.1.

### **Auxiliary Connector**

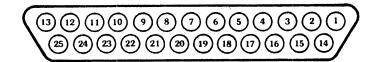

A 25-pin, D subminiature female connector. It provides RS-232C signals and additional control signals to auxiliary equipment (i.e., signature analyzer, oscilloscope, target system, development system). See Section 9-1.

### **Option Switches**

These switches control characteristics of the EM-188 RESET circuitry and communications interface. The normal switch positions for most users are shown in Figure 2-2. The EM-188 is shipped from the factory in this configuration. Alternative positions are discussed and illustrated in Section 9-2.

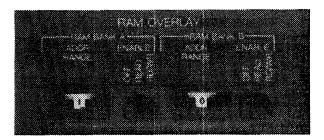

### RAM Overlay Bank A and Bank B Address Switches

Two 16-position switches are used to select the address range to which the A and B blocks of enabled overlay memory responds. See Section 5, RAM Overlay

### RAM Overlay Bank A and Bank B Enable Switches

Two 3-position toggle switches control the A or B block of overlay memory. The left position (OFF) disables a memory block, effectively removing it from the system. The center position (READ) enables the memory block for read-only operations (read-only-memory simulation). The right position (RD/WR) enables a memory block for both read and write operations.

### 2-8 RAM OVERLAY

The EM-188 may be configured to include optional overlay memory. This feature consists of 8K bytes of 200 nsec static memory that is divided into two independent 4K byte blocks. Each block may be enabled as read-write memory, used as read-only memory or disabled. Back Panel switches are used to adjust each memory block to reside in any one of 16 address blocks in the target address space. When a memory block is enabled, it is mapped into the target address space, overlaying the user's system in the address block selected. The overlay memory may be loaded from the target system memory, front panel EPROM or external device by executing the appropriate Code Function. See Section 5, RAM Overlay.

### 2-9 DISASSEMBLER

The EM-188 may be configured with an optional firmware package that provides for formating and output of system information to an ASCII terminal device with RS-232C interface such as a CRT or hard copy terminal. The disassembly firmware extracts information from the EM-188 Trace Memory and emulation processor registers, formats the data for display with instruction op-codes given in standard Intel mnemonic form (LDA, LHLD, INR, JMP, etc.) and outputs the data through the serial port. See Section 6.

10

# S|E(C/[[(O)]N] 8.

## **BASIC OPERATING INSTRUCTIONS**

- 3-1 Operating Voltage

- 3-2 Safety Information

- 3-3 Connection to Target Equipment

### 3-1 OPERATING VOLTAGE

The EM-188 Diagnostic Emulator is normally supplied for operation from 90 to 140 Volts AC at 58 to 62 Hz line. The unit is also available to operation from 180 to 280 Volts AC at 48 to 52 Hz line if specified at time of order. The EM-188 uses a regulating transformer that also has the advantage of providing good blocking of conducted noise that may be present on the power input to the unit.

### 3-2 SAFETY INFORMATION

The EM-188 is supplied with a 3-wire cord with a 3-terminal polarized plug for connection to the power source and protective ground. The ground terminal of the plug is connected to the metal chassis parts of the instrument. Electric-shock protection is provided if the plug is connected to a mating outlet with a protective ground contact that is properly grounded.

The internal (logic) ground of the EM-188 is not connected to the protective ground, but floats to the same potential as the equipment to which the unit is connected. The user is cautioned that it is conceivable that grounding conflicts could occur if the EM-188 is connected to two different items of equipment with differing ground potentials such as the target equipment and a RS-232C terminal.

# 3-3 CONNECTION TO TARGET EQUIPMENT

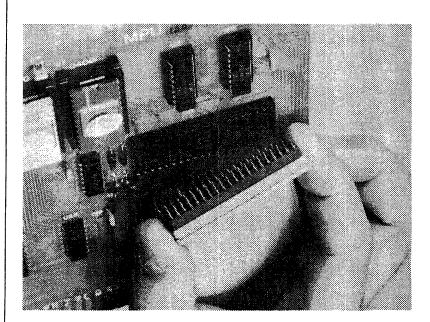

Connect the EM-188 Diagnostic Emulator to the target system by removing the microprocessor from its socket in the user's system and plugging in the 40-pin plug of the EM-188. (See Figure 3-3.1.)

Figure 3-3.1. Installing 40-pin plug.

### CAUTION: NOTE CORRECT PIN 1 ORIENTATION

### BASIC OPERATING INSTRUCTIONS

Apply power to the EM-188 and the target system after the unit is properly connected to the target circuitry. Once power is applied to the Diagnostic Emulator and the clock begins operating, it performs a Power-on-reset operation during which the following functions are performed:

- 1. Reset CPU.

- 2. Clear Trace Memory and CPU Registers.

- 3. Clear the program starting address to zero (the default starting address) and display the address.

- 4. The Diagnostic Emulator awaits further input from the operator.

After the EM-188 is connected to the target system and power is applied to both the EM-188 and the target system, perform the following checks to verify that the unit is operating correctly:

- The Clock Fault and Reset Fault indicators are not illuminated. This means that the 8085 clock oscillator is operating (or if an 8080, that clock signals are present from the target system) and that there is not a continuous RESET signal from the target system.

- 2. The PAUSE indicator should be illuminated. This indicates that no target program is executing and that the EM-188 is awaiting operator commands.

- 3. At power on time, the ADDRESS Display should indicate 0000. If it does, the EM-188 internal control program is operating.

If all is well, proceed to operate the Diagnostic Emulator as appropriate. See Section 4 for details of EM-188 functions.

# SECIION &

## **EM-188 FUNCTIONS**

- 4-1 Execution Control

- 4-2 Examination and Alteration of CPU Registers

- 4-3 Examination and Alteration of Memory Locations

- 4-4 Examination and Alteration of I/O Ports

A basic function of the EM-188 is to emulate the target system microprocessor. Effectively, the Diagnostic Emulator is a pin-compatible functional replacement for the microprocessor in the target system. The unit is designed to meet the timing specifications of the emulated processor and to minimize the increase in electrical loading of the user's system.

The EM-188 is always in one of two modes: RUN or PAUSE. If in the RUN mode, the EM-188 is emulating the target system microprocessor and executing the target system program at full system speed. The Trace Memory will be active (unless inhibited by external control) and all bus cycles of the emulated microprocessor are recorded for possible later display. In the PAUSE mode, emulation of the target system microprocessor is suspended and the operator is able to perform other functions such as manually examining or altering memory locations, I/O ports or internal registers of the emulated microprocessor; the operator may also review the history of the target program execution from the Trace Memory or execute one of the Code Function routines.

### 4-1 EXECUTION CONTROL

The operator controls the EM-188 primarily through the Operator's Station Keyboard. Keyswitch groupings are designed for easy understanding and convenient use. The EM-188 display provides the operator with information about program execution, CPU status and EM-188 conditions. Table 4-1.1 defines the Display Panel indicators.

### 4-1.0 RESET Keyswitch

The red RESET Keyswitch always resets the microprocessor and initializes the EM- 188 in the PAUSE mode. At this time the Address Display shows the program starting address. The program starting address may be changed at this time by entering digits with the hexadecimal keyswitches, or the current program starting address may be used.

The option switches accessible at the Back Panel of the EM-188 may be used to set up one of several options concerning the RESET circuitry of the EM-188 and the target system. See Section 9-2.

### 4-1.1 RUN Keyswitch

Pressing the RUN Keyswitch causes the EM-188 to execute the target program beginning at the preset address or continuing from the last instruction executed. Execution is at full system speed with no extra wait states beyond those commanded by the target system. The activity of the executing program is recorded continuously in the Trace Memory. It is also possible to obtain a general view of the program activity by watching the displays. For example, it is possible to tell if the program is in a tight loop or ranging widely in the program address space by observing changes in the Address Display.

**EM-188 FUNCTIONS**

### 4-1.2 RUN BKPT Keyswitch

does RUN, except the breakpoint-stop circuitry is enabled. If a breakpoint is detected, the EM-188 will pause before executing the next instruction, and the display will show the cycle where the breakpoint was detected. Pressing RUN BKPT again will cause execution to resume until the breakpoint is again detected. The breakpoint- stop circuitry may be disabled during program execution by pressing RUN.

This Keyswitch starts the EM-188 running the target program in real time, as

### 4-1.3 STEP Keyswitch

Pressing the STEP Keyswitch while the program is running causes the program execution to stop. The displays at this point show the operation code fetch cycle of the last instruction executed, with the address, op-code (data) and control signals visible. When the Diagnostic Emulator stops executing the target program, the following events take place:

- 1. The processor stops executing the target program.

- 2. The processor registers are saved in internal scratch pad memory and are accessible for display or alteration.

The operator, in effect, freezes the target program execution at the point reached when STEP was depressed. The operator then has several options:

- 1. Continue executing the program at full speed by pressing RUN.

- 2. Continue executing the program one instruction at a time by pressing STEP for each additional instruction execution.

- 3. Examine or change the contents of any of the processor registers.

- 4. Examine any memory or I/O address, and if the location is writable, store new data in it.

- 5. Review the last 251 bus cycles performed by the processor by decrementing through the Trace Memory.

The state of the target program is not changed by any of these operations (except as purposely altered by the operator) and program execution may be continued from the point where it stopped.

The program may be executed one instruction at a time by pressing STEP once for each instruction. If STEP is pressed and held down, the Diagnostic Emulator begins stepping at about seven instructions per second. The step rate then accelerates gradually from 7 steps per second to about 50 steps per second. Execution stops again if the keyswitch is released.

Table 4-1.1. Display Panel Indicators

### **FAULT GROUP**

ILLUMINATES IF:

CLK Target system clock not operating.

Target system clock is low in frequency.

EM-188 not connected to target system.

RESET Processor and Diagnostic Emulator held in Reset by a low on the RESET IN terminal

of the microprocessor socket.

### MACHINE CYCLE GROUP

ILLUMINATES IF:

FETCH Displayed machine cycle is an op-code fetch cycle.

BK A Breakpoint A. Conditions set up for an output from Breakpoint A Comparator were

satisfied during the displayed machine cycle.

BK B Breakpoint B. Conditions set up for an output from the Breakpoint B Comparator

were satisfied during the displayed machine cycle.

EXT External. External Breakpoint input low (active) during displayed machine cycle.

I/O Input/Output. Machine cycle being displayed is a data transfer from an input port

address or to an output port address.

IACK Interrupt Acknowledge. Machine cycle being displayed is an interrupt acknowledge

cycle.

RD Read. Machine cycle being displayed is read from memory or read from I/O cycle.

WR Write. Machine cycle being displayed is a write to memory or write to I/O cycle.

### **FLAGS**

ILLUMINATES IF:

S Sign bit is true.

Z Zero bit is true.

AC Auxiliary Carry bit is true.

P Parity bit is true.

CY Carry bit is true.

### **CPU STATUS**

ILLUMINATES IF:

IENA Emulated processor is ready to respond to an interrupt. (Interrupts enabled)

INT Interrupt. One of the following inputs to 8085 is active: INTR (PIN 10); RST 5.5 (PIN 0); RST 5.5 (PIN 7); For the 2000 of the INTR (PIN 14) is a state of the following inputs to 8085 is active: INTR (PIN 14); RST 5.5 (PIN 7); RST 5.5 (PIN

9); RST 6.5 (PIN 8); RST 7.5 (PIN 7). For the 8080, the INT (PIN 14) input is active.

Trap TRAP (PIN 6) input to 8085 is active. Not applicable to 8080.

Hold HOLD input of the 8085 or 8080 active.

Wait READY input to 8085 (PIN 35) or 8080 (PIN 23) is not active. CPU is waiting. If the CPU is working with a system that requires some wait states, the indicator may

be more or less dimly lit.

Halt Processor has executed a HALT instruction and has entered the HALT state.

Pause Real-time emulation of the target program is suspended and the Diagnostic Emulator is

awaiting another command.

BKPT Breakpoint Enable. Illuminates if the RUN BKPT keyswitch is depressed.

**ENA**

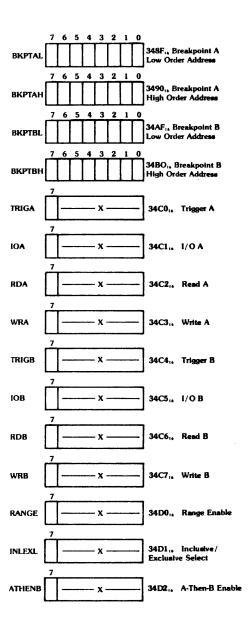

### 4-1.4 Breakpoint System

The Diagnostic Emulator incorporates a Regional/Relational breakpoint generation system to enable the user to monitor the operation of his program and to stop execution of his program when desired. The EM-188 contains two independent address comparators. Each of these comparators continuously monitors the 16-bit address bus of the microprocessor. In addition, each comparator may be qualified to respond to read cycles only, to write cycles only, or to both read and write cycles. The comparators may also be configured to respond to memory addresses or to I/O port addresses.

It is also possible to configure the breakpoint system so that a specified relationship must hold between the A and B breakpoint comparators before PAUSE occurs. The relationships that may be specified are the following:

| 1. | A then B. | Break if condition A is found followed some time |

|----|-----------|--------------------------------------------------|

|    |           | later by condition B.                            |

Break if any address outside of the range from A to B is found. (Including addresses A and B.)

Table 4-1.2. Breakpoint Qualifiers

| () · Disable          | 5 - I/O Read             |  |

|-----------------------|--------------------------|--|

| 1 - Memory Read       | 6 - I/O Write            |  |

| 2 - Memory Write      | 7 - I/O Read/Write       |  |

| 3 - Memory Read/Write | 8 - Range A to B         |  |

| 4 - A then B          | 9 - Range outside A to B |  |

|                       |                          |  |

The various breakpoint qualifiers and relationships are set up by simple keystroke sequences. Some examples of these sequences follow.

### **EXAMPLE:**

3.

Set up breakpoint comparator A to respond to read or write cycles at address 4300<sub>16</sub>; disable comparator B.

### **KEYSTROKE SEQUENCE:**

Set breakpoint address.

Set qualifier 3 (memory R/W).

Press and hold down BKPT A Key while qualifier is entered.

Set qualifier 0 (Disable).

Press and hold down BKPT B Key while qualifier is entered.

### **EXAMPLE:**

Set up breakpoint comparator A to respond to read cycles only at memory address 8A72<sub>16</sub>, and breakpoint comparator B to respond to write cycles to I/O port 13<sub>16</sub>.

**KEYSTROKE SEQUENCE:**

Set A breakpoint address.

SKPT 1

Set A qualifier to 1 (MEMORY read).

Press and hold down BKPT A Key while qualifier is entered.

Set B breakpoint address.

Set B qualifier to 6 (I/O WRITE).

Press and hold down BKPT B Key while qualifier is entered.

When the breakpoint circuitry is set up as desired, program execution may be started using RUN BKPT. The function RUN BKPT is the same as the function of RUN except that when the breakpoint condition occurs, program execution stops.

### **EXAMPLE:**

Set up breakpoint range from 4307<sub>16</sub> to FFFF<sub>16</sub>.

KEYSTROKE SEQUENCE:

BKPT 4 3 0 7

Set A to range beginning (4307<sub>16</sub>).

HKPT &

Set A qualifier to 8 (Range A to B).

Press and hold down BKPT A Key while qualifer is entered.

Set B to range end (FFFF<sub>16</sub>).

Note that the qualifier for B is automatically set to eight when the range qualifier was selected for A, since both breakpoint qualifiers are affected when selecting A then B or RANGE qualifiers.

### 4-1.5 TRACE MEMORY

One of the most useful EM-188 features is its 251 bus cycle Trace Memory. The Trace Memory is organized as a ring buffer that records all target program activity. It operates in both real-time and single-step modes, and its contents remain in the correct sequence, regardless of whether the user operates the program wholly or partly in either of these two modes.

To review the Trace Memory contents, the EM-188 must be paused. The PAUSE mode is entered automatically when the program encounters a breakpoint, or it can be entered manually by depressing STEP. When the program enters PAUSE, the Display shows the fetch cycle address and data for the last instruction recorded.

When a breakpoint event triggers PAUSE, the Display shows the cycle where the breakpoint was detected, and the user can easily review the program activities leading up to the event. Depressing DEC allows the user to examine the last 251 bus cycles of program activity prior to the breakpoint. Depressing INC allows the user to review forward up to the last cycle traced. Depressing STEP advances the target program past the breakpoint event, one instruction at a time. Depressing TRACE allows the user to return to Trace Memory again after selecting another mode (i.e., MEM ADDR, I/O ADDR, etc.) and return the original program event or bus cycle to the display. The TRACE Key has no effect unless the program is already in PAUSE. STEP actually causes the emulator to execute another program instruction and this instruction is entered into the Trace Memory like all others.

The 8085/8080 machine instructions may have one or several bus cycles per instruction. The following two examples illustrate displayed Trace Memory contents, first after executing a simple instruction and then after a more complex one.

### EXAMPLE 1 MOV B, C

| Cycle | Addr | Data | Fetch | RD | WR |

|-------|------|------|-------|----|----|

| 1     | 4000 | 41   | •     | •  |    |

Single bus cycle instruction: Move contents of C register to B register. Assume the instruction location is address  $4000_{16}$  in the target memory. The Trace Memory records a bus cycle with the address of  $4000_{16}$ , data of  $41_{16}$  and control bits indicating that it is a fetch operation and a read cycle.

### EXAMPLE 2 SHLD 7055H

| Cycle | Addr | Data       | Fetch | RD | WR |

|-------|------|------------|-------|----|----|

| 1     | 4000 | 22         | •     | •  |    |

| 2     | 4001 | <b>5</b> 5 |       | •  |    |

| 3     | 4002 | 70         |       | •  |    |

| 4     | 7055 | 34         |       |    | •  |

| 5     | 7056 | 12         |       |    | •  |

Five bus cycle instruction: Cycle one fetches op-code 22 of the SHLD instruction located at address 4000<sub>16</sub>. Cycles two and three read low order and high order bytes (55<sub>16</sub> and 70<sub>16</sub>) of the 16-bit address located at 4001<sub>16</sub> and 4002<sub>16</sub>. Cycles four and five write the contents of the HL register pair (34<sub>16</sub> and 12<sub>16</sub>). The Trace Memory records all five bus cycles of the instruction. The address location, program data and cycle type are shown on the Display Panel for each bus cycle of the instruction. If the EM-188 had entered PAUSE and displayed Cycle 1 (the OP-CODE fetch), then the INC Key would be used to advance through the Trace Memory and observe the subsequent bus cycles.

# 4-2 EXAMINATION AND ALTERATION OF CPU REGISTERS

The 8085 and 8080 register contents may be examined by the operator, and if desired, overwritten with new data.

Register data is accessed for display by using the blue REG Keyswitch, followed by one of the hexadecimal keyswitches. This designates which register should be displayed. Table 4-2.1 shows the registers selected by the various keyswitches. Note that 4 through 7 do not correspond to actual 8085 or 8080 registers. These keyswitches are used to set up parameters for the Built-In test routines or User Code Functions. These Code Functions are described in later sections. (See Section 7 and Section 8).

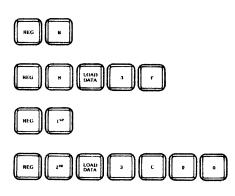

Examples of readout and alteration of CPU registers:

### **EXAMPLE:**

B register contents displayed on data display.

B register is accessed and then overwritten with data  $3F_{16}$ .

Stack Pointer is accessed and displayed on 16-bit address display.

HL Register Pair is accessed, and then the contents are overwritten with  $3C00_{16}$ .

Table 4-2.1. Keyboard Designators

| KEY | REGISTER               | DESCRIPTION                               |

|-----|------------------------|-------------------------------------------|

| 0   | PC                     | Program Counter                           |

| 1   | SP                     | Stack Pointer                             |

| 2   | HL                     | HL Register Pair                          |

| 3   | DE                     | DE Register Pair                          |

| 4   | * BEG                  | BEGIN Address (for programmed tests)      |

| 5   | • END                  | END Address (for programmed tests)        |

| 6   | <ul><li>ADDR</li></ul> | Address (programmed test parameter)       |

| 7   | * DATA                 | Data (programmed test parameter)          |

| 8   | · · RIM                | Current Status of Interrupt Mask Register |

| 9   | · · SIM                | Data to load to Interrupt Mask Register   |

| Α   | Α                      | Accumulator                               |

| В   | В                      | B Register                                |

| С   | С                      | C Register                                |

| D   | D                      | D Register                                |

| Ε   | Е                      | E Register                                |

| F   | F                      | Condition Flags                           |

<sup>•</sup> Not an actual 8080 or 8085 register.

Not used for 8080 emulation.

### **EXAMPLE:**

SIM Register is accessed and then overwritten with data  $C0_{16}$ .

# 4-3 EXAMINATION AND ALTERATION OF MEMORY LOCATIONS

Any memory location accessible to the emulated microprocessor may be accessed and displayed by the EM-188. If desired, new data may be written to the location.

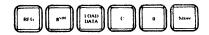

### **EXAMPLE:**

Address  $431A_{16}$  is entered, and when EXAM is pressed, the EM-188 will read from address  $431A_{16}$  and display the data obtained.

If the operator wishes to review a group of sequential memory locations, this may be done by entering the initial address and examining that location as above; then examine successive locations by depressing INC.

### **EXAMPLE:**

Examine data at 4300<sub>16</sub>.

Examine data at 4301<sub>16</sub>

etc.

Examine data at successive locations, etc.

A memory location may be altered by entering an address, as shown above, then entering data using LOAD DATA and finally storing the data to the selected memory address using STORE.

### **EXAMPLE:**

The above sequence writes the data  $55_{16}$  to memory address  $13FE_{16}$  in the target system.

Sequential locations may be quickly altered by incrementing the address after each data entry operation. For example, the following keystroke sequence enters a short program fragment into memory:

### **EXAMPLE:**

Enter initial address 080016.

Enter data  $C3_{16}$  then store the data to  $0800_{16}$  and increment to  $0801_{16}$ .

Enter data  $00_{16}$  then store the data to  $0801_{16}$  and increment to  $0802_{16}$ .

Enter data  $08_{16}$  and store to  $0802_{16}$ ; increment to  $0803_{16}$ , etc.

The EM-188 does not require redundant keystrokes. The unit assumes that if the operator has entered new data while a particular memory address is accessed, then the operator wants to store that data before going to the next address.

In all of the above examples in which INC was used, DEC (decrement) could also have been used.

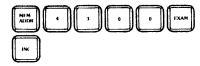

# 4-4 EXAMINATION AND ALTERATION OF I/O PORTS

Input/Output ports of the 8085 or 8080 may be accessed and displayed in a parallel manner to that described for memory addresses, with two differences. The first is that the I/O ports respond to an eight-bit address and consequently only eight-bit addresses need be entered. The second difference is that the INC and DEC keyswitches do not perform an automatic read of the next (or previous) I/O port address. The intent of this characteristic is to help the operator avoid unintended reading of an I/O port, since this sometimes results in a change of state of complex I/O devices. For example, a communications interface circuit such as the Intel 8251 will clear the DATA PRESENT status bit when the receive data register is read. The following is a keystroke sequence that may be used to examine data at an input port:

### **EXAMPLE:**

Read and display data at Input Port 3.

Data A0<sub>16</sub> is written to Output Port 1B<sub>16</sub>. (No READ cycle was performed at Port 1B.)

# SECTION 5

## **RAM OVERLAY**

- 5-1 Overview

- 5-2 Controls

### 5-1 OVERVIEW

The EM-188 may be configured with an optional RAM Overlay feature. The RAM Overlay consists of a circuit board with 8K bytes of 200 nSEC static memory along with appropriate addressing and control logic.

The 8K bytes of memory is divided into two independent 4K byte blocks. Each block has independent addressing and control circuitry and may be enabled as read-write memory, as read-only memory or disabled. Controls for the two memory blocks are located on the back panel of the Operator's Station.

If the RAM Overlay is set up to respond to a range of addresses, say 0000<sub>16</sub> to 0FFF<sub>16</sub>, then target system memory in the same address range becomes inaccessible to the emulation processor. The memory block has "overlayed" the corresponding target system addresses. (See, however, the description of Code Function C5 for an exception to this characteristic of the EM-188.)

The contents of the RAM Overlay is retained as long as power is applied to the EM- 188. It is possible to load the RAM Overlay with data, then switch the enable switches to the OFF Position, then at some later time, switch the enable switches to READ or RD/WR and use the data.

### 5-2 CONTROLS

Figure 5-2.1. RAM Overlay Controls.

Each 4K byte block of memory has an associated Address Range switch and Enable switch. See Figure 5-2.1.

The Enable switches are three-position toggle switches that place the memory bank into one of three conditions:

### 1. Off

The memory bank is disabled and is effectively removed from the system.

### 2. Read

The memory bank is placed in a Read-Only configuration so that from the point of view of the target system the memory bank behaves like Read-Only-Memory. In this mode, it is not possible for the target system program to alter the contents of the memory. Note, however, that the EM-188 is still able to write to the memory bank from the Keyboard or from a Code Function routine such as Code Function C3 (download).

### 3. Read/Write

The memory bank is placed in a Read/Write configuration. Both the target system and the EM-188 are able to read the memory and write new information to it.

If a memory bank is disabled (toggle switch in the OFF position), the memory will nevertheless continue to retain data. The data will reappear in the target address space whenever the memory is again enabled.

The Address Range switches are 16-position rotary switches used to select the address range where the 4K memory blocks will reside in the target address space. Each of the 4K memory blocks can be moved to any of 16 positions, beginning at a 4K boundary. See Table 5-2.1.

Table 5-2.1. Memory Block Address -- A and B

| SWITCH POSITION | MEMORY BLOCK<br>ADDRESS                 | SWITCH POSITION | MEMORY BLOCK<br>ADDRESS                 |

|-----------------|-----------------------------------------|-----------------|-----------------------------------------|

| 0 .             | 0000 <sub>16</sub> - 0FFF <sub>16</sub> | 8               | 8000 <sub>16</sub> - 8FFF <sub>16</sub> |

| 1               | 1000 <sub>16</sub> - 1FFF <sub>16</sub> | 9               | 9000 <sub>16</sub> - 9FFF <sub>16</sub> |

| 2               | 2000 <sub>16</sub> - 2FFF <sub>16</sub> | Α               | A000 <sub>16</sub> - AFFF <sub>16</sub> |

| 3               | 3000 <sub>16</sub> - 3FFF <sub>16</sub> | В               | B000 <sub>16</sub> - BFFF <sub>16</sub> |

| 4               | 4000 <sub>16</sub> - 4FFF <sub>16</sub> | С               | C000 <sub>16</sub> - CFFF <sub>16</sub> |

| 5               | 5000 <sub>16</sub> - 5FFF <sub>16</sub> | D               | D000 <sub>16</sub> - DFFF <sub>16</sub> |

| 6               | 6000 <sub>16</sub> - 6FFF <sub>16</sub> | E               | E000 <sub>16</sub> - EFFF <sub>16</sub> |

| . 7             | 7000 <sub>16</sub> - 7FFF <sub>16</sub> | F               | F000 <sub>16</sub> - FFFF <sub>16</sub> |

# SECIION (E

## **DISASSEMBLY**

- 6-1 Overview

- **6-2** Format Definition

### 6-1 OVERVIEW

The EM-188 Diagnostic Emulator may be configured with an enhanced firmware package that includes a disassembler. The disassembler firmware gives the EM-188 the ability to output the contents of the Trace Memory and emulation processor registers to the serial port; in this way a readable and attractive display may be created on a CRT or hardcopy terminal.

The disassembly firmware is disabled when the EM-188 is first powered up and must be enabled before use. The following procedure will make the EM-188 ready to operate with an ASCII terminal and disassembly firmware:

# 6-1.1 OPERATION PREPARATION PROCEDURES

Connect the terminal to the EM-188 using an appropriate cable. The minimum circuits that must be connected are:

Pin 1 - Frame Ground

Pin 2 - Serial Data Out

Pin 7 - Ground

Some RS-232 terminals may also require the following connection:

Pin 20 - Data Terminal Ready

Take care that Pins 10, 11, 12, 13, 22, 23, 24 and 25 are not connected to incompatible circuits. See 9-1, Auxiliary Connector.

- 2. Set the Baud Rate Selector switches of the EM-188 and the terminal to compatible settings.

- 3. Check the setting of Option Switch 3. If Option Switch 3 is open (up), then the EM-188 will not output serial data unless the Clear-to-Send signal (Pin 5) is high. If the Clear-to-Send signal is not important in your application, set Option Switch 3 to the CLOSED (down) position and the EM-188 will output data on command regardless of the state of Pin 5.

- 4. Enable the disassembly firmware by executing the Code Function E1. The EM-188 is now ready to output lines of up to 72 characters to the terminal device. Since 72 characters is not a long enough line to include the interrupt mask register display, this register will not appear.

- 5. If the ASCII terminal is capable of displaying lines of 80 characters or longer, enable the display of 80 character lines by executing Code Function E3.

The disassembly firmware may be turned off by executing Code Function E0. The 80-character line may be turned off by executing Code Function E2.

Operate the EM-188 in the normal manner. Any time that the EM-188 transfers from RUN to PAUSE, the disassembly firmware will format and dump a part of the contents of the Trace Memory to the terminal; normally 24 lines of output are produced. The last line output represents the last instruction executed and the firmware will then output the register display.

If the EM-188 is operated in single-step mode, the firmware will be able to output the register display after every instruction.

### 6-2 FORMAT DEFINITION

Figure 6-2.1 shows some lines from a printer connected to our EM-188. The program was executed in single-step mode; as a consequence, a register display is obtained after each instruction execution. The various fields of the disassembly presentation are identified in the figure. All numbers that are output by the disassembler are in hexadecimal representation. Additional information about the fields of the display follows:

### Address

The address of the op-code byte of the instruction.

### **Op-Code**

The operation code of the instruction.

### Operand

The operand bytes of the instruction (if any).

### **Op-Code Mnemonic**

The operation code of the instruction given in mnemonic form.

### **Operand**

The operand field of the instruction in symbolic format, except that addresses and constants are given as hexadecimal numbers.

### **Data Transfer**

Any data transfer operations that occur as a consequence of the instruction are shown here. The most common formats are:

The first format means that the processor wrote data 'DD' to address 'AAAA'. The second format means that the processor read data 'DD' from address 'AAAA'. The other formats are associated with I/O instructions and take the form:

$$-PP > DD$$

or

$$-PP < DD$$

The first of these formats means that the processor wrote data 'DD' to output port 'PP'. The second format means that the processor read data 'DD' from input port 'PP'.

### **Data Transfer**

Some instructions transfer more than one byte of data. The second byte of a data transfer will be shown in this field. If there are more than two bytes transferred, the additional bytes are shown in fields 6 and 7 on the following line. See, for example, the XTHL instruction which reads two bytes from the top of stack and then writes two other bytes to the top of stack. All of these transfers are easily seen from the display.

### **Breakpoint**

If a breakpoint occurred during the execution of the instruction on this line, it will be identified in this column. If the Breakpoint A conditions were satisfied, an 'A' will appear in this column. If the Breakpoint B conditions were satisfied, a 'B' will appear in this column. If both the A and B conditions are satisfied during the execution of the same instruction, the 'B' will take precedence and be displayed.

### Flag Register

The CPU flag register (condition code register) is shown in this field. Each of the five characters in this field represent one of the condition code bits as follows:

First - 'S' if sign bit is true. Second - 'Z' if zero bit is true.

Third - 'A' if auxiliary carry bit is true.

Fourth - 'P' if parity bit is true.

Fifth - 'C' if carry bit is true.

If any of the condition code bits are not true, the letter is replaced by a period.

### Accumulator

The content of the accumulator after the execution of the instruction.

### **BC** Register Pair

The content of the BC register pair following the execution of the instruction.

### **DE Register Pair**

The content of the DE register pair following the execution of the instruction.

### **HL Register Pair**

The content of the HL register pair following the execution of the instruction.

### Stack Pointer

The content of the stack pointer following the execution of the instruction.

### **Interrupt Mask**

The content of the interrupt mask register following the execution of the instruction.

Figure 6-2.1 Disassembly format.

| INTERRUPT  MASK REGISTER | 1                                                                                                                                                                                                                                                            |           |      |              |                                                                                                                                                                                                     |            |        |          |       |               |       |           |           |           |                                         |       |       |                |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|----------|-------|---------------|-------|-----------|-----------|-----------|-----------------------------------------|-------|-------|----------------|

| STACK<br>— POINTER       | 30EB                                                                                                                                                                                                                                                         | 30EB      | 30EB | 30EB         | 30EB                                                                                                                                                                                                | 30EB       | 30EB   | 30FB     | 30EB  | 30EB          | SOEB  | 30EB      | 30EB      | 30EB      | 30E9                                    | 3089  | 30E.9 | 3089           |

| нг <b>к</b> есіѕтек<br>— | 0000                                                                                                                                                                                                                                                         | 0000      | 0000 | 309F         | 309F                                                                                                                                                                                                | 3008       | 309F   | 309F     | 309F  | 309F          | 309F  | 309F      | 309F      | 309F      | 309F                                    | 309F  | 309F  | 309F           |

| DE REGISTER              | 621m                                                                                                                                                                                                                                                         | 6200      | 62mn | 62100        | 10000                                                                                                                                                                                               | 62000      | 621111 | 6200     | 6200  | 6200          | 62100 | 6200      | 8000      | 6000      | 6000                                    | 6000  | 60100 | 4011JJ         |

| BC REGISTER              | 0000                                                                                                                                                                                                                                                         | 0000      | 0000 | 0000         | 0000                                                                                                                                                                                                | 0000       | 0000   | 0000     | 0000  | 0000          | 0000  | 0000      | 0000      | 0000      | 0000                                    | 0300  | 0300  | 0305           |

| ACCUMULATOR —            | 1:1                                                                                                                                                                                                                                                          | 40        | ्र   | 40           | 1                                                                                                                                                                                                   | <u>+</u>   | 1      | <u>:</u> |       | <del></del> - |       | 79        | 16        | 30        | 03                                      | 0.3   | 0.3   | $\mathbb{S}_0$ |

| н∧с<br>Твесізтев         | 1.7.Y.                                                                                                                                                                                                                                                       | * * Å * * | À    | A            | ÷ ₩•;                                                                                                                                                                                               | S, AP,     | S.AF.  | S.AP.    | S.AP. | S.AP.         | A     | * * M * * | * * W * * | * • A • • | * • A • •                               | , . A | 3(    | 3 + + + 6      |

| BREAKPOINT               | 1                                                                                                                                                                                                                                                            |           |      |              |                                                                                                                                                                                                     |            |        |          |       |               |       |           |           |           |                                         |       |       |                |

| DATA<br>TRANSFER         |                                                                                                                                                                                                                                                              |           |      |              |                                                                                                                                                                                                     |            |        |          |       |               |       |           |           |           | 30E9>A7                                 |       |       |                |

| ataci<br>Afirmant        | 3400 <ff< th=""><th></th><th></th><th></th><th>309F<ff< th=""><th></th><th></th><th>309F&gt;40</th><th>36&lt;17</th><th>3080&gt;17</th><th></th><th>3084&gt;16</th><th></th><th>8098408</th><th>30E.A&gt;00</th><th></th><th></th><th></th></ff<></th></ff<> |           |      |              | 309F <ff< th=""><th></th><th></th><th>309F&gt;40</th><th>36&lt;17</th><th>3080&gt;17</th><th></th><th>3084&gt;16</th><th></th><th>8098408</th><th>30E.A&gt;00</th><th></th><th></th><th></th></ff<> |            |        | 309F>40  | 36<17 | 3080>17       |       | 3084>16   |           | 8098408   | 30E.A>00                                |       |       |                |

| OPERAND                  | 3400                                                                                                                                                                                                                                                         | 40        | 0080 | H, 309F      | A,M                                                                                                                                                                                                 | ₹          | 1600   | M + 40   | 36    | 3080          | ₩.    | 308A      | 0940      | 3095      | 02E4                                    | B,A   | 80    | C+05           |

| WAEWOAIC OF-CODE         | L Jin                                                                                                                                                                                                                                                        | ANI       | SNS. | LXI          | AOM                                                                                                                                                                                                 | AKA        | ₹,     | MUI      | Z.    | S:            | NCR   | SIA       | MUI       | L.JJ.A    | CAL L                                   | AUM.  | CFI   | MOI            |

| OPERAND                  | 0034                                                                                                                                                                                                                                                         | 40        | 0038 | 9F30         |                                                                                                                                                                                                     |            | 9F.00  | 40       | 36    | 80.30         |       | 8430      | 09        | 9530      | E402                                    |       | 80    | 0.5            |

| OP-CODE                  | ₩<br>24                                                                                                                                                                                                                                                      | Εę        | S    | <del>F</del> | <b>7E</b>                                                                                                                                                                                           | <b>/</b> W | S.     | 36       | Ĭ     | 32            | 310   | 32        | 16        | Ø₽        | ======================================= | 47    | F     | OF.            |

| VDDKE28                  | 0053                                                                                                                                                                                                                                                         | 0056      | 0058 | 0080         | 008F                                                                                                                                                                                                | 0600       | 0091   | 0094     | 9600  | 8600          | 0098  | 0090      | 3600      | 00A1      | 00A4                                    | 02E4  | 02E5  | 02E7           |

# SECIION Z

### **BUILT-IN DIAGNOSTIC FUNCTIONS**

- 7-1 Group A: Memory Tests

- 7-2 Group B: Oscilloscope Loops

- 7-3 Group C: Memory Load and Dump

- 7-4 Group D: Miscellaneous

- 7-5 Group E: Change Default Parameters

- 7-6 Group F: Internal Operations

The Diagnostic Emulator contains Built-In test functions and utility routines designed to be convenient and useful for testing systems and verifying their proper operation. These test and utility routines have been named Code Functions because they are accessed by depressing the CODE keyswitch, followed by hexadecimal digits designating the routine desired. Table 7-1 lists all of the Code Functions programmed into the Diagnostic Emulator.

# 7-1 GROUP A: MEMORY TESTS

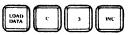

### CODE A1 - 00/FF DATA TEST

The Code Function A1 memory test routine quickly determines whether all locations within a specified range can be set to  $00_{16}$  and  $FF_{16}$ . The range tested is from the address specified by the BEG (begin) register through the address specified by the END register. The routine operates by setting the first location of the range to  $00_{16}$  and reading the location to see if a  $00_{16}$  is returned. Then the routine stores an  $FF_{16}$  to this location and reads the location to see if an  $FF_{16}$  is returned. Finally, the routine increments the address and tests the next location in the range. When all locations in the range have been tested, the EM-188 will emit a short beep and the test will repeat. During the execution of this test, the address and data activity are visible on the displays and stored in the Trace Memory.

If a memory error is encountered, the routine emits 3 beeps and displays the address of the failure and the erroneous data read. At this time the operator has three options:

- 1. Depress EXAM to display the data the routine expected to read from the memory. Relese the keyswitch to again display the bad data.

- Depress INC to continue testing at the next address in the range. If additional problems are found, the program will stop again and any of the options listed may be taken.

- 3. Exit the test routine by using any of the mode keys (MEM, I/O, REG, RUN, etc.) or RESET.

After testing all locations in the specified range, the EM-188 emits one short beep and repeats the test. The RESET keyswitch is used to terminate the test at any time.

# SECTION 7 BUILT-IN DIAGNOSTIC FUNCTIONS

| Table 7-1. Code Functions | GROU       | GROUP A: MEMORY TESTS                                              |                            |                   |  |  |  |

|---------------------------|------------|--------------------------------------------------------------------|----------------------------|-------------------|--|--|--|

|                           | A1         | RAM TEST                                                           | (00/FF)                    |                   |  |  |  |

|                           | A2         | RAM TEST                                                           | (Rotating 1s)              | D T t             |  |  |  |

|                           | A3         | RAM TEST                                                           | (Addresses)                | Repeating Tests   |  |  |  |

|                           | A4         | ALL RAM TESTS                                                      | )                          |                   |  |  |  |

|                           | <b>A</b> 5 | ALL RAM TESTS                                                      | •                          |                   |  |  |  |

|                           | A6         | RAM TEST                                                           | (00/FF)                    |                   |  |  |  |

|                           | A7         | RAM TEST                                                           | (Rotating 1's)             | One Pass and Stop |  |  |  |

|                           | A8         | RAM TEST                                                           | (Addresses)                |                   |  |  |  |

|                           | GROU       | P B: OSCILLOSCOPE LOOPS                                            |                            |                   |  |  |  |

|                           | B1         | Repetitive Memory Read                                             |                            |                   |  |  |  |

|                           | B2         | Repetitive Memory Write                                            |                            |                   |  |  |  |

|                           | B3         | Repetitive I/O Read                                                |                            |                   |  |  |  |

|                           | B4         | Repetitive I/O Write                                               |                            |                   |  |  |  |

|                           | B5         | Continuous Address Increment                                       |                            |                   |  |  |  |

|                           | B6         | Repetitive Memory Write ( Dat                                      |                            |                   |  |  |  |

|                           | B7         | Repetitive I/O Write ( Data / I                                    | Data )                     |                   |  |  |  |

|                           | B8         | Toggle SOD Line (8085 only)                                        |                            |                   |  |  |  |

|                           | GROUI      | P C: MEMORY LOAD AND DUI                                           | MP                         |                   |  |  |  |

| •                         | C1         | Load Target from Front Panel                                       | PROM                       |                   |  |  |  |

|                           | C2         | Verify Target with Front Panel                                     | PROM                       |                   |  |  |  |

|                           | C3         | Load Target from Serial Link (                                     |                            |                   |  |  |  |

|                           | C4         | Dump Target to Serial Link (U                                      |                            |                   |  |  |  |

|                           | C5         | Load RAM Overlay from Targe                                        |                            |                   |  |  |  |

|                           | C6         | Verify RAM Overlay with Target                                     |                            |                   |  |  |  |

|                           | C7         | Verify Target Against Serial Lir                                   | nk                         |                   |  |  |  |

| ,                         | C8<br>C9   | Fill Target with Specified Data<br>Verify Target with Specified Da | .ta                        |                   |  |  |  |

|                           |            |                                                                    | i da                       |                   |  |  |  |

|                           |            | P D: MISCELLANEOUS                                                 |                            |                   |  |  |  |

|                           | D0<br>D1   | Clear Interrupt Enable Flip-Flop                                   | )                          |                   |  |  |  |

|                           | D2         | Set Interrupt Enable Flip-Flop                                     |                            |                   |  |  |  |

|                           | D3         | Display Clock Frequency Display PROM/ROM Signature                 |                            |                   |  |  |  |

|                           | D3         | Output 50 Nulls from Serial Lin                                    |                            |                   |  |  |  |

|                           | D5         | Call User Routine in Internal R                                    |                            |                   |  |  |  |

|                           | D6         | Call User Routine in Internal R.                                   | MM at 2000 <sub>16</sub>   |                   |  |  |  |

|                           | D7         | Clear Trace Memory                                                 | MIVI at 3003 <sub>16</sub> |                   |  |  |  |

|                           | D8         | Call Remote Control Software                                       |                            |                   |  |  |  |

|                           | D9         | Halt CPU (for changing Front F                                     | Panel PROM)                |                   |  |  |  |

|                           | GROUI      | P E: CHANGE DEFAULT PARA                                           | METERS                     |                   |  |  |  |

|                           | EO         | Disable Disassembly (Default)                                      |                            |                   |  |  |  |

|                           | E1         | Enable Disassembly                                                 |                            |                   |  |  |  |

|                           | E2         | Output 72 Character Lines (De                                      | fault)                     |                   |  |  |  |

|                           | F3         | Output 80 Character Lines                                          |                            |                   |  |  |  |

**GROUP F:**

ЕЗ

Set "Introspection" Mode (for self testing)

Output 80 Character Lines

### **CODE A2 - ROTATE 1s**

Code Function A2 memory test routine performs a test on all data bits in the range specified. The range tested is from the address contained in the BEG register through the address contained in the END register. The routine starts with the first location in the range and tests the location by writing and checking a bit, one bit at a time, in all of the positions of the word under test. The routine writes and checks by writing and reading the following data patterns:

| Bii | Binary Pattern |   |   |   |   |   |   | Hexadecimal |

|-----|----------------|---|---|---|---|---|---|-------------|

| 0   | 0              | 0 | 0 | 0 | 0 | 0 | 1 | 01,6        |

| 0   | 0              | 0 | 0 | 0 | 0 | 1 | 0 | 02,6        |

| 0   | 0              | 0 | 0 | 0 | 1 | 0 | 0 | 04,6        |

| 0   | 0              | 0 | 0 | 1 | 0 | 0 | 0 | 0816        |

| 0   | 0              | 0 | 1 | 0 | 0 | 0 | 0 | 10,6        |

| 0   | 0              | 1 | 0 | 0 | 0 | 0 | 0 | 20,6        |

| 0   | 1              | 0 | 0 | 0 | 0 | 0 | 0 | 40,6        |

| 1   | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 8016        |

|     |                |   |   |   |   |   |   |             |

After a location has been tested it is known that all bit positions in the location may be set and cleared independently of each other. The program then increments to the next sequential address in the range and proceeds to test in the same manner. If an error is detected, the test stops, the EM-188 emits the three beeps that signify an error, and the Display Panel shows the defective memory address and the bad data. At this point the operator has three options:

- 1. Depress EXAM to display the data the diagnostic routine expected to read (good data). Release EXAM to return the bad data to the display.

- 2. Depress INC to continue testing. If additional problems are found, the test stops and any of the options listed may be taken again.

- 3. To terminate the test, depress RESET, RUN, or any of the mode select keyswitches.

After testing all locations in the specified range, the EM-188 emits one short beep and repeats the test. The RESET keyswitch is used to terminate the test at any time.

38 AMC 9112 4-81

### **BUILT-IN DIAGNOSTIC FUNCTIONS**

### **CODE A3 - ADDRESS TEST**

Code Function A3 memory test determines whether an address decoding failure exists in the memory system under test. It tests the memory range from the address contained in the BEG register to the address contained in the END register. The routine prepares for operation by clearing all locations in the range to  $00_{16}$ . Next, the first location is set to  $FF_{16}$  and then a check is made of all address- related locations in the range to determine if any of them have been altered by the writing of the  $FF_{16}$ . After all locations in the range that are address-related to the first location have been checked, the program resets the first location to  $00_{16}$ . Then the next sequential location in the range is set to  $FF_{16}$ , and the address- related locations checked. The test proceeds until all locations in the specified range have been set to  $FF_{16}$ , and the respective address-related locations checked.

For the purposes of this test, an address is said to be related to a second address if it differs from it by only one bit (in any bit position). The test checks all possible address-related combinations as long as a generated address does not fall outside the specified range.

If an addressing error is found the test stops, the EM-188 emits three beeps signifying an error, and the display shows the erroneous data and its address. At this point the operator has three options:

- 1. Depress EXAM to display the data the diagnostic routine expected to read. Release EXAM to return the erroneous data back to display.

- 2. Depress INC to continue testing. If additional problems are found, the test will stop and any of the options listed may be taken again.

- 3. To terminate the test depress RESET, or RUN or any of the mode selection keyswitches.

After all locations in the specified range have been tested, the EM-188 emits one short beep and repeats the test. To exit this code function at any time, depress RESET.

### **CODE A4 - ALL TESTS AND REPEAT**

Code Function A4 executes the A1, A2, and A3 diagnostic functions in sequence, then emits a short beep and repeats. The test may be terminated by depressing RESET. In the event that an error is found, the operator may respond in any of the ways described for the individual diagnostic functions.

### **CODE A5 - ALL TESTS AND STOP**

Code Function A5 executes the A1, A2 and A3 diagnostic functions in sequence, emits a short beep and stops. In the event an error is found, the operator may respond in any of the ways described for the individual diagnostic functions. When the test is complete, the displays will read CODE A5 and the Trace Memory will contain a record of the last 251 bus transfers.

AMC 9112 9-81

### **CODE A6 - 00/FF DATA TEST**

Code Function A6 is identical to the Code Function A1 except the function stops after a single pass through the test. When the test is complete, the displays will read CODE A6 and the Trace Memory will contain a record of the last 251 bus transfers.

### **CODE A7 - ROTATE 1's**

Code Function A7 is identical to the Code Function A2 except that the function stops after a single pass through the test. When the test is complete, the displays will read CODE A7 and the Trace Memory will contain a record of the last 251 bus transfers.

### **CODE A8 - ADDRESS TEST**

Code Function A8 is identical to the Code Function A3 except the function stops after a single pass through the test. When the test is complete, the displays will read CODE A8 and the Trace Memory will contain a record of the last 251 bus transfers.

# 7-2 GROUP B: OSCILLOSCOPE LOOPS

The Oscilloscope Loop Functions are a group of functions that provide several types of repetitive stimuli to a target system. They provide repetitive waveforms in the target system hardware that may easily be examined at various circuit points with an oscilloscope or other test equipment. Some of the functions are also useful as stimulus routines for Signature Analysis testing.

NOTE: ADDR register referred to below is "Hex Keyswitch - #6."

### **CODE B1 - REPETITIVE MEMORY READ**

This function repetitively reads the single memory location addressed by the **ADDR register.** These address, data and RD signals are all shown on the Display. An EM- 188 configured for an 8085 processor reads the location about 30,000 times per second with a 5 MHz clock. Depress RESET to exit this function.

### **CODE B2 - REPETITIVE MEMORY WRITE**

This function repetitively writes the data contained in the DATA register to the single memory location addressed by the **ADDR register**. These address, data and WR signals are all shown on the Display. An EM-188 configured for an 8085 processor writes the data to the addressed location about 30,000 times per second with a 5 MHz clock. Depress RESET to exit this function.

### CODE B3 - REPETITIVE I/O READ

This function repetitively reads the single I/O port location addressed by the **ADDR register.** The address, data and RD signals are all shown on the display. An EM- 188 configured for an 8085 processor reads the location about 30,000 times per second with a 5 MHz clock. Depress RESET to exit this function.

### **CODE B4 - REPETITIVE I/O WRITE**

This function repetitively writes the data contained in the DATA register to the I/O location addressed by the **ADDR register**. These address, data and WR signals are all shown on the Display. An EM-188 configured for an 8085 processor writes the data to the addressed location about 30,000 times per second with a 5 MHz clock. Depress RESET to exit this function.

### **CODE B5 - CONTINUOUS ADDRESS INCREMENT**

This function places the EM-188 in a special mode in which it outputs successive addresses from  $0000_{16}$  to  $FFFF_{16}$  at a very high rate. Internal to the EM-188 this is accomplished by forcing a NOP instruction to the processor on every fetch cycle. Externally the EM-188 appears to be doing a fetch cycle at each address at the full speed of the processor (as determined by the clock frequency).

In this mode, the processor does **not** respond to target system WAIT commands.

The Continuous Address Increment function is used to check out address decoding networks in hardware systems and as a stimulus for signature analysis troubleshooting.

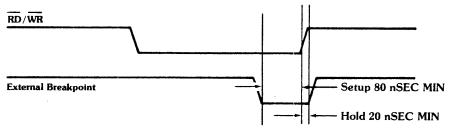

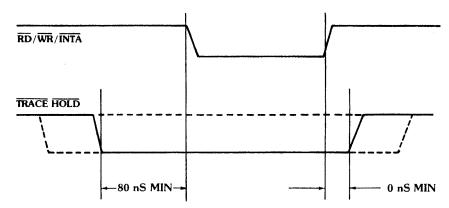

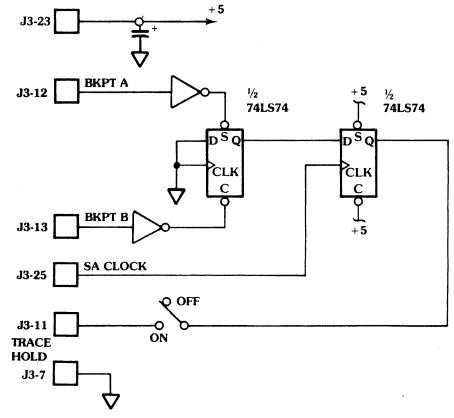

It is possible to obtain a sync pulse for triggering an oscilloscope or a signature analyzer from either the Breakpoint A or Breakpoint B output at the Auxiliary Connector; the output pulse occurs each time the processor reads from the breakpoint address. (The processor does not stop.)