# MODEL 810-D DIGITAL LOGIC RECORDER

# OPERATING AND SERVICE MANUAL

# OPERATING & SERVICE MANUAL

# MODEL 810-D

# Table of Contents

| Section |                     |                             |    |  |

|---------|---------------------|-----------------------------|----|--|

| I       | General Information |                             |    |  |

|         | 1.1 C               | ertification                | 1  |  |

|         | 1.2 W               | arranty                     | 1  |  |

|         | 1.3 I               | nstrument Description       | 1  |  |

|         | 1.4 P               | erformance Specifications   | 2  |  |

|         | Tnatol              | lation                      | 6  |  |

| II      | Installation        |                             |    |  |

|         | 2.1 I               | ntroduction                 | 6  |  |

|         | 2.2 U               | npacking and Inspection     | 6  |  |

|         | 2.3 S               | torage and Shipment         | 6  |  |

|         | 2.4 P               | ower Connections            | 6  |  |

|         | 2.5 P               | reparation for Use          | 7  |  |

|         | 2.6 I               | nitial Warm-up              | 7  |  |

|         |                     |                             |    |  |

| III     | Princi              | ples of Operation           | 8  |  |

|         | 3.1 Ba              | asic Functional Description | 8  |  |

|         | 3.2 Re              | ecording Considerations     | 11 |  |

# Section

| IV   | Oper        | Operation                             |    |

|------|-------------|---------------------------------------|----|

|      | 4.1         | Introduction                          | 12 |

|      | 4.2         | Front Panel Control and Connectors    | 12 |

|      | 4.3         | Rear Panel Controls and<br>Connectors | 17 |

|      | 4.4         | Setup Procedures                      | 18 |

|      | 4.5         | Operation Procedures                  | 21 |

| V    | Digi        | tal Interface                         | 23 |

|      | 5.1         | Introduction                          | 23 |

|      | 5.2         | Digital Output                        | 23 |

| VI   | <u>Cali</u> | bration Procedures                    | 27 |

|      | 6.1         | Calibration of Display Output         | 27 |

|      | 6.2         | Recalibration of Internal Circuits    | 27 |

| VII  | Tech        | nical Description                     | 28 |

|      | 7.1         | General Description                   | 28 |

|      | 7.2         | Circuit Details                       | 29 |

|      | 7.3         | Operating Modes                       | 45 |

| VIII | Main        | tenance Procedures                    | 51 |

|      | 8.1         | Maintenance                           | 51 |

|      | 8.2         | Trouble-Shooting Procedure            | 51 |

|      | 8.3         | Power Supply                          | 52 |

|      | 8.4         | Front Panel                           | 52 |

|      | 8.5         | Main PC Assembly                      | 53 |

| IX   | Sche        | matics and Assembly Drawings          | 54 |

|      | 9.0         | List of Drawings                      | 54 |

### SECTION I

### General Information

# 1.1 Certification

Biomation Corporation certifies that this instrument was thoroughly tested and inspected and found to meet its published specifications when it was shipped from the factory.

# 1.2 Warranty

All Biomation products are warranted against defects in materials and workmanship. This warranty applies for one year from the date of delivery, or, in the case of certain major components listed in the operating manual, for the specified period. We will repair or replace products which prove to be defective during the warranty period. No other warranty is expressed or implied. We are not liable for consequential damages.

### 1.3 Instrument Description

The 810-D Digital Logic Recorder is a new instrumentation tool for the design and repair of digital logic circuits. Complex logic timing relationships can be conveniently recorded, displayed, and analyzed. Eight channels of digital information can be recorded and monitored at rates up to 10MHz.

The Biomation Model 810-D is designed specifically for analysis of digital logic circuits and signals. The unit can be used on both synchronous and asynchronous signals and can detect random logic pulses as narrow as 10 nanoseconds with the use of the "LATCH" input feature.

The Model 810-D Digital Logic Recorder provides the ability to measure up to eight digital signals against a preset threshold, update the detectors with an internal or external clock, and store 256 such simultaneous decisions for each input signal. This information is then presented

for display on an oscilloscope in an eight trace timingdiagram presentation. Thus, the user can capture unique combinations of digital events for concise and rapid analysis.

The Model 810-D is a bench-type instrument with tiltup stand and may be rack mounted either as a single unit or two units with the factory option rack mount kit which occupies a 7-inch vertical space in a standard 19" wide rack.

Specifications for the Model 810-D are given in the following paragraphs.

# 1.4 Specifications

SIGNAL INPUTS

Number 8.

Impedance: 1  $M\Omega/25pf$ . Inputs greater than + 15 V clamped

to + 15 V through  $1K\Omega$ .

Threshold: Selectable; -10, -5, -2, -1.3, 0, 1.4, 2, 5,

10 and variable + 10V. Accuracy of levels is

nominally + 5%.

Max Input Voltage: + 50V continuous, + 100V transient.

Input Modes: Selectable; SAMPLE or LATCH.

SAMPLE Mode: Unit stores the detected logic level present

at each positive clock transition.

Set Up Time: Zero ns prior to the clock transition.

Hold Time: 15 ns maximum after clock transition typ-

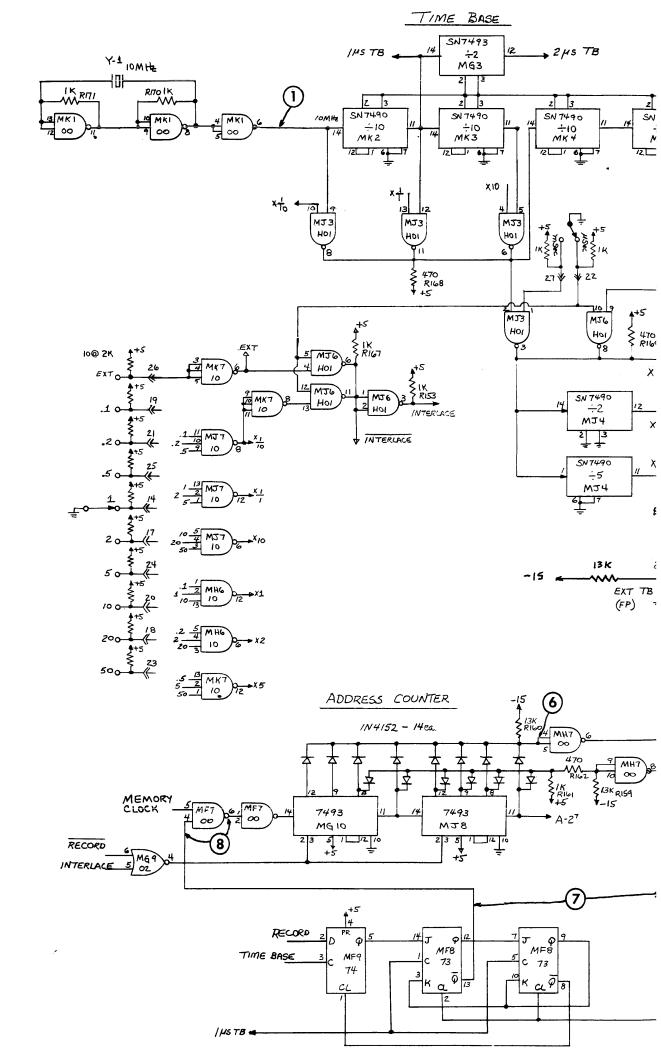

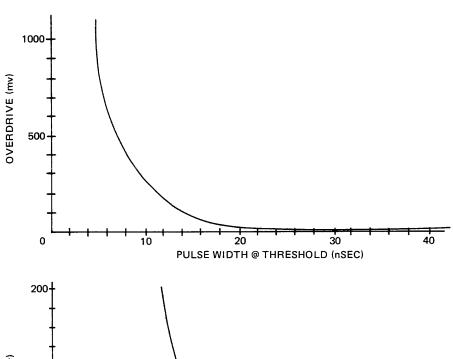

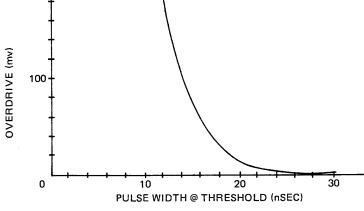

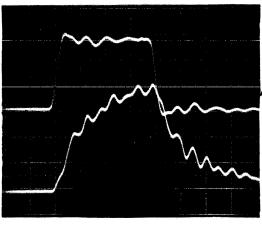

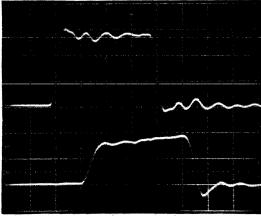

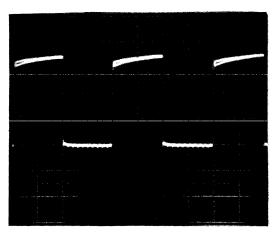

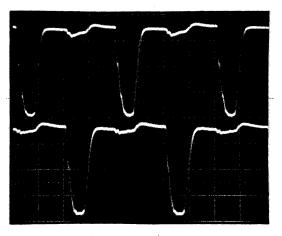

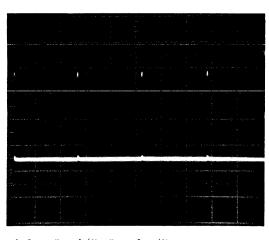

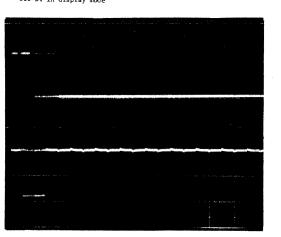

ically 10 ns (refer to Figure 1.1).

LATCH Mode: Threshold detector latches in state opposite

that stored at previous clock transition in the event that multiple transitions of the threshold occur prior to next clock transi-

tion.

Minimum Pulse width

+- TAMOII.

to LATCH:

15 ns with 150 mv overdrive beyond actual threshold, (typically 10 ns, refer to Fig.

1.1).

CLOCK

Internal: Selectable .1, .2, .5, 1, 2, 5, 10, 20, 50

microseconds or milliseconds clock intervals.

External: Via Front panel BNC connector, continuous rates

from 10MHz and to 1kHz and below 1kHz. Clock

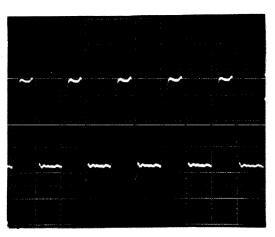

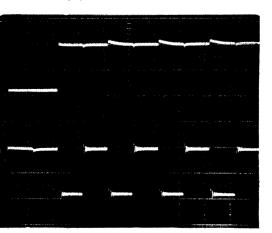

# LATCH MODE-TYPICAL DATA

### SAMPLE MODE-TIMING REQUIREMENTS\*

\*AS MEASURE WITH 1 nSEC RISE & FALL SIGNALS, CLOCK = 0 to +3 V, DATA = 0 to 2 V & THRESHOLD = 1.4V.

Figure 1.1

pulses to be TTL levels with rise and fall times of less than 100 ns and minimum pulsewidth of 50 nS. Clock input impedance is one TTL load. Data is stored on positive clock transition.

### TRIGGER

Source: Selectable; Internal or External.

Internal: Via #8 input signal BNC.

External: Via Front panel BNC connector. Input Impedance,  $1M\Omega/25pf$ .

Slope: Selectable + or -.

<u>Level</u>: Internal, same as signal threshold; External, adjustable + 10V.

### **MEMORY**

Size: 8 x 256 bits. \*See Note Page 5

Start via Front panel momentary RECORD switch or via rear panel logic pulse input. Stop via trigger detection and after selectable Delay, or via front panel momentary switch.

Delay: Data in 32, 128 or 224 (selectable) clock periods prior to the detected trigger is retained.

### DISPLAY OUTPUTS

X Output: Repetitive 1 V p-p ramp waveform, period of 512  $\mu$ s, origin adjustable  $\pm 1.5$ V.

X Expand: X5, X Ramp Slope increased 5 times. Max amplitude clamped at + 1.5V.

Y Output: Repetitive 4608  $\mu s$  long stair step ramp, each step equally spaced in amplitude. Data for each channel modulates each respective step level. Full range nominally 0 to +1V.

Z Output: Nominal zero to +5 V pulse, 8  $\mu$ sec in duration occuring every 512  $\mu$ s and synchronized with X ramp.

$\overline{Z}$  Output: Nominal +5V to zero pulse, 8 µsec in duration occurring every 512 µs and synchronized with X ramp.

### DIGITAL INTERFACE

Data: Output, 8 bits parallel, TTL levels positive true, word serial asynchronous data transfer under control of Flag and Command signals. Rates 500 kHz down to 2kHz. \*See Note Below

Flag: Output of positive TTL transition indicates data word on output lines can be read. Min. width 0.1 µS.

Command: Input of negative TTL transition requests next

data word.

Output Request: Input of TTL low or ground stops the display and initiates the digital data output.

Output Enabled: Output occurs within 512 µS after Output Request indicating data output mode is established. Nominal zero to +4 V transition, remains high during output of data and returns low after 256 words are transferred.

Timebase I/O: Record timebase input and output. Used for connecting several 810-D units together for synchronous recording.

Delayed Trigger I/O:

Used for connecting several 810-D

units together for simultaneous

triggering. Provides simultaneous end

of record of several units when any

one is triggered (after trigger delay).

### **MISCELLANEOUS**

Operating Temp. Range: 0-50C.

Power: 104-126 or 209-253 VAC, approximately, 25 W, 50-400Hz.

Size: Height; 5.25" (13.5 cm.) Width; 8.5" (21.5 cm) Depth 17" (43 cm).

Weight: Approximately 16 lbs (7.3 Kg).

\*NOTE: The first data word in the memory (i.e., first bit in each channel) is not specified to contain good data.

Therefore, timing measurements with respect to this first word may be invalid. All other data words will be accurate and contiguous relative to the record clock.

### SECTION II

### Installation

# 2.1 Introduction

This section contains information on unpacking, inspection, repacking, storage and installation of the Model 810-D.

# 2.2 Unpacking and Inspection

Inspect instrument for shipping damage as soon as it is unpacked. Check for broken knobs and connectors; inspect cabinet and panel surfaces for dents and scratches. If the instrument is damaged in any way or fails to operate properly, notify the carrier immediately. For assistance of any kind, including help with instruments under warranty, contact your local Biomation representative or Biomation in Cupertino, California, U.S.A.

# 2.3 Storage and Shipment

To protect valuable electronic equipment during storage or shipment, always use the best packaging methods available. Contract packaging companies in many cities can provide dependable custom packaging on short notice.

# 2.4 Power Connection

Line Voltage: The Model 810-D may be operated from either 115 or 230 volt (+ 10%) power lines. A rear panel line voltage switch permits quick and safe conversion for operation from either voltage.

CAUTION: Before plugging instrument into AC power line be sure line voltage switch is properly positioned.

Power Cable: The Model 810-D is equipped with a detachable 3-wire power cable. Proceed as follows for installation:

a) Connect line-cord plug (3-socket connector) to AC line jack at rear of instrument.

# Power Cable (cont'd)

connect plug (2-blade with round grounding pin) to 3-wire (grounded) power outlet. Exposed portions of instrument are grounded through the round pin on the plug for safety. When only 2-blade outlet is available, use connector adapter, then connect short wire from side of adapter to ground.

# 2.5 Preparation for Use

The Model 810-D is not a "self-contained" instrument in that it must be interfaced with other types of instrumentation in order for the data to be visible or analyzed. The following sections of this manual cover operation, set ups and interface requirements.

# 2.6 Initial Warm-Up

Although the Model 810-D is a solid state instrument, a brief warm-up period of approximately 5 minutes is required for the input amplifiers and comparators to reach thermal stabilization. This warm-up period is recommended for both the Model 810-D and its associated output device.

### SECTION III

### Principle of Operation

# 3.1 Basic Functional Description

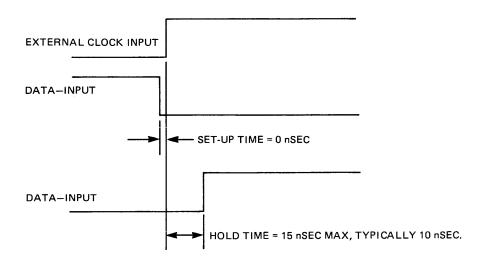

The Model 810-D offers convenient and useful capabilities for the analysis of digital signals. The unit is an eight channel solid state digital recorder which operates at a maximum bit rate of 80 megabits/sec. Figure 3.1 presents a block diagram of the 810-D.

The memory in the 810-D stores a 256 bit record for each of the eight channels. Operation of the RECORD switch causes the unit to monitor and record the status of the eight input lines at the selected clock rate. When a triggering event occurs, recording is terminated after a delay period. Selection of the delay determines the position of the "display window" before and after the triggering event. In this way, eight points in a digital circuit can be continuously monitored, waiting for a specific fault or logic event. When the event occurs, a contiguous record of events before and after the trigger is recorded for display and analysis.

# 3.11 Input Threshold

The definition of a stored data signal as a binary "1" or "0" is determined by a switch selected logic threshold level. A selection of nine threshold voltages are provided, including a +1.4 Volt "TTL" threshold level. In addition, an adjustable level position can be selected which can be set to any level between + 10 Volts.

### 3.12 Sample Mode

In the "SAMPLE" mode of operation, the input levels are strobed into the memory as "1" or "0" based on the signal level with respect to the selected threshold at the time of the rising edge of the clock.

Figure 3.1

### 3.13 Latch Mode

The "LATCH" mode of recording permits narrow spikes to be recorded. Any spike (positive or negative) with sufficient amplitude that is wider than 15 nS causes an input latch to set. This changes the state of the next bit to be written in memory. In this way, narrow spikes or "glitches" occuring at random times between sample clock transitions can be captured.

### 3.14 Signal Inputs

The eight signal inputs plus the external trigger inputs are buffered to provide  $1 \text{ M}\Omega/25 \text{pf}$  input impedances. This permits the use of common passive scope probes for connections to the circuit under analysis.

### 3.15 Record Rates

Internal clock rates are selectable from 20 samples/ second up to 10 Megasamples/second in 1-2-5 steps. Or, the clock of the device under test may be used to provide synchronous recording, a distinct advantage when synchronous logic is under test.

# 3.16 Record Operation

A record sweep proceeds as follows: pressing the record switch starts the unit recording; i.e., continuously shifting new data into the shift register memories. On trigger detection (External, Manual, or Internal from Channel 8 input), the unit will begin a preset count as determined by the delay control and then stop recording.

If a delay of 1/8 is selected, the unit will count down for 224 clock periods after trigger and stop recording. If a delay of 1/2 is selected, the time out count is 128 clock periods. Similarly, the selection of the 7/8 delay will cause 7/8 of the memory length to contain prior trigger data by counting for 32 clock periods after the detected trigger point.

### 3.17 Display Output

Once Record is halted, the unit automatically goes into a display mode, where the memory is continuously circulated and the contents are repetitively output in analog form for display on a CRT or oscilloscope.

The display presentation is an eight signal timing diagram on the CRT. With no horizontal expansion, 252 bits of information are displayed on the CRT for each signal (about 25 per div). Using the built-in horizontal expansion switch, the display is expanded by a factor of 5. Therefore, each division of the CRT in the expand mode contains approximately 5 bits of data on each signal.

# 3.2 Recording Considerations

As the Model 810-D can record as a function of either the internal clock or an external clock, note must be taken of some basic differences in these two methods.

When the internal clock is used for recording no particular phase relationship will exist between this clock and any synchronous information rate in the signals being recorded. Therefore, a "beat" frequency can exist between these two basic rates. If the 810-D internal clock is 10 times or more higher in frequency that the "signal" rate, very little effect will be noted in the recorded data. For higher "signal" rates (with respect to the record clock) a "beat rate" effect can be seen by varying widths in the recorded "pulses" and even periodic "dropped" bits when these rates approach the limiting ratio of two to one.

When the synchronous clock used for the generation of the input signals to the 810-D is used as the record clock in the 810-D, no phase errors exist and no beat frequencies will be evident; i.e., the beat note is zero frequency. In this case, signals with information rates up to and including 1/2 the clock frequency can be recorded, without distortion. This is called synchronous recording.

### SECTION IV

# Operation

# 4.1 Introduction

This section identifies and describes front panel controls, rear panel connections and typical operating procedures. Included are complete descriptions of front panel controls and their effective ranges, location and proper use of rear panel connectors, set up procedures prior to using the Model 810-D, and step by step operating procedures for various modes of operation. A thorough understanding of this section is essential to the successful use of the instrument.

# 4.2 Front Panel Controls and Connectors

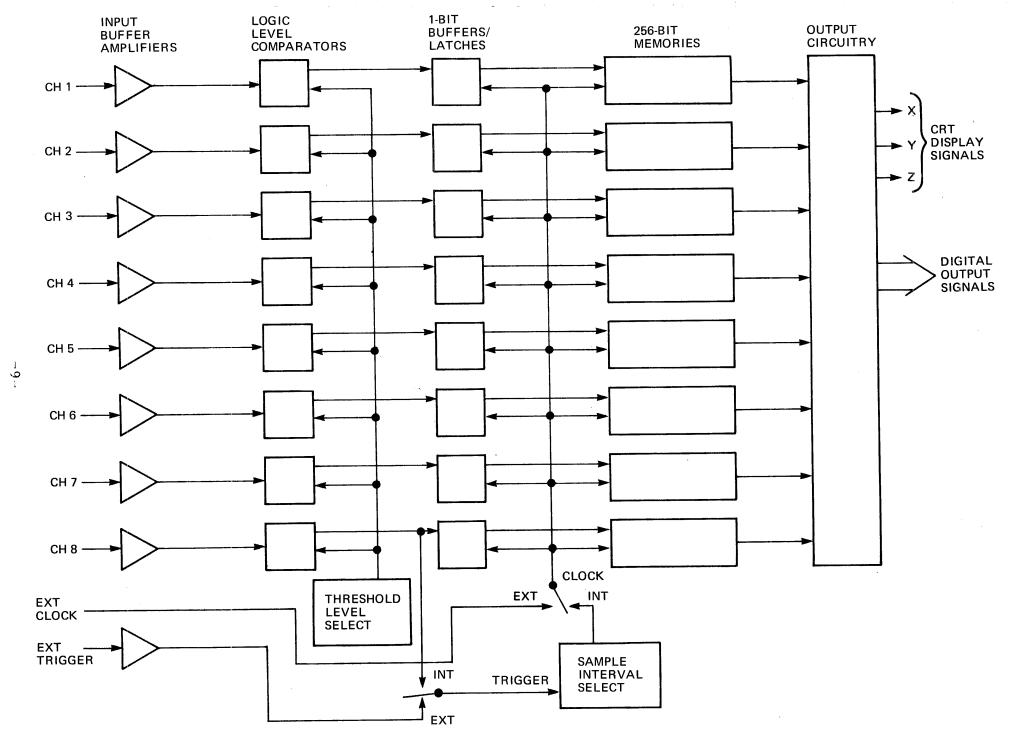

### 4.21 Control Clusters

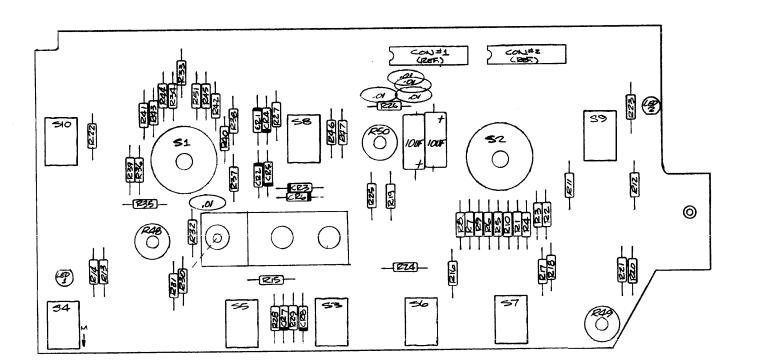

The controls of the Model 810-D may be divided into five groups. Each group contains separate controls with related functions. Figure 4.1 is a front panel photograph of the 810-D. The five control groups are as follows:

Mode and Threshold Display Clock Record and Trigger General

### 4.22 Mode and Threshold

(1) SAMPLE/LATCH. In SAMPLE position, the unit compares input levels with the preselected threshold level and stores a high or low, as appropriate, on the positive transition of the clock. Thus, the data stored in memory reflects the input states at the clock transition.

In the LATCH mode, the unit stores as above for single threshold transitions in a clock period, but also "latches" to a state opposite that last stored when multiple transitions occur in a clock period. For instance, a single narrow pulse between clock transition would not effect the memory contents in SAMPLE mode but would effect the stored data in LATCH mode. This "glitch" catching feature words for either positive or negative pulses by "stretching" the

Figure 4.1 810-D Front Panel

random pulse to one full data period. The 810-D will typically "latch" on pulses as narrow as 10 hS.

# (2) THRESHOLD, VOLTS.

Provides switch selection of -10, -5, -2, -1.3, 0, 1.4, 2, 5, 10 volts threshold, as well as variable (VAR). In the VAR position, the user may adjust a vernier threshold level, using the potentiometer marked VARIABLE (3) and the test point marked TEST (4).

When the input level is more positive than the threshold, a logic "one" (high) is stored in memory; when the input is less positive, a logic "zero" (low) is stored.

# (3), (4) VARIABLE TEST.

To set a vernier threshold, set THRESHOLD, VOLTS (2), to VAR. Adjust VARIABLE (3) with a screwdriver for the desired threshold as measured at TEST (4). The selected threshold voltage for any of the positions on the THRESHOLD selector switch can be checked at the TEST point (4). The output impedance at this test point is  $10 \text{K}\ \Omega$ . The accuracy of the threshold voltages are nominally + 5% of the indicated value.

### 4.23 Display

Note: These controls give the following action only when the 810-D is providing X axis drive to the CRT.

(5) X1/X5. This switch provides a X5 horizontal expansion. Without expansion, 250 clock periods are displayed, or 25 clock periods per division, assuming 10 display divisions. With X5 expansion, 5 clock periods per division are displayed.

### (6) POSITION.

This control sets the horizontal position on the CRT display with Xl expansion selected and gives the ability to place any 50 clock periods of data cross the full CRT display width with X5 expansion selected.

### 4.24 Clock

### (7) CLOCK INTERVAL.

Selects, in conjunction with the  $\mu$ SEC/mSEC switch, the choice of internal clock intervals of 0.1, 0.2, 0.5, 1, 2, 5, 10, 20, 50  $\mu$ SEC/m SEC or EXT. clock input.

### (8) $\mu SEC/mSEC$ .

Provides multiplication factor for switch (7) (when EXT clock interval is selected, this switch must be set per the red legends (<lms, >lms) appropriately for the clock interval being used.

(9) EXT CLOCK (TTL LEVEL).

This BNC connector allows input of an external clock when switch (7) is in EXT position. For clock intervals from lms to the minimum interval of  $0.1 \mu s$  switch (8) must be in the <1ms position; for intervals greater than lms switch (8) must be in the >1ms position.

This input accepts TTL levels, and the input load is one TTL gate. The unit samples on the rising edge of the clock.

# 4.25 Record and Trigger

# (10) RECORD, (11) RECORD Indicator

Pressing this momentary toggle switch starts the unit sampling the inputs and clocking data into memory. The red LED (11) illuminates to indicate Recording in process. When recording at slower rates, hold this switch down to inhibit trigger. This will ensure that the memory is cleared of old data before any new data is loaded.

### (12) MANUAL.

This momentary switch provides a manual trigger. Pressing it stops the Record mode and a display is presented.

### (13) DELAY.

This three position switch allows three delay selections as follows:

1/8: 32 clock periods prior to trigger are retained in memory.

1/2: 128 clock periods are retained.

7/8: 224 clock periods are retained.

### (14) SLOPE, +.

Allows selection of triggering on the positive (+) or negative (-) going transition.

### (15) EXT/INT.

Allows selection of internal or external trigger source.

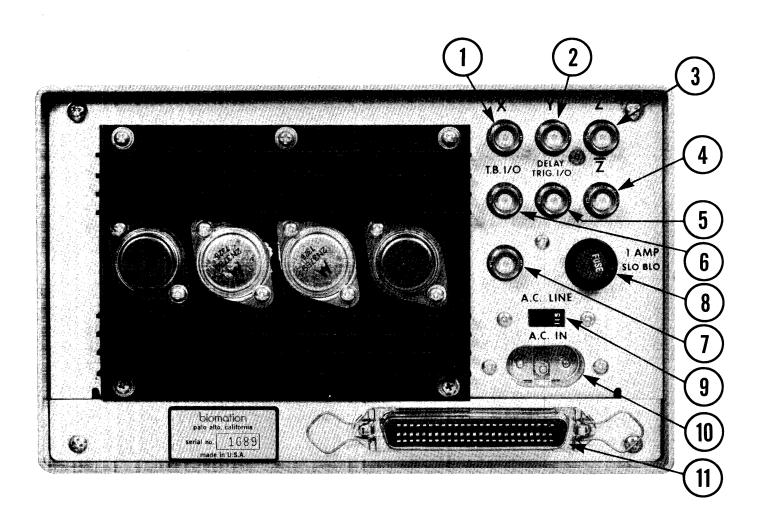

Figure 4.2 810-D Rear Panel

On INT, the unit triggers on a transition (+ or - as selected) of the signal on channel 8 that exceeds the threshold level selected by switch (2).

On EXT, the unit will be triggered by the transition of a signal applied to connector (17).

(16) EXTERNAL TRIGGER, LEVEL.

Allows adjustment of external trigger signal threshold between + 10 V.

(17) BNC Connector.

External trigger input connector, input impedance of  $1M\Omega//25pf$ .

- 4.26 General

- (18) INPUTS (8 each).

Any or all inputs may be used at one time. Input impedance is  $1M\Omega/25pf$ .

(19) AC POWER.

When switch is on, LED (20) illuminates.

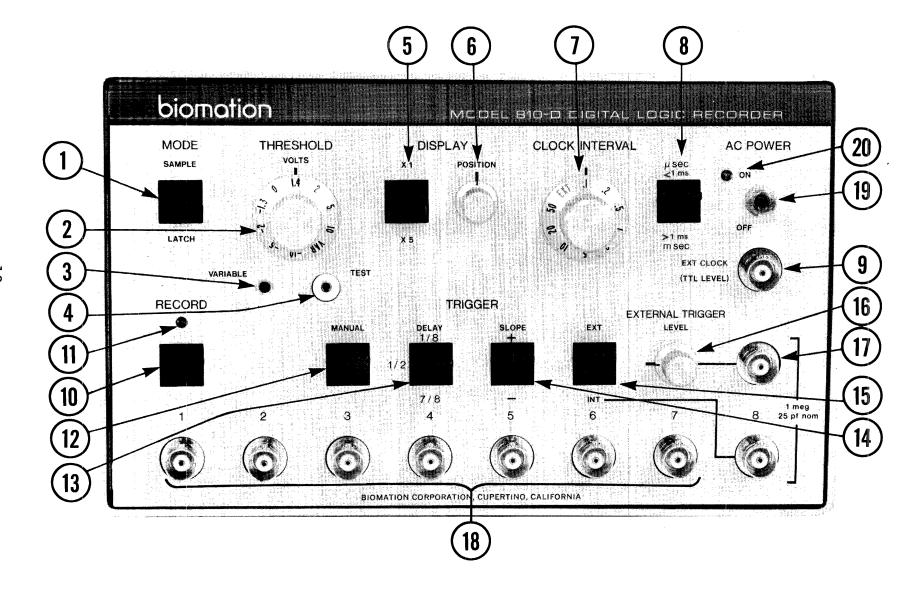

- 4.3 Rear Panel Connectors. (See Figure 4.2).

- (1) X Output.

Repetitive lV pp ramp, waveform, with a period of 512  $\mu S$  Ramp is 504  $\mu S$  long with a "retrace" of 8msec. Origin is adjustable + 1.5V. Using DISPLAY expand switch (5), the slope of the ramp is increased 5 times. The maximum amplitude of the ramp is clamped at + 1.5V.

(2) Y Output.

Repetitive  $4608\,\mu\text{S}$  long stair-step ramp; each step equally spaced in amplitude; total amplitude lV p-p. Data from each channel modulates each respective step level. A CRT display is swept nine times per Y "ramp." The Y "ramp" step for channel 8 is swept twice by the X signal and each other channel step swept once. The eighth data step is repeated to facilitate operation with a triggered sweep (using the Z (3) or  $\overline{Z}$  (4) signal of an oscilloscope. The number of data bits viewed per channel is 252, counting from the first bit in each channel.

(3) Z Output.

Nominal 0 to +5V pulse, 8  $\mu$ S in duration and occurs every 512  $\mu$ S. This pulse is synchronized with X and Y outputs.

(4)  $\overline{Z}$  Output.

Nominal +5 to OV pulse, the negation of the Z pulse, above.

(5) DELAY TRIG I/O.

Used to connect several 810-D units together for simultaneous triggering. Provides simultaneous end of record of several units when any one is triggered (after trigger delay).

(6) Timebase I/O.

Record timebase input and output. Used to connect several 810-D units together for synchronous recording. To operate select the desired clock interval on one unit, and set the CLOCK INTERVAL switch on the other units to EXT. To use an external clock, set all interconnected units to EXT, and input the external clock to the front panel EXT CLOCK connector (9) of one unit. Ensure that the <lms/>lms switch (8) is in the proper position. See Section 4.2.

- (7) Spare BNC Connector

- (8) Fuse. 1 AMP SLO BLO for 115V operation, 0.5 amp for 230V operation.

- (9) AC LINE. Switch for selection of operating line voltage, 115V or 230V. Change fuse to 0.5 amp Slo Blo for 230V operation.

- (10) AC IN. Power line connection, 25W input. Use mating power cord, Belden 17358.

- (11) Digital Interface Connector J19. For the description of the signals on this connector, refer to Section V, Output Interface.

# 4.4 Set Up Procedure

### 4.41 Initial Set Up

This section describes the connection of a Model 810-D with a CRT display or oscilloscope and the steps to record and display a known signal.

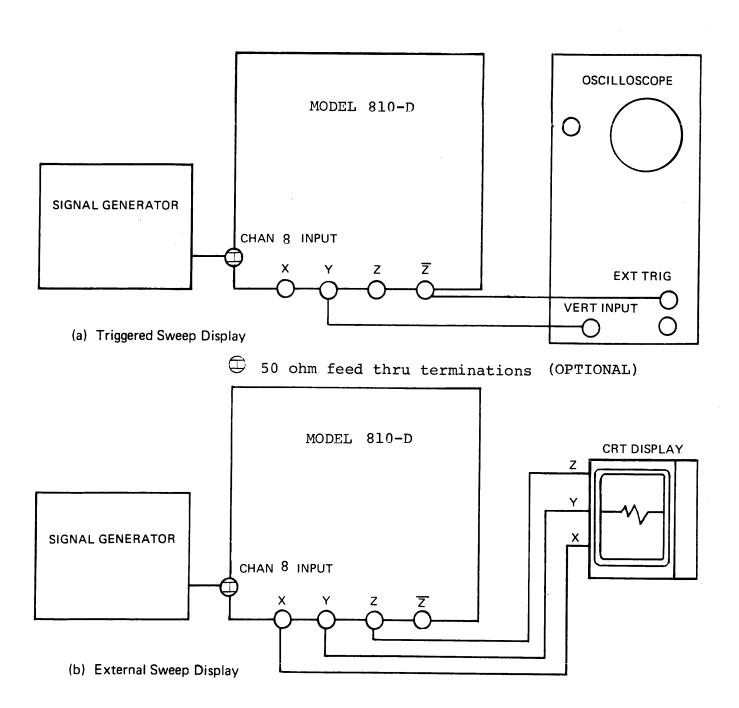

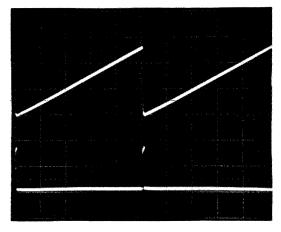

Figure 4.3 Display Interconnections

Before connecting the unit to line power, check the voltage selector switch on the rear panel to ensure that it is set to the proper line voltage and be sure that the correct size fuse (as printed on the rear panel) is installed.

Connect the Model 810-D to a pulse generator with a manual single pulse capability and CRT display as shown in Figure 4.3a or 4.3b. Depending upon the particular CRT or oscilloscope being used, it may be necessary to use the  $\overline{\mathbf{Z}}$  output of the 810-D for the retrace blanking signal.

CAUTION - Some older "tube type" oscilloscopes have a high voltage on their Z axis inputs. THIS COULD DAMAGE THE Z or Z OUTPUT OF THE 810-D. PLEASE CHECK BEFORE CONNECTING THE UNITS TOGETHER.

Set the units (where appropriate) as follows:

Vertical sensitivity 0.1V/div. uncalibrated,

DC coupled

Vertical position Bottom of display

Horizontal sweep 50  $\mu$ S/div., (Fig. 4.3a)

Horizontal sensitivity 0.1V/div., DC coupled

(Fig. 4.3b)

Trigger input -, DC coupled, external

(Fig. 4.3a)

Pulse Generator Single manual pulse, 2.5

$\mu S$  wide, 0 to +3V pulses

Set the Model 810-D as follows:

MODE: Sample

THRESHOLD: 1.4 volts

DISPLAY: X1

CLOCK INTERVAL: 0.1µS

TRIGGER

DELAY: 1/8

SLOPE: Positive

SOURCE: Internal

When initially powering up the unit, always press RECORD and then TRIGGER, MANUAL to reset circuitry. Center the eight traces on the CRT using the vertical and horizontal controls on the scope or display and the horizontal position control on the 810-D.

# 4.5 Operating Procedures

In this section two modes of operation will be discussed and illustrated. A pulse generator capable of generating a single pulse upon manual command is required.

Set the generator to give single manually initiated pulses of approximately 2.5  $\mu S$  wide, and 0 to +3V amplitude.

# 4.51 Sample Mode

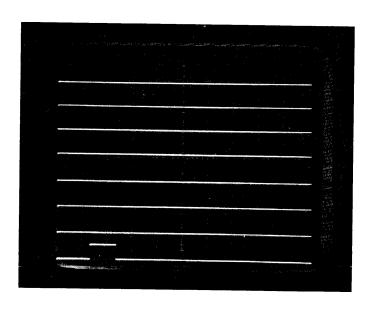

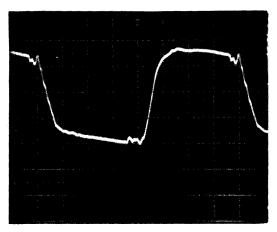

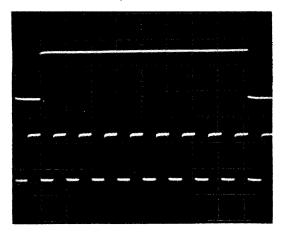

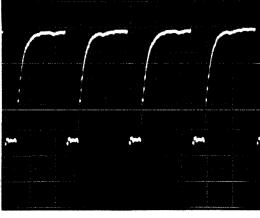

Press RECORD and pulse the generator. Figure 4.4 illustrates the display obtained. Channels 1 through 7 will display a low level, while Channel 8 displays the pulse. The pulse will occupy one division on the CRT, and be comprised of 25 clock intervals. Thirty-two clock intervals will have been recorded before the positive transition of the pulse.

Figure 4.4

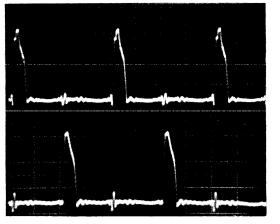

### 4.52 Latch Mode

Set CLOCK INTERVAL to 50  $\mu$ S. In the SAMPLE MODE, press RECORD and pulse the generator while observing the CRT. Repeat this routine several times. Note that although the unit triggers each time on the pulse it seldom records the pulse. In the SAMPLE MODE, the unit stores the input levels present at the clock edge. The clock interval is approximately 20 times as long as the pulse, so the unit can only see the pulse when the clock transition is coincident with it, an unlikely occurence with 2.5  $\mu$ S input pulses and 50  $\mu$ S clock intervals.

Select MODE, LATCH. Repeat pressing the RECORD switch and pulsing the generator. Observe that the unit captures the pulse each time and represents it with one clock interval, or 50  $\mu$ S. This feature is particularly useful for detecting narrow random noise pulses or "glitches".

This mode operates in the same manner independent of the chosen clock interval. A glitch typically as short as 10 ns may be detected and displayed at any clock interval.

# 4.53 Manual Trigger

To verify operation of each channel, change the pulse generator to a repetitive output, approximately 5KHz rate, with the same pulse as before. Starting with channel 1, connect the generator to the input BNC. Press the RECORD switch, and then the TRIGGER MANUAL, switch. Several pulses of one clock interval will be displayed on the CRT, on the top trace. Repeat the above procedure for each channel, 1 through 7. The trace corresponding to that channel will display several pulses in turn.

### SECTION V

### Output Interface

# 5.1 Introduction

The output interface of the Model 810-D includes two methods of analog output: one, using a CRT in an X-Y mode, and two, using an oscilloscope in the triggered mode. These methods are explained in Section 4.41.

The instrument also offers a digital output of data. This data is output in an 8 bit parallel format, the bits representing a simultaneous data entry for all channels. Two hundred fifty six such 8-bit words are available through the digital output mode.

# 5.2 Digital Output

All inputs and outputs at the 50 pin rear panel connector J19 are positive logic, TTL signals. Direct access to control gates is available at J19. This connector provides the physical interface for digital data output. The connector is an Amphenol Micro-Ribbon 57-40500. The mating connector is an Amphenol part number 57-30500.

The pin assignments, and signal descriptions for the digital interface are listed in the following table:

| Pin #                                | Signal Name                                                                                                                    |                            | Description                                                                                                                                                                                                       |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | Detected Ch. (OUTPUTS) | 2<br>3<br>4<br>5<br>6<br>7 | These outputs are the detected input signals after passing through the Input Buffer, Descriminator, and Data Latch circuits, and a buffer gate. No "sense" inversion takes place. This data requires no clocking. |

| Pin #                                       | Signal Name                                                                                                               | Description                                                                                                                                              |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9<br>10<br>13<br>16<br>11<br>12<br>14<br>15 | Data Output 1 Data Output 2 Data Output 3 Data Output 4 Data Output 5 Data Output 6 Data Output 7 Data Output 8 (OUTPUTS) | These lines supply data stored in memory when the digital output procedure, outlined in Section 5.21 or 5.22, below, is followed. Buffering is provided. |

| 19                                          | Output Request<br>(INPUT)                                                                                                 | Line is normally pulled high. To initiate output, pull low until Output Enable goes high.                                                                |

| 21                                          | Output Enable (OUTPUT)                                                                                                    | Goes high within 512 $\mu S$ after Output Request providing the unit is not recording and indicates that the first data word is ready to be read.        |

| 18                                          | Command<br>(INPUT)                                                                                                        | Normally high. Changing to a low level causes unit to "fetch" next data word. The high to low transition time must be 200 nS or less.                    |

| 17                                          | Flag<br>(OUTPUT)                                                                                                          | Goes high when next data word is available, approximately 100 nS after command goes low.                                                                 |

| 20                                          | Record<br>(OUTPUT)                                                                                                        | High when unit is recording; low otherwise.                                                                                                              |

| 45                                          | Trigger<br>(INPUT)                                                                                                        | Logic Level Trigger input.                                                                                                                               |

| 23                                          | +5V Power<br>(OUTPUT)                                                                                                     | May be used to power delay counters, combinational trigger circuits, etc. Available current is approximately 500ma.                                      |

| Pin # | Signal Name           | Description                                                               |

|-------|-----------------------|---------------------------------------------------------------------------|

| 22    | Remote Arm<br>(INPUT) | Line is normally held high and brought low to initiate recording process. |

| 27-44 | Ground                | Power and logic return.                                                   |

5.21 Digital Output Sequence - After Display

Immediately after recording, the 810-D will enter the display mode, repetitively cycling the memory and producing the X, Y and Z display signals. In this condition, the Record (pin 20) and Output Enable (pin 21) output signals will be low. The Output Request (pin 19) input will be pulled high.

When a low is input to the Output Request, the Output Enable will go high within 512  $\mu\,\mathrm{S}$  depending on the instantaneous position of the memory in its display cycle. Flag (pin 17) will go high at the same time. Output Request should be held low until Output Enable goes high. Output Request should then be returned high. It is recommended that the Request and Enable signals be externally interlocked for proper operation. When Flag goes high, the first data word in memory may be read on the data output pins 9 through 16.

The next, and subsequent data words will be presented on the data output lines after each Command (pin 18) input negative transition. For proper data output the interval between Command inputs should be from 2  $\mu\text{S}$  to 500  $\mu\text{S}$ , giving asynchronous data word rates of 500KHz through 2KHz.

CAUTION - Once digital output is established (Output Enabled high), the interval between command transitions must be 500  $\mu\,\mathrm{S}$  or less. Longer intervals may cause permanent loss of the stored data in the 810-D.

The negative transition time of the Command signal must be 200 nS or less. When the command signal goes low, the Flag will go low for 100 nS and then return high again, which indicates that the next data word is settled on the data output lines and can be used. After 256 commands the unit will automatically revert to the display mode. If the Output Request line is held low, the unit will return to output mode after one display cycle.

NOTE: It is essential that at least 256 Command signals are generated. Otherwise, the unit will remain in the Output mode until Record is initiated.

# 5.22 Digital Output Sequence - After Record

If it is desired to output digital data immediately after Record, proceed as follows: Monitor Record (pin 20). When Record goes high, issue a low to Output Request (pin 19). As soon as Record is complete (Record goes low) Output Enable (pin 21) and Flag (pin 17) will go high, indicating the first data word can be read. When this occurs, proceed with Command Flag operation as described above. The unit will automatically revert to display mode after the 256 Command/Flag sequences necessary to complete one data output cycle are completed.

### SECTION VI

# CALIBRATION PROCEDURES

# 6.1 Calibration of Display Output

Adjustments are provided to calibrate the X and Y output to a specific display unit or oscilloscope. In addition, an adjustment is provided for the height of the "1-0" bit. Table 1 gives the location of these adjustments and their nominal P-P output values.

| <u>Function</u> | Location              | Nominal Level P-P |

|-----------------|-----------------------|-------------------|

| X-out           | R181 (next<br>to ME5) | lV                |

| Y-out           | R180                  | 0.8V              |

| Bit Height      | R174                  | 0.06V             |

# 6.2 Recalibration of Internal Circuits

There are no adjustable components in the 810-D except those listed in Section 6.1 above. No further calibration is required.

### SECTION VII

### Technical Description

# 7.1 General Description

The Model 810-D, Digital Logic Recorder, is a very simple instrument. It simultaneously measures whether the input signals are above or below the selected threshold voltage and writes a corresponding 1 or 0 in a semi-conductor memory. The memory used is of the shift register configuration, such that new data is put into the input end of the memory, shifted throughout the length of the memory and discarded at the output end. The recording process may continue for an extended period of time. However, the memory is a finite length (256 data points), so that at any point in time, only the previous 256 data points are remembered.

When data storage is halted by means of a electrical or manual trigger, the data contents of the memory can then be used either visually or by means of the digital output. When the Model 810-D receives a trigger instructing it to stop data storage, a delay process is started. If a delay of 128(½)data points is selected, then new data will continue to be inserted into the memory for 128 clock intervals. Since the memory contains 256 data points, the result will be that 128 points of information prior to the trigger plus 128 points after the trigger will be stored in the memory for use by the operator. This feature allows the operator to look both forward and backward in time relative to his trigger signal.

When data storage ceases, the instrument normally goes into what is called the "display mode" of operation. In this mode, the contents of the memory are continuously recirculated and made available at the output port of the memory. With the memory outputs being updated at a high rate, it is relatively easy to achieve a non-flickering CRT display of the memory contents. By this technique, an X-Y CRT display unit or any conventional oscilloscope can be used to display the timing relationships between logic

signals on the 8 input lines. The logic waveforms displayed will be identical to those shown by component manufacturers or in the timing diagram provided for a system if the operator of the 810-D has chosen the clock interval sufficiently high.

An alternative to the display mode is the digital output mode. This mode allows the 810-D to be used with a suitable interface to output the stored information to a computer system. Once the computer via its interface requests output data from the 810-D via the interface to the computer, the data is supplied one word at a time sequentially, beginning with the first word in memory through the final word in memory. Each word is available at the output connector (8 bits in parallel) with a Flag signal indicating to the computer that the data is valid and ready to be clocked into the computer. The computer must monitor and count the number of data words removed from the 810-D, and all 256 words must be removed. There are minor clocking restrictions which must not be violated if valid data is to be obtained. These restrictions are covered in other parts of this instruction manual.

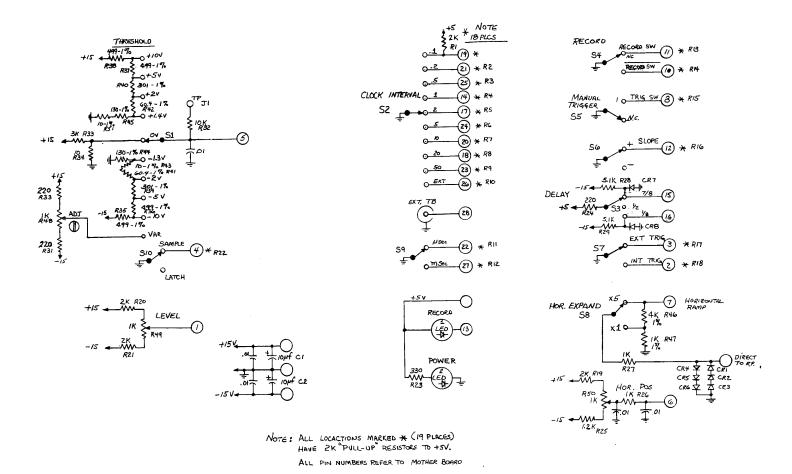

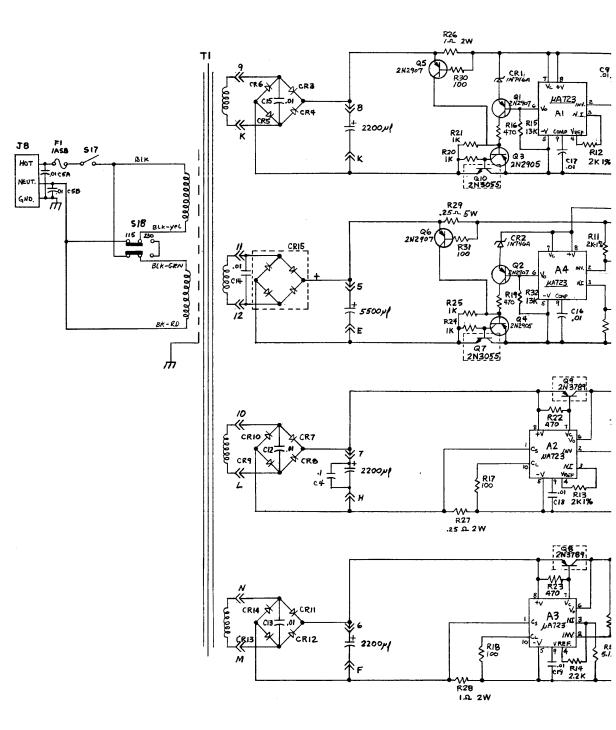

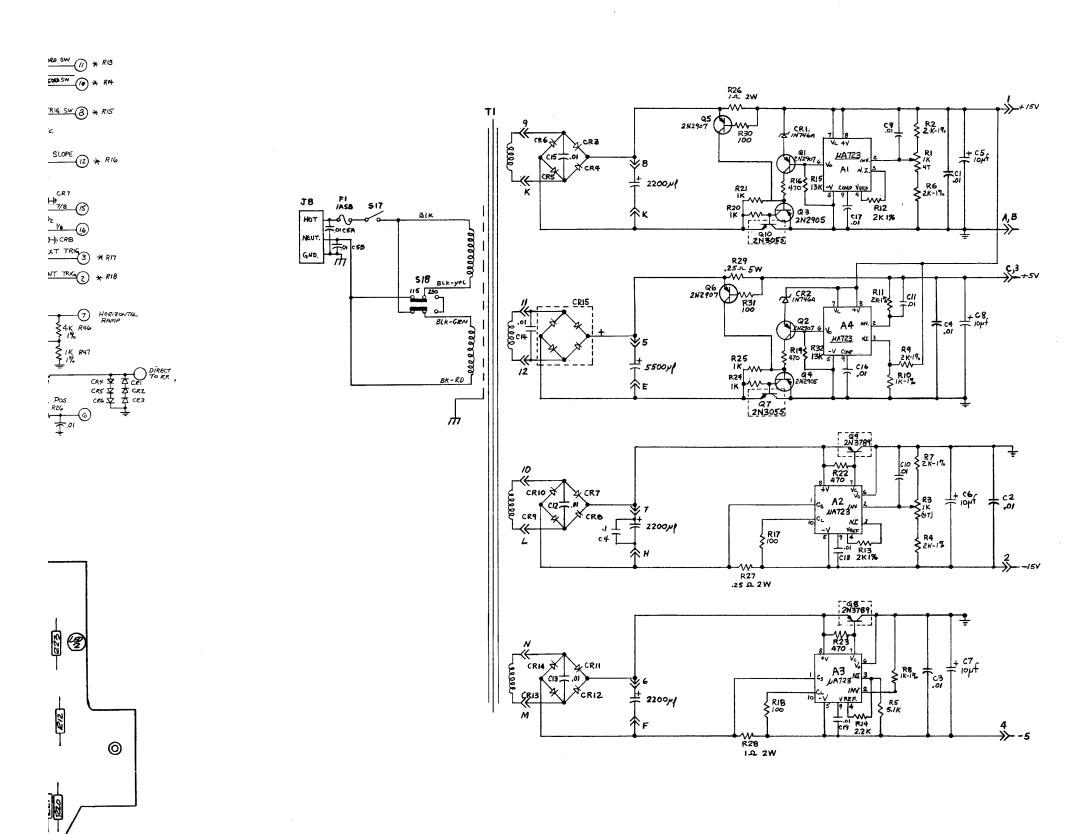

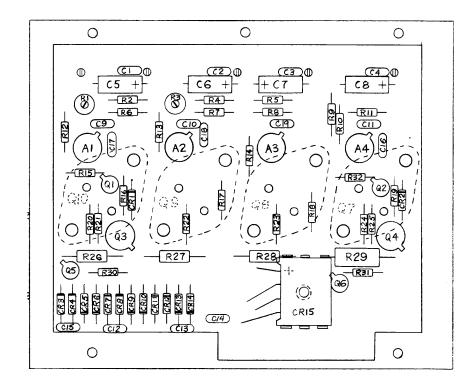

### 7.2 Circuit Details

This section will deal with the individual circuits of the 810-D. Section 7.3 will tie these circuits together as they function in various modes. In using this section, reference will be made to the 810-D Schematic Diagrams (0811-0002). This Schematic is drawn on four individual sheets. Reference will be made at the beginning of each new circuit description to indicate the reference sheet. Any attempt to discuss individual circuits of an instrument must lead to some frustration on the part of the reader. However, it is felt that if the individual circuit groupings can be understood, a better feeling of the overall instrument design and concept will be obtained. Ultimately, such an understanding is necessary if one is to satisfactorily service and maintain an instrument over an extended period of time.

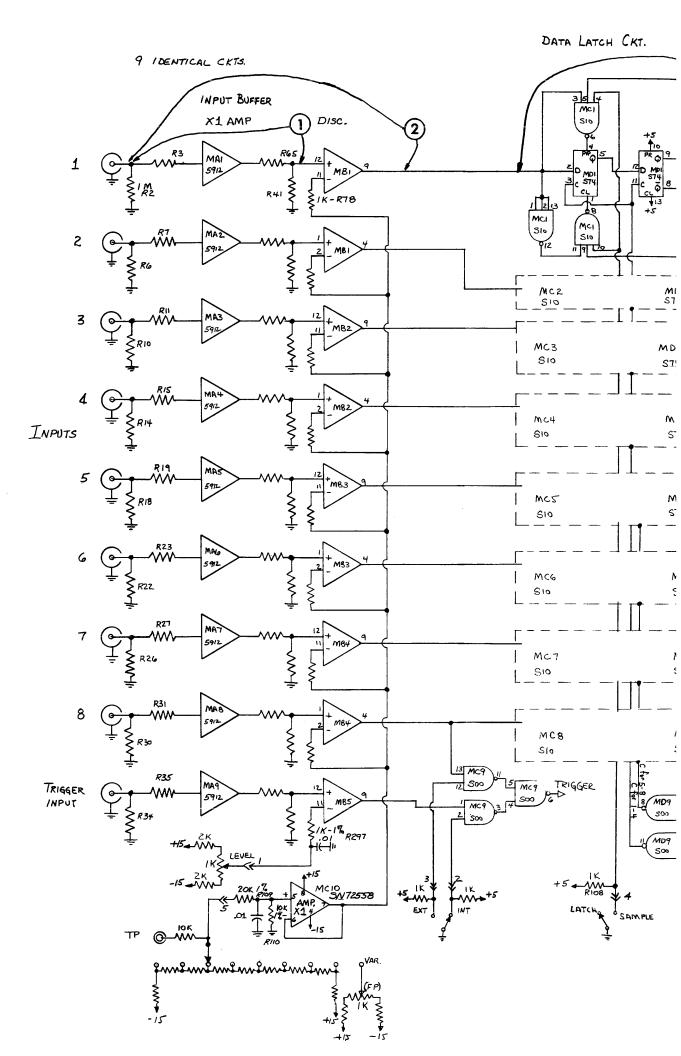

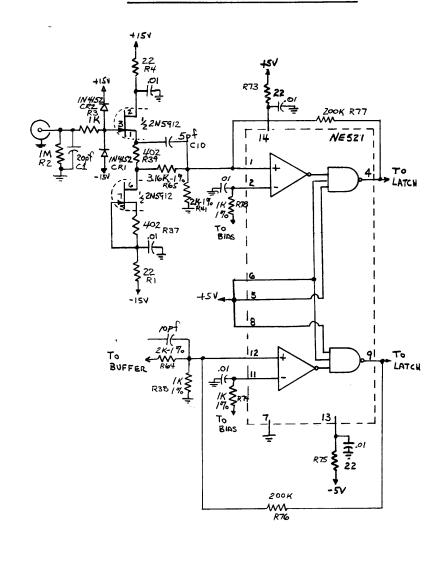

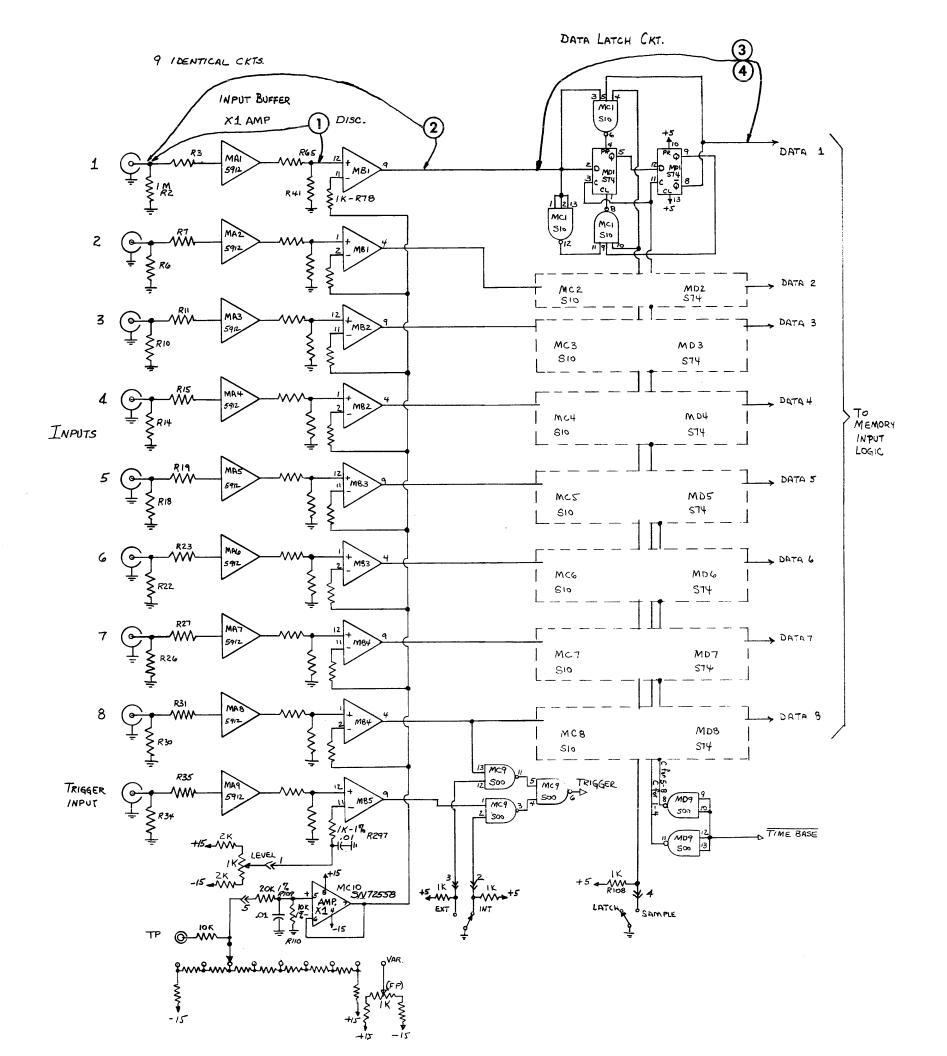

### 7.21 Input Circuit (Schematic Part 1, Page 56)

Referring to the left side of the schematic, one will note that the eight signal inputs, plus the trigger input, have identical circuits. Each has a Xl buffer amplifier. Each has a passive attenuator following the buffer amplifier, which attenuates the signal by a factor of 3. The attenuated signal from each goes to the non-inverting input of a threshold descriminator. The only difference between these nine signals is that the threshold level for the 8 signal inputs are tied to a common threshold level

and the threshold to the trigger input goes to a separate control. It will be noted that the left side of the Schematic encompassing the buffer amplifiers and the descriminators represents a block diagram of the circuit, and not the circuit details. Now referring to the upper right of the Schematic, the details of the buffer amplifier-descriminator will be described.

The input buffer amplifier has approximately unity gain and virtually zero offset from input to output. It consists of a pair of matched field effect transistors combined in a follower configuration. The passive attenuator consisting of resistors R-65 and R-41, along with the output impedance of the amplifier gives a gain of 1/3 from the input BNC connector to the input of the threshold detector following the amplifier. This reduction in signal is necessary when high input levels are applied to the input, because these high levels (greater than 5 Volts) if unattenuated, would exceed the dynamic range characteristics of the descriminator. Referring back to the input connector, it will be noted that the input impedance consist of a 1 Megohm resistor in parallel with a 20 pf capacitor along with the load associated with the input clamp and the field effect transistor. For signal levels below + 15 Volts the input impedance will be determined by the RCnetwork on the input terminal. For signal levels greater than + 15 Volts, the dynamic input impedance will drop to 1 K.

The level detector is a monolithic device, fabricated two per package. The component type is NE521. It will be noted from the Schematic Diagram that, in addition to having a level detector, the device also contains a gated output capability. It will also be noted from the Schematic Diagram that the output gate is not used in the Model 810-D. The gate inputs are tied firmly to the +5V power supply, thereby enabling the output gate. Feedback around the descriminator is provided by a 200 K resistor. The feedback is positive and contributes about 25 mv of hystereses to the device. This hystereses entirely dominates the normal hystereses of the threshold detector and when reflected to the input terminal, represents a hystereses of approximately 75 mv.

The threshold level for the 8 input signals is determined by the front panel control. In addition to the 9 levels, there is also a variable level which the user can use within a range of + 10 Volts. Referring to the Schematic Diagram, it will be noted that the input switch is buffered by an operational amplifier used in a follower configuration. This provides a low driving point impedance for the common bias line. The threshold level for

the Trigger input is driven directly from a front panel potentiometer and provides a range of approximately  $\pm$  10 Volts for the independent trigger input (taking into effect the 1/3 gain of the input section.)

# Latch Circuit

If the signal level exceeds the threshold, a high level is written in the 810-D memory section. If the signal does not exceed the threshold, then a low level is written in the memory. However, prior to the memory, a data latch circuit is used as a temporary buffer and to allow two distinctly different modes of operation to be available for the user. This is shown in the center of Sheet 1 and is entitled "Data Latch Circuit". If the unit is operating in the Sample mode, then one input to the routing gates going into the preset and clear inputs on the first D register is grounded by the switch. This prevents the input signal to the latch circuit from influencing the D registers in any mode other than the data input (D input) to the first register. Likewise, the feedback from the second register to the first register is inhibited by the grounded input to the routing gate. Consequently, in the Sample mode the D register is set to a high or low level by the buffered Timebase signal. One clock pulse later, the information is transferred from the first register to the second register and read into the memory of the Model 810-D. In the Sample mode, the operation can be simply stated, "if the input signal is above the threshold at the time of the clock, a logic 1 will be written in memory." Conversely, if the input signal is below the threshold at the time of the clock edge, then a low level will be written in the memory. There is an additional one clock delay caused by the second register. However, since all eight data channels operate in an identical fashion, the data will still be lined up as stored in memory.

The Latch mode is somewhat more complex, but its presence in the unit allows much greater flexibility in the use of the instrument. The Latch mode allows the unit to capture small pulses (glitches) that often occur asynchronously within a system. It is the same narrow pulses occuring infrequently that are the most difficult to measure and to determine a timing relationship for. The latch capability of the Model 810-D largely overcomes these problems.

Let us assume that the input level has been below the threshold for some period of time. In this case, the Q output of the second register (MD-1, pin 9) will be at a low level and pin 8 will be high. The output levels will

condition the routing gates such that the gate to the preset input of the first register is capable of acceping a signal, whereas the clear routing gate is incapable of transmitting If a narrow input signal occurs which crosses a signal. the threshold, a narrow positive pulse will be generated at pin 2 of the first register. The pulse will have no effect at pin 2 because it has occurred unrelated to the Timebase. However, it will be transmitted via the preset routing gate (located above the first register on the Schematic) to preset the first register such that pin 5 goes to a high level. At the next clock pulse, the contents of the first register will be transmitted to the second register and consequently into the memory of the unit. The action just described will occur for pulses as narrow as 10 nanoseconds. It must be understood, however, that to transmit a pulse as narrow as 10 nanoseconds, a considerable amount of over-drive must be applied to the input section. If we reverse the conditions, whereby the input level has been above the threshold for some period of time, with the occurance of a narrow negative pulse, we will see that the same type of action occurs as with a positive pulse. The negative pulse, however, is transmitted to the clear routing gate such that it will cause pin 5 of the first register to go low for subsequent storage into the second register at the next clock pulse. In either the case for a positive or a negative pulse the first clock occuring after the pulse will change the first register back to its original quiescent state (high if the signal has been at the high level or low if the signal had been low), and this same clock pulse will transmit the contents of the first register to the second register where it will remain for a full clock period such that it can be written reliably into the memory section. In the event that a "glitch" occurs between each pair of clock pulses then the data written into the memory will alternate high and low levels. Such a condition if observed on the CRT display would indicate to the user that either there is an excessive amount of noise on this particular line or that a faster clock rate is needed. One point to remember as we leave the discussion of the data latch circuit is that data appears on the output of the second register (pin 8 of MD1-MD8) for a full clock interval and should never change except at the edge of the Time Base signal. Data is transmitted from the data latch circuit to the data circuit.

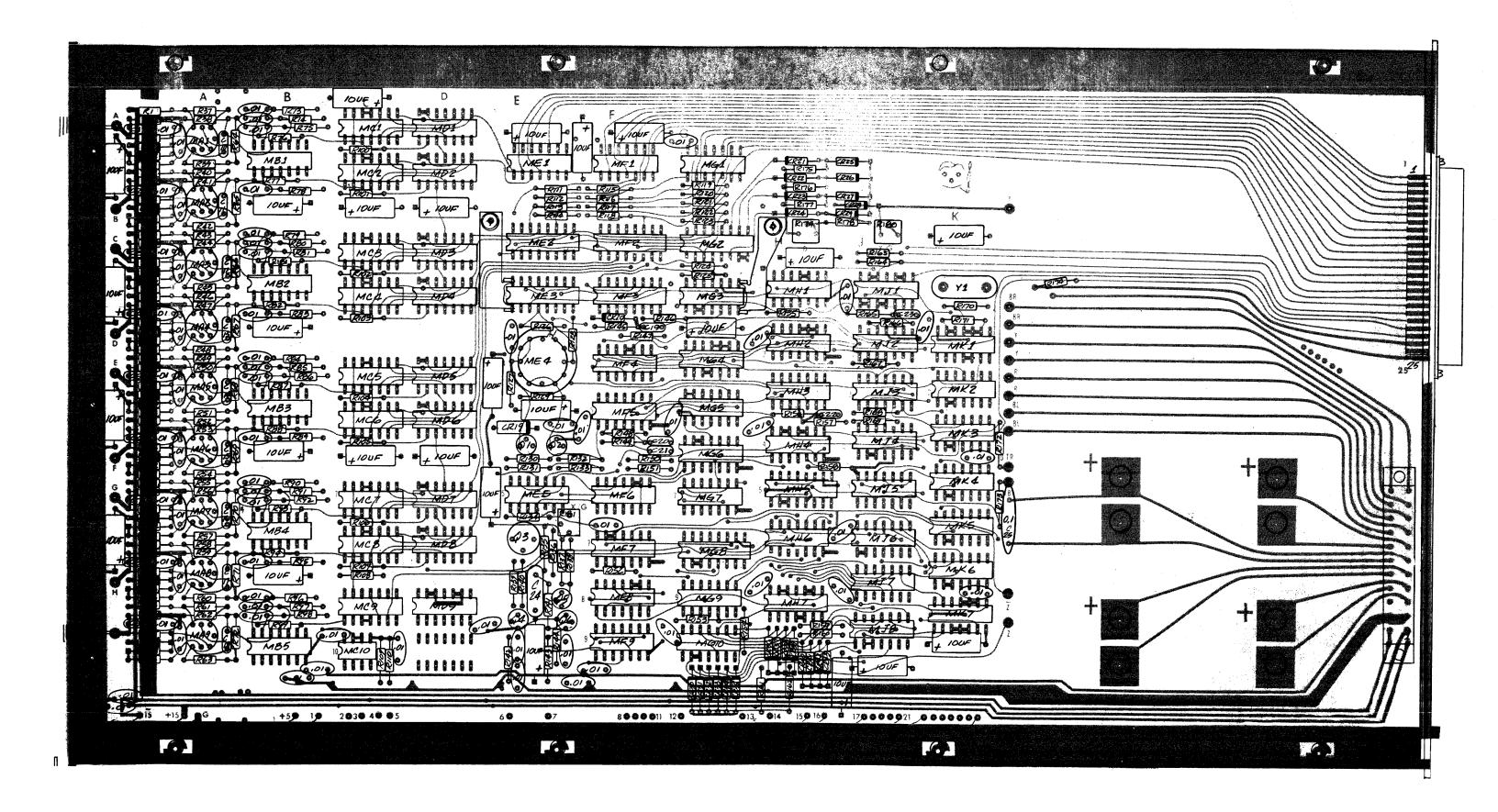

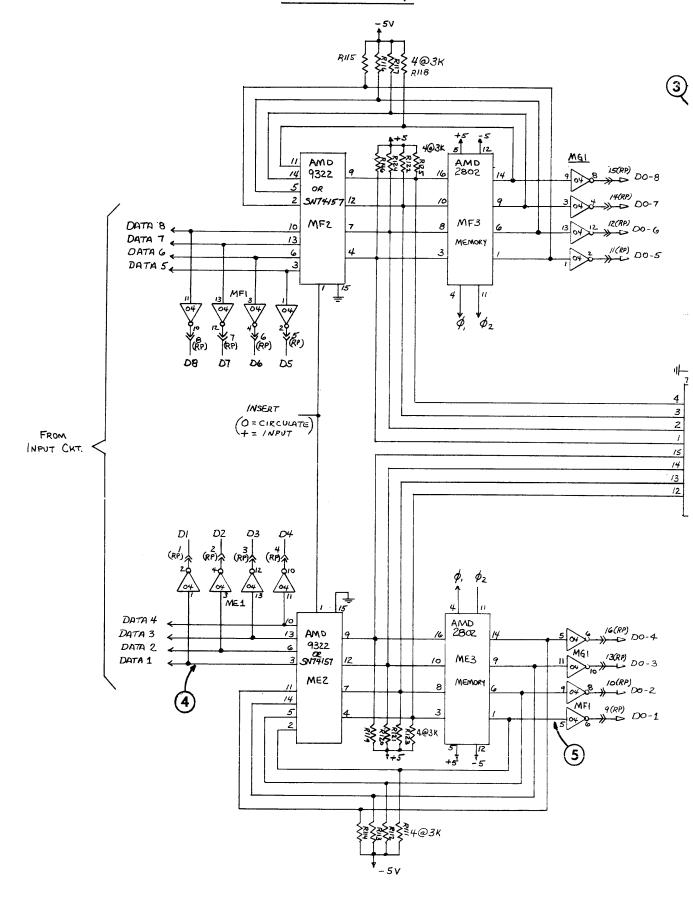

# 7.22 Data Circuit (Schematic Part 2, Page 57)

The data circuit consists of shift register memories, routing gates for the memories and buffered outputs to be used by peripheral devices. Referring to sheet 2 we can trace a data signal from the data latch discussed in the previous section through the memory section. Note that

the outputs from the data latches are buffered and made available at the rear panel by means of the inverting buffers (MEl & MFl). Referring for a moment back to the data latch circuit on Sheet l it will be noted that the inverting output of the second latch is used instead of the non-inverting one. The use of an inverting buffer on the input to the data circuit restores the signal to the proper state at the rear panel.

The data circuit serves the purpose of storing the input signal. The heart of the data circuit is a 256 word shift register for each of the 8 input signals. These shift registers are clocked synchronously such that data appearing on the inputs are recorded synchronously within the memory. This maintains the timing relationship present on the original data at the input connectors. If the Insert signal is at a high level, then the input data from the latch circuits is transmitted to the memory. Under these conditions a signal appearing on pin 3 of ME-2 Data -1 would appear on pin 4 of ME-2. In like fashion, the Data 2 signal on pin 6 would appear on pin 7 and so forth. In the event that the Insert signal is at the low level, the Data signals are not transmitted to the memory. Instead, the output of the memory is fed back to its own input. Insert signal therefore controls whether or not data will be input to the memory or old information will be circulated within the memory. The memory outputs in addition to being routed back to the input multiplexer (AMD 9322) are also buffered (MG 1 & MF1) for use at the rear panel. two memories, ME-3 and MF-3 are clocked by a two phase clock system common to both units. This will be described in section 7.24 of this manual.

### 7.23 Y-Display Circuit (Schematic Part 2, Page 57)

The Y-Display Circuit functions to provide a CRT display of the memory contents. With the data stored in memory, the full contents of the memory are output during an interval of 512 microseconds. The timing relationship between each set of 8 bits must be maintained throughout the full display of the memory contents. This is accomplished by sequentially displaying each bit. For example, during 1 memory cycle bit 1 would be displayed. During the second memory cycle bit 2 would be displayed. Under these conditions the entire memory contents would be displayed each 4 milliseconds to provide a refresh frequency of 250Hz. With a reasonable CRT persistence this will provide a flickerfree display. NOTE: Because of the duty cycle limitations of conventional oscilloscopes the display circuit of this instrument has been modified slightly from what is described above. Instead of reproducing the data frame for every 8 memory cycles, an additional cycle has been added. First, visualize the Y-Display circuit without flip-flop

MF-4 in the circuit. Without this flip-flop, A-2<sup>7</sup> which is the most significant address bit would cause the binary counter MG-3 to count zero through seven and repeat itself. This action would occur at any time the address counter is operating and therefore is functional during a data display mode of operation. Counter MG-3 feeds its 3 binary outputs both to a digital-to-analog converter and to a "1 of 8 decoder" (MG-2). When the counter is at zero data bit 8 is routed through MG-2; when the counter is at the binary state 1, bit 7 is routed through the decoder; and when the counter is at the binary condition 7, bit 1 is routed through the decoder. By this technique the state of the binary counter feeds both a selected data bit to the DAC and simultaneously provides the proper offset to the display by means of the DAC.

Recalling that we are assuming that MF-4 is not in the circuit, the above description is of a circuit which would provide a 8 level stair step on the Y-output. Each major stair step portion of the display would be modulated by the data bit selected for that step. The amplitude adjustment is controlled by the Y-gain potentiometer, R180. height of the bit is controlled by the bit adjust potentiometer, R179. Recalling the earlier comment that the fundamental display cycle described above has been modified because of the limitation on duty cycle for most oscilloscopes, we must now expand our circuit description by a small amount. The purpose of flip-flop MF4 in the Y-Display Circuit is to force the stair step to remain at its zero level for two consecutive memory cycles. This is accomplished by using the overflow from the binary counter to clear the flip-flop MF-4 by means of its direct clear input. When the flip-flop has been cleared it will inhibit the next count from going to the binary counter by means of the gate MG-4, pin 13. The overflow from the address counter (A-2') instead sets the flip-flop MF-4 back to its normal state thereby allowing the binary counter to progress normally until it overflows the next time, at which time the sequence repeats. Now if we were to take a look at the Y-output we would see again a stair-step but this time it would remain on the lower step for twice as long as it remains on each of the other positions. This technique allows the 810-D to be used with any oscilloscope without in any way violating the duty cycle capabilities of that oscilloscope.

## 7.24 Clock Drive Circuit (Schematic Part 2, Page 57)

With a shift register memory it is necessary to provide shift or clock pulses. These pulses read old data from the memory, write new data into the memory and shift data through the memory. The memories employed in this unit require a two-phase clocked system. Referring to sheet 2 it will be noted that the memory in the data

circuit have clocks designated as  $\emptyset$  1 and  $\emptyset$  2. The clocks alternate words in the memory such that Ø 1 would write a word in the memory and  $\emptyset$  2 would be used at the next word. It is the purpose of the clock drive circuitry to generate these clock pulses. Before explaining the circuit in detail, it is well to remember that the clock pulses to the shift register memories are negative going pulses originating from +5 Volts and falling to a low level of about -12 or -13 Volts. These clock pulses have a width of about 80 nanoseconds, with data being read from the memory on the leading or negative going edge of the pulse and new data being written into the memory on the positive or trailing edge of the pulse. In observing the clock drive circuit, it will be noted on the right hand portion of the circuit that there are three fundamental inputs to the circuit. These are: 1. Clock pulses are generated by the Time Base during Record operation at high speed (interlace). 2. Output mode, with the Command signals from the output interface providing the timing for the memory. 3. At 2 µsec intervals when either the Display mode or Record at low speeds (interlace) is the mode of operation. There are no other methods by which a clock signal can be generated. To repeat, clock signals are generated in the Record mode by the Time Base signal at high speeds and by the  $2\mu sec$  time base at low speeds. They are generated by the Command pulse in the Output mode, and in the Display mode they are generated by the 2µsec time base. The active signal is called Memory Clock and causes the edge triggered flip-flop MG-5 to toggle as a binary counter. The binary counter divides the Memory Clock rate by 2 and on each edge of the flipflop output causes a clock pulse to be generated. quently, for each Memory Clock signal there is a clock pulse generated, but each clock pulse is 1/2 of the rate of the Memory Clock.

The clocks themselves are generated by a monolithic clock driver MH0013C in location ME-4. The inputs to this clock driver on pins 2,4 and 6,8 are driven from the collectors of grounded base transistors Q1 and Q2. Emitter current is injected into each transistor from MF-5 which drives the respective emitter through a 330 ohm resistor. The signal from the gate MF-5 is generated by a shaping circuit connected back to MG-5 the binary divider for the memory clock. The current pulse from transistors Q1 and Q2 is approximately 80 nanoseconds wide and is the primary determining factor for the memory clock pulse width. Additional speed-up drive is given to the clock drive circuit by the feed forward capacitors from the outputs of the memory clock flip-flop to the inputs of the clock driver. These feed forward capacitors serve to overcome the circuit delays associated with the shaping gates and the transistors.

The only critical timing associated with the memory clock drive circuit occurs in the record mode at the fastest recording rate -10MHz. At this rate it is essential that the back edge of a clock pulse is terminated before a data change occurs at the memory inputs from the next Time Base Pulse. The design provides for approximately 25-30 nanoseconds of time from the back edge to the change of new data in the memory. This should more than provide enough data hold time for the memory device.

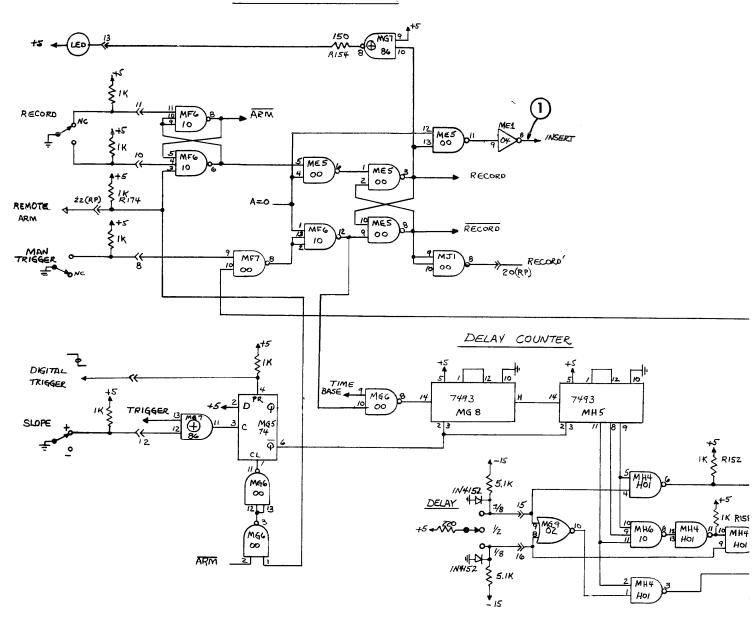

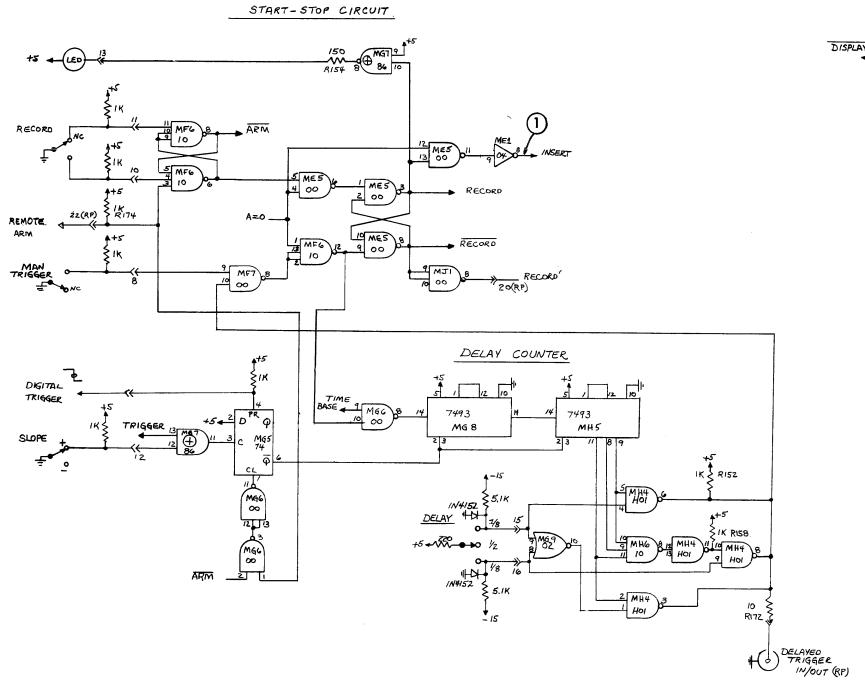

## 7.25 Start-Stop Circuit (Schematic Part 3, Page 58)

The record process is normally started with the front panel momentary switch labeled, Record. The process can also be started with the Remote Arm signal located on pin 22 of the rear panel connector. The front panel switch utilizes a de-bouncing flip-flop consisting of two parts of the gate In either the manual start or the remote start a positive going signal is generated at pin 5 of gate ME-5. If the signal at pin 5 of ME-5 is positive when A=0 (address = zero) is positive then a negative signal will be generated at pin 1 of ME-5 causing the Record flip-flop to be set with the Record signal at a high level. As we have seen earlier when the Record signal is at a high level the memory clock drive circuit produces memory clock pulses at a rate determined by the time base in the non-interlace mode of operation and at the 2 microsecond rate and the interlace mode. We will also note in the start stop circuit that the insert signal is positive if the record flipflop is set and if A=0 is also high. As explained in section 7.29 we shall see that A=0 constantly during the Record, interlace mode of operation. During Interlace operation, new data is properly input to the memory only when A=0 is high.

If we assume that the unit was operating in the Display mode prior to pushing the Record button then it is apparent that there will be a latency of up to 512 microseconds before A=0 occurs to set the flip-flop. Since the operation has been started manually this latency period is of little consequence. In the event that the record function has been started by means of the Remote Arm signal, it will be necessary for the Remote Arm signal to be held at the low level for a minimum of 512 microseconds or until the interface detects that the Record signal located on pin 20 of the rear panel connector has gone to the high level. The record process is terminated by a low signal on either pin 9 or pin 10 of MF-7. The signal on pin 9 is generated by the front panel momentary switch, Manual Trig-The signal on pin 10 is generated from the delay ger. counter which will be described in the next section. If either of these signals goes low, a high level is generated

at pin 12 of MF-6 resetting the Record flip-flop and terminating the record process.

## 7.26 Delay Counter (Schematic Part 3, Page 58)

The normal process of stopping the recording operation is by means of a Trigger. As seen in the lower portion of Sheet 1, the Trigger signal can come by means of the Trigger input with its separate threshold detector, if External triggering is selected by the front panel control; or it can come via input number 8 with the common threshold, if Internal triggering is selected. In either of these cases a signal called Trigger is generated. Trigger will be in phase with the signal which generated it. In other words trigger will go high as the generating signal crosses the threshold in the positive direction and trigger will go low when the generating signal crosses the threshold going in the low direction. Trigger is one input to the "exclusive or" gate MG-7. The other input comes via the front panel Slope control. If Slope is set positive then Trigger going positive will generate an activating signal into the clock input of the edge trigger flip-flop MG-5. If Slope is set to the negative position then Trigger going low will generate an activating signal into this same input of the flip-flop. Since the D input is held positive the positive transition of pin 3 will cause the Q output to go high and the  $\overline{Q}$  signal to go low unless the  $\overline{arm}$  or Record signals are holding the flip-flop in the reset condition.

Backing up for just a moment, we can visualize a situation where a manual record operation is started and where input conditions are such that triggers would be continuously generated. Under such a condition the record process would be started and stopped almost immediately. However, the memory contents (old information) would not be completely flushed out and the user would be presented with a scrambled set of data consisting of a mixture of both old By utilizing the arm signal to prevent and new data. Triggers from being accepted during the time that the Record push-button is activated we can assure that old data is completely flushed out of the memory during the fast record rates. Picking up where we left off, if we assume that a Record operation has been started and that a Trigger is generated then flip-flop MG-5 will be set. Setting of MG-5 will remove the DC resets on the 8 bit binary counter consisting of MG-8 and MH-5. This reset comes from the  $\overline{Q}$  of MG-5 and goes to pins 2 and 3 of MG-8 and MH-5. With the flip-flop set to the true level the Time Base signal is counted in the Delay Counter. When the selected number of counts have been accumulated in the binary counter a Delayed Trigger pulse will be generated at the rear panel and simultaneously will feed upward on the Schematic into

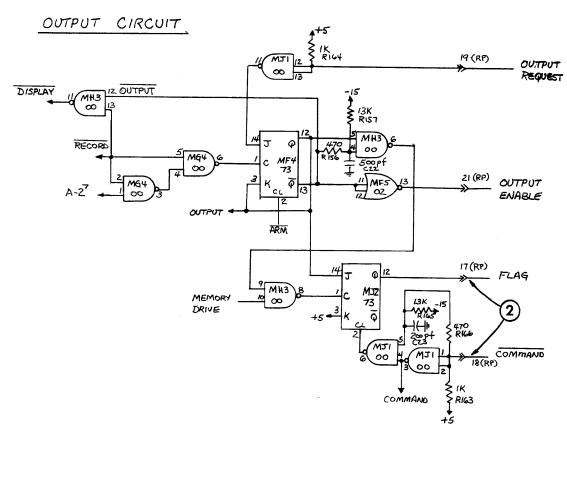

Display is generated when neither the Output nor Record modes of operation are selected. This is controlled by gate MH-3. The Output mode is selected when the flip-flop MF-4 has been triggered such that pin 12 is at the high level. Output is obtained only upon the request from the external interface. When Output is requested, pin 19 of the rear panel connector is pulled to a low level. raises pin 14 of MF-4 to a high state, such that when the signal on pin 1 of MF-4 goes to a low level, the flip-flop will be set such that pin 12 is high. If we assume that the unit is operating in the Display mode such that Record is at a low level, we can talk our way through the circuit description. Under these conditions the signal A-2' is occuring every 512 microseconds (the total cycle time of the memory). If at some arbitrary time the Output Request signal signal is pulled low, then within a period of 512 microseconds A-2' will transmit a negative going edge to pin 1 of MF-4. This will cause the flip-flop to be set, and at that time the Output Enable signal on pin 21 of the rear panel connector will go to the high level. This is a signal to the output device that the Output Request signal can now be returned to its normal high level. At the same time that Output goes high then a negative pulse is generated at pin 6 at MH-3. This negative pulse appears as a positive pulse on pin 1 of MJ-2, the Flag flip-flop. The trailing edge of the positive pulse on pin 1 of MJ-2 causes the Flag signal on pin 12 to go high. The positive transition of Flag signal should be utilized by the interface device to strobe data from the model 810-D into buffer storage of the peripheral device.

When the peripheral device is ready for the next word of information, the Command signal should go to the low level. This leading edge of the negative going Command signal generates a pulse in the two gates of MJ-1 to clear the Flag flip-flop. The Flag signal will go to the low level upon the leading edge of Command. Also on the leading edge of Command a new word of information will be clocked from the memory as described in the earlier description of the clock drive circuit. Approximately 100 nanoseconds after the leading edge of Command a Memory Drive occuring on pin 10 of MH-3 will clock the Flag signal back to the high level, indicating to the interface device that new data is available. This process of Command-Flag is known as a hand shake routine and can continue word for word until all 256 words of data have been clocked from the 810-D. At that time, the most significant address bit A-2' will go low on pin 1 of MG-4, and will be transmitted as a negative going signal on pin 1 of the Output flip-flop MF-4. This will return the Output Enable to the low level and place the unit back into the Display mode.

the start-stop circuit through pin 10 of MF-7. As described earlier a signal on this pin occuring in synchron-ization with A=0 will terminate the record process. When Record goes low, the Delay Counter will stop counting because Record on pin 10 of MG-6 prevents the gate from transmitting Time Base signals to the counter.

It is important to keep in mind that once the recording process has been started, valid data is in the memory at all times. The Trigger merely tells the unit when to stop recording. This is the reverse operation from many conventional instruments. However, it is very significant to point out again that the model 810-D has the capability of looking in front of the Trigger signal and thereby achieving a negative time delay. When we select a delay we are in effect determining the amount of data to be observed prior to or in front of the Trigger. If a Delay of 7/8 is selected then this is interpreted as a desire to have 7/8 of the recorded data in front of the Trigger. Consequently, upon receipt of a trigger 32 Time Base pulses will be counted before the Delayed Trigger signal is generated to stop the recording process. Likewise if a delay of 1/2 is selected then 1/2 of the data recorded is before the trigger occured and the trigger allows 128 time base pulses to be recorded before stopping the recording process. Similarly, if a Delay of 1/8 is selected, then only 1/8 of the stored data occured prior to the trigger and 224 time base pulses are counted after the Trigger. The Delayed Trigger is routed to the rear panel of the unit to be used for multiple unit connections. It normally is not used when a single unit is being operated. The Delayed Trigger as described earlier stops the recording process by feeding through gate MF-7 and MF-6 to reset the record flip-flop. Trigger on pin 45 of the rear panel connector is available for this function. The digital trigger is normally held at a high level and upon going to a low level activates the Delay Counter. From this point, the Delay Counter functions in an identical manner as described above.

When the recording process is stopped by means of the Manual Trigger, the delay circuit is bypassed. This bypass feature is intentionally provided for slow recording speeds where the operator may see a pattern of interest on the CRT display and make the decision to stop data recording. With the delay eliminated he does not have to take into consideration the additional data recording that would otherwise occur if the Delay Counter was active.

## 7.27 Output Circuit (Schematic Part 3, Page 58)

The Output Circuit is used only when an interface device is used in conjunction with the model 810-D to transfer the contents of the 810-D to an external device. First, note that at the left portion of the Output Circuit the signal

NOTE: In the previous discussion two significant items were omitted. 1) After the external interface has detected Output Enable going to the high state, a period of no longer than 500 microseconds must elapse before the first Command signal is generated. Furthermore, there must not be a period greater than 500 microseconds elapse between successive Command signals. Should the time between these signals become greater than the specified period, the output data may not be valid. 2) Once the output mode has been entered, a minimum of 256 Command pulses must be generated. Otherwise, the unit will be left in the output mode with no way to exit this mode, other than by means of pushing the Record pushbutton which generates Arm signal on pin 2 of the Output flip-flop thereby resetting this flip-flop.

A second mode of operation would occur if the Output Request is initiated during the Record process. This would be used in those conditions where an automatic data outputting process is to be initiated each time the device is triggered. If we assume that the Record is in process then the Record signal on pins 2 and 5 of MG-4 is at a low level. In addition, pin 14 of MF-4 is assumed to be at the high level because the Output Request line is being held low. Finally, A-2 will either be in the low state or will go to the low state just prior to ending the record process. In either case pin 4 of MG-4 will be high when  $\overline{\text{Record}}$  on pin 5 goes high. This will cause a negative transition at pin 6 at MG-4 and pin 1 of MF-4 forcing the Output flip-flop to change to the Output mode. From this time on, the circuit functions as described earlier and at the end of Output the unit will revert to the Display mode.

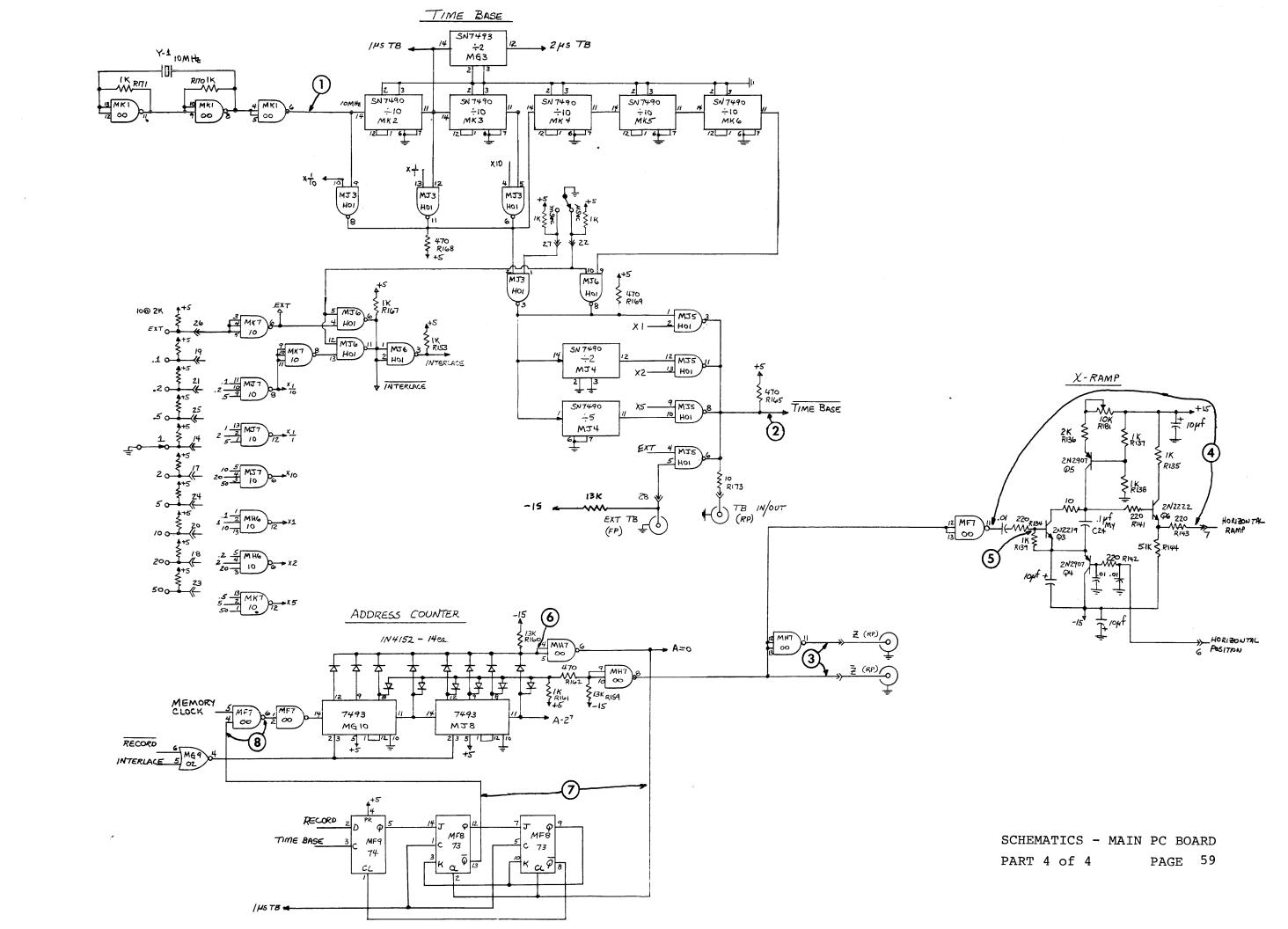

## 7.28 Time Base (Schematic Part 4, Page 59)

The Time Base Circuit of the unit provides both the periodic clock for circulating the memory in the Display mode of operation which is fixed at 2 microseconds per word and the selectable clock rate used for strobing data into the memory. Before describing the Time Base circuit it should be noted that dynamic shift registers have both a high frequency and a low frequency limitation. In the model 810-D the memory devices that are utilized have a quaranteed upper frequency of operation of 10MHz, and this is the upper rate at which these devices are used in the instrument. The low frequency limitation however, does not allow the instrument to run as slowly as might be desireable for some applications. Under these conditions the memory must be clocked at a much higher rate than the rate at which new data is input to the memory. For this unit we define two types of recording: 1. Interlace recording - Interlace recording occurs when the data input rate is slower than the

actual clock rate. This occurs at data rates that occur below the minimum specified operating frequency of the shift register memory. The model 810-D utilizes devices which are guaranteed to operate as slowly as 1 Khz.

2. Non-interlaced recording - This applies to recording rates at which the memory is clocked at precisely the same frequency at which new data is entered into storage. This occurs for all clock intervals shorter than 1 millisecond.

As we shall see in section 7.29, the Address Counter does not operate at the non-interlace recording speeds and consequently there is no data display on the CRT monitor attached to the unit. Referring to the Time Base Circuit, it will be noted that the basic clock is derived from a 10MHz crystal oscillator connected into a feedback circuit utilizing two parts of gate MK-1. The 1  $\mu sec$  Time Base and the 2  $\mu sec$  Time Base are derived by dividing the 10 MHz crystal oscillator down to 1MHz by decade divider MK-2. This produces a 1MHz time base signal at pin 11 at MK-2 which is further divided by a factor of 2 by the binary counter MG-3. The signal on pin 12 of MG-3 is the 2  $\mu sec$  time base utilized for clocking the memory at all Interlace recordings speeds and in the Display mode.

Referring to the switch decoding circuit shown in the middle of sheet 4, it will be observed that a very simple decoding scheme is utilized whereby 3 signals for multiplication factors of 10 are derived - these are called 1/10, 1/1, and 10. Three additional signals are generated for intermediate ranges, and these are called X1, X2, and X5. Under any internal selected conditions, two of these 6 signals will be in the high state. The other four will be in a low level. The signals which tell the unit to interlace or not to interlace are also derived from the Sample Interval switch in conjunction with the multiplier switch for microseconds or milleseconds operation. The decoding for the Interlace control is such that the Interlace signal on pin 3 of MJ-6 is at a high level when the microseconds/milliseconds switch is in the milliseconds position and the interval switch is in any position other than .1, .2 or .5.

For purposes of illustration let us take an example whereby the clock is selected to operate at 5 microseconds clock intervals. Under these conditions the signals X1/1 and X 5 will be true and Interlace will be low. We can trace a signal path from pin 6 of MK-1, the oscillator buffer gate; through MK-2 pin 11 where the frequency has been divided down to lMHz; through MJ-3 pin 11 where we maintain the lMHz rate. We will note in passing that the

1MHz rate is divided down by MK-4, MK-5 and MK-6 to a 1Kz rate on pin 9 of MJ-6. However, this signal is gated off with the microseconds multiplier switch grounding pin 10 of MJ-6. However, the millisecond position on pin 1 of MJ-3 is pulled high by the resistor on the front panel and allows the lMHz signal on pin 11 of MJ-3 to be gated through to pin 3 of MJ-3. At this point the signal has three possible paths only one of which we have selected. That is the route through the ÷ 5 portion of MJ-4 into pin 10 of MJ-5. The positive signal on pin 9 corresponds to our selection of 5 microsecond intervals. The Time Base signal on the common outputs of MJ-5 represents a pulse-train at the selected time interval. As we have seen in other parts of this circuit description, this signal is used for clocking the memory and strobing data into the input data latches. revise our example to select 5 millisecond time intervals rather than 5 microsecond time intervals, we will find that the signal at the common pin 3, pin 8 connection of the MJ-6 will be exactly 1,000 times slower than earlier. This occurs because the signal from MJ-3 pin 6, 8 and 11 is routed through the three decade counters, MK-4, MK-5 and MK-6 back into MJ-6.

If an external clock rate is selected by means of the front panel Clock Interval selector, then the input goes from the front panel to pin 5 of MJ-5. Pin 4 will be at the high level due to the selection of the External rate. At the leading edge of the External Time Base signal, Time Base will go low and after 1 additional gate delay will strobe data into the input Data Latches (Section 7.21). It is important to remember that the leading or positive going edge of the External clock is the activating edge for that signal. It is also important to note that the microseconds/ milliseconds switch must be used properly with the External clock. If the clock interval is less than 1 millisecond than the multiplier switch should be at the microseconds position. If the interval is greater than 1 millisecond than the switch should be set to the milliseconds. As seen earlier this will determine whether or not the unit operates in the Interlace or Interlace mode.