Publication Number 0117-0308-10 February 1984

K105-D LOGIC ANALYZER

USERS MANUAL ADDENDUM

**Z80 DISASSEMBLER**

# PREMIAN

Gould Inc., Design & Test Systems Division 4600 Old Ironsides Drive Santa Clara, CA 95050-1279 Telephone: (408) 988-6800 TWX/TELEX # 910-338-0509

Copyright • 1984. No part of this publication may be reproduced without written permission from Gould Inc., Design and Test Systems

Division. Printed in U.S.A.

# CONTENTS

| Chapter                                          |                                                         | Page                     |

|--------------------------------------------------|---------------------------------------------------------|--------------------------|

| 1                                                | INTRODUCTION INTRODUCTION                               |                          |

| 2                                                | SPECIFICATIONS PHYSICAL DIMENSIONS AND WEIGHT           | 2-1                      |

| 3                                                | DISPLAYS  SCREEN DISPLAYS OF PREPROGRAMMED SET UP MENUS | 3-1                      |

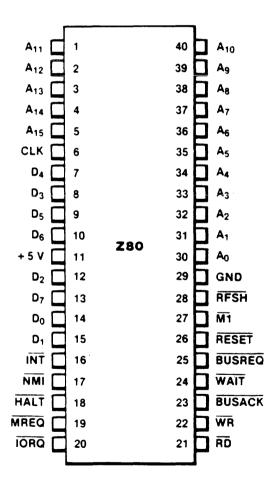

| Figure<br>1-1<br>1-2<br>3-1<br>3-2<br>3-3<br>3-4 | Z80 Microprocessor Pinout Diagram                       | 1-3<br>3-1<br>3-2<br>3-3 |

| 1 - 1                                            | Microprocessor-To-Logic Analyzer Connection Data        | 1_2                      |

INTRODUCTION

### INTRODUCTION

This addendum provides the user with specific information on the Z80 target microprocessor Disassemblers. Included in the addendum is a microprocessor pinout diagram, microprocessor-to-logic analyzer connection data, screen displays of the preprogrammed menus, a screen display of captured data in the disassembled format and special notes on the disassembler/logic analyzer.

Figure 1-1. Z80 Microprocessor Pinout Diagram

Table 1-1. Microprocessor-To-Logic Analyzer Connection Data

| Z80<br>SIGNAL                                                                                      | Z80<br>PIN                                                             | K105-D PIN<br>ASSIGNMENT                                                                                                      | RTE PIN<br>ASSIGNMENT                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL  A11 A12 A13 A14 A15 CLK D4 D3 D5 D6 +5V D2 D7 D0 D1 INT MREQ IORQ RD WR BUSACK WAIT BUSREQ | PIN  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 | ASSIGNMENT  C3 C4 C5 C6 C7 BK A4 A3 A5 A6 NOT CONNECTED A2 A7 A0 A1 D6 C7 D4 D2 D1,CJ D3,BJ DJ NOT CONNECTED D5 NOT CONNECTED | ASSIGNMENT  J1-45  J1-47  J1-49  J1-51  J1-53  J1-78  J1-69  J1-67  J1-71  J1-73  NOT CONNECTED  J1-65  J1-75  J1-61  J1-63  J1-52  J1-44  J1-42,57  J1-46,80  J1-58  NOT CONNECTED  J1-50  NOT CONNECTED |

| WR<br>BUSACK<br>WAIT                                                                               | 22<br>23<br>24                                                         | DJ<br>NOT CONNECTED<br>D5                                                                                                     | J1-58<br>NOT CONNECTED<br>J1-50                                                                                                                                                                           |

| RFSH<br>GND<br>A0<br>A1<br>A2<br>A3<br>A4                                                          | 28<br>29<br>30<br>31<br>32<br>33<br>34                                 | NOT CONNECTED GND A-B-C-D SECT. B0 B1 B2 B3 B4                                                                                | NOT CONNECTED J1-1,2,37,38,59,60 J1-62 J1-64 J1-66 J1-68                                                                                                                                                  |

| A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10                                                            | 35<br>36<br>37<br>38<br>39<br>40                                       | B4<br>B5<br>B6<br>B7<br>C0<br>C1<br>C2                                                                                        | J1-70<br>J1-72<br>J1-74<br>J1-76<br>J1-39<br>J1-41<br>J1-43                                                                                                                                               |

NOTE: The J1 Scrambler board is equivalent to the J7 Motherboard.

#### ATTACHMENT TO A TARGET SYSTEM

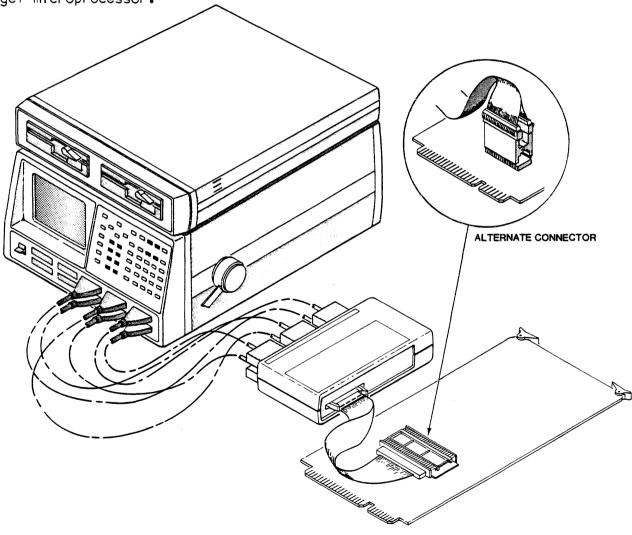

Figure 1-2 illustrates a typical RTE (Real Time Execution) to target system connection.

The RTE probe connectors are labeled to identify the input probe that must be plugged into the specific connector. The user shall remove the probe tips and install the probes, label up, into the RTE connectors. When connecting the microprocessor dip-cable into the RTE, special attention should be given to the keyed position of the connectors. The user should also ensure that pin 1 of the dip-clip is aligned with pin 1 of the microprocessor when connecting to the target microprocessor.

Figure 1-2. Typical RTE to Target System Connection

NOTE: Figure 1-2 shows one of several possible connections of the RTE to a target system. As the configuration of the microprocessor pinouts change, the RTE to target system interface may also change.

# ATTACHMENT TO A TARGET SYSTEM

\*

\* CAUTION

\*

\* In the event the microprocessor on your

\* target system is soldered to the board and

\* the alternate connector is being used, there

\* is the possibility of inducing reflective

\* noise into the test signals. To eliminate

\* this problem, we recommend varying the

\* threshold voltage levels beyond noise levels.

\*

#### LOADING THE DISASSEMBLER

The following procedure provides step-by-step instructions for loading the Disassembler:

- a. Enter the Disk Operating System screen.

- b. Gently insert the disk into Drive B, with the disk slot toward the rear of the unit and the label up. Next, lock the disk in place with the drive latch handle.

- c. Depress function key F3 to display the B directory.

- d. Depress 1 to select the Recall function.

- e. Use the right arrow cursor to enter the filename field and then use either the up or down cursor to select the Disassembler.

- f. Depress function key F4 to load the Disassembler.

- g. Depress the Format key to enter the Format screen.

- h. Depress 6 and then DATA to enter Disassembler mode.

#### **SPECIFICATIONS**

#### PHYSICAL DIMENSIONS AND WEIGHT

Height - 2.25 inches (5.7 cm) Width - 9.5 inches (24.1 cm) Depth - 5.5 inches (14 cm)

Weight - 1 lb. 11 oz. (.77 kg) with flat cable, device clip and probe printed circuit board

#### **ELECTRICAL CHARACTERISTICS**

# Loading (Signal Inputs)

Input Resistance - 1 megohm  $\pm 2\%$  to threshold (-1.4 volts)

Input Impedance - 150 ohms (approximate)

Typical Rise/Fall Distortion - heavily dependent on negative drive of micro processor and its support devices. The 8086/8088 microprocessor slows approximately 5 nanoseconds on edge rates.

# Loading (Ground/Reference Input)

Input Resistance - Less than 1 ohm referenced to target system ground.

Ground Difference Immunity -  $\pm$  0.25 maximum volts between logic analyzer ground and target system ground.

# Reflected Noise Into Target System

Probed with Dip Clip or Circuit Board Socket - heavily dependent on target system ground. Typically, the system noise is reduced due to slower edge rates caused by probe load. This condition occasionally masks the problem being pursued.

DISPLAYS

# SCREEN DISPLAYS OF PREPROGRAMMED SET UP MENUS

Figures 3-1 through 3-4 illustrate the preprogrammed setup menus downloaded from disk to the K105-D. Figure 3-4 illustrates the Disassembled Data. When in the Disassembled Data display, sequential depression of the SHIFT and V keys causes the software version number for the disassembler to be displayed.

|                                                                          | SET UP                                        | MAIN FORMAT |                      |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------|-------------|----------------------|--|--|--|

| DATA FORMAT                                                              |                                               |             |                      |  |  |  |

| RADIX L                                                                  | ADDR                                          | STATUS      | DATA                 |  |  |  |

| SECTION                                                                  | CCBB                                          | ממממממממ    | AA                   |  |  |  |

| INPUTS                                                                   | 7373<br>6262<br>5151<br>4 <b>0</b> 4 <b>0</b> | 76543210    | 73<br>62<br>51<br>40 |  |  |  |

| DATA INPUTS DF-D8 D7-D0 CF-C8 C7-C0 BF-B8 B7-B0 AF-A8 A7-A0 CLOCK INPUTS |                                               | HRESHOLD    |                      |  |  |  |

| (FI)→DATA FORMAT, (FZ)→TOP THRESHOLD MEMORY=M MAIN MAIN                  |                                               |             |                      |  |  |  |

Figure 3-1. Disassembler Data Format Set Up Menu

SCREEN DISPLAYS OF PREPROGRAMMED SET UP MENUS (contid)

```

SET UP MAIN CLOCKS

CLOCK SOURCE

MASTER CLOCK

SECTION D - MANAGEMEN

SECTION C - SAMPLE

ON BRIBERS

CLIPETICAL D. CARRESTORMA

THE PROPERTY OF THE PROPERTY O

on equalization

SECTION A - SAMPLE

EXTERNAL CLOCK COMBINATION DEFINITIONS

MAME:

CLOCK INPUTS:

---

---

2277

MEMORY=M MAIN

MAINERDY

```

Figure 3-2. Clock Set Up Menu

# SCREEN DISPLAYS OF PREPROGRAMMED SET UP MENUS (contid)

SET UP MAIN TRACE

LVL COMMAND SEQUENCE:

0: TRACE UNTIL SAMPLE = ENABLE

1: TRACE UNTIL SAMPLE = TRIGGER

2: LINK ON ENTRY TO LEVEL

TRACE FOR 00512 CLOCKS

PATTERN DEFINITIONS: NAME: ADDR STATUS DATA 00 ENABLE = XXXXXXXXXXXX 01 TRIGGER =XXXX XXXXXXXX XX 02 =XXXX XXXXXXXX F 1

ED→TOP CMD, ED→TOP PTRN MEMORY=M MAIN

MAIN=RDY

Figure 3-3. Trace Control Set Up Menu

NOTE: In disassembler mode, the trace control patterns are formatted into address, status and data. When the status field is selected as the active field, the possible choices are the status conditions of the processor as follows:

(0) READ (5) HALT (1) WRITE (6) ACK (2) INPUT (7) INT (3) OUTPUT (8) NMI (4) FETCH

In Edit mode, status bits can be edited on a bit-by-bit basis. "X" selects all don't cares.

# SCREEN DISPLAYS OF PREPROGRAMMED SET UP MENUS (contid)

|                                                    | <b>Z</b> 8 <b>Ø</b> | DISASSEMBLE                 | F                                   | CLK=       | 50 | nSEC                                    |

|----------------------------------------------------|---------------------|-----------------------------|-------------------------------------|------------|----|-----------------------------------------|

| S=XXXX<br>FRAME ADDR<br>C 436 <b>080</b> A         |                     | C3020B<br>OBJ CODE          | MNEMO                               | 0802       |    | <b>X</b><br><u>L</u><br>1               |

|                                                    | RITE<br>RITE        | F5<br>27<br>20              | PUSH                                | AF         |    |                                         |

| 442 <b>080</b> 3<br>444 2700 IM                    | NPUT                | DBDC                        | IN                                  | A. (DC)    |    | 1.<br>1                                 |

|                                                    | EAD<br>EAD          | F 1<br>20<br>27             | POF                                 | AF         |    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|                                                    | UTPUT               | U503<br>D3DC<br>2A          | OUT                                 | (DC),A     |    | 1<br>1<br>1                             |

| 453 <b>080</b> A<br>456 <b>080</b> 2<br>457 FF8F N | RITE                | C3 <b>020</b> B<br>F5<br>2A | JP<br>PUSH                          | ØBØ2<br>AF |    | 1<br>1<br>1                             |

| 458 FF8E WF<br>459 <b>0</b> 8 <b>0</b> 3           | RITĒ<br>MPUT        | DEDC<br>PEDC                | IN                                  | A. (DC)    |    | :.<br>1<br>1                            |

| 462 <b>0</b> B <b>0</b> 5<br>463 FF8E RE           | EAD<br>EAD          | F1<br>28<br>2A              | P'OF'                               | AF         |    |                                         |

| CONTROL=0436<br>F1)+PG UP F2+P<br>MEMORY=A MAIN    | PG DOWN F3          | .023 F<br>]+DSPLY OBJ       | ? — [] == +<br>[ <b>F4</b> ] → [] § | FLY MME    |    | i ys)<br>IICS<br>RDY                    |

Figure 3-4. Captured Data in Disassembled Format

#### NOTES:

- 1. After the disassembler data format, and clock select menus of the logic analyzer are pre-programmed, the trace control selections must be made by the user before making a recording. The trace control selections determine exactly which portions of the data stream are recorded or ignored.

- 2. Although displayed, the sample labeled "SAMP" is not decoded.

- 3. If the disassembler is loaded and active, and an additional disassembler is to be loaded, always return to the Data Format screen to ensure the necessary tables are set up.

- 4. The SEARCH and COMPARE keys are not active in the Data Display Screen. The Edit mode can be used to change the search word. After leaving Edit mode, the NEXT and PREVIOUS keys locate target data in memory. If the search word is not active, the NEXT and PREVIOUS keys update the display to the next or previous trace level transition.

- 5. Depression of the F3 function key changes the display of recorded information. Code is not disassembled, but recorded information is displayed from the control cursor (C) position to the end of memory as frame number, address, status and data.

- If recorded data is displayed in object format, depressing the F4 function key invokes the disassembly process for data from the control cursor to the end of memory.

- 6. Illegal instructions are displayed as ???.

- 7. The disassembler is first downloaded from disk to the K105-D and the disassembler format is selected. The trace patterns are then configured as desired.