# 22A PROM PROGRAMMER

10-990-0003 REV H Applies to configuration 990-0003-007

**APR 84**

Copyright © Data I/O Corporation, 1984. All rights reserved.

| assumes no liability for errors | y attempt to ensure that t<br>s, or for any damages tha<br>ght to make changes to th | t result from use of this o | locument or the equipmen | mplete. However, Data I/O<br>t that it accompanies. |

|---------------------------------|--------------------------------------------------------------------------------------|-----------------------------|--------------------------|-----------------------------------------------------|

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

|                                 |                                                                                      |                             |                          |                                                     |

i 10-990-0003

# **TABLE OF CONTENTS**

## **SECTION 1. INTRODUCTION**

| 1.1 | GENERAL INFORMATION                                                                                                                                                 |                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.2 | THEORY OF OPERATION  1.2.1 The Copy Key  1.2.2 The Verify Key  1.2.3 The Edit Key  1.2.4 The Select Key                                                             | 1-1<br>1-3<br>1-3 |

| 1.3 | HOW TO USE THIS MANUAL                                                                                                                                              | 1-4               |

| 1.4 | SPECIFICATIONS  1.4.1 Major Components  1.4.2 Power Requirements  1.4.3 Data Translation Formats                                                                    | 1-5<br>1-5        |

| 1.5 | FIELD APPLICATIONS SUPPORT                                                                                                                                          | 1-5               |

| 1.6 | WARRANTY                                                                                                                                                            | 1-5               |

| 1.7 | SERVICE                                                                                                                                                             | 1-5               |

| 1.8 | ORDERING                                                                                                                                                            | 1-5               |

|     | SECTION 2. INSTALLATION                                                                                                                                             |                   |

| 2.1 | INTRODUCTION                                                                                                                                                        | 2-1               |

| 2.2 | DUST COVER REMOVAL                                                                                                                                                  |                   |

| 2.3 | INSPECTION                                                                                                                                                          | 2-1               |

| 2.4 | POWER CONNECTION  2.4.1 Checking the Operating Voltage  2.4.2 Line Fuse Verification  2.4.3 Grounding the Unit  2.4.4 Plugging in the Programmer and Applying Power | 2-2<br>2-3<br>2-3 |

| 2.5 | INSTALLING A SOCKET ADAPTER                                                                                                                                         |                   |

| 2.6 | SERIAL I/O OPERATIONS  2.6.1 Cabling  2.6.2 Setting Parameters  2.6.3 Hooking-up a Serial Paper Tape Reader                                                         | 2-5<br>2-6        |

| 27  | REPACKAGING FOR SHIPMENT                                                                                                                                            | 2-7               |

## **SECTION 3. OPERATION**

| 3.1 | OVERVIEW 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | POWER UP         3-1           3.2.1 General Operational Notes         3-1                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3 | POWER DOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

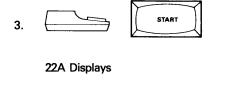

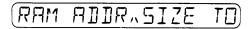

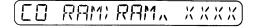

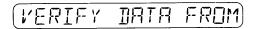

| 3.4 | BASIC OPERATIONS       3-2         3.4.1 Family Code and Pinout Codes       3-2         3.4.2 Device Insertion       3-2         3.4.3 Device Removal       3-3         3.4.4 Load RAM With Master Device Data       3-5         3.4.5 Input from Port       3-7         3.4.6 Program Device with RAM Data       3-9         3.4.7 Output to Port       3-11         3.4.8 Block Move       3-13         3.4.9 Verify Device       3-15         3.4.10 Input Verify       3-17         3.4.11 Edit       3-18 |

| 3.5 | THE SELECT KEY       3-19         3.5.1 Accessing Select Functions       3-19         3.5.2 Descriptions and Key Sequences       3-19         3.5.3 Power Down Save Feature       3-19                                                                                                                                                                                                                                                                                                                         |

| 3.6 | ERASING YOUR MOS PROMS       3-19         3.6.1 UV Lamp Specification       3-19         3.6.2 Procedure for Erasing MOS PROMs       3-19                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7 | SOURCE/DESTINATION METHOD OF SYNTAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

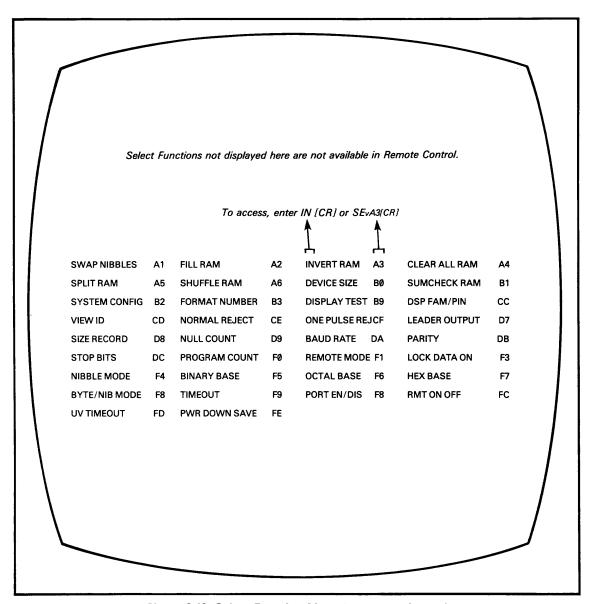

| 3.8 | STANDARD REMOTE CONTROL       3-28         3.8.1 Command Protocol       3-28         3.8.2 Command Entry       3-29         3.8.3 Inputting Parameters       3-29         3.8.4 Copy and Verify Operations       3-29         3.8.5 Edit Operations       3-29         3.8.6 Select Functions       3-30                                                                                                                                                                                                       |

| 3.9 | ERROR CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | SECTION 4. MAINTENANCE/CALIBRATION/TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.1 | OVERVIEW 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2 | MAINTENANCE       4-1         4.2.1 Cleaning       4-1         4.2.2 Inspection       4-1                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.3 | CALIE | BRATION                                                            | 4-1 |

|-----|-------|--------------------------------------------------------------------|-----|

|     | 4.3.1 | DC Calibration                                                     | 4-3 |

|     | 4.3.2 | Optional Verify-Voltage Checks                                     | 4-3 |

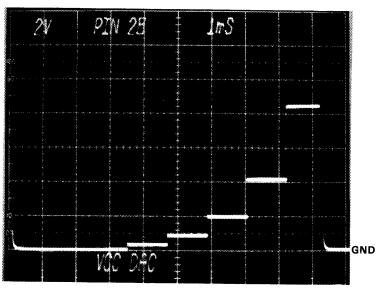

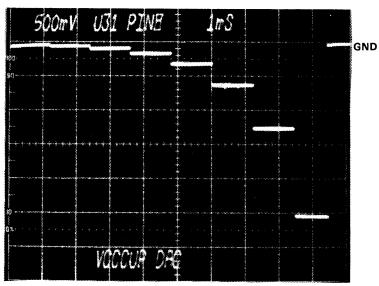

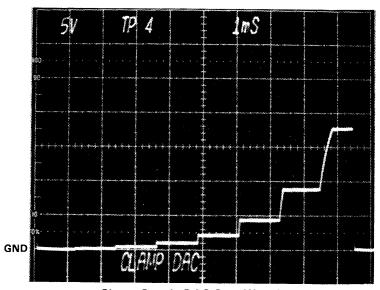

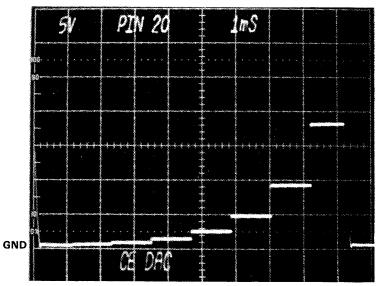

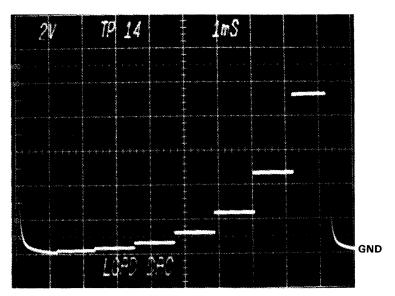

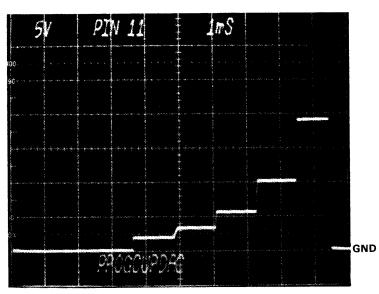

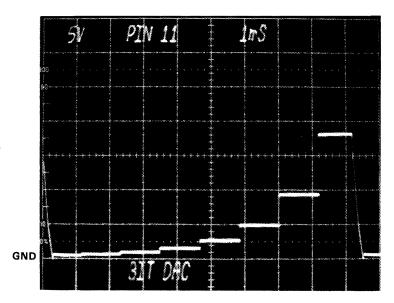

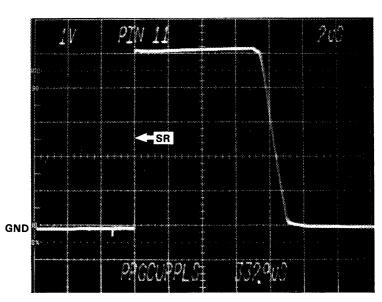

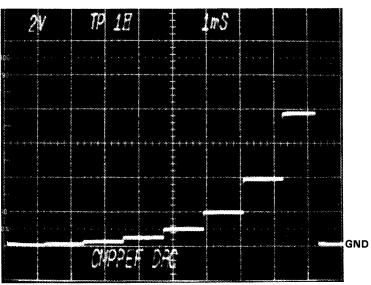

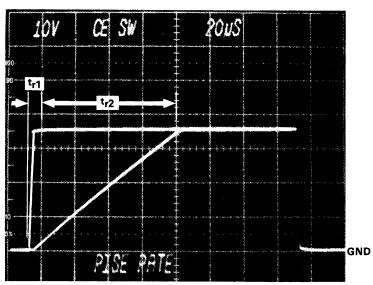

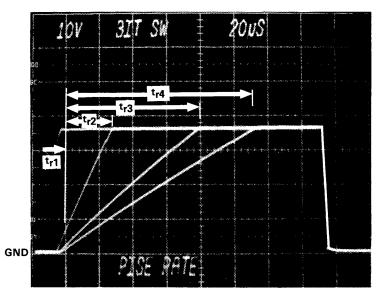

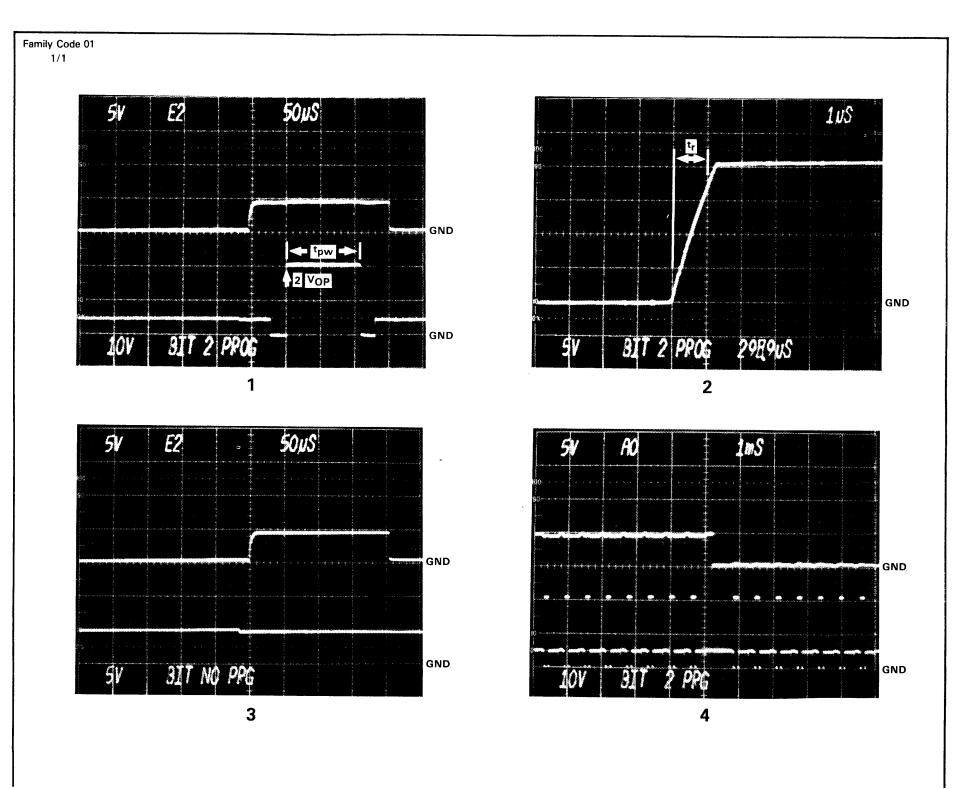

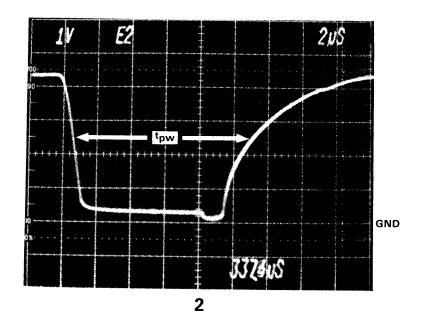

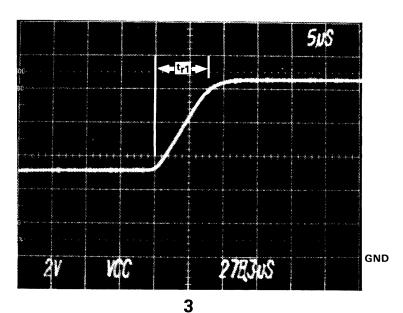

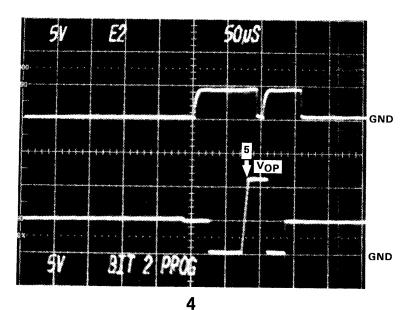

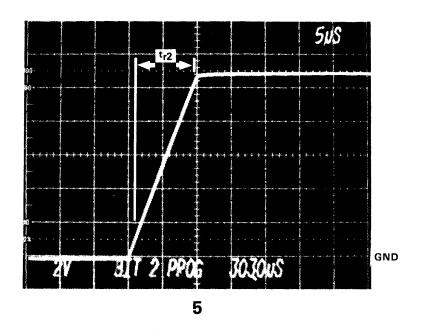

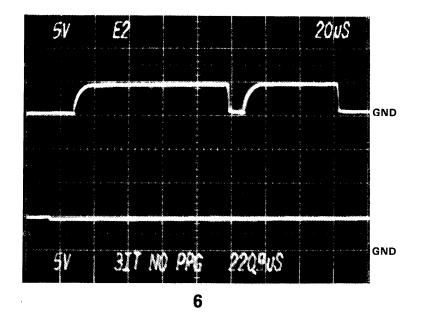

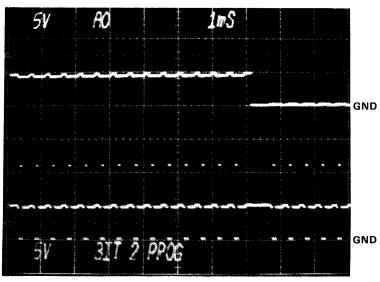

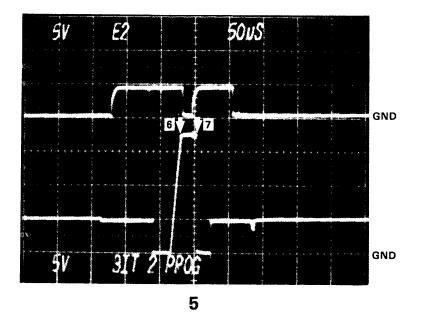

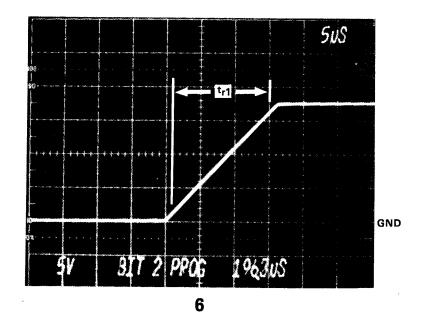

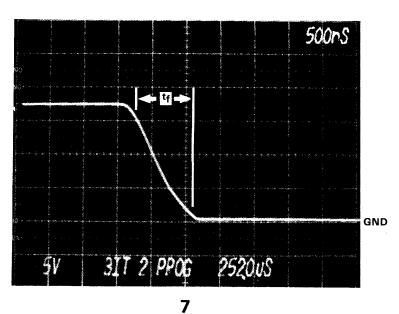

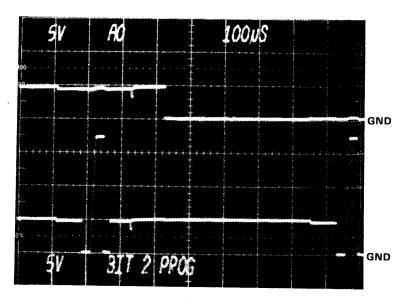

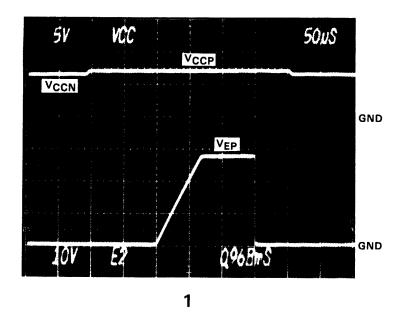

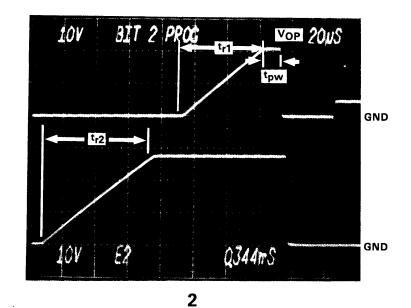

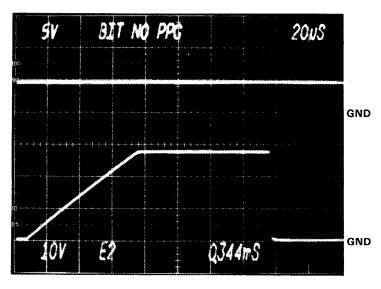

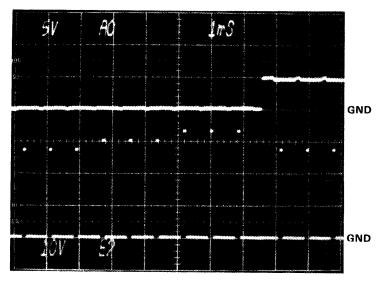

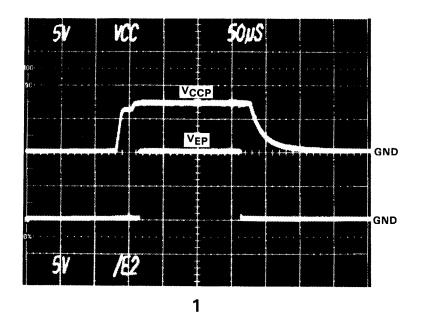

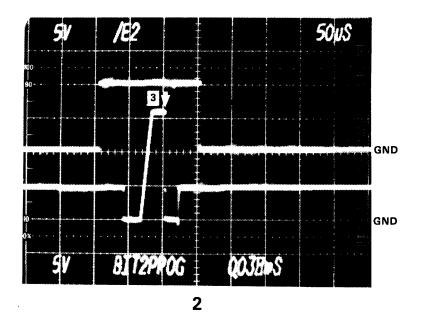

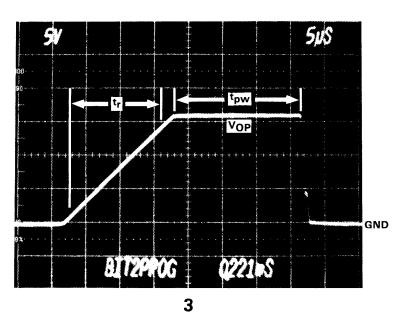

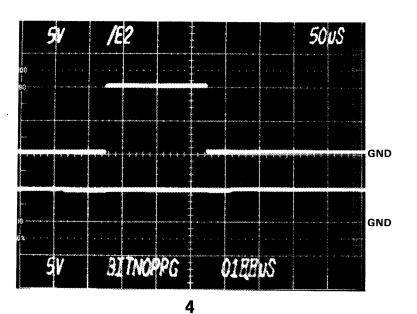

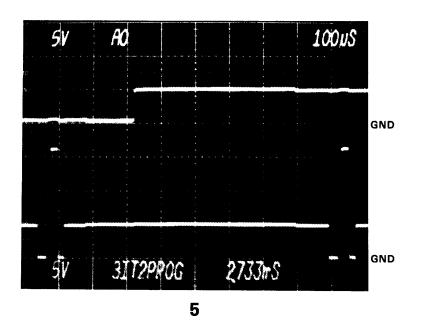

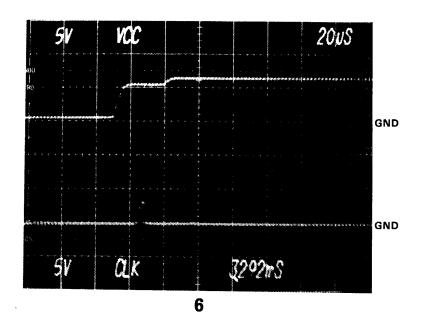

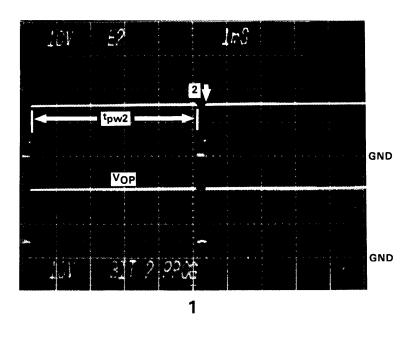

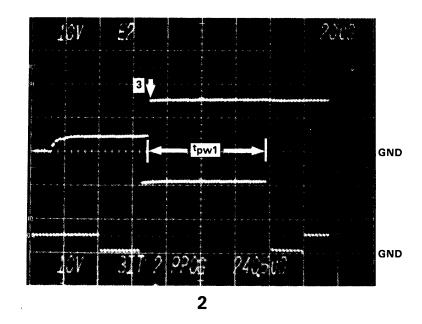

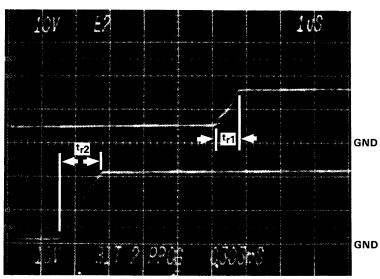

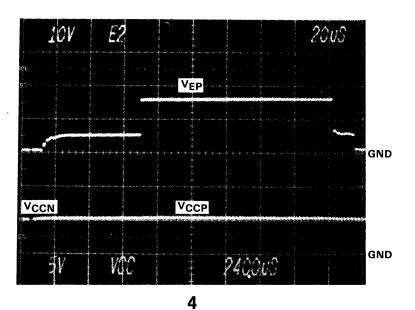

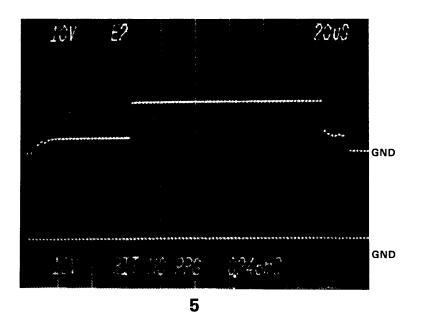

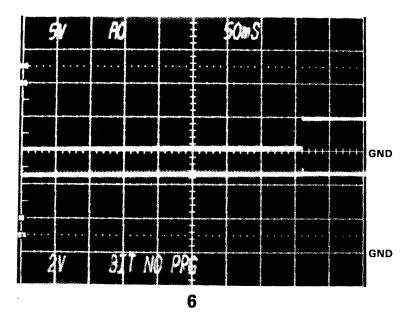

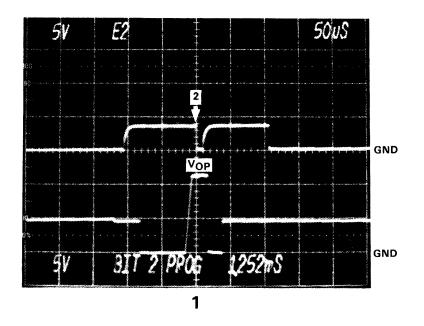

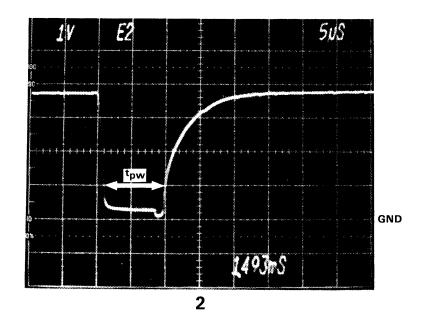

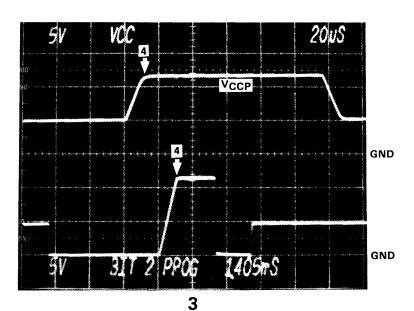

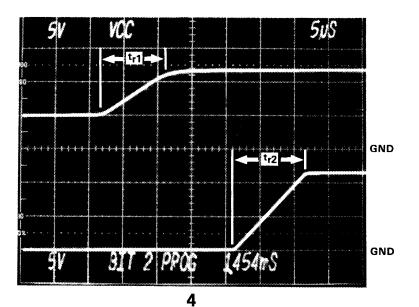

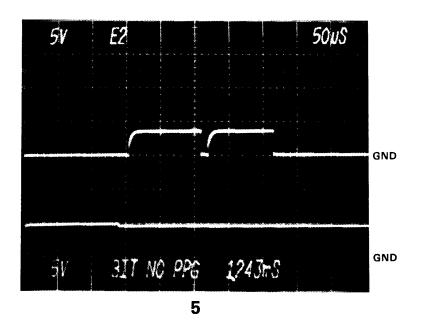

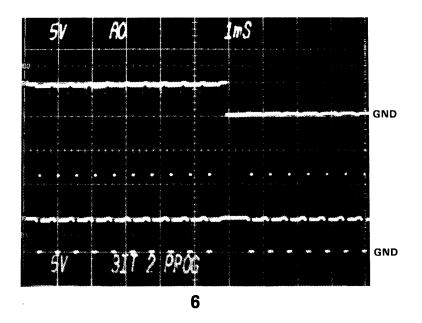

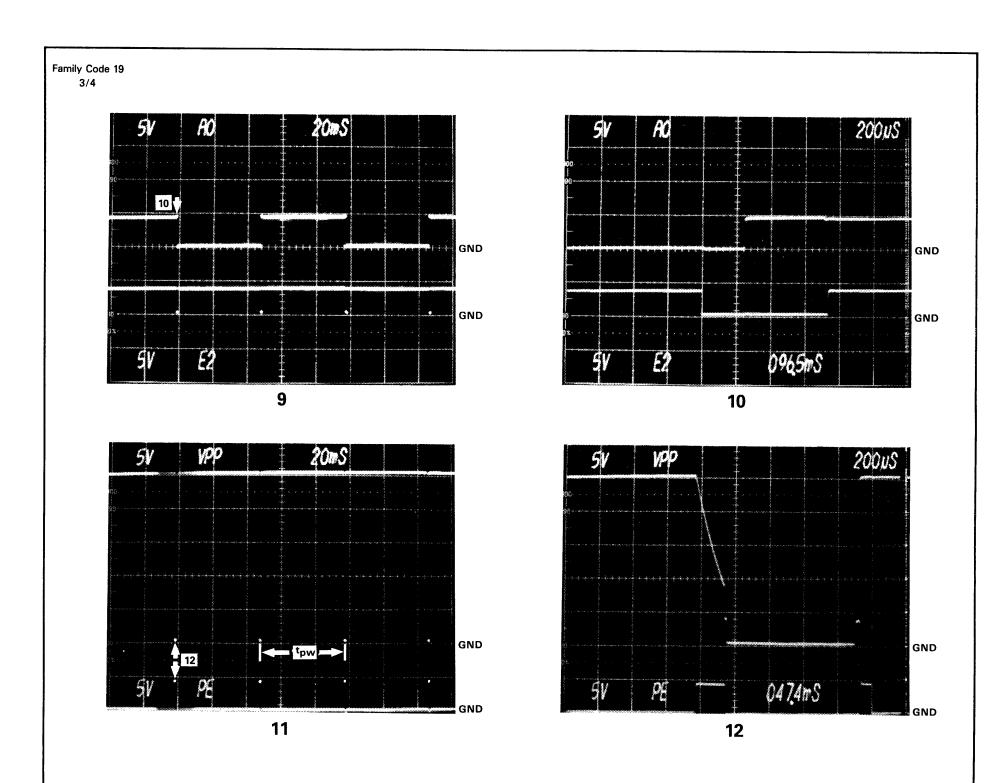

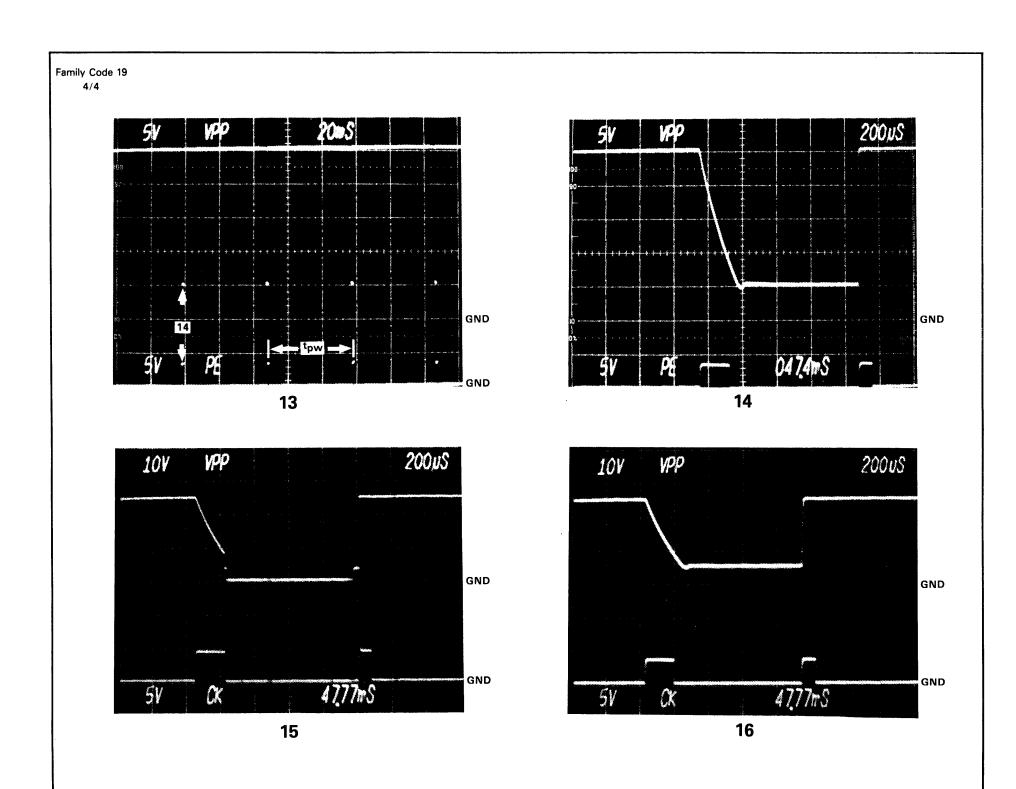

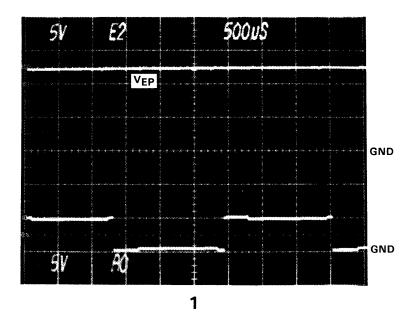

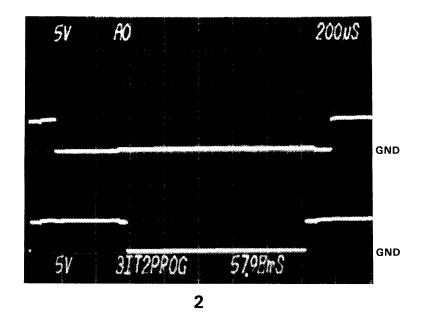

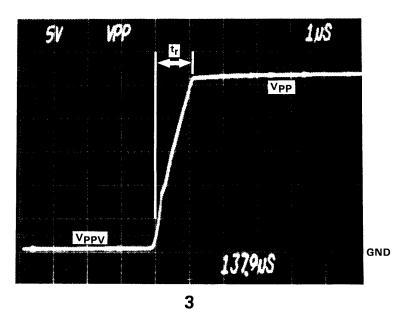

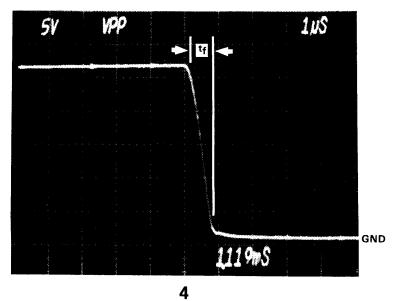

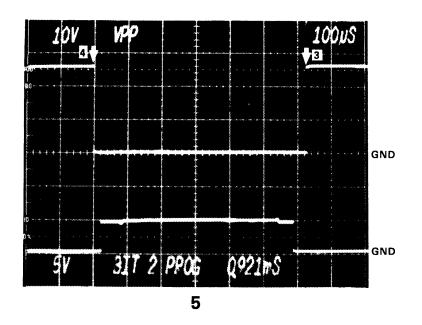

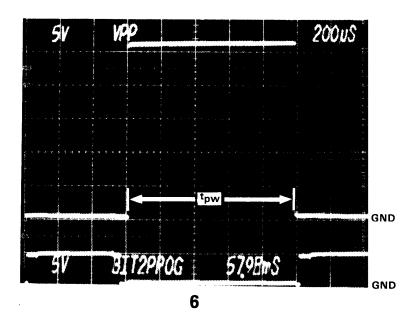

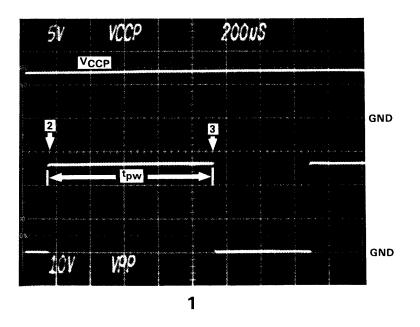

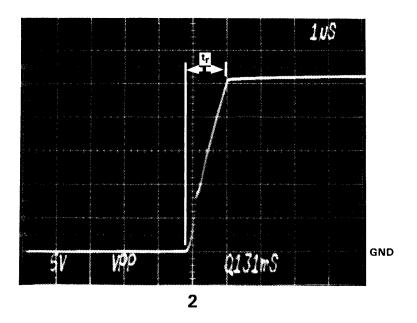

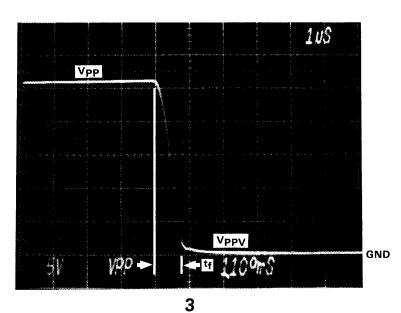

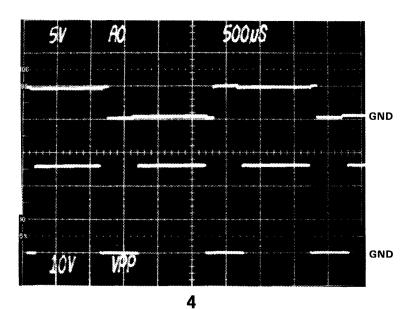

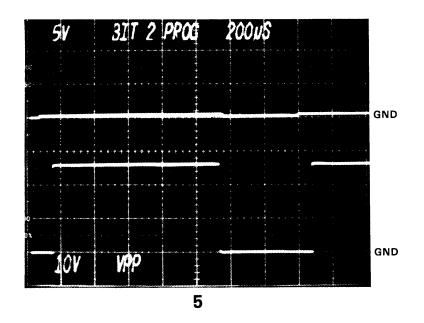

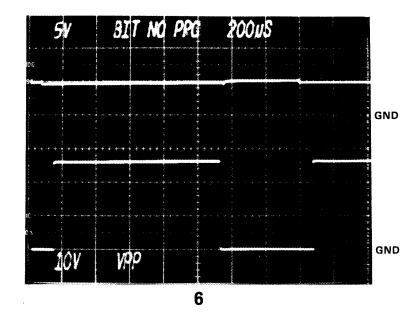

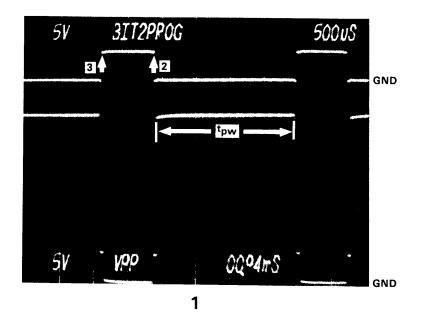

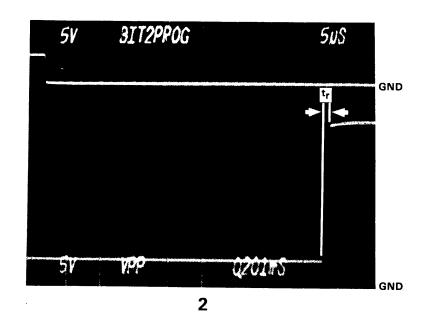

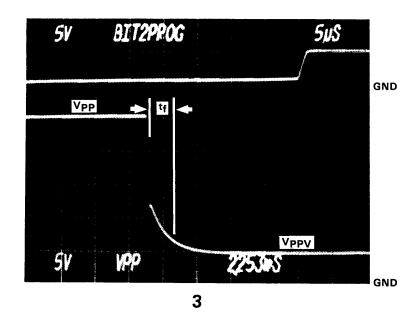

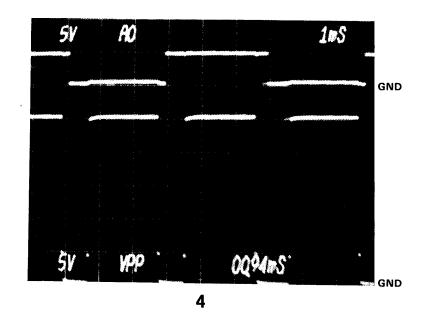

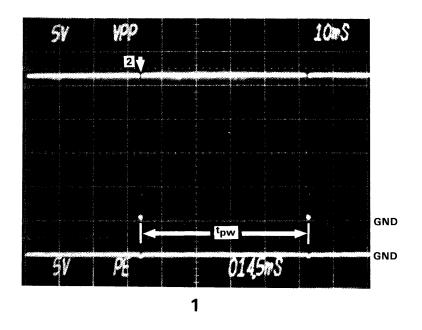

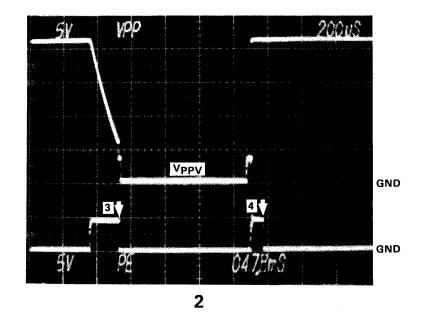

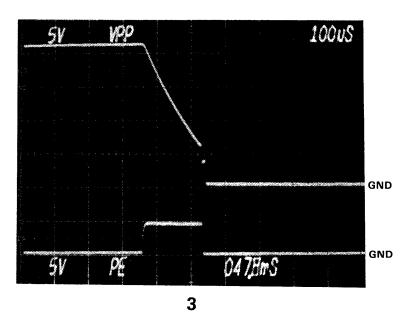

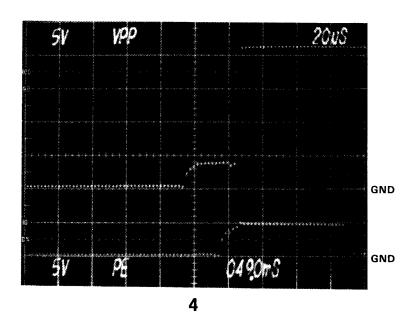

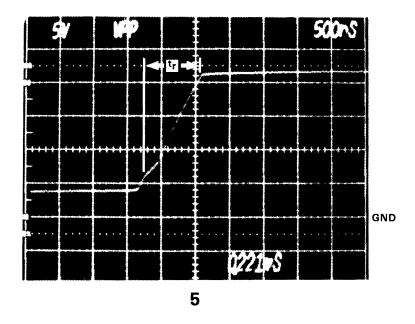

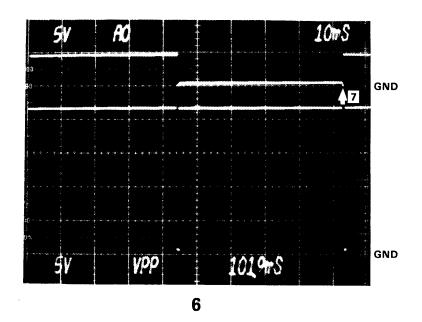

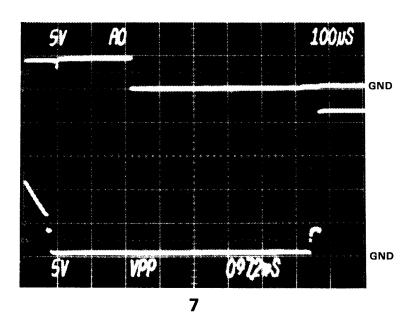

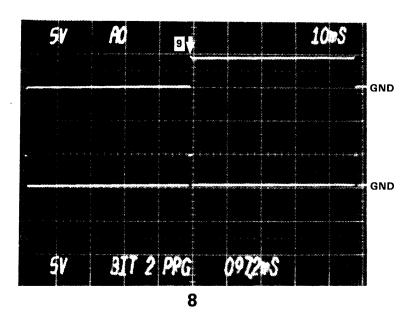

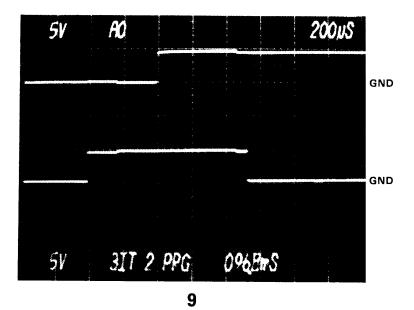

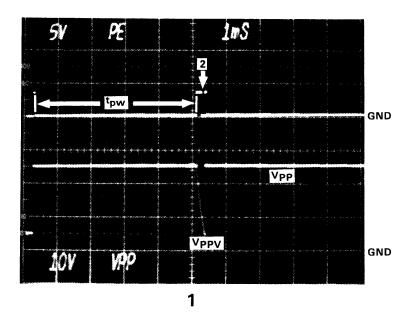

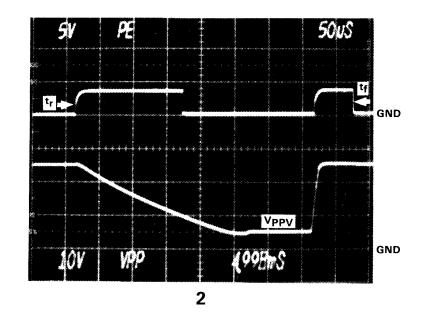

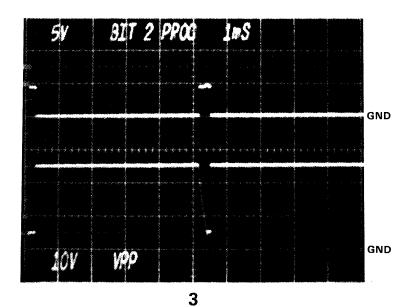

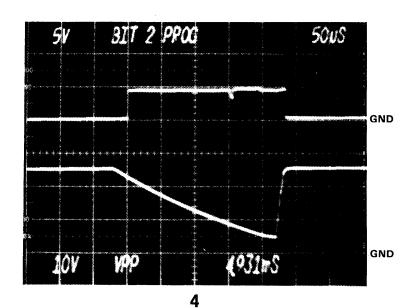

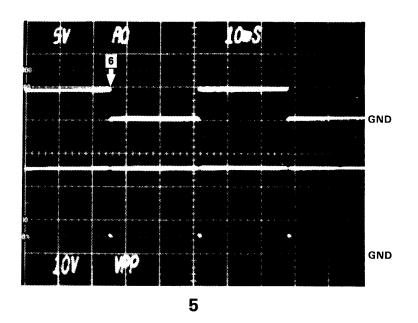

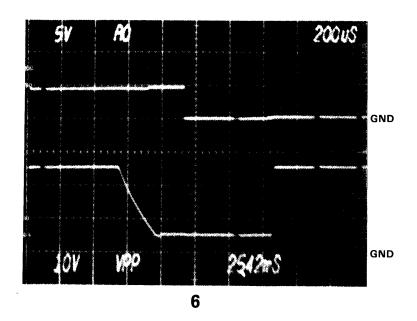

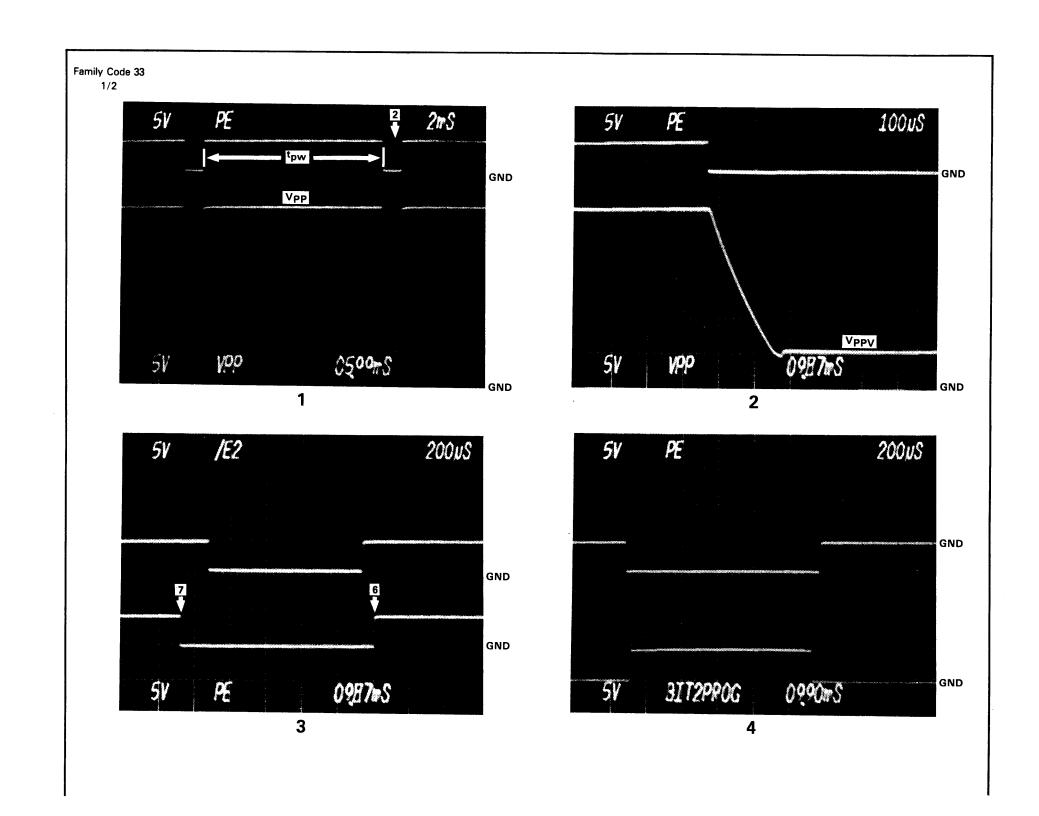

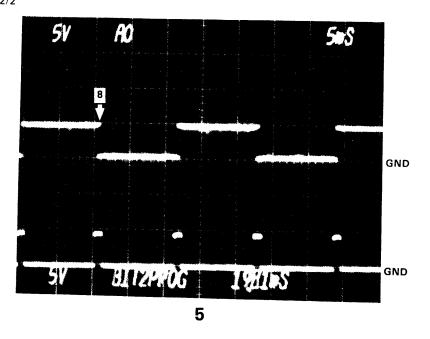

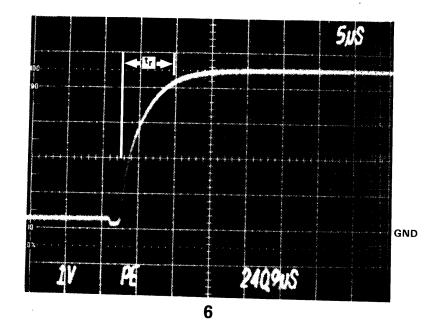

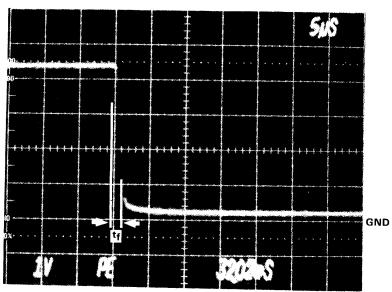

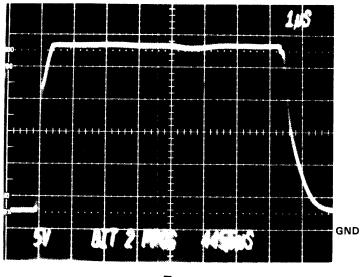

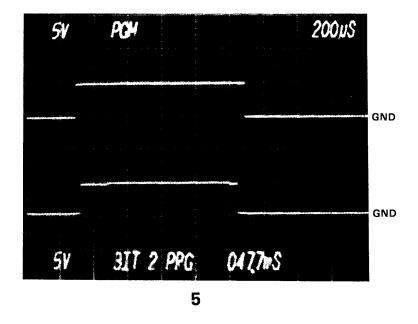

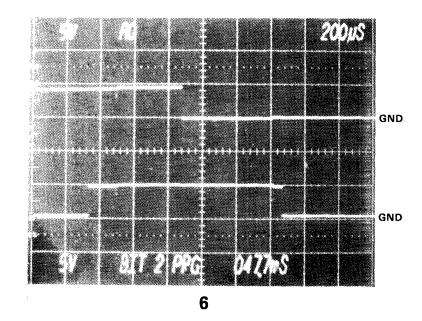

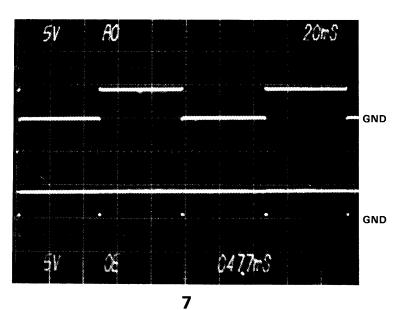

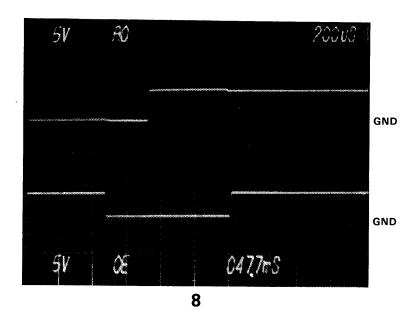

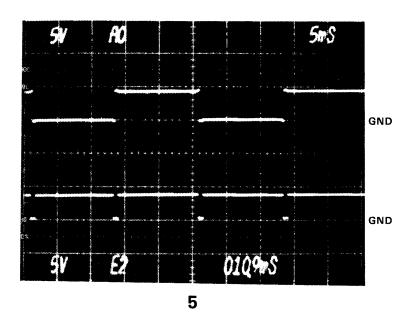

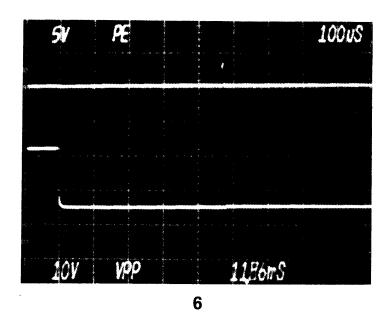

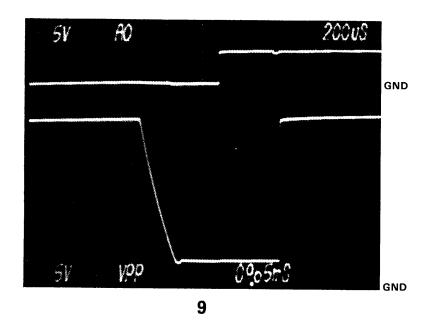

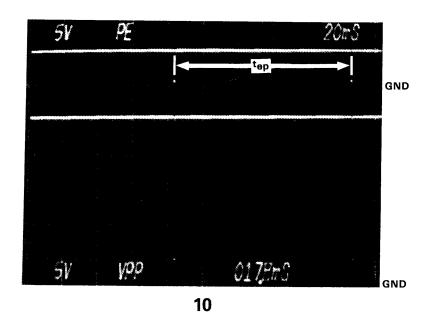

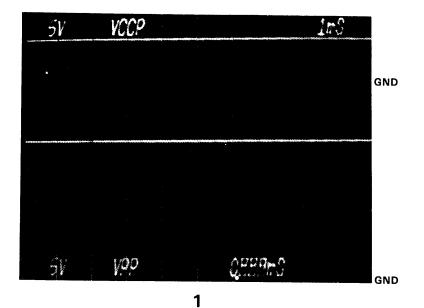

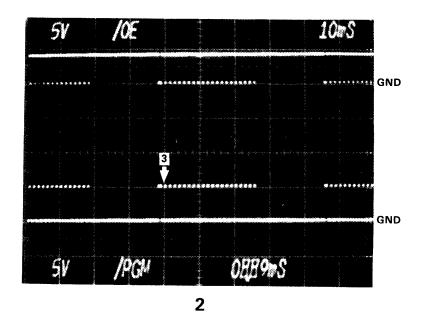

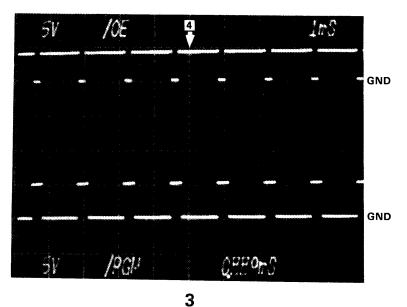

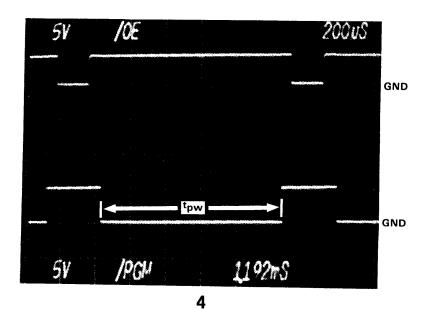

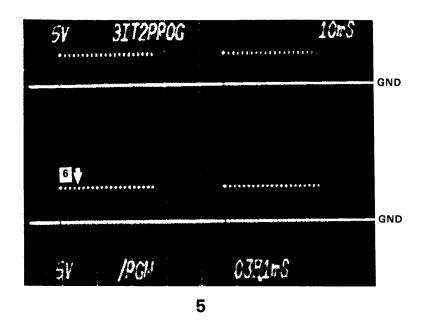

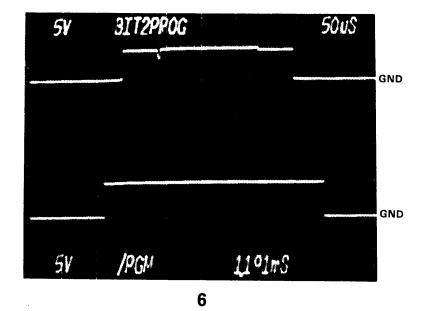

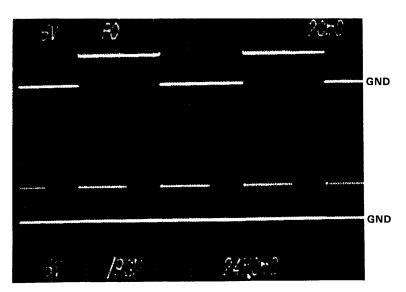

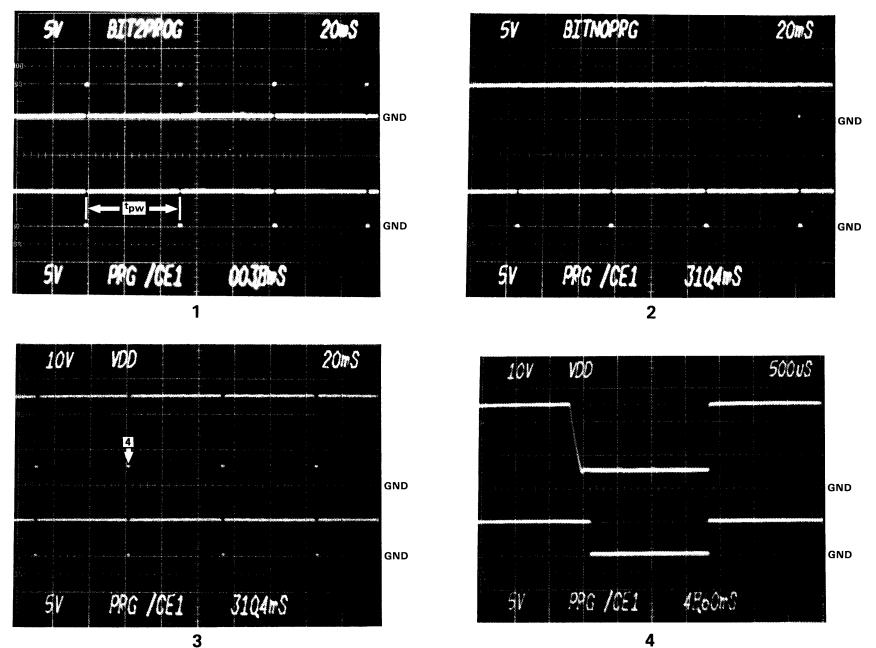

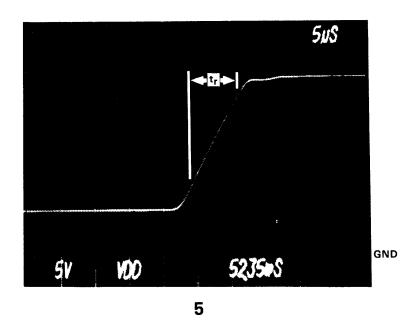

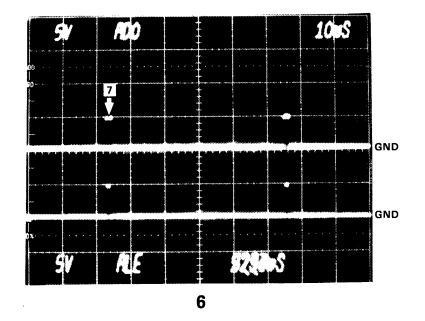

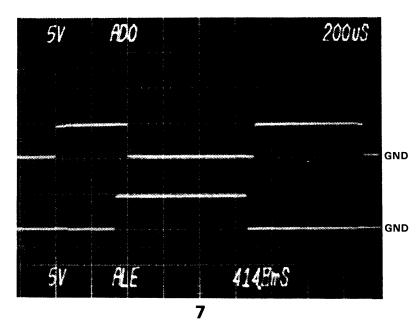

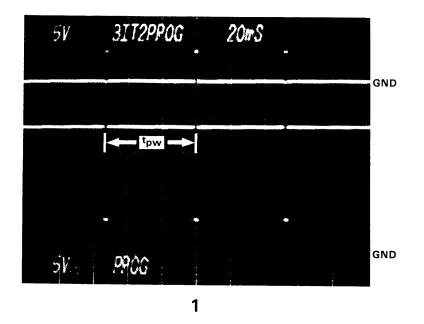

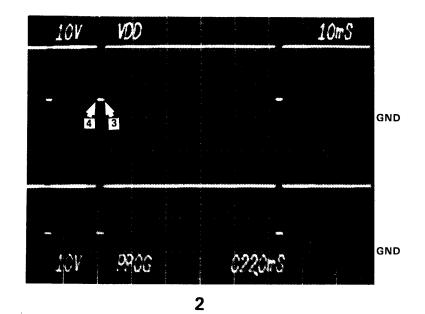

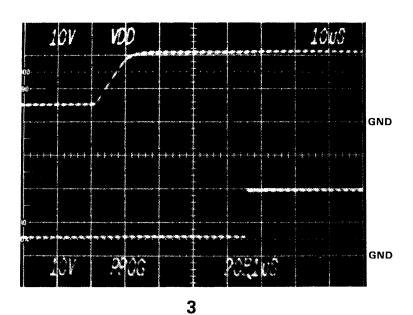

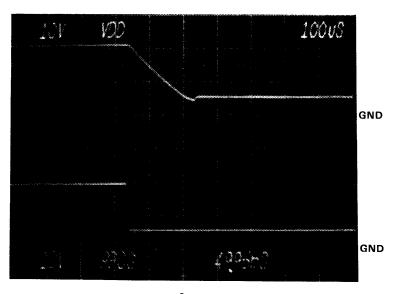

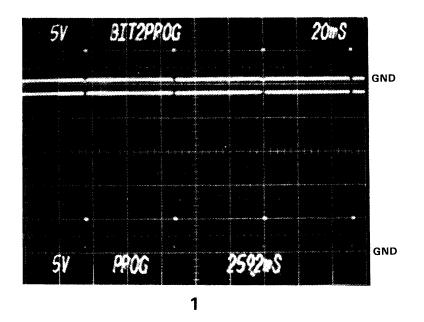

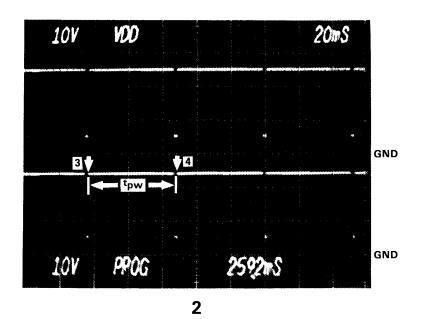

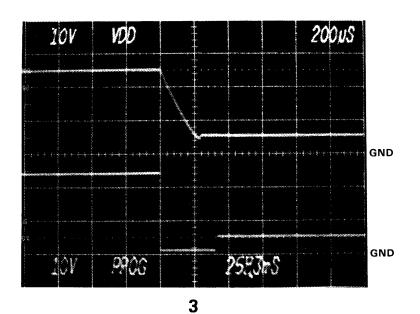

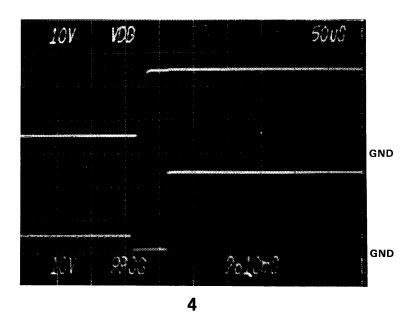

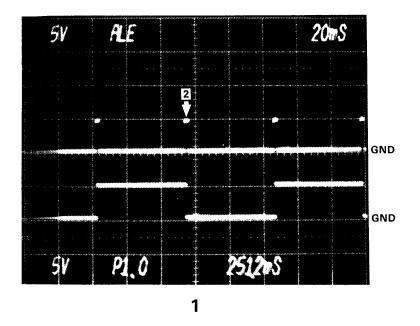

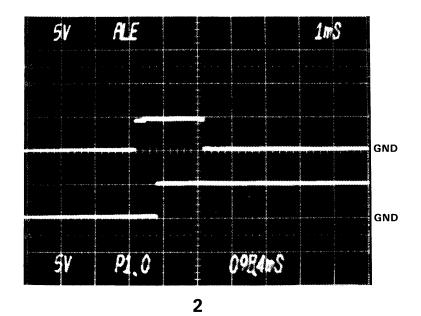

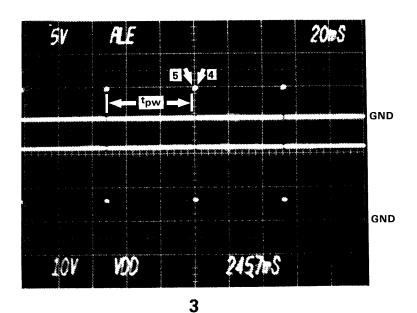

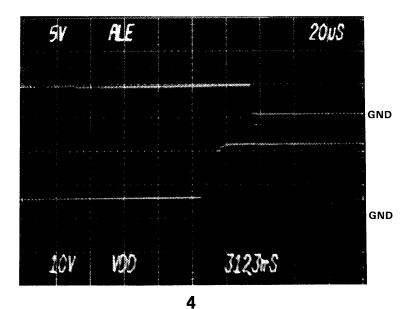

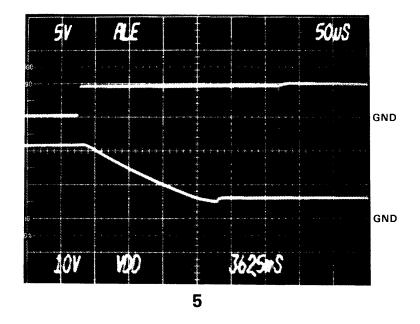

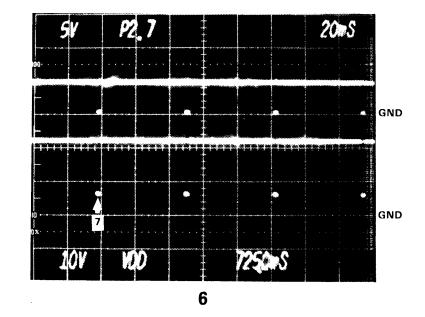

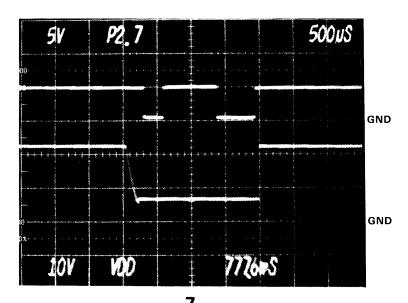

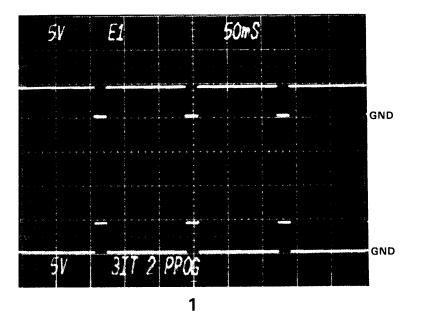

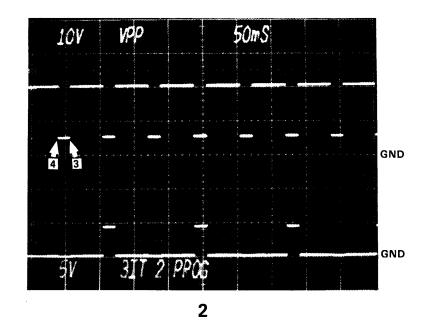

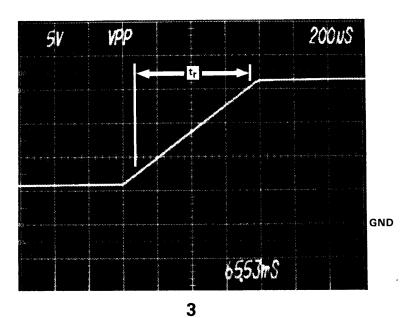

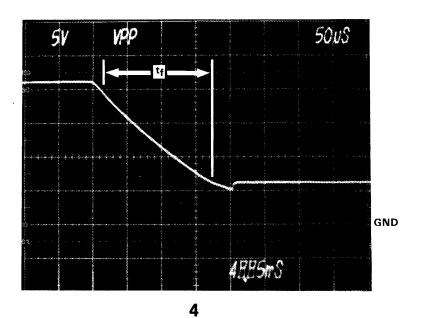

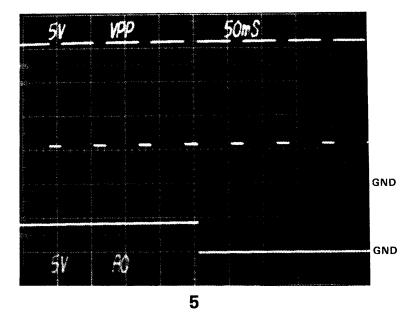

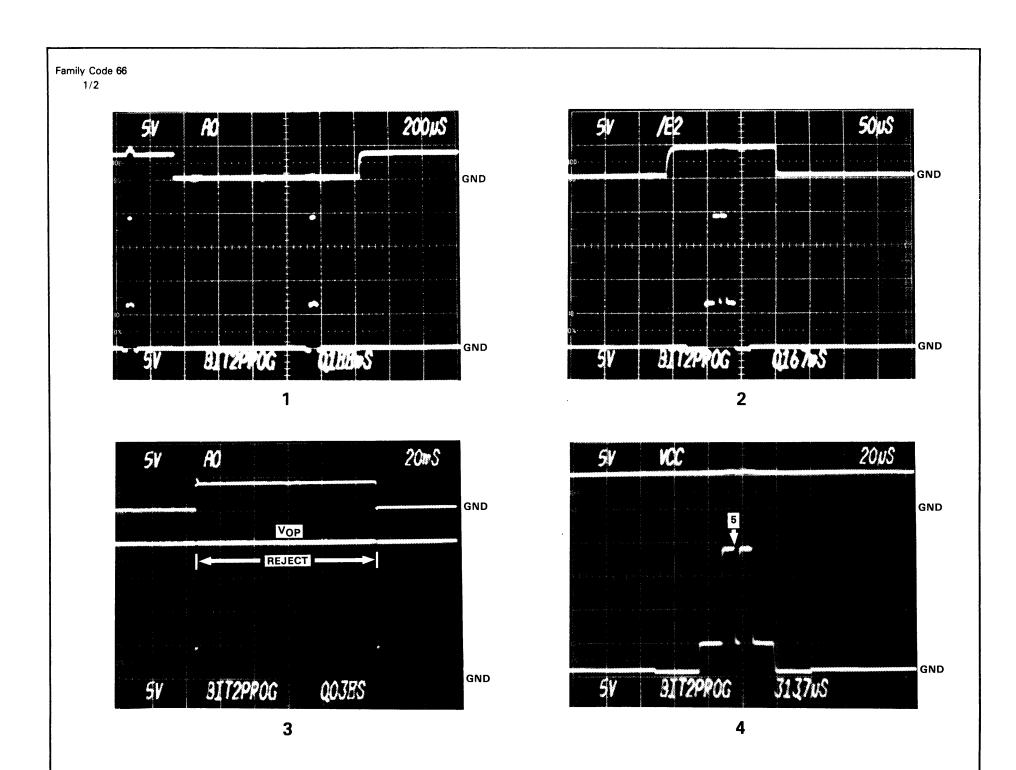

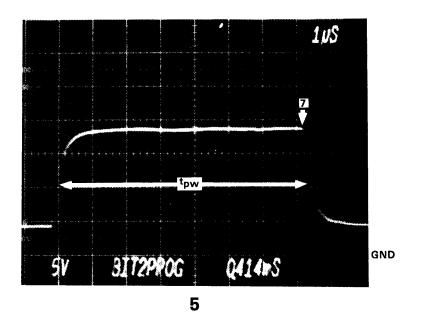

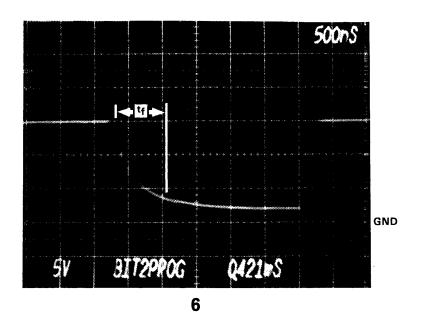

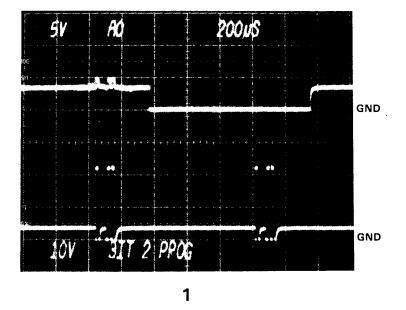

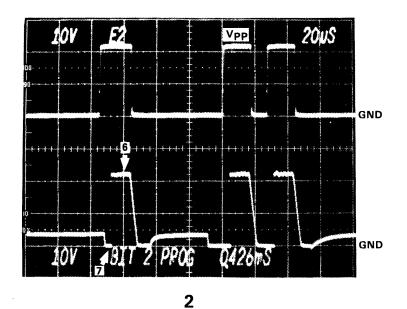

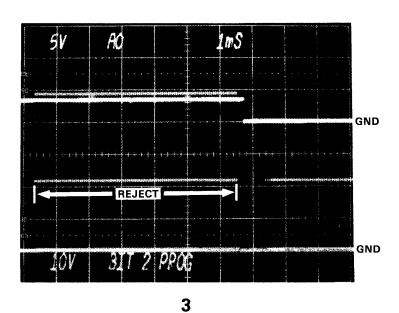

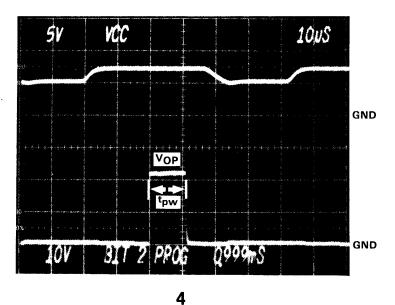

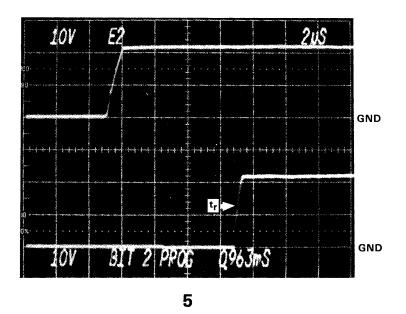

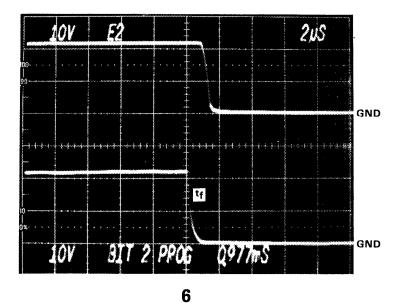

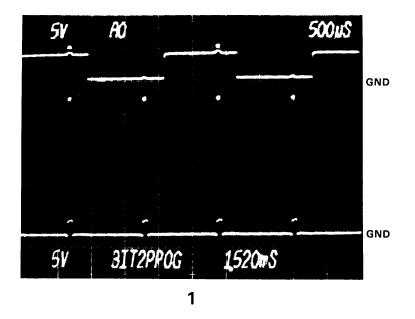

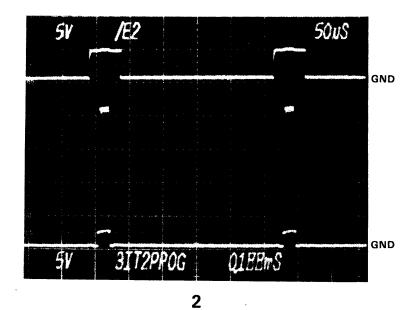

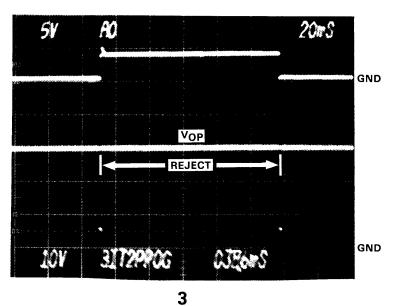

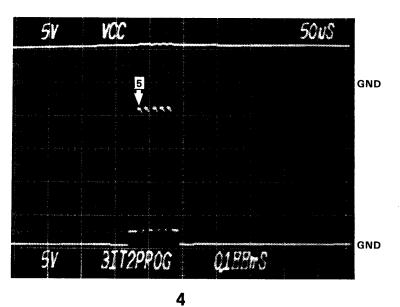

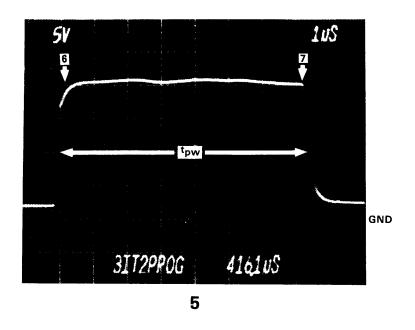

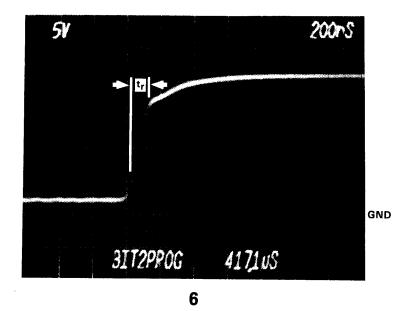

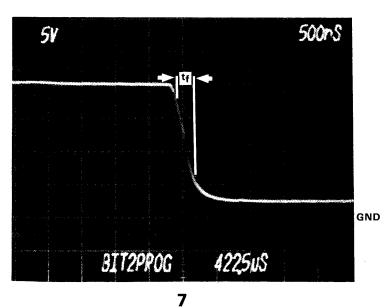

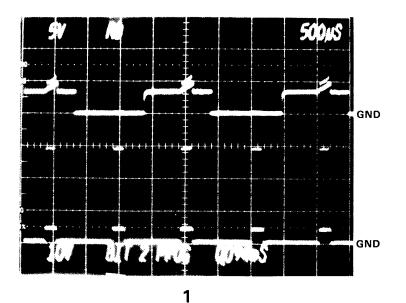

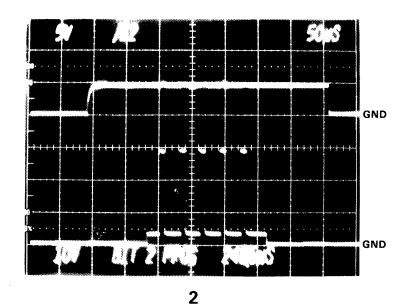

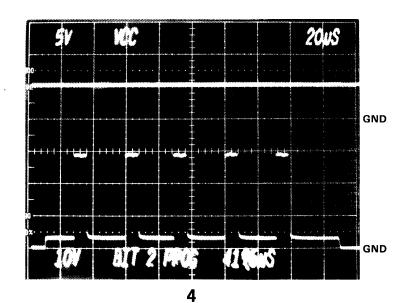

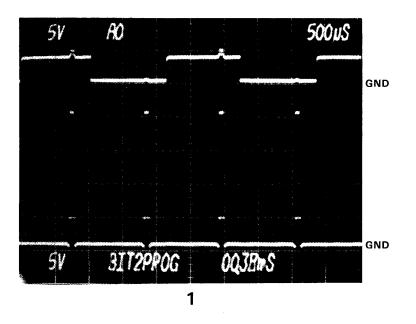

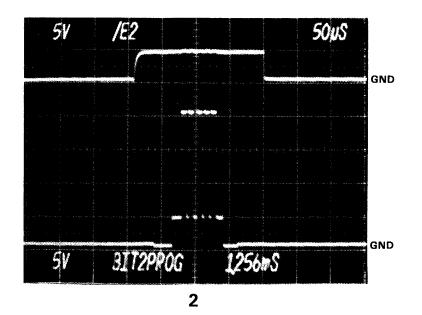

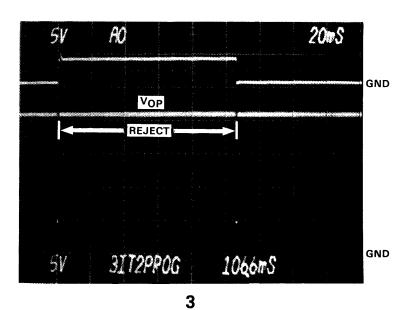

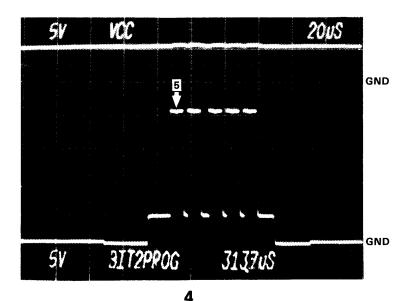

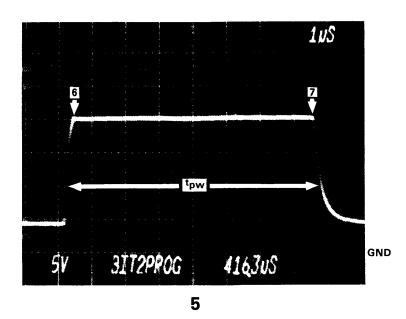

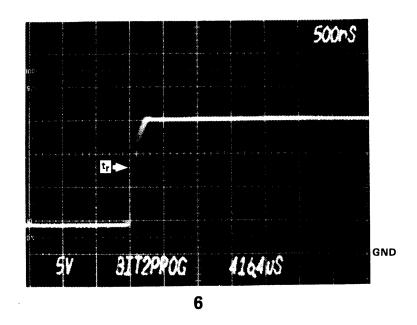

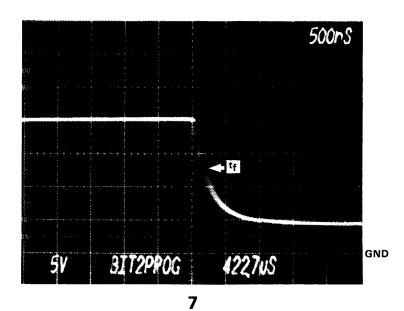

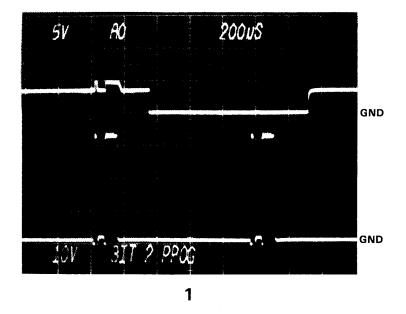

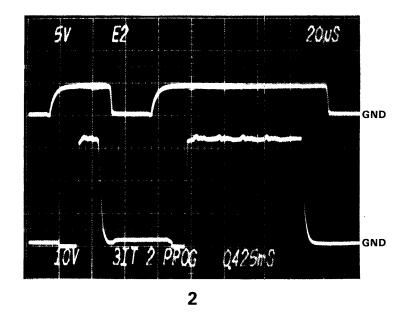

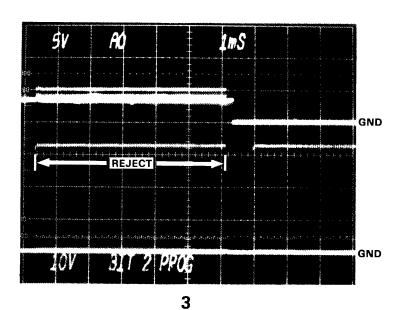

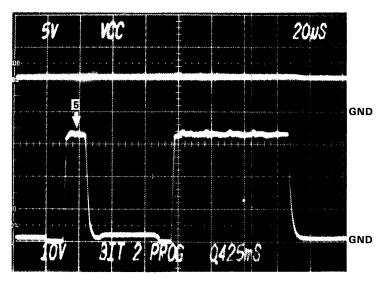

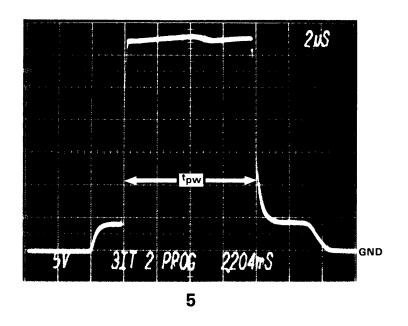

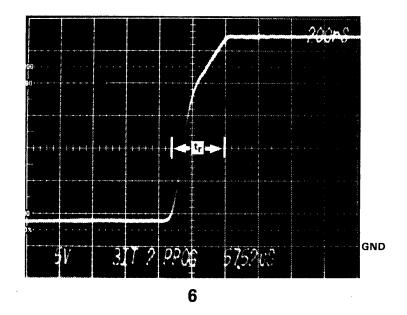

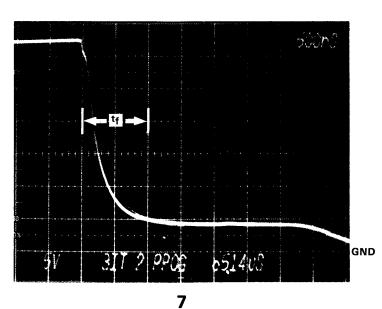

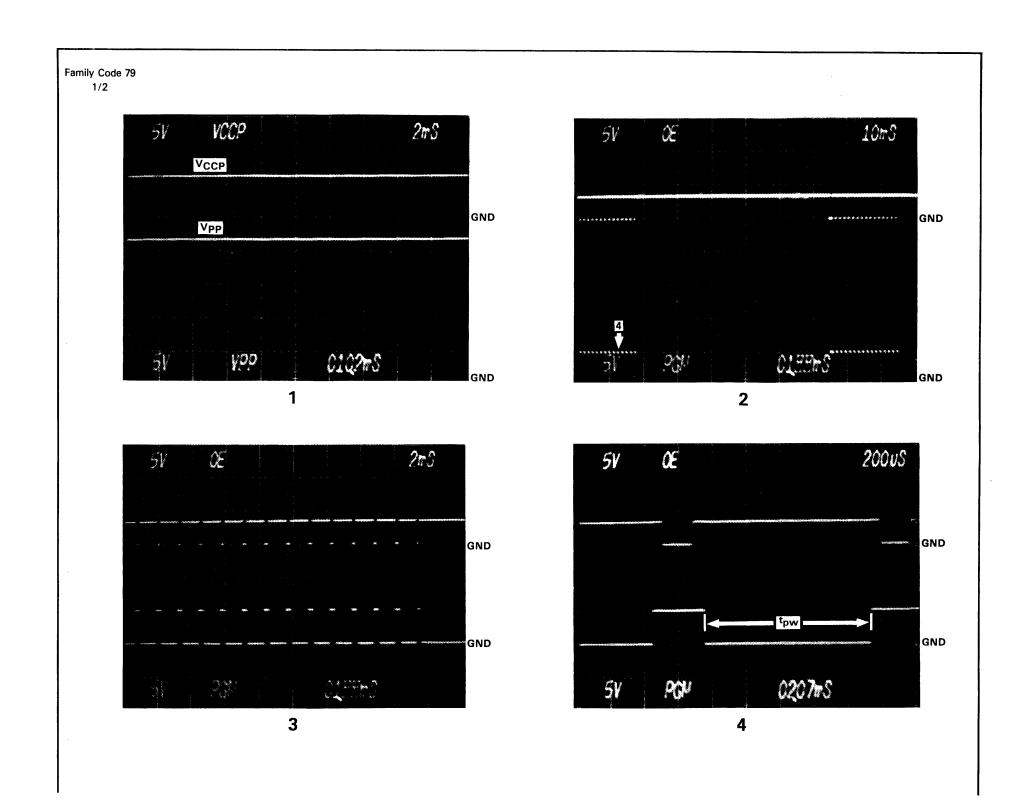

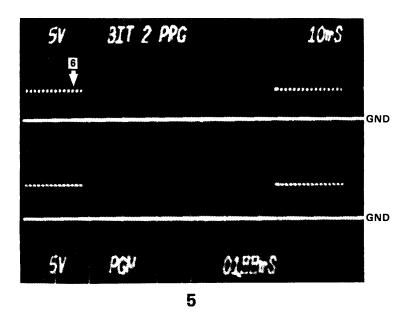

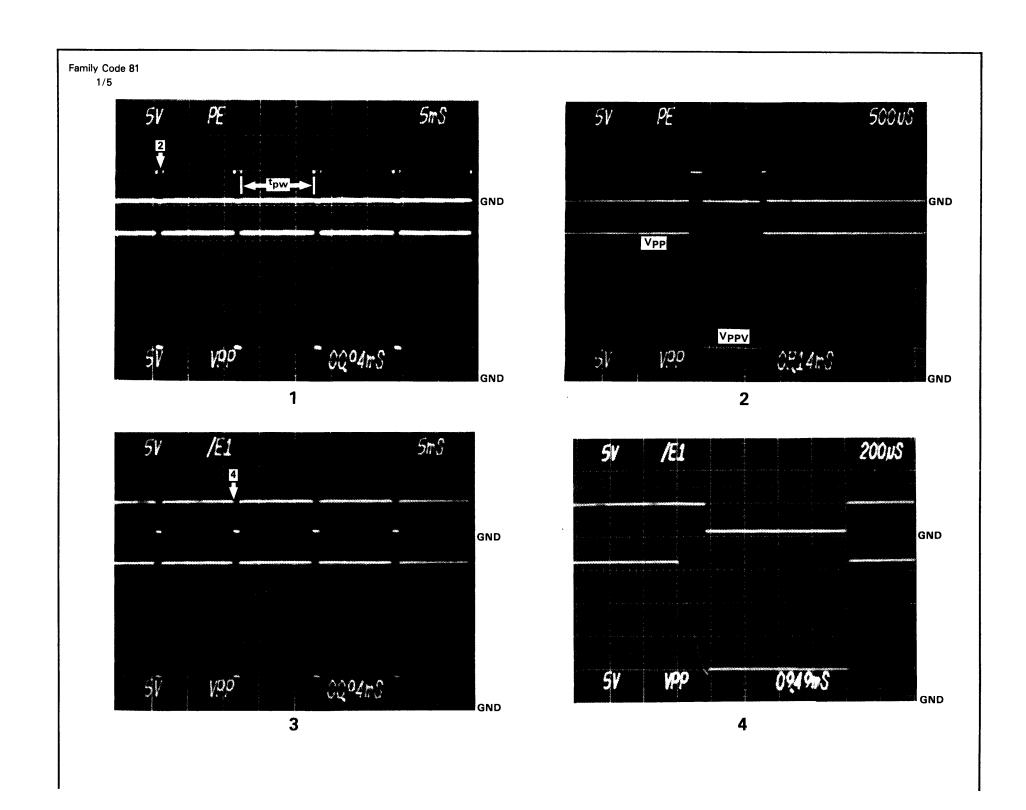

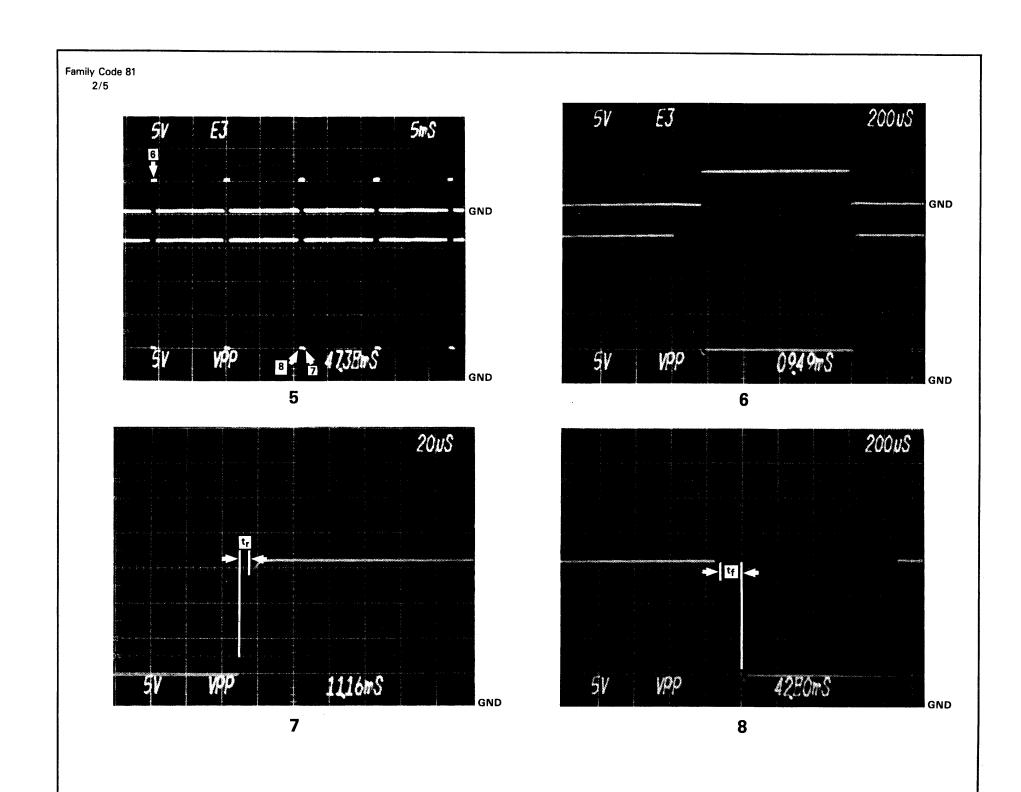

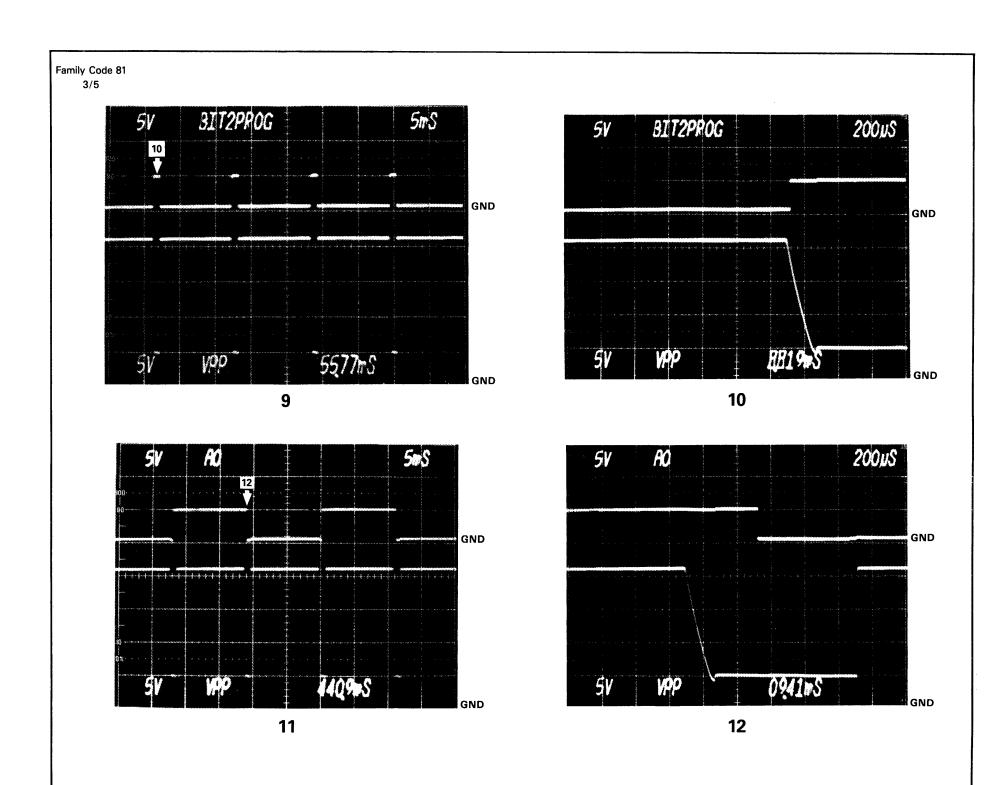

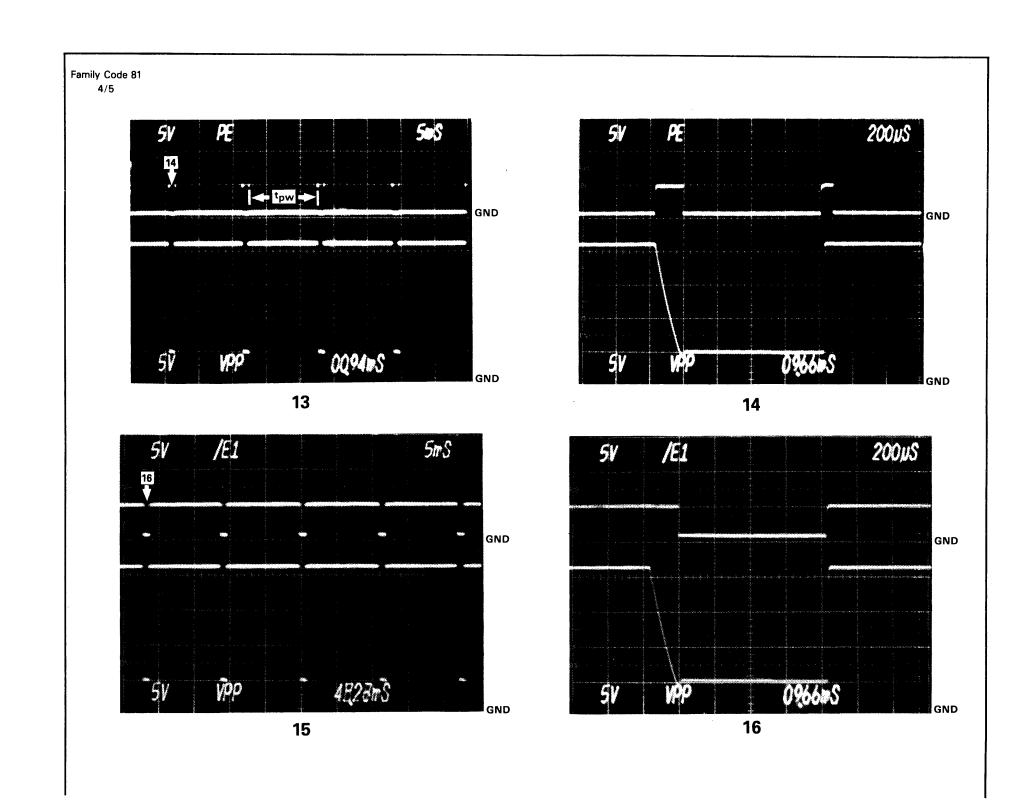

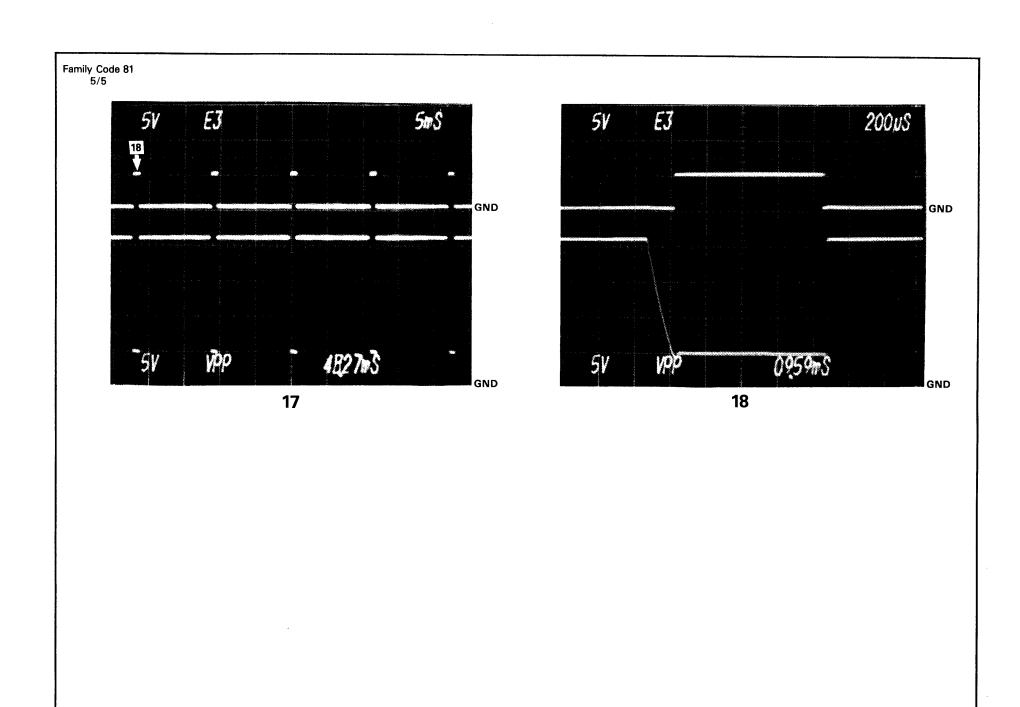

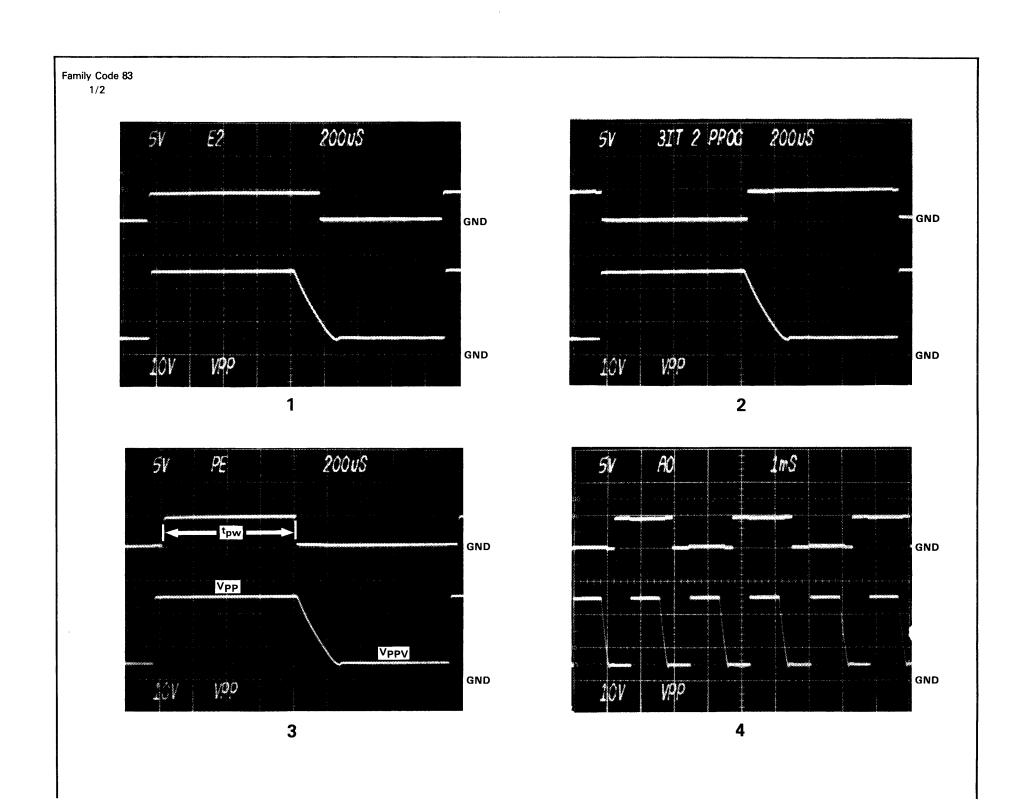

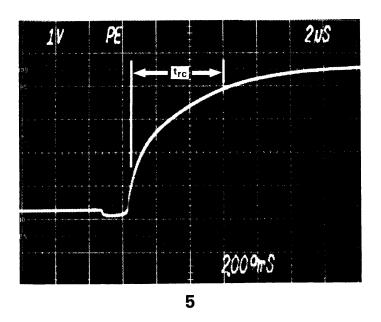

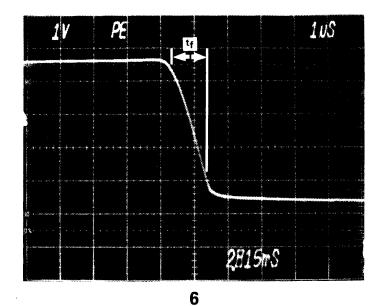

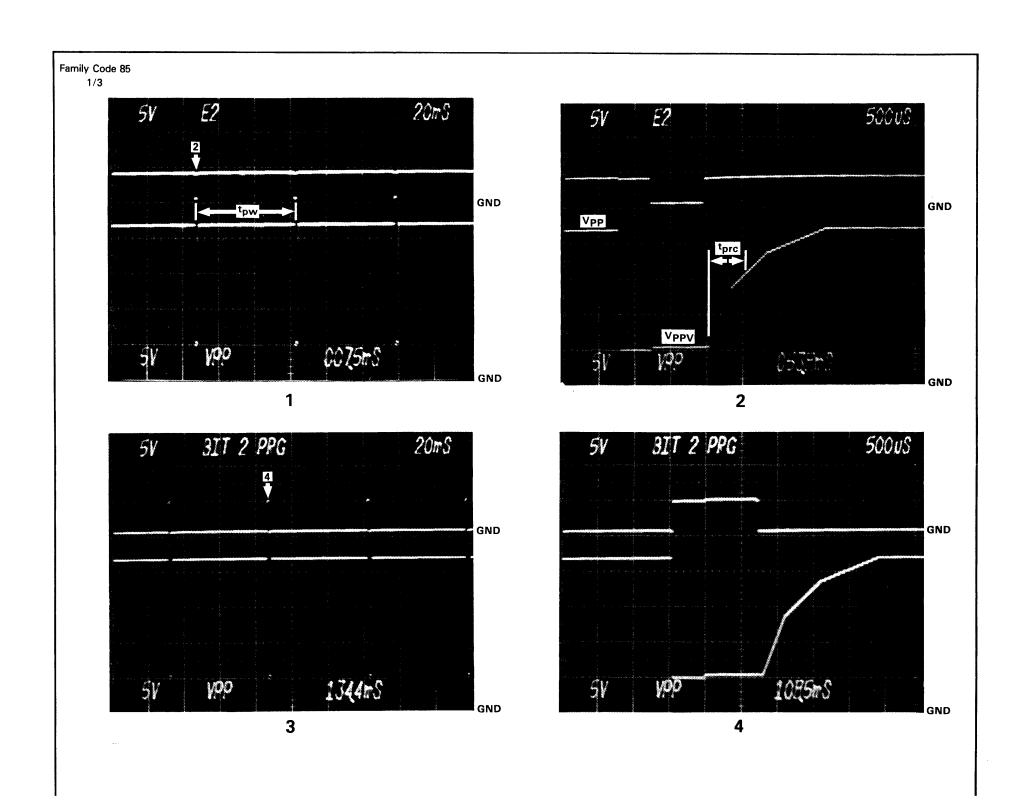

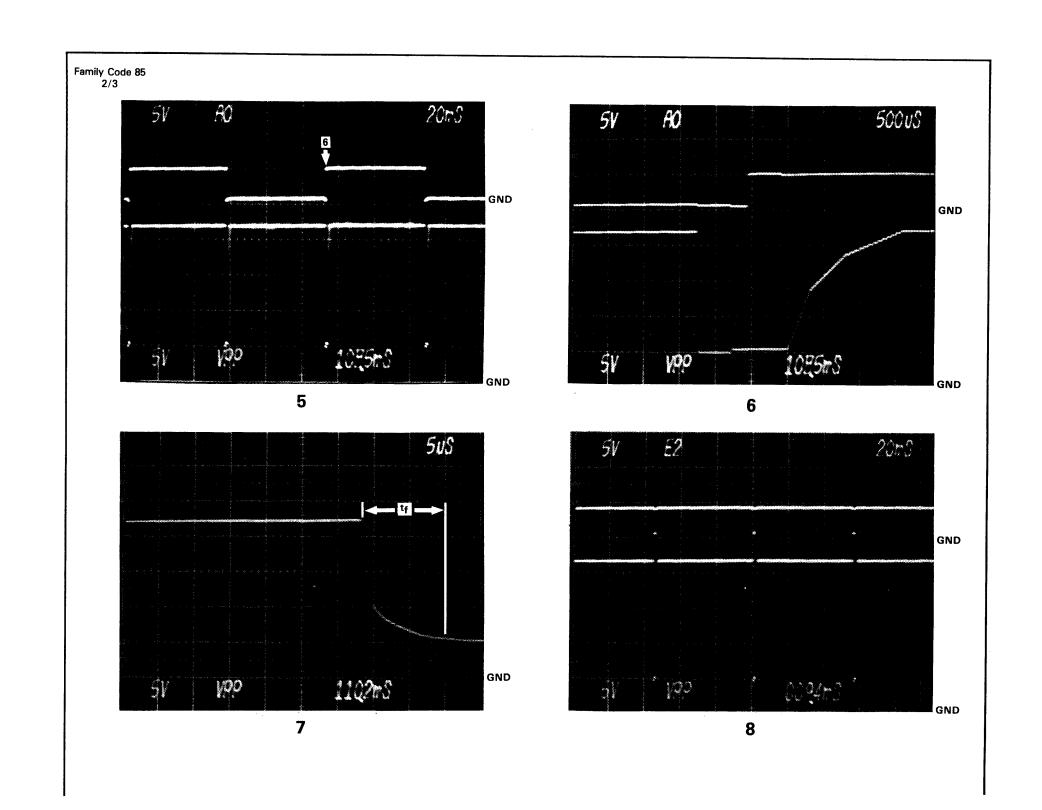

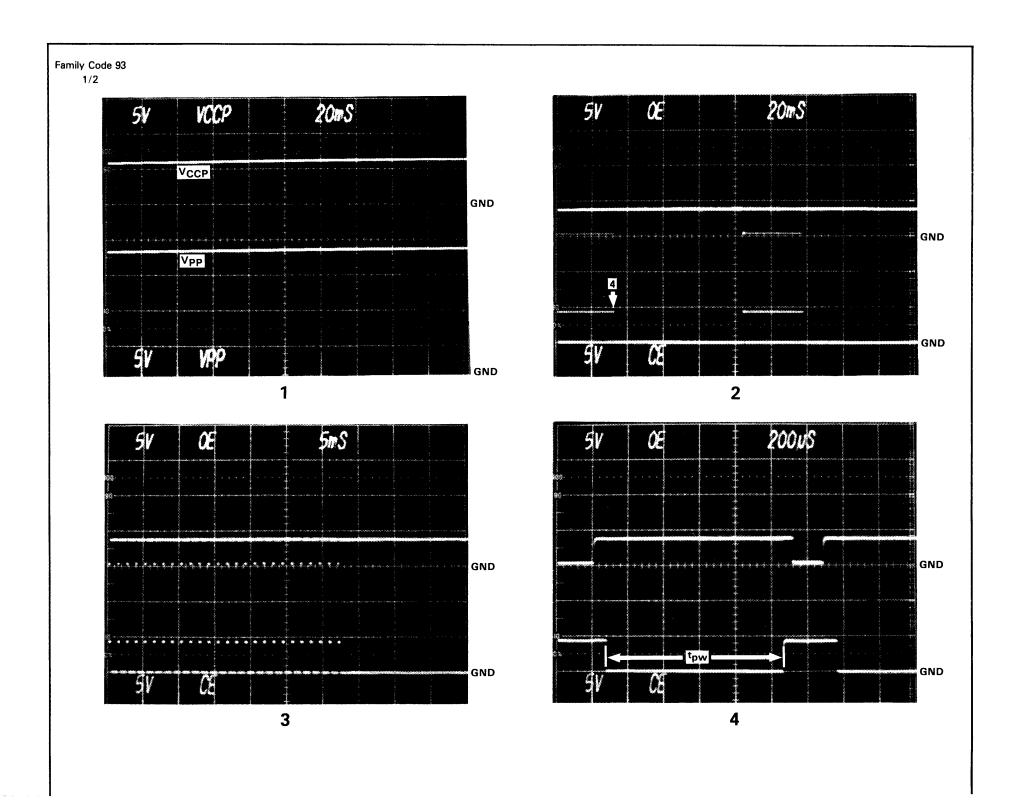

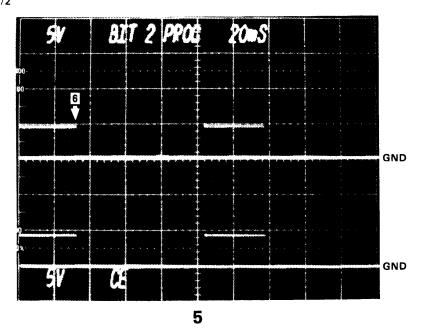

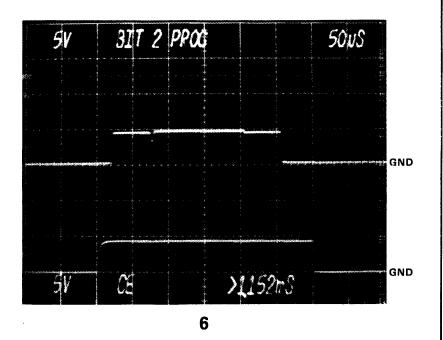

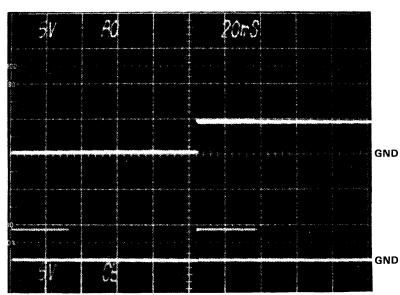

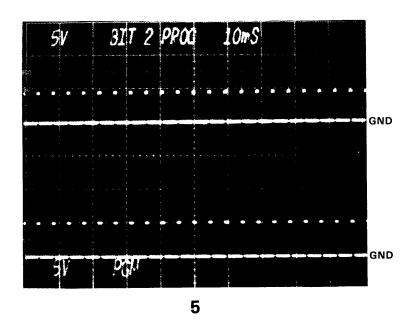

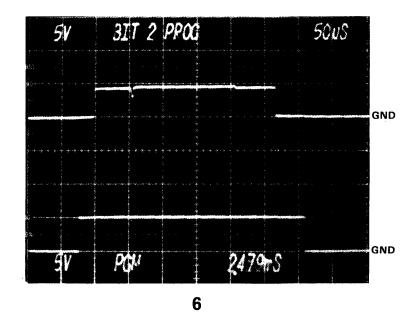

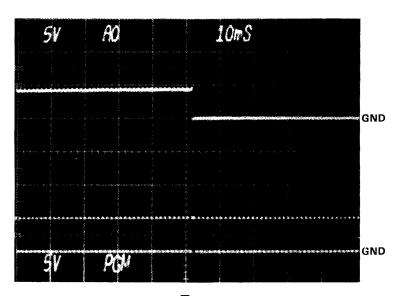

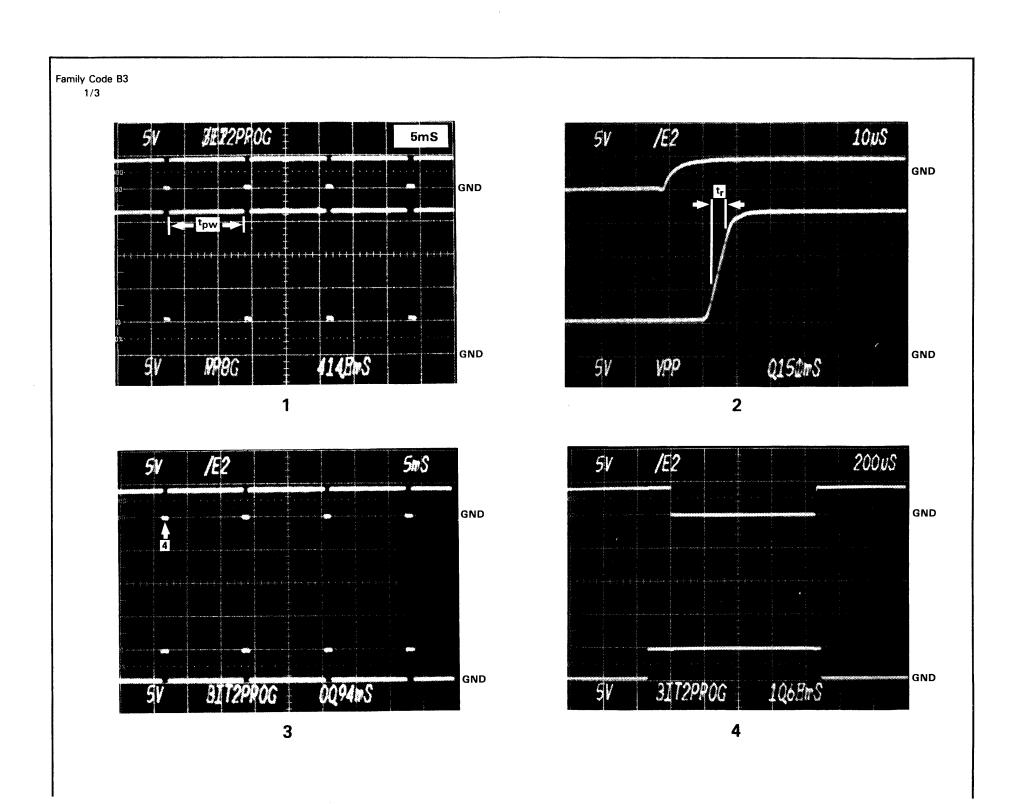

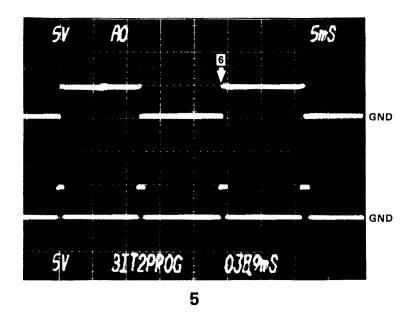

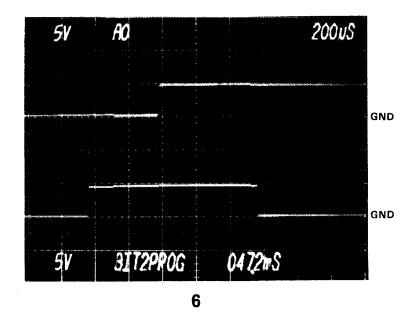

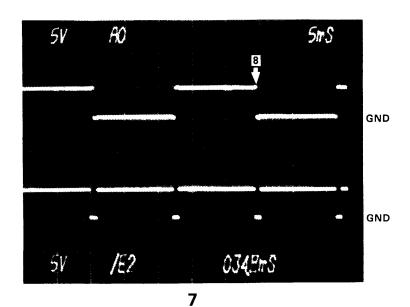

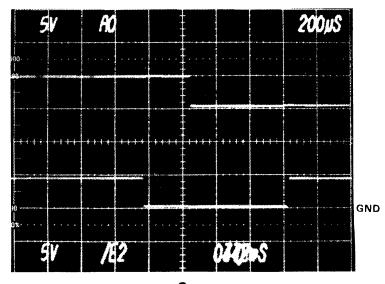

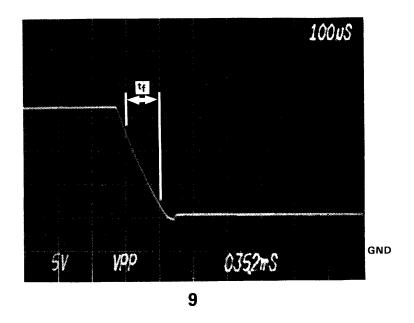

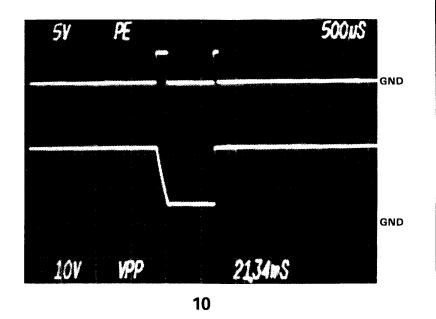

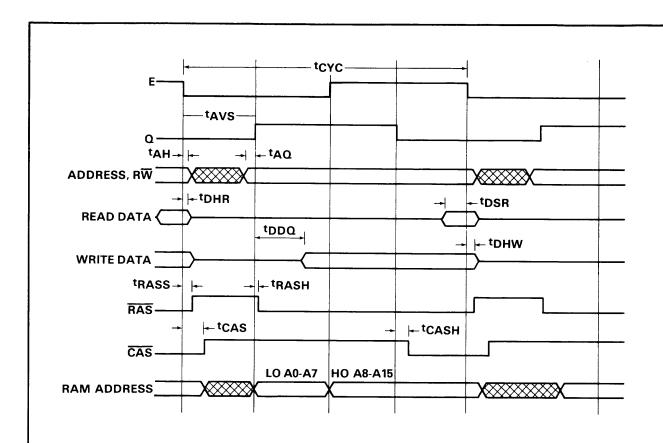

|     | 4.3.3 | Waveform Observation                                               | 4-3 |

|     | 4.3.4 | Detailed Explanation of the Timing Diagrams                        | 4-5 |

|     |       | Timing Diagrams                                                    |     |

| 4.4 | TROU  | IBLESHOOTING                                                       | 4-7 |

|     | 4.4.1 | Programmer Does Not Power Up                                       | 4-7 |

|     | 4.4.2 | Erratic Programmer Display or No Keyboard Response                 | 4-7 |

|     | 4.4.3 | Programmer Will Not Perform a Device-related Operation Properly    | 4-7 |

|     | 4.4.4 | Programmer Will Not Perform a Port-related Operation Properly      | 4-7 |

|     | 4.4.5 | Programmer Ultraviolet (UV) Lamp Will Not Erase MOS PROMs Properly | 4-7 |

|     |       | SECTION 5. CIRCUIT DESCRIPTION                                     |     |

| 5.1 | INTRO | DDUCTION                                                           | 5-1 |

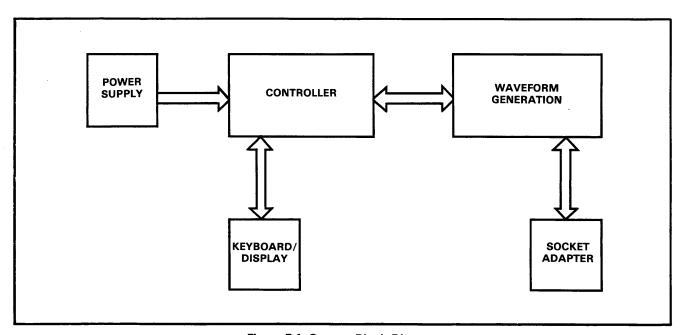

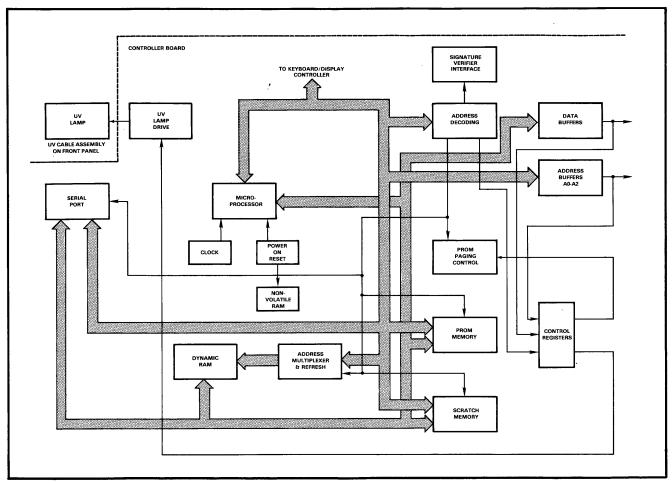

| 5.2 | ARCH  | IITECTURE                                                          | 5-1 |

|     | 5.2.1 | The Bus                                                            | 5-1 |

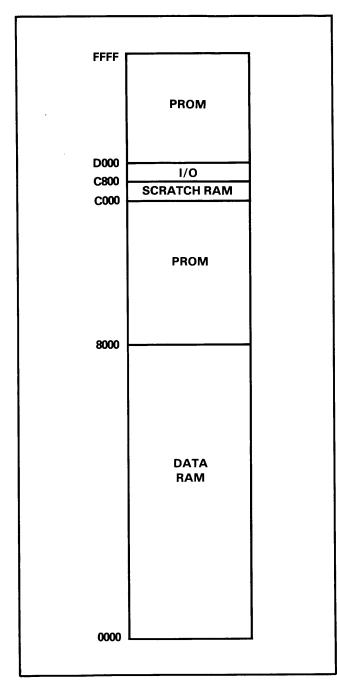

|     | 5.2.2 | Address Map                                                        | 5-2 |

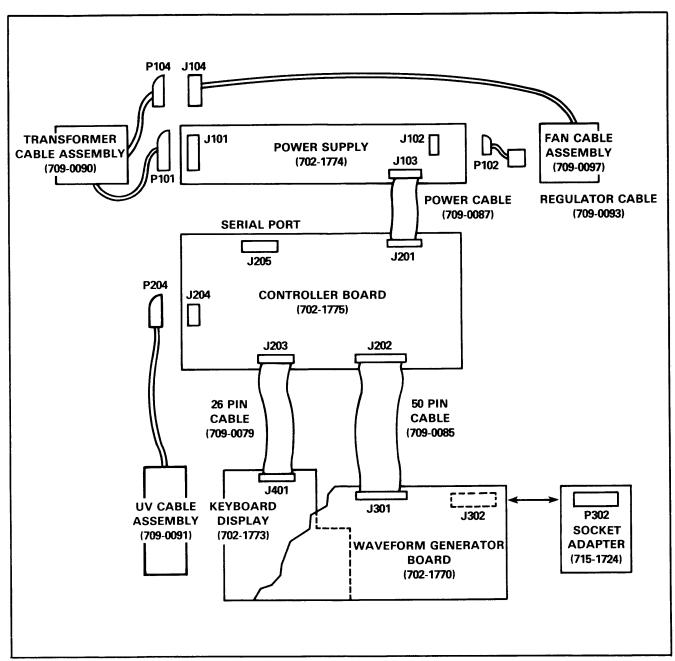

|     | 5.2.3 | Hardware Interconnection                                           | 5-2 |

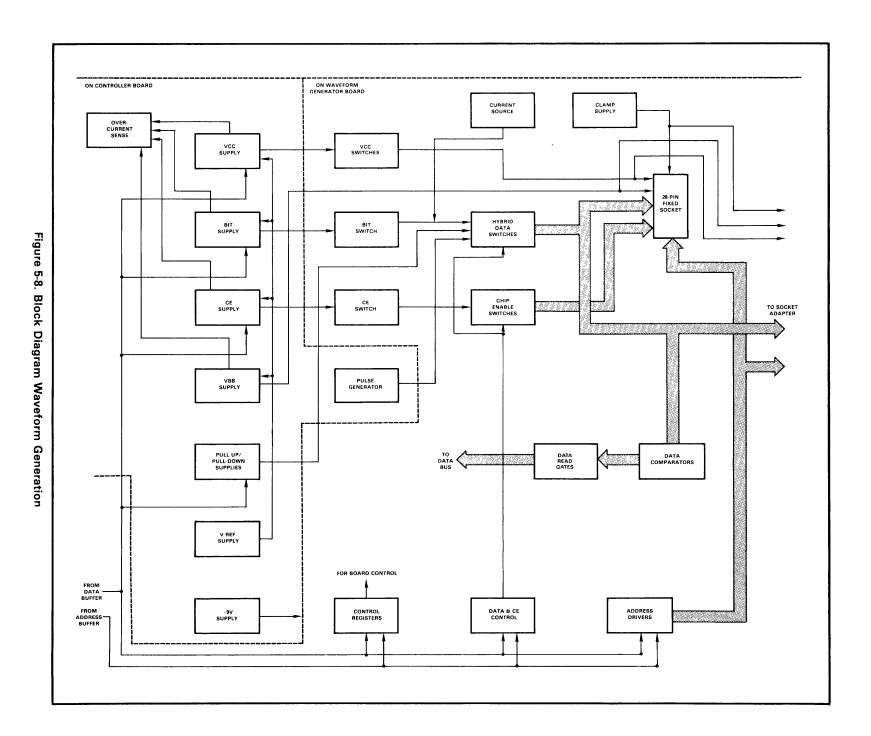

| 5.3 | MAIN  | CIRCUITRY FUNCTIONS                                                | 5-2 |

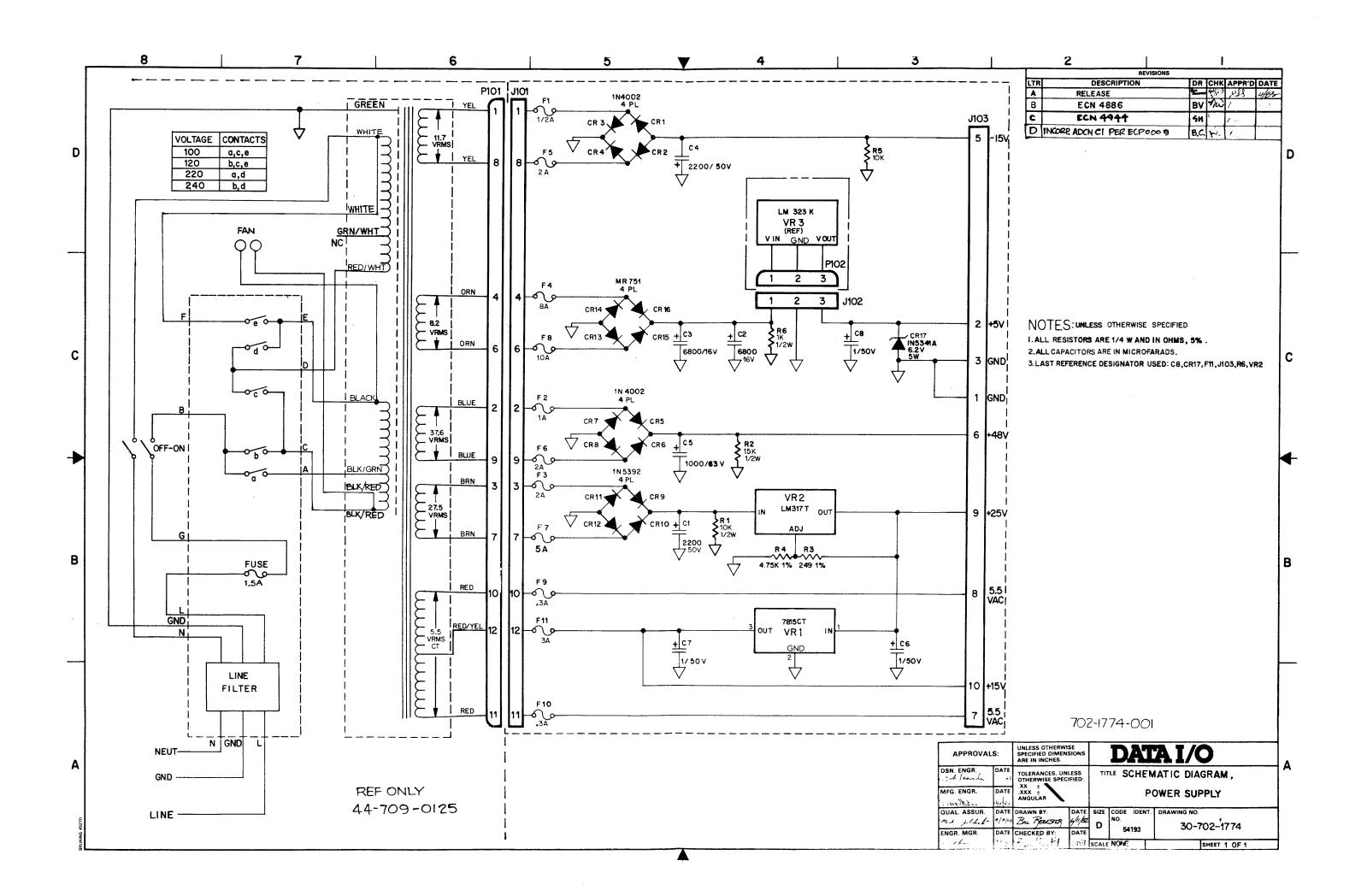

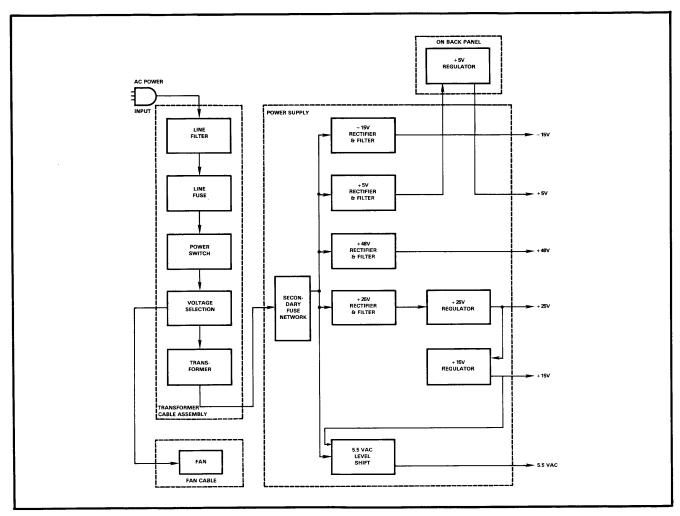

|     | 5.3.1 | Power Supply                                                       | 5-3 |

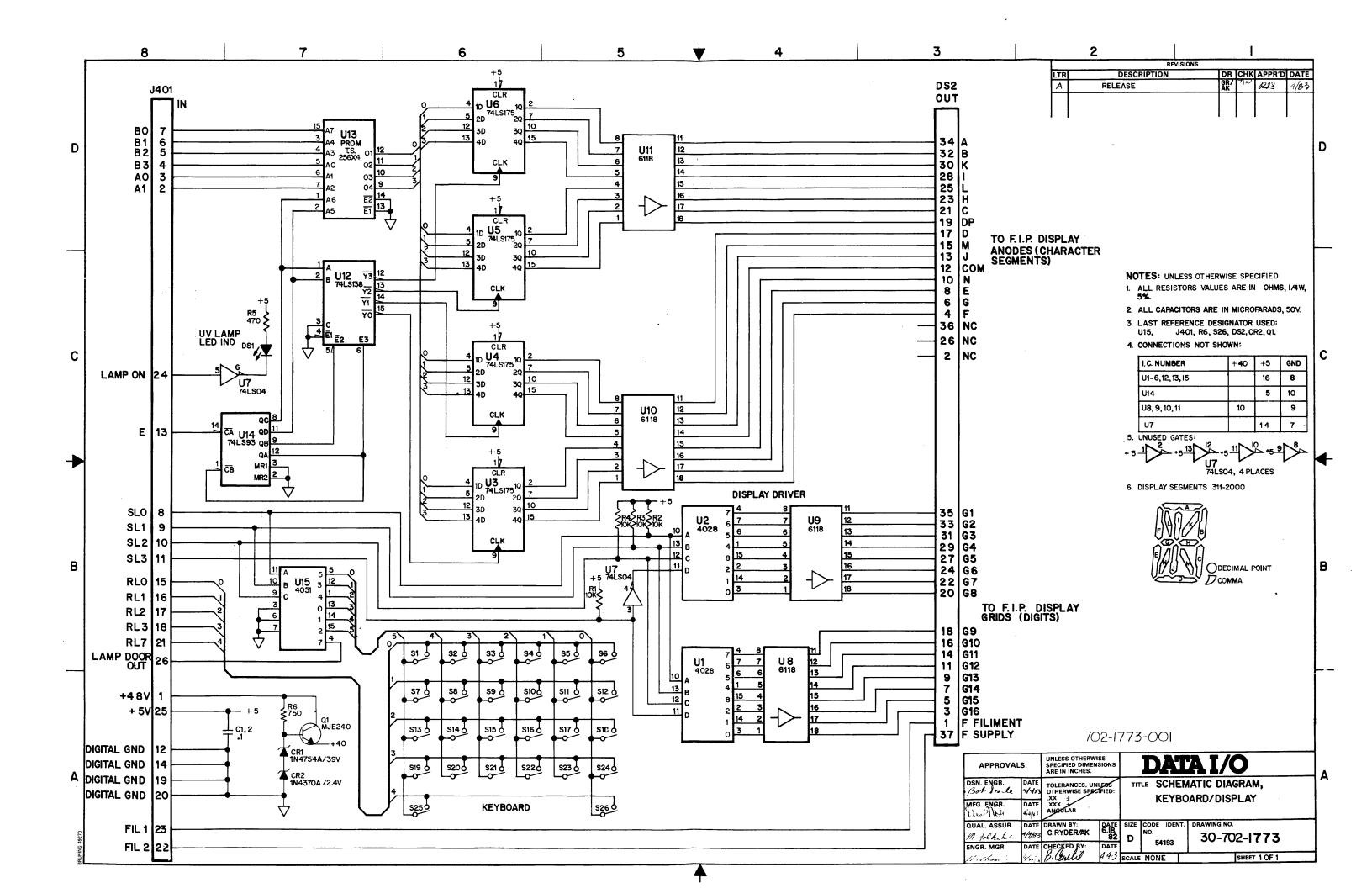

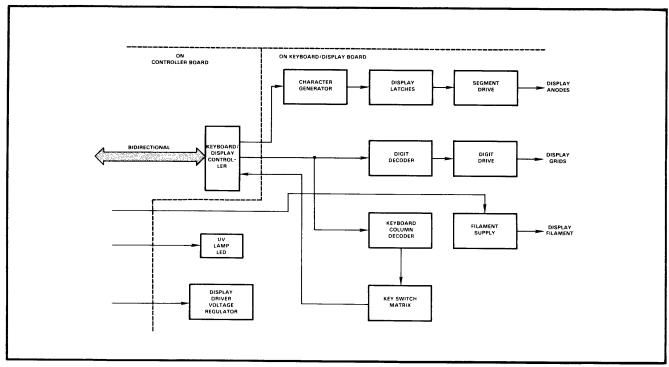

|     | 5.3.2 | Keyboard/Display                                                   | 5-5 |

|     | 5.3.3 | Socket Adapters                                                    | 5-6 |

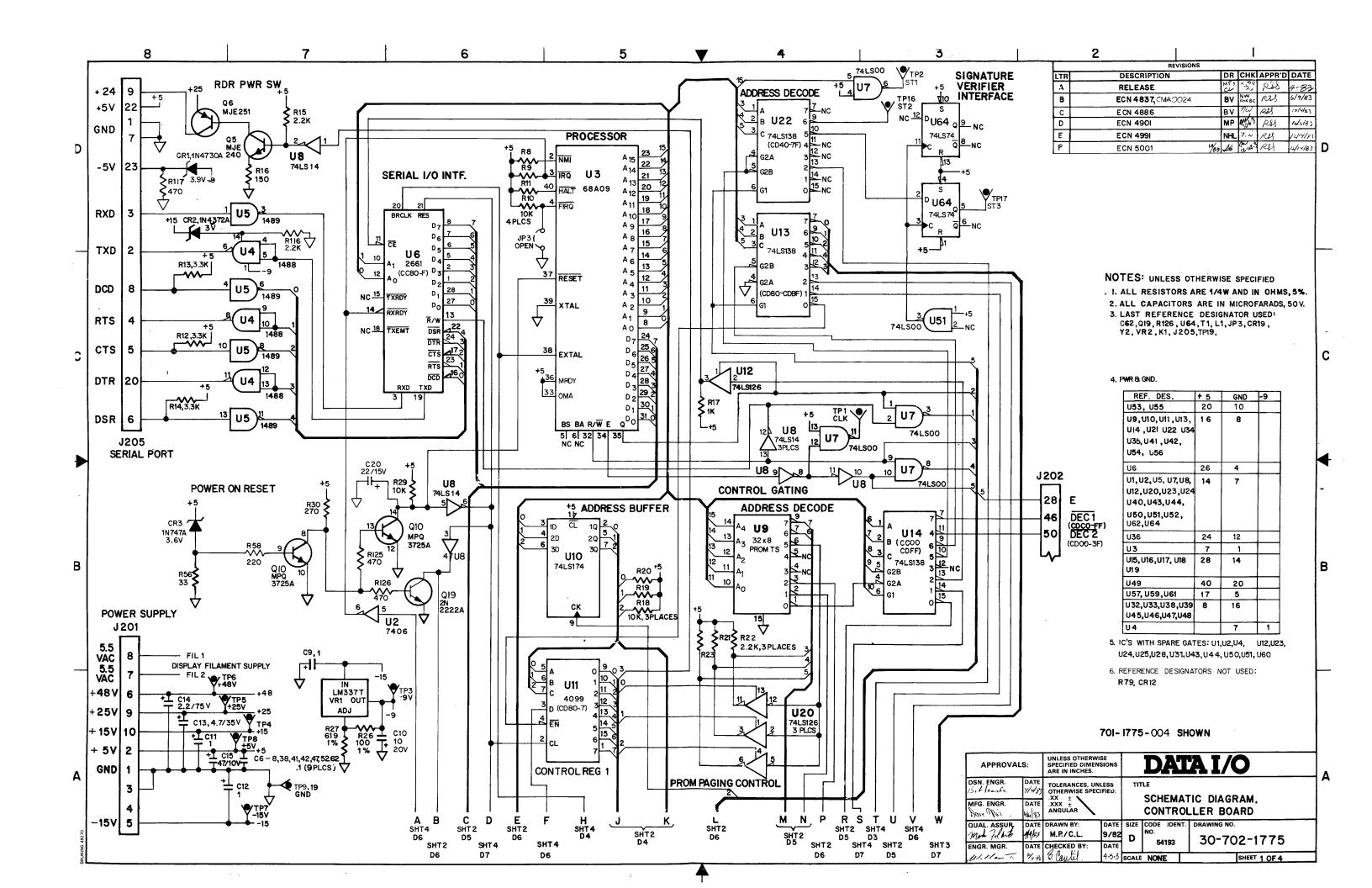

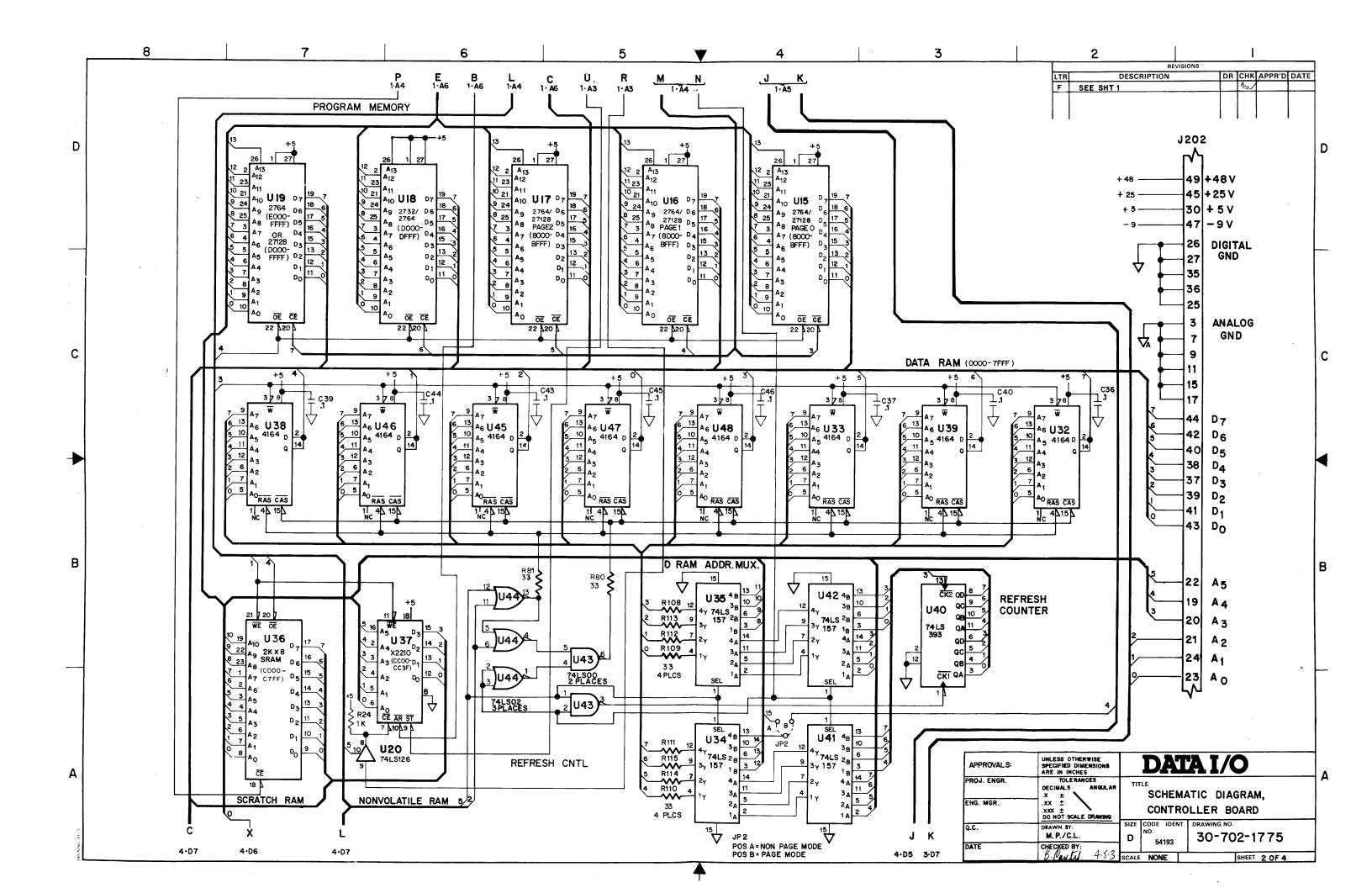

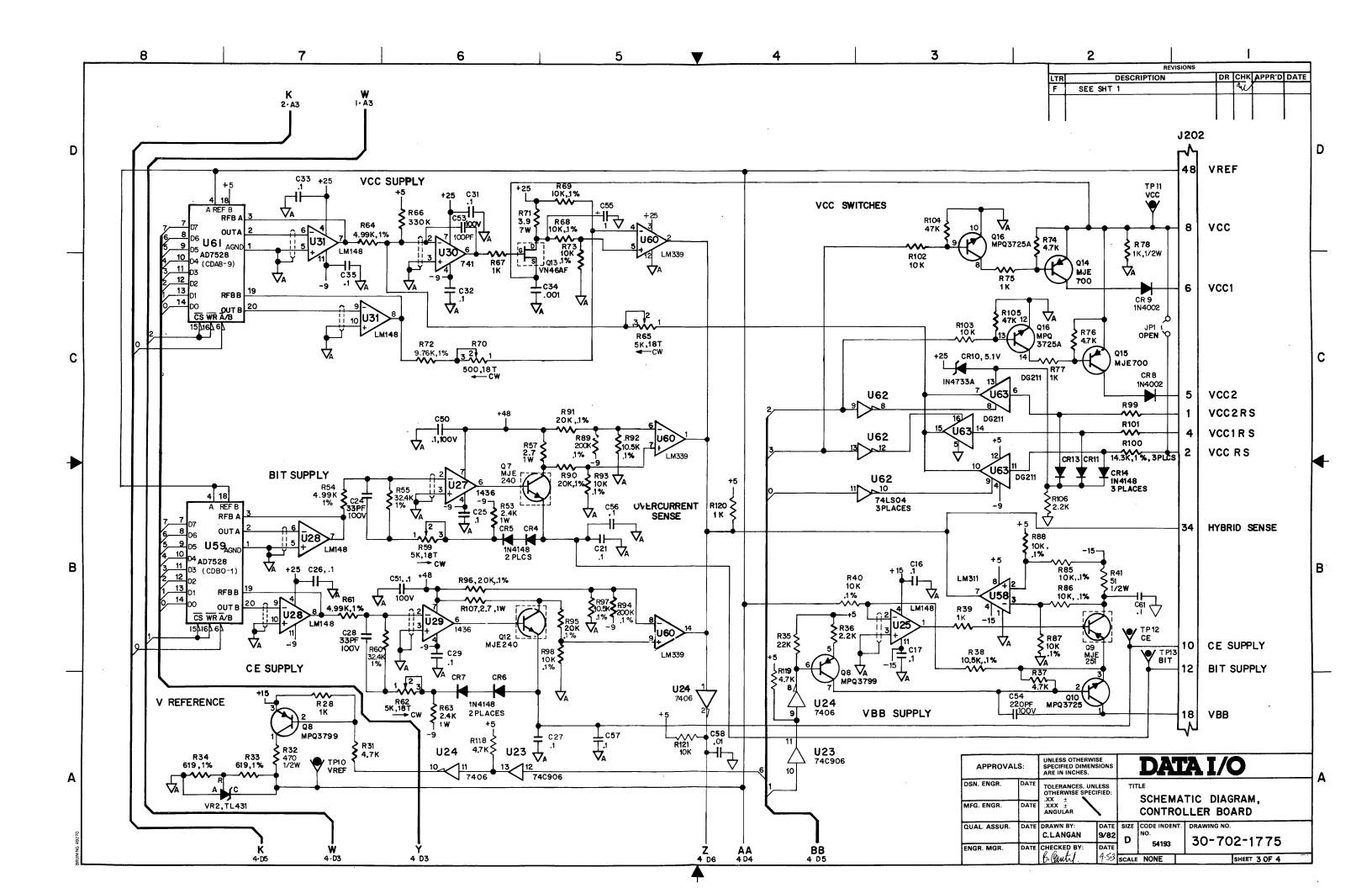

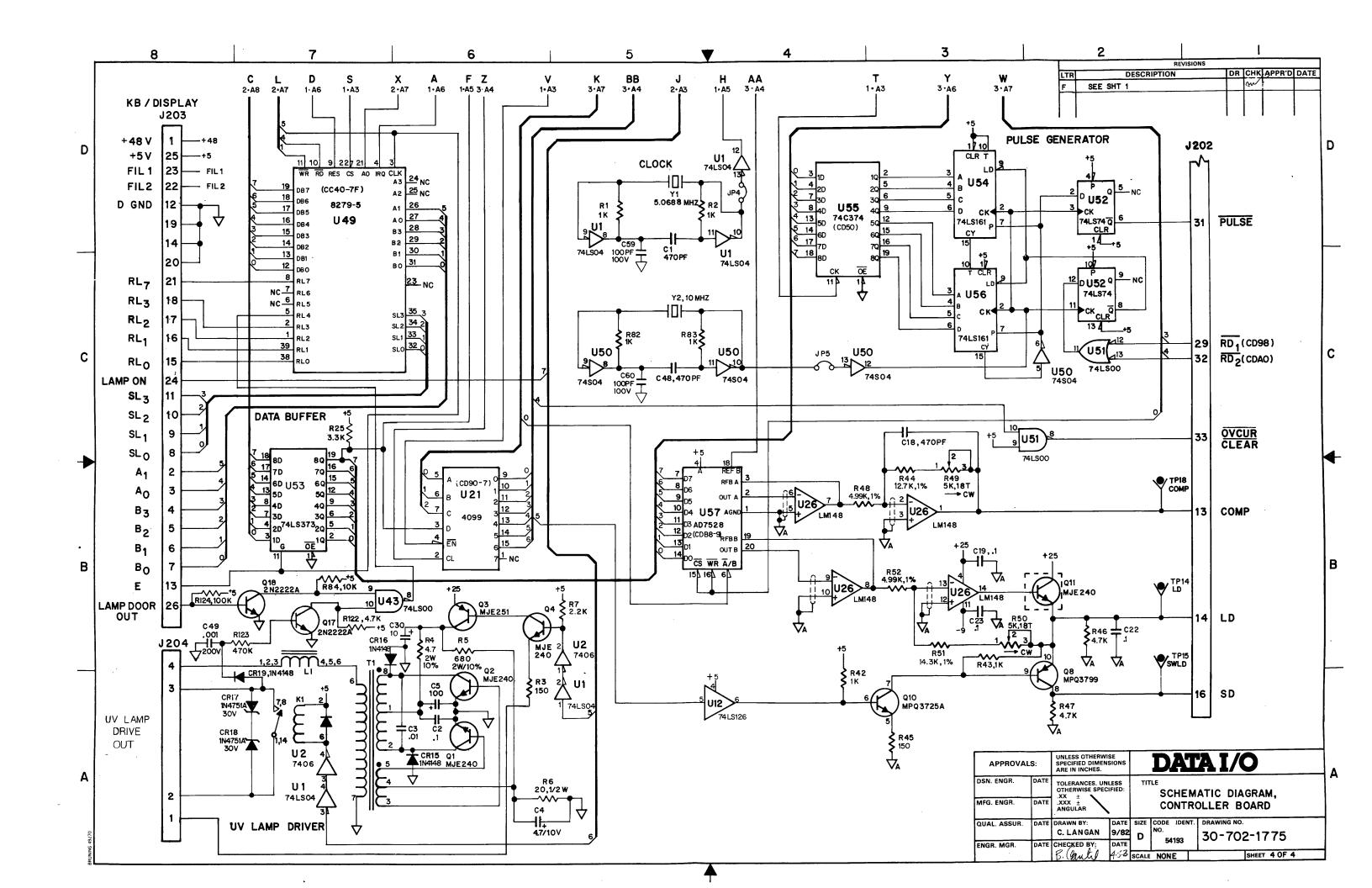

|     | 5.3.4 | Controller                                                         | 5-6 |

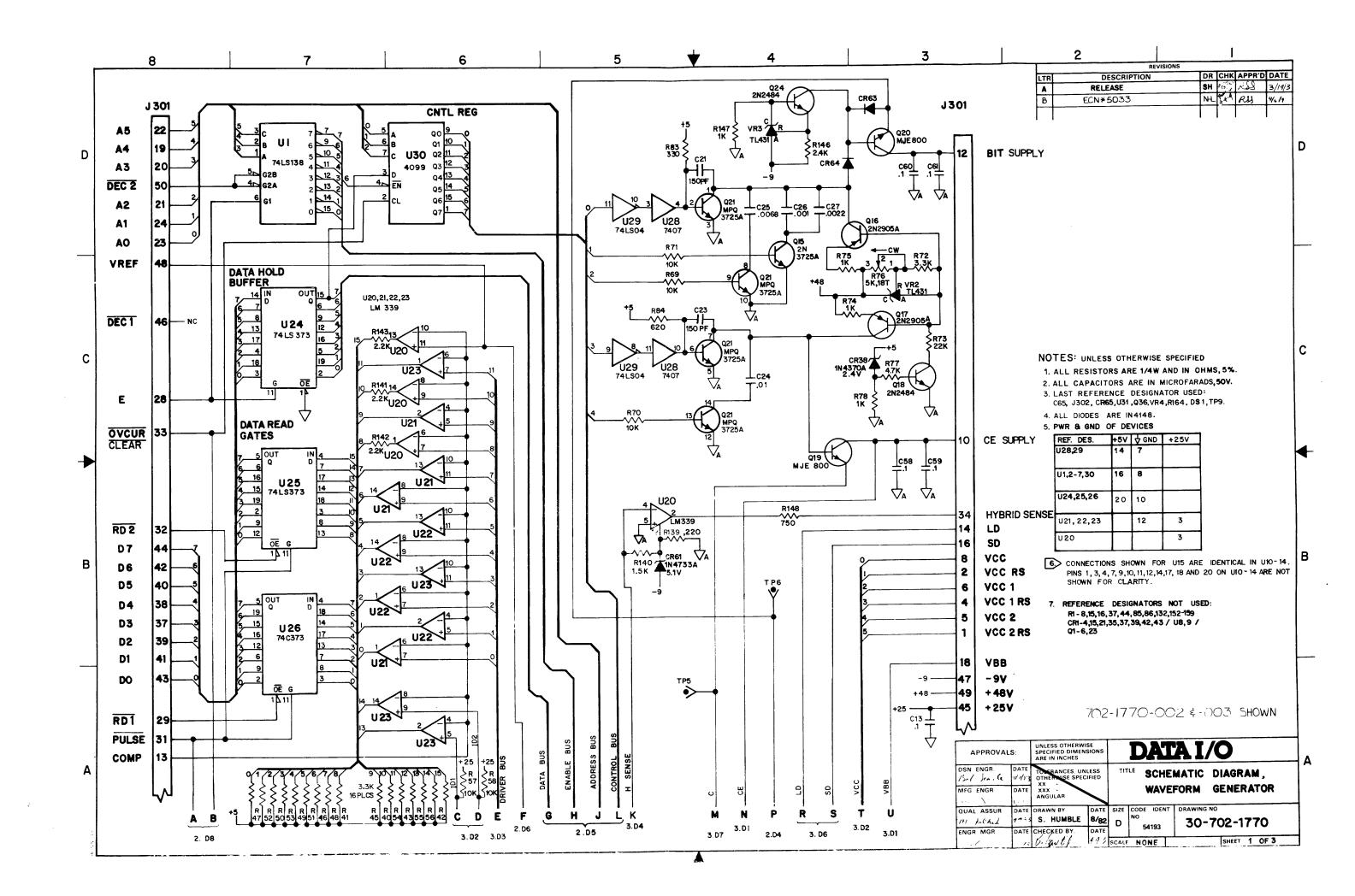

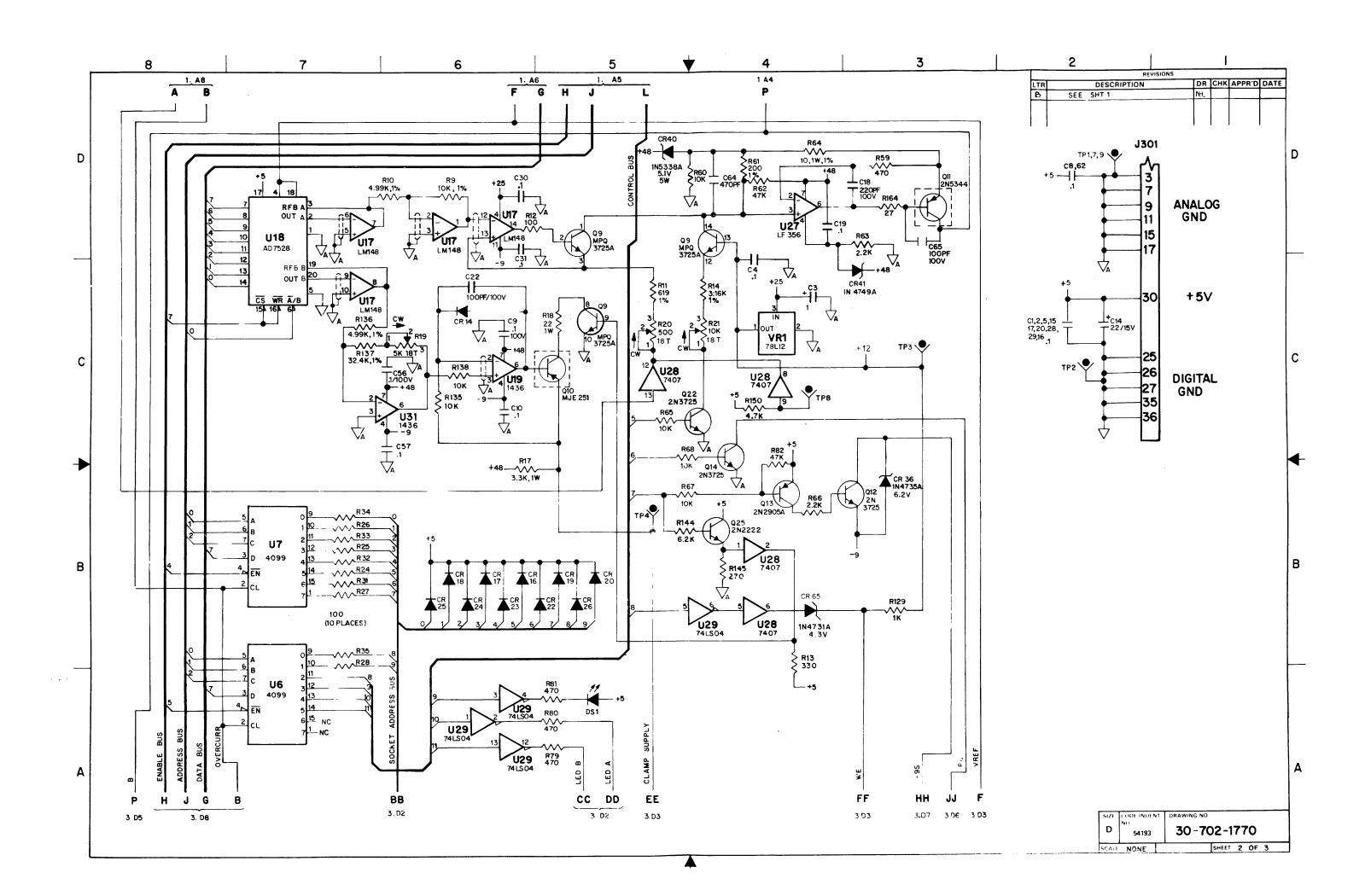

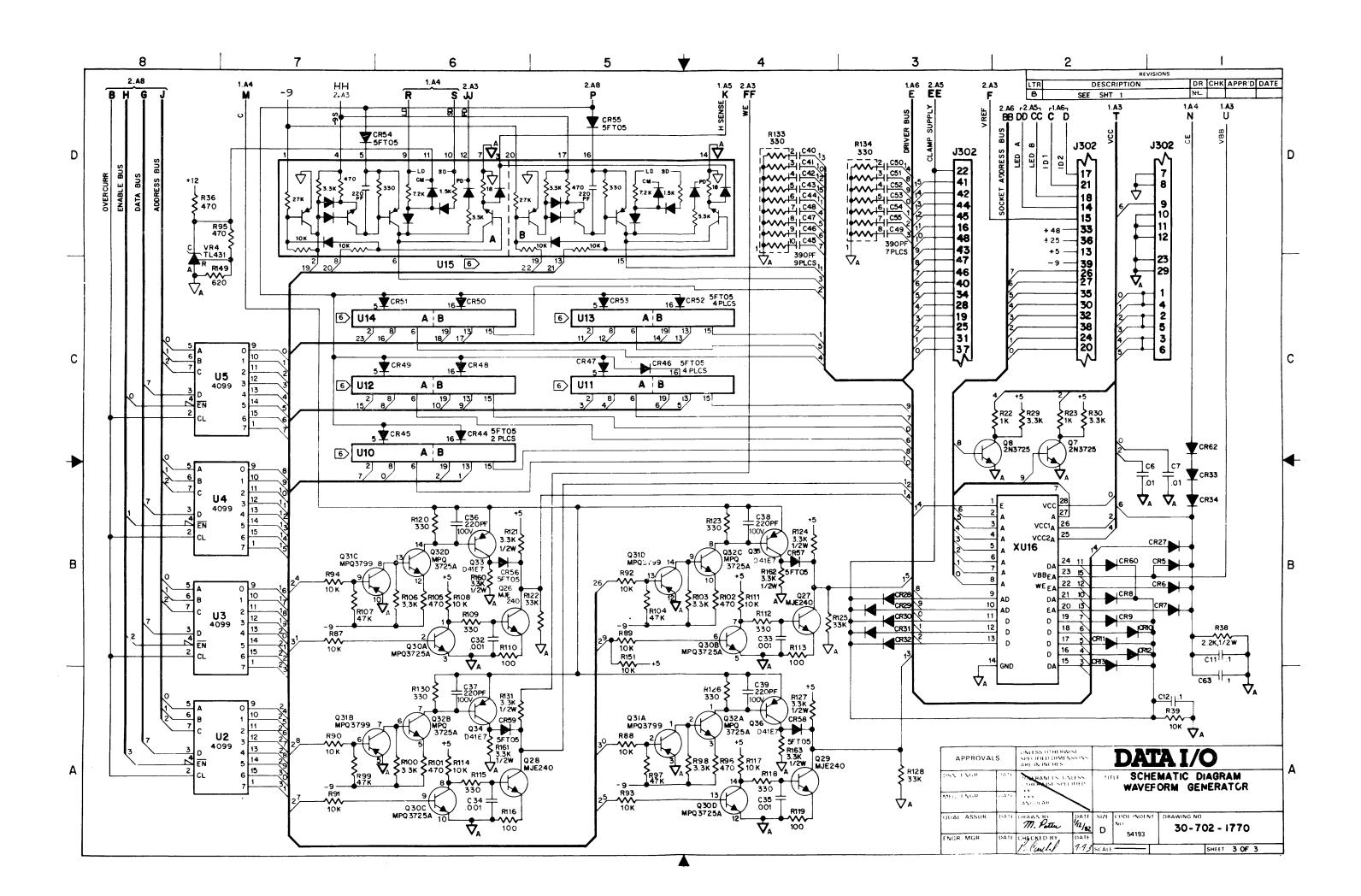

|     | 535   | Waveform Generation                                                | 5-7 |

APPENDIX A. DATA TRANSLATION FORMATS

APPENDIX B. REFERENCE MATERIAL

APPENDIX C. COMPUTER REMOTE CONTROL

APPENDIX D. SCHEMATICS

# **LIST OF FIGURES**

| 1-1        | Tasks Performed by the Keys on the 22A Keyboard                         | . 1-2 |

|------------|-------------------------------------------------------------------------|-------|

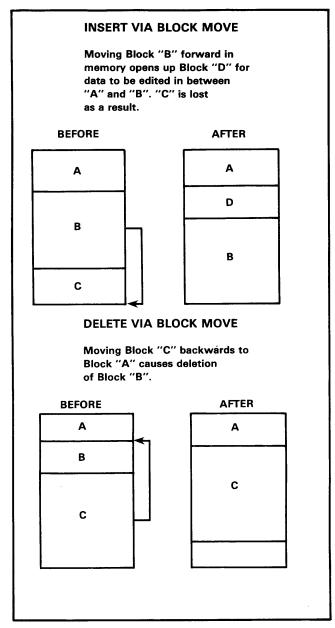

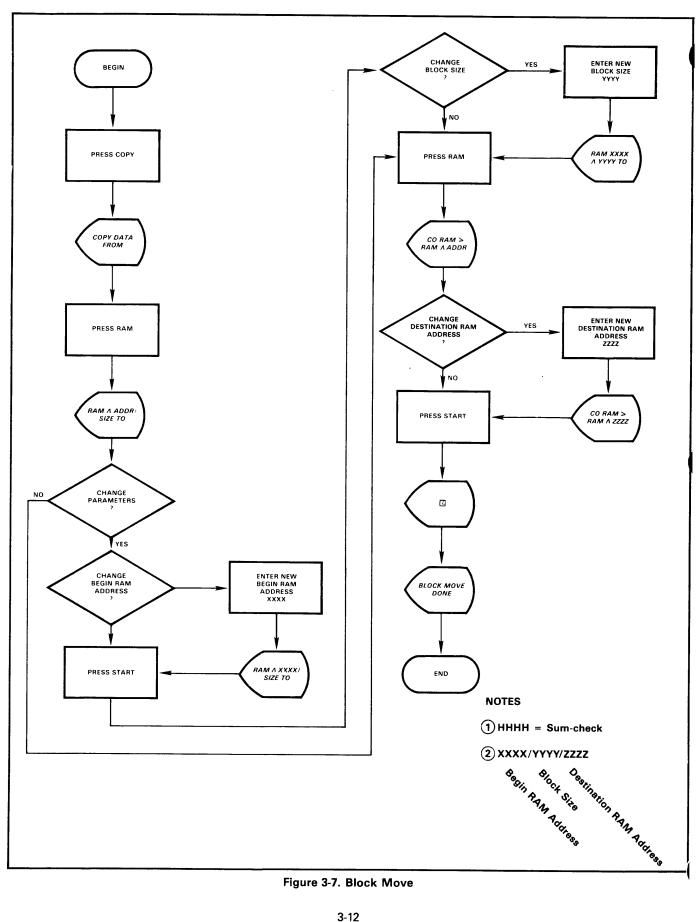

| 1-2        | Block Move                                                              | . 1-3 |

| 1-3        | Using the 22A Manual to Meet Your Programming Needs                     | . 1-4 |

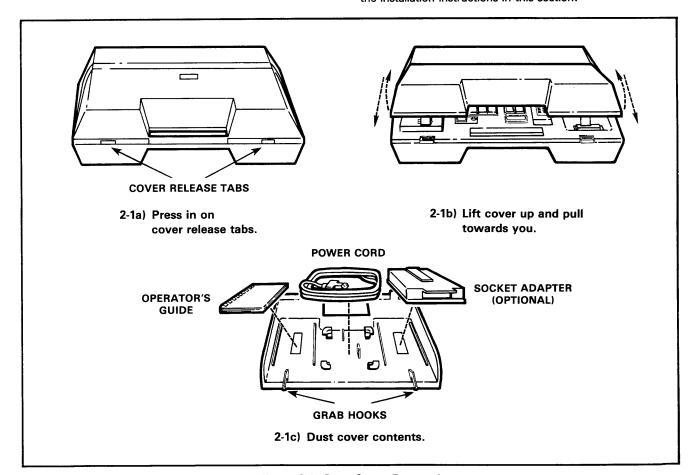

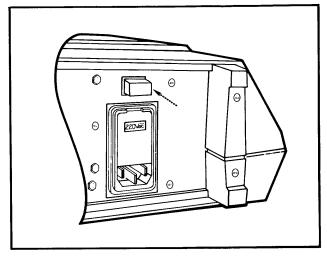

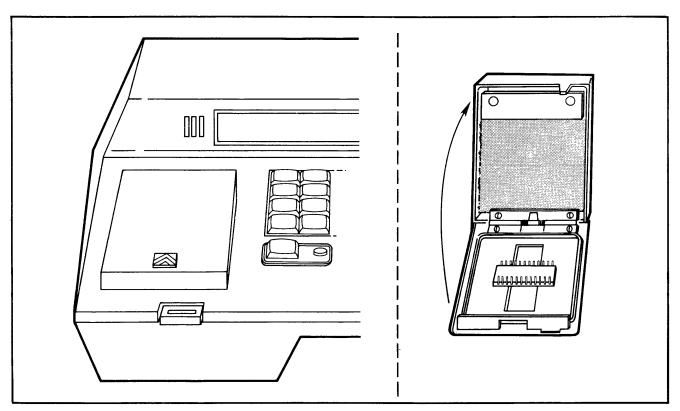

| 2-1        | Dust Cover Removal                                                      | . 2-1 |

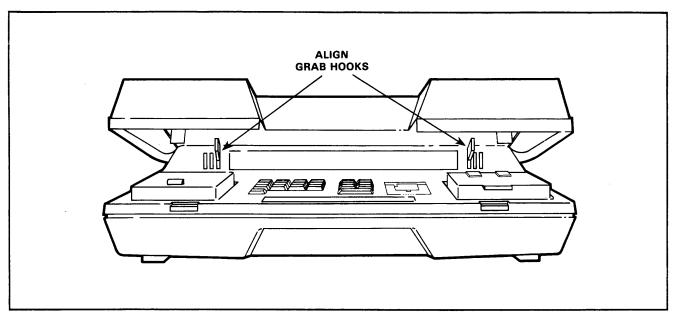

| 2-2        | Installing the Dust Cover                                               |       |

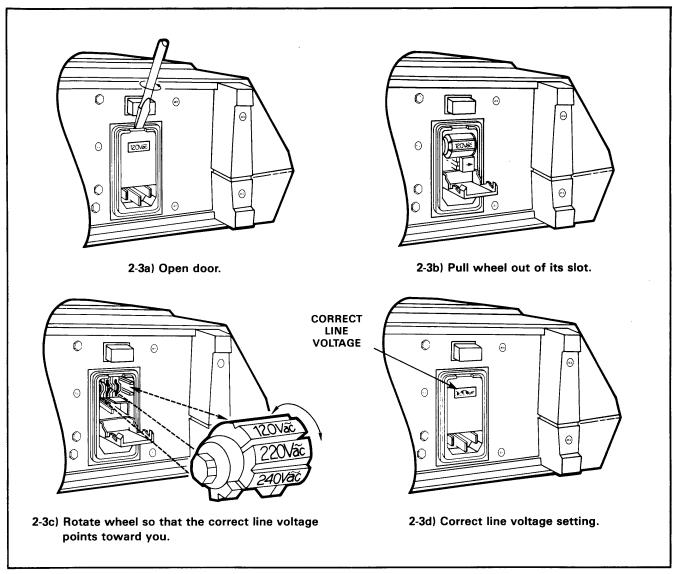

| 2-3        | Voltage Wheel Selector                                                  |       |

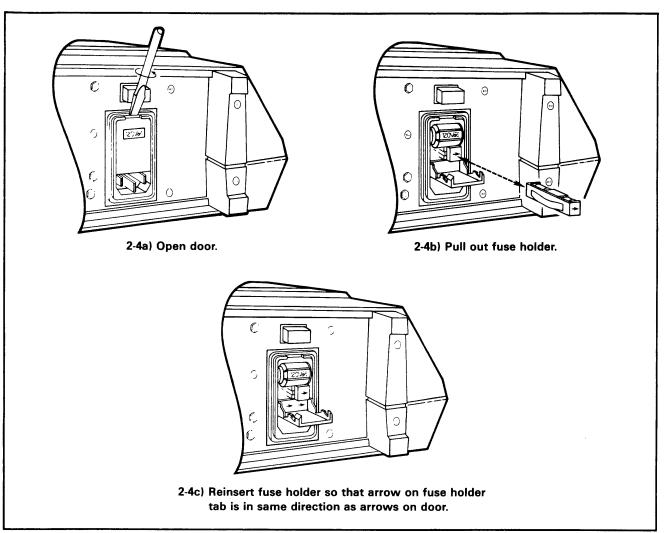

| 2-4        | Accessing the Line Fuse                                                 |       |

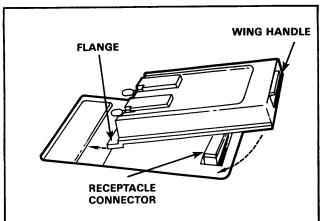

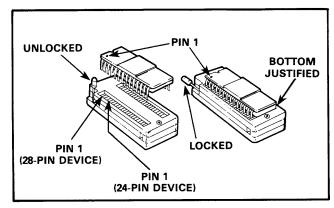

| 2-5        | Installing a Socket Adapter                                             |       |

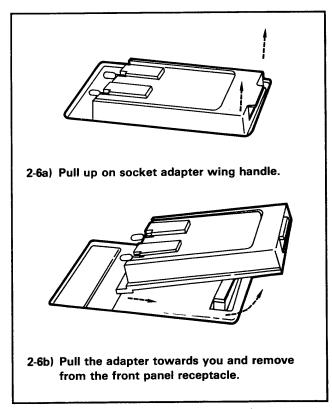

| 2-6        | Removing a Socket Adapter                                               |       |

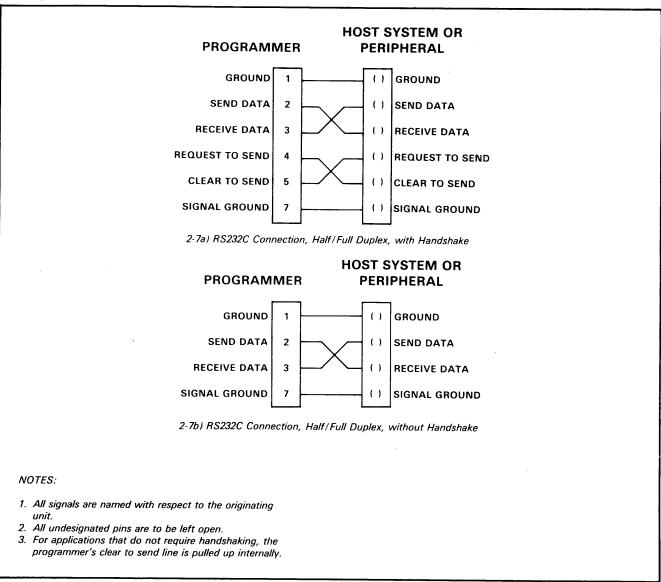

| 2-7        | Sample Interconnection Methods                                          | . 2-6 |

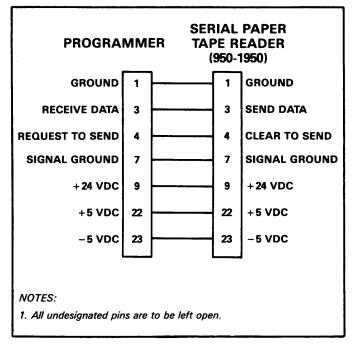

| 2-8        | Interconnection Method for Serial Paper Tape Reader                     | . 2-7 |

| 3-1        | Programmer Power Switch Location                                        |       |

| 3-2        | Device Installation                                                     |       |

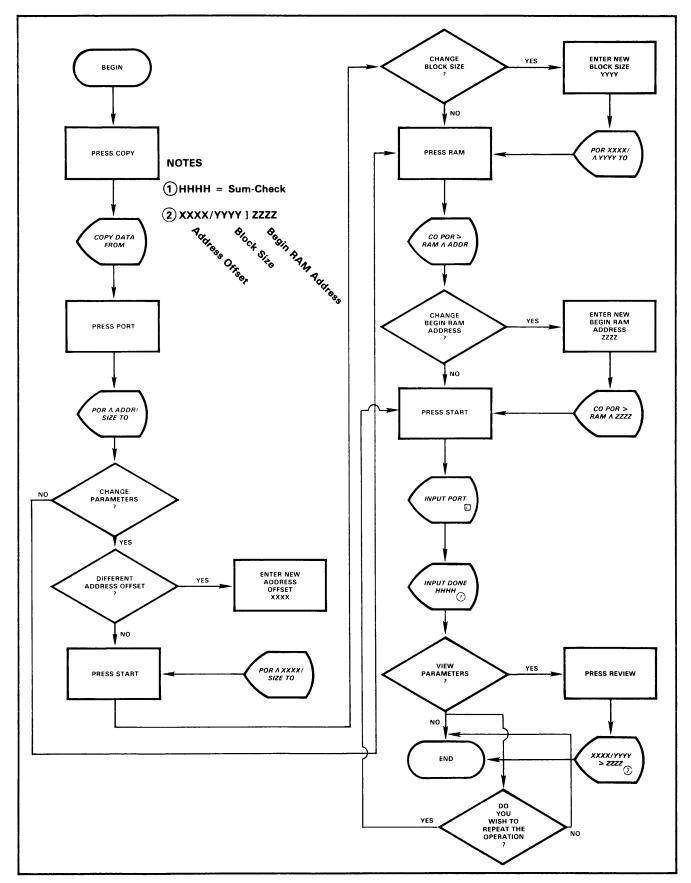

| 3-3        | Load RAM with Master Device Data                                        | 3-4   |

| 3-4        | Input from Port                                                         |       |

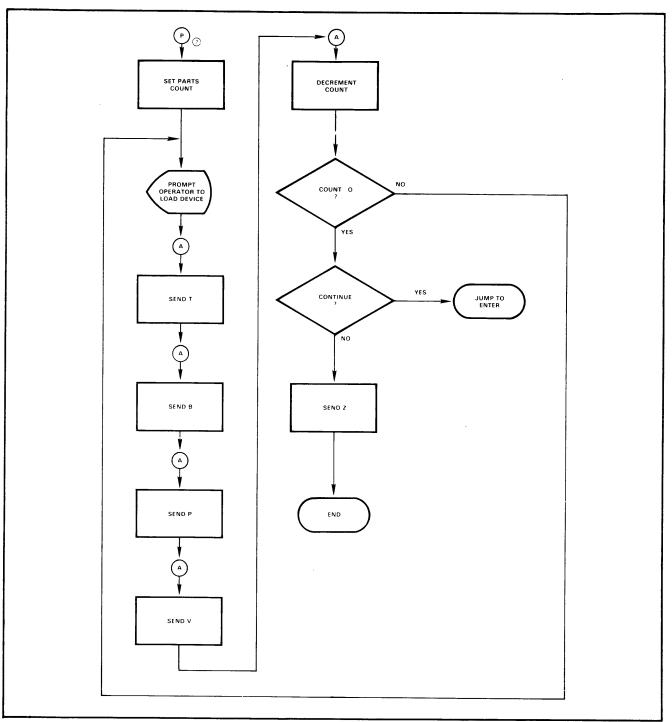

| 3-5        | Program Device                                                          |       |

| 3-6        | Output to Port                                                          |       |

| 3-7        | Block Move                                                              |       |

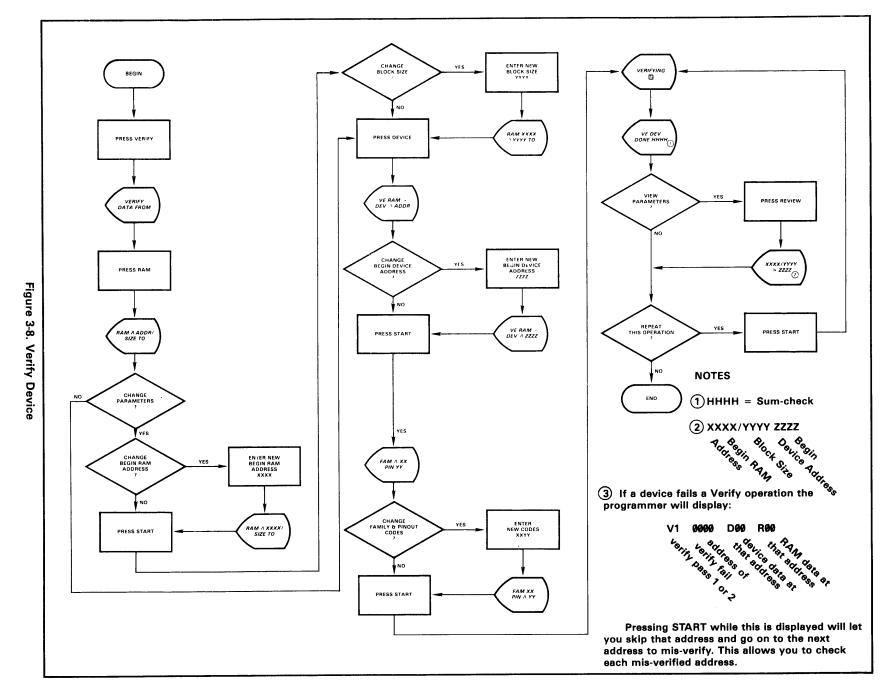

| 3-8        | Verify Device                                                           |       |

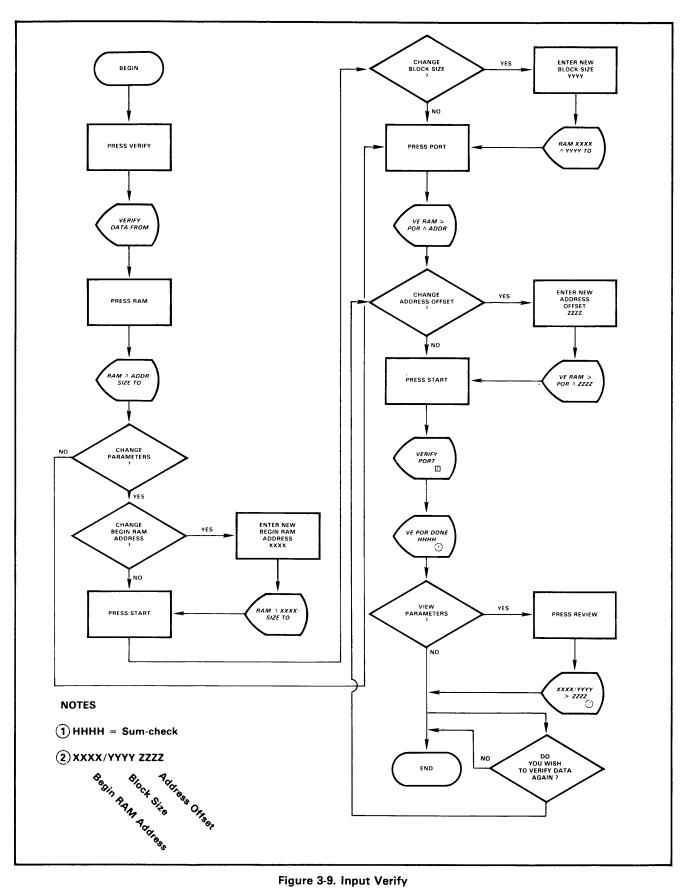

| 3-9        | Input Verify                                                            |       |

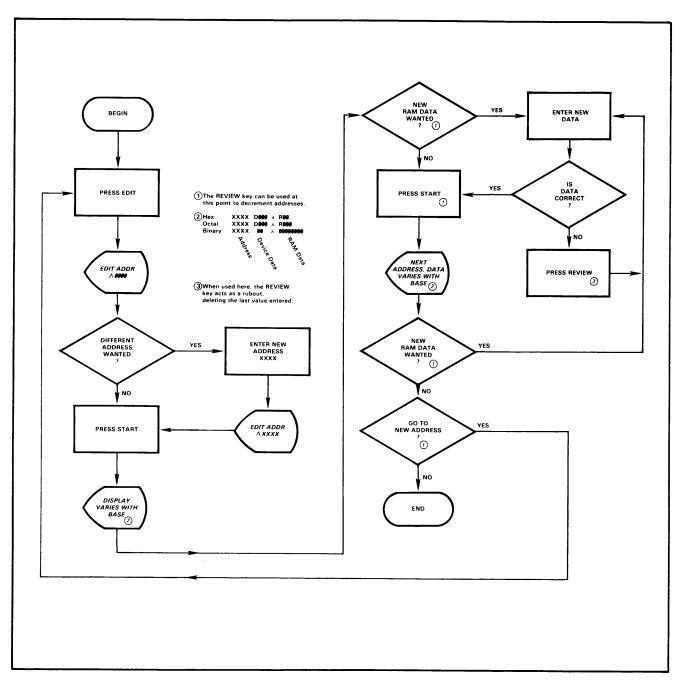

|            | Edit                                                                    |       |

|            | Opening the UV Lamp Cover Door                                          |       |

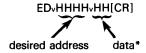

|            | Inputting Remote Control Parameters                                     |       |

|            | Select Function Menu in Remote Control                                  |       |

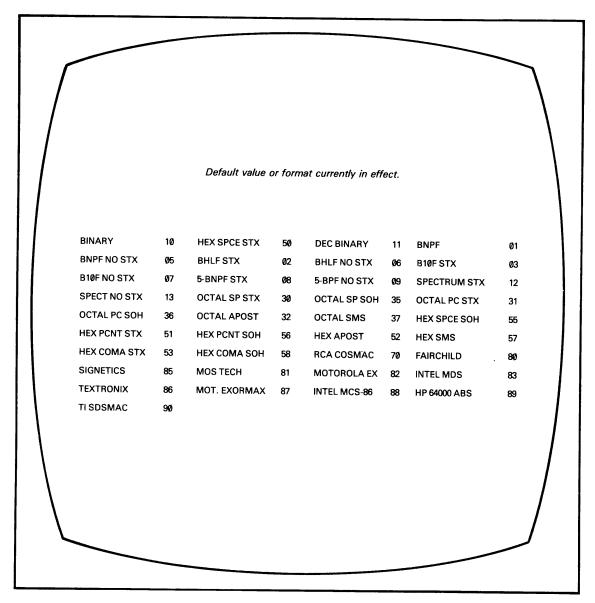

|            | Data Translation Format Menu in Remote Control                          |       |

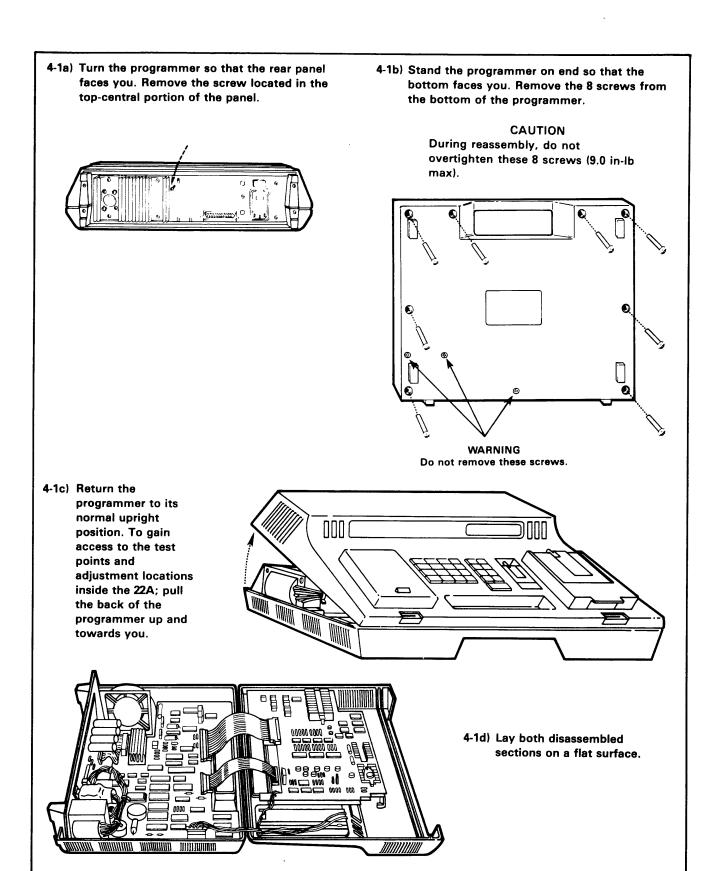

| 4-1        | Disassembly of the 22A                                                  |       |

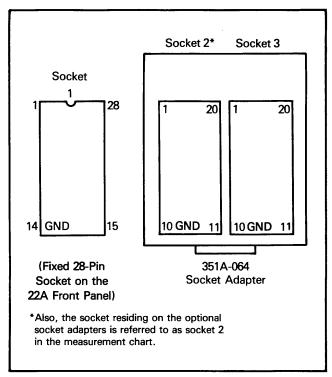

| 4-2        | Pin Numbers of the Device Sockets                                       |       |

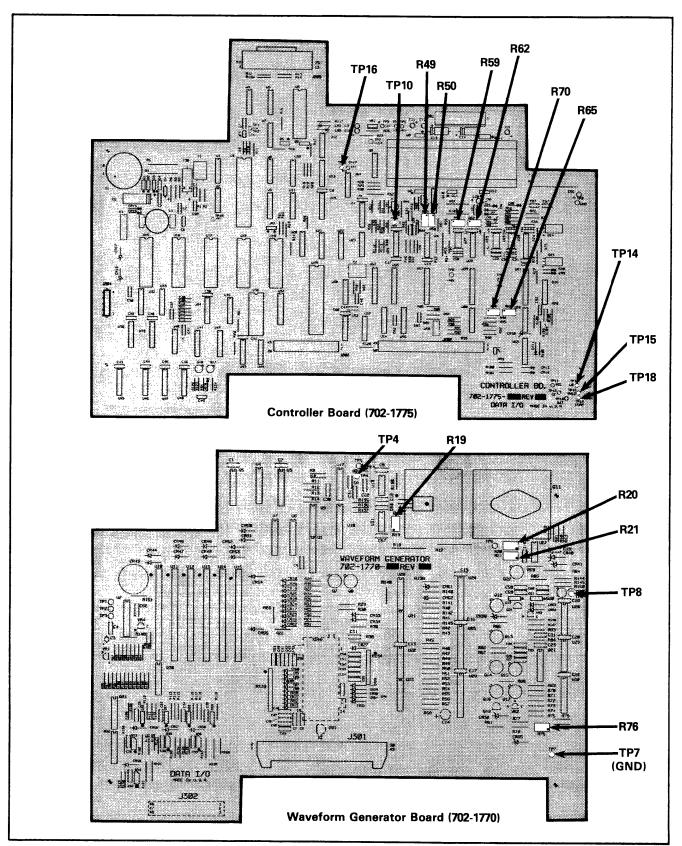

| 4-2<br>4-3 | Adjustment and Test Point Locations                                     |       |

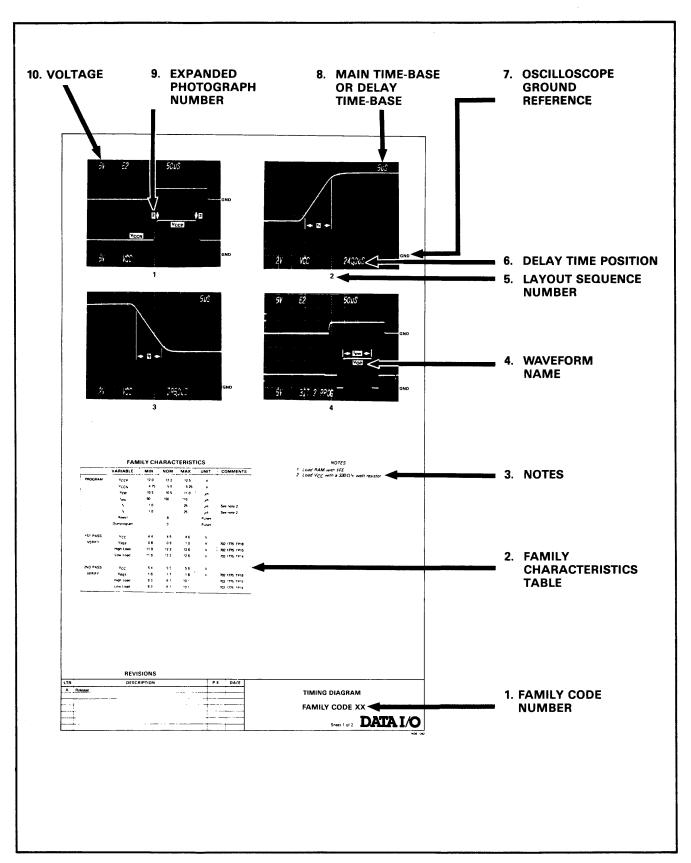

| 4-3<br>4-4 | Sample Timing Diagram                                                   |       |

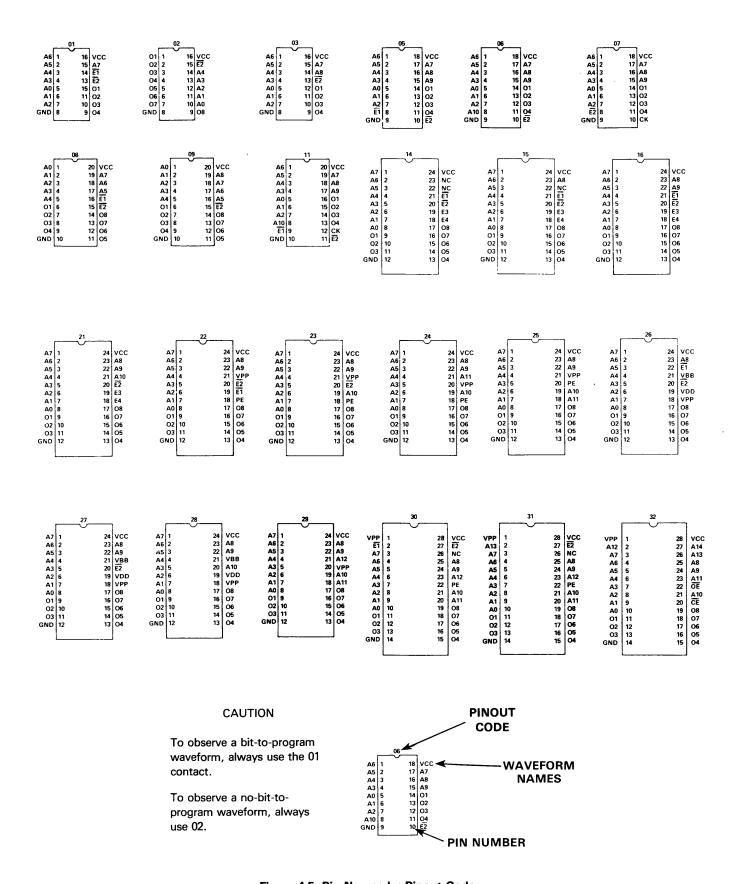

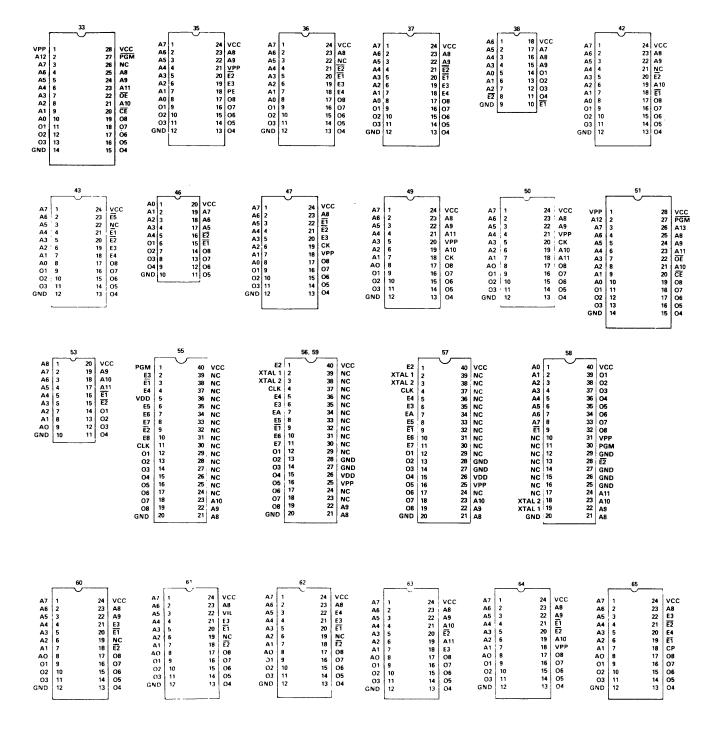

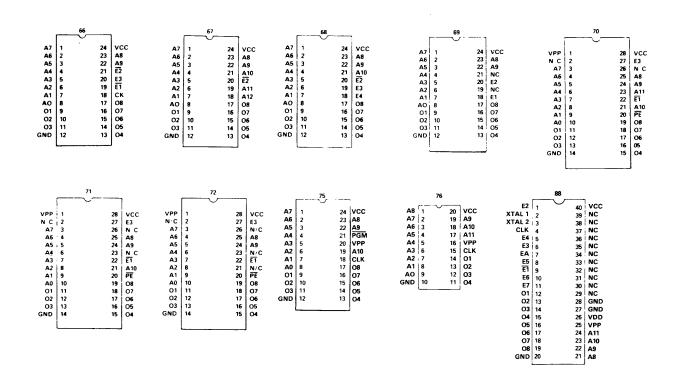

| 4-5        | Pin Names by Pinout Code                                                |       |

| 4-5<br>5-1 | System Block Diagram                                                    |       |

| 5-1<br>5-2 | Modular Bus                                                             |       |

| 5-2<br>5-3 | Address Map                                                             |       |

| 5-3<br>5-4 |                                                                         |       |

| 5-4<br>5-5 | Interconnection Diagram                                                 |       |

|            | Block Diagram, Power Supply                                             |       |

| 5-6        | Block Diagram, Keyboard/Display Function                                |       |

| 5-7        | Block Diagram, Controller Board                                         |       |

| 5-8        | Block Diagram, Waveform Generation                                      |       |

| A-1        | Formatting the Instrument Control Code and Data Translation Format Code |       |

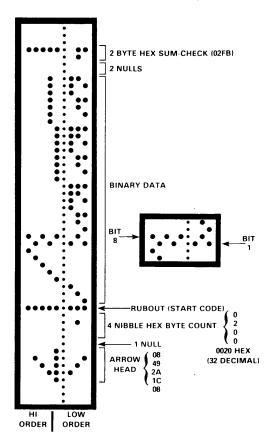

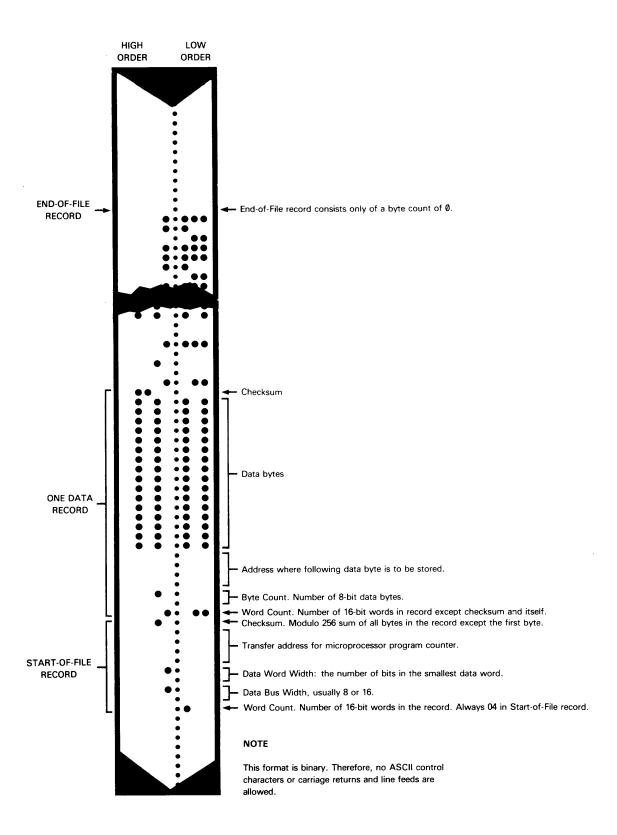

| A-2        | Input or Output Binary Tape                                             |       |

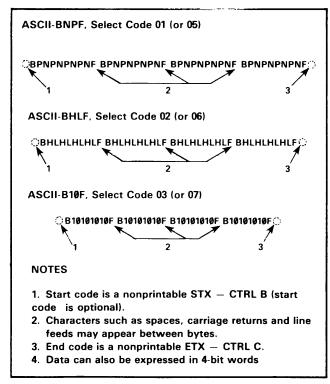

| A-3        | ASCII Binary Formats                                                    |       |

| A-4        | Spectrum Format                                                         |       |

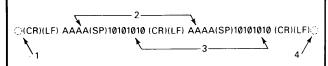

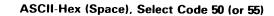

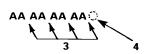

| A-5        | ASCII-Octal and Hex Formats                                             |       |

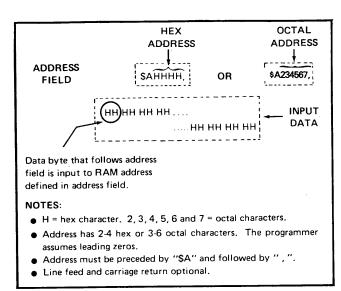

| A-6        | Optional Address Field in ASCII-Octal and Hex Formats                   |       |

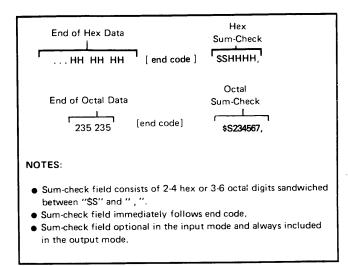

| A-7        | Syntax of the Sum-check Field in I/O Operations                         |       |

| A-8        | Specifications for RCA Cosmac Data Files                                |       |

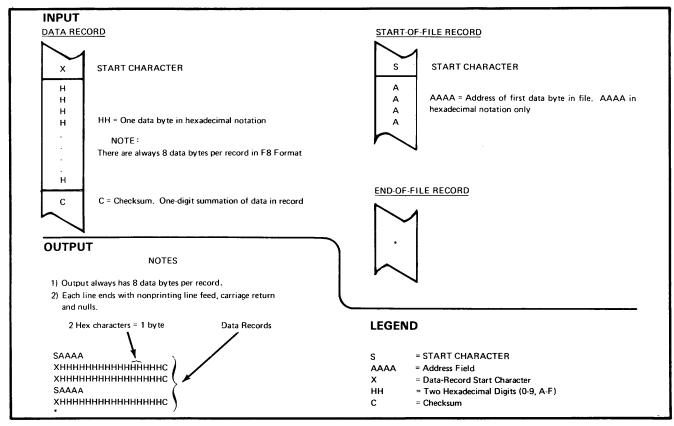

| A-9        | Specifications for Fairchild Fairbug Data Files                         |       |

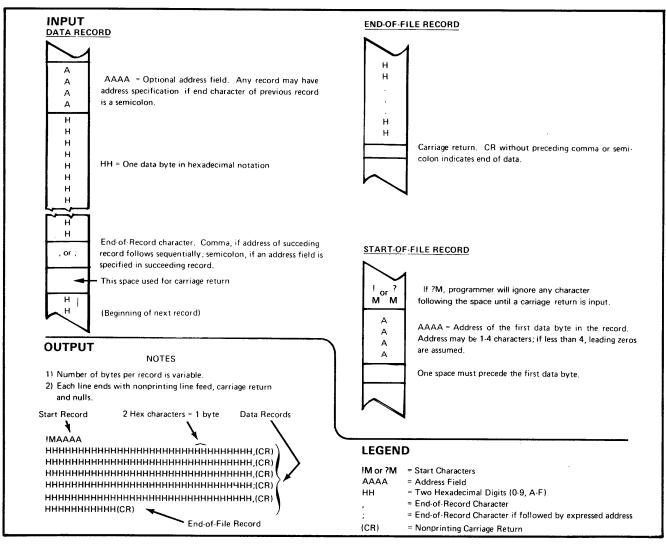

|            | Specifications for MOS Technology Data Files                            |       |

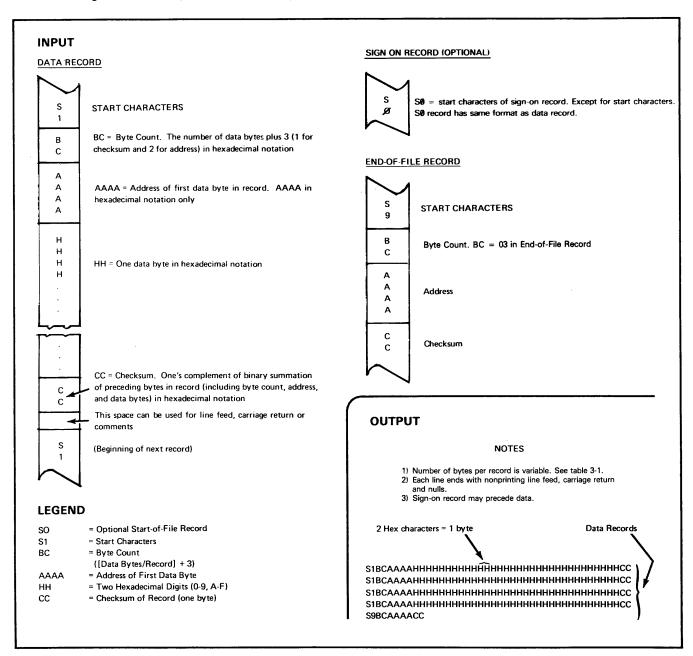

|            | Specifications for Motorola Data Files                                  |       |

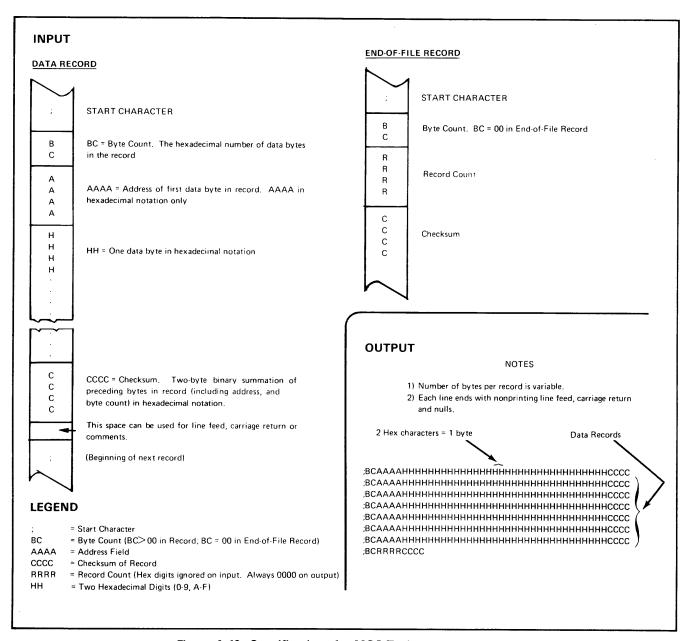

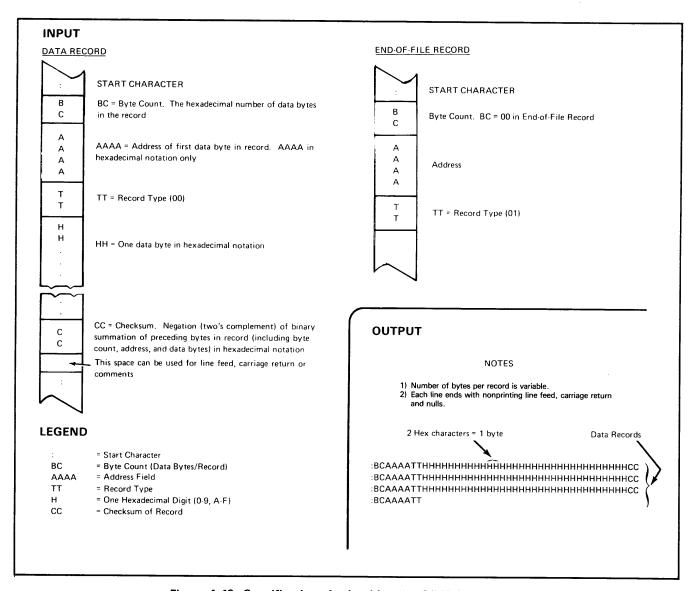

|            | Specifications for Intel Intellec 8/MDS Data Files                      |       |

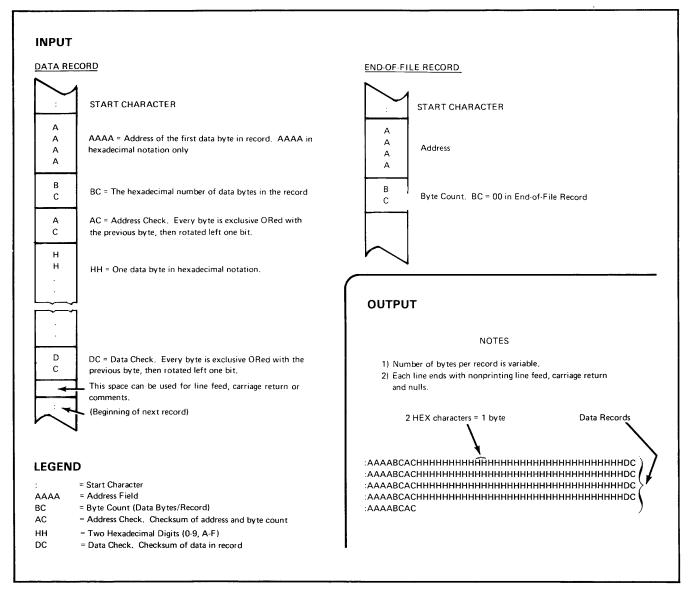

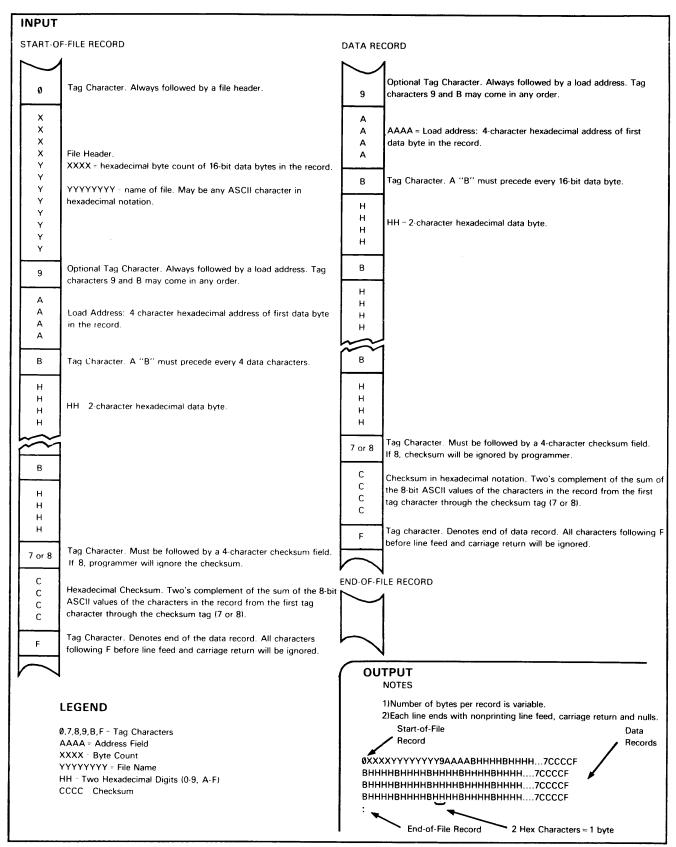

|            | Specifications for Signetics Absolute Object Data Files                 |       |

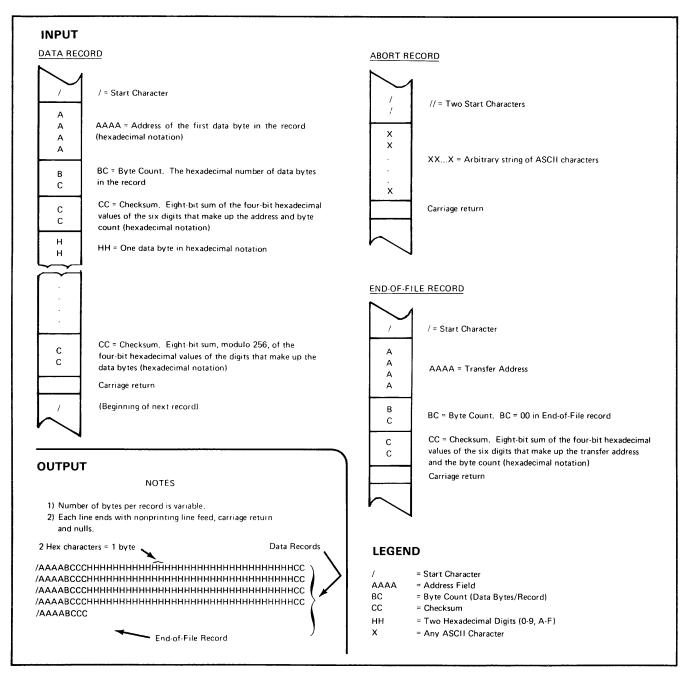

|            | Specifications for Tektronix Hexadecimal Data Files                     |       |

|            | Specifications for Motorola Exormax Data Files                          |       |

|            | Specifications for Hewlett Packard Absolute Format Data Files           |       |

| A-17       | Specifications for Texas Instruments SDSMAC Data Files                  | A-16  |

| B-1 | Sample Sum-check Calculation                           | B-1  |

|-----|--------------------------------------------------------|------|

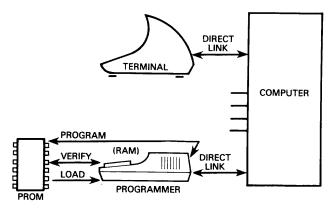

| C-1 | Computer Remote Control Components                     | C-1  |

| C-2 |                                                        |      |

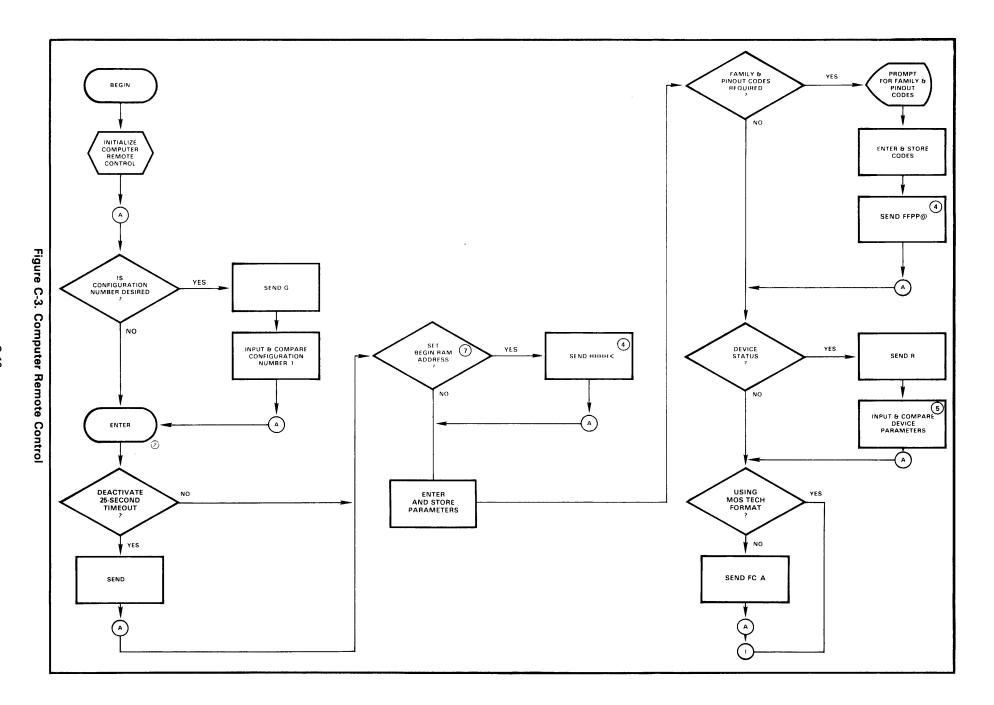

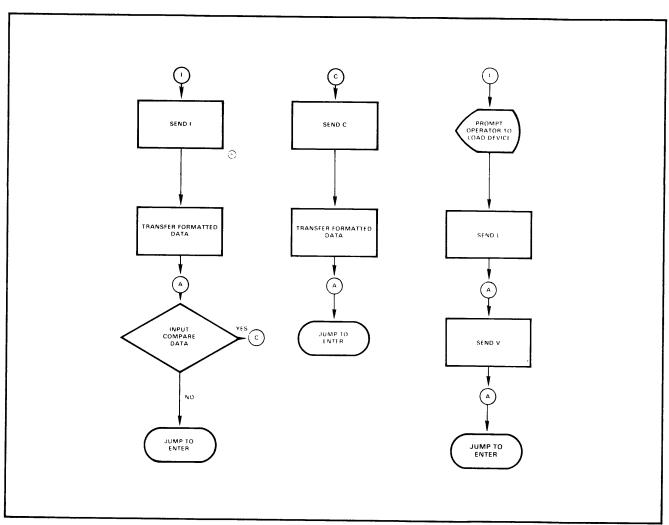

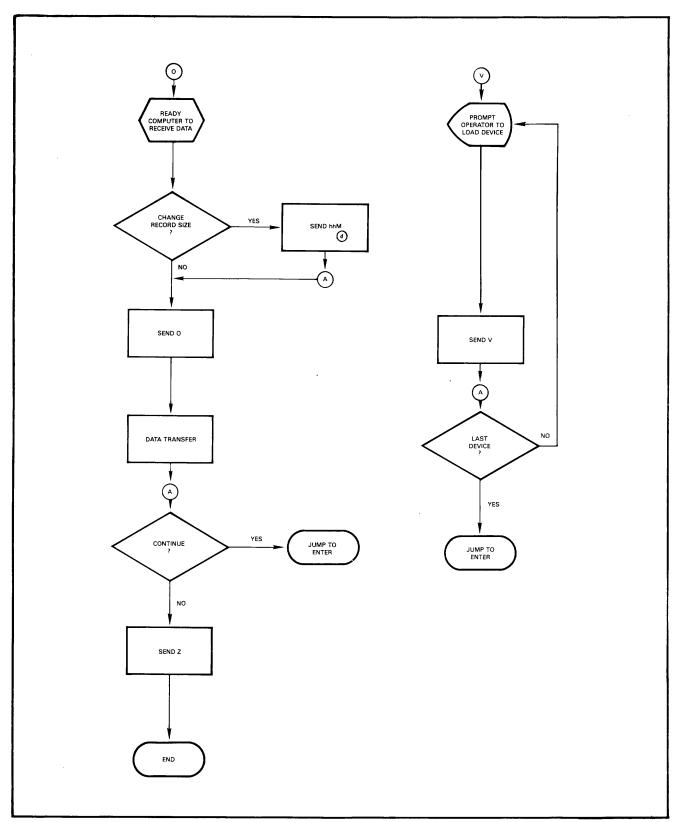

| C-3 | Computer Remote Control                                | C-10 |

|     |                                                        |      |

|     |                                                        |      |

|     |                                                        |      |

|     | LIST OF TABLES                                         |      |

|     | LIGI OI IADELO                                         |      |

| 1-1 | Family and Pinout Codes                                | 1-6  |

|     | Conductor Colors by Country/Continent                  |      |

|     | Serial Interface Connector Pin Assignment              |      |

|     | Power Down Save Parameters and Original Default States |      |

|     | Select Functions                                       |      |

| 3-3 | COPY and VERIFY Keyboard Operations                    | 3-28 |

| 3-4 | Address Parameters                                     | 3-28 |

| 3-5 | Command Entry in Remote Control                        | 3-28 |

|     | Remote Control Commands                                |      |

|     | Error Codes                                            |      |

|     | I/O Address Map                                        |      |

|     | Power Supply Fuse Requirements                         |      |

| A-1 | Instrument Control Codes                               | A-1  |

|     | Pata Translation Formats                               |      |

|     | Glossary                                               |      |

|     | Abbreviations                                          |      |

|     | Cross-Reference Chart of Number Bases                  |      |

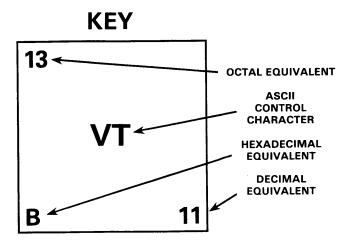

|     | ASCII & IEEE Code Chart                                |      |

|     | ASCII Control Characters                               |      |

|     | Response Characters                                    |      |

|     | Command Summary                                        |      |

| C-3 | Data Translation Formats                               | C-8  |

## **SECTION 1**

## INTRODUCTION

### 1.1 GENERAL INFORMATION

The 22A is Data I/O's fully integrated portable programmer. It is capable of programming many different kinds of PROMs. For a list of specific devices that the 22A programs, refer to the information in table 1-1. Most MOS PROMs can be programmed by using the fixed 28-pin socket located to the right of the 22A's keyboard. Other devices may require the use of additional socket adapters listed in table 1-1.

In addition to the programming convenience of programming many devices in a single package, the 22A contains a built-in ultra violet (UV) lamp for erasing MOS devices.

The 22A utilizes a full hexadecimal keypad and a 16-character alphanumeric florescent display to provide data entry and editing from the front panel. A standard 32K byte x 8 data RAM gives you the flexibility to handle large amounts of data. A serial I/O port is also standard. The RS232 port provides the ability to interface to different kinds of peripheral equipment for data transfers and remote control operations.

### 1.1.1 THE 22A APPROACH TO PROGRAMMING

Values for programming variables, including pinouts, voltage levels and timing are stored in firmware tables within the 22A. When you choose the family and pinout codes for a particular device, the programmer uses the information in these tables to assemble a specialized programming routine in scratch RAM. This method allows high-speed operation with minimum firmware overhead.

To maximize control speed during programming, the 22A makes extensive use of addressable latches for control signals. For flexibility in waveform generation, digital-to-analog converters (DACs) control all major power supplies, with several rise and fall times selected by firmware.

## 1.2 THEORY OF OPERATION

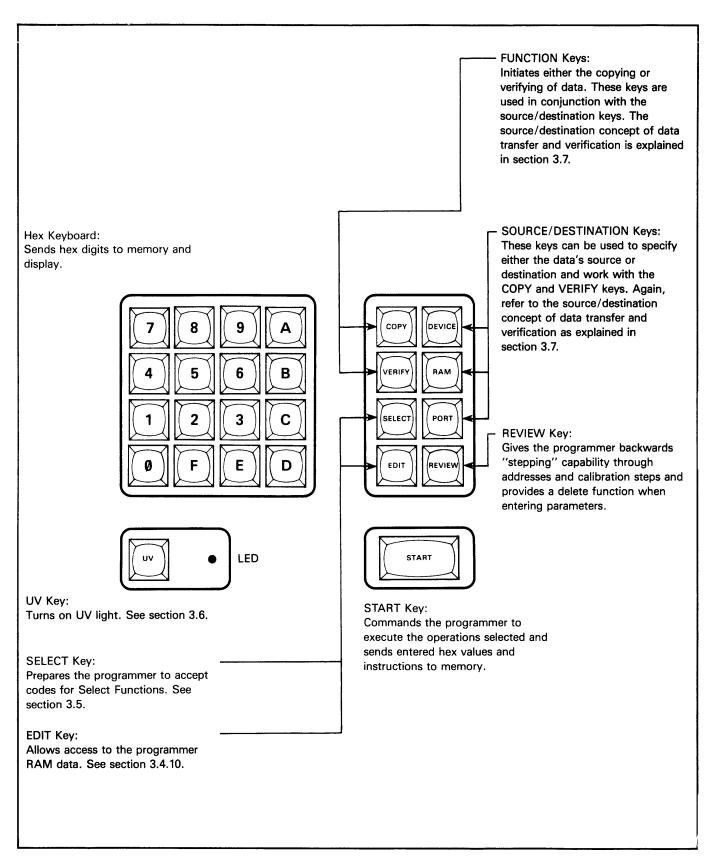

The 22A is easy to operate. As you can see from figure 1-1, each of the four major operations of the 22A has its own key (blue) assignment on the front panel keyboard. Each of these mode keys and their uses are discussed in the following subsections.

Operations performed by the 22A consist of:

- Copy—moves data from a source (device, RAM or Port) to a destination (device, RAM or Port).

- Verify—compares data between a source and destination.

### NOTE

Both Copy and Verify operations follow the source/destination method of data transfer and verification. In short, the operator initiates the operation by choosing either the COPY or VERIFY key and then specifies the source of data (device, RAM or port) and then the destination for that data (again, either device, RAM or port). This concept is explained in detail in section 3.7.

- Edit—changes data at selected addresses within the programmer RAM.

- Select Function—allows you to either manipulate RAM data or change various operating parameters.

Section 3 of this manual (Operation) provides specific step-by-step instructions on how to execute the operations listed in the following subsections.

### 1.2.1 THE COPY KEY

The COPY key is used to copy data from one medium to another or one RAM location to another. When the COPY key is used, data is moved from the source to the destination; for example, from the programmer data RAM to a blank device in the socket. At the completion of this operation the device will contain a copy of the data in the programmer data RAM - the device is now "programmed". The "source/destination" concept is explained in section 3.7.

There are five basic types of copy operations. Instructions for performing the specific bulleted operations which follow, are located in section 3.

- A data transfer from a device to the programmer RAM is a Load operation.

- Load with Master Device Data

- A data transfer from the serial port to the programmer RAM is an Input operation.

- Input from Port

- A data transfer from the programmer RAM to a device is a Program operation.

- Program Device

Figure 1-1. Tasks Performed by the Keys on the 22A Keyboard

- A data transfer from the programmer RAM to the serial port is an Output operation.

- Output to Port

- A data transfer that moves a block of RAM data to another location within RAM is a Block Move.

- Block Move

LOAD. A load operation consists of taking programming data from a master device and transferring it to the programmer RAM. When the data transfer is complete, the 22A calculates the sum-check (see Glossary for definition) of the loaded data and displays it.

**INPUT.** In an input operation, data received at the serial port is translated and transferred to the programmer RAM. When completed, the programmer calculates and displays the sum-check of the data. If a sum-check has been sent with the data from the serial port, the programmer will compare the two and signal an error if they do not match.

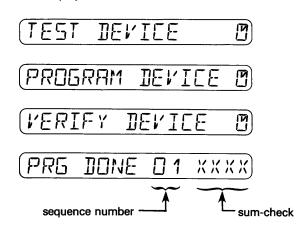

**PROGRAM.** A program operation duplicates the data in the programmer RAM into a device. Programming is automatic starting with an illegal bit test and a blank check (see Glossary for definition) to insure that the device can be programmed. Data is then programmed into the device in the socket one byte at a time. This continues until all data bytes have been programmed into the device. After programming is completed, the data in the device is automatically compared with the source data to insure correct programming.

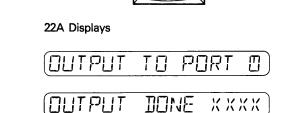

**OUTPUT.** In an output operation, data from the programmer RAM is translated and transferred to the serial port.

**BLOCK MOVE.** A Block move is accomplished by using the COPY key. In a Block Move, blocks of data within RAM can be rearranged. Refer to figure 1-2.

## 1.2.2 THE VERIFY KEY

The VERIFY key is used to make a byte-by-byte comparison of data in two locations, one referred to as the "source" and one as the "destination". The source/destination method of syntax is explained in section 3-7.

There are two types of Verify operations. Instructions for performing the bulleted operations are located in Section 3.

- Verify Device. In a verify device operation, data from the device (the destination) is compared byte-by-byte twice with the data in RAM (the source). On the first pass (first comparison), parametric checking is done by lowering V<sub>CC</sub> within the manufacturer's specified lower level. On the second pass, V<sub>CC</sub> is raised to the upper level specification range.

- Verify Device

- Input Verify. In an input verify operation, incoming data from the serial port is compared byte-by-byte with the data in RAM.

- Input Verify

Figure 1-2. Block Move

### 1.2.3 THE EDIT KEY

The EDIT key allows you to view and change data at specified RAM addresses. Section 3 provides specific details.

### 1.2.4 THE SELECT KEY

The SELECT key allows you to change certain operational parameter default values, perform RAM data manipulations and access certain less frequently used operations. These operations are referred to in this manual as Select Functions. Detailed Select Function information and operation is located in section 3.5.

### 1.3 HOW TO USE THIS MANUAL

Using the 22A programmer is easy. Figure 1-3 illustrates the programming components of the 22A. The illustration explains how to set these components up so you can start programming right away. It is a central reference point directing you to specific locations within the manual.

## 1.4 SPECIFICATIONS

The following subsections describe the major components and power requirements of your programmer.

### Situation **Reference Point** Situation **Reference Point** 1. Plugging in your programmer and Consult Section 4. If, according to table 1-1, a special Read section 2.5 applying power 2.4.4 socket adapter is required to program for installation this device... instructions 2. Serial I/O Operation Yes Read Section 2.6 5. Select your programming operation. Read section 3.1 No Continue to next 6. Execute the operation. Consult section 3.4 step 7. Data manipulation required? Refer to section 3.5 3. Select the device you wish to 8. Remote Control operation? Read section 3.8 program, and its corresponding family and pinout code, from table 1-1. **DUST COVER** Instructions for installing or removing your dust cover are located in section 2.2. **OPERATOR GUIDE POWER CORD OPTIONAL SOCKET ADAPTER** Instructions for plugging in your The Operator Guide is located inside Instructions for installing or the dust cover. It contains reference programmer and applying power are removing a socket adapter are information for commonly used located in section 2.4.4. located in section 2.5. operations.

Figure 1-3. Using the 22A Manual to Meet Your Programming Needs

### 1.4.1 MAJOR COMPONENTS

The 22A is a self-contained portable programmer. This unit has a 32K x 8 data RAM.

The unit's serial I/O port can be used to accept or transmit data from a peripheral device, or allow for remote control operations.

Since all programming electronics reside within the programmer, there is no need for extra programming modules; however, certain devices do require a socket adapter for programming. Most MOS PROMs can be programmed by using the fixed 28-pin socket located on the programmer's front panel. Table 1-1 provides a quick reference to the socket (or socket adapter) you need to use to program your device.

Voltages are current limited and regulated to meet the device manufacturers' programming specifications.

### 1.4.2 POWER REQUIREMENTS

The following are the 22A's power requirements. Section 2.3 discusses power connection.

• Operating Voltages: 100, 120, 220, 240 VAC (± 10%)

• Frequency Range: 48 - 62 Hz

Input Power: minimum 28 watts maximum 72 watts

The 22A's physical and environmental specifications are listed below:

| <ul> <li>Dimensions</li> </ul> | 34 x 43 x 11 cm      |

|--------------------------------|----------------------|

|                                | (13.5" x 17" x 4.5") |

WeightOperating Temperature Range

5° to 45° (41° to 113°F)

16 lbs.

Storage

Temperature Range

-40° to 70° (-40° to 158°F)

Relative Humidity

90% noncondensing

### 1.4.3 DATA TRANSLATION FORMATS

Appendix A provides specific details for each data translation format available on the 22A.

### 1.5 FIELD APPLICATIONS SUPPORT

Data I/O has Field Applications Engineers (FAEs) who can provide you additional information about interfacing Data I/O products with other equipment or answer your questions about problems you may have with your equipment.

The location of the FAE nearest you is given on the address list at the back of this manual. Call your FAE if you have any questions or problems.

### 1.6 WARRANTY

Data I/O equipment is warranted against defects in materials and workmanship. The warranty period is one year and begins when you receive the programmer. The warranty card at the back of this manual explains the length and conditions of the warranty. For warranty service, contact your nearest Data I/O Service Center.

### 1.7 SERVICE

Data I/O maintains Service Centers throughout the world, each staffed with factory trained technicians to provide prompt, quality service. A list of all the Service Centers is located at the back of this manual.

### 1.8 ORDERING

To place an order for equipment, contact your Data I/O Sales Representative.

Orders for shipment must include the following:

- description of the equipment; see the latest Data I/O Price list or contact your sales representative for equipment and part numbers,

- purchase order number,

- desired method of shipment,

- · quantity of each item ordered,

- · shipping and billing address of firm, including zip code, and

- name of person ordering the equipment.

Table 1-1. Family and Pinout Codes

| Part        | Family     |          |          |           |          | Device          |                |         |          |           | _      |

|-------------|------------|----------|----------|-----------|----------|-----------------|----------------|---------|----------|-----------|--------|

|             | an         |          | Software | A         | Approval | Part            |                |         | Software | A dames - | Approv |

| Number      | Pinout     | Code     | Version  | Adapter   | Status   | Number          | Pinout         | Code    | Version  | Adapter   | Status |

| dvanced Mic | ro Devices | 3        |          |           |          | Advanced Mici   | ro Devices     | (Cont.) |          |           |        |

| 27LS18      | 16         | 02       | V01      | 351A-064  | S        | 27S49           | 16             | 67      | V01      | _         | s      |

| 27LS19      | 16         | 02       | V01      | 351A-064  | S        |                 |                |         |          |           | _      |

| 27508       | 15         | 02       | V01      | 351A-064  | 0        | 2708            | 21             | 27      | V01      | _         | Α      |

| 27509       | 15         | 02       | V01      | 351A-064  | ō        | AM9708          | 21             | 27      | V01      | _         | Â      |

| 27000       | .0         | O.L      | ***      | 3317-004  | · ·      | 2716            | 19             | 23      | V01      | =         | Â      |

| 27S18       | 16         | 02       | V01      | 351A-064  | Α        | AM9716          | 19             | 23      | V01      | -         | Â      |

|             | 16         | 02       |          |           | Â        | AIVISTIO        | 19             | 23      | VUI      | -         | Α.     |

| 27519       |            |          | V01      | 351A-064  |          | 0700            | 40             | 04      | 1 (04    |           |        |

| 29750A      | 16         | 02       | V01      | 351A-064  | A        | 2732            | 19             | 24      | V01      | -         | A      |

| 29751A      | 16         | 02       | V01      | 351A-064  | Α        | 2732A           | 27             | 24      | V01      | -         | A      |

|             |            |          |          |           | _        | AM9732          | 19             | 24      | V01      | -         | Α      |

| 27S10       | 15         | 01       | V01      | 351A-064  | 0        | 2764            | AF             | 33      | V01      | -         | Α      |

| 27511       | 15         | 01       | V01      | 351A-064  | 0        |                 |                |         |          |           |        |

| 27S20       | 16         | 01       | V01      | 351A-064  | Α        | AM9764          | AF             | 33      | V01      | -         | Α      |

| 27S21       | 16         | 01       | V01      | 351A-064  | Α        | 27128           | AF             | 51      | V01      | -         | Α      |

|             |            |          |          |           |          |                 |                |         |          |           |        |

| 29760A      | 16         | 01       | V01      | 351A-064  | Α        | Electronic Arra | avs            |         |          |           |        |

| 29761A      | 16         | 01       | V01      | 351A-064  | Â        |                 | · <del>-</del> |         |          |           |        |

| 27S12       | 16         | 03       | V01      | 351A-064  | Â        | 2708            | 21             | 27      | V01      | -         | 0      |

|             |            |          |          |           |          | 2716            | 19             | 23      | V01      | -         | 0      |

| 27S13       | 16         | 03       | V01      | 351A-064  | Α        |                 |                |         |          |           |        |

|             |            | _        |          |           | _        | Fairchild       |                |         |          |           |        |

| 29770       | 16         | 03       | V01      | 351A-064  | Α        |                 |                |         | 1.00     |           |        |

| 29771       | 16         | 03       | V01      | 351A-064  | Α        | 93417           | 01             | 01      | V01      | 351A-064  | Ą      |

| 27S24       | 16         | 65       | V01      | 351A-074  | S        | 93427           | 01             | 01      | V01      | 351A-064  | Α      |

| 27S25       | 16         | 65       | V01      | 351A-074  | S        | 93436           | 01             | 03      | V01      | 351A-064  | Α      |

|             |            |          |          |           | •        | 93446           | 01             | 03      | V01      | 351A-064  | Α      |

| 27S28       | 16         | 09       | V01      | 351A-064  | Α        | I               |                |         |          |           |        |

| 27S29       | 16         | 09       | V01      | 351A-064  | Â        | 93438           | 01             | 15      | V01      | _         | Α      |

|             |            |          |          | 331A-004  |          | 93448           | 01             | 15      | V01      | _         | A      |

| 27S30       | 16         | 36       | V01      | •         | A        | 93452           | 01             | 05      | V01      | 351A-064  | Â      |

| 27531       | 16         | 36       | V01      | •         | Α        | 93453           |                |         |          |           |        |

|             |            |          |          |           |          | 93453           | 01             | 05      | V01      | 351A-064  | Α      |

| 27S32       | 16         | 38       | V01      | 351A-064  | Α        | 1               |                |         |          |           | _      |

| 27533       | 16         | 38       | V01      | 351A-064  | Α        | 93450           | 01             | 16      | V01      | =         | Α      |

| 27PS181     | 16         | 37       | V01      | -         | S        | 93451           | 01             | 16      | V01      | -         | Α      |

| 27PS281     | 16         | 37       | V01      | 351A-074  | S        | 93460           | 01             | 16      | V01      | -         | S      |

|             |            | •        |          |           |          | 93461           | 01             | 16      | V01      | -         | S      |

| 27S180      | 16         | 37       | V01      | _         | Α        | 1               |                |         |          |           |        |

| 275181      | 16         | 37       | V01      |           | Â        | 93L450          | 01             | 16      | V01      | _         | S      |

|             | 16         |          |          | 251 4 074 | ŝ        | 93L451          | 01             | 16      | V01      | _         | Š      |

| 275280      |            | 37       | V01      | 351A-074  |          | 93514           | 01             | 06      | V01      | 351A-064  | Š      |

| 27S281      | 16         | 37       | V01      | 351A-074  | S        | 93515           | 01             | 06      | V01      |           | S      |

|             |            |          |          |           |          | 33515           | O1             | 00      | VOI      | 351A-064  | 3      |

| 27S35       | 16         | 66       | V01      | 351A-074  | S        | 20542           |                |         |          |           | _      |

| 27S37       | 16         | 66       | V01      | 351A-074  | S        | 93510           | 01             | 21      | V01      | -         | Α      |

| 27LS185     | 16         | 06       | V01      | 351A-064  | S        | 93511           | 01             | 21      | V01      | -         | Α      |

| 27PS184     | 16         | 06       | V01      | 351A-064  | S        | 1               |                |         |          |           |        |

| 27.0.0.     |            | -        |          | 00111001  | •        | 2708            | 21             | 27      | V01      | -         | S      |

| 27PS185     | 16         | 06       | V01      | 351A-064  | s        | I               | _              | _       | -        |           |        |

|             | 16         |          |          |           | Ā        | E               |                |         |          |           |        |

| 27S184      |            | 06<br>06 | V01      | 351A-064  |          | Fujitsu         | ~~             |         |          |           |        |

| 27S185      | 16         | 06       | V01      | 351A-064  | A        | 27C32A          | 27             | 24      | V01      | -         | S      |

| 27PS191     | 16         | 68       | V01      | -         | S        | 27C64           | 45             | 33      | V01      | -         | S      |

|             |            |          |          |           |          | 7051            | 78             | 02      | V01      | 351A-064  | S      |

| 27PS291     | 16         | 68       | V01      | 351A-074  | S        | 7056            | 78             | 02      | V01      | 351A-064  | S      |

| 27\$190     | 16         | 68       | V01      | -         | Α        |                 |                |         | = -      |           | _      |

| 275191      | 16         | 68       | V01      | -         | Α        | 7111            | 68             | 02      | V01      | 351A-064  | s      |

| 275290      | 16         | 68       | V01      | 351A-074  | S        | 7112            | 68             | 02      | V01      | 351A-064  | S      |

| 0_00        | . •        | •        |          | 33171 077 | •        | 7052            | 78             | 01      |          |           |        |

| 27S291      | 16         | 68       | V01      | 351A-074  | s        |                 |                |         | V01      | 351A-064  | S      |

|             |            |          |          |           | S        | 7057            | 78             | 01      | V01      | 351A-064  | S      |

| 27545       | 16         | 77       | V01      | 351A-074  |          |                 |                |         |          |           |        |

| 27547       | 16         | 77       | V01      | 351A-074  | S        | 7113            | 68             | 01      | V01      | 351A-064  | S      |

| 27PS41      | 16         | 53       | V01      | 351A-064  | S        | 7114            | 68             | 01      | V01      | 351A-064  | S      |

|             |            |          |          |           |          | 7117            | 68             | 08      | V01      | 351A-064  | S      |

| 27S40       | 16         | 53       | V01      | 351A-064  | Α        | 7118            | 68             | 08      | V01      | 351A-064  | š      |

| 27S41       | 16         | 53       | V01      | 351A-064  | A        | 1               |                |         |          | 20        | J      |

| 27PS43      | 16         | 63       | V01      | -         | Ä        | 7119            | 68             | 14      | V01      |           |        |

| 27543       | 16         | 63       | V01      | _         | Â        | 7120            | 68             | 14      |          | -         | S      |

| 2,0-10      | ,,,        | w        | ¥01      | •         | ^        |                 |                |         | V01      | 0044 004  | · S    |

| 270640      | 10         | ~~       | 1/01     |           |          | 7053            | 78             | 03      | V01      | 351A-064  | S      |

| 27PS49      | 16         | 67       | V01      | -         | s        | 7058            | 78             | 03      | V01      | 351A-064  | S      |

|             |            |          |          |           |          |                 |                |         |          |           |        |

|             |            |          |          |           |          |                 |                |         |          |           |        |

Table 1-1. Family and Pinout Codes (Continued)

| Device          | Fan         | ilv      |             |          |            | Device          | Far                  | nily     |             |           |          |

|-----------------|-------------|----------|-------------|----------|------------|-----------------|----------------------|----------|-------------|-----------|----------|

| Part            | an          |          | Software    |          | Approval   | Part            |                      | nd       | Software    |           | Approvai |

| Number          | Pinout Code |          | Version     | Adapter  | Status     | Number          |                      | Code     | Version     | Adapter   | Status   |

|                 |             |          |             |          |            |                 |                      |          |             |           |          |

| Fujitsu (Cont.) |             |          |             |          |            | Harris Semico   | nductor (C           | cont.)   |             |           |          |

| 7115            | 68          | 03       | V01         | 351A-064 | S          | 7681RP          | 05                   | 16       | V01         | -         | Α        |

| 7116            | 68          | 03       | V01         | 351A-064 | S          | 7684            | 05                   | 06       | V01         | 351A-064  | Α        |

| 7123            | 68          | 09       | V01         | 351A-064 | S          | 7684P           | 05                   | 06       | V01         | 351A-064  | Α        |

| 7124            | 68          | 09       | V01         | 351A-064 | S          | 7685            | 05                   | 06       | V01         | 351A-064  | Α        |

| 7405            | 60          | 45       | 104         |          | •          |                 | 05                   | ~        |             |           |          |

| 7125<br>7126    | 68<br>68    | 15<br>15 | V01<br>V01  | •        | s<br>s     | 7685P<br>7616   | 05<br>05             | 06<br>42 | V01<br>V01  | 351A-064  | A        |

|                 | 78          | 05       | V01         | 351A-064 |            |                 | 05                   |          |             | -         |          |

| 7054            |             | 05       |             |          | s          | 76160           |                      | 21       | V01         | •         | A        |

| 7059            | 78          | US       | V01         | 351A-064 | S          | 76161           | 05                   | 21       | V01         | -         | A        |

| 7121            | 68          | 05       | V01         | 351A-064 | s          | 76165           | 05                   | 53       | V01         | 351A-064  | Α        |

| 7122            | 68          | 05       | V01         | 351A-064 | S          | 76320           | 05                   | 63       | V01         | -         | Α        |

| 7055            | 78          | 69       | V01         | -        | S          | 76321           | 05                   | 63       | V01         | -         | Α        |

| 7060            | 78          | 69       | V01         | -        | S          | 76641           | 05                   | 67       | V01         | -         | A        |

|                 |             |          |             |          |            |                 |                      |          |             |           |          |

| 7131            | 68<br>69    | 16       | V01         | -        | s          | Hitachi         |                      |          |             |           |          |

| 7132            | 68          | 16       | V01         |          | S          | 25044           | 74                   | 05       | V01         | 351A-064  | S        |

| 7127            | 68          | 06       | V01         | 351A-064 | S          | 25045           | 74                   | 05       | V01         | 351A-064  | Š        |

| 7128            | 68          | 06       | V01         | 351A-064 | S          | 25088           | 74                   | 16       | V01         | •         | Š        |

|                 |             | _        |             |          |            | 25088S          | 66                   | 16       | V01         | -         | Š        |

| 7137            | 68          | 21       | V01         | -        | S          | 1 230003        | 30                   | 10       | ***         | -         | 9        |

| 7138            | 68          | 21       | V01         | -        | S          | 25089           | 74                   | 16       | V01         | _         | s        |

| 7151            | 68          | 53       | V01         | 351A-064 | S          | 25089<br>25089S | 66                   | 16       | V01         | -         | S        |

| 7152            | 68          | 53       | V01         | 351A-064 | S          | 250895          | 74                   | 06       | V01<br>V01  | 351A-064  | S        |

|                 |             |          |             |          |            | 25084S          | 66                   | 06       | V01         | 351A-064  | S        |

| 7141            | 68          | 63       | V01         | -        | S          | 250845          | 00                   | 00       | <b>V</b> U1 | 351A-004  | 3        |

| 7142            | 68          | 63       | V01         | +        | S          | 05005           | 74                   | 00       | 1/01        | 251 A 064 | s        |

| 7143            | 68          | 67       | V01         | -        | s          | 25085           | 74                   | 06       | V01         | 351A-064  |          |

| 7144            | 68          | 67       | V01         | -        | S          | 25085S          | 66                   | 06       | V01         | 351A-064  | S        |

|                 |             |          |             |          |            | 25168           | 74                   | 21       | V01         | -         | s        |

| 8518            | 21          | 27       | V01         | -        | S          | 25168S          | 66                   | 21       | V01         | -         | s        |

| 8516            | 19          | 23       | V01         | -        | Š          |                 |                      |          |             |           | _        |

| 8742            | 50          | 57       | V01         | 351A-075 | S<br>S     | 25169           | 74                   | 21       | V01         | -         | s        |

| 8749H           | 50          | 57       | V01         | 351A-075 | Š          | 25169S          | 66                   | 21       | V01         | -         | S        |

| 07-1011         | ••          | 0.       | 70.         | 301A-0/3 | •          | 27C32           | 19                   | 24       | V01         | -         | S        |

| 2732A           | 27          | 24       | V01         | _        | s          | 27C32A          | 27                   | 24       | V01         | -         | S        |

| 2732A-35        | 27          | 24       | V01         |          | š          |                 |                      |          |             |           |          |

| 8532            | 19          | 24       | V01         | -        | Š          | 462716          | 19                   | 23       | V01         | -         | S        |

| 2764            | 45          | 33       | V01         | -        | s          | 48016           | 33                   | 23       | V01         | -         | S        |

| 2/04            |             | 33       | <b>V</b> 01 | •        | 3          | 462532          | 19                   | 25       | V01         | -         | S        |

| 27128           | 45          | 51       | V01         | _        | s          | 462732          | 19                   | 24       | V01         | -         | s        |

| <u> </u>        |             |          |             |          | _          | 462732P         | 19                   | 24       | V01         |           | s        |

| General Instru  | ments       |          |             |          |            | 482732A         | 27                   | 24       | V01         | -         | Š        |

| 5716            | 83          | 23       | V01         | _        | s          | 482764          | 79                   | 33       | V01         |           | Š        |

| 5816            | 37          | 23       | V01         |          | š          | 4827128         | 7 <del>9</del><br>79 | 51       | V01         | -         | S        |

| 33.0            | •           |          |             |          | _          | TOZ/120         | ,,                   | ٠.       | •••         |           | J        |

| Harris Semicor  |             |          |             |          |            | Hughes          |                      |          |             |           |          |

| 6641            | 40          | 47       | V01         | -        | S          | 3004-1          | 58                   | 62       | V01         | _         | s        |

| 7602            | 05          | 02       | V01         | 351A-064 | Α          | 3004-2          | 58                   | 61       | V01<br>V01  | -         | S        |

| 7603            | 05          | 02       | V01         | 351A-064 | Α          | 3704-1          | 58                   | 62       | V01         | •         | s        |

| 7610            | 05          | 01       | V01         | 351A-064 | Α          | 3704-2          | 58                   | 61       | V01         | -         | S        |

| 7614            | 0E          | 01       | 1/01        | 351A-064 |            |                 |                      | •        |             |           |          |

| 7611<br>7620    | 05<br>05    | 01<br>43 | V01         | 301A-U04 | A          | 3008            | 58                   | 60       | V01         | -         | s        |

| 7629            | 05<br>05    | 43       | V01         | 0544.004 | Ą          | 3708            | 58                   | 60       | V01         | -         | S        |

| 7620            | 05<br>05    | 03       | V01         | 351A-064 | Ą          | 1               |                      |          |             |           |          |

| 7621            | 05          | 03       | V01         | 351A-064 | A          | Intel           |                      |          |             |           |          |

| 7640            | 05          | 15       | V01         |          | · <b>A</b> | 2704            | 21                   | 26       | V01         | -         | 0        |

| 7641            | 05          | 15       | V01         | =        | Â          | 8704            | 21                   | 26       | V01         | -         | ō        |

| 7648            | 05          | 09       | V01<br>V01  | 351A-064 | â          | 2708            | 21                   | 27       | V01         | -         | ŏ        |

| 7649            | 05          | 09       | V01         | 351A-064 | Â          | 2758            | 19                   | 22       | V01         | -         | ŏ        |

| , , , ,         |             | •••      | •••         |          |            | =:              |                      |          |             |           |          |

| 7642            | 05          | 05       | V01         | 351A-064 | Α          | 8708            | 21                   | 27       | V01         | -         | 0        |

| 7642P           | 05          | 38       | V01         | 351A-064 | A          | 8741            | 56                   | 59       | V01         | 351A-075  | S        |

| 7643            | 05          | 05       | V01         | 351A-064 | A          | 8741A           | 56                   | 59       | V01         | 351A-075  | S        |

| 7643P           | 05          | 38       | V01         | 351A-064 | Ä          | 8748            | 52                   | 56       | V01         | 351A-075  | A        |

|                 |             |          |             |          | _          |                 |                      |          |             | 0011      |          |

| 7608            | 05          | 16       | V01         | -        | Ą          | 8748H           | 50                   | 56       | V01         | 351A-075  | Ą        |

| 7680            | 05          | 16       | V01         | -        | A          | 2716            | 19                   | 23       | V01         | -         | A        |

| <b>7680</b> RP  | 05          | 16       | V01         | -        | A          | 2815            | 85                   | 23       | V01         | •         | A        |

| 3004            | 05          | 16       | V01         | -        | Α          | 1               |                      |          |             |           |          |

| <b>768</b> 1    |             |          |             |          |            | 1               |                      |          |             |           |          |

Table 1-1. Family and Pinout Codes (Continued)

|                |            |            |            | 510 1 1. 1 4         | Thiny arta i | inout Codes (     | Contint    | ieu,       |            |                      |          |

|----------------|------------|------------|------------|----------------------|--------------|-------------------|------------|------------|------------|----------------------|----------|

| Device<br>Part | ar         | nily<br>nd | Software   |                      | Approval     | Device<br>Part    | Fan<br>ar  | nd         | Software   |                      | Approval |

| Number         | Pinou      | t Code     | Version    | Adapter              | Status       | Number            | Pinout     | Code       | Version    | Adapter              | Status   |

| Intel (Cont.)  |            |            |            |                      |              | Monolithic Me     | mories, In | c. (Cont.  | )          |                      |          |

| 2816           | 37         | 23         | V01        | •                    | A            | 6306              | 11         | 03         | V01        | 351A-064             | S        |

| 8742           | 50         | 57         | V01        | 351A-075             | s            | 63LS240           | 18         | 03         | V01        | 351A-064             | S        |

| 8749H          | 50         | 57         | V01        | 351A-075             | Α            | 63LS241           | 18         | 03         | V01        | 351A-064             | S        |

| 8755A          | 47         | 55         | V01        | 351A-075             | S            | 63S240            | 18         | 03         | V01        | 351A-064             | S        |

| 0700           | 40         | 04         | 1/04       |                      |              |                   |            |            |            |                      |          |

| 2732<br>2732A  | 19<br>27   | 24<br>24   | V01<br>V01 | -                    | A            | 63S241            | 18         | 03         | V01        | 351A-064             | S        |

|                |            |            |            | -                    | A            | 5340              | 11         | 15         | V01        |                      | S        |

| 8751<br>2764   | 53<br>79   | 58<br>33   | V01<br>V01 | 351A-076             | A            | 5340JS            | 11         | 15         | V01        | 351A-074             | S        |

| 2704           | 75         | 33         | VUI        | -                    | Α            | 5341              | 11         | 15         | V01        | -                    | s        |

| 27128          | 79         | 51         | V01        | _                    | Α            | 5341JS            | 11         | 15         | V01        | 351A-074             | S        |

| 27256          | 93         | 32         | V01        | -                    | Α            | 5348              | 11         | 09         | V01        | 351A-056             | š        |

|                |            |            |            |                      |              | 5349              | 11         | 09         | V01        | 351A-064             | Š        |

| Intersil       |            |            |            |                      |              | 6340              | 11         | 15         | V01        | -                    | Š        |

| 5600           | 70         | 02         | V01        | 351A-064             | 0            |                   |            |            |            |                      |          |

| 5610           | 70         | 02         | V01        | 351A-064             | ŏ            | 6340JS            | 11         | 15         | V01        | 351A-074             | S        |

| 5603A          | 70         | 01         | V01        | 351A-064             | ŏ            | 6341              | 11         | 15         | V01        | -                    | S        |

| 5623           | 70         | 01         | V01        | 351A-064             | ŏ            | 6341JS            | 11         | 15         | V01        | 351A-074             | S        |

|                |            | •          |            |                      | •            | 6348              | 11         | 09         | V01        | 351A-064             | s        |

| 5604           | 70         | 03         | V01        | 351A-064             | 0            |                   |            |            |            |                      |          |

| 5624           | 70         | 03         | V01        | 351A-064             | ŏ            | 6349              | 11         | 09         | V01        | 351A-064             | s        |

| 6716           | 59         | 64         | V01        | -                    | Ā            | 63S480            | 18         | 09         | V01        | 351A-064             | 0        |

|                |            |            |            |                      |              | 63S481            | 18         | 09         | V01        | 351A-064             | 0        |

| Mitsubishi     |            |            |            |                      |              | 5352              | 11         | 05         | V01        | 351A-064             | S        |

| 2708           | 21         | 27         | V01        | _                    | s            |                   |            |            |            |                      |          |

| 8748           | 52         | 56         | V01        | 351A-075             | Š            | 5353              | 11         | 05         | V01        | 351A-064             | S        |

| 2716           | 19         | 23         | V01        | -                    | Š            | 6352              | 11         | 05         | V01        | 351A-064             | S        |

| 2732           | 19         | 24         | V01        | -                    | Š            | 6353              | 11         | 05<br>05   | V01        | 351A-064             | S        |

|                |            |            |            |                      | _            | 63LS441           | 18         | 05         | V01        | 351A-064             | 0        |

| 2732A          | 27         | 24         | V01        | -                    | S            | 63RA441           | 18         | 07         | V01        | 351A-064             |          |

| 2764           | 79         | 33         | V01        | -                    | S            | 63RD441           | 18         | 07<br>07   | V01        | 351A-064             | S<br>S   |

| 27128          | 79         | 51         | V01        |                      | S            | 63RS441           | 18         | 07         | V01        | 351A-064             | Ö        |

|                |            |            |            |                      |              | 635440            | 18         | 05         | V01        | 351A-064             | s        |

| Monolithic Mer | mories, li | nc.        |            |                      |              | 635441            | 18         | 05         | V01        | 351A-064             | S        |

| 5330           | 29         | 02         | V01        | 351A-064             | A            | ~~~               | .0         | •          | ***        | 0017 007             | J        |

| 5331           | 29         | 02         | V01        | 351A-064             | Â            | 5380              | 11         | 16         | V01        | _                    | s        |

| 53LS080        | 18         | 02         | V01        | 351A-064             | Ö            | 5380JS            | 11         | 16         | V01        | 351A-074             | Š        |

|                |            |            |            | 00.71001             | •            | 5381              | 11         | 16         | V01        | -                    | Š        |

| 53LS081        | 18         | 02         | V01        | 351A-064             | 0            | 5381JS            | 11         | 16         | V01        | 351A-074             | Š        |

| 538080         | 18         | 02         | V01        | 351A-064             | Α            |                   |            |            |            |                      |          |

| 53S081         | 18         | 02         | V01        | 351A-064             | Α            | 6380              | 11         | 16         | V01        | -                    | S        |

| 6330           | 29         | 02         | V01        | 351A-064             | A            | 6380JS            | 11         | 16         | V01        | 351A-074             | S        |

|                |            |            |            |                      |              | 6381              | 11         | 16         | V01        | -                    | S        |

| 6331           | 29         | 02         | V01        | 351A-064             | Α            | 6381JS            | 11         | 16         | V01        | 351A-074             | S        |

| 63LS080        | 18         | 02         | V01        | 351A-064             | 0            |                   |            |            |            |                      |          |

| 63LS081        | 18         | 02         | V01        | 351A-064             | 0            | 5388              | 11         | 06         | V01        | 351A-064             | S        |

| 63S080         | 18         | 02         | V01        | 351A-064             | Α            | 5389              | 11         | 06         | V01        | 351A-064             | S        |

| 200.004        | 40         |            |            |                      | _            | 6388              | 11         | 06         | V01        | 351A-064             | S        |

| 63S081         | 18         | 02         | V01        | 351A-064             | A            | 6389              | 11         | 06         | V01        | 351A-064             | s        |

| 5300<br>5301   | 11         | 01<br>01   | V01        | 351A-064             | A            | 63D A 044         | 10         | 14         | 1404       | 2014-004             | ^        |

| 6300           | 11<br>11   | 01<br>01   | V01<br>V01 | 351A-064<br>351A-064 | A<br>A       | 63RA841<br>63S840 | 18<br>18   | 11<br>06   | V01<br>V01 | 351A-064             | 0        |

| <b></b>        | " "        | 01         | ¥U1        | 301A-004             | Α            | 63S841            | 18         | υσ<br>06 ⋅ |            | 351A-064<br>351A-064 | 0<br>\$  |

| 6301           | 11         | 01         | V01        | 351A-064             | Α            | 63S1681JS         | 18         | 21         | V01        | 351A-004<br>351A-074 | S        |

| 63LS140        | 18         | 01         | V01        | 351A-064             | Â            |                   | 70         | ۲,         | 401        | W1A-0/4              | 3        |

| 63LS141        | 18         | 01         | V01        | 351A-064             | Â            | 63PL1681          | 18         | 21         | V01        | _                    | s        |

| 63S140         | 18         | 01         | V01        | 351A-064             | Â            | 63PS1681          | 18         | 21         | V01        | -                    | S        |

|                |            |            |            |                      | • •          | 63S1680           | 18         | 21         | V01        | -                    | ŏ        |

| 63S141         | 18         | 01         | V01        | 351A-064             | Α            | 63\$1681          | 18         | 21         | V01        | -                    | š        |

| 5308           | 11         | 08         | V01        | 351A-064             | s            | 1                 |            |            |            |                      | -        |

| 5309           | 11         | 08         | V01        | 351A-064             | s            | 63S1640           | 18         | 53         | V01        | 351A-064             | 0        |

| 5335           | 11         | 14         | V01        | -                    | 0            | 63S1641           | 18         | 53         | V01        | 351A-064             | s        |

|                |            |            |            |                      |              | 6353281           | 18         | 63         | V01        | -                    | s        |

| 5336           | 11         | 14         | V01        |                      | S            | l                 |            |            |            |                      |          |

| 6308           | 11         | 08         | V01        | 351A-064             | S            | Mostek            |            |            |            |                      |          |

| 6309           | 11         | 08         | V01        | 351A-064             | S            | 2716              | 19         | 23         | V01        | -                    | 0        |

| 6335           | 11         | 14         | V01        | -                    | S            |                   |            |            |            |                      |          |

| 6336           | 11         | 14         | V01        |                      | s            |                   |            |            |            |                      |          |

| 5305           | 11         | 03         | V01<br>V01 | 351A-064             | S            |                   |            |            |            |                      |          |

| 5306           | 11         | 03         | V01        | 351A-064<br>351A-064 | S            |                   |            |            |            |                      |          |

| 6305           | 11         | 03         | V01        | 351A-064<br>351A-064 | S            | ]                 |            |            |            |                      |          |

| ~~~            | 11         | w          | VOI        | 301A-004             | 3            | <u> </u>          |            |            |            |                      |          |

Table 1-1. Family and Pinout Codes (Continued)

| Device          | Farr        | nilv     |            | _                    |          | Device           | Fai               | mily     |            |                     |          |

|-----------------|-------------|----------|------------|----------------------|----------|------------------|-------------------|----------|------------|---------------------|----------|

| Part            | an          | ď        | Software   |                      | Approval | Part             | а                 | nd       | Software   |                     | Approval |

| Number          | Pinout Code |          | Version    | Adapter              | Status   | Number           | Pinou             | t Code   | Version    | Adapter             | Status   |

| Motorola        |             |          |            |                      |          | National Semi    | conductor (Cont.) |          |            |                     |          |

| 7620            | 05          | 03       | V01        | 351A-064             | 0        | 74S573           | 08                | 05       | V01        | 351A-064            | Α        |

| 7621            | 05          | 03       | V01        | 351A-064             | Ă        | 77LS181          | 08                | 16       | V01        | -                   | Α        |

| 7640            | 05          | 15       | V01        | 301A 004             | ô        | 77S180           | 08                | 16       | V01        | _                   | A        |

| 7641            | 05          | 15       | V01        | -                    | Ā        | 87LS181          | 08                | 16       | V01        | -                   | Ä        |

|                 |             |          |            |                      |          | 970190           | 00                | 16       | 1/01       |                     |          |

| 7649<br>7642    | 05<br>05    | 09<br>05 | V01<br>V01 | 351A-064<br>351A-064 | A<br>0   | 87S180<br>87S181 | 08<br>08          | 16<br>16 | V01<br>V01 | -                   | A<br>A   |

|                 |             |          |            |                      |          | 87S280           | 08                | 16       | V01        | 351A-074            | ŝ        |

| 7643<br>7680    | 05<br>05    | 05<br>16 | V01<br>V01 | 351A-064             | A<br>0   | 87S281           | 08                | 16       | V01        | 351A-074            | S        |