#### NOTE

This manual documents the Model 9000A-8088 and its assemblies at the revision levels identified in Section 7. If your instrument contains assemblies with different revision letters, it will be necessary for you to either update or backdate this manual. Refer to the supplemental change/errata sheet for newer assemblies, or to the backdating information in Section 7 for older assemblies.

# 9000A-8088 Interface Pod

Instruction Manual

## **Table of Contents**

| SECTION | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PAGE                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1                                                                   |

|         | 1-1. PURPOSE OF INTERFACE POD  1-2. DESCRIPTION OF POD  1-3. SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                   |

| 2       | INSTALLATION AND SELF TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1                                                                   |

|         | 2-1. INTRODUCTION 2-2. PERFORMING THE POD SELF TEST 2-3. CONNECTING THE POD TO THE UUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1                                                                   |

| 3       | MICROPROCESSOR DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1                                                                   |

|         | 3-1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

| 4       | OPERATING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1                                                                   |

|         | 4-1. INTRODUCTION 4-2. GETTING STARTED 4-3. ADDRESS SPACE ASSIGNMENT 4-4. Introduction 4-5. Special Address 4-6. Role of 8088 Segment Registers in Memory Addressing 4-7. Demultiplexing Memory Addresses with the A16/S3 and A17/S4 Lin 4-8. STATUS/CONTROL LINES 4-9. Introduction 4-10. Status Line Bit Assignments 4-11. User-Enableable Lines 4-12. Status Lines Unique to the Pod 4-17. Forcing Lines 4-18. Interrupt Lines 4-19. User-Writeable Control Lines 4-19. User-Writeable Control Lines 4-22. Control Line Bit Assignments 4-23. SPECIAL FUNCTIONS UNIQUE TO THE 8088 POD 4-24. Introduction 4-25. Quick Looping Read or Write 4-26. Quick RAM Test 4-27. Quick ROM Test | 4-1 4-2 4-2 4-2 nes 4-3 4-4 4-4 4-5 4-6 4-6 4-7 4-8 4-9 4-9 4-12 4-13 |

|         | 4-28. RUN UUT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |

#### **TABLE OF CONTENTS,** continued

| SECTION |                | TITLE                                                              | PAGE |

|---------|----------------|--------------------------------------------------------------------|------|

|         | 4-30.          | Specifying Execution Address                                       | 4-14 |

|         | 4-31.          | Specifying Segment Register Contents Before Execution              |      |

|         | 4-32.          | DEFAULT ADDRESSES FOR LEARN AND BUS TEST                           | 4-15 |

|         | 4-33.          | Learn Operation Default Address                                    | 4-15 |

|         | 4-34.          | Default Address for Data Line Testing for Bus Test                 |      |

|         | 4-35.          | INTERRUPT HANDLING                                                 |      |

|         | 4-36.          | Introduction                                                       |      |

|         | 4-37.          | Using Special Addresses to Read Interrupt Type and Cascade Address |      |

|         | 4-38.          | Forcing the Execution of the Interrupt Acknowledge Routine         |      |

|         | 4-39.          | PROBE AND SCOPE SYNCHRONIZATION MODES                              |      |

|         | 4-40.          | PROBLEMS DUE TO A MARGINAL UUT                                     |      |

|         | 4-41.          | Introduction                                                       |      |

|         | 4-42.          | UUT Operating Speed and Memory Access                              |      |

|         | 4-43.          | UUT Noise Levels                                                   |      |

|         | 4-44.          | Bus Loading                                                        |      |

|         | 4-45.<br>4-46. | Clock Loading                                                      |      |

|         | 4-40.<br>4-47. | POD DRIVE CAPABILITYLOW UUT POWER DETECTION                        |      |

|         | 4-4/.          | LOW UUT POWER DETECTION                                            | 4-19 |

| 5       | THEO           | PRY OF OPERATION                                                   |      |

|         | 5-1.           | INTRODUCTION                                                       |      |

|         | 5-2.           | GENERAL POD OPERATION                                              |      |

|         | 5-3.           | Processor Section                                                  |      |

|         | 5-4.           | Timing and Control Section                                         |      |

|         | 5-5.           | Interface Section                                                  |      |

|         | 5-6.           | DETAILED BLOCK DIAGRAM DESCRIPTION                                 |      |

|         | 5-7.           | Detailed Description of Processor Section                          |      |

|         | 5-8.           | Detailed Description of Timing and Control Section                 |      |

|         | 5-9.           | Interface Section                                                  | 5-11 |

| 6       | TROU           | IBLESHOOTING                                                       | 6-1  |

|         | 6-1.           | INTRODUCTION                                                       | 6-1  |

|         | 6-2.           | DETERMINING WHETHER THE POD IS DEFECTIVE OR                        |      |

|         |                | INOPERATIVE                                                        | 6-2  |

|         | 6-3.           | TROUBLESHOOTING A DEFECTIVE POD                                    |      |

|         | 6-4.           | Preparation for Troubleshooting a Defective Pod                    |      |

|         | 6-5.           | Recreating the Enhanced Self Test Routines                         |      |

|         | <b>6-6</b> .   | Recreating the Standard Self Test Routines                         |      |

|         | 6-7.           | TROUBLESHOOTING AN INOPERATIVE POD                                 |      |

|         | 6-8.           | Introduction                                                       |      |

|         | 6-9.           | Procedure for Troubleshooting an Inoperative Pod                   |      |

|         | 6-10.          | EXTENDED TROUBLESHOOTING PROCEDURES                                |      |

|         | 6-11.          | Partially Checked Circuits                                         |      |

|         | 6-12.          | Timing and Noise Problems                                          |      |

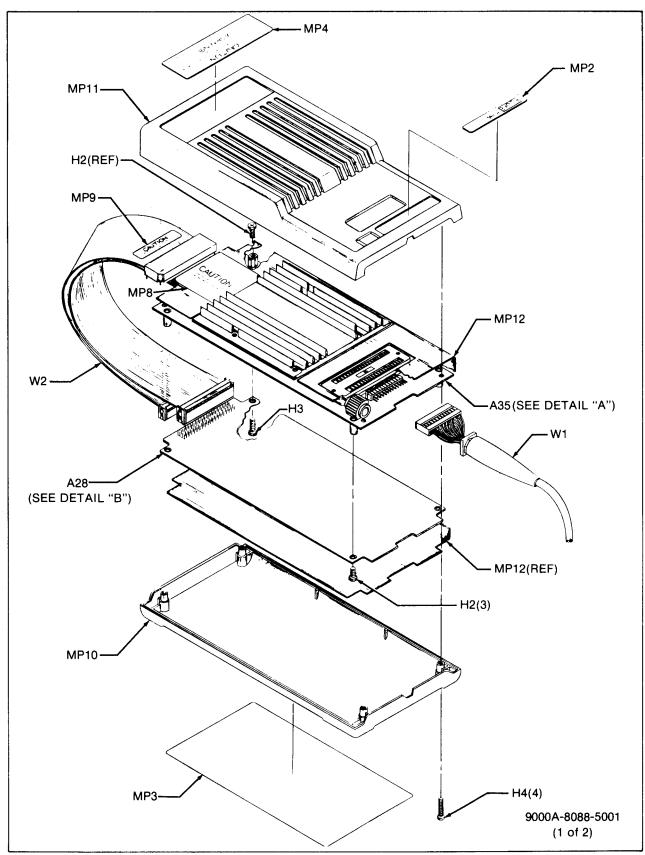

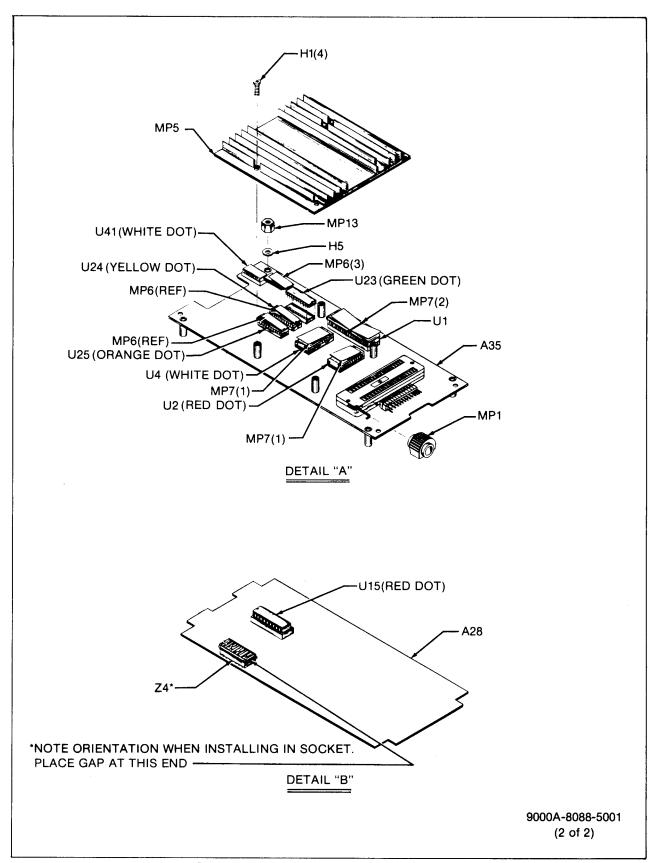

|         | 6-13.          | DISASSEMBLY                                                        | 6-12 |

| 7       | LIST           | OF REPLACEABLE PARTS                                               | 7-1  |

|         | 7-1.           | INTRODUCTION                                                       |      |

|         | 7-2.           | HOW TO OBTAIN PARTS                                                |      |

|         | 7-3.           | MANUAL CHANGE AND BACKDATING INFORMATION                           | 7-2  |

#### **TABLE OF CONTENTS**, continued

| SECTION | TITLE                  | AGE  |

|---------|------------------------|------|

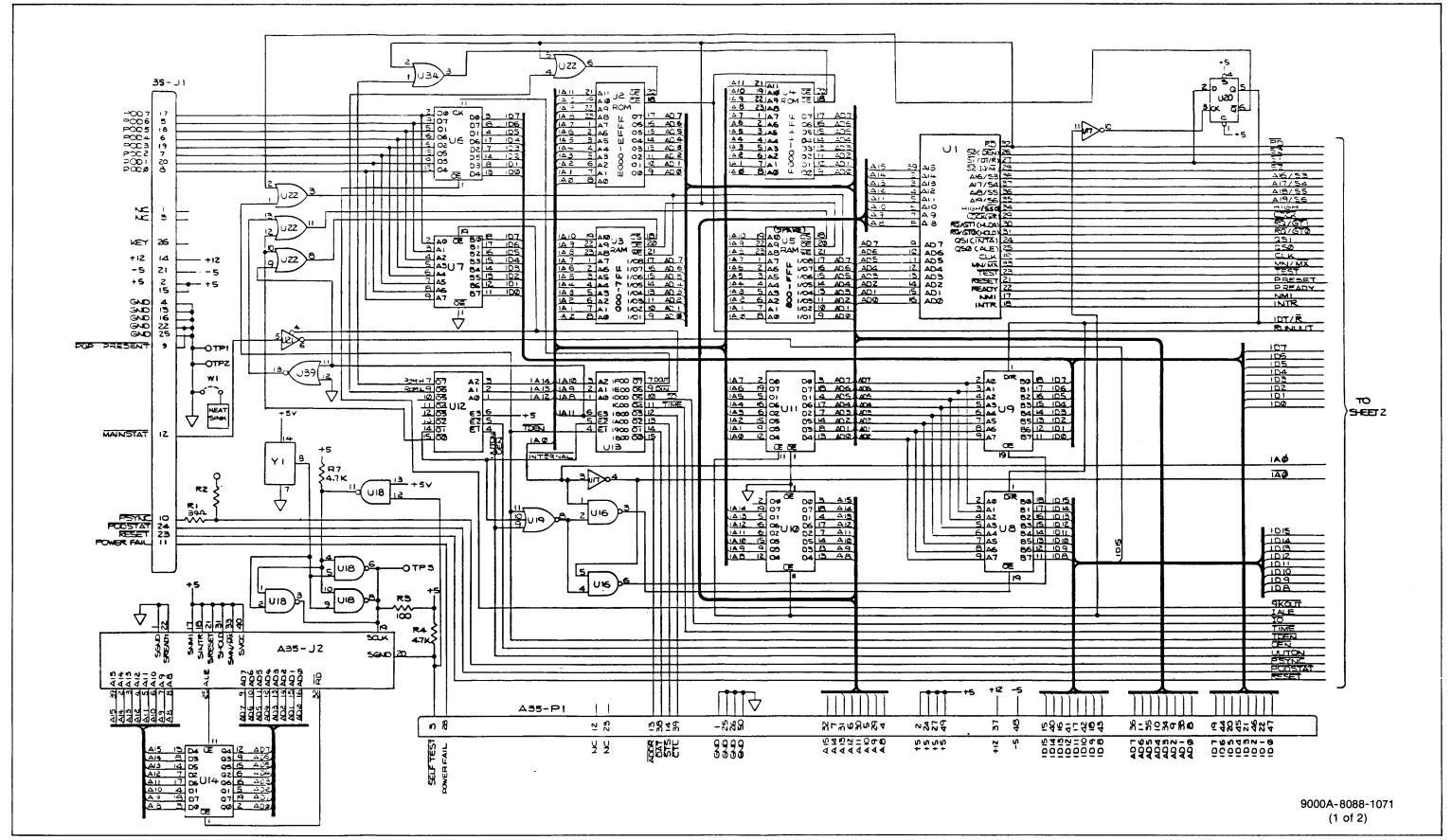

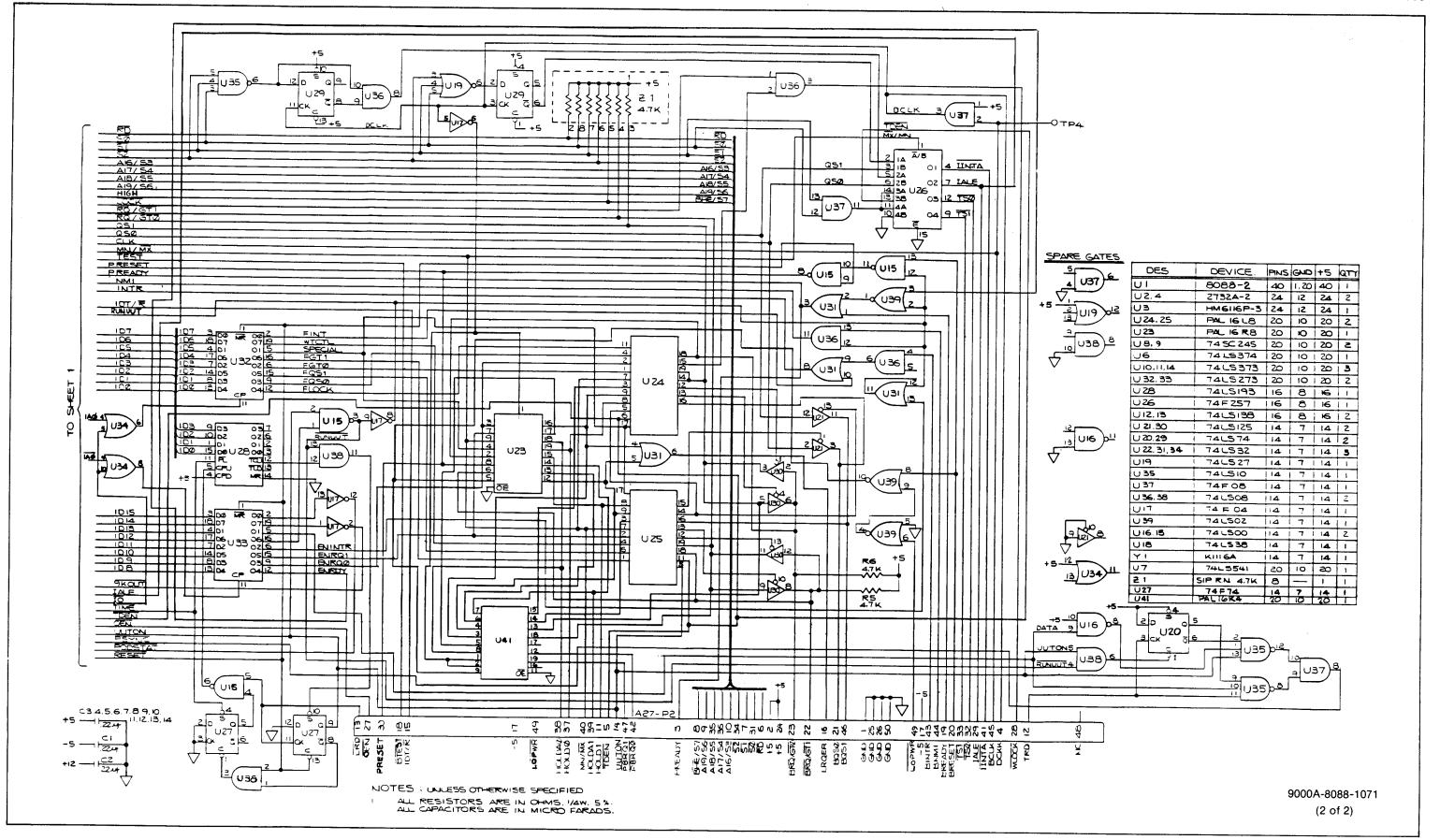

| 8       | SCHEMATIC DIAGRAMS     | B-1  |

|         | 8-1. TABLE OF CONTENTS | 8-1  |

|         | INDEX {                | 8-12 |

### **List of Tables**

| TABLE | TITLE                                                     | PAGE |

|-------|-----------------------------------------------------------|------|

| 1-1.  | 8088 Pod Specifications                                   | 1-4  |

| 3-1.  | Microprocessor Signals                                    | 3-1  |

| 4-1.  | Address Space Assignment                                  | 4-3  |

| 4-2.  | Status and Control Line Bit Assignments                   | 4-5  |

| 4-3.  | Special Functions Unique to the 8088 Pod                  | 4-10 |

| 4-4.  | Special Addresses for Run UUT Mode                        | 4-14 |

| 4-5.  | Special Addresses for Interrupt Handling                  | 4-17 |

| 6-1.  | Required Test Equipment for Pod Troubleshooting           | 6-2  |

| 6-2.  | Standard Self Test Failure Codes                          | 6-3  |

| 6-3.  | Enhanced Self Test Failure Codes                          | 6-6  |

| 6-4.  | Pod Device Addresses                                      | 6-9  |

| 6-5.  | Bit Definitions for Selected Pod Addresses                | 6-10 |

| 6-6   | Pod Ribbon Cable Lines Partially Checked in Pod Self Test | 6-11 |

## **List of Illustrations**

| FIGURE | TITLE                                                          | PAGE |

|--------|----------------------------------------------------------------|------|

| 1-1.   | Communication Between the Troubleshooter, the Pod, and the UUT | 1-3  |

| 1-2.   | External Features of the 8088 Interface Pod                    |      |

| 2-1.   | Connection of Interface Pod to Troubleshooter                  |      |

| 3-1.   | 8088 Pin Assignments                                           |      |

| 5-1.   | 8088 Interface Pod General Block Diagram                       |      |

| 5-2.   | 8088 Interface Pod Detailed Block Diagram                      | 5-6  |

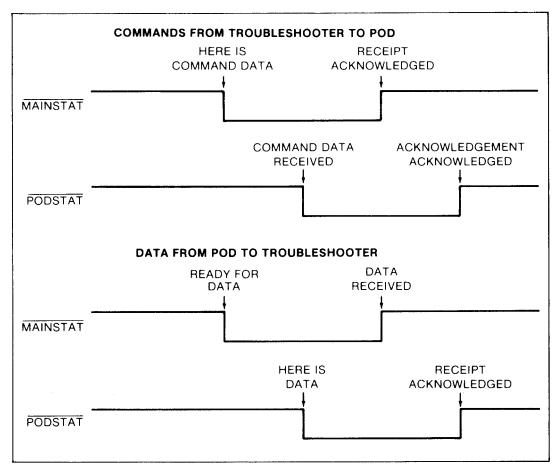

| 5-3.   | Handshake Signals                                              | 5-8  |

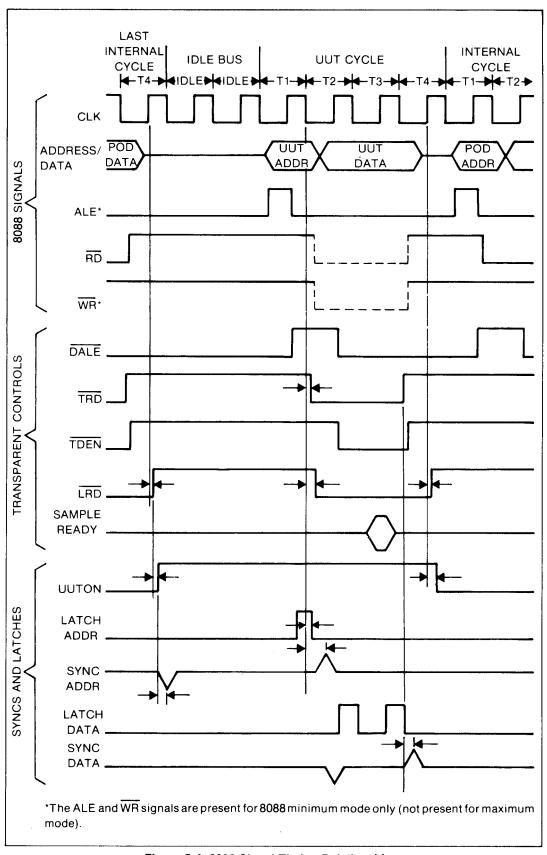

| 5-4.   | 8088 Signal Timing Relationships                               |      |

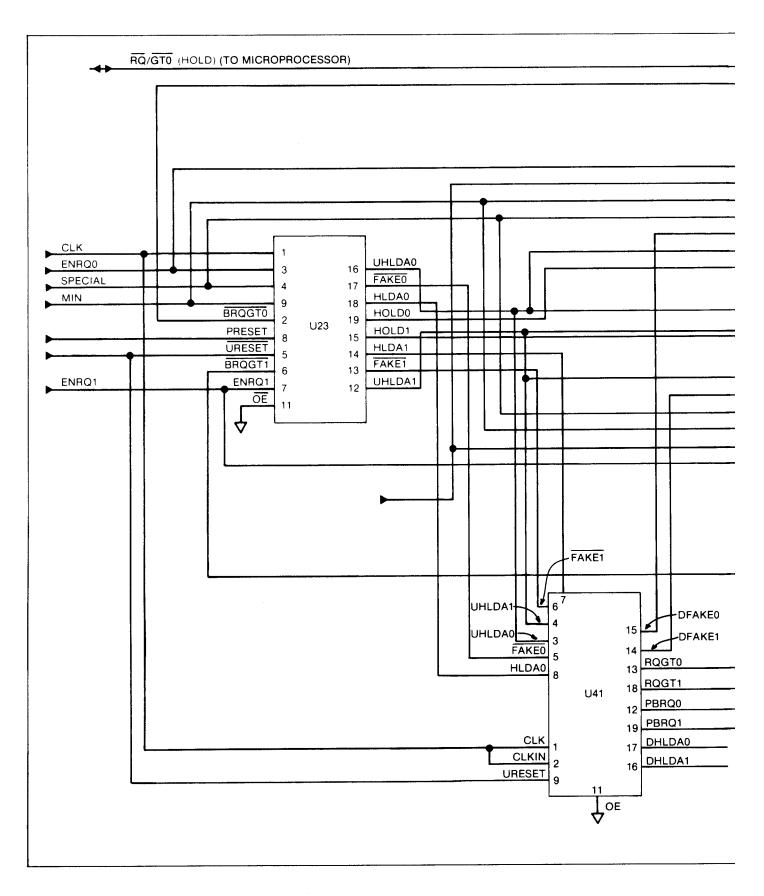

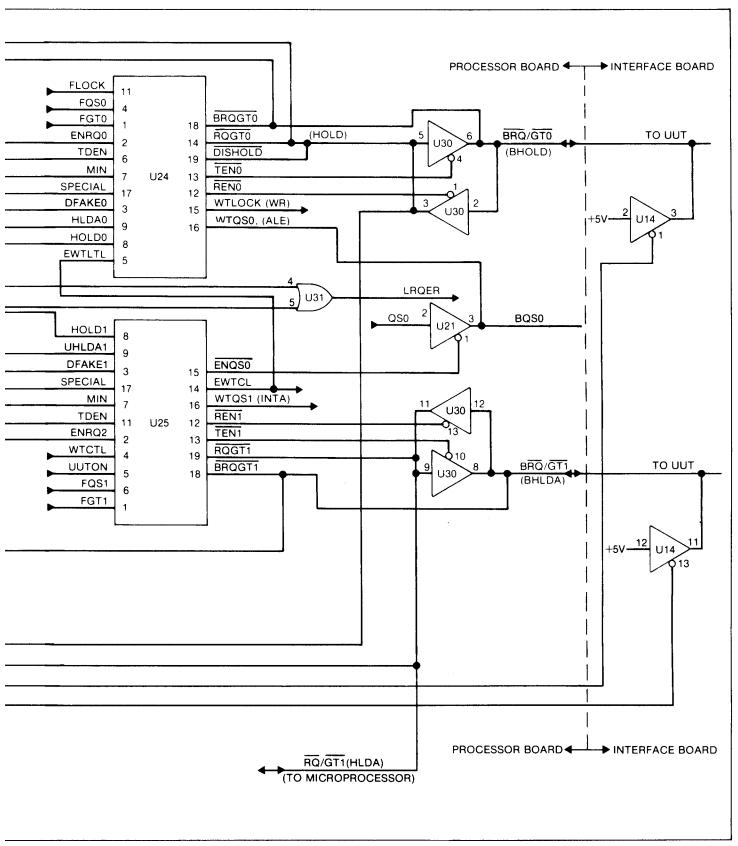

| 5-5.   | The Request/Grant Circuitry                                    | 5-12 |

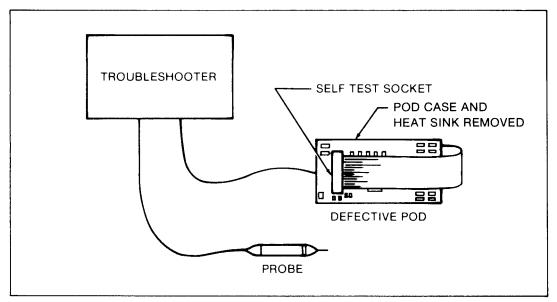

| 6-1.   | Troubleshooting a Defective Pod                                |      |

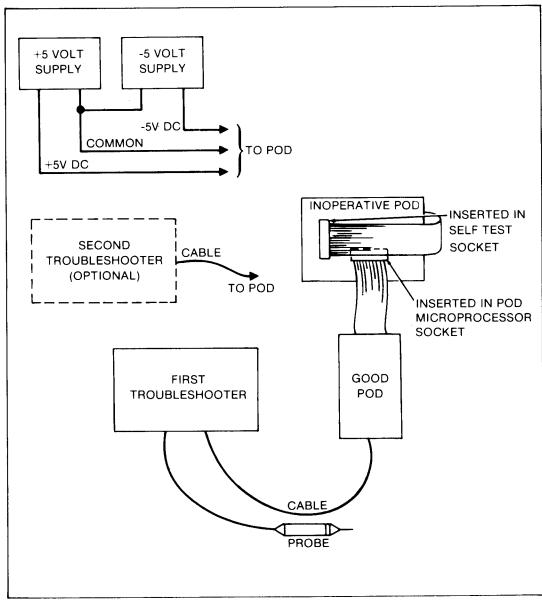

| 6-2.   | Troubleshooting an Inoperative Pod                             |      |

## Section 1 Introduction

#### NOTE

It is assumed that the user of this manual is familiar with the basic operation of one of the 9000 Series Micro System Troubleshooters as described in the 9000 Series Operator manuals.

#### 1-1. PURPOSE OF INTERFACE POD

The purpose of the 9000A-8088 Interface Pod (hereafter referred to as the pod) is to interface any 9000 Series Micro System Troubleshooter (hereafter referred to as the troubleshooter) to equipment employing an 8088 microprocessor.

The troubleshooter is designed to service printed circuit boards, instruments, and systems employing microprocessors. The architecture of the troubleshooter is general in nature, and is designed to accommodate devices with up to 32 address lines and 32 data lines. The pod adapts the general purpose architecture of the troubleshooter to a specific microprocessor or microprocessor family. The pod adapts such microprocessor-specific functions as pin layout, status/control functions, interrupt handling, timing, and memory and I/O addressing.

#### 1-2. DESCRIPTION OF POD

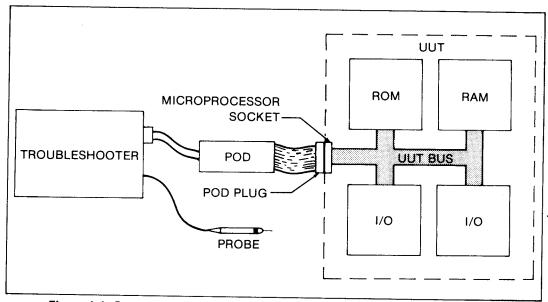

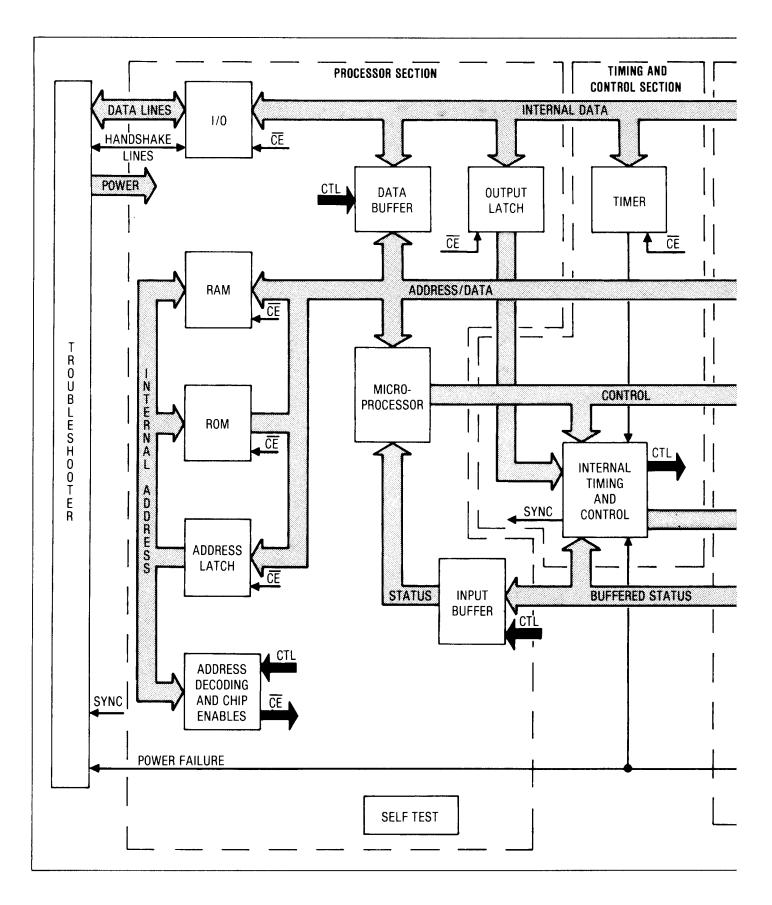

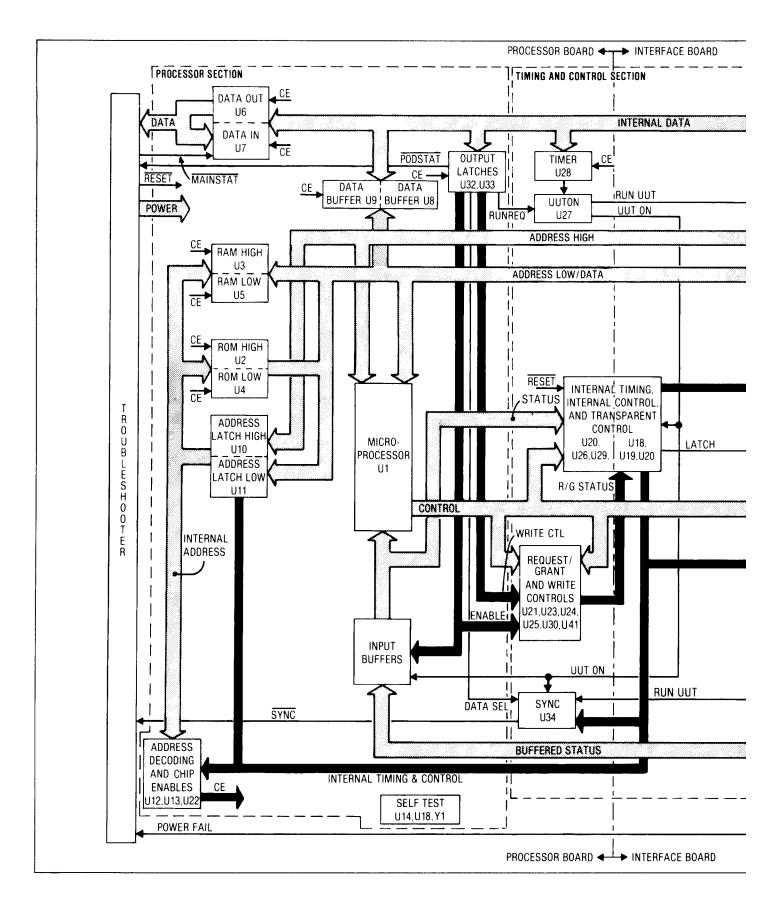

Figure 1-1 shows the communication between the pod, the troubleshooter, and the unitunder-test (hereafter referred to as the UUT). The pod connects to the troubleshooter through a shielded 24-conductor cable. The pod connects to the UUT through the microprocessor socket, which gives the troubleshooter access to all system components which normally communicate with the microprocessor.

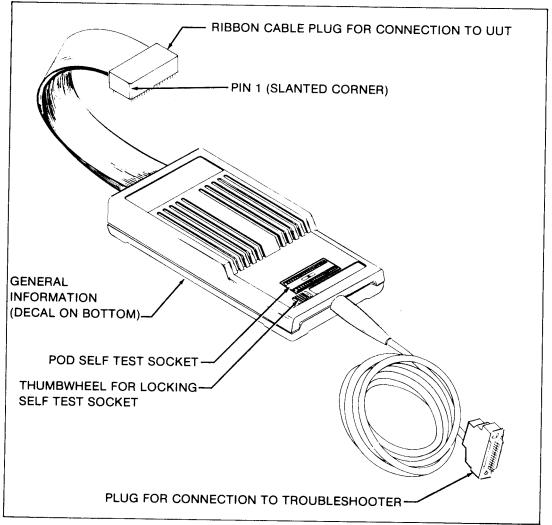

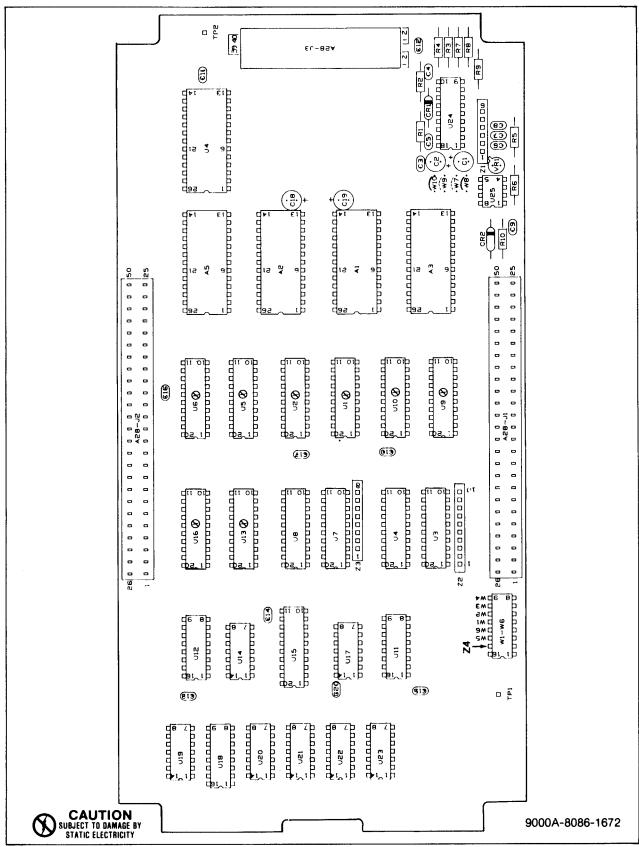

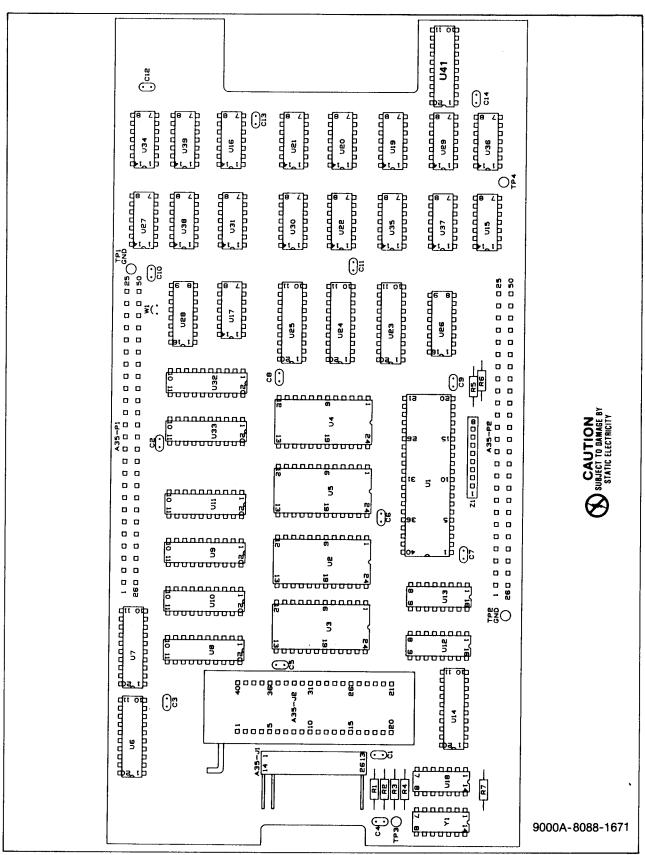

The external features of the pod are shown in Figure 1-2. The pod consists of a pair of printed circuit board assemblies mounted within a break-resistant case. The pod contains an 8088-2 microprocessor along with the supporting hardware and control software that is required to do the following:

- 1. Perform handshaking with the troubleshooter.

- 2. Receive and execute commands from the troubleshooter.

- 3. Report UUT status to the troubleshooter.

- 4. Allow the UUT microprocessor to operate with the UUT.

The troubleshooter supplies operating power (+5V,+12V and -5V) for the pod. The UUT provides the external clock signal required by the pod for operation. Using the UUT

clock signal allows the troubleshooter and pod to function at the designed operating speed of the UUT.

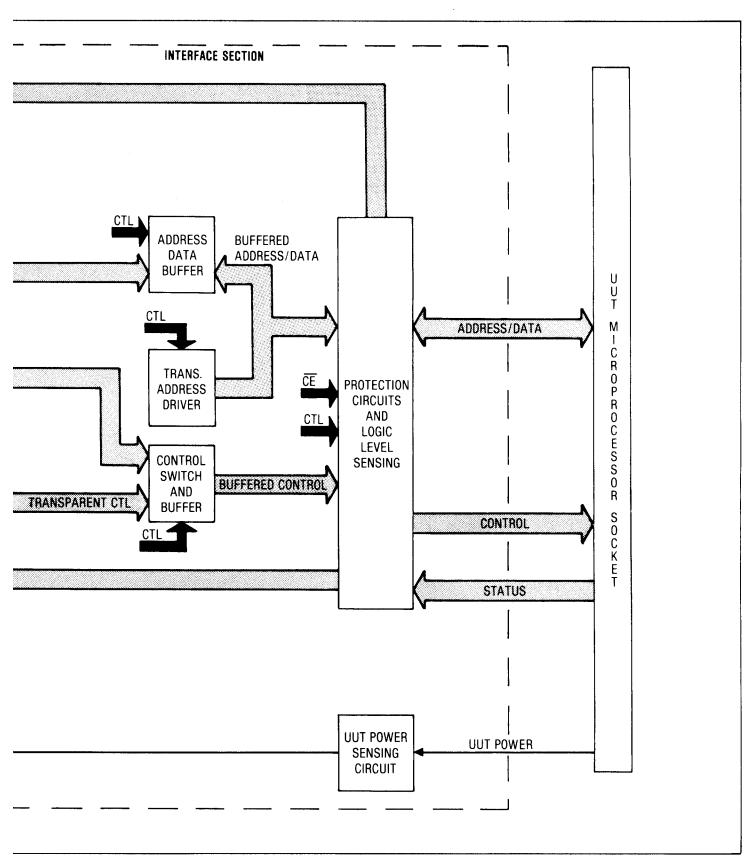

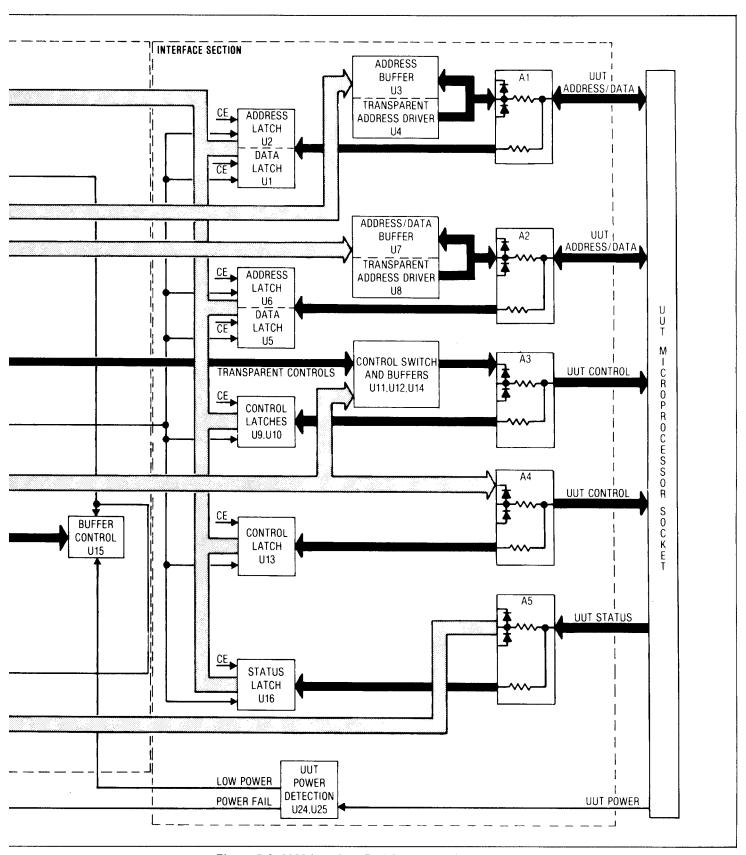

Logic level detection circuits are provided on each line to the UUT. These circuits allow detection of bus shorts, stuck-high or stuck-low conditions, and any bus drive conflict (two or more drivers attempting to drive the same bus line).

Over-voltage protection circuits are also provided on each line to the UUT. These circuits guard against pod damage which could result from the following:

- 1. Incorrectly inserting the ribbon cable plug in the UUT microprocessor socket.

- 2. UUT faults which place potentially-damaging voltages on the UUT microprocessor socket.

The over-voltage protection circuits guard against voltages of +12 to -7 volts on any one pin. Multiple faults, especially of long duration, may cause pod damage.

A power level sensing circuit constantly monitors the voltage level of the UUT power supply (+5V). If UUT power rises above or drops below an acceptable level the pod notifies the troubleshooter of the power fail condition.

A self test socket provided on the pod enables the troubleshooter to check pod operation. The self test socket is a 40-pin zero-insertion force type socket. The ribbon cable plug must be connected to the self test socket during self test operation. The ribbon cable plug should also be inserted into this socket when the pod is not in use to provide protection for the plug.

#### 1-3. SPECIFICATIONS

Specifications for the pod are listed in Table 1-1.

Figure 1-1. Communication Between the Troubleshooter, the Pod, and the UUT

Figure 1-2. External Features of the 8088 Interface Pod

#### Table 1-1. 8088 Pod Specifications

#### **ELECTRICAL PERFORMANCE**

Power Dissipation ...... 10.0 watts maximum

Maximum External Voltage ...... -7 to +12 volts may be applied between ground

and any ribbon cable plug pin continuously.

#### **MICROPROCESSOR SIGNALS**

Tristate Output Leakage Current .....  $+20/-100 \mu A$  typical

#### TIMING CHARACTERISTICS

#### Maximum Clock Frequency

Added Delays to 8086 Signals

LOW-TO-HIGH TRANSITIONS .... 20 ns typical HIGH-TO-LOW TRANSITIONS .... 24 ns typical

#### **UUT POWER DETECTION**

Detection of Low Vcc Fault ......... Vcc < +4.5VDetection of High Vcc Fault ........ Vcc > +5.5V

#### **GENERAL**

**Size** ...... 5.7 cm H x 14.5 cm W x 27.1 cm L (2.2 in H x

5.7 in W x 10.7 in L)

Weight ..... 1.4 kg (3.1 lbs)

Environment

+40°C to +50°C, RH\* <45%

Protection Class 3 ...... Relates solely to insulation or grounding

defined in IEC 348.

<sup>\*</sup>All relative humidity (RH) conditions are non-condensing.

## Section 2 Installation and Self Test

#### 2-1. INTRODUCTION

The procedures for performing the pod self test and connecting the pod to the troubleshooter and the UUT are given in the following paragraphs.

#### 2-2. PERFORMING THE POD SELF TEST

To perform the pod self test, perform the following steps:

- 1. Remove power from the troubleshooter.

- 2. Open the pins of the pod self test socket by operating the adjacent thumbwheel. Insert the ribbon cable plug into the socket and close the socket using the thumbwheel.

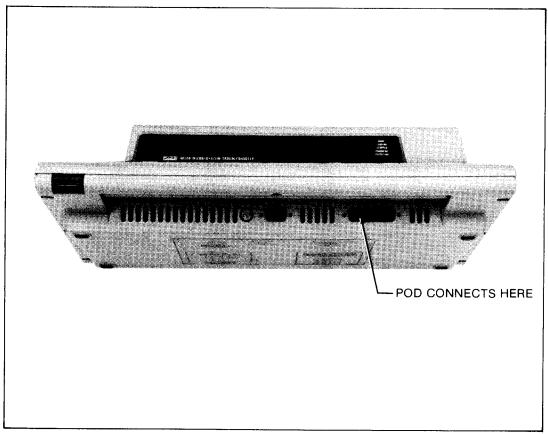

- 3. Using the round shielded cable, connect the pod to the troubleshooter at the location shown in Figure 2-1. Secure the connector using the sliding collar.

- 4. Apply power to the troubleshooter.

- 5. Press the BUS TEST key to initiate the pod self test.

If the troubleshooter displays the message POD SELF TEST 8088 OK, then the pod is operating properly.

If the troubleshooter displays the message POD SELF TEST 8088 FAIL xx, the pod may not be operating properly. (The letters xx correspond to a failure code describing the error; the failure codes are listed in Section 6.) Make sure the pod ribbon cable plug is properly positioned in the self test socket and try the self test again.

For information about pod troubleshooting and repair, refer to Section 6.

#### 2-3. CONNECTING THE POD TO THE UUT

#### WARNING

TO PREVENT POSSIBLE HAZARDS TO THE OPERATOR OR DAMAGE TO THE UUT, DISCONNECT ALL HIGH-VOLTAGE POWER SUPPLIES, THERMAL ELEMENTS, MOTORS, OR MECHANICAL ACTUATORS WHICH ARE CONTROLLED OR PROGRAMMED BY THE UUT MICROPROCESSOR BEFORE CONNECTING THE POD.

Connect the pod between the troubleshooter and the UUT as follows:

- 1. Be sure that power is removed from the UUT.

- 2. Disconnect UUT analog outputs or potentially hazardous UUT peripheral devices as described in the warning at the beginning of this section.

- 3. Disassemble the UUT to gain access to the UUT microprocessor socket. If the UUT microprocessor is still in the socket, remove the microprocessor.

- 4. Turn the pod self test socket thumbwheel to release the pod plug, and remove the pod plug from the self test socket.

- 5. Insert the pod plug into the UUT microprocessor socket. Make sure the slanted corner of the pod plug is aligned with pin 1 of the UUT microprocessor socket.

- 6. Reassemble the UUT using extender boards if necessary.

#### **CAUTION**

Be sure that troubleshooter power is on before turning UUT power on in order to activate pod protection circuits.

7. Apply power to the troubleshooter and the UUT.

Figure 2-1. Connection of Interface Pod to Troubleshooter

## Section 3 Microprocessor Data

#### 3-1. INTRODUCTION

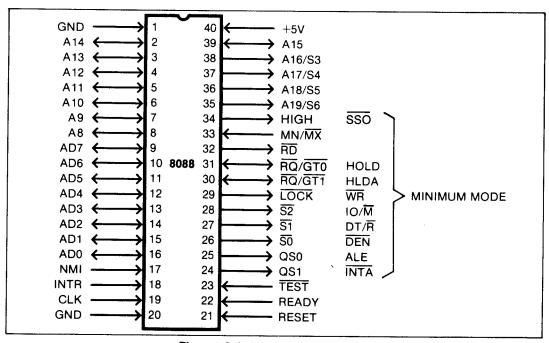

This section contains microprocessor data which may be useful during operation of the troubleshooter. This information includes descriptions of 8088 signals and pin assignments for both the minimum and maximum modes of operation.

#### 3-2. MICROPROCESSOR SIGNALS

Table 3-1 lists all of the 8088 microprocessor signals and provides a brief description of each signal. Figure 3-1 shows the 8088 pin assignments.

Table 3-1. Microprocessor Signals

| SIGNAL NAME                          | DESCRIPTION                                                                                                                                                                                 |                                                     |                                                                                                                                                       |                                |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| AD0-AD7                              | ADDRESS/DATA LINES. These 8 lines constitute 8 lines of the time-multiplexed memory address bus (during T1 of the bus cycle) and the data bus (during T2, T3, TW, and T4 of the bus cycle). |                                                     |                                                                                                                                                       |                                |

| A8-A15                               |                                                                                                                                                                                             |                                                     | s constitute 8 lines of the or the entire bus cycle (T1-T                                                                                             |                                |

| A19/S6<br>A18/S5<br>A17/S4<br>A16/S3 | lines of the time-mu<br>bus cycle) and four b<br>the bus cycle). S5 re                                                                                                                      | Itiplexed mem<br>us cycle statu<br>Iflects the stat | e four output lines constitution or address bus (during Tous slines (during T2, T3, TW, are of the interrupt enable flater to the following table for | of the<br>nd T4 of<br>g. S6 is |

|                                      | S4                                                                                                                                                                                          | S3                                                  | REGISTER USED                                                                                                                                         |                                |

|                                      | 0                                                                                                                                                                                           | 0                                                   | Extra data (ES)                                                                                                                                       |                                |

|                                      | 0                                                                                                                                                                                           | 1                                                   | Stack (SS)                                                                                                                                            |                                |

|                                      | 1                                                                                                                                                                                           | 0                                                   | Code (CS) or none                                                                                                                                     |                                |

|                                      | 1                                                                                                                                                                                           | 1                                                   | Data (DS)                                                                                                                                             |                                |

|                                      |                                                                                                                                                                                             |                                                     |                                                                                                                                                       |                                |

| RD                                   |                                                                                                                                                                                             |                                                     | put is made low to notify e<br>ead data from the time mult                                                                                            |                                |

Table 3-1. Microprocessor Signals (cont)

| the minimum relects of the system bus.  Tound applied to nitroller, rather that (such as easonable allows mand outputs nections.  TATUS LINES (in aximum mode, easy external of the soss is set to the | mode or manum mode in this line so that constitute that the 80 in a multi-perior the lines perior to be redefined in these outpersons. The | elects the elects the elects the rocessor soreviously fined in ordenate per the status s            | allows the 8088 to be operated ode. A +5V applied to this line he 8088 supports small, single-ew devices configured around maximum mode in which a buses all bus control and command ystem). In the maximum mode, delegated to bus control and der to support multi-processing en the 8088 is configured in the rovide eight status signals for ignals identify the type of buse the following table for status |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the minimum relects of the system bus.  Tound applied to nitroller, rather that (such as easonable allows mand outputs nections.  TATUS LINES (in aximum mode, easy external of the soss is set to the | mode or manum mode in this line so this line so than the 80 in a multi-p the lines posto be rede                                           | elects the elects the elects the rocessor soreviously fined in ordenate per the status s            | maximum mode in which a buses all bus control and command ystem). In the maximum mode, delegated to bus control and der to support multi-processing en the 8088 is configured in the rovide eight status signals for ignals identify the type of bus                                                                                                                                                            |

| aximum mode,<br>e by external o<br>cle the 8088 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | these outp<br>devices. Th                                                                                                                  | out lines p<br>e status s                                                                           | rovide eight status signals for ignals identify the type of bus                                                                                                                                                                                                                                                                                                                                                 |

| e coding.  S2  0 0 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51<br>0<br>0<br>1<br>1<br>0<br>0                                                                                                           | 50<br>0<br>1<br>0<br>1<br>0<br>1<br>0                                                               | TYPE OF BUS CYCLE Interrupt Acknowledge Read I/O Write I/O Halt Instruction Fetch Read Memory Write Memory Passive, no bus cycle                                                                                                                                                                                                                                                                                |

| e is logically embination of \$\overline{S}\$.  88 is starting to \$\overline{1}\$.  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | quivalent to<br>SO, I0/M, ar                                                                                                               | the SO lind DT/R id                                                                                 | ne in the maximum mode. The entifies the type of bus cycle the                                                                                                                                                                                                                                                                                                                                                  |

| f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e is logically embination of \$\overline{S}\$ is starting to \$\overline{IO/M}\$  1  1  1                                                  | is logically equivalent to mbination of SSO, I0/M, as is starting to execute. S   IO/M   DT/R     1 | 1 0 0<br>1 0 1<br>1 1 0 1<br>1 1 1 0<br>1 1 1 0<br>0 0 0 0<br>0 0 1                                                                                                                                                                                                                                                                                                                                             |

Table 3-1. Microprocessor Signals (cont)

| SIGNAL NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QS0,QS1     | QUEUE LINES (maximum mode). When the 8088 is configured in the maximum mode, these output lines permit external monitoring of the internal instruction queue. This allows instruction set extension processing by a co-processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LOCK        | LOCK OUTPUT LINE (maximum mode). When the 8088 is configured in the maximum mode, this software-controlled output is used in conjunction with an external bus arbiter to guarantee exclusive access of a shared system bus for the duration of an instruction. During an interrupt acknowledge sequence, the Lock output is activated to signal bus arbiters in the system that the bus should not be accessed by any other processor.                                                                                                                                                                                                                                                                                                                                                    |

| RQ/GT0      | REQUEST/GRANT LINE (maximum mode). This input/output is used in multi-processor applications to request and grant bus usage, and is tied to the same line of the CPU. The request/grant sequence is a three-phase cycle:  1. Request Phase: the requesting device outputs a pulse on the RQ/GTO line.  2. Grant Phase: the CPU outputs a pulse (onto this same line) at the end of either the current bus cycle or the idle clock period, indicating to the requesting device that it has floated the system bus, and is about to disconnect from the bus controller and enter a hold state.  3. Release Phase: the requesting device again outputs a pulse onto the same line to notify the CPU that it is ready to release the bus. The CPU regains bus access on the next clock cycle. |

| RQ/GT1      | REQUEST/GRANT LINE (maximum mode). This line is similar to the RQ/GTO line described above except that the RQ/GTO line has priority when simultaneous requests are received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HOLD        | HOLD LINE (minimum mode). This input, when made high, causes the 8088 to halt at the completion of the current instruction. During the Hold state, the 8088 floats the RD, WR, INTA, and IO/M command lines, the DEN and DT/R bus control lines, and the multiplexed address/data/status lines to a high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HLDA        | HOLD ACKNOWLEDGE LINE (minimum mode). This output is made high by the 8088 when a Hold input is acknowledged and the appropriate command, status, bus lines are floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 3-1. Microprocessor Signals (cont)

| Table 3-1. Microprocessor Signals (cont) |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SIGNAL NAME                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| WR                                       | WRITE CONTROL LINE (minimum mode). This output is made low when the 8088 places data on the multiplexed address/data lines (AD0-AD7) during a bus write operation.                                                                                                                                                                                                                                                                               |  |  |

| IO/M                                     | IO/MEMORY CONTROL LINE. This output is made high by the 8088 when the current bus operation involves an I/O device; this output is made low when the current bus write operation involves memory.                                                                                                                                                                                                                                                |  |  |

| DT/R̄                                    | DATA TRANSMIT/RECEIVE LINE (minimum mode). This output is made high by the 8088 during a bus write operation; this output is made low during a bus read operation. This line is typically used to control the direction of bus transceivers employed in the system.                                                                                                                                                                              |  |  |

| DEN                                      | DATA ENABLE LINE (minimum mode). This output is made low by the 8088 during the latter portion of a bus read or bus write operation when the multiplexed address/data bus is ready to handle data. This line is typically used to enable bus transceivers employed in the system.                                                                                                                                                                |  |  |

| ALE                                      | ADDRESS LATCH ENABLE LINE (minimum mode). This output is made high by the 8088 during T1 of the bus cycle to indicate the presence of address on the time-multiplexed memory bus. The falling edge of ALE is typically used by external devices to latch the address from the data/status information.                                                                                                                                           |  |  |

| INTA                                     | INTERRUPT ACKNOWLEDGE LINE (minimum mode). This output is made low by the 8088 during each of two interrupt acknowledge bus cycles which follow an interrupt request on the INTR line. The first INTA signal is used by external devices as an indication that the address/data bus is floated; and the second INTA signal is used by the external interrupt system to place a byte on the data bus that identifies the source of the interrupt. |  |  |

| INTR                                     | INTERRUPT REQUEST LINE. This input, when made high during the clock period preceding the end of the current instruction, requests external interrupt of the 8088. Interrupt requests at this input may be software masked/enabled.                                                                                                                                                                                                               |  |  |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

Table 3-1. Microprocessor Signals (cont)

| SIGNAL NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI         | NON-MASKABLE INTERRUPT. This input, when made high for a period of two or more clock cycles, provides a non-maskable interrupt to the 8088.                                                                                                                                                                                                                                         |

| READY       | WAIT STATE CONTROL. This input, when placed at a logic low level (not ready), causes the 8088 to enter a wait state. During the wait state, the 8088 inserts clock pulses to extend the bus cycle as required by the external device selecting the wait state.                                                                                                                      |

| TEST        | WAIT FOR TEST. This input allows software to test for some external condition before proceeding, thereby synchronizing operation to some external event. When required by software, this input is checked for a logic low every five clock periods, with the 8088 in an idle state between these checks. When the TEST input is tested and found low, the 8088 continues operation. |

| RESET       | RESET INPUT. When the 8088 receives a positive-going transition at the Reset input, it suspends all operations until the Reset signal goes low, at which time it initializes the system. System initialization includes clearing flags, setting the instruction pointer, setting various internal registers, and emptying the instruction queue.                                    |

Figures 3-1. 8088 Pin Assignments

## Section 4 Operating Information

#### 4-1. INTRODUCTION

This section contains information which pertains to operating the troubleshooter with 8088-based systems. This additional information complements the information in the troubleshooter operator and programming manuals, and covers such items as the following:

- Address space assignment

- Special address functions

- Characteristics of 8088 memory addressing

- Definition and bit assignment of status lines

- Definition of forcing and interrupt lines

- Bit assignment of control lines

- Definition and characteristics of user-writable control lines

- Interrupt handling

- Characteristics of Bus Test, Learn, and Run UUT

- Marginal UUT problems

#### 4-2. GETTING STARTED

After the pod is installed in the UUT and the UUT power is turned on (the troubleshooter power should already be on), it is possible to see the message POD TIMEOUT - ATTEMPTING RESET. When this message appears at power on, it is usually caused by faulty status lines (input lines to the pod microprocessor) called pod enable lines. The first thing to try is to reset the UUT. If that does not work, you can disable the enable lines with the troubleshooter Setup function by setting the Setup messages SET - ENABLE xxxx? to NO.

If you attempt an operation and the message is now ACTIVE FORCE LINE - LOOP?, the problem is probably caused by the same faulty status line. You can disable the reporting of this error and continue operation by selecting the troubleshooter Setup function again and setting the Setup message SET - TRAP ACTIVE FORCE LINE? to NO. For more information about enable lines refer to a later section titled User-Enableable Status Lines. For more information about forcing lines, refer to a later section titled Forcing Lines.

#### **NOTE**

Operating the pod with the enable lines disabled may degrade pod performance, especially if the UUT uses Wait states or DMA accesses.

If the message POD TIMEOUT - ATTEMPTING RESET remains even after you have disabled the enable lines, the problem may be caused by the UUT power supply (if the UUT power supply is below 3.5V, the pod will disable the inputs to the UUT to protect the UUT) or by a faulty UUT clock. If either of these problems exist, the pod will not operate until they are corrected. If the clock and the power supply are operating properly and the pod still does not work, perform a pod self test as described in Section 2.

If the UUT uses the maximum mode Request/Grant circuitry, it is recommended that you reset the UUT (after power is applied to the troubleshooter and the UUT) and then complete some operation involving the pod, such as Bus Test. This will ensure that the pod and UUT Request/Grant circuitry is synchronized.

#### 4-3. ADDRESS SPACE ASSIGNMENT

#### 4-4. Introduction

The 8088 has 20 physical address lines, AD0 through AD7, A8 through A15, and A16/S3 through A19/S6, which allow the 8088 to address one megabyte (1,048,576 bytes) of memory.

The address space assignment for the 8088 is listed in Table 4-1. The address space assignments are divided into two categories: memory address space and I/O address space.

For most UUTs, the basic word address memory space consists of 00 0000 through 0F FFFF. This address space includes all the addresses that are needed to test most UUT memory spaces. (Of course, for I/O space you will need the I/O addresses.)

Notice in Table 4-1 that the other memory address spaces are simply variants on the basic address space that are formed by using the prefixes 1X XXXX, 2X XXXX, and 3X XXXX (X may be any hexadecimal digit). These variant addresses result from using different "segment" registers to form the physical address, and are not encountered on most UUTs. The 8088 segment registers and the role they play in forming the 8088 addresses is described in a later section titled Role of 8088 Segment Registers in Memory Addressing.

The 8088 can address up to 64K (65,536 decimal) 8-bit ports. The I/O space is not segmented; to access a port address, the 8088 places the address on the lower 16 lines of the address bus. As shown in Table 4-1, the troubleshooter may access I/O ports at addresses 40 0000 through 40 FFFF.

#### 4-5. Special Addresses

In addition to the regular address spaces listed in Table 4-1, the pod has some special addresses that are used to access information in the pod or to cause the pod to perform some special functions. These special functions include interrupt handling routines, address specifications for Run UUT, a Quick Looping function, and a Quick RAM Test and Quick ROM Test. The special addresses used by each function are included with the description of each function in later sections.

#### 4-6. Role of 8088 Segment Registers in Memory Addressing

The 8088 has four segment registers that are used to form the effective memory address. The registers are the Extra Data register (ES), Stack register (SS), Code register (CS), and Data register (DS).

Table 4-1. Address Space Assignment

| FUNCTION        | ADDRESS            | DESCRIPTION                                                        |

|-----------------|--------------------|--------------------------------------------------------------------|

|                 | 00 0000 to 0F FFFF | Addresses memory space using the ES (Extra Data Segment) register. |

| MEMORY ACCESSES | 10 0000 to 1F FFFF | Addresses memory space using the SS (Stack segment) register.      |

| MEMORI ACCESSES | 20 0000 to 2F FFFF | Addresses memory space using the CS (Code Segment) register.       |

|                 | 30 0000 to 3F FFFF | Addresses memory space using the DS (Data Segment) register.       |

| I/O ACCESSES    | 40 0000 to 40 FFFF | Addresses I/O space.                                               |

The segments are logical units of memory up to 64K bytes long. Each segment is made up of contiguous memory locations and is an independent, separately-addressable unit. Each segment is assigned (by software) a base address which is its starting location in memory space. Segments may be contiguous to each other, separated from each other, or they may overlap partially or fully.

The 8088 CPU has direct access to four segments at a time. The CS register points to the current code segment from which instructions are fetched. The DS register points to the current data segment, which generally contains program variables. The SS register points to the current stack segment; stack operations are performed on locations in this segment. The ES register points to the current extra data segment, which is typically used for data storage.

During normal 8088 operation, a particular segment register contains the base (or starting) address of a segment. Memory addresses within the segment are created by adding the contents of some other register (which functions as an offset register) or memory location to the base address contained in the segment register.

For example, in the case of the code segment, which typically contains the object code, the base or starting address of the instruction code is held in the code (CS) registr while the offset address is maintained in the instruction pointer (similar in function to the program counter in other microprocessors). When the contents of the instruction pointer are added to the contents of the code register, the actual memory address is created for the instruction read from the system bus. Table 4-1 indicates which particular troubleshooter addresses use each segment register.

### 4-7. Demultiplexing Memory Addresses with the A16/S3 and A17/S4 Lines

The A16/S3 and A17/S4 Lines also play a role in determining the address. The 8088 provides only 20 physical address lines which would ordinarily allow only one megabyte of memory locations to be addressed (F FFFF hexadecimal). However, by demultiplexing the status information contained on lines A16/S3 and A17/S4 in conjunction with using the four segment registers, the available memory locations that may be addressed increases by a factor of four (3F FFFF hexadecimal). Lines A17/S4 and A16/S3 contain address information during the first portion of a bus cycle, and they

contain status information during the latter portion of a bus cycle. As shown in Table 3-1, these two lines indicate the segment register used in forming the memory address (presented on the address lines during the first portion of the current bus cycle).

In order to use the status information as the two high-order address bits, the system must first use the particular segment register which yields the bit pattern on lines A17/S4 and A16/S3 required for the desired memory address; then the system must demultiplex these two lines so that A17 and A16 address bits can be separated from the address bits contained in the S4 and S3 status bits.

#### 4-8. STATUS/CONTROL LINES

#### 4-9. Introduction

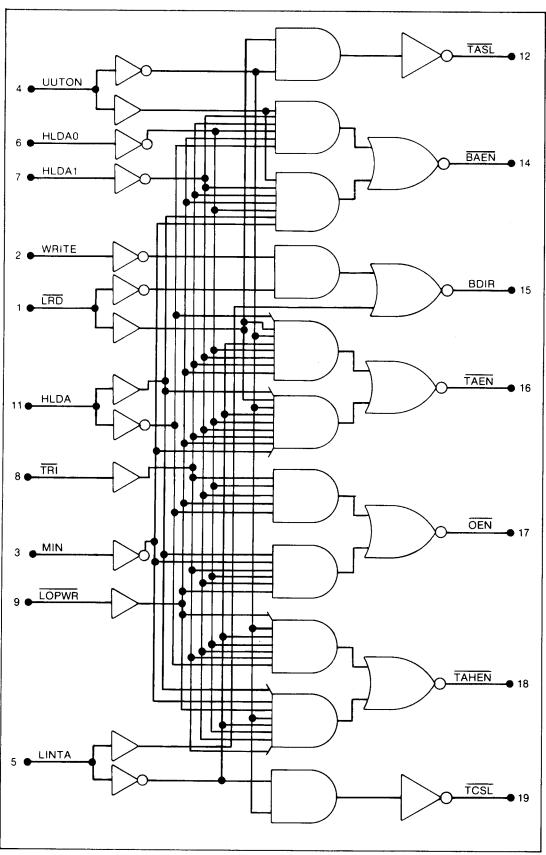

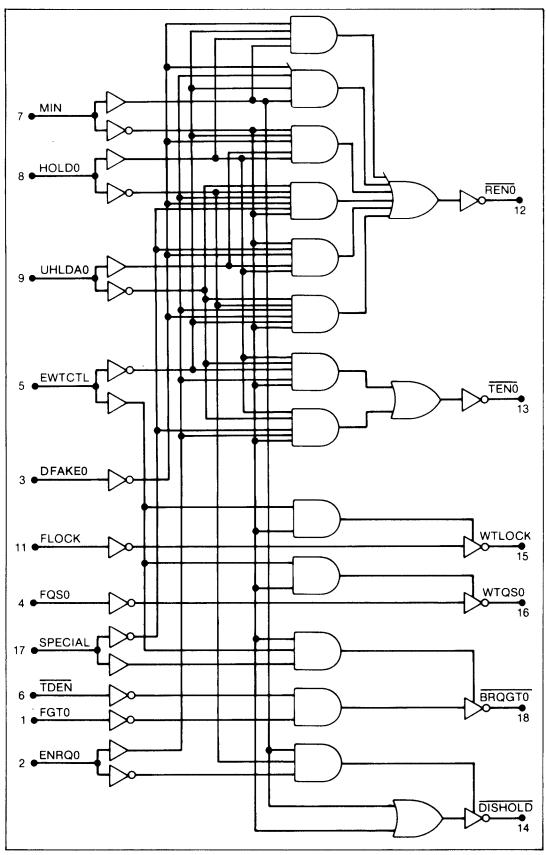

As part of the task of interfacing the general troubleshooter architecture with the UUT architecture, the pod makes specific assignments between the microprocessor lines and the troubleshooter. These assignments include the following:

- Bit number assignment of status lines

- User-writable control lines

- Bit number assignment of control lines

These assignments, which are summarized on a decal on the bottom of the pod, are listed in Table 4-2 and described in the following paragraphs:

#### NOTE

The terms status and control as used in this manual differ in meaning from the same terms used in the microprocessor manufacturer's literature. The troubleshooter considers input lines to the microprocessor to be status lines, and output lines to be control lines.

#### 4-10. Status Line Bit Assignments

When a Read Status operation is performed, the troubleshooter displays the result in binary form, where "1" indicates a logic high status line and a "0" indicates a logic low status line. To determine which characters of the display correspond to specific status lines, refer to Table 4-2.

#### NOTE

The status line assignments vary depending on the operating mode of the 8088 (maximum or minimum mode). Assignments for each mode are listed in Table 4-2 and on the pod decal.

For example, if a Read Status operation is performed and the Ready (Bit 0) and Interrupt Vector (Bit 11) lines are low with all other status lines high, the troubleshooter displays the message READ @ STS = 0111 1011 1110 OK. Bit numbers 0 (Ready) and 11 (Interrupt Vector) are zero to indicate a logic low, while other meaningful bits are 1 to indicate a logic high. Bit 6, which has no meaning as an 8088 status line, is always represented by a zero in the troubleshooter display message.

#### NOTE

The Power Fail, R/G Error, Interrupt Vector, HOLD0, and HOLD1 bits do not represent particular 8088 signals, but are generated within the pod. (Refer to the section titled Status Lines Unique to the Pod.) Bits 1 and 5 (HOLD0 and HOLD1) indicate the latched condition of these lines when operating in the maximum mode.

**STATUS LINES CONTROL LINES SIGNAL SIGNAL** BIT BIT **MAXIMUM** MINIMUM MAXIMUM MINIMUM NUMBER NUMBER MODE MODE MODE MODE 15 INT VECT INT VECT 11 14 **S6** S6 10 \*\*R/G ERROR **TEST** 13 TEST S5 S5 9 8 MN/MX MN/MX 12 S4 S4 7 **PWR FAIL PWR FAIL** 11 S3 S3  $\overline{S2}$ 10 IO/M 6 <u>S1</u> DT/R 9 5 †\*\*HOLD1  $\overline{so}$ 8 DEN 4 \*\*RESET \*\*RESET 7 SSO 3 †INTR †INTR 6 RD  $\overline{\mathsf{RD}}$ 2 NMI NMI 1 †\*\*HOLD0 †\*\*HOLD 5 \*SPECIAL 0 †\*\*READY †\*\*READY 4 \*GT1 \*HLDA 3 \*GT0 2 \*QS1 \*INTA \*QS0 1 ALE 0 \*LOCK WR

Table 4-2. Status and Control Line Bit Assignments

**†USER ENABLEABLE**

#### 4-11. User-Enableable Lines

The 8088 has several inputs which the operator can individually enable or disable (Ready, Hold, and INTR in the minimum mode, and Ready, RQ/GT0, RQ/GT1, and INTR in the maximum mode) by selecting the proper Setup message using the Setup function of the troubleshooter.

#### NOTE

The two maximum mode enable lines, RQ/GT0 and RQ/GT1, are related to the status lines HOLD0 and HOLD1. HOLD0 and HOLD1 are latches within the pod that indicate when the RQ/GT0 and RQ/GT1 lines have been pulsed. Because the request pulse is usually very brief, the condition of the latches HOLD0 and HOLD1 is reported in the Read Status operation. RQ/GT0 and RQ/GT1 are the physical lines that are enabled, and are the names used in the Setup messages SET-ENABLE xxxxxxx?

When these inputs are disabled, UUT-generated signals appearing at these inputs are prevented from affecting troubleshooter and pod operation. For example, a stuck-low Ready line would cause the 8088 within the pod to remain in a wait state, preventing normal troubleshooter/pod operation. When the Setup function of the troubleshooter is used to disable this input to the 8088 (by means of hardware in the pod), the Ready signal is prevented from reaching the 8088 within the pod, thus allowing the troubleshooter/pod interactions to take place normally.

<sup>\*</sup>USER WRITABLE

<sup>\*\*</sup>FORCING LINES

Any of these status lines may be enabled or disabled using the troubleshooter Setup function as described in the troubleshooter operator manual. The relevant Setup display message is SET-ENABLE xxxxxxx? where xxxxxx is the name of the status line (there is one Setup message for each enable line). Pressing the YES key on the troubleshooter enables the status line; pressing the NO key disables the status line.

#### NOTE

During troubleshooter Setup, selecting the message SET-ENABLE xxxxxx? NO prevents the enable line from affecting the operation of the pod (although the pod can still detect whether the line is high or low). This differs from selecting the troubleshooter Setup message SET-TRAP ACTIVE FORCE LINE? NO which does not prevent an enable line from affecting the operation of the microprocessor, but does prevent the active condition from being reported on the troubleshooter display.

#### 4-12. Status Lines Unique to the Pod

Several of the status lines reported during a Read Status operation are generated by the pod and not by the UUT. These lines consist of Power Fail, R/G Error, Interrupt Vector, HOLD0, and HOLD1. Since these lines are a function of the pod and not the 8088, they are not described in Section 3, but are described in the following paragraphs:

#### 4-13. POWER FAIL STATUS LINE

The Power Fail status line is set high by the pod whenever UUT power supply voltages drops below 4.5V or rises above 5.5V.

#### 4-14. R/G ERROR STATUS LINE (MAXIMUM MODE ONLY)

The Request/Grant Error (R/G ERROR) line is set high whenever the pod determines that the pod and UUT Request-Grant signals are not synchronized. This condition can be caused if the pod is reset and the UUT is not, or by a Write Control operation which toggles the GT0 or GT1 line. A reset from the UUT to the pod clears this condition.

#### 4-15. INTERRUPT VECTOR STATUS LINE

The Interrupt Vector line is set high by the pod whenever a new unread interrupt vector is available. This vector may be read as described in a part of Section 4 titled Using Special Addresses to Read Interrupt Type and Cascade Address.

#### 4-16. HOLDO AND HOLD1 STATUS LINES (MAXIMUM MODE ONLY)

The HOLD0 or HOLD1 line is set high by the pod to signify that the RQ/GT0 or RQ/GT1 line has been pulsed, which indicates that a Hold operation has been requested. The HOLD0 or HOLD1 line is cleared at the end of the Request/Grant release operation, or by a UUT reset.

#### 4-17. Forcing Lines

One of the troubleshooter error messages that may be displayed is the message ACTIVE FORCE LINE (@ aaaa)-LOOP? Forcing lines are a special category of status lines which, when active, can force the microprocessor into some specific state or action which causes a pod timeout. The ACTIVE FORCE LINE error message helps isolate status lines which are not functioning properly.

The forcing lines consist of Ready, HOLD0, HOLD1, Reset, and R/G Error in the maximum mode, and Ready, Hold, and Reset in the minimum mode. Notice that the Ready, Hold, HOLD0, and HOLD1 lines are user-enableable lines. If these user-enableable lines are disabled (using the troubleshooter Setup function), their inputs to the pod microprocessor are disabled, but the pod continues to monitor their condition; if

they are active (high), the pod reports to the troubleshooter that a forcing line is active. Note that if these user-enableable lines are enabled (using the troubleshooter Setup function), they are not considered forcing lines even when they are active.

The Reset line is hardware-disabled except during Run UUT, but it is monitored and reported as an active forcing line if it is active during non-Run UUT operation.

A typical way the ACTIVE FORCE LINE message would be encountered is as follows. Assume the pod and troubleshooter are connected to a UUT and the operator first turns on the power to the troubleshooter and the UUT (at power on the user-enableable lines are all enabled). When attempting a Read operation with the troubleshooter, the error message POD TIMEOUT - ATTEMPTING RESET appears. The operator enters the troubleshooter Setup function, disables the Ready enableable line, and again attempts a Read operation. This time the troubleshooter displays the message ACTIVE FORCE LINE @ aaaa-LOOP? (aaaa is the address specified for the Read operation).

To find out which line or lines are the active forcing lines, the operator presses the MORE key and the message STS BTS 0000 0000 0001 is displayed. According to Table 4-2, the Ready line is the 0 bit, so the display message indicates that the Ready line is the active forcing line that is not functioning properly. While the Ready line was enabled, its improper function caused the pod timeout to occur. After the Ready line was disabled, its improper function caused the ACTIVE FORCE LINE error message to appear.

#### *NOTE*

It is possible to disable the reporting of active forcing lines by selecting the troubleshooter Setup function message SET-TRAP ACTIVE FORCE LINE? NO. The pod will still monitor the lines, but the troubleshooter will not interrupt its operation to display the ACTIVE FORCE LINE error message on the display. Sometimes it is useful to disable the reporting of active forcing lines, particularly if the information is not needed by the operator. Reporting of the error message is enabled at power on.

#### 4-18. Interrupt Lines

Interrupt lines for the 8088 consist of INTR and NMI. The INTR input may be enabled by the operator as described in the previous section titled User-Enableable Status Lines. The NMI input is hardware-disabled except during operation in the Run UUT mode. Although disabled, the NMI input is routinely checked by the pod software and reported to the troubleshooter if held high by the UUT.

#### **NOTE**