## **Keystroke Functional Test (Part A)**

## **CONNECTION TABLE**

| STIMULUS     | MEASUREMENT  |  |  |

|--------------|--------------|--|--|

| I/O MOD      | I/O MOD      |  |  |

| U4-4<br>U4-5 | U1-4<br>U4-6 |  |  |

## **RESPONSE TABLE**

| SIGNAL | PART PIN | I/O MOD PIN | SIGNATURE |  |

|--------|----------|-------------|-----------|--|

| READY  | U1-4     | 4           | 0015      |  |

| SRDY   | U4-6     | 26          | 0015      |  |

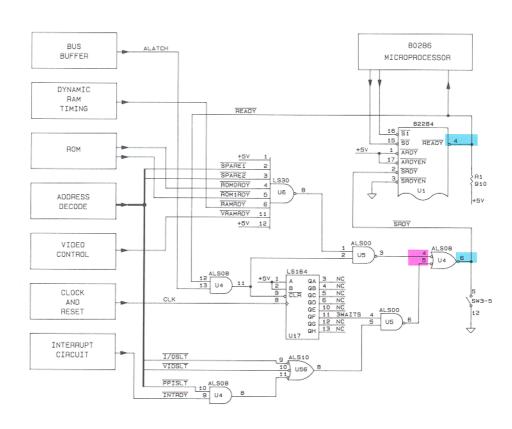

Figure 4-125: Ready Circuit Functional Test (Part A)

## **Keystroke Functional Test (Part B)**

### **CONNECTION TABLE**

| STIMULUS           | MEASUREMENT |

|--------------------|-------------|

| POD                | I/O MOD     |

| TEST ACCESS SOCKET | U4-6        |

| I/O MOD            |             |

| U4-11              |             |

### **RESPONSE TABLE #1**

| SIGNAL | PART PIN | I/O MOD PIN | SIGNATURE | ASYNC LEVEL |

|--------|----------|-------------|-----------|-------------|

| SRDY   | U4-6     | 26          | 0 0 0 0   | 10          |

### **RESPONSE TABLE #2**

| SIGNAL | PART PIN | I/O MOD PIN | ASYNC LEVEL | TRANS COUNT |

|--------|----------|-------------|-------------|-------------|

| SRDY   | U4-6     | 26          | 0 1         | 3           |

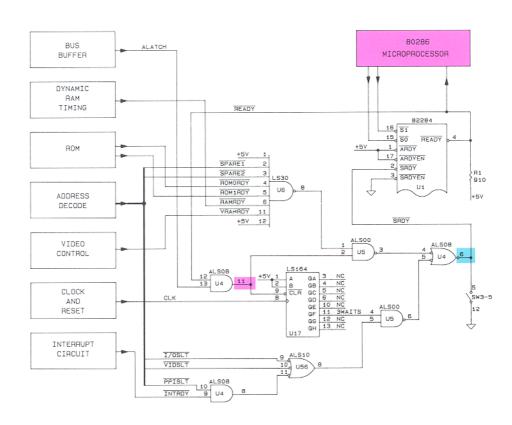

Figure 4-126: Ready Circuit Functional Test (Part B)

## **Keystroke Functional Test (Part C)**

## **CONNECTION TABLE**

| STIMULUS | MEASUREMENT |

|----------|-------------|

| U5-1     | I/O MOD     |

| U17-9    | U5-3        |

## **RESPONSE TABLE**

| SIGNAL | PART PIN | I/O MOD PIN | SIGNATURE |  |

|--------|----------|-------------|-----------|--|

|        | U5-3     | 3           | 0 0 0 A   |  |

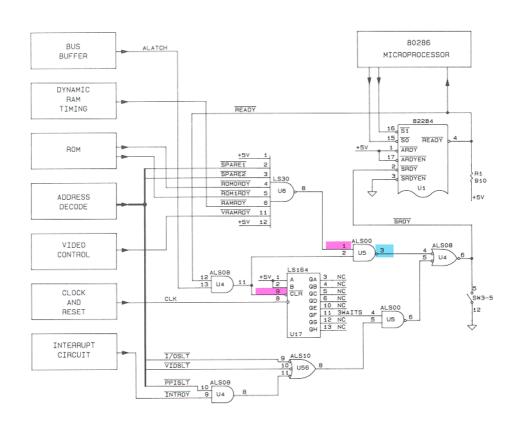

Figure 4-127: Ready Circuit Functional Test (Part C)

## **Keystroke Functional Test (Part D)**

### **CONNECTION TABLE**

| STIMULUS | MEASUREMENT CONTROL        | MEASUREMENT |

|----------|----------------------------|-------------|

| I/O MOD  | I/O MOD                    | I/O MOD     |

| U17-9    | CLOCK U1-10<br>START U4-11 | U17-11      |

### **RESPONSE TABLE #1**

| SIGNAL | PART PIN | I/O MOD PIN | ASYNC LEVEL | TRANS COUNT |

|--------|----------|-------------|-------------|-------------|

| 3WAITS | U17-11   | 17          | 01          | 1           |

## **RESPONSE TABLE #2**

| SIGNAL | PART PIN | I/O MOD PIN | TRANS COUNT |  |

|--------|----------|-------------|-------------|--|

| 3WAITS | U17-11   | 17          | 0           |  |

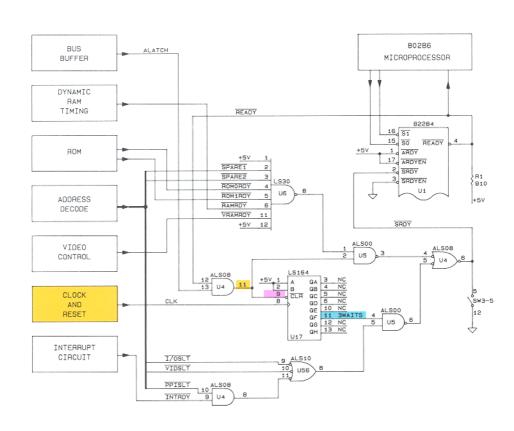

Figure 4-128: Ready Circuit Functional Test (Part D)

4.14.6.

The tst\_ready program is the programmed functional test for the Ready Circuit functional block. This program checks the Ready circuit using the gfi test command. If the gfi test command fails, the abort\_test program is executed and GFI troubleshooting begins. (See the Bus Buffer functional block for a discussion of the abort\_test program).

The *gfi test* command executes a number of stimulus programs. The *ready\_1*, *ready\_2*, *ready\_3*, and *ready\_4* stimulus programs overdrive nodes in order to break the feedback loop in the Ready circuit. These programs will ask the operator to use a second clip on a second component so that the circuit can be overdriven.

```

program tst ready

! FUNCTIONAL TEST of the READY functional block.

! This program tests the READY functional block of the Demo/Trainer.

! The gfi test command and I/O module are used to perform the test. The !

! ready test involves overdriving components to break the feedback loop !

! in the ready partition. Two I/O module clips are required; one for

! measurement and one for stimulus (overdriving).

! TEST PROGRAMS CALLED:

abort test (ref-pin)

If gfi has an accusation

display the accusation else

create a gfi hint for the

ref-pin and terminate the test!

program (GFI begins trouble- !

shooting).

if (qfi status "U1-4") = "untested" then

print "\nl\nlTESTING READY CIRCUIT"

podsetup 'enable ~ready' "off"

podsetup 'report forcing' "off"

if (gfi status "U1-4") = "untested" then gfi test "U1-4"

if (gfi status "U1-4") = "bad" or (gfi status "U1-2") = "bad" or

(gfi status "U1-3") = "bad" then

abort_test ("U1-4")

else

print "READY CIRCUIT PASSES"

end if

end if

end program

```

## **Stimulus Programs and Responses**

4.14.7.

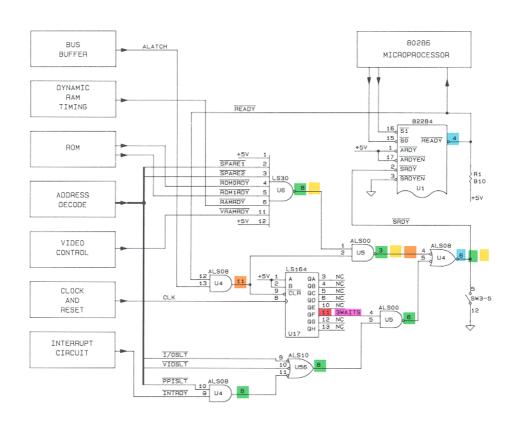

Figure 4-129 is the stimulus program planning diagram for the Ready Circuit functional block. The ready\_1, ready\_2, ready\_3, and ready\_4 stimulus programs use one clip for measurement and a second clip to overdrive the Ready circuit in order to break the feedback loop in this circuit. ready\_5 and ready\_6 provide stimulus to measure the operation of the I/O ready generator, U17. These two stimulus programs count how many 8 Mhz clocks occur during the wait state generated by U17.

The steps to break the Ready feedback loop to diagnose a fault are shown below:

- 1. Overdrive inputs U4-4 and U4-5. Then measure outputs U4-6 and U1-4. The 82284 chip (U1) synchronizes the Ready output (U4-6) to the microprocessor read/write cycles. This requires the ready\_I stimulus program to output the level, allow enough time for the signal to get synchronized, then check the level at the output U1-4.

- 2. Finish breaking the Ready signal feedback loop by overdriving inputs U4-12 and U4-13, then measure the outputs U4-11, U5-3, and U4-6. In order to measure U5-3 and U4-6, the other inputs U5-1 and U4-5 must be held high so the signals will flow through the AND gates. The ready\_4 stimulus program performs this step.

- 3. Hold the node with output source U4-11 high. This allows signals from U6 to flow through U5-3 to U4-6. At the same time, holding U4-11 high causes output U17-11 to stabilize at a high state, allowing signals from U56 to ripple through U5-6 to U4-6. Now use the pod to exercise the Ready Circuit inputs that are driven by the Address Decode functional block. The ready 2 stimulus program performs this sequence for all components that can be forced to use zero wait states. It does this by disabling U17 (all

components except RAM and Video RAM). Since the pod has turned ~READY ENABLE OFF, the pod generates a sync pulse with zero wait states. Because the RAM and Video RAM return wait states, taking signature measurements on RAM and Video RAM will turn out to be unstable. To solve this problem, ready 2 accesses all components except RAM and Video RAM. Then the ready 3 stimulus program performs a similar operation, but exercises only RAM and Video RAM. ready 3 responses are characterized by asynchronous level history and transition counts to allow the RAM and Video RAM wait state signals to be measured.

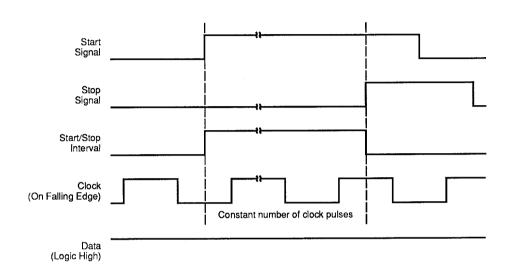

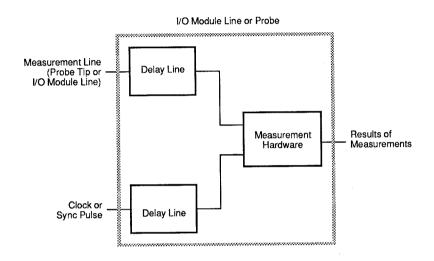

4. Measure the I/O component wait state generator, U17. The Clear input at U17-9 is toggled low. At the same time a measurement using external Clock (and Start) is made. The External Clock line is connected to the 8 MHz clock CLK and the Start line is connected to the node which includes U17-9. A Stop Count is set and transition counts and level history are measured. The ready 6 stimulus program uses a Stop Count of four clocks and the response is expected to be low level history and zero transitions, indicating that the wait state output was low for at least four clocks. The ready 5 stimulus program uses a Stop Count of six clocks. In this case, a response of high and low level history is expected, and a transition count of 1 is expected. These results indicate that the wait state finished within six clock cycles.

## Advice for Making GFI Work in the Presence of Ready Faults

When a Ready fault exists, a forcing-line fault condition will be generated. However, the pod must ignore the Ready forcing-line fault condition so that the stimulus program will execute completely. Otherwise, a fault condition would be generated and GFI would terminate. To turn this report off, a SETUP REPORT FORCING ~READY OFF command can be

performed. When this is done, the pod will continue to respond to the Ready signal, but will not generate a fault message. If the Ready signal is stuck high, the pod will cause the 9100A/9105A to generate a pod timeout fault condition. To cure this, a SETUP ENABLE ~READY OFF command is performed. At this point, GFI will work properly and Ready problems can be isolated to the failing component or node.

More generally, GFI works best if every stimulus program turns all reporting conditions off. In addition, those stimulus programs that create activity in the kernel area, may need to turn off Enable Ready. All Demo/Trainer UUT stimulus programs related to the address bus, data bus, control signals, address decoding, interrupts, and ready circuitry turn the Ready Enable off at the beginning of the stimulus program and the turn Ready Enable back on at the end of the program.

One more note: the 80286 microprocessor uses a separate bus controller that has no feedback lines to the microprocessor. When the pod disables the Ready input and performs zero wait state operations regardless of the Ready input, the bus controller can get out of synchronization from the pod and may get confused. When this happens, an enabled line timeout fault condition is generated. The solution is to provide a handler for that fault condition in each stimulus program that enables and disables Ready. The handler for the fault condition should call a program which performs a recovery procedure. The recovery procedure depends on the UUT. Usually, forcing the Ready line active or performing a Reset will recover synchronization. Or, by disabling Ready and then performing a read or write in memory space followed by enabling Ready may recover synchronization of the 80286 pod and the bus controller. Most other microprocessors do not have this problem.

## Stimulus Program Planning

### PROGRAM: READY\_1

OVERDRIVES U4-6 TO CHECK THE SYNCHRONIZED READY OUTPUT

#### **MEASUREMENT AT:**

U1-4 U4-6

### PROGRAM: READY\_4

BREAKS THE READY FEEDBACK LOOP BY OVERDRIVING THE NODE AT U4-11

#### **MEASUREMENT AT:**

U4-11 U5-3

# PROGRAM: READY\_5

OVERDRIVES THE INPUT TO THE I/O WAIT STATE GENERATOR AND CHECKS THAT THE OUTPUT U17-11 TRANSITIONS FROM LOW TO HIGH WITHIN 7 CLOCKS OF THE INPUT U17-9

### MEASUREMENT AT:

1147 44

#### PROGRAM: READY\_2

OVERDRIVES THE NODE AT U4-11 AND ALSO EXERCISES THE READY RETURN LINES (EXCEPT VRAM AND VRAMRDY)

### **MEASUREMENT AT:**

U4-6,8 U5-3,6 U6-8 U56-8

### PROGRAM: READY\_3

OVERDRIVES THE NODE AT U4-11 AND EXERCISES THE READY RETURN LINES VRAM AND VRAMRDY

### MEASUREMENT AT:

U4-6

U5-3 U6-8

#### PROGRAM: READY\_6

OVERDRIVES THE INTUT TO THE I/O WAIT STATE GENERATOR AND CHECKS THAT THE OUTPUT U17-11 TRANSITIONS FROM HIGH TO LOW WITHIN 4 CLOCKS AFTER U17-9 GOES HIGH

#### MEASUREMENT AT:

U17-11

Figure 4-129: Ready Circuit Stimulus Program Planning

program ready\_1

! the outputs in the UUT that are stimulated by the stimulus program. !

! This stimulus program is one of the programs which creates activity !

! In the kernel area of the UUT. These programs create activity with !

! or without the ready circuit working properly. Because of this, all !

! the stimulus programs in the kernel area must disable the READY input !

! to the pod, then perform the stimulus, then re-enable the READY input !

! to the pod. The 80286 microprocessor has a separate bus controller; !

! the stimulus programs in the kernel area must disable the READY input! to the pod, then perform the stimulus, then re-enable the READY input! to the pod. The 80286 microprocessor has a separate bus controller; for this reason, disabling ready and performing stimulus can get the! bus controller out of synchronization with the pod. Two fault! handlers trap pod timeout conditions that indicate the bus controller is out of synchronization. The recover() program is executed to! resynchronize the bus controller and the pod.

### ! TEST PROGRAMS CALLED:

recover () The 80286 microprocessor has all bus controller that is totally! separate from the pod. In ! some cases the pod can get out! of sync with the bus control-! ler. The recover program ! resynchronizes the pod and the! bus controller.!

! GRAPHICS PROGRAMS CALLED: ! (none)

! Global Variables Modified:

recover times Reset to Zero

! Local Variables Modified: ! measure dev

! measure\_dev Measurement device !

! stimulus\_dev Stimulus device (overdrives) !

declare global numeric recover times

(continued on the next page)

Figure 4-130: Stimulus Program (ready\_1)

```

FAULT HANDLERS:

handle pod_timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

handle pod timout no clk

end handle

! Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine measurement device

if (gfi control) = "yes" then

measure dev = gfi device

measure ref = gfi ref

print "Enter reference name of part to measure:"

(Chose U1, U4, U14 or U15)"

measure ref = "" \ input measure ref

if measure ref <> "Ul4" then

measure dev = clip ref measure ref

probe ref "U14-63" \ measure_dev = "/probe"

end if

end if

! Determine stimulus device

if measure ref = "U4" then

stimulus dev = measure dev

print "\07\1B[2J\1B[201\1B[3:1f

USING \1Bf7mSECOND\1Bf0m CLIP."

stimulus dev = clip ref "U4"

print "\1B[20h"

end if

print "Stimulus Program READY 1"

```

Figure 4-130: Stimulus Program (ready\_1) - continued

! Setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'standby function off'

```

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

reset device measure dev

reset device stimulus dev

sync device measure_dev, mode "int"

! Perform Stimulus

arm device measure dev

writepin device "U4", pin 4, level "1", mode "latch"

writepin device "U4", pin 5, level "1", mode "latch"

strobeclock device measure dev

writepin device "U4", pin \overline{4}, level "0", mode "latch"

writepin device "U4", pin 5, level "1", mode "latch"

strobeclock device measure dev

writepin device "U4", pin \overline{4}, level "1", mode "latch"

writepin device "U4", pin 5, level "1", mode "latch"

strobeclock device measure dev

writepin device "U4", pin \overline{4}, level "1", mode "latch"

writepin device "U4", pin 5, level "0", mode "latch"

strobeclock device measure dev

writepin device "U4", pin \overline{4}, level "1", mode "latch"

writepin device "U4", pin 5, level "1", mode "latch"

strobeclock device measure dev

readout device measure_dev

clearoutputs device stimulus dev

podsetup 'standby function on'

podsetup 'enable ~ready' "on"

end program

```

Figure 4-130: Stimulus Program (ready\_1) - continued

| STIMULUS P<br>DESCRIPTIO | ROGRAM NAME:<br>N:                | READY_               | 1                 |                                      | SIZE:         | 94 BYTES        |

|--------------------------|-----------------------------------|----------------------|-------------------|--------------------------------------|---------------|-----------------|

| Node<br>Signal Src       | Learned<br>With                   | sig                  |                   | onse Data<br>Clk Counter<br>LVL Mode | Counter Range | Priority<br>Pin |

| U4-6<br>U1-4<br>U1-4     | I/O MODULE<br>PROBE<br>I/O MODULE | 0015<br>0015<br>0015 | 1 0<br>1 0<br>1 0 | TRANS<br>TRANS<br>TRANS              |               |                 |

Figure 4-131: Response File (ready\_1)

program ready\_2

! STIMULUS PROGRAM overdrives U4 in ready circuit. ! Characterizes U4-6 and U1-4.

! Stimulus programs and response files are used by GFI to backtrace ! from a failing node. The stimulus program must create repeatable UUT ! activity and the response file contains the known-good responses for ! the outputs in the UUT that are stimulated by the stimulus program. !

! This stimulus program is one of the programs which creates activity ! in the kernel area of the UUT. These programs create activity with ! ! or without the ready circuit working properly. Because of this, all ! the stimulus programs in the kernel area must disable the READY input ! to the pod, then perform the stimulus, then re-enable the READY input ! to the pod. The 80286 microprocessor has a separate bus controller; ! for this reason, disabling ready and performing stimulus can get the ! bus controller out of synchronization with the pod. Two fault ! handlers trap pod timeout conditions that indicate the bus controller ! is out of synchronization. The recover() program is executed to ! resynchronize the bus controller and the pod. !

! TEST PROGRAMS CALLED:

recover () The 80286 microprocessor has a! bus controller that is totally! separate from the pod. In ! some cases the pod can get out! of sync with the bus control-! ler. The recover program !

resynchronizes the pod and the!

bus controller.

GRAPHICS PROGRAMS CALLED: (none)

! Global Variables Modified: ! recover times Reset to Zero

! Local Variables Modified:

! measure\_dev Measurement\_device !

! stimulus\_dev Stimulus\_device (overdrives) !

declare global numeric recover times

(continued on the next page)

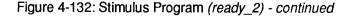

Figure 4-132: Stimulus Program (ready\_2)

```

FAULT HANDLERS:

handle pod timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

handle pod timout no clk

end handle

! Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine measurement device

if (gfi control) = "yes" then

measure dev = gfi device

measure ref = gfi ref

print "Enter reference name of part to measure:"

print "

(Chose U1, U4, U5, U6, U56 or U17)"

measure ref = "" \ input measure_ref

measure dev = clip ref measure ref

end if

! Determine stimulus device

if measure ref = "U1" then

print "\07\1B[2J\1B[201\1B[3;1f

USING \1B[7mSECOND\1B[0m CLIP."

stimulus dev = clip ref "U4"

print "\1B[20h"

else

stimulus_dev = measure_dev

end if

print "Stimulus Program READY 2"

! Setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

io byte = getspace space "i/o", size "byte"

mem word = getspace space "memory", size "word"

```

Figure 4-132: Stimulus Program (ready\_2) - continued

```

reset device measure dev

reset device stimulus dev

sync device measure dev, mode "pod"

sync device "/pod", mode "data"

old_cal = getoffset device measure dev

setoffset device measure dev, offset (1000000 - 56)

if measure ref = "U5" then

writepin device "U5", pin 2, level "1", mode "latch"

writepin device "U5", pin 4, level "1", mode "latch"

else if measure_ref = "U4" or measure_ref = "U1" then

writepin device "U4", pin 11, level "1", mode "latch"

end if

! Stimulate ICs and capture response.

arm device measure dev

! Start response capture.

setspace (mem word)

read addr $30000

! IPOLL

read addr $40000

! SPARE1

read addr $50000

: SPARE2

read addr $E0000

! ROMO

read addr $F0000

! ROM1

setspace (io_byte)

read addr 0

! VIDSLT

read addr $2000

! I/OSLT

read addr $4000

! PPISLT

readout device measure_dev

! End response capture.

if stimulus dev <> "/probe" then clearoutputs device stimulus dev

setoffset device measure_dev, offset old_cal

podsetup 'enable ~ready' "on"

end program

```

| STIMULUS P | ROGRAM NAME: | READY_ | _2    |               | SIZE:         | 143 BYTES |

|------------|--------------|--------|-------|---------------|---------------|-----------|

|            |              |        | Resp  | onse Data     |               |           |

| Node       | Learned      |        | Async | : Clk Counter |               | Priority  |

| Signal Src | With         | SIG    | LVL   | LVL Mode      | Counter Range | Pin       |

|            |              |        |       |               |               |           |

| U4-6       | I/O MODULE   | 0000   | 1 0   | TRANS         |               |           |

| U4-8       | PROBE        | 007E   | 1 0   | TRANS         |               |           |

| U4-8       | I/O MODULE   | 007E   | 1 0   | TRANS         |               |           |

| U5-3       | I/O MODULE   | 0086   | 1 0   | TRANS         |               |           |

| U5-6       | I/O MODULE   | 0078   | 1 0   | TRANS         |               |           |

| U56-8      | PROBE        | 0086   | 1 0   | TRANS         |               |           |

| U56-8      | I/O MODULE   | 0086   | 1 0   | TRANS         |               |           |

| U6-8       | I/O MODULE   | 0078   | 1 0   | TRANS         |               |           |

Figure 4-133: Response File (ready\_2)

```

program ready_3

```

! Stimulus programs and response files are used by GFI to backtrace ! from a failing node. The stimulus program must create repeatable UUT ! activity and the response file contains the known-good responses for ! the outputs in the UUT that are stimulated by the stimulus program.

! This stimulus program is one of the programs which creates activity ! in the kernel area of the UUT. These programs create activity with ! or without the ready circuit working properly. Because of this, all ! the stimulus programs in the kernel area must disable the READY input ! to the pod, then perform the stimulus, then re-enable the READY input ! to the pod. The 80286 microprocessor has a separate bus controller; ! for this reason, disabling ready and performing stimulus can get the ! bus controller out of synchronization with the pod. Two fault ! handlers trap pod timeout conditions that indicate the bus controller ! is out of synchronization. The recover() program is executed to ! resynchronize the bus controller and the pod.

! TEST PROGRAMS CALLED:

recover ()

The 80286 microprocessor has all bus controller that is totally! separate from the pod. In some cases the pod can get out! of sync with the bus control-! ler. The recover program! resynchronizes the pod and the! bus controller.!

GRAPHICS PROGRAMS CALLED: (none)

! Global Variables Modified: ! recover times

Reset to Zero

Local Variables Modified: measure dev

stimulus dev

Measurement device Stimulus device (overdrives)

declare global numeric recover times

(continued on the next page)

Figure 4-134: Stimulus Program (ready\_3)

```

FAULT HANDLERS:

handle pod timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

handle pod timout no clk

end handle

Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine measurement device

if (gfi control) = "yes" then

measure_dev = gfi device

measure_ref = gfi ref

print "Enter reference name of part to measure:"

print " (Chose U1, U4, U5 or U6)"

measure ref = "" \ input measure ref

measure dev = clip ref measure ref

end if

! Determine stimulus device

if measure ref = "U1" then

print "\07\1B[2J\1B[201\1B[3;1f

USING \1B[7mSECOND\1B[0m CLIP."

stimulus dev = clip ref "U4"

print "\1B[20h"

else

stimulus dev = measure dev

print "Stimulus Program READY 3"

```

Figure 4-134: Stimulus Program (ready\_3) - continued

```

! Setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'standby function off'

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

io byte = getspace space "i/o", size "byte"

mem word = getspace space "memory", size "word"

reset device measure dev

reset device stimulus dev

sync device measure dev, mode "pod"

sync device "/pod", mode "data"

old cal = getoffset device measure dev

setoffset device measure dev, offset (1000000 - 56)

if measure ref = "U5" then

writepi\overline{n} device "U5", pin 2, level "1", mode "latch" writepin device "U5", pin 4, level "1", mode "latch"

else if measure_ref = "U4" or measure_ref = "U1" then

writepin device "U4", pin 11, level "1", mode "latch"

end if

! Stimulate ICs and capture response.

arm device measure dev

! Start response capture.

setspace (mem word)

read addr 0

! RAMO

read addr $10000

! RAM1

write addr $20000, data 0

! VRAM (write only)

readout device measure dev

! End response capture.

clearoutputs device stimulus dev

setoffset device measure dev, offset old cal

podsetup 'standby function on'

podsetup 'enable ~ready' "on"

end program

```

Figure 4-134: Stimulus Program (ready\_3) - continued

| STIMULUS P<br>DESCRIPTIC | ROGRAM NAME:<br>N:    | READY_ | .3                |                         | SIZE:         | 112 BYTES       |

|--------------------------|-----------------------|--------|-------------------|-------------------------|---------------|-----------------|

| Node<br>Signal Src       | Learned<br>With       | sig    | -                 | k Counter               | Counter Range | Priority<br>Pin |

| U4-6<br>U5-3<br>U6-8     | I/O MODULE I/O MODULE |        | 1 0<br>1 0<br>1 0 | TRANS<br>TRANS<br>TRANS | 3<br>3<br>3   |                 |

Figure 4-135: Response File (ready\_3)

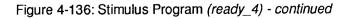

program ready\_4

! STIMULUS PROGRAM overdrives U4 in ready circuit. Characterizes U4-6 and U1-4. ! Stimulus programs and response files are used by GFI to backtrace ! from a failing node. The stimulus program must create repeatable UUT ! ! activity and the response file contains the known-good responses for ! the outputs in the UUT that are stimulated by the stimulus program. ! This stimulus program is one of the programs which creates activity ! in the kernel area of the UUT. These programs create activity with ! or without the ready circuit working properly. Because of this, all ! the stimulus programs in the kernel area must disable the READY input ! ! to the pod, then perform the stimulus, then re-enable the READY input ! ! to the pod. The 80286 microprocessor has a separate bus controller; ! for this reason, disabling ready and performing stimulus can get the ! bus controller out of synchronization with the pod. Two fault ! handlers trap pod timeout conditions that indicate the bus controller ! is out of synchronization. The recover() program is executed to ! resynchronize the bus controller and the pod. ! TEST PROGRAMS CALLED: The 80286 microprocessor has a! recover bus controller that is totally! separate from the pod. In some cases the pod can get out! of sync with the bus control-! ler. The recover program resynchronizes the pod and the! bus controller. ! GRAPHICS PROGRAMS CALLED: (none) ! Global Variables Modified: recover times 1 Reset to Zero Local Variables Modified: measure dev Measurement device stimulus dev Stimulus device (overdrives) ! Main Declarations

declare global numeric recover\_times

(continued on the next page)

Figure 4-136: Stimulus Program (ready\_4)

```

! FAULT HANDLERS:

handle pod timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

handle pod timout no clk

end handle

Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine measurement device

if (gfi control) = "yes" then

measure dev = gfi device

measure_ref = gfi ref

print "Enter reference name of part to measure:"

print " (Chose U4, U5 or U17)"

measure ref = "" \ input measure ref

measure dev = clip ref measure ref

end if

! Determine stimulus device

if measure ref = "U4" then

print "\07\1B[2J\1B[201\1B[3:1f

USING \1B[7mSECOND\1B[0m CLIP."

stimulus dev = clip ref "U45"

else if measure ref = "U5" then

print "\07\1\overline{B}[2J\1B[201\1B[3;1f

USING \1B[7mSECOND\1B[0m CLIP."

stimulus dev = clip ref "U17"

else if measure ref = "U17" then

print "\07\1B[2J\1B[201\1B[3;1f

USING \1B[7mSECOND\1B[0m CLIP."

stimulus dev = clip ref "U4"

end if

print "\1B[20h"

print "Stimulus Program READY 4"

```

Figure 4-136: Stimulus Program (ready\_4) - continued

```

The state of the s

```

```

! Setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

reset device measure dev

reset device stimulus dev

sync device measure dev, mode "int"

sync device stimulus_dev, mode "int"

if measure ref = "U4" then

storepatt device "U4", pin 12, patt "10111"

storepatt device "U4", pin 13, patt "11101"

storepatt device "U45", pin 6, patt "00000"

storepatt device "U45", pin 3, patt "00000" else if measure_ref = "U5" then

storepatt device "U5", pin 1,

patt "11111"

storepatt device "U17", pin 9, patt "10101"

else if measure ref = "U17" then

storepatt device "U4", pin 12, patt "10111"

storepatt device "U4", pin 13, patt "11101"

! Provide stimulus to UUT using I/O module to overdrive.

arm device measure dev

if measure ref = "U4" then

writepatt device "U45,U4", mode "pulse"

else if measure ref = "U5" then

writepatt device "U17, U5", mode "pulse"

else if measure_ref = "U17" then

writepatt device "U4", mode "pulse"

end if

readout device measure_dev

podsetup 'enable ~ready' "on"

end program

```

| DESCRIPTIO         | ROGRAM NAME:<br>ON:      | READY_       | _4         |                                     | SIZE:         | 78 BYTES        |

|--------------------|--------------------------|--------------|------------|-------------------------------------|---------------|-----------------|

| Node<br>Signal Src | Learned<br>With          | sig          | Async      | nse Data<br>Clk Counter<br>LVL Mode | Counter Range | Priority<br>Pin |

| U4-11<br>U5-3      | I/O MODULE<br>I/O MODULE | 0015<br>000A | 1 0<br>1 0 | TRANS<br>TRANS                      |               |                 |

Figure 4-137: Response File (ready\_4)

```

program ready 5

! STIMULUS PROGRAM characterizes the ready circuit.

! Stimulus programs and response files are used by GFI to backtrace

! from a failing node. The stimulus program must create repeatable UUT

activity and the response file contains the known-good responses for

! the outputs in the UUT that are stimulated by the stimulus program.

! This stimulus program is one of the programs which creates activity

! in the kernel area of the UUT. These programs create activity with

! or without the ready circuit working properly. Because of this, all

! the stimulus programs in the kernel area must disable the READY input

! to the pod, then perform the stimulus, then re-enable the READY input !

! to the pod. The 80286 microprocessor has a separate bus controller;

! for this reason, disabling ready and performing stimulus can get the

! bus controller out of synchronization with the pod. Two fault

! handlers trap pod timeout conditions that indicate the bus controller !

! is out of synchronization. The recover() program is executed to

! resynchronize the bus controller and the pod.

! TEST PROGRAMS CALLED:

The 80286 microprocessor has a!

recover

()

bus controller that is totally!

separate from the pod. In

some cases the pod can get out!

of sync with the bus control- !

ler. The recover program

resynchronizes the pod and the!

bus controller.

check meas (device, start, stop, clock, enable)

Checks to see if the measure-

ment is complete using the

TL/1 checkstatus command. If !

the measurement times out then!

redisplay connect locations.

! GRAPHICS PROGRAMS CALLED:

(none)

! Local Variables Modified:

returned from check meas ()

ţ

done

1

! Global Variables Modified:

Reset to Zero

recover times

! Local Variables Modified:

```

Measurement device

Stimulus device (overdrives)

Figure 4-138: Stimulus Program (ready\_5)

measure dev

stimulus dev

```

! Main Declarations

declare global numeric recover times

declare numeric done = 0

! FAULT HANDLERS:

handle pod timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

! Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine the measurement device.

if (gfi control) = "yes" then

measure dev = ofi device

measure ref = qfi ref

print "Enter reference name of part to measure:"

(Chose U5 or U17)"

measure ref = "" \ input measure ref

measure_dev = clip ref measure_ref

print "Stimulus Program READY 5"

! Set addressing mode and setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'standby function off'

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

setspace ( getspace ( "i/o", "byte" ))

reset device measure dev

sync device measure dev, mode "ext"

enable device measure dev, mode "high"

edge device measure dev, start "+", stop "count", clock "-"

stopcount device measure dev, count 7

```

Figure 4-138: Stimulus Program (ready\_5) - continued

```

! Prompt user to connect external lines.

if measure ref = "U17" then

connect device measure dev, start "U4-11", clock "U1-10", common "gnd"

connect device measure dev, start "U17-9", clock "U1-10", common "gnd"

end if

! External lines determine measurement.

loop until done = 1

arm device measure dev

read addr 0

done = check meas(measure_dev,"U4-11", "*", "U1-10", "*")

readout device measure dev

end loop

clearoutputs device measure dev

podsetup 'standby function on'

podsetup 'enable ~ready' "on"

end program

```

Figure 4-138: Stimulus Program (ready\_5) - continued

| STIMULUS P<br>DESCRIPTIC | ROGRAM NAME:    | READY_5 |     |         | SIZE:   | 69 BYTES        |

|--------------------------|-----------------|---------|-----|---------|---------|-----------------|

| Node<br>Signal Src       | Learned<br>With | A       | -   | Counter | Counter | Priority<br>Pin |

| U17-11                   | I/O MODULE      |         | 1 0 | TRANS   | 1       |                 |

Figure 4-139: Response File (ready\_5)

program ready 6

! STIMULUS PROGRAM to wiggle all address lines from the uP.

! Stimulus programs and response files are used by GFI to backtrace ! from a failing node. The stimulus program must create repeatable UUT ! ! activity and the response file contains the known-good responses for ! the outputs in the UUT that are stimulated by the stimulus program.

! This stimulus program is one of the programs which creates activity ! in the kernel area of the UUT. These programs create activity with ! or without the ready circuit working properly. Because of this, all ! the stimulus programs in the kernel area must disable the READY input ! to the pod, then perform the stimulus, then re-enable the READY input ! to the pod. The 80286 microprocessor has a separate bus controller; ! for this reason, disabling ready and performing stimulus can get the ! bus controller out of synchronization with the pod. Two fault ! handlers trap pod timeout conditions that indicate the bus controller ! is out of synchronization. The recover() program is executed to ! resynchronize the bus controller and the pod.

! TEST PROGRAMS CALLED: recover

()

The 80286 microprocessor has a! bus controller that is totally! separate from the pod. In some cases the pod can get out! of sync with the bus control- ! ler. The recover program resynchronizes the pod and the! bus controller.

GRAPHICS PROGRAMS CALLED:

(none)

! Global Variables Modified:

recover\_times

Reset to Zero

! Local Variables Modified:

measure dev Measurement device

stimulus dev Stimulus device (overdrives)

(continued on the next page)

Figure 4-140: Stimulus Program (ready\_6)

```

! Main Declarations

declare global numeric recover times

declare numeric done = 0

! FAULT HANDLERS:

handle pod timeout enabled line

recover()

end handle

handle pod timeout recovered

recover()

end handle

! Main part of STIMULUS PROGRAM

recover times = 0

! Let GFI determine the measurement device.

if (qfi control) = "yes" then

measure dev = qfi device

measure ref = gfi ref

print "Enter reference name of part to measure:"

print " (Chose U5 or U17)"

measure ref = "" \ input measure ref

measure dev = clip ref measure ref

end if

print "Stimulus Program READY 6"

! Set addressing mode and setup measurement device.

podsetup 'enable ~ready' "off"

podsetup 'standby function off'

podsetup 'report power' "off"

podsetup 'report forcing' "off"

podsetup 'report intr' "off"

podsetup 'report address' "off"

podsetup 'report data' "off"

podsetup 'report control' "off"

setspace( getspace( "i/o", "byte" ))

reset device measure dev

sync device measure dev, mode "ext"

enable device measure_dev, mode "high"

edge device measure_dev, start "+", stop "count", clock "-"

stopcount device measure dev, count 4

```

Figure 4-140: Stimulus Program (ready\_6) - continued

```

! Prompt user to connect external lines.

if measure ref = "U17" then

connect device measure dev, start "U4-11", clock "U1-10", common "gnd"

connect device measure dev, start "U17-9", clock "U1-10", common "gnd"

end if

! External lines determine measurement.

loop until done = 1

arm device measure dev

read addr 0

done = check meas (measure dev, "U4-11", "*", "U1-10", "*")

readout device measure dev

end loop

clearoutputs device measure_dev

podsetup 'standby function on'

podsetup 'enable ~ready' "on"

end program

```

Figure 4-140: Stimulus Program (ready\_6) - continued

| STIMULUS P<br>DESCRIPTIO | ROGRAM NAME:<br>N: | READY_ | 6   |   |         | SIZE:     | 70 BYTES        |

|--------------------------|--------------------|--------|-----|---|---------|-----------|-----------------|

| Node<br>Signal Src       | Learned<br>With    | sig    |     |   | Counter | Counter F | Priority<br>Pin |

| U17-11                   | I/O MODULE         |        | 1 0 | 0 | TRANS   | 0         |                 |

Figure 4-141: Response File (ready\_6)

# Summary of Complete Solution for Ready Circuit

4.14.8.

The entire set of programs and files needed to test and GFI troubleshoot the Ready Circuit functional block is shown below. The format below is similar to a 9100A/9105A UUT directory (you could consider the functional block to be a small UUT), but in addition shows the use of each program and the location in this manual for each file.

## UUT DIRECTORY (Complete File Set for Ready Circuit)

#### Programs (PROGRAM):

| TST_READY | Functional Test  | Section 4.14.5 |

|-----------|------------------|----------------|

| READY_1   | Stimulus Program | Figure 4-130   |

| READY_2   | Stimulus Program | Figure 4-132   |

| READY_3   | Stimulus Program | Figure 4-134   |

| READY_4   | Stimulus Program | Figure 4-136   |

| READY_5   | Stimulus Program | Figure 4-138   |

| READY_6   | Stimulus Program | Figure 4-140   |

#### Stimulus Program Responses (RESPONSE):

| READY_1 | Figure 4-131 |

|---------|--------------|

| READY_2 | Figure 4-133 |

| READY_3 | Figure 4-135 |

| READY_4 | Figure 4-137 |

| READY_5 | Figure 4-139 |

| READY_6 | Figure 4-141 |

Node List (NODE):

NODELIST Appendix B

Text Files (TEXT):

Reference Designator List (REF):

REFLIST Appendix A

Compiled Database (DATABASE):

GFIDATA Compiled by the 9100A

#### OTHER FUNCTIONAL BLOCKS AND CIRCUITS

4.15.

The 9100A/9105A provides the capability to handle a number of special circuits or situations. Among these are watchdog timers forcing lines, feedback loops, and in-circuit component testing.

#### **Watchdog Timers**

4.15.1.

Watchdog timers usually interfere with testing and troubleshooting. If your UUT has a watchdog timer, your test procedure or program must disable it before performing tests.

Many watchdog timers initiate a master reset when they detect incorrect activity. Others may use a high-priority interrupt line to reset the system.

Whenever possible, physically disable the watchdog timer with a jumper or switch provided for that purpose. If the watchdog timer cannot be disabled at the UUT, the 9100A/9105A may be able to ignore it with the SETUP POD REPORT FORCING SIGNAL ACTIVE OFF keypad command, or disable it with a command like SETUP POD ENABLE READY ON/OFF. Be very careful, however, when doing this. Read the precautions about these commands in Section 4.15.2, "Forcing Lines."

#### **Forcing Lines**

4.15.2.

In some situations, forcing lines must be disabled (disconnected from the pod microprocessor) during a test. You can do this with the SETUP POD ENABLE READY ON/OFF keypad command ("READY" is a pod-dependent choice; some pods may call this line by a different name).

Exercise care whenever you disable a forcing line. Write or read commands to circuits that generate wait states through a Ready line may become unpredictable after the Ready line is disabled at the pod.

In addition to disabling forcing lines, you can also ignore them. The SETUP POD REPORT FORCING SIGNAL ACTIVE OFF keypad command will prevent the reporting of forcing lines. In this mode, the pod behaves normally but forcing conditions are not reported by the pod to the 9100A/9105A.

Exercise care with this mode also. The pod's hardware performance is not affected and the pod will continue reacting to the forcing line. If the UUT generates a permanent wait state using a forcing line, the pod will halt and the system will display a timeout message. Other fault-indicating signals on your UUT will also be ignored if the forcing line is disabled. Be sure that your UUT hardware is not affected by the same forcing line.

#### **Breaking Feedback Loops**

4.15.3.

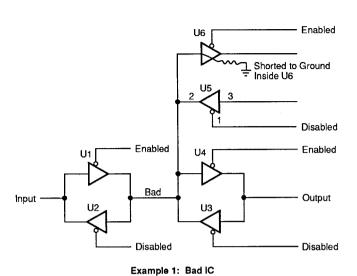

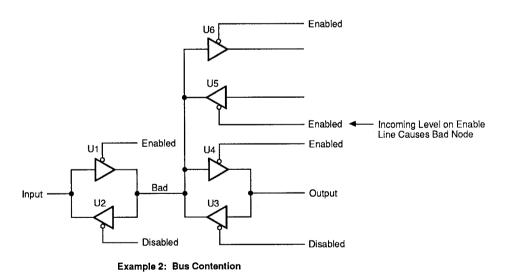

Microprocessor-based systems often have several feedback loops. The microprocessor and the components tied to the data and address buses form a large feedback loop. Most of the loops in the system will be broken when the microprocessor is replaced by the pod, because the pod can selectively ignore or report conditions of status and forcing lines. However, there may be additional loops which are not broken by the pod.

Figure 4-125 shows a feedback loop in the Ready functional block of the Demo/Trainer UUT. The READY output (U1-4) is fed back as an input at U4-12.

To test a functional block that contains a feedback loop, drive all of its inputs, including the inputs connected to outputs that form the feedback loop, and measure the outputs. Use the I/O module to overdrive inputs while measuring signature, level, and count at the outputs.

#### **Visual and Acoustic Interfaces**

4.15.4.

Some circuits, such as LEDs and beepers, have both electrical characteristics and visual or acoustic characteristics. In general, stimulus programs should ignore the visual or acoustic

characteristics and measure only the electrical characteristics. The functional tests should prompt the test operator to verify the visual or acoustical characteristics.

If the functional test fails, use the *gfi test* command. If *gfi test* fails, start GFI troubleshooting. If the functional test fails and *gfi test* passes, the part is bad, since the part operates incorrectly but the electrical signals at the part are good.

In the case of the Parallel I/O functional block on the Demo/Trainer UUT, the functional test includes a prompt to the operator to verify the correct display on the LEDs. If the LEDs fail, the Parallel I/O functional test should perform a gfi test, which will run the stimulus programs and check the electrical properties. If gfi test passes (when the Parallel I/O functional test failed), it means that the electrical characteristics are good but the display is bad. The LEDs are bad and the operator should be prompted to replace them. If the gfi test fails, GFI troubleshooting can begin at the pin where the gfi test failed.

#### **In-Circuit Component Tests**

4.15.5.

If you wish, you can write TL/1 programs to test individual components rather than using the GFI to do so. These in-circuit component tests use a sequence of ones and zeroes defined with the TL/1 storepatt command and executed by the TL/1 writepatt command to overdrive the inputs of the component to be tested while measuring the signatures or level histories of its outputs. A test operator runs these tests by using the EXEC key to run the required program.

### Other Functional Blocks and Circuits

(This page is intentionally blank.)

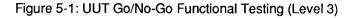

# Section 5 UUT Go/No-Go Functional Tests

# PROGRAMMED GO/NO-GO FUNCTIONAL TESTING

5.1.

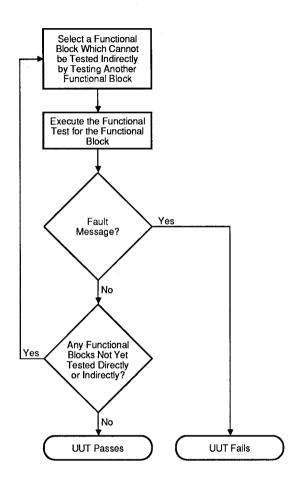

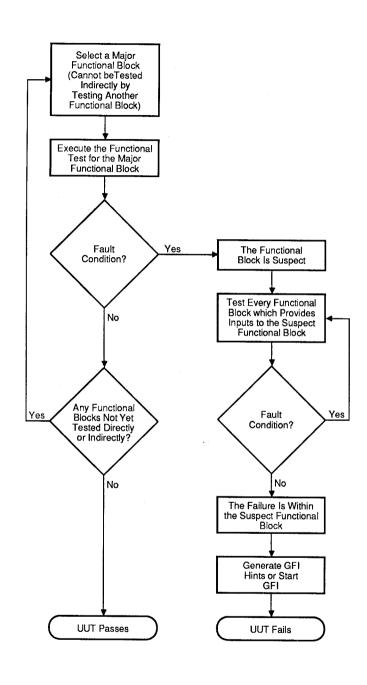

The UUT go/no-go test is the third of four modular levels in programming the 9100A, as shown in Figure 5-1. In this third level, the go/no-go test determines whether the UUT is good (passes) or bad (fails). The go/no-go test combines built-in functional test commands with functional tests designed by the programmer.

The go/no-go test is simple because it builds on the tests of functional blocks. It determines only whether the entire UUT is good or bad. It does not determine which functional block is causing a failure.

# CREATING A PROGRAMMED GO/NO-GO FUNCTIONAL TEST

5.2.

Suppose a UUT has 14 functional blocks and a functional test is defined for each of them. One way to create a go/no-go test is to perform all 14 functional tests. Some blocks, however, can be tested indirectly by testing other blocks. For example, the bus buffer is assumed to be good if the ROM, RAM, and other blocks pass their tests. Therefore, a second way to create the go/no-go test is to perform functional tests only on functional blocks which cannot be tested indirectly by testing other blocks.

#### Level 1

- Stimulus Programs for Nodes

- Learned Node Responses from Known-Good UUT

- Node List and Reference Designator List (Both Optional)

#### Level 2

Functional Tests of Entire Functional Blocks

#### Level 3

Go/No-Go Test for the Entire UUT

#### Level 4

Go/No-Go Test for the Entire UUT, with Fault Isolation to the Block Level

Figure 5-2 shows the steps used to reach a go/no-go status decision. Care must be taken to ensure that your go/no-go test really does test the UUT for all possible faults.

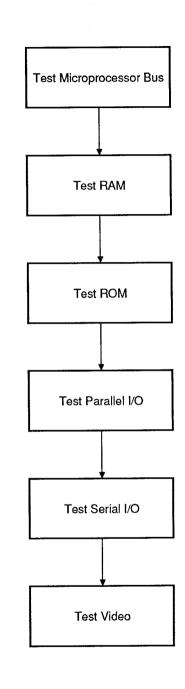

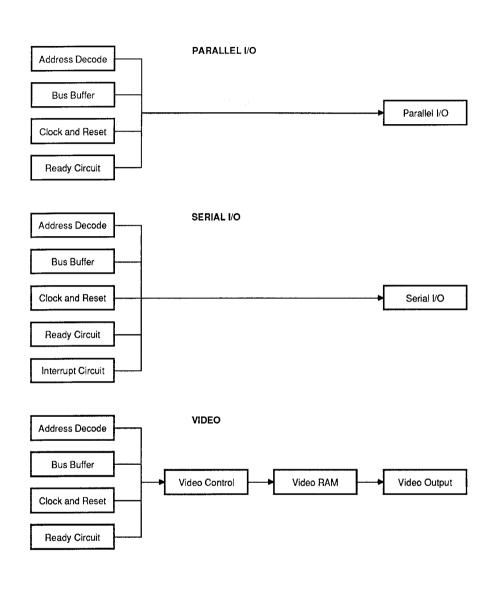

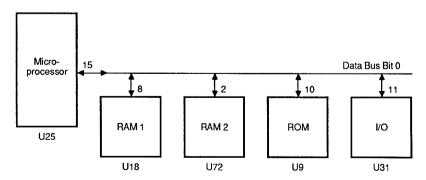

Figure 5-3 shows the structure of a go/no-go functional test for the Demo/Trainer UUT. For this UUT, only six functional blocks need to be tested for the go/no-go functional test of the UUT: Microprocessor Bus, RAM, ROM, Parallel I/O, Serial I/O, and Video. The microprocessor bus test is run first because it is built-in, fast, and provides excellent diagnostic information. A failure on the microprocessor bus will cause most other circuits to fail, so it is most efficient to check this functional block first.

In the Demo/Trainer UUT, the following functional blocks are tested indirectly by the go/no-go test:

Clock and Reset Ready Circuit Interrupt Circuit Bus Buffer Dynamic RAM Timing Address Decode Video Control Video RAM

Figure 5-4 is a listing of the go/no-go functional test program for the Demo/Trainer UUT. It calls the functional test for each of the functional blocks which must be tested directly for the UUT go/no-go functional test to be complete. The remaining functional blocks are tested indirectly; if they fail, one of the six blocks that is tested by the go/no-go test will fail also.

#### **EVALUATING TEST EFFECTIVENESS**

5.3.

The purpose of the go/no-go test is to determine whether the UUT is good or bad. Two measures are frequently used to evaluate how well a go/no-go functional test performs: node activity and fault coverage. Node activity is important because

Figure 5-2: Go/No-Go Test Sequence

Figure 5-3: Demo/Trainer UUT Go/No-Go Test

```

program go nogo

```

```

! The Go/No-Go program is the highest level of the functional testing

! and fault handlers. The purpose of the Go/No-Go test is to determine !

! whether the UUT is good or bad. This program executes six programs !

! which test the six major functional blocks (Microprocessor Bus, ROM,

! RAM, Parallel I/O, Serial I/O, and Video functional blocks).

! By testing the six major functional blocks, the remaining

! functional blocks are indirectly tested.

! TEST PROGRAMS CALLED:

test bus

Test the microprocessor bus,

buffered bus, and address

1

select logic.

test rom

Test the ROM functional block !

of the Demo/Trainer UUT.

test ram

Test the RAM functional block !

of the Demo/Trainer UUT.

test pia

Test the PARALLEL I/O

functional block of the

Demo/Trainer UUT.

test rs232 ()

Test the SERIAL I/O

functional block and the

Interrupt Circuit functional !

block of the Demo/Trainer UUT.!

test video ()

Test the VIDEO circuit of the !

Demo/Trainer UUT.

! SETUP AND SYSTEM INITIALIZATION !

podsetup 'report power' "on"

! Turn on reporting functions except

podsetup 'report intr' "off"

! interrupt which is tested in the

podsetup 'report address' "on"

! SERIAL I/O test (test rs232).

podsetup 'report control' "on"

podsetup 'report data' "on"

podsetup 'report forcing' "on"

! This is the go/no-go test which runs the major functional tests. !

gfi clear

! CLEAR ALL GFI RECOMMENDATIONS

connect clear "yes"

! Clear all connect information.

execute test bus()

execute test rom()

execute test ram()

execute test_pia()

execute test_rs232()

execute test video()

end program

```

Figure 5-4: Go/No-Go Test for Demo/Trainer UUT

each node on the UUT must be exercised for a thorough functional test.

However, activity on each node is not a sufficient evaluation of test effectiveness. In addition, you need to evaluate how well your test detects faults in the UUT. This is done by injecting faults (such as stuck lows, stuck highs, intermittent highs, or intermittent lows) at each node in the UUT while running your functional test to see if the test fails. The 9100A/9105A probe (used as a source) provides a convenient tool for this purpose.

Fault coverage is the percentage of faults that will be detected by the functional test software. It is often measured as the ratio of the number of nodes where injected faults can be detected by a test to the total number of nodes in the UUT. This ratio is usually expressed in percent. If the fault coverage is not high, you can analyze the pattern of faults that are not detected to determine additions to your test program to increase the fault coverage.

#### **EXECUTING UUT SELF-TESTS**

5.4.

Self-test routines contained in UUT memory can be executed from the 9100A/9105A by pressing the RUN UUT key at the operator's keypad and entering the UUT's starting address of the routine. These self-test routines can also be run from TL/1 programs by using the *runuut* command. Self-test routines typically save their test results in UUT RAM. The 9100A/9105A can later read the appropriate RAM addresses to get these results.

An I/O module can generate one hardware breakpoint (system interrupt) upon detection of any user-defined combination of logic-highs and logic-lows on selected I/O module lines. This feature may be invoked at the operator's keypad (SET I/O MOD COMPARE WORD command), or through program execution. Once set up for a breakpoint, the I/O module continuously monitors the specified lines while other functions (such as RUN UUT) are performed. When the breakpoint event occurs, RUN UUT execution halts. A breakpoint message will interrupt any

A complete functional test for a UUT might begin with the BUS, RAM, and ROM tests, followed by execution of UUT self-test routines. By using RUN UUT breakpoints to detect addresses, data, and other UUT logic levels, the program can integrate the UUT's self-tests with 9100A/9105A functional tests.

Some pods can also generate UUT breakpoints without using the I/O module. For these pods, breakpoint-related softkeys appear when the RUN UUT key is pressed. Consult your pod manual for these pod-specific breakpoint capabilities, if any.

#### EXECUTING DOWNLOADED MACHINE CODE

5.5.

After part of the UUT RAM has been tested and found to be good, machine code can be downloaded to the tested RAM and executed. The machine code may be downloaded using a series of WRITE commands or the WRITE BLOCK command, which downloads an entire Motorola-format user file.

After the code is downloaded, you can execute it with the RUN UUT command, specifying the code's starting address. Although most testing can be done efficiently through the TL/1 test language, downloading machine code is useful when the code for a test already exists, when the testing must be done at machine-code speeds, or when a feature not supported by the pod must be used as part of the test.

The pod's microprocessor bus cycles are actually done at full UUT speed. The 9100A/9105A, however, is often slower than the UUT. For example, when the system performs a looping READ, each bus cycle is at full UUT speed but individual read operations are not done one immediately after the other.

# Section 6 Identifying a Faulty Functional Block

After the go/no-go test determines that a UUT is faulty, the next step is to identify the failing functional block. Doing so before starting to troubleshoot will greatly improve troubleshooting efficiency because troubleshooting can begin *closer to the failure* and will take less time to reach the failing node. In addition, fault detection will be more accurate because the diagnostic test can check for special types of faults, such as bus contention, before troubleshooting begins.

Programs that identify faulty functional blocks are called diagnostic programs. Diagnostic programs, which are a subset of troubleshooting procedures, build on the UUT go/no-go test, functional tests of blocks, and stimulus programs. They are the last of the four modular levels in programming the 9100A, as shown in Figure 6-1. In this fourth programming level, fault condition handlers and *gfi hint* commands are added to the UUT go/no-go test to create a diagnostic program that traps faults and initiates tests of functional blocks that may be responsible for the fault, thereby isolating the block that is causing the UUT to fail. In addition, a failing output of the faulty block is identified as a starting point for backtracing toward the fault that causes the block to fail. At that point, GFI troubleshooting (the GFI key on the operator's keypad) can be used to backtrace to the bad node or component.

# Level 1 - Stimulus Programs for Nodes - Learned Node Responses from Known-Good UUT - Node List and Reference Designator List (Both Optional) Level 2 Functional Tests of Entire Functional Blocks Level 3 Go/No-Go Test for the Entire UUT Level 4 Go/No-Go Test for the Entire UUT, with Fault Isolation to the Block Level

Figure 6-1: Diagnostic Programs (Level 4)

#### STRATEGY OF DIAGNOSTIC PROGRAMS

The first step in developing a diagnostic strategy is to draw a diagram showing the major functional blocks used in the go/no-go functional test. Next, show all other functional blocks that provide input to these major functional blocks. Figure 6-2 shows such a diagram for the Demo/Trainer UUT. The figure shows six sets of functional blocks, one for each major functional block tested by the go/no-go functional test. The blocks on the left provide input to the blocks on the right, and the blocks tested by the go/no-go functional test are on the right side of each set.

The task of the diagnostic program is to select a failing functional block for troubleshooting and to generate an appropriate starting point (or points) where GFI can begin automated troubleshooting. When a major functional block fails, you know that one or more outputs of the block are bad. But it doesn't necessarily mean that the block itself is bad; bad inputs to the major functional block may be causing the block to fail. How do you continue from there to isolate the failing block and select an efficient starting point for GFI?

One diagnostic strategy is to test blocks that provide input to the failing major block. Isolating the block causing a failure involves tracing from the right-hand side toward the left, testing each block in the path until one is found with good inputs and bad outputs. This strategy works best when the string of blocks leading up to a major block is short. Such is the case for most of the sets of blocks in Figure 6-2.

A second diagnostic strategy, helpful when you have a longer string of blocks leading up to a failing major block, is to divide the blocks in half and begin testing a block halfway between the first block in the string and the major block at the end. If the middle block passes, keep dividing the failing string of blocks in half and testing a middle block. If the middle block fails, test the blocks to the left starting at the middle block. This second strategy would be appropriate for the Video set of blocks in Figure 6-2.

(continued on the next page)

Figure 6-2: Inputs to Functional Blocks

Figure 6-2: Inputs to Functional Blocks- continued

Another strategy, used when a fault is likely to be near a failing output pin of the failing major block, is to begin GFI backtracing directly from the failing output pin, without checking the inputs to the major functional block.

Diagnostic programs can speed up troubleshooting by starting GFI closer to the actual problem. On the other hand, isolating the failure to a very small area may require more time than is saved in reduced troubleshooting time. There is a balance between isolating the failure to a very small area and doing no isolation of the failing circuit. Decisions on when to start GFI and when to isolate the failure to a smaller area depend on your UUT and the relative cost of additional programming effort compared to the resulting savings in troubleshooting time.

# IMPLEMENTING THE STRATEGY FOR DIAGNOSTIC PROGRAMS

6.2.

Figure 6-3 shows a typical process to implement a diagnostic program strategy. The diagnostic program executes a functional test for each major functional block. If a fault condition is generated during the test, the major functional block is possibly faulty. To verify this suspicion, the inputs to the functional block are checked. If the inputs are all good, then the major functional block is indeed faulty. However, if one of the inputs to a major functional block is not good, the fault probably lies in the functional blocks which provide input to the major functional block. In this case, the input functional blocks become the suspect blocks and their inputs are checked. This process continues until a block is found with all good inputs but a bad output.

When this faulty functional block is identified, appropriate GFI hints are generated to indicate the node (or nodes) where GFI should start troubleshooting.

Figure 6-3: Identifying a Faulty Functional Block

# DIAGNOSIS USING FAULT CONDITION HANDLERS

6.3.

Fault condition handlers provide the means for communicating 9100A/9105A functional test failure information to the operator for keystroke troubleshooting or to GFI for automated troubleshooting.

#### What are Fault Condition Handlers?

6.3.1.

A fault condition is generated or "raised" in one of two ways:

- A built-in TL/1 function is run, and the UUT does not respond correctly. For example, a microprocessor address line cannot be driven to logic-high during a read or write operation.

- A fault command is executed in a TL/1 program.

A fault condition handler is a TL/1 procedure, called by a fault condition of the same name, that responds in some way to the fault condition. For example, the handler might try to determine the cause of the fault.

Each fault condition has a name. Fault conditions created by built-in functions have defined names and parameters, listed in *TL/1 Reference Manual* appendices. Fault conditions created by your *fault* commands may have any name, including the same name used by the built-in functions.

When a fault condition is raised, the system halts execution of the current program. If your program contains a fault condition handler with the same name as the fault condition, the program statements inside the handler are executed. After the handler is finished, execution of your program resumes where it left off.

If your program does not contain an appropriate fault condition handler, execution of the program terminates and its calling program (if any) is searched for a fault condition handler with

the specified fault condition name. This process continues until an appropriate handler is found. If no handler is found, a fault message will appear on the operator's display.

For more information on fault condition handlers, see Section 3.7 of the *Programmer's Manual*.

#### **Using Fault Condition Handlers**

6.3.2.

The UUT go/no-go test should test only those functional blocks that cannot be tested indirectly by other blocks. When the go/no-go test detects a failure, the diagnostic program is used to identify the failing block and to identify a failing node as a starting point for troubleshooting.

To use fault condition handlers in a diagnostic program, you need to do two programming tasks for each handler:

- 1. Use the fault command (with an appropriate fault condition that you create) to generate the fault condition if a test (or part of a test) of a functional block fails. For example, if the diagnostic program finds that the functional test of the video output circuitry fails, you might choose to generate a fault condition named video\_output.

- 2. Create a handler for this fault condition. The handler should check other input blocks to isolate the failing functional block. It might also do further testing to narrow down the zone of failure within a failing functional block. And the handler will generate the appropriate starting point for GFI by using the *gfi hint* command.

#### A Diagnostic Test Example

6.3.3.

Suppose the video circuitry is failing. Testing begins with execution of the go/no-go2 program, listed in Section 6.4 of this manual. This program has many fault condition handlers at the

beginning, and it has six execute statements at the end that actually execute the go/no-go test. Each of these execute statements executes a different functional test program for a major functional block. And each of these functional test programs include the necessary fault condition handlers to generate GFI hints appropriate for the fault condition encountered (a listing for each of these programs is contained in Section 6.5 of this manual). The GFI hints are very important to the troubleshooting process; they are the means by which the 9100A/9105A communicates the results of its functional testing to provide efficient starting points for GFI troubleshooting.

Suppose that the failing video circuitry does not affect any of the six major functional blocks except <code>test\_video2</code>. In this case, <code>test\_bus2</code>, <code>test\_rom2</code>, <code>test\_ram2</code>, <code>test\_pia2</code>, and <code>test\_rs232b</code> all pass, but <code>test\_video2</code> fails. The <code>test\_video2</code> test is really the test of the Video Output functional block. If this test fails, a video fault condition is generated (suppose the <code>video\_scan</code> fault condition is generated). Since the <code>test\_video2</code> program has a handler for <code>video\_scan</code>, the program statements inside this handler are executed.

Once the hints to GFI are passed, execution of the video fault condition handler (video\_scan) ends, the test program (test\_video2) ends, and the diagnostic program (go\_nogo2) ends. A message appears on the operator's display saying that GFI hints have been generated, and that GFI should be run.

The diagnostic program is structured so that only one failure is isolated at a time. The problem should be isolated with GFI and fixed when it is detected. It is appropriate to repair an isolated fault before testing any further, since apparent multiple failures often result from one physical problem on a board. For example, a short between two nodes can appear as two failures. After a fault has been repaired, the diagnostic program should be run again to find other faults or to verify that no more faults can be found.

#### 6.4.

# DIAGNOSTIC PROGRAM FOR THE DEMO/TRAINER UUT

program go nogo2

! If the Go/No-go test detects a faulty UUT, further fault isolation is ! performed to isolate which circuit is causing the failure. The fault ! condition handlers in the Go/No-go program and the other functional ! test programs perform the fault isolation. The fault condition ! handlers included in this program are handlers for those fault ! conditions which may occur during any of the six major functional ! tests.

! The major functional test programs include fault condition handlers ! for fault conditions which are only generated within that program. ! The first three programs (TEST\_BOS, TEST\_ROM, and TEST\_RAM) use ! built-in TL/1 tests and the built-in fault condition handlers that ! are documented in the 9100/9105A TL/1 Reference Manual.

TEST PROGRAMS CALLED:

test bus2

Test the microprocessor bus, buffered bus, and address select logic.

test rom2

Test the ROM functional block ! of the Demo/Trainer UUT.

test\_ram2

Test the RAM functional block of the Demo/Trainer UUT.

test pia2

Test the PARALLEL I/O functional block of the Demo/Trainer UUT.

test rs232b

Test the SERIAL I/O functional! block and the Interrupt ! Circuit functional block of ! the Demo/Trainer UUT.

test\_video2

Test the VIDEO circuit of the !

Demo/Trainer UUT.

recover

The 80286 microprocessor has at bus controller that is totally! separate from the pod. In ! some cases, the pod can get! out of sync with the bus ! controller. The recover ! program resynchronizes the pod! and the bus controller. !!

```

! FUNCTIONS CALLED:

retry_access (access, addr, control) This function is executed when!

1

a pod timeout recovered fault !

t

condition occurs. This

function repeats the attempted!

access that failed and

t

determines if the access can

t

be sucessfully repeated.

! Global Variables Modified:

Reset to Zero

recover times

! Main Declarations

global numeric recover times

! Count of executing recover().

end declare

! GENERAL PURPOSE FAULT CONDITION HANDLERS

! The built-in fault conditions "pod addr tied", "pod ctl tied",

! "pod data_incorrect" and pod_data_tied are generated when the pod

! detects a stuck or tied line at the pod socket. These fault

! conditions are not handled because the diagnostic message for these !

! faults cannot be made better by additional testing. If one of these !

! fault conditions occurs, the built-in fault message will be displayed!

! and the UUT needs to be repaired.

handle pod forcing active (mask)

declare string mask

declare global numeric tlo

declare string clear screen = "\1B[2J"

print on tlo ,clear screen, "POD Forcing Lines Active fault"

fault forcing_lines mask mask

! Redirect fault

end handle

handle pod interrupt active (mask)

declare string mask

declare global numeric tlo

declare string clear_screen = "\1B[2J"

print on tlo ,clear screen, "POD Interrupt Line Active fault"

! Get the last two characters of the 64 bit string mask and decode to INTR/NMI

lines = val (mid (mask, len (mask) - 3, 2), 16)

if (lines and $10) <> 0 then

execute tst intrpt()

else if (lines and 1) <> 0 then

fault NMI active

end if

end handle

handle pod misc fault

! Redirect fault

fault bad power

end handle

```

```

handle pod_special

end handle

handle pod timeout bad pwr

declare global numeric tlo

declare string clear screen = "\1B(2J"

print on tlo ,clear screen, "POD timeout bad power fault"

fault bad power

end handle

handle pod timeout enabled line (mask)

declare string mask

declare global numeric tlo

declare string clear screen = "\lB[2J"

print on tlo ,clear screen, "POD Timeout Enabled line fault"

fault forcing_lines mask mask

! Redirect fault

end handle

handle pod timeout no clk

declare global numeric tlo

declare string clear screen = "\1B[2J"

print on tlo ,clear screen, "POD Timeout No Clock at POD Pin 31"

execute tst clock()

! Test Clock and Reset

end handle

handle pod timeout recovered (access attempted, ctl, addr)

declare string access attempted

declare numeric ctl = $E0000000

declare numeric addr = $E0000000

declare global numeric t1o

declare string clear screen = "\1B[2J"

declare global numeric repeated timeouts

print on tlo ,clear_screen, "pod timeout recovered: "

podsetup 'enable ~ready' "off"

podsetup 'enable hold' "off"

podsetup 'report forcing' "off"

repeated_timeouts = repeated_timeouts + 1

! DISABLE all lines that can be enabled, retry access, then turn enable

! lines on until the access cannot be repeated. The lines that can be

! enabled on the 80286 are Hold and Ready.

if repeated timeouts > 10 then

fault dead kernel

else if retry_access(access_attempted, ctl, addr) fails then

fault dead_kernel

else

podsetup 'enable hold' "on"

if retry access (access attempted, ctl, addr) fails then

fault hold_circuit

podsetup 'enable ~ready' "on"

if retry access (access attempted, ctl, addr) fails then

execute tst decode()

execute tst ready()

print on tlo ,clear_screen

end if

end if

end if

end handle

```

```

handle pod timeout setup

end handle

handle pod uut power

fault bad power

! Redirect fault

end handle

handle iomod dce

end handle

! Redirected Fault Handlers !

handle forcing lines (mask)

declare string mask

declare global numeric recover times

! attempt to recover synchronization between pod and bus controller before

! testing the decode, ready or clock circuits. If the recover procedure

! has been executed at least twice, then go ahead and test decode, ready or

! the clock circuit.

if recover times < 2 then

execute recover()

6156

lines = val (mid (mask, len (mask) - 7, 8), 16)

if (lines and 1) <> 0 then

execute tst decode()

execute tst ready()

else if (lines and $10) <> 0 then

execute tst clock()

! Test Clock and Reset

end if

! The status lines HOLD, PEREQ, BUSY and ERROR are not used in the

! Demo/Trainer UUT. Display a message if one of these lines is active

! and wait for the condition to be fixed.

loop while (lines and $E2) <> 0

print on tlo ,clear screen

if (lines and 2) <> 0 then

print on tlo ,"HOLD is active; Press RESET to continue"

else if (lines and $20) <> 0 then

print on tlo , "PEREQ is active; Press RESET to continue"

else if (lines and $40) <> 0 then

print on tlo ,"~BUSY is active; Press RESET to continue"

else if (lines and $80) <> 0 then

print on tlo ,"~ERROR is active; Press RESET to continue"

end if

wait time 2000

end loop

end if

end handle

```

```

handle bad power

declare global numeric t2o

declare string clear screen = "\1B[2J"

declare global string messg

print on t2o ,messg+"FAULT DETECTED"

loop until (readstatus() and $3D00) = 0

fail ($14)

if (readstatus() and $3C00) = $3C00 then

print on tlo ,clear screen, "POD UUT Power"

print on tlo , "POWER_UP and press RESET on Trainer UUT"

wait time 2000

print on tlo ,clear screen, "CONTINUING..."

else

if (readstatus() and $100) <> 0 then fault 'CAP failure at POD Pin 52'

if (readstatus() and $400) <> 0 then fault 'POWER failure at POD Pin 30'

if (readstatus() and $800) <> 0 then fault 'POWER failure at POD Pin 62'

if (readstatus() and $1000) <> 0 then fault 'GROUND failure at POD Pin 35'

if (readstatus() and $2000) <> 0 then fault 'GROUND failure at POD Pin 9'

end if

end loop

untested ($14)

end handle

function retry access (ACCESS, ADDR, CTL)

! Retry last access performed using parameters from fault handlers.

handle pod timeout bad pwr

fault

end handle

handle pod timeout enabled line

fault

end handle

handle pod_timeout no clk

fault

end handle

handle pod timeout recovered

fault

end handle

handle pod_timeout setup

fault

end handle

```

```

declare string ACCESS

declare numeric CTL

declare numeric ADDR

if ADDR <> $E0000000 then

address = ADDR

else if CTL <> $E0000000 then

address = CTL

else

address = 0

end if

if ACCESS = "READ" then

if read addr address fails then fault

else if ACCESS = "WRITE" then

if write addr address, data $A5C3 fails then fault

end if

end function

! SETUP AND SYSTEM INITIALIZATION !

recover times = 0

execute recover()

! Recover synchronization between POD

! and the 80288 bus controller.

podsetup 'report power' "on"

! Turn on reporting functions except

podsetup 'report intr' "off"

! interrupts which is tested in the

podsetup 'report address' "on"

! SERIAL I/O test (test rs232b).

podsetup 'report control' "on"

podsetup 'report data' "on"

podsetup 'report forcing' "on"

! This is the go/no-go test which runs the major functional tests. !

gfi clear

! CLEAR ALL GFI RECOMENDATIONS

connect clear "yes"

! Clear all connect information.

execute test bus2 ()

execute test rom2 ()

execute test ram2 ()

execute test pia2 ()

execute test rs232b ()

execute test_video2 ()

end program

```

# FUNCTIONAL BLOCK TESTS FOR THE DEMO/TRAINER UUT DIAGNOSTIC PROGRAM

6.5.

This section contains the following functional test programs, which are necessary to support the diagnostic program for the Demo/Trainer UUT:

| test_bus2   | Tests the Microprocessor Bus functional block.                                                |

|-------------|-----------------------------------------------------------------------------------------------|

| test_pia2   | Tests the Parallel I/O function block.                                                        |

| test_ram2   | Test the RAM functional block.                                                                |

| test_rom2   | Tests the ROM function block.                                                                 |

| test_rs232b | Tests the Serial I/O function block.                                                          |

| test_video2 | Tests the video circuitry (the Video Control, Video RAM, and Video Output functional blocks). |