# 1611A LOGIC STATE ANALYZER

# FIELD TRAINING MANUAL

# **TABLE OF CONTENTS**

| FC                         | aye |

|----------------------------|-----|

| INTRODUCTION               | 2   |

| DISPLAY MODES              | 2   |

| TRACE                      | . 2 |

| TRACE TRIGS                | . 3 |

| COUNT TRIGS                | . 3 |

| TIME INTERVAL              | . 3 |

| TRIGGERING                 | 3   |

| WHY IS THE 1611A NEEDED?   | 3   |

| FEATURES AND ADVANTAGES    | 4   |

| PRINCIPLES OF OPERATION    | 5   |

| PARTIAL DISPLAYS           | . 5 |

| PROBES                     | . 6 |

| CONTROLS                   | . 6 |

| EXECUTE CONTROLS           | . 8 |

| DISPLAY GROUP              | . 9 |

| THE 1611A TRIGGERING STORY | 10  |

| PERSONALITY MODULE PANELS  | 12  |

| SELF TEST                  | 13  |

| PROBE TEST                 | 13  |

| QUESTIONS ABOUT THE 1611A  | 13  |

| BO80A INSTRUCTION SET      | 14  |

| 6800 INSTRUCTION SET       | 15  |

| SPECIFICATIONS             | 17  |

#### What the HP 1611A can do for your customer:

- Provide more triggering capability than ever before possible

- Increase efficiency in solving microprocessor problems and systems debug

- Measure time intervals from point to point in his program

- Provide a display of program flow as he wrote it in mnemonic code

- Automatically code Address and Data in hexadecimal or octal

#### INTRODUCTION

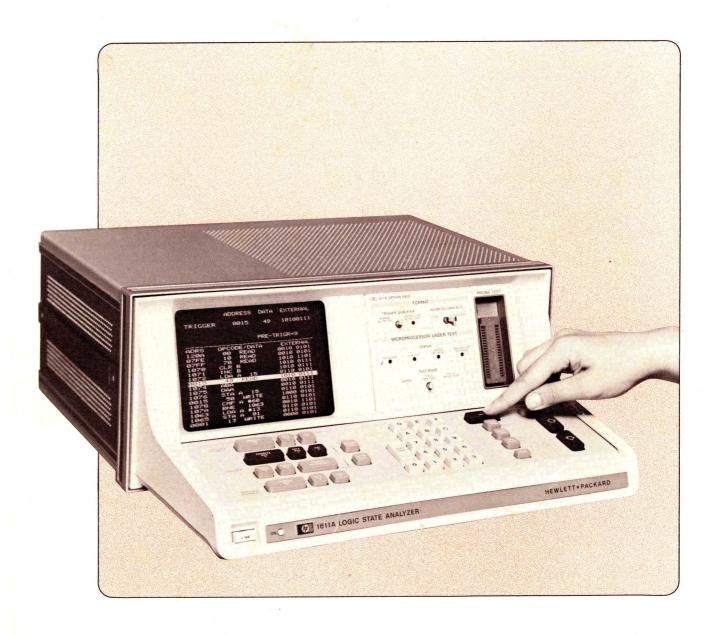

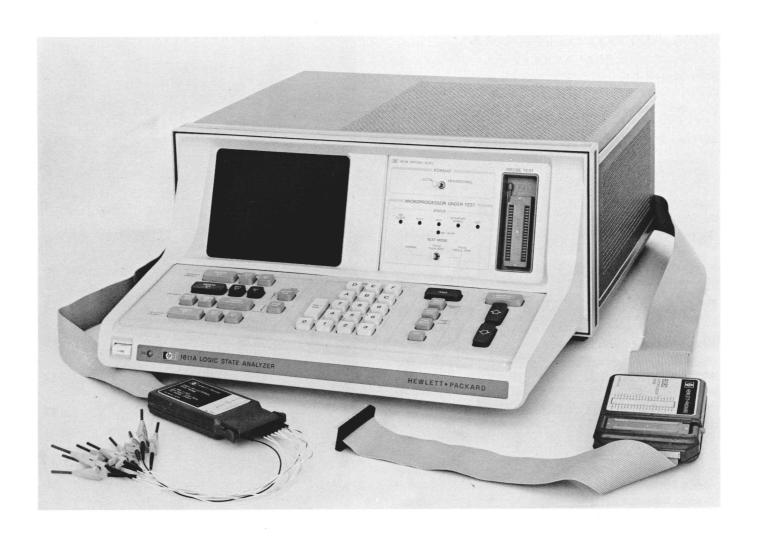

The 1611A is the first of a new generation of digital measurement instruments. It has an on board microprocessor which provides intelligence to simplify the controls and reduce setup and measurement errors. Instead of a bewildering array of knobs, pushbuttons and switches, most of the controls are located neatly on a keyboard and grouped together according to function. The instrument has self testing capabilities which make checks on its internal hardware and software.

It is a special purpose synchronous state analyzer designed specifically for use with microprocessors. At present there are two interchangeable options available: Option 080 for use with the Intel 8080A and 8080 plus second source versions and Option 068 for the Motorola 6800 and second source versions. Additional option modules can be added to the line in the future if the potential volume justifies the development cost.

Among the many measurement contributions offered by the 1611A, the most significant is the

greatly expanded triggering capability. Other contributions include new measurement features such as trigger counting, time interval measurement, mnemonic display, and error messages to warn of improper operation or setup.

#### **DISPLAY MODES**

The 1611A has several different display modes which can be selected depending on the type of information required from the measurement.

#### **TRACE**

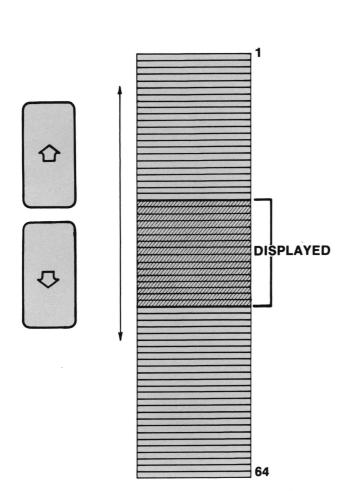

The most commonly used mode is Trace which is a line by line listing of the memory transactions or program flow and an information field which provides further descriptive information about the memory transaction. After a completed trace run the memory contains 64 bytes of data, 32 bits in length. The memory is viewed through a 16 line movable window (figure 1).

Trace display is interchangeable between either of two modes. The absolute mode displays the program address and the machine language op code or data (figure 2). In the mnemonic mode, the program address

Figure 1. The 64-byte memory is viewed through a 16-byte window which is positioned with the "ROLL" keys.

|              | ADI      | DRESS         | DATA | EXT        | ERNAL        |

|--------------|----------|---------------|------|------------|--------------|

| TRIGGER      | ₹ .      | 1300          |      |            |              |

|              |          |               |      |            |              |

| ADRS         | OPCO     | DE/DAT        |      | EXTE       | RNAL         |

| 1300         | 5F       | OPCOD         | E 0  | 000        | 0011         |

| 1301         | 5C       | READ          |      | 000        | 0011         |

| 1301         | 50       | OPCOD         |      | 000        | 0011         |

| 1302         | 96       | READ          |      | 000        | 0011         |

| 1302         | 96       | OPCOD         |      | 000        | 0011<br>0011 |

| 1303         | 11       | READ          |      | 000<br>000 | 0011         |

| 9911         | 94       | READ          |      | 000<br>000 | 0011         |

| 1304         | 1B       | OPCOD         |      | 000        | 0011         |

| 1305         | 19<br>19 | READ<br>OPCOD |      | 000        | 0011         |

| 1305<br>1306 | 97       | READ          |      | ดดด        | 0011         |

| 1306         | 97       | OPCOD         | _    | 000        | 0011         |

| 1300         | 11       | READ          |      | 000        | 0011         |

| 0011         | ēŝ.      | WRITE         |      | 000        | 0010         |

| 1308         | 02       | OPCOD         |      | 000        | 0011         |

| 1309         | 02       | READ          |      | 000        | 0011         |

Figure 2. Absolute mode displays data or op codes in numeric format.

|        | ADDRESS D   | ATA EXTERNAL           |

|--------|-------------|------------------------|

| TRIGGE | R 1300      |                        |

|        |             |                        |

|        |             |                        |

|        |             |                        |

| ADRS   | OPCODE/DATA | EXTERNAL               |

| 1300   | CLR B       | 0000 0011              |

| 13D1   | INC B       | 0000 0011              |

| 1302   | LDA A 11    | 0000 0011              |

| 0011   | Ø4 READ     | 0000 0011              |

| 1304   | ABA         | 0000 0011              |

| 13D5   | DAA         | 0000 0011              |

| 1306   | STA A 11    | 0000 0011              |

| 0011   | 05 WRITE    | 0000 0010              |

| 13D8   | NOP         | 0000 0011              |

| 1309   | NOP         | 0000 0011<br>0000 0011 |

| 13DA   | NOP _       |                        |

| 13DB   | LDA B_ 10   |                        |

| 0010   | 00 READ     | 0000 0011<br>0000 0011 |

| 1300   | ABA         | 9999 9911              |

| 13DE   | DAA         | 0000 0011              |

| 13DF   | STA A 12    | 8666 6511              |

**Figure 3.** Display format may be switched to mnemonic for referencing the written program.

is displayed along with the assembly language mnemonic and 8 or 16 bit operand (figure 3). Either display mode is selectable and interchangeable in hexadecimal or octal format.

#### TRACE TRIGS

Trace Trigs display is a listing in the absolute mode of only those words that match the preselected trigger conditions (figure 4).

| ENABLE<br>TRIGGER<br>DISABLE | AE<br><=<br>>= | DRESS<br>1000<br>4010<br>4000<br>105F | DATA       |              | rernaL<br>XXXXX0 |

|------------------------------|----------------|---------------------------------------|------------|--------------|------------------|

| TRIGGER                      | STO            | RF                                    |            |              |                  |

|                              |                | DE/DAT                                | A          | EXTE         | ERNAL            |

| 4006                         | ø5 <u> </u>    | WRITE                                 |            | 000          | 0010             |

| 4006                         | 94             | WRITE                                 | Ø          | 999          | 0010             |

| 4006                         | ĕз             | WRITE                                 | ē          | 999          | 0010             |

| 4006                         | ØA             | WRITE                                 |            | 000          | 0010             |

| 4006                         | $\bar{1}$ $1$  | WRITE                                 | 91         | 000          | 0010             |

| 4006                         | 38             | WRITE                                 | Ø          | 999          | 0010             |

| 4006                         | 05             | WRITE                                 | 91         | 999          | 0010             |

| 4006                         | Ø4             | WRITE                                 | <b>9</b> 1 | 000          | 0010             |

| 4006                         | 03             | WRITE                                 | 0          | 000          | 0010             |

| 4006                         | ØA             | WRITE                                 | 91         | 999          | 0010             |

| 4006                         | 1 1            | WRITE                                 | 91         | 999          | 0010             |

| 4006                         | 40             | WRITE                                 | 91         | 999          | 0010             |

| 4006                         | 95             | WRITE                                 | 91         | 900          | 0010             |

| 4006                         | Ø4             | WRITE                                 |            | 9 <b>9</b> 0 | 0010             |

| 4006                         | <b>93</b>      | WRITE                                 | 91         | <u> </u>     | 0010             |

| 4006                         | ØA             | MRITE                                 | 90         | 3 <b>9</b> 9 | 0010             |

|                              |                |                                       |            |              |                  |

**Figure 4.** Trace Triggers mode provides a display of data that satisfies only the trigger conditions. In this photo, the External trigger of LSB 0 defined that only writes to a display would be captured.

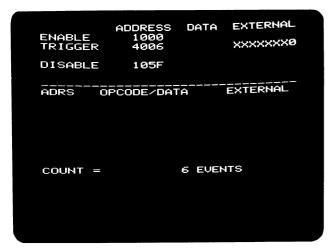

#### **COUNT TRIGS**

Display is a decimal number equal to the number of trigger matches which occur between two selected points in the program. The count can be updated in real time (figure 5).

**Figure 5.** Count Triggers mode provides a measurement of the number of trigger events occurring between two program points. This photo shows that six trigger events (4006) occurred between the Enable and Disable points.

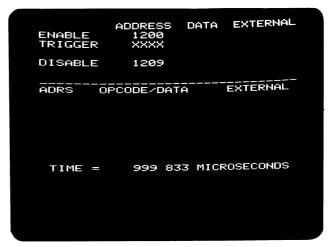

#### TIME INTERVAL

Time interval display is a single decimal number equal to the elapsed time between two selected points in the program (figure 6).

Figure 6. Time Interval mode counts the time between the trigger Enable and Disable points and directly displays the time in microseconds

#### **TRIGGERING**

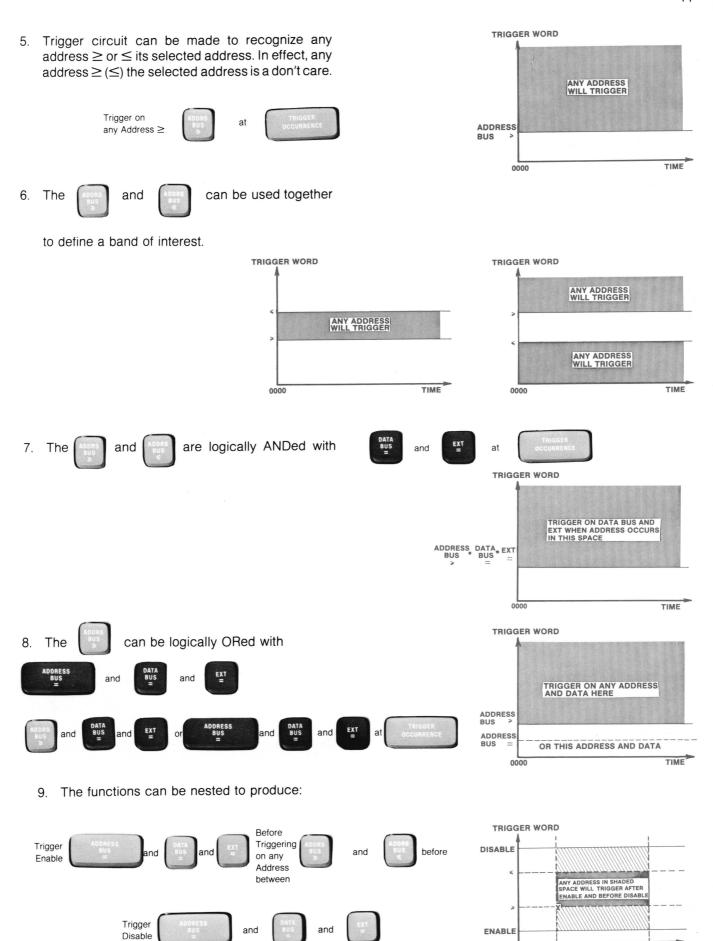

The 1611A makes its greatest contribution in the area of triggering capability which has been extended far beyond that of other instrumentation. With the 1611A it's possible to enter a trigger word of up to 24 bits in hex or octal plus an additional 8 bits in binary. The trigger word can then be qualified in a number of ways using additional trigger controls. For example, the trigger word may be enabled or disabled by another word or it may be recognized on the nth occurrence, 1≤n ≤256.

Another set of trigger controls (Address Bus≥, Address Bus ≤) are used to allow trigger recognition on any occurrence ≥ or ≤ the preselected address. These two modes may be used together to define a band over which any address bus activity will be recognized.

#### WHY IS THE 1611A NEEDED?

The 1611A is a very powerful yet very specialized instrument. It is designed to serve a market consisting of those people engaged in design and development, debug, production test, or maintenance of systems using the 8080A or the 6800 microprocessors. Although the market may be quite narrow, it has considerable depth. The 8080A and the 6800 are the two most widely used microprocessors in the industry today. This is a market which is still in its infancy and is growing rapidly.

There are an abundance of microprocessor analyzers, emulators, and simulators now on the market. All of these systems can solve microprocessor problems in various ways but none contain as much measurement power in one instrument as the 1611A. The powerful triggering capability, mnemonic display, and time interval features can save hours of time over other measurement techniques.

# TABLE I FEATURES AND ADVANTAGES

| 1. | On Board Micro-  | Simplifies controls. Pro-                                                                                                                                                                                                                                                      | 8   | Trigger Enable/               | Errors may occur only in                                                                                                                                                                      |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | processor        | vides diagnostic and error<br>messages, increases mea-<br>surement power.                                                                                                                                                                                                      | 0.  | Disable                       | one branch of program;<br>Trigger search can be<br>limited to area of interest.                                                                                                               |

| 2. | Trace Trigs      | Very powerful display qualifier scheme which allows selective trace on data of interest while ignoring all else. For example all "write" instruction occurring in a range of memory can be captured and displayed.                                                             | 9.  | Trigger Occurrence<br>Counter | Now the user can select which transaction to observe in a multiple pass operation.                                                                                                            |

| 3. | 64 Byte Memory   | Deeper memory provides larger window and allows looking back further in time before trig event.                                                                                                                                                                                | 10. | Address ≥<br>Address ≤        | Often it is of interest to know if a program has gone into a forbidden area of memory and if so how it got there. These trigger functions substitute for the 1600A map in this respect.       |

| 4. | Mnemonic Display | Allows operator to view code as written, saves time translating from machine language.                                                                                                                                                                                         | 11. | Trig Out                      | Provides a method of obtaining a real time look at area of interest.                                                                                                                          |

| 5. | Hex/Octal        | Operator can choose number system with which he is most comfortable or that used by his assembler.                                                                                                                                                                             | 12. | Trace Point<br>Out            | Provides a gate pulse which can be used by peripheral equipment to enable or inhibit activity during Trace. Can be used to generate an interrupt signal to the processor for a register dump. |

| 6. | Time Interval    | Allows measurement of true time elapsed in subroutine or between any two states of interest.                                                                                                                                                                                   | 13. | Trace Single<br>Step          | Provides interaction with processor. Processor can be stepped through area of interest one operation at a time.                                                                               |

| 7. | Trigger Count    | Operator can quickly obtain<br>an accurate count of the<br>occurrence of a word or<br>words without resorting to<br>calculation or hand count-<br>ing from a code sheet. Al-<br>lows optimization of code<br>by determining where the<br>processor spends most of<br>its time. | 14. | Self Test                     | No external equipment is needed to determine if the instrument is working properly.                                                                                                           |

#### PRINCIPLES OF OPERATION

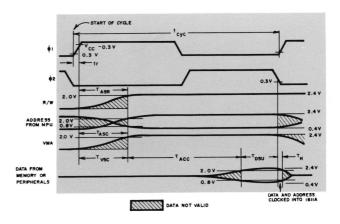

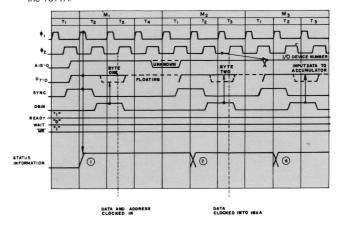

The 1611A is a state analyzer which is synchronous with the  $\phi_2$  clock pulse of the microprocessor under test. The clock is internally qualified such that the instrument can look at an entire instruction cycle and clock in only the desired information (figure 7). The 32 bits are entered as 16 bits of address from the address bus followed by 16 bits from the data bus and uncommitted external lines. Data is clocked in until the memory is full and the trigger and delay conditions have been met or the capture is halted. The capture memory then becomes the display memory until a new Execute function is initiated and the memory is cleared.

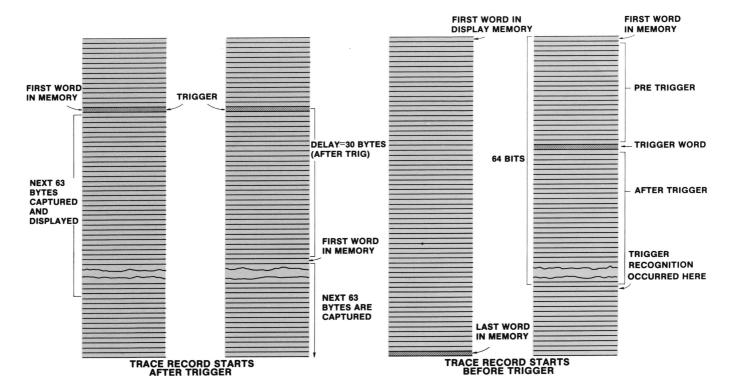

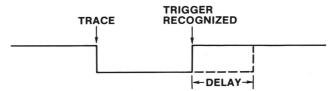

The Trace may be made to start before the trigger (Before Trig) or following the trigger (After Trig). When Before Trig is selected, the 1611A counts 63 minus the Before Trig number of bytes after the trigger is recognized and then displays the contents of memory. If After Trig is selected, 63 plus the After Trig number of bytes are clocked in before the contents of the memory are displayed. If no selection is made the display starts with the inverse video trigger word and continues through the following 63 bytes (figure 8).

#### **PARTIAL DISPLAYS**

When Trace or Trace Trigs is initiated, all previous data is lost except the 16 lines in the display buffer and if Count Trigs or Time Interval is selected, all data is lost. If the data capture is halted before 64 bytes have been entered, only the new data is displayed.

Figure 7A. 6800 memory read cycle shows when data is clocked into the 1611A.

Figure 7B. 8080 instruction cycle shows when data is clocked into the 1611A.

Figure 8. Memory diagrams show relationships of delay and pretrigger conditions.

**Figure 9.** Dedicated probe offers fast connection to the system microprocessor socket with its 40-pin connector. The system microprocessor is relocated to the probe body.

#### **PROBES**

The 1611A uses two probes to acquire data from the system under test. The primary probe is dedicated to the microprocessor and is not interchangeable with other 1611A options. It is a pod that gathers the signals from the microprocessor data and address buses along with the  $\phi_2$  clock and control signals and transmits them to the 1611A (figure 9). The pod contains a 40-pin connector socket in which the microprocessor is placed. Connection is made from the pod to the microprocessor socket in the system under test through a ribbon cable and 40-pin connector plug. If the microprocessor cannot be removed from the system, the connector cable and plug can be replaced with a ribbon cable terminated with a 40-pin dual in-line package connector (figure 10) which provides a direct connection from the pod to the processor.

Figure 10. Where the microprocessor is easily accessible or not easily removed a 40-pin clip can be used for connection to the system.

The External probe is secondary, with no clock input, and is not required for instrument operation (figure 11). It does have 8 uncommitted input lines to accept data coincident with data bus inputs on the primary probe. The input impedance is specified at approx 1  $\text{M}\Omega$  shunted by  $\leq\!\!25~\text{pF}$  at the probe tip.

#### **CONTROLS**

The on board microprocessor in the 1611A allows keyboard entry for most of the controls which offers several advantages. The controls can be neatly arranged in related groups. Front panel clutter is reduced and fewer controls are required because the internal intelligence makes each one more powerful. Another advantage is that all of the information concerning the status of the controls is presented on the display rather than depending on the operator to read the status of various switches, knobs, and pushbuttons.

Figure 11. An external probe permits connection to other points of interest in the system for additional data gathering capability.

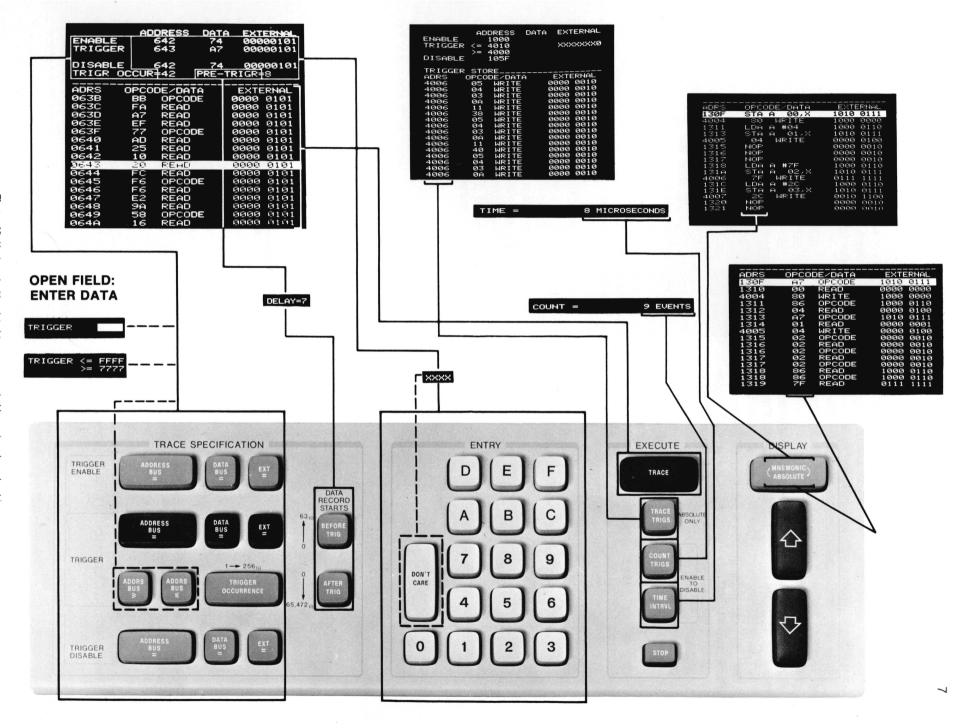

The keyboard controls are arranged in four groups (figure 12). The various controls are discussed in some detail in the following paragraphs. For more detailed descriptions, refer to the 1611A Operator's Manual.

**Trace Specification:** This group contains all of the controls associated with setting up the trigger conditions. Selection of one of these keys opens a field as indicated by the inverse video on the display.

**Entry Keys:** Numerical data is entered into the open Trace Specification field using keys in the Entry Group. **Execute:** Selection of these keys determines the type measurement which the 1611A is to perform and therefore the type of display obtained.

**Display:** The display group controls are used to manipulate the CRT display but have no effect on the memory content.

#### TRACE SPECIFICATION

The Trace Specification group contains three subgroups—Trigger, Trigger Enable, and Trigger Disable.

**Trigger:** The selected trigger word may be as short as one bit or as long as thirty-two bits in length. Any unspecified fields are automatically read as don't cares. Trigger entry is separated into three parts. As the key is selected for each part, the corresponding field is opened on the display.

Address Bus =: Controls the field for entry of the desired program or memory address trigger word. Entry is made with 4 hex or 6 octal characters and is automatically right justified with leading zeroes assumed. Data Bus =: Controls the selection of an 8 bit trigger word on the data bus. Entries may be made as 2 hex or 3 octal characters and are automatically right justified with leading zeroes.

The Address Bus and Data Bus controls allow the operator to enter trigger conditions exactly as they appear on his code sheets. The arrangement is also much less confusing than working with individual bits from 24 uncommitted inputs which can lead to time-consuming errors in setup.

**Ext** =: Controls trigger recognition on 8 external lines. Entry is made in binary and is automatically right justified with leading don't cares assumed. These eight lines can be used to monitor the activity external to the processor such as control lines and can also be used as trigger and display qualifiers. For example, the Trace Trigs display could be qualified with a signal such as the R/W line on the 6800 to produce a display containing only "write" instructions. The Ext inputs are active only when the Data Bus inputs are active.

The trigger word recognized by the 1611A is the AND combination of the 32 bits controlled by the Address Bus, Data Bus, and Ext keys. Further qualification can be obtained using additional Trigger group keys.

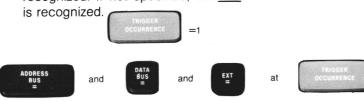

**Trigger Occurrence:** This control is used to determine the number of trigger word occurrences before recognition. Selection of the key opens a field for the entry of a decimal number 1≤n ≤256. An obvious application for this control is triggering on the nth occurrence of a subroutine to look for an error. This feature could also be used to trigger on the nth occurrence of an external bit or combination of bits such as the output of a shift register.

**Address Bus**  $\geq$ , **(Address Bus**  $\leq$ ): Additional triggering power is achieved with the use of these keys which limit triggering to activity  $\geq$  ( $\leq$ ) the selected address. An alternate approach is to consider any address  $\geq$  ( $\leq$ ) the selected address as a don't care. These controls can be used to look for trigger occurrences in forbidden areas of ROM or RAM using pretrigger to determine how the program arrived there. In this respect, they perform one of the functions of the map mode of the 1600A. The Address Bus  $\geq$  ( $\leq$ ) controls could also be used along with the occurrence counter to page through a section of ROM or RAM

where an error is suspected in a stored table which is a common problem encountered when debugging a system. For example:

ADDRS ADDRS

BUS 8000 BUS 9000 n = 1, 2, 3, ... 256

> <

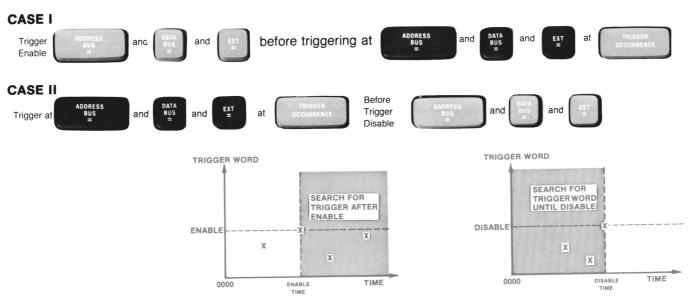

**Trigger Enable and Trigger Disable:** Functions are entered in the same manner as the Trigger word. They can be considered as a trigger arm and disarm circuit. When used in conjunction with the Trigger word, a sequence of trigger events is described. The 1611A will look for a trigger word after the occurrence of the Enable word and before the occurrence of the Disable word. These features, for example, allow the search for a trigger word only as it occurs in a subroutine bounded by the Enable and Disable Addresses or perhaps by an external control signal going high and then returning low.

Trigger Enable and Trigger Disable functions are also used in conjunction with the Count Trigs and Time Interval modes to determine the limits of activity.

Unless otherwise specified, the display begins with the trigger word (displayed in inverse video) and continues through the following 63 words. **Delay** can be added by selecting Trace Starts After Trig and entering a decimal number  $n \le 65$  472.

"Negative Time" or pretrigger is displayed by selecting Trace Starts Before Trig and entering a decimal number  $n \le 63$ . Note that Delay refers to qualified clocks or memory transactions and not to the number of  $\phi_2$  clocks.

#### **EXECUTE CONTROLS**

The execute group is used to instruct the 1611A to perform a specific task or measurement. Any Execute function except Stop immediately clears the main memory of old data. Upon execution of a Trace or Trace Trig, the 16 bytes of data in the display buffer will remain on display until the new acquisition is complete and a display cycle is initiated.

**Trace:** The Trace is the most general mode of data acquisition because it provides the capture of 64 consecutive memory transactions in order to provide a display of microprocessor program execution. When Trace is selected, the trigger circuit is activated and data acquisition begins. After the main memory is filled and the delay and trigger conditions have been satisfied, data acquisition is halted and a display cycle is initiated. The display cycle consists of a transfer of data from the main memory to the display and requires approximately 200 ms (figure 13).

**Trace Triggers:** In the Trace Trigger mode, the 1611A captures and displays only those bytes that contain a match with the preselected trigger conditions. This mode can be considered as a qualified display. For example, the operator may want to look at only the

**Figure 13.** 16-bytes of data out of the 64 bytes in memory are written directly to the display.

"Read" instruction from a block of memory in order to verify that the proper data was entered there or he may want to acquire data only when a specified peripheral device is addressed.

Count Trigs: In the Count Trigs mode, 1611A counts the trigger occurrences between the Trig Enable and Trig Disable words. The display contains no data other than the decimal number equal to the number of trigger words recognized. One of the primary uses of this mode is in determing the number of times a subroutine is called in a branch of the program. Some times a programmer might miscalculate the number of times a program iterates through an increment, decrement or delay loop. This new feature allows rapid verification of the number of iterations that occur.

**Time Interval:** The Time Interval mode produces a readout of the elapsed time between the occurrence of two states defined by the Trigger Enable and the Trigger Disable. The timing measurement is made using an internal 1 MHz clock and the accuracy of the measurement is within  $0.1\% \pm 1~\mu s$ .

Verifying the accuracy of wait loops is an obvious application of the time interval features but it is also useful to know the time required for execution of a subroutine when a critical timing interface is involved with the system hardware or an external device.

**Stop:** Selection of the Stop key halts any execute function in progress. A display of the activity leading to the Stop command will result.

#### **DISPLAY GROUP**

Display group controls are used to determine the format in which data is displayed—they have no bearing on the actual data stored in memory.

Mnemonic/Absolute: This control determines whether the data is displayed as captured (absolute) or if the data is to be inverse assembled into mnemonic statements with operands (mnemonic). In Absolute mode, each line of display represents one memory transaction which includes an address, data word, description of operation (i.e. op code, read, write), and 8 external bits. The mnemonic mode data is inverse assembled into a display which often contains more than one memory transaction per line. Each line contains an address, a mnemonic symbol, and possibly an 8 or 16 bit operand in addition to the operation description field and 8 bits of external probe data. It's usual for the mnemonic display to contain less than 64 lines although the data content is the same as the 64 line absolute display.

**Roll** † ‡ : These key controls are used to roll the 16 line display window through the 64 byte memory.

#### TRIGGER OUT

Three output connectors are provided on the rear panel of the 1611A for supplying trigger pulses to peripheral device.

**Trigger Output:** \*Provides ~ 75 ns, RZ, TTL output on each and every occurrence of the selected trigger word. This output can be especially useful for triggering an oscilloscope.

Trace Point Out (」) (「L): \*These outputs are levels which change state when a trace is initiated and return to previous state when a trigger word is recognized or the trace point is reached after delay.\*\*

This provides a transition for triggering and pulse for gating. A useful application is to connect one of these outputs to the interrupt line of the microprocessor under test. The arrival at the trace point is under control of the operator who can initiate an interrupt at any time, which enables him to call up special debug software of his own during development.

\*The Trigger Output and Trace Point Out transitions occur within 350 ns (opt 080) or 550 ns (opt 068) of trigger recognition.

\*\*If delay has been added, the output transition will occur one memory transaction before the first word in the display (figure 14).

**Figure 14.** Trace Point timing diagram. When Trace is pressed the signal changes state and upon trigger recognition returns to its original level. If delay is added the return transition occurs one memory transaction prior to the first displayed word.

# TABLE II THE 1611A TRIGGERING STORY

TRIGGER WORD

0000

TIME

Simple triggering is accomplished with the logical AND combinations of 32 possible bits with don't cares allowed.

2. Triggering power can be increased by specifying which occurrence of the trigger word is to be recognized. If not specified, the <u>first</u> occurrence is recognized.

3. The trigger word can be further qualified using the Trigger Enable and Trigger Disable features.

4. Used together triggering can be limited to area of interest such as a subroutine.

DISABLE TIME

0000

ENABLE

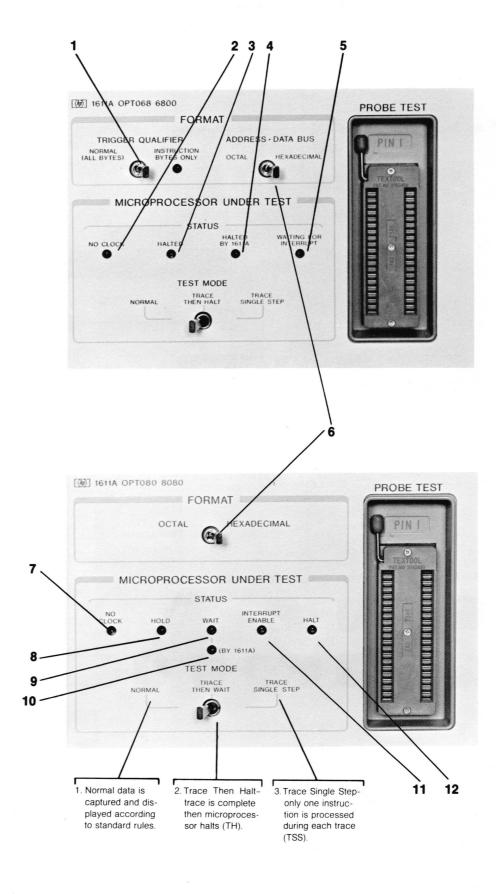

#### Option 068

Allows operator to prevent 1611A from triggering on 6800 "look ahead." Also excludes triggering on data bytes.

No Clock light is on when no  $\phi_2$  clock is present. Halted indicated when microprocessor has been halted externally.

Halted by 1611A indicates the microprocessor has been halted after Trace has completed or Trace Single Step has been executed.

Waiting For Interrupt indicates that microprocessor has executed a Wait for Interrupt instruction (WAI).

Selects Octal or Hex format for data display and heading decimal numbers are unchanged (figure 15).

#### Option 080

- **7** No Clock light is on when no  $\phi_2$  clock is present.

- 8 Hold indicates Hold line low and 8080 is holding.

- Wait indicates 8080 is in Wait mode and is waiting for inputs from memory or peripheral device.

- By 1611A indicates when Wait state is generated by 1611A in TH or TSS mode. Interrupt enable indicates status of internal enable bit which will allow interrupt to be processed. Halt indicates that a Halt instruction has been executed by 8080A.

Switch selects test move.

|         | ADDRESS D  | DATA EXTERNAL          |

|---------|------------|------------------------|

| TRIGGER | 1300       |                        |

|         |            |                        |

|         |            |                        |

| ADRS O  | PCODE/DATA | EXTERNAL               |

|         | LR B       | 0000 0011              |

| 13D1 II | NC B       | 0000 0011              |

| 1302 LI | DA A 11    | 0000 0011              |

| 9911    | 04 READ    | 0000 0011              |

| 13D4 AI | BA         | 0000 0011              |

| 1305 Di | AA         | 0000 0011              |

| 13D6 S  | TA A 11    | 0000 0011              |

|         | 05 WRITE   | 0000 0010              |

|         | OP         | 0000 0011              |

|         | OP         | 0000 0011              |

|         | OP _       | 0000 0011              |

|         | DA B10     | 0000 0011              |

|         | 00 READ    | 0000 0011              |

|         | BA         | 0000 0011<br>0000 0011 |

|         | <u>88 </u> |                        |

| 13DF S  | TA A 12    | 0000 0011              |

accuracy. Upon satisfactory completion of these tests, the message "SELF TEST COMPLETED" is written on screen by the microprocessor which gives a visual indication that the display circuitry and microprocessor are working properly.

**PROBE TEST:** Functional tests may be made on the 1611A without any external circuits. These tests are made by connecting the microprocessor probe plug into the front panel socket. Executing a trace generates the display shown in figure 16. All of the system's functions and controls may then be exercised on this pattern.

|          | ADDRESS    | DATA | EXTERNAL |

|----------|------------|------|----------|

| TRIGGER  | 011720     |      |          |

|          |            |      |          |

|          |            |      |          |

| ADRS C   | PCODE/DATA |      | XTERNAL  |

| 011720 C | LR B       | 99   | 000 011  |

| 011721 I | NC B       | 00   | 000 011  |

| 011722 L | DA A 021   | 00   | 000 011  |

| 000021   | 004 READ   | 00   | 000 011  |

| 011724 £ | aBA        | 00   | 000 011  |

| 011725 C | DAA        | 00   | 000 011  |

| 011726 9 | STA A 021  | 00   | 000 011  |

| 000021   | 005 WRITE  | 00   | 000 010  |

| 011730 h | 10P        | 00   | 000 011  |

| 011731 h | 10P        | 00   | 000 011  |

|          | 10P        | 00   | 000 011  |

|          | DA B 020   | 00   | 000 011  |

| 000020   | 000 READ   | 00   | 000 011  |

|          | ABA        | 00   | 000 011  |

|          | DAA        | 00   | 000 011  |

| 011737 9 | STA A 022  | 00   | 000 011  |

|          |            |      |          |

**Figure 15.** Traces at the same trigger point showing capability of switching from hexadecimal format (upper photo) to octal format (lower photo).

#### **SELF TEST**

During power up, the internal microprocessor makes some internal tests on the 1611A. A check sum on the ROM is performed which tests the ROM for dropped bits. Next a test pattern is written to the RAM and then read back and checked for

|         | ΑD       | DRESS  | DATA   | EXT          | ERNAL        |  |

|---------|----------|--------|--------|--------------|--------------|--|

|         |          |        |        |              |              |  |

| TRIGGER |          | XXXX   | AA     |              |              |  |

|         |          |        |        |              |              |  |

|         |          |        |        |              | _            |  |

|         |          |        | PRE-TI | RIGK=        | = (          |  |

|         | 5555     | DEZDAT |        | -EUTE        | RNAL         |  |

|         |          | DEZDAT |        | елт<br>Обоб  |              |  |

| 3333    | 33       | WRITE  |        |              | 9999<br>9999 |  |

| 4444    | 44       | WRITE  |        | 8888         | овов<br>Обоб |  |

| 5555    | 55       | WRITE  |        | 9999<br>9999 | 0000<br>0000 |  |

| 6666    | 66       | WRITE  |        | 0000         |              |  |

| 7777    | 77       | WRITE  |        | 9999         | 9999         |  |

| 8888    | 88       | WRITE  |        | 9999<br>9999 | 9999         |  |

| 9999    | 88       | MRITE  |        | <u> </u>     | 9999         |  |

| AAAA    | AA       | WRITE  |        | 9999<br>9999 | 0000         |  |

| BBBB    | 88<br>CC | WRITE  |        | 0000         | 0000<br>0000 |  |

| 0000    | 00       | WRITE  |        | 0000         | 9999         |  |

| 0000    | ËΕ       | WRITE  |        | 0000         | 9999         |  |

| EEEE    | 름        | WRITE  |        | 0000         | 0000         |  |

| ดดออ    | ออ       | WRITE  |        | рава         | 0000         |  |

| 1111    | 11       | WRITE  |        | 0000         | 9999         |  |

| 2222    | 22       | WRITE  |        | 0000         | 0000         |  |

|         |          |        |        |              |              |  |

Figure 16. Internally generated test display in the probe test mode.

### **QUESTIONS ABOUT THE 1611A**

- Q Are there any additional microprocessor options planned for the near future?

- A Additional options are being considered and can be introduced as required when the market picture clarifies and settles on various processors. Field Engineers should make their inputs known to the Colorado Springs Division.

- Q What is involved in converting from one option to another?

- A The conversion process involves removing the top cover, exchanging two boards, and replacing the front panel unit and microprocessor probe with the new option. It takes about 15 minutes to make a changeover.

- Q Can the 1611A be used as a general purpose state analyzer?

- A No. The personality modules require special qualification of the  $\phi_2$  clock in order to capture data in the proper order.

- Q Will Hewlett-Packard design and build option kits for a customer's "in house" microprocessor?

- A Probably not, the development would be expensive and the customer would probably be required to commit to purchase a substantial number of units.

- Q Can the 1611A option 080 be used with 8080A's produced by manufacturers other than Intel?

- A Yes, the 1611A is compatible with all the second source versions of the 8080A.

- Q Why was a map mode not included?

- A The map was omitted for a number of reasons, one being that it is not compatible with the CRT used in the 1611A. However, one of the key features of the map is available with the 1611A Trace Specification keys. For example, if the program is running off to the "bushes" use the ≥(≤) keys and enter the allowable address bounds along with several bits of pretrig. The 1611A will then trigger and display on any memory transaction which occurs at an address outside that specified.

## SILICON GATE MOS 8080A

#### **INSTRUCTION SET**

#### **Summary of Processor Instructions**

| Mnemonic             | Description                                      | D <sub>7</sub> | D <sub>6</sub> |   | tructi<br>D <sub>4</sub> |    |        |   | <sub>1</sub> D <sub>0</sub> | Clock [2]<br>Cycles | Mnemonic   | Description                        | D <sub>7</sub> | D <sub>6</sub> |   |   |   | ode [ |   | D <sub>0</sub> | Clock [2]<br>Cycles |

|----------------------|--------------------------------------------------|----------------|----------------|---|--------------------------|----|--------|---|-----------------------------|---------------------|------------|------------------------------------|----------------|----------------|---|---|---|-------|---|----------------|---------------------|

| MOV <sub>r1,r2</sub> | Move register to register                        | 0              | 1              | D | D                        | D  | s      | s | s                           | 5                   | RZ         | Return on zero                     | 1              | 1              | 0 | 0 | 1 | 0     | 0 | 0              | 5/11                |

| MOV M, r             | Move register to memory                          | Ŏ              | 1              | 1 | 1                        | 0  | S      | S | S                           | 7                   | RNZ        | Return on no zero                  | 1              | 1              | 0 | 0 | 0 | 0     | C | 0              | 5/11                |

| MOV r, M             | Move memory to register                          | 0              | 1              | D | D                        | D  | 1      | 1 | 0                           | 7                   | RP         | Return on positive                 | 1              | 1              | 1 | 1 | 0 | 0     | 0 | 0              | 5/11                |

| HLT                  | Halt                                             | 0              | 1              | 1 | 1                        | 0  | 1      | 1 | 0                           | 7                   | RM         | Return on minus                    | 1              | 1              | 1 | 1 | 1 | 0     | 0 | 0              | 5/11                |

| MVIr                 | Move immediate register                          | 0              | 0              | D | D                        | D  | 1      | 1 | 0                           | 7                   | RPE        | Return on parity even              | 1              | 1              | 1 | 0 | 1 | 0     | 0 | 0              | 5/11                |

| MVIM                 | Move immediate memory                            | 0              | 0              | 1 | 1                        | 0  | 1      | 1 | 0                           | 10                  | RPO        | Return on parity odd               | 1              | 1              | 1 | 0 | 0 | 0     | 0 | 0              | 5/11                |

| 1NR r                | Increment register                               | 0              | 0              | D | D                        | D  | 1      | 0 | 0                           | 5                   | RST        | Restart                            | 1              | 1              | A | A | A | 1     | 1 | 1              | 11                  |

| DCR r                | Decrement register                               | 0              | 0              | D | D                        | D  | 1      | 0 | 1                           | 5                   | IN         | Input                              | 1              | 1              | 0 | 1 | 1 | 0     | 1 | 1              | 10                  |

| INR M                | Increment memory                                 | 0              | 0              | 1 | 1                        | 0  | 1      | 0 | 0                           | 10                  | OUT        | Output                             | 1              | 1              | 0 | 1 | 0 | 0     | 1 | 1              | 10                  |

| DCR M                | Decrement memory                                 | 0              | 0              | 1 | 1                        | 0  | 1      | 0 | 1                           | 10                  | LXIB       | Load immediate register            | 0              | 0              | 0 | 0 | 0 | 0     | 0 | 1              | 10                  |

| ADD r                | Add register to A                                | 1              | 0              | 0 | 0                        | 0  | S      | S | S                           | 4                   |            | Pair B & C                         |                |                |   |   |   |       | 0 | 1              | 10                  |

| ADC r                | Add register to A with carry                     | 1              | 0              | 0 | 0                        | 1  | S      | S | S                           | 4                   | LXID       | Load immediate register            | 0              | 0              | 0 | 1 | 0 | 0     | U | '              | 10                  |

| SUB r                | Subtract register from A                         | 1              | 0              | 0 | 1                        | 0  | S      | S | S<br>S                      | 4<br>4              |            | Pair D & E                         | 0              | 0              | 1 | 0 | 0 | 0     | 0 | 1              | 10                  |

| SBB r                | Subtract register from A with borrow             | 1              | 0              | 0 | 1                        | 1  | S      | S |                             |                     | LXI H      | Load immediate register Pair H & L |                |                |   |   |   |       | 0 | ,              | 10                  |

| ANA r                | And register with A                              | 1              | 0              | 1 | 0                        | 0  | S      | S | S                           | 4                   | LXI SP     | Load immediate stack pointer       | 0              | 0              | 1 | 1 | 0 | 0     | Ö | i              | 11                  |

| XRA r                | Exclusive Or register with A                     | 1              | 0              | 1 | 0                        | 1  | S      | S | S<br>S                      | 4<br>4              | PUSH B     | Push register Pair B & C on        | 1              | 1              | U | 0 | U | '     | U | •              | • • •               |

| ORA r                | Or register with A                               | 1              | 0              | 1 | 1                        | 1  | S<br>S | S | S                           | 4                   | PUSH D     | stack                              | 1              |                | 0 | 1 | 0 | 1     | 0 | 1              | 11                  |

| CMPr                 | Compare register with A                          | 1              | 0              | 0 | Ö                        | Ó  | 1      | 1 | 0                           | i                   | PUSH D     | Push register Pair D & E on stack  | •              | •              | U | • | ٠ | •     | ٠ | •              | •••                 |

| ADD M                | Add memory to A                                  | 1              | 0              | 0 | 0                        | 1  | 1      | i | 0                           | 'n                  | PUSH H     | Push register Pair H & L on        | 1              | 1              | 1 | 0 | 0 | 1     | 0 | 1              | 11                  |

| ADC M                | Add memory to A with carry                       | 1              | 0              | 0 | 1                        | ò  | i      | i | Ö                           | 'n                  | rusnin     | stack                              | •              | •              | • | ٠ | ٠ | •     | ٠ | •              | ••                  |

| SUB M<br>SBB M       | Subtract memory from A<br>Subtract memory from A | 1              | 0              | 0 | i                        | 1  | i      | i | Ö                           | 7                   | PUSH PSW   | Push A and Flags<br>on stack       | 1              | 1              | 1 | 1 | 0 | 1     | 0 | 1              | 11                  |

| ANA M                | with borrow<br>And memory with A                 | 1              | 0              | 1 | 0                        | 0  | 1      | 1 | 0                           | 7<br>7              | POP B      | Pop register pair B & C off        | 1              | 1              | 0 | 0 | 0 | 0     | 0 | 1              | 10                  |

| XRA M                | Exclusive Or memory with A                       | 1              | 0              | 1 | 0                        | 1  | 1      | 1 | 0                           | ,                   | POP D      | stack                              | 1              | 1              | 0 | 1 | 0 | 0     | 0 | 1              | 10                  |

| ORA M                | Or memory with A                                 | 1              | 0              | 1 | 1                        | 1  | 1      | 1 | 0                           | 7                   | PUPU       | Pop register pair D & E off stack  | •              | •              | U | • | ٠ | Ü     | ٠ | •              |                     |

| CMP M                | Compare memory with A                            | 1              | 1              | 0 | 0                        | Ó  | i      | i | 0                           | ,                   | POP H      | Pop register pair H & L off        | 1              | 1              | 1 | 0 | 0 | 0     | 0 | 1              | 10                  |

| ADI                  | Add immediate to A<br>Add immediate to A with    | 1              | i              | 0 | 0                        | 1  | i      | 1 | 0                           | 7                   | '0' ''     | stack                              | •              | •              | • | ٠ | • | -     | • |                |                     |

| ACI                  | carry                                            | -              | ·              |   | 1                        |    | 1      | 1 | 0                           | 7                   | POP PSW    | Pop A and Flags<br>off stack       | 1              | 1              | 1 | 1 | 0 | 0     | 0 | 1              | 10                  |

| SUI                  | Subtract immediate from A                        | 1              | 1              | 0 | i                        | 0  | i      | i | Ö                           | ,                   | STA        | Store A direct                     | 0              | 0              | 1 | 1 | 0 | 0     | 1 | 0              | 13                  |

| SBI                  | Subtract immediate from A                        | •              | '              | U | '                        | •  | •      | ٠ | ٠                           | •                   | LDA        | Load A direct                      | Ō              | Ŏ              | 1 | 1 | 1 | Ö     | 1 | Ô              | 13                  |

| ANI                  | with borrow And immediate with A                 | 1              | 1              | 1 | 0                        | 0  | 1      | 1 | 0                           | 7                   | XCHG       | Exchange D & E, H & L              | 1              | 1              | 1 | Ó | 1 | Ō     | 1 | 1              | 4                   |

| XRI                  | Exclusive Or immediate with                      | i              | i              | i | ŏ                        | 1  | i      | 1 | Ö                           | 7                   | ~0         | Registers                          |                |                |   |   |   |       |   |                |                     |

| A111                 | A                                                |                | •              | • | -                        |    |        |   |                             |                     | XTHL       | Exchange top of stack, H & L       | 1              | 1              | 1 | 0 | 0 | 0     | 1 | 1              | 18                  |

| ORI                  | Or immediate with A                              | 1              | 1              | 1 | 1                        | 0  | 1      | 1 | 0                           | 7                   | SPHL       | H & L to stack pointer             | 1              | 1              | 1 | 1 | 1 | 0     | 0 | 1              | 5                   |

| CPI                  | Compare immediate with A                         | 1              | 1              | 1 | 1                        | 1  | 1      | 1 | 0                           | 7                   | PCHL       | H & L to program counter           | 1              | 1              | 1 | 0 | 1 | 0     | 0 | 1              | 5                   |

| RLC                  | Rotate A left                                    | 0              | 0              | 0 | 0                        | 0  | 1      | 1 | 1                           | 4                   | DADB       | Add B & C to H & L                 | 0              | 0              | 0 | 0 | 1 | 0     | 0 | 1              | 10                  |

| RRC                  | Rotate A right                                   | 0              | 0              | 0 | 0                        | 1  | 1      | 1 | 1                           | 4                   | DAD D      | Add D & E to H & L                 | 0              | 0              | 0 | 1 | 1 | 0     | 0 | 1              | 10                  |

| RAL                  | Rotate A left through carry                      | 0              | 0              | 0 | 1                        | 0  | 1      | 1 | 1                           | 4                   | DADH       | Add H & L to H & L                 | 0              | 0              | 1 | 0 | 1 | 0     | 0 | 1              | 10                  |

| RAR                  | Rotate A right through                           | 0              | 0              | 0 | 1                        | 1  | 1      | 1 | 1                           | 4                   | DAD SP     | Add stack pointer to H & L         | 0              | 0              | 1 | 1 | 1 | 0     | 0 | 1              | 10                  |

|                      | carry                                            |                |                |   |                          |    |        |   |                             |                     | STAX B     | Store A indirect                   | 0              | 0              | 0 | 0 | 0 | 0     | 1 | 0              | 7                   |

| JMP                  | Jump unconditional                               | 1              | 1              | 0 | 0                        | .0 | 0      | 1 | 1                           | 10                  | STAX D     | Store A indirect                   | 0              | 0              | 0 | 1 | 0 | 0     | 1 | 0              | 7                   |

| JC                   | Jump on carry                                    | 1              | 1              | 0 | 1                        | 1  | 0      | 1 | 0                           | 10                  | LDAXB      | Load A indirect                    | 0              | 0              | 0 | 0 | 1 | 0     | 1 | 0              | 7                   |

| JNC                  | Jump on no carry                                 | 1              | 1              | 0 | 1                        | 0  | 0      | 1 | 0                           | 10                  | LDAXD      | Load A indirect                    | 0              | 0              | 0 | 1 | 1 | 0     | 1 | 0              | 7                   |

| JZ                   | Jump on zero                                     | 1              | 1              | 0 | 0                        | 1  | 0      | 1 | 0                           | 10                  | INXB       | Increment B & C registers          | 0              | 0              | 0 | 0 | 0 | 0     | 1 | 1              | 5                   |

| JNZ                  | Jump on no zero                                  | 1              | 1              | 0 | 0                        | 0  | 0      | 1 | 0                           | 10                  | INXD       | Increment D & E registers          | 0              | 0              | 0 | 1 | 0 | 0     | 1 | 1              | 5                   |

| JP                   | Jump on positive                                 | 1              | 1              | 1 | 1                        | 0  | 0      | 1 | 0                           | 10                  | INXH       | Increment H & L registers          | 0              | 0              | 1 | 0 | 0 | 0     | 1 | 1              | 5<br>5              |

| JM                   | Jump on minus                                    | 1              | 1              | 1 | 1                        | 1  | 0      | 1 | 0                           | 10                  | INX SP     | Increment stack pointer            | 0              | 0              | 1 | 1 | 0 | 0     | 1 | 1              | 5                   |

| JPE                  | Jump on parity even                              | 1              | 1              | 1 | 0                        | 1  | 0      | 1 | 0                           | 10                  | DCX B      | Decrement B & C                    | 0              | 0              | 0 | 0 | 1 | 0     | 1 | 1              | 5<br>5              |

| JP0                  | Jump on parity odd                               | 1              | 1              | 1 | 0                        | 0  | 0      | 1 | 0                           | 10                  | DCX D      | Decrement D & E                    | 0              | 0              | 0 | 1 | 1 | 0     | 1 | 1              | 5                   |

| CALL                 | Call unconditional                               | !              | 1              | 0 | 0                        | 1  | !      | 0 | 1                           | 17                  | DCX H      | Decrement H & L                    | 0              | 0              | 1 | 0 | 1 | 0     |   | i              | 5                   |

| CC                   | Call on carry                                    | 1              | 1              | 0 | 1                        | 1  | 1      | 0 | 0                           | 11/17<br>11/17      | DCX SP     | Decrement stack pointer            | 0              | 0              | 1 | 1 | 1 | 1     | 1 | 1              | 4                   |

| CNC                  | Call on no carry                                 | 1              | 1              | 0 | 1                        | 0  | 1      | 0 | 0                           | 11/17               | CMA        | Complement A                       | 0              | 0              | i | 1 | ó | i     | i | i              | 4                   |

| CZ                   | Call on zero                                     | 1              | 1              | 0 | 0                        | 1  | 1      | 0 | 0                           | 11/17               | STC<br>CMC | Set carry<br>Complement carry      | 0              | 0              | 1 | 1 | 1 | 1     | 1 | i              | 4                   |

| CNZ                  | Call on no zero                                  | 1              | 1              | 0 | 0                        | 0  | 1      | 0 | 0                           | 11/17               | DAA        | Decimal adjust A                   | Ö              | 0              | i | Ö | ò | 1     | i | i              | 4                   |

| CP                   | Call on positive                                 | 1              | 1              | 1 | 1                        | 1  | i      | 0 | 0                           | 11/17               | SHLD       | Store H & L direct                 | Ö              | Ö              | i | Ö | Ö | ò     | i | ò              | 16                  |

| CM                   | Call on minus                                    | i              | 1              | 1 | 0                        | 1  | i      | 0 | Ö                           | 11/17               | LHLD       | Load H & L direct                  | ő              | Ö              | i | Ö | 1 | Ö     | i | ŏ              | 16                  |

| CPE<br>CPO           | Call on parity even<br>Call on parity odd        | 1              | 1              | 1 | 0                        | Ö  | i      | 0 | Ö                           | 11/17               | EI         | Enable Interrupts                  | 1              | 1              | i | 1 | i | ŏ     | 1 | 1              | 4                   |

| RET                  | Return                                           | i              | i              | Ö | ŏ                        | 1  | Ö      | Ö | 1                           | 10                  | Di         | Disable interrupt                  | 1              | 1              | 1 | 1 | Ó | 0     | 1 | 1              | 4                   |

| RC                   | Return on carry                                  | i              | i              | Ö | 1                        | i  | Ö      | ŏ | Ö                           | 5/11                | NOP        | No-operation                       | Ó              | Ó              | Ó | 0 | 0 | 0     | 0 | 0              | 4                   |

| RNC                  | Return on no carry                               | i              | i              | Ö | i                        | ó  | Ö      | Ö | Ö                           | 5/11                |            |                                    |                |                |   |   |   |       |   |                |                     |

NOTES: 1. DDD or SSS -000 B - 001 C - 010 D - 011 E - 100 H - 101 L - 110 Memory - 111 A.

2. Two possible cycle times, (5/11) indicate instruction cycles dependent on condition flags.

## M6800 INSTRUCTION SET SUMMARY

|                         |              |          |      |     |          |      |     | DRES     |      |   | <b>E3</b>  |     |    | <del></del> |      |     | BOOLEAN/ARITHMETIC OPERATION                                                                  |    |   | . CO     |          | _          | $\overline{}$ |

|-------------------------|--------------|----------|------|-----|----------|------|-----|----------|------|---|------------|-----|----|-------------|------|-----|-----------------------------------------------------------------------------------------------|----|---|----------|----------|------------|---------------|

| ACCUMULATOR AN          | D MEMORY     |          | IMME | D   |          | DIRE | CT  |          | INDE | X |            | EXT | ID |             | INHE | R   | (All register labels                                                                          | 5  | 4 | 3        | 2        | 1          | 0             |

| OPERATIONS              | MNEMONIC     | OP       | ~    | #   | OP       | ~    | #   | OP       | ~    | # | OP         | ~   | #  | OP          | ~    | #   | refer to contents)                                                                            | Н  | L | N        | Z        | ٧          | C             |

| Add                     | ADDA         | 8B       | 2    | 2   | 9B       | 3    | 2   | АВ       | 5    | 2 | ВВ         | 4   | 3  |             |      |     | A + M → A                                                                                     | ‡  | • | ‡        | ‡        | <b>‡</b>   | ‡             |

| ı                       | ADDB         | СВ       | 2    | 2   | DB       | 3    | 2   | EB       | 5    | 2 | FB         | 4   | 3  |             |      |     | B + M → B                                                                                     | ‡  | • | \$       | ‡        | ‡          | ‡             |

| Add Acmitrs             | ABA          | ļ        |      |     |          |      |     |          |      |   |            |     |    | 18          | 2    | 1   | A + B → A                                                                                     | #  | • | ‡        | ‡        | ‡          | \$            |

| Add with Carry          | ADCA         | 89       | 2    | 2   | 99       | 3    | 2   | A9       | 5    | 2 | B9         | 4   | 3  |             |      |     | A + M + C → A                                                                                 | 1  | • | ‡        | ‡<br>‡   | ‡          | ‡<br>‡        |

|                         | ADCB         | C9       | 2    | 2   | D9       | 3    | 2   | E9       | 5    | 2 | F9         | 4   | 3  |             |      |     | B + M + C → B                                                                                 | 1  | • | ‡<br>‡   | ‡        | ‡<br>R     |               |

| And                     | ANDA         | 84       | 2    | 2   | 94       | 3    | 2   | A4<br>E4 | 5    | 2 | B4<br>F4   | 4   | 3  |             |      |     | $A \cdot M \rightarrow A$ $B \cdot M \rightarrow B$                                           |    | • | ‡        | ‡        | R          |               |

| . n:. +                 | ANDB         | C4       | 2    | 2   | D4<br>95 | 3    | 2   | A5       | 5    | 2 | B5         | 4   | 3  |             |      |     | A • M                                                                                         |    | • | ‡        | ‡        | R          |               |

| Bit Test                | BITA<br>BITB | 85<br>C5 | 2 2  | 2   | D5       | 3    | 2   | E5       | 5    | 2 | F5         | 4   | 3  |             |      |     | B • M                                                                                         |    | • | ‡        | ‡        | R          |               |

| Clear                   | CLR          | "        | *    | `   |          | ľ    | _   | 6F       | 7    | 2 | 7F         | 6   | 3  | l           |      |     | 00 → M                                                                                        | •  | • | R        | s        | R          | R             |

| Cital                   | CLRA         | İ        |      |     |          |      |     |          |      |   |            |     |    | 4F          | 2    | 1   | 00 → A                                                                                        | •  | • | R        | s        | R          | R             |

|                         | CLRB         | ļ        |      |     |          |      |     | 1        |      |   |            |     |    | 5F          | 2    | 1   | 00 → B                                                                                        | •  | • | R        | S        | R          | R             |

| Compare                 | CMPA         | 81       | 2    | 2   | 91       | 3    | 2   | A1       | 5    | 2 | В1         | 4   | 3  |             |      |     | A – M                                                                                         | •  | • | ‡        | \$       | ‡          | 1             |

|                         | CMPB         | C1       | 2    | 2   | D1       | 3    | 2   | E1       | 5    | 2 | F1         | 4   | 3  |             |      |     | B – M                                                                                         | •  | • | <b>‡</b> | <b>‡</b> | \$         | 1             |

| Compare Acmitrs         | CBA          | İ        |      |     |          |      |     | 1        |      |   |            |     |    | 11          | 2    | 1   | A - B                                                                                         | •  | • | \$       | ‡        | ‡          | 1             |

| Complement, 1's         | COM          |          | -    |     |          |      |     | 63       | 7    | 2 | 73         | 6   | 3  |             |      |     | M → M                                                                                         | •  | • | ‡        | ‡<br>•   | R          | S             |

|                         | COMA         |          |      |     | İ        |      |     |          |      |   |            |     |    | 43          | 2    | 1   | Ā→A<br>Ā · · · ·                                                                              | •  | • | ‡<br>‡   | ‡<br>‡   | R          | S             |

|                         | COMB         |          |      |     |          |      |     |          |      |   |            |     |    | 53          | 2    | 1   | $\overline{B} \rightarrow B$<br>$00 - M \rightarrow M$                                        | •  | • | ‡        | 1        | 0          |               |

| Complement, 2's         | NEG          |          |      |     |          |      |     | 60       | 7    | 2 | 70         | 6   | 3  | 40          | 2    | 1   | 00 - A → A                                                                                    |    | • | ‡        | 1        | 0          |               |

| (Negate)                | NEGA         |          |      |     |          |      |     |          |      |   |            |     |    | 50          | 2    | 1   | 00 - B → B                                                                                    |    |   | t        | 1        | 0          |               |

|                         | NEGB         |          |      |     | ľ        |      |     | İ        |      |   |            |     |    |             |      | ļ   | Converts Binary Add. of BCD Characters                                                        | 1_ |   |          | ‡        | ‡          | 3             |

| Decimal Adjust, A       | DAA          |          |      |     |          |      |     |          |      |   |            |     |    | 19          | 2    | 1   | into BCD Format                                                                               | •  | • | 1        |          |            | 9             |

| Decrement               | DEC          |          |      |     |          |      |     | 6A       | 7    | 2 | 7A         | 6   | 3  |             | ļ    |     | $M-1 \rightarrow M$                                                                           | •  | • | 1        | 1        | <b>(4)</b> | •             |

|                         | DECA         |          |      |     |          |      |     |          |      |   |            |     |    | 4A          | 2    | 1   | A – 1 → A                                                                                     | •  | • | ‡        | ‡        | <b>(4)</b> | •             |

|                         | DECB         |          |      |     |          |      |     |          | İ    |   |            |     |    | 5A          | 2    | 1   | B - 1 → B                                                                                     | •  | • | ‡        | ‡        | <b>4</b>   | •             |

| Exclusive OR            | EORA         | 88       | 2    | 2   | 98       | 3    | 2   | A8       | 5    | 2 | B8         | 4   | 3  |             | ł    | ļ   | $A \oplus M \rightarrow A$                                                                    | •  | • | ‡        | ‡<br>‡   | R          |               |

|                         | EORB         | C8       | 2    | 2   | D8       | 3    | 2   | E8       | 5    | 2 | F8         | 4   | 3  |             |      |     | $B \oplus M \rightarrow B$                                                                    | •  | • | ‡        | ‡        | 5          |               |

| Increment               | INC          |          | 1    |     |          |      |     | 6C       | 7    | 2 | 7C         | 6   | 3  | 4.0         | ١,   | 1   | $ \begin{array}{c} M+1 \to M \\ A+1 \to A \end{array} $                                       |    |   | 1        | <b>‡</b> | (3)        |               |

|                         | INCA         | 1        |      |     |          |      |     |          | ł    |   |            |     |    | 4C<br>5C    | 2 2  | 1   | B +1→B                                                                                        |    | • | t        | ‡        | (3)        |               |

|                         | INCB         | 00       | 1,   | ,   | 96       | 3    | 2   | A6       | 5    | 2 | В6         | 4   | 3  | 1 30        | 1    | l ' | M→A                                                                                           | •  | • | 1        | ‡        | R          | •             |

| Load Acmitr             | LDAA         | 86<br>C6 | 2 2  | 2 2 | D6       | 3    | 2   | E6       | 5    | 2 | F6         | 4   | 3  |             | ł    |     | M→B                                                                                           | •  | • | t        | 1        | R          | •             |

| Or, Inclusive           | LDAB<br>Oraa | 8A       | 2    | 2   | 9A       | 3    | 2   | AA       | 5    | 2 | ВА         | 4   | 3  |             |      | ł   | A + M → A                                                                                     | •  | • | ‡        | Į į      | R          | •             |

| OI, IIICIUSIVE          | ORAB         | CA       | 2    | 2   | DA       | 3    | 2   | EA       | 5    | 2 | FA         | 4   | 3  |             |      |     | B <b>+</b> M → B                                                                              | •  | • | \$       | \$       | R          | •             |

| Push Data               | PSHA         |          |      |     |          |      |     |          | 1    |   |            | ļ   |    | 36          | 4    | 1   | $A \rightarrow M_{SP}, SP-1 \rightarrow SP$                                                   | •  | • | •        | •        | •          | •             |

|                         | PSHB         |          |      |     | l        |      |     | 1        |      |   |            | 1   |    | 37          | 4    | 1   | $B \rightarrow M_{SP}, SP-1 \rightarrow SP$                                                   | •  | • | •        | •        | •          | •             |

| Pull Data               | PULA         |          |      |     |          |      |     | l        |      |   |            |     |    | 32          | 4    | 1   | SP + 1 → SP, M <sub>SP</sub> → A                                                              | •  | • | •        | •        | •          | •             |

|                         | PULB         | 1        |      |     |          |      |     |          |      |   |            | ١.  |    | 33          | 4    | 1   | $SP + 1 \rightarrow SP, M_{SP} \rightarrow B$                                                 | •  | • | •        | ‡        | •          | 1             |

| Rotate Left             | ROL          |          |      |     |          |      |     | 69       | 7    | 2 | 79         | 6   | 3  |             | ١.   | ١.  | M CO COUNTY                                                                                   |    | • | ‡<br>‡   | 1        | (6)<br>(6) | 1             |

|                         | ROLA         |          | l    |     |          |      |     | ļ        | ĺ    |   |            |     |    | 49          | 2    | 1   | $ \begin{bmatrix} A \\ B \end{bmatrix} $ $ \begin{bmatrix} C \\ b_7 \\ \hline \end{bmatrix} $ |    | • | 1        | 1        | 6          | 1             |

|                         | ROLB         |          |      |     |          |      |     | 66       | 7    | 2 | 76         | 6   | 3  | 59          | 2    | '   | M)                                                                                            |    | • | ‡        | 1        | 6          | 1             |

| Rotate Right            | ROR          |          | 1    | ļ   |          |      |     | 00       | '    | ' | /"         | "   | ľ  | 46          | 2    | 1   | A GO A COLUMN                                                                                 | •  | • | 1        | 1        | 6          | 1             |

|                         | RORB         |          |      |     | i        |      |     |          |      |   |            |     |    | 56          | 2    | 1   | $\begin{bmatrix} \overline{C} & \overline{b_7} \rightarrow b_0 \end{bmatrix}$                 | •  | • | 1        | ‡        | 6          |               |

| Shift Left, Arithmetic  | ASL          |          |      |     |          |      |     | 68       | 7    | 2 | 78         | 6   | 3  |             |      |     | M) ←                                                                                          | •  | • | 1        | ‡        | 6          | 1             |

| Sint Cert, Arttimetic   | ASLA         |          |      |     |          |      |     |          |      |   |            |     |    | 48          | 2    | 1   | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                         | •  | • | <b>‡</b> | \$       | 6          |               |

|                         | ASLB         |          |      |     |          |      |     | 1        |      |   |            |     |    | 58          | 2    | 1   | B J C 57 56                                                                                   | •  | • | 1        | \$       | 6          |               |

| Shift Right, Arithmetic | ASR          | 1        |      |     | 1        |      |     | 67       | 7    | 2 | 77         | 6   | 3  |             |      |     | M ]                                                                                           | •  | • | 1        | 1        | <b>(</b>   | 1             |