#### **HP 64774**

# 29000/29050 Emulator

# **PC Interface User's Guide**

HP Part No. 64774-97010 Printed in U.S.A. June 1992

**Edition 4**

#### **Notice**

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

© Copyright 1990-1992, Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

29K, ADAPT29K, Am29000, Am29027, and Am29050 are trademarks of Advanced Micro Devices, Inc.

Advancelink, Vectra, and HP are trademarks of Hewlett-Packard Company.

IBM and PC AT are registered trademarks of International Business Machines Corporation.

MS-DOS is a trademark of Microsoft Corporation.

UNIX is a registered trademark of UNIX System Laboratories Inc. in the U.S.A. and other countries.

Hewlett-Packard Company P.O. Box 2197 1900 Garden of the Gods Road Colorado Springs, CO 80901-2197, U.S.A.

**RESTRICTED RIGHTS LEGEND** Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (C) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227-7013. Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304

### **Printing History**

New editions are complete revisions of the manual. The date on the title page changes only when a new edition is published.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual was issued. Many product updates and fixes do not require manual changes, and manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual revisions.

| Edition 1 | 64774-97002, June 1990   |

|-----------|--------------------------|

| Edition 2 | 64774-97004, August 1990 |

| Edition 3 | 64774-97007, May 1991    |

Edition 4 64774-97010, June 1992

# **Using this Manual**

This manual shows you how to use the HP 64774 29000/29050 emulator with the PC Interface.

#### This manual:

- Lists the features of the 29000/29050 emulator.

- Shows you how to use emulation commands.

- Describes the target system design considerations that you must make when using the 29000/29050 emulator.

- Shows you how to connect the emulator to the target system.

- Shows you how to configure the emulator for your development needs.

This manual does not show you how to use every PC Interface command and option. This is done in the *HP 64700-Series Emulators PC Interface Reference*.

### **Organization**

- **Chapter 1** Introduction. This chapter describes the emulator functions and lists its basic features.

- **Chapter 2** Getting Started. This chapter shows you how to use emulation commands to view the execution of a sample program.

- **Chapter 3** Using the Emulator The Basics. This chapter describes target system design considerations that you must make when using the 29000/29050 emulator. It also shows you how to connect the emulator to the target system.

- **Chapter 4** Using the Emulator In Depth. This chapter describes some of the emulation features in more detail. Topics include the memory mapper and emulation memory, and coordinated measurements.

- **Chapter 5 Configuring the Emulator**. This chapter describes the options available for configuring the 29000/29050 emulator. It also describes storing and loading the emulator configuration.

- **Appendix A** Using the HP 64000 Reader. This appendix describes the HP 64000 reader.

- **Appendix B** Using the IEEE-695 Reader. This appendix describes the IEEE-695 reader.

# **Contents**

| 1 | Introduction to the 29000/29050 Emulator           |

|---|----------------------------------------------------|

|   | Purpose of the Emulator                            |

|   | Description                                        |

|   | Features of the 29000/29050 Emulator               |

|   | Full-Featured Operation at 25 MHz1-4               |

|   | Active-Probe Technology                            |

|   | Unbuffered Instruction and Data Busses 1-5         |

|   | Memory Mapper Bypass Mode                          |

|   | Single-Step and Disassembly of Instruction Bus 1-5 |

|   | Product Upgrades                                   |

|   | Emulation Memory                                   |

|   | Emulation Memory Size                              |

|   | Independent Banks of Emulation Memory 1-6          |

|   | Memory Mapping                                     |

|   | Fast Upload/Download with RS-422 Card 1-7          |

|   | Coverage Measurements                              |

|   | Analysis                                           |

|   | Floating Point Format Displays                     |

|   | Register Display and Modification                  |

|   | Breakpoints                                        |

|   | Reset Support                                      |

|   | Real-Time Execution                                |

| 2 | Getting Started                                    |

|   | Introduction                                       |

|   | Before You Begin                                   |

|   | Prerequisites                                      |

|   | A Look at the Sample Program                       |

|   | Data Declarations                                  |

|   | Reading Input                                      |

|   | Processing Commands                                |

|   | The Destination Area                               |

|   | Assembling the Sample Program                      |

|   | Linking the Sample Program                         |

|   |                                                    |

Contents-1

| Converting Absolute File Format                       |

|-------------------------------------------------------|

| Starting the 29000/29050 PC Interface                 |

| Selecting PC Interface Commands                       |

| Emulator Status                                       |

| Mapping Memory                                        |

| Which Memory Locations Should Be Mapped? 2-10         |

| Loading Programs into Memory                          |

| Using Symbols                                         |

| IEEE-695 or HP 64000 Format Symbols 2-15              |

| Other File Formats                                    |

| Loading Global Symbols 2-16                           |

| Displaying Global Symbols                             |

| Displaying Local Symbols 2-17                         |

| Transferring Symbols to the Emulator 2-18             |

| Removing Symbols from the Emulator 2-18               |

| Displaying Memory in Mnemonic Format 2-19             |

| Stepping Through the Program                          |

| Specifying a Step Count                               |

| Modifying Memory                                      |

| Running the Program                                   |

| Searching Memory for Data                             |

| Breaking into the Monitor                             |

| Using Breakpoints                                     |

| Defining a Breakpoint                                 |

| Displaying Breakpoints                                |

| Setting a Breakpoint                                  |

| Clearing a Breakpoint                                 |

| Using the Analyzer                                    |

| Predefined Trace Labels                               |

| Predefined Status Equates                             |

| Resetting the Analysis Specification 2-31             |

| Specifying a Simple Trigger                           |

| Starting the Trace                                    |

| Displaying the Trace                                  |

| Switching the Analysis Mode at the Trigger Point 2-37 |

| Modifying the General Emulator Configuration 2-37     |

| Modifying the Trigger Configuration 2-38              |

| Restarting the Trace                                  |

| Changing the Trace Display Format 2-40                |

| For a Complete Description 2-41                       |

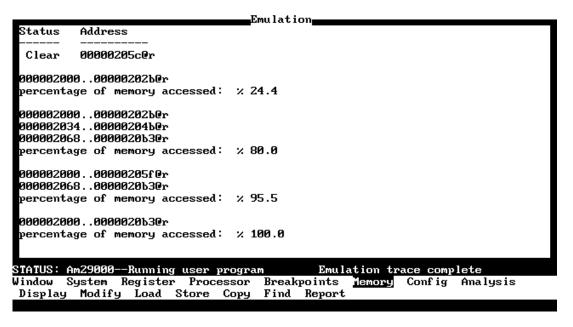

| Testing for Coverage                                  |

|          |   | Copying Memory                                                                                                                                                                                                                                                                                                                                                          | . 2-44                                                                            |

|----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|          |   | Resetting the Emulator                                                                                                                                                                                                                                                                                                                                                  | . 2-44                                                                            |

|          |   | Exiting the PC Interface                                                                                                                                                                                                                                                                                                                                                | . 2-45                                                                            |

|          | 3 | Using the Emulator — The Basics                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

|          |   | Target System Design Considerations                                                                                                                                                                                                                                                                                                                                     | 3-1                                                                               |

|          |   | Access for Emulator Probe                                                                                                                                                                                                                                                                                                                                               | 3-1                                                                               |

|          |   | Probe Power Requirements                                                                                                                                                                                                                                                                                                                                                | 3-1                                                                               |

|          |   | Probe Cooling                                                                                                                                                                                                                                                                                                                                                           | 3-1                                                                               |

|          |   | Disable Target Data Bus Buffers                                                                                                                                                                                                                                                                                                                                         | 3-1                                                                               |

|          |   | When Using Emulation Memory                                                                                                                                                                                                                                                                                                                                             | 3-3                                                                               |

|          |   | When Not Using Emulation Memory                                                                                                                                                                                                                                                                                                                                         | 3-5                                                                               |

|          |   | Processor Signal Considerations                                                                                                                                                                                                                                                                                                                                         | 3-5                                                                               |

|          |   | WARN Line                                                                                                                                                                                                                                                                                                                                                               | 3-5                                                                               |

|          |   | Control Lines Intercepted                                                                                                                                                                                                                                                                                                                                               | 3-5                                                                               |

|          |   | SYSCLK                                                                                                                                                                                                                                                                                                                                                                  | 3-5                                                                               |

|          |   | Other Signals                                                                                                                                                                                                                                                                                                                                                           | 3-6                                                                               |

|          |   | Effects of Using Emulation Memory                                                                                                                                                                                                                                                                                                                                       |                                                                                   |

|          |   | Effects of the Background Monitor                                                                                                                                                                                                                                                                                                                                       |                                                                                   |

| ٨        |   | Memory Accesses                                                                                                                                                                                                                                                                                                                                                         | 3-7                                                                               |

|          |   |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

| <u> </u> |   | Plugging the Emulator into a Target System                                                                                                                                                                                                                                                                                                                              | 3-7                                                                               |

| <u> </u> | 4 | Plugging the Emulator into a Target System                                                                                                                                                                                                                                                                                                                              | 3-7                                                                               |

| <u> </u> | 4 |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

| <u> </u> | 4 | Using the Emulator — In Depth                                                                                                                                                                                                                                                                                                                                           | 4-1                                                                               |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1                                                                        |

| ∠!\      | 4 | Using the Emulator — In Depth  Introduction                                                                                                                                                                                                                                                                                                                             | 4-1<br>4-1<br>4-2                                                                 |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1<br>4-2<br>4-3                                                          |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1<br>4-2<br>4-3<br>4-3                                                   |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-5                                            |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5                                     |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5<br>4-5                                     |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction                                                                                                                                                                                                                                                                                                                              | 4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5<br>4-6                                     |

| <u> </u> | 4 | Using the Emulator — In Depth Introduction Prerequisites Mapping Memory Address Ranges Address Space Designators Types of Memory Attributes Emulation Memory Available Emulation Memory Attributes Overlaying Ranges in Emulation Memory. Displaying Overlaid Ranges.                                                                                                   | 4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5<br>4-6<br>4-6                              |

| <u> </u> | 4 | Using the Emulator — In Depth  Introduction                                                                                                                                                                                                                                                                                                                             | 4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-8         |

| <u> </u> | 4 | Using the Emulator — In Depth  Introduction                                                                                                                                                                                                                                                                                                                             | 4-1<br>4-2<br>4-3<br>4-3<br>4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-8                |

| <u> </u> | 4 | Using the Emulator — In Depth  Introduction Prerequisites Mapping Memory Address Ranges Address Space Designators Types of Memory Attributes Emulation Memory Available Emulation Memory Attributes Overlaying Ranges in Emulation Memory. Displaying Overlaid Ranges. Target Memory Attributes Ranges with Different I-bus and D-bus Addresses. Access Mode Attributes | 4-1<br>4-2<br>4-3<br>4-5<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9                       |

| <u> </u> | 4 | Using the Emulator — In Depth  Introduction                                                                                                                                                                                                                                                                                                                             | 4-1<br>4-2<br>4-3<br>4-5<br>4-5<br>4-6<br>4-6<br>4-8<br>4-9<br>4-10               |

| <u> </u> | 4 | Using the Emulator — In Depth  Introduction Prerequisites Mapping Memory Address Ranges Address Space Designators Types of Memory Attributes Emulation Memory Available Emulation Memory Attributes Overlaying Ranges in Emulation Memory. Displaying Overlaid Ranges. Target Memory Attributes Ranges with Different I-bus and D-bus Addresses. Access Mode Attributes | 4-1<br>4-2<br>4-3<br>4-5<br>4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10 |

|   | Register Names and Classes                                |

|---|-----------------------------------------------------------|

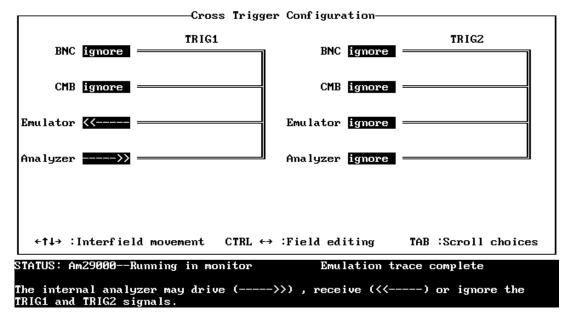

|   | Making Coordinated Measurements 4-16                      |

|   | CMB Signals                                               |

|   | Running the Emulator at /EXECUTE 4-17                     |

|   | Using the Analyzer Trigger to Break into the Monitor 4-17 |

| 5 | Configuring the Emulator                                  |

|   | Introduction                                              |

|   | Emulator Speed Configuration                              |

|   | Clock Speed                                               |

|   | Emulation Memory                                          |

|   | Clocks for Emulation Memory                               |

|   | Summary of Configuration Items Related to SYSCLK 5-5      |

|   | Clock Speed and the Analyzer 5-6                          |

|   | Number of Wait States for Emulation Memory 5-8            |

|   | Burst Mode                                                |

|   | Simple Mode                                               |

|   | Wait State Summary                                        |

|   | Real-Time Mode                                            |

|   | Emulation Memory Configuration 5-11                       |

|   | Primary Bus for Emulation Memory 5-11                     |

|   | Lock Emulation Ready for Access Type 5-11                 |

|   | Analysis Mode Configuration 5-12                          |

|   | Analysis Mode                                             |

|   | Analysis Switching Signal 5-13                            |

|   | Emulator Break Configuration 5-14                         |

|   | Software Breakpoints                                      |

|   | Break on Write to ROM 5-14                                |

|   | Break on IERR or DERR Signal 5-15                         |

|   | Break on WARN Signal 5-15                                 |

|   | General Emulator Configuration 5-15                       |

|   | Use Coprocessor                                           |

|   | Byte Ordering for Memory and I/O Ports 5-16               |

|   | Force Simple Mode                                         |

|   | Access Width                                              |

|   | Default Address Space                                     |

|   | CMB Interaction                                           |

|   | Storing an Emulator Configuration 5-19                    |

|   | Loading an Emulator Configuration 5-19                    |

| A | Using the HP 64000 Reader                           |

|---|-----------------------------------------------------|

|   | What the Reader Does                                |

|   | The Absolute File                                   |

|   | The ASCII Symbol File                               |

|   | Location of the HP 64000 Reader Program             |

|   | Using the Reader from MS-DOS                        |

|   | Using the Reader from the PC Interface              |

|   | If the Reader Won't Run                             |

|   | Including RHP64000 in a Make File                   |

| В | Using the IEEE-695 Reader                           |

|   | What the Reader Does                                |

|   | The Absolute File                                   |

|   | The ASCII Symbol File                               |

|   | Location of the IEEE-695 Reader Program             |

|   | Using the IEEE-695 Reader from MS-DOS               |

|   | Using the IEEE-695 Reader from the PC Interface B-4 |

|   | If the IEEE-695 Reader Won't Run B-6                |

|   | Including RIEEE695 in a Make File                   |

|   |                                                     |

Index

# Illustrations

| Figure 1-1. The HP 64774 Emulator for the 29000/29050 1-2 |

|-----------------------------------------------------------|

| Figure 1-2. 29000/29050 Probe Plugged into Harbor Box 1-3 |

| Figure 2-1. Sample Program Listing                        |

| Figure 2-2. Linker Load Map for the Sample Program 2-14   |

| Figure 2-3. Symbol Text File for the Sample Program 2-22  |

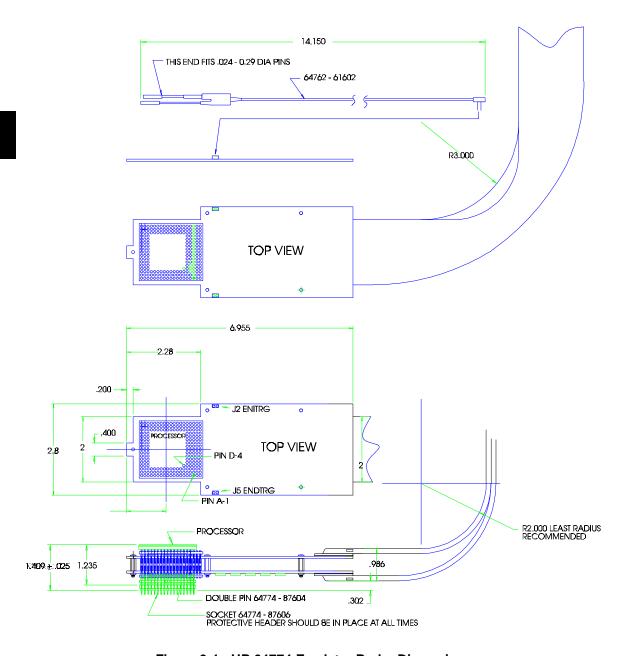

| Figure 3-1. HP 64774 Emulator Probe Dimensions            |

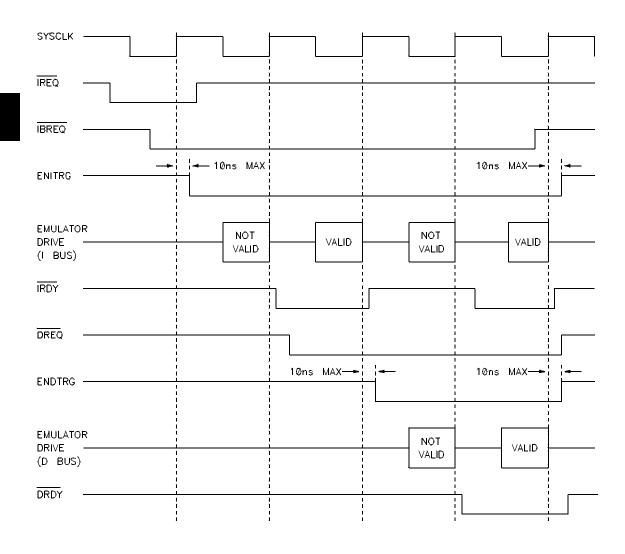

| Figure 3-2. ENITRG and ENDTRG Timing                      |

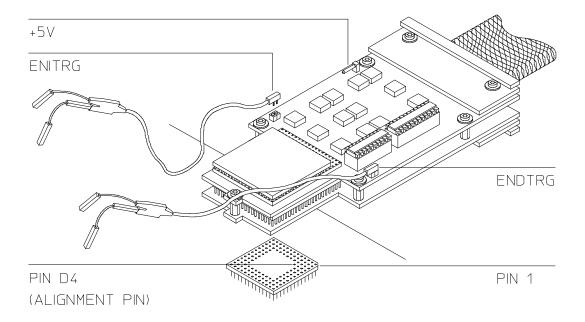

| Figure 3-3. Plugging into a Target System                 |

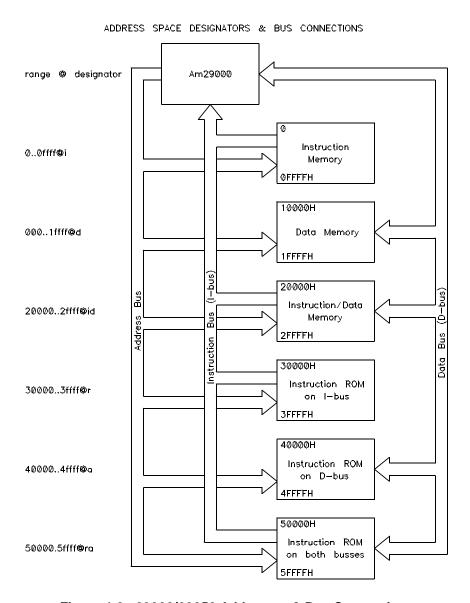

| Figure 4-1. Addr. Space Designators & Bus Connections 4-4 |

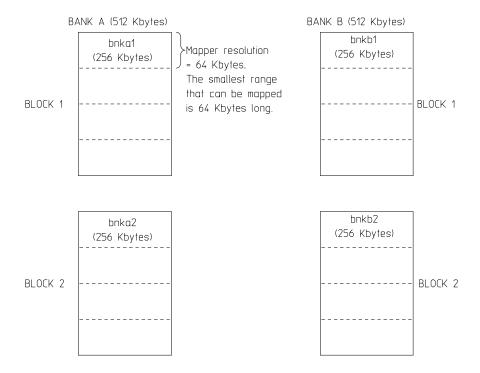

| Figure 4-2. Emulation Memory Example                      |

# **Tables**

| Table 2-1. | Trace Signal Assignments               | 2-37  |

|------------|----------------------------------------|-------|

| Table 2-2. | Predefined Equates for Analyzer Labels | 2-39  |

| Table 2-3. | Trace Mnemonics                        | 2-43  |

| Table 5-1. | SYSCLK Related Configuration Settings  | . 5-5 |

| Table 5-2. | Wait State Summary                     | . 5-8 |

6-Contents

### Introduction to the 29000/29050 Emulator

### Purpose of the Emulator

The HP 64774 29000/29050 emulator is designed to replace the Am29000/Am29050 microprocessor in your target system to help you integrate target system software and hardware. The emulator acts like the processor that it replaces and gives you information about the operation of the processor. You can control target system execution and view or modify the contents of processor registers, target system memory, and I/O resources.

### **Description**

The HP 64774 emulator supports the Am29000 and Am29050 microprocessors. The HP 64774 is a self-contained emulation and analysis system that can contain up to 4 Mbytes of emulation memory.

#### Communications

- \* RS-232/RS-422 Port A (connects to host computer or terminal)

- \* RS-232 Port B

- \* Coordinated Measurement Bus

- \* BNC Connector

- Emulator (contains):

\* Up to 4M of Emulation Memory

- \* Internal Analyzer

- \* System Controller

- \* Power Supply

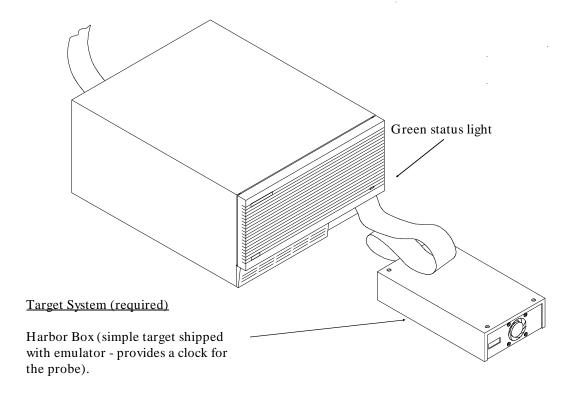

Figure 1-1. The HP 64774 Emulator for the 29000/29050

#### 1-2 Introduction

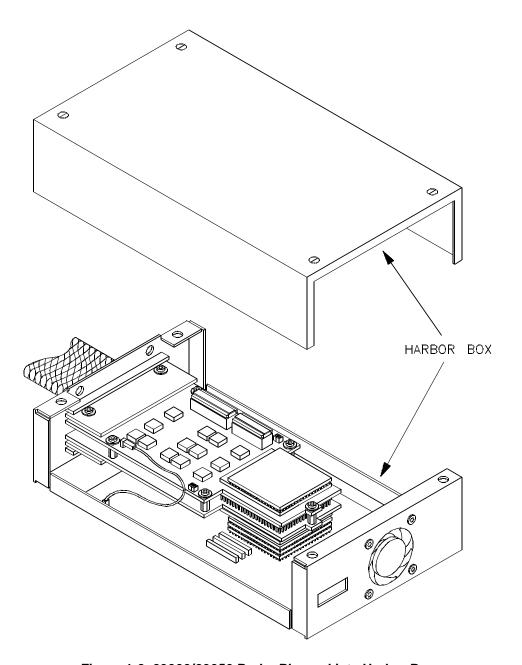

Figure 1-2. 29000/29050 Probe Plugged into Harbor Box

Introduction 1-3

# Features of the 29000/29050 Emulator

This section introduces the features of the HP  $64774\ 29000/29050$  emulator.

# Full-Featured Operation at 25 MHz

**Note**

The 29000/29050 emulator can execute in a target system at full clock speed (33 MHz); however, the analyzer may provide incorrect data above 25 MHz. As a result, Hewlett-Packard only supports operation of the HP 64774 emulator with analysis at clock speeds up to 25 MHz.

Operation of the emulator at high clock speeds is achieved with:

- Active-probe technology.

- Unbuffered instruction and data busses.

- A mode that bypasses the memory mapper.

#### **Active-Probe Technology**

Active-probe technology allows the emulator to closely imitate the electrical characteristics of the microprocessor, avoiding the timing problems that can occur with passive probes.

You need a target system clock to use the emulator. The emulator is shipped with a "harbor box" assembly around the active probe connector, which provides the target system clock when you are operating the emulator out-of-circuit. It also suppresses radio frequency interference (RFI), and cools the processor in the probe.

#### **Unbuffered Instruction and Data Busses**

The instruction and data busses at the target system are unbuffered to achieve high-speed emulator operation in the target system. The emulator provides control signals to the target system to tell the target system data bus buffers when one or both of the busses must be tristated.

#### **Memory Mapper Bypass Mode**

Memory mapper circuitry affects signal timing. To allow the processor to execute in target memory above 25 MHz without wait states, the emulator has a mode that bypasses the mapper circuitry. (No emulation memory can be used in the bypass mode.) In this mode, the emulator must execute out of target memory.

Because large amounts of emulation memory cannot be put in the probe, and because the probe cabling affects timing, wait-states are generated when executing out of emulation memory.

#### Single-Step and Disassembly of Instruction Bus

You can direct the emulation processor to execute a single instruction or a specified number of instructions.

While the 29000/29050 processor will fetch instructions from memory connected only to its I-bus, it cannot explicitly read it. However, the HP 64774 emulator has circuitry to read this memory so that it can both single-step and disassemble instructions without a D-bus connection.

#### **Product Upgrades**

Because the HP 64774 contains programmable parts, you can reprogram the emulator firmware without disassembling the emulator. This means that you can update product firmware without having to call an HP field representative to your site.

#### **Emulation Memory**

Emulation memory is multi-ported memory. This allows the emulator to run in real-time while you enter emulation commands that access emulation memory.

#### **Emulation Memory Size**

Emulation memory is available in 0.5 Mbyte or 2 Mbyte block with the HP 64774Y 0.5 Mbyte 29000/29050 Emulation Memory Module or HP 64774Z 2 Mbyte 29000/29050 Emulation Memory Module. Zero, one, or two of either module may be plugged into the 29000/29050 emulator card. The emulator supports the following configurations:

0.0 M bytes 0.5 M bytes 1.0 M bytes 2.0 M bytes

2.0 M bytes

2.5 M bytes

4.0 M bytes

Memory in the 2 Mbyte memory module has a slower access time (35 ns) than memory in the 0.5 Mbyte memory module (25 ns). When you mix these modules, the emulator treats both modules as the slower memory.

You can see how much memory is installed in your HP 64774 by executing the Terminal Interface **map** command.

#### **Independent Banks of Emulation Memory**

If the emulator contains two banks of emulation memory, code space may be mapped in one bank and data space in the other. This allows simultaneous fetching of both instruction and data bus information - eliminating the need for instruction/data bus arbitration that might affect emulator performance.

#### **Memory Mapping**

You can map up to 15 memory ranges. Mapped ranges must be at least 64 Kbytes long. You can characterize memory ranges as emulation RAM or ROM, target system RAM or ROM, or as guarded memory. Additionally, you must select the bank and block of emulation memory into which the address range is mapped.

The emulator issues an error message and breaks execution into the monitor when guarded memory is accessed. Also, you can enable a break condition that causes emulator execution to break out of the user program (into the emulation monitor program) when writes to memory mapped as ROM occur.

#### Fast Upload/Download with RS-422 Card

The RS-422 capability of the emulator's A communication port and an RS-422 interface card on the host computer (for example, the HP 64037 for the PC) provide upload/download rates of up to 230.4K baud.

#### Coverage Measurements

Coverage memory is provided along with emulation memory. This memory allows you to make code coverage measurements, as well as measurements that determine maximum stack sizes.

#### **Analysis**

The analyzer supplied with the emulator, called the *emulation* analyzer, captures emulator bus cycle information and bus cycle states synchronously with the processor clock.

#### **Note**

No external analysis (capability to probe signals external to the emulator) is available with the HP 64774 emulator.

See the *HP 64700 Emulators PC Interface: Analyzer User's Guide* for a complete list of analyzer features.

# Floating Point Format Displays

The 29000/29050 emulator has commands that allow you to display memory and registers in floating point formats.

# Register Display and Modification

You can display or modify the contents of one or more registers in the 29000/29050. The register display command allows the display and modification of multiple registers. Also, the bit fields of various registers are labeled in the default display. An option allows you to display only the full hex value of the registers.

#### **Breakpoints**

You can set up the emulator/analyzer interaction so that when the analyzer finds a specific state, emulator execution will break out of the user program into the emulation monitor. These are called hardware breakpoints. Note that the analyzer monitors bus activity, which may not correspond to execution, because the 29000/29050 is a pipelined processor.

You can also define software breakpoints in your program. When you define a software breakpoint and the opcode at the breakpoint address is executed, the emulator breaks into background.

#### **Reset Support**

You can reset the emulator from the emulation system, or your target system can reset the emulation processor.

#### **Real-Time Execution**

Real-time operation means continuous execution of your program without interference from the emulator. Such interference occurs when the emulator temporarily breaks into the monitor so that it can access register contents or target system memory.

You can restrict the emulator to real-time execution. When the emulator is executing your program in real-time, commands that display or modify registers or target system memory are not allowed.

## **Getting Started**

#### Introduction

This chapter is a tutorial that shows how to use the HP 64774 29000/29050 emulator with the PC Interface.

This chapter will:

- Tell you what to do before you use the emulator in the tutorial examples.

- Describe the sample program used for the examples.

- Briefly describe how to enter PC Interface commands and how emulator status is displayed.

This chapter will show you how to:

- Start the PC Interface from the MS-DOS prompt.

- Define (map) emulation and target system memory.

- Load programs into emulation and target system memory.

- Enter emulation commands to view execution of the sample program.

The commands described in this chapter include: displaying and modifying memory, stepping, displaying registers, defining keystroke macros, searching memory, running, breaking, using breakpoints, tracing program execution, changing the trace format, copying memory, and testing coverage.

### **Before You Begin**

The examples in this chapter were performed with the 29000 the emulator plugged into the harbor box. Also, the emulator contained 0.5 Mbyte of emulation memory. Your emulator must have an emulation memory module to run the sample program.

#### **Prerequisites**

Before beginning the tutorial, you must do the following:

- 1. Connect the emulator to your computer. The *HP 64700* Series Emulators Installation Guide shows you how to do this.

- 2. Install the PC Interface software on your computer. Software installation instructions are shipped with the media containing the PC Interface software. The HP 64700 Emulators PC Interface Reference manual contains more information on the installation and setup of the PC Interface.

- 3. You should read and understand the concepts of emulation presented in the *Concepts of Emulation and Analysis* manual. Understanding these concepts may help you avoid problems later.

- 4. You should read the *HP 64700 Emulators PC Interface Reference* manual to learn general PC Interface operation. It contains information specific to the 29000/29050 emulator.

#### A Look at the Sample Program

Figure 2-1 shows the sample program used in this chapter. The program is a primitive command interpreter.

#### **Data Declarations**

The first two lines in the "cmd\_rdr.src" source file define the **Msgs**, **Init**, **Cmd\_Input**, and **Msg\_Dest** labels as global symbols.

Advanced Micro Devices, Inc. Am29000 Assembler - Version 2.0-5 Copyright (c) 1987, 1988 Microtec Research Inc. ALL RIGHTS RESERVED. Serial Number AS2002563

Advanced Micro Devices, Inc. ASM29K Assembler Rel. 2.0-5 Sat Mar 03 19:20:26 1990 Page 1

| Cmdline - \USR\C29K\BIN\AS29.EXE -l -fgosx cmd_rdr.src |                            |                                        |          |                                            |                              |                                         |

|--------------------------------------------------------|----------------------------|----------------------------------------|----------|--------------------------------------------|------------------------------|-----------------------------------------|

| 1<br>2<br>3                                            | Address                    |                                        |          |                                            | .global<br>.global           | <pre>Init,Msgs,Cmd_Input Msg_Dest</pre> |

| 4<br>5                                                 |                            |                                        |          | M                                          | .data                        |                                         |

| 6                                                      | 41<br>74                   | 6F 6D<br>6E 64<br>20 65<br>65 72<br>20 | 20<br>6E | Msgs:<br>Msg_A:                            | .ascii                       | "Command A entered "                    |

| 7<br>8                                                 | 42<br>6D                   | 6E 74<br>65 64<br>20 63<br>6D 61<br>20 | 20<br>6F | Msg_B:                                     | .align<br>.ascii             | 4<br>"Entered B command "               |

| 9                                                      | 43                         | 6E 76<br>69 64<br>6F 6D<br>6E 64       | 20<br>6D | Msg_I:                                     | .align<br>.ascii             | 4<br>"Invalid Command "                 |

| 11<br>12<br>13<br>14                                   |                            |                                        |          | End_Msgs:                                  | .align                       | 4                                       |

| 15<br>16                                               |                            |                                        |          | ;*****                                     | .text<br>******              | ******                                  |

| 17<br>18                                               |                            |                                        |          | ;* Clear previo                            |                              | *****                                   |

| 19                                                     | 00000000 03                |                                        |          | Init:                                      | const                        | gr65,0                                  |

| 20<br>21                                               | 00000004 03<br>00000008 02 | 00 40                                  | 00 R     |                                            | const<br>consth              | gr64,Cmd_Input<br>gr64,Cmd_Input        |

| 22<br>23                                               | 0000000C 1E                | 00 41                                  | 40       | ;******                                    | store<br>******              | 0,0,gr65,gr64<br>******                 |

| 24<br>25<br>26                                         |                            |                                        |          |                                            | , continue t                 | If no command has o scan for input.     |

| 27<br>28                                               | 00000010 16<br>00000014 61 |                                        |          | Scan:                                      | load<br>cpeq                 | 0,0,gr65,gr64<br>gr66,gr65,0            |

| 29                                                     | 00000011 01<br>00000018 AC |                                        |          |                                            | jmpt                         | gr66,Scan<br>*******                    |

| 30<br>31<br>32<br>33                                   |                            |                                        |          | <pre>;* A command ha ;* command A, c</pre> | s been enter<br>ommand B, or | ed. Check if it is                      |

| 34<br>35                                               | 0000001C 61<br>00000020 AC |                                        |          | Exe_Cmd:                                   | cpeq<br>jmpt                 | gr66,gr65,0x41<br>gr66,Cmd_A            |

Figure 2-1. Sample Program Listing

```

00000024 61 42 41 42

36

gr66,gr65,0x42

cpea

37

00000028 AC 00 42 08

gr66,Cmd_B

impt

38

0000002C 70 40 01 01

0x40,gr1,gr1; NOP

aseq

00000030 A0 00 00 0B

39

40

;* Command A is entered. gr65 = the number of

41

;* bytes in message A divided by 4.

;* gr66 = location of the message. Jump to the

42

43

44

45

46

00000034 03 00 41 04

Cmd_A:

const.

gr65,((Msg_B-Msg_A)/4)-1

47

00000038 03 00 42 00

const

gr66,Msg_A

48

0000003C 02 00 42 00

R

consth

gr66,Msg_A

49

00000040 A0 00 00 0A

jmp

Write_Msg

50

00000044 70 40 01 01

0x40,gr1,gr1; NOP

51

;* Command B is entered.

52

53

54

00000048 03 00 41 04

Cmd_B:

const

gr65,((Msg_I-Msg_B)/4)-1

55

0000004C 03 00 42 14

const

gr66, Msg_B

56

00000050 02 00 42 00

consth

gr66, Msg_B

57

00000054 A0 00 00 05

jmp

Write_Msg

00000058 70 40 01 01

0x40,gr1,gr1; NOP

aseq

;*****************************

59

;* An invalid command is entered.

60

; *************

61

const

gr65,((End_Msgs-Msg_I)/4)-1

62

0000005C 03 00 41 03

Cmd_I:

00000060 03 00 42 28

63

R

const

gr66,Msg_I

64

00000064 02 00 42 00

R

65

66

;* Message is written to the destination.

67

00000068 03 00 43 04

R Write_Msg:

const

gr67,Msg_Dest

68

69

0000006C 02 00 43 00

consth

gr67,Msg_Dest

70

00000070 CE 00 87 41

mtsr

cr,gr65

00000074 36 00 48 42

00000078 CE 00 87 41

loadm

71

72

0,0,gr72,gr66

mtsr

cr, gr65

0000007C 3E 00 48 43

73

74

75

;* The rest of the destination area is filled

76

77

78

00000080 03 00 40 00

gr64,0

const

79

00000084 03 00 42 24

const

gr66,Msg_Dest+0x20

80

00000088 02 00 42 00

R

consth

gr66,Msg_Dest+0x20

81

0000008C 15 41 41 01

add

gr65,gr65,1

82

00000090 81 41 41 02

sll

gr65,gr65,2

83

00000094 14 43 43 41

add

gr67,gr67,gr65

84

00000098 1E 00 40 43

Fill_Dest:

store

0,0,gr64,gr67

85

0000009C 15 43 43 04

add

gr67,gr67,4

86

000000A0 60 41 42 43

cpeq

gr65,gr66,gr67

87

000000A4 A4 FF 41 FD

gr65,Fill_Dest

jmpf

88

000000A8 70 40 01 01

89

;* Go back and scan for next command.

90

```

Figure 2-1. Sample Program Listing (Cont'd)

#### 2-4 Getting Started

```

92

000000AC A0 FF 00 D5

jmp

Init

93

000000B0 70 40 01 01

aseq

0x40,gr1,gr1; NOP

94

95

.bss

96

97

98

00000000

99

Cmd_Input: .block

4

100

;* Destination of the command messages.

101

102

00000004

103

Msg_Dest:

.block

0xfb

104

.end

```

Advanced Micro Devices, Inc. ASM29K Assembler Rel. 2.0-5 Sat Mar 03 19:20:26 1990 Page 4

```

Cross Reference

Label

Value

References

Cmd_A

.text:00000034

-46

-54

-62

.text:00000048

37

Cmd_B

Cmd_I .text:0000005C

Cmd_Input .bss:00000000

.text:0000005C

39

1 20

21

.data:00000038

-12

62

End_Msgs

.text:0000001C

-34

Exe_Cmd

Fill_Dest .text:00000098

-84

87

1 -19 92

-6 46 47 48

-8 46 54 55 56

2 68 69 79 80 -102

.text:00000000

Init

Msg_A

.data:00000000

.data:00000014

Msq B

Msg_Dest

.bss :00000004

.data:00000028

-10 54 62 63 64

Msa I

.data:00000000

-5

1 -5

-27 29

Msqs

.text:00000010

Scan

49 57 -68

Write_Msg .text:00000068

```

Figure 2-1. Sample Program Listing (Cont'd)

The ".data" area defines the messages used by the program to respond to various command inputs. These messages are labeled Msg\_A, Msg\_B, and Msg\_I.

#### **Reading Input**

The instructions that follow the **Read\_Cmd** label clear any random data or previous commands from the **Cmd\_Input** word. The **Scan** loop continually reads the **Cmd\_Input** word to see if a command is entered (a value other than 0H).

#### **Processing Commands**

When a command is entered, the instructions after **Exe\_Cmd** determine whether the command was "A", "B", or an invalid command.

If the command input word is "A" (ASCII 41H), execution jumps to the **Cmd\_A** label where the length of the "Command A entered" message is loaded into register gr65, the location of **Msg\_A** is loaded into register gr66, and execution is transferred to the instructions at **Write\_Msg**. Similar operations are performed when the command input word is "B" or when there is an invalid command.

The instructions at **Write\_Msg** load a word from the appropriate message location, store the word into the destination area, increment the source and destination addresses, decrement the message length counter, and perform these instructions again until all words are transferred.

After the message is written, the instructions at **Fill\_Dest** fill the remaining destination locations with zeros. (The destination area is 20H bytes long.) Then, the program returns to read the next command.

#### The Destination Area

The ".bss" area declares storage for the command input byte and the destination area.

#### Assembling the Sample Program

You can use several PC hosted software development tools to generate absolute files. However, your compiler/assembler/linker must be able to generate files in one of the following formats:

- IEEE-695 MUFOM (Microprocessor Universal Format for Object Modules).

- HP absolute (either with associated symbol files or just raw absolute file).

- Intel hexadecimal.

- Motorola S-records.

- Tektronix hexadecimal.

The sample program was written for and assembled with AMD's PC hosted assembler for the 29000/29050. The following command was used to assemble the sample program.

```

C> as29 -l -fgosx cmd_rdr.src > cmd_rdr.lis

<RETURN>

```

In addition to the assembler listing (cmd\_rdr.lis), the "cmd\_rdr.obj" relocatable file is created. Relocatable files are linked together to form the absolute file, which is loaded into the emulator.

# Linking the Sample Program

The linker command file (cmd\_rdr.lnk) shown in figure 2-2 and the following linker command were used to generate the absolute file.

```

C> ld29 -c cmd_rdr.lnk -o cmd_rdr.abs -m -e

Init > cmd_rdr.map <RETURN>

```

In addition to the linker load map listing (cmd\_rdr.map), the "cmd\_rdr.abs" absolute file is created. This file contains the COFF format absolute code.

ORDER .data=0x10000,.text=0x2000,.bss=0x20000 LOAD cmd\_rdr.obj

Figure 2-2. The "cmd\_rdr.lnk" Linker Command File

#### Converting Absolute File Format

Because the COFF absolute file format created by the "ld29" linker is not accepted by the HP 64774 emulator, the absolute file must be converted to a format that is acceptable. The AMD software development tools contain a utility that converts COFF format files. The following command uses this utility to create a Motorola S-record format absolute file.

C> coff2hex -m -o cmd\_rdr.hex cmd\_rdr.abs

<RETURN>

# Starting the 29000/29050 PC Interface

If you have set up the emulator device table and the **HPTABLES** shell environment variable as shown in the *HP 64700 Emulators PC Interface Reference*, you can start up the 29000/29050 PC Interface by entering the following command from the MS-DOS prompt:

C> pcam29k <emulname>

In the command above, **pcam29k** is the command to start the PC Interface; "< emulname>" is the logical emulator name given in the emulator device table.

The processor type in the emulator device table should be "am29000".

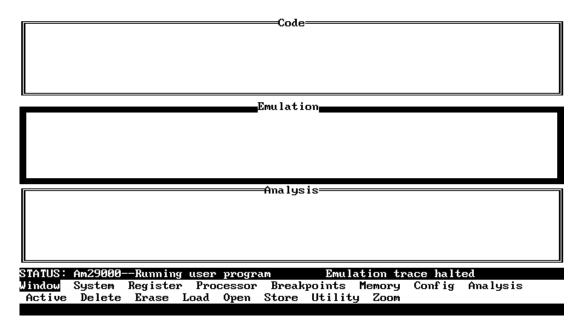

You should see the display shown in figure 2-3. If this command is not successful, you will see an error message and will return to the MS-DOS prompt.

# Selecting PC Interface Commands

You can select command options by either using the left and right arrow keys to highlight the option and press the < **Enter>** key, or you can type the first letter of that option. If you select the wrong option, you can press the < **ESC>** key to retrace up the command tree.

When a command option is highlighted, either the next level of options or a short message describing that option is shown on the bottom line of the display.

Figure 2-3. PC Interface Display

#### **Emulator Status**

The status of the emulator is shown on the line above the command options. The PC Interface periodically checks the status of the emulator and updates the status line. Error messages are saved in the "Error Log" window. Status messages include the following:

| Status Messages                 | Description of Message                                      |  |

|---------------------------------|-------------------------------------------------------------|--|

| Emulator in reset state         | The emulation processor is reset.                           |  |

| Running user program            | The emulator is running a program.                          |  |

| No target system clock          | The emulator is expecting, but not receiving, a clock from  |  |

|                                 | the target system.                                          |  |

| Monitor is accepting commands   | The monitor is allowing commands to be executed.            |  |

| No bus cycles                   | Activity on the bus cannot be processed.                    |  |

| Waiting for CMB to become ready | The emulator is waiting for a READY signal on the CMB.      |  |

| Processor halted                | The emulation processor was stopped.                        |  |

| Waiting for target reset        | The emulator is waiting for a reset from the target system. |  |

| Target system reset active      | A reset has been executed in the target system.             |  |

| Unknown state                   | The state of the emulation processor is unknown.            |  |

### **Mapping Memory**

The memory mapper tells the emulator how to access memory locations in a particular range.

- The emulator needs to know whether memory is located in the emulator or in the target system.

- The emulator also needs to know whether the memory is RAM or ROM, which locations of physical emulation memory are used for a particular address range, which ranges are overlaid, and whether word, half-word, or byte accesses should be used for particular ranges in target memory.

### Which Memory Locations Should Be Mapped?

Typically, assemblers generate relocatable files and linkers combine relocatable files to form the absolute file. The linker load map listing will show what memory locations your program will occupy in memory. Figure 2-4 shows an Advanced Micro Devices linker load map listing for the sample program.

```

Advanced Micro Devices, Inc. Am29000 Loader - Version 2.0-9

Copyright (c) 1987 - 1989 Microtec Research Inc. ALL RIGHTS RESERVED. Serial Number AS2002563

Advanced Micro Devices, Inc. ASM29K Linker Rel. 2.0-9

Sat Mar 03 19:20:29 1990

Command line: \USR\C29K\BIN\LD29.EXE -c cmd_rdr.lnk -o cmd_rdr.abs -m -e Init

ORDER .data=0x10000,.text=0x2000,.bss=0x20000

LOAD cmd_rdr.obj

OUTPUT MODULE NAME:

cmd_rdr.abs

OUTPUT MODULE FORMAT: ABSOLUTE

SECTION SUMMARY

SECTION

TYPE

START

SIZE

ALIGN

MODIILE

END

00002000 000020B3

000000B4 4 BYTES

00000038 8 BYTES

TEXT

cmd_rdr.obj

.text

00010000 00010037

.data

DATA

00000038

8 BYTES

cmd_rdr.obj

8 BYTES

.bss

BSS

00020000 000200FF

00000100

cmd_rdr.obj

```

Figure 2-4. Linker Load Map for the Sample Program

#### 2-10 Getting Started

| LOCAL SYMBOL TABLE                                                     |                                                            | DEBUG) - Special<br>ABSOLUTE) - Abso                                                                                                                                             | symbolic debugging symbol lute symbol                                                                                                                                                                                                                                                                       |  |  |

|------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL                                                                 | SECTION                                                    | VALUE                                                                                                                                                                            | MODULE                                                                                                                                                                                                                                                                                                      |  |  |

| .data .bss Write_Msg End_Msgs Scan Exe_Cmd Cmd_A Cmd_B Msg_I Fill_Dest | .text<br>.text<br>.data<br>.text<br>.text                  | 00000013<br>00002000<br>00010000<br>00020000<br>00002068<br>00010038<br>00002010<br>0000201C<br>00002034<br>00002048<br>00010028<br>00002098<br>00002098<br>00002098<br>00002098 | cmd_rdr.obj |  |  |

| GLOBAL SYMBOL                                                          | TABLE                                                      |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             |  |  |

|                                                                        |                                                            | VALUE                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                             |  |  |

| Init Msgs Cmd_Input Msg_Dest edata end etext                           | .text<br>.data<br>.bss<br>.bss<br>(ABSOLUTE)<br>(ABSOLUTE) | 00002000<br>00010000<br>00020000<br>00020004<br>00010038<br>00020100<br>000020B0                                                                                                 |                                                                                                                                                                                                                                                                                                             |  |  |

| CROSS REFERENCE TABLE * Defined Module                                 |                                                            |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             |  |  |

| SYMBOL                                                                 | SECTION                                                    | REFERENCED                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             |  |  |

| Init Msgs Cmd_Input Msg_Dest edata end etext                           | .text<br>.data<br>.bss<br>.bss<br>(ABSOLUTE)<br>(ABSOLUTE) | - cmd_rdr.obj<br>- cmd_rdr.obj<br>- cmd_rdr.obj<br>- cmd_rdr.obj<br>LINKER-DEFINED<br>LINKER-DEFINED<br>LINKER-DEFINED                                                           |                                                                                                                                                                                                                                                                                                             |  |  |

| START ADDRESS:                                                         | 00002000                                                   |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             |  |  |

Figure 2-4. Linker Load Map for Sample Program (Cont'd)

From the load map listing, you can see that the sample program occupies code segment locations in three address ranges. The ".text" area, which contains the opcodes and operands of the sample program, occupies locations 2000H through 20B3H. The ".data" area, which contains the ASCII values of the messages the program displays, occupies locations 10000H through 10037H. The ".bss" segment in the sample program, which contains the command input byte and the destination area, occupies locations 20000H through 200FFH.

The minimum size of a block of emulation memory is 64 Kbytes. When mapping memory, you can specify a range smaller than 64 Kbytes, but the mapper will automatically map the entire 64 Kbyte block in which that range resides.

Two mapper terms are specified for the example program. Since the program writes to the destination locations, the mapper block containing the destination locations should not be characterized as ROM memory.

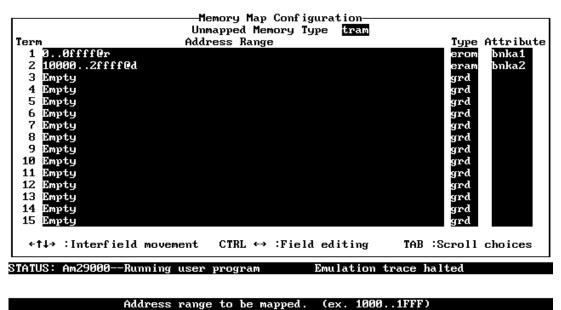

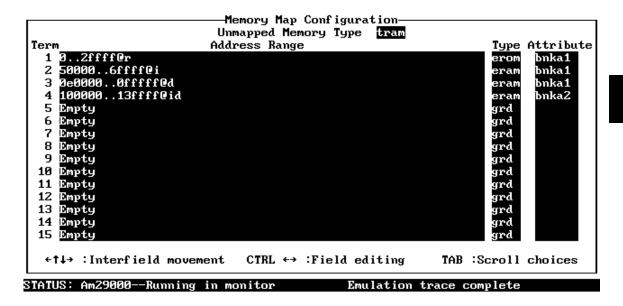

To map memory for the sample program, select:

```

Config Map Modify

```

Using the arrow keys, move the cursor to the "address range" field of term 1. Enter:

```

0..0ffff@r

```

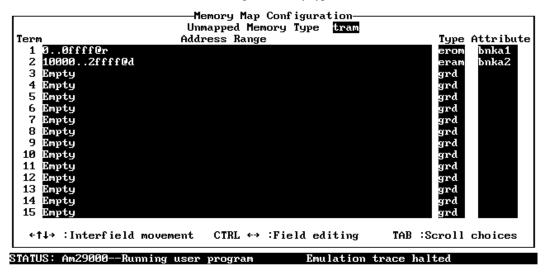

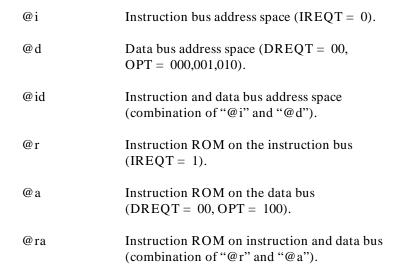

The "@r" appended to the address range above is an address space designator; it specifies that the range be mapped to instruction ROM address space. Address space designators are described in more detail in the chapter "Using the Emulator — In Depth".

Move the cursor to the "memory type" field of term 1, and press the < **Tab>** key to select the "erom" (emulation ROM) type. Move the cursor to the "attribute" field of term 1, and press the < **Tab>** key to select "bnka1". Move the cursor to the "address range" field of term 2, and enter:

```

10000..2ffff@d

```

The "@d" address space designator maps the range to data memory address space.

Move the cursor to the "memory type" field of term 2, and press the < **Tab>** key to select the "eram" (emulation RAM) type. Move the cursor to the "attribute" field of term 2, and press the < **Tab>** key to select "bnka2".

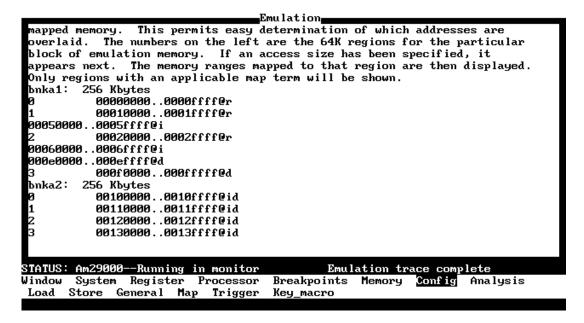

To save the memory map, use the **Enter>** key to exit the field in the lower right corner. (The **End>** key on Vectra keyboards moves the cursor directly to the last field.) Figure 2-5 shows the memory configuration display.

Figure 2-5. Memory Map Configuration

When mapping memory for your target system programs, you may want to map emulation memory locations containing programs and constants (locations which should not be written to) as ROM. This will prevent programs and constants from being written over accidentally, and will cause breaks when instructions attempt to do so.

For more information on the memory mapper and emulation memory, refer to the "Mapping Memory" section in the chapter "Using the Emulator — In Depth".

# **Loading Programs** into Memory

Because two address spaces were mapped (instruction ROM with @r, and data memory with @d), you must load the absolute file twice. First, load the instruction ROM address space by selecting:

Memory Load

Enter the format of your absolute file. The emulator accepts absolute files in the following formats:

- IEEE-695 MUFOM (Microprocessor Universal Format for Object Modules).

- HP absolute (either with associated symbol files or just raw absolute file).

- Intel hexadecimal.

- Motorola S-records.

- Tektronix hexadecimal.

The "cmd\_rdr.hex" absolute file is in Motorola S-record format, so use the < **Tab>** key to select "Motorola\_Hex".

The next field allows you to selectively load the portions of the absolute file which reside the following:

- emulation memory

- target system memory

- both emulation and target system memory

- background monitor

Because emulation memory is mapped for sample program locations, you can enter either "emulation" or "both".

Next, you select the address space designator for the load operation. You will load the sample program into instruction ROM address space with the "r" designator.

Finally, enter the name of your absolute file ("cmd\_rdr.hex" in this example) in the last field, and press < **Enter>** to start the memory download.

Now, to load the absolute file into data memory, select:

Memory Load

Use all the same options except for the address space designator. Move the cursor to the "address space designator" field and use the < Tab> key to select "d" for data memory designator.

Press the **< End>** key to move the cursor to the last field, and press **< Enter>** to start the memory download.

### **Using Symbols**

#### IEEE-695 or HP 64000 Format Symbols

Symbols are part of the IEEE-695 and HP 64000 file format definitions. That is, symbols can be contained in these file formats. When you load IEEE-695 or HP 64000 format files, the PC Interface uses a reader program to create files with the extensions ".HPA" and ".HPS" (whose base names are the same as the absolute file). The ".HPA" file is in a binary format that is compatible with the HP 64700-Series firmware. The ".HPS" file is an ASCII source file that contains the symbol to address mappings used by the PC Interface. See the appendices "U sing the HP 64000 Reader" and "U sing the IEEE-695 Reader" for more information.

#### Other File Formats

When your absolute file is not an IEEE-695 or HP 64000 format file, the PC Interface does not create ".HPA" or ".HPS" files. However, you can use an editor create a ".HPS" file using symbol information from the linker load map output listing. Figure 2-6 shows the ".HPS" file for the sample program.

#### Note

The format of a ".HPS" file requires

- module names to be preceded by a single space,

- symbols and addresses to be separated by a single < **Tab>** character, and

- the lines in the file that you will sort (you can use the MS-DOS sort command to do this).

```

{\tt cmd\_rdr}

00020000@d

Cmd_Input

00002000@r

Init

Msg_Dest

00020004@d

Msgs

00010000@d

cmd_rdr|Cmd_A 00002034@r

cmd_rdr | Cmd_B 00002048@r

cmd_rdr Cmd_I 0000205C@r

cmd_rdr End_Msgs

00010038@d

cmd_rdr Exe_Cmd

0000201C@r

cmd_rdr Fill_Dest

00002098@r

cmd_rdr Msg_A 00010000@d

cmd_rdr Msg_B 00010014@d

cmd_rdr Msg_I

00010028@d

cmd_rdr Scan

00002010@r

cmd_rdr Write_Msg

00002068@r

```

Figure 2-6. The "cmd\_rdr.hps" Symbol File

# Loading Global Symbols

When you load memory with IEEE-695 format absolute files, global symbols are automatically loaded.

When you load memory with non-IEEE-695 format absolute files and create the ".HPS" file, you must load the symbols in the ".HPS" file by selecting the following command:

```

System Symbols Global Load

```

Enter the name of the ".HPS" file, and press < **Enter>** to load the symbols.

# Displaying Global Symbols

After global symbols are loaded, both global and local symbols can be used when entering expressions. Global symbols are entered as they appear in the source file or in the global symbols display.

To display global symbols, select:

```

System Symbols Global Display

```

The symbols window automatically becomes active. You can press < CTRL> Z to zoom the window. The resulting display follows.

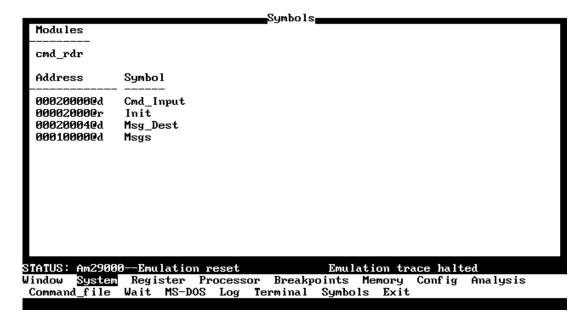

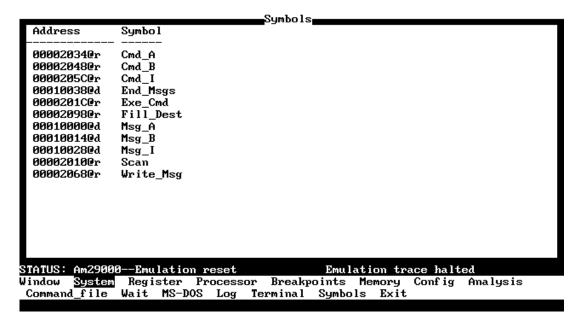

Figure 2-7. Global Symbols Display

# Displaying Local Symbols

To load and display local symbols, select:

System Symbols Local, Display

Enter the name of the module in which the local symbols appear (for example, "cmd\_rdr"). Press < **Enter>** . The resulting display follows.

After you load and display local symbols with the System Symbols Local command, you can use local symbols as they appear in the source file or local symbol display.

Figure 2-8. Local Symbols Display

# Transferring Symbols to the Emulator

Before you can view symbols in mnemonic memory and trace displays, you must transfer them to the emulator.

After global symbols are loaded, you can transfer them to the emulator by selecting:

System Symbols Global Transfer

To transfer local symbols for the module "cmd\_rdr" to the emulator, select:

System Symbols Local Transfer Group "cmd\_rdr"

#### **Removing Symbols from the Emulator**

If you transferred many symbols to the emulator, you can fill the memory used to store them. You can remove global and local symbols from the emulator by using the **R**emove option in place of the **T**ransfer option in the symbols commands.

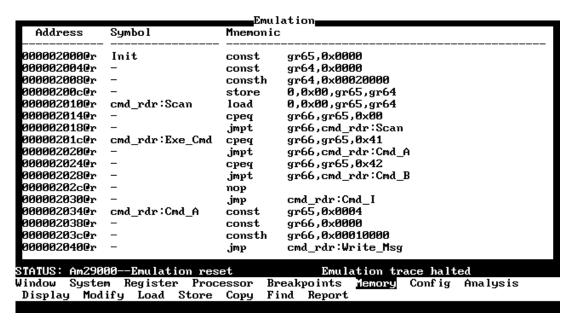

# Displaying Memory in Mnemonic Format

Once you have loaded a program into the emulator, you can verify that the program was loaded by displaying memory in mnemonic format. To do this, select:

Memory Display Mnemonic

Enter the address range **Init...** The two periods indicate you are specifying an address range. The range size is 128 bytes when no second address in the range is specified. The emulation window automatically becomes active. You can press < **CTRL> Z** to zoom the window and < **PgUp>** to see the beginning of the range.

As with any window, you can use the < PgUp> and < PgDn> keys to scroll the information in the window.

Figure 2-9. Memory Mnemonic Display

# Stepping Through the Program

The emulator allows you to execute one instruction or a number of instructions with the step command. To begin stepping through the sample program, select:

Processor Step Address

Enter a step count of 1, enter the symbol "Init" (defined as a global symbol in the source file), and press < **Enter>** to step from the program's first address, 2000H in instruction ROM. The executed instruction, the program counter address, and the resulting register contents are displayed. Figure 2-10 shows the resulting display.

```

Emulation_

gr65,0x0003

00000205c0r

cmd_rdr:Cmd_I

const

0000020600r

const

gr66,0x0028

gr66,0x00010000

0000020640r

consth

0000020680r

d_rdr:Write_Msg

const

gr67,0x0004

00000206c0r

consth

gr67,0x00020000

0000020700r

mtsr

cr,gr65

0000020740r

loadm

0,0x00,gr72,gr66

0000020780r

cr,gr65

mtsr

0,0x00,gr72,gr67

00000207c@r

storem

gr65,0x0000

000002000@r

Init

const

PC = 0000020040r

CA IP TE TP TU FZ LK RE WM PD PI SM IM DI DA

0000

0 1 0 1 0 1 1 1 00 1 1

PRL DW VF RV BO CP CD

cfg 03 0 1 0 0 0 1

pc0 fffffffc pc1 fffffffc

STATUS: Am29000--Running in monitor

Emulation trace halted

Window

System Register

Processor

Breakpoints Memory Config Analysis

Go Break Reset CMB Step

```

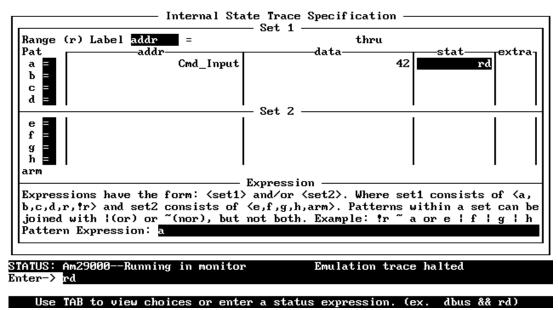

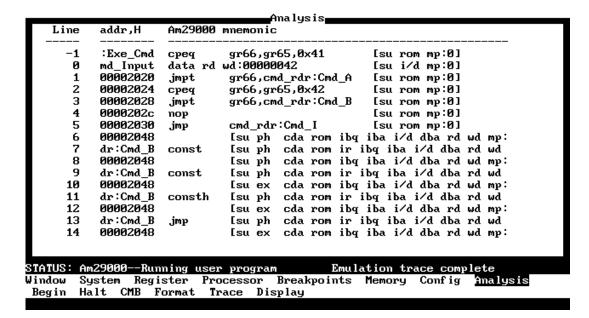

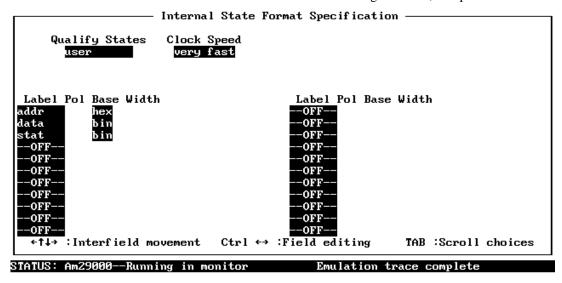

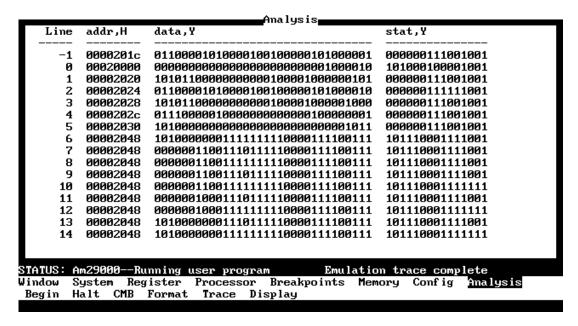

Figure 2-10. Register Contents