# **HP 64784**

# H8/3003 Emulator Terminal Interface

# **User's Guide**

HP Part No. 64784-97010 August 1995

**Edition 6**

## **Notice**

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

© Copyright 1995, Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

HP is a trademark of Hewlett-Packard Company.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

H8/3003<sup>TM</sup> is a registered trademark of Hitachi Ltd.

Hewlett-Packard Company P.O. Box 2197 1900 Garden of the Gods Road Colorado Springs, CO 80901-2197, U.S.A.

**RESTRICTED RIGHTS LEGEND** Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (C) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227-7013. Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A. Right for non-DOD U.S. Government Department and Agencies are as set forth in FAR 52.227-19(c)(1,2).

# **Printing History**

New editions are complete revisions of the manual. The date on the title page changes only when a new edition is published.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual was issued. Many product updates and fixes do not require manual changes, and manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual revisions.

| Edition 6 | 64784-97010, Aug 1995    |

|-----------|--------------------------|

| Edition 5 | 64784-97008, May 1995    |

| Edition 4 | 64784-97006, April 1995  |

| Edition 3 | 64784-97004, August 1994 |

| Edition 2 | 64784-97002, March 1994  |

| Edition 1 | 64784-97000, July 1993   |

# **Using This Manual**

This manual is designed to give you an introduction to the HP 64784 H8/3003 Emulator. This manual will also help define how these emulators differ from other HP 64700 Emulators.

## This manual will:

- give you an introduction to using the emulator

- explore various ways of applying the emulator to accomplish your tasks

- show you emulator commands which are specific to the H8/3003 Emulator

## This manual will not:

■ tell you how to use each and every emulator/analyzer command (refer to the *User's Reference* manual)

# Organization

Chapter 1 An introduction to the H8/3003 emulator features and how they can help you in developing new hardware and software.

Chapter 2 A brief introduction to using the H8/3003 Emulator. You will load and execute a short program, and make some measurements using the emulation analyzer.

Chapter 3 How to plug the emulator probe into a target system.

**Chapter 4** Configuring the emulator to adapt it to your specific measurement needs.

**Appendix A** H8/3003 Emulator Specific Command Syntax and Error Message

# **Contents**

| 1 | Introduction to the H8/3003 Emulator      |

|---|-------------------------------------------|

|   | Introduction                              |

|   | Purpose of the H8/3003 Emulator           |

|   | Features of the H8/3003 Emulator          |

|   | Supported Microprocessors                 |

|   | Clock Speeds                              |

|   | Emulation memory                          |

|   | Analysis                                  |

|   | Registers                                 |

|   | Breakpoints                               |

|   | Reset Support                             |

|   | Real Time Operation                       |

|   | Limitations, Restrictions                 |

|   | Foreground Monitor                        |

|   | DMA Support                               |

|   | Internal RAM of H8/3005                   |

|   | Watch Dog Timer in Background             |

|   | Monitor Break at Sleep/Standby Mode 1-9   |

|   | Hardware Standby Mode                     |

|   | Interrupts in Background Cycles           |

|   | Reset Output Enable Bit                   |

|   | Evaluation chip                           |

| 2 | Getting Started                           |

|   | Introduction                              |

|   | Before You Begin                          |

|   | A Look at the Sample Program              |

|   | Using the Help Facility                   |

|   | Initialize the Emulator to a Known State  |

|   | Set Up the Proper Emulation Configuration |

|   | Set Up Emulation Conditions               |

|   | Mapping Memory                            |

|   | mapping monory                            |

|   | Transfer Code into Emulation Memory                 | 2-12  |

|---|-----------------------------------------------------|-------|

|   | <u>e</u>                                            | 2 10  |

|   | In Standalone Configuration                         | 2-12  |

|   |                                                     | 2 15  |

|   | HP 64700 In Transparent Configuration               |       |

|   | Looking at Your Code                                |       |

|   | Familiarize Yourself with the System Prompts        |       |

|   | Running the Sample Program                          |       |

|   | Stepping Through the Program                        |       |

|   | Tracing Program Execution                           |       |

|   | Predefined Trace Labels                             | 2-22  |

|   | Predefined Status Equates                           |       |

|   | Specifying a Trigger                                |       |

|   | Using Software Breakpoints                          |       |

|   | Displaying and Modifying the Break Conditions       |       |

|   | Defining a Software Breakpoint                      |       |

|   | Searching Memory for Strings or Numeric Expressions |       |

|   | Making Program Coverage Measurements                | 2-29  |

|   | Trace Analysis Considerations                       | 2-30  |

|   | How to Specify the Trigger Condition                | 2-30  |

|   | Store Condition and Disassembling                   |       |

|   | Triggering the Analyzer by Data                     | 2-34  |

| 3 | In-Circuit Emulation                                |       |

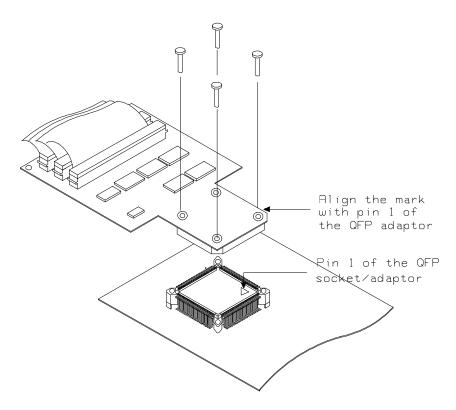

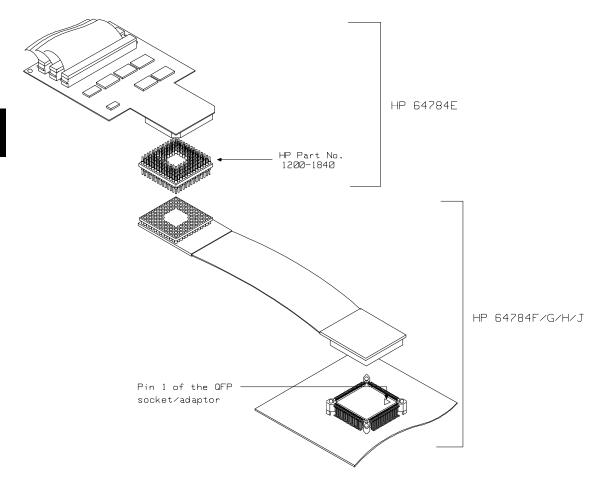

|   | Installing the Target System Probe                  | . 3-2 |

|   | QFP adaptor                                         |       |

|   | PGA adaptor                                         |       |

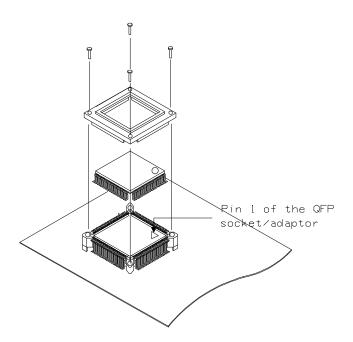

|   | QFP socket/adaptor                                  |       |

|   | Installing the QFP Adaptor                          |       |

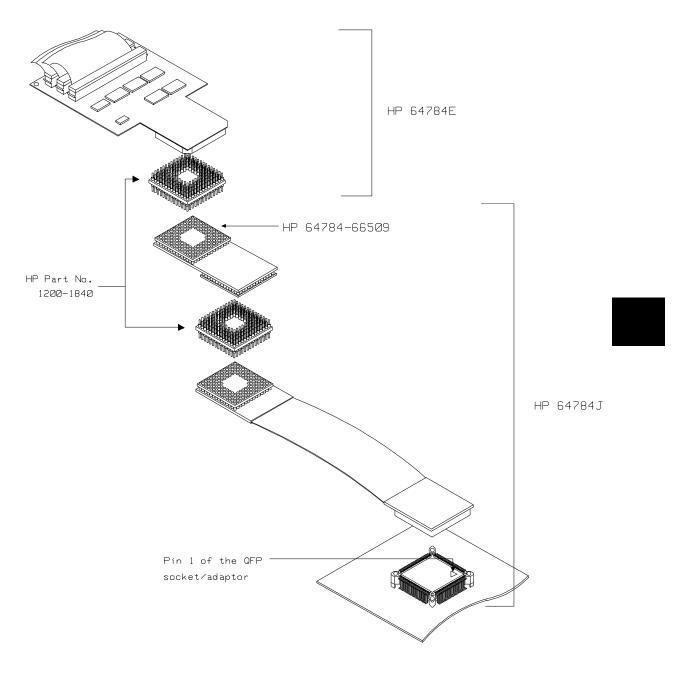

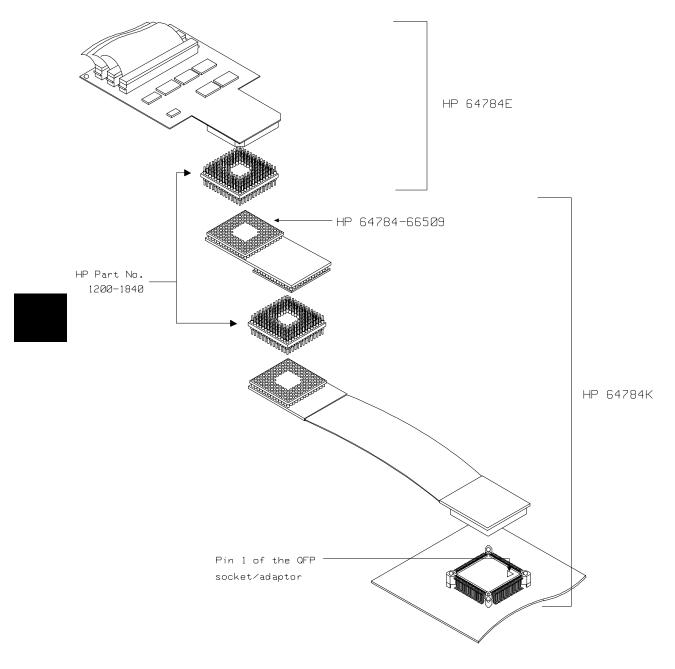

|   | Installing the 64784E PGA adaptor                   |       |

|   | Installing the H8/3003 microprocessor               |       |

|   | Using Low Voltage Adaptor                           |       |

|   | Specification                                       |       |

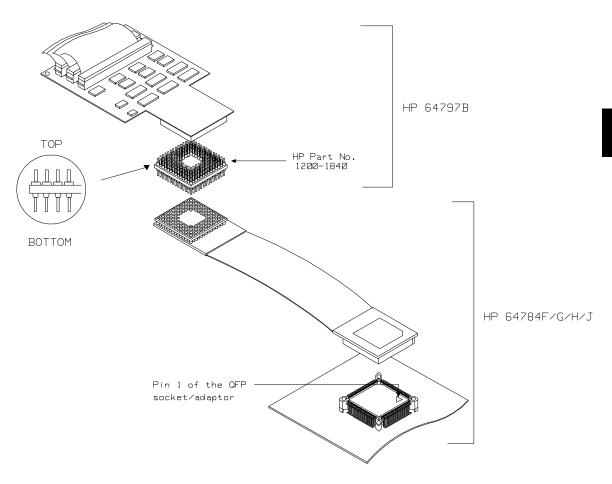

|   | Installing the 64797B PGA adaptor                   |       |

|   | Run from Target System Reset                        |       |

|   | Electrical Characteristics                          |       |

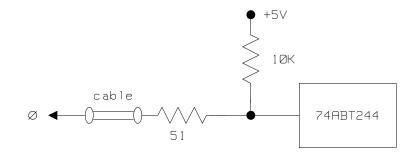

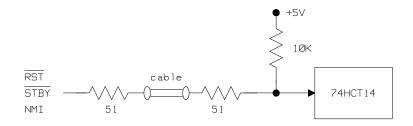

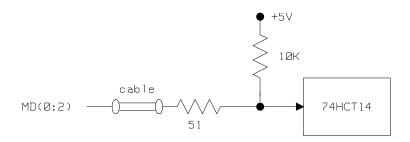

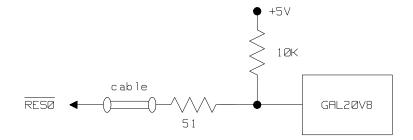

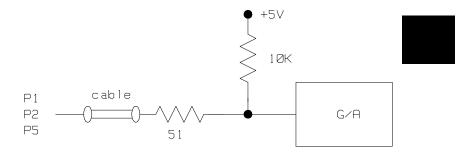

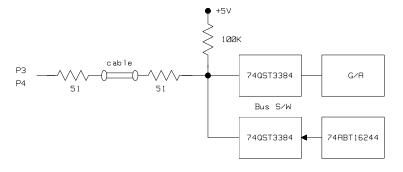

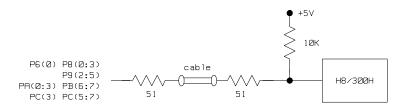

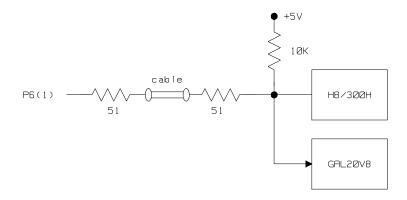

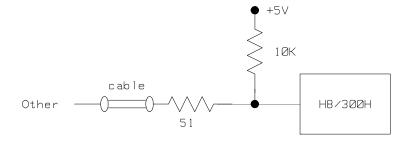

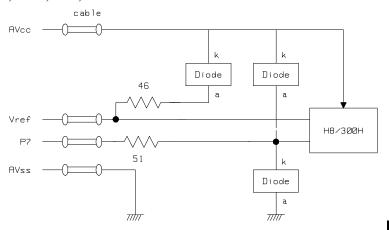

|   | Target System Interface                             |       |

| 4 | Configuring the H8/3003 Emulator                    |       |

| - |                                                     | A 1   |

|   | Types of Emulator Configuration                     |       |

|   | Commands Which Perform an Action or Measurement 4-2 |

|---|-----------------------------------------------------|

|   | Coordinated Measurements                            |

|   | Analyzer                                            |

|   | System                                              |

|   | Emulation Processor to Emulator/Target System       |

|   | cf ba                                               |

|   | cf dbc                                              |

|   | cf drst                                             |

|   | Memory Mapping                                      |

|   | Break Conditions                                    |

|   | Where to Find More Information                      |

|   |                                                     |

| A | H8/3003 Emulator Specific Command Syntax            |

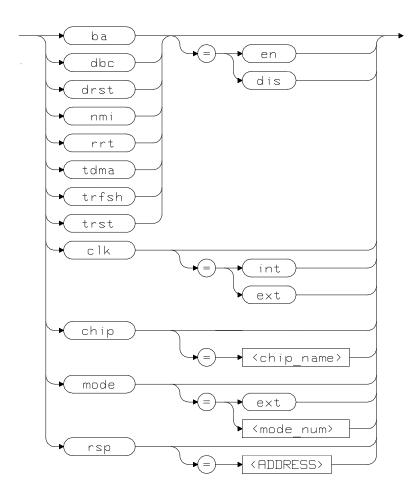

|   | CONFIG_ITEMS                                        |

|   | Summary                                             |

|   | Syntax                                              |

|   | Description                                         |

|   | Examples                                            |

|   | Related information                                 |

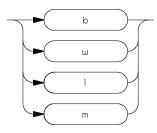

|   | ACCESS MODE and DISPLAY MODE                        |

|   | Summary                                             |

|   | Syntax                                              |

|   | Defaults                                            |

|   | Related Information                                 |

|   | ADDRESS                                             |

|   | Summary                                             |

|   | Description                                         |

|   | Examples                                            |

|   | REGISTER CLASS and NAME                             |

|   | Summary                                             |

|   | Emulator Specific Error Messages                    |

|   | Message                                             |

# Illustrations

**Tables**

| Figure 1-1. HP 64784 Emulator for the H8/3003 . Figure 2-1. Sample Program Listing Figure 3-1. Installing the QFP adaptor Figure 3-2 Installing the PGA adaptor (General) . Figure 3-3 Installing the PGA adaptor (3001 mode 3 Figure 3-4 Installing the PGA adaptor (3004/5 mode Figure 3-5 Installing the H8/3003 microprocessor . Figure 3-6 Installing the PGA adaptor (General) . | 3/4)<br>e 3) | <br><br><br> | <br>. 2-5<br>. 3-5<br>. 3-6<br>. 3-7<br>. 3-8<br>. 3-9 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                        |              |              |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                        |              |              |                                                        |

| Table 1-1. Supported Microprocessors                                                                                                                                                                                                                                                                                                                                                   |              | <br>         | . 1-3                                                  |

| Table 1-2. Clock Speeds                                                                                                                                                                                                                                                                                                                                                                |              | <br>         | . 1-6                                                  |

| Table 3-1. DC Characteristics of input high voltage                                                                                                                                                                                                                                                                                                                                    |              | <br>         | 3-10                                                   |

| Table 3-2. Bus timing ( $Vcc = 5.0V$ , $f = 16MHz$ ).                                                                                                                                                                                                                                                                                                                                  |              | <br>         | 3-13                                                   |

| Table 3-3. Refresh controller timing                                                                                                                                                                                                                                                                                                                                                   |              |              |                                                        |

| (Vcc = 5.0V, f = 16MHz)                                                                                                                                                                                                                                                                                                                                                                |              | <br>         | 3-16                                                   |

| Table 3-4. Control signal timing                                                                                                                                                                                                                                                                                                                                                       |              |              |                                                        |

| (Vcc = 5.0V, f = 16MHz)                                                                                                                                                                                                                                                                                                                                                                |              | <br>         | 3-17                                                   |

| Table 3-5. Timing condition of On-chip supporting                                                                                                                                                                                                                                                                                                                                      |              |              |                                                        |

| modules $(Vcc = 5.0V, f = 16MHz)$                                                                                                                                                                                                                                                                                                                                                      |              | <br>         | 3-18                                                   |

| Table 3-6. Bus timing ( $Vcc = 3.0V$ , $f = 10MHz$ ).                                                                                                                                                                                                                                                                                                                                  |              | <br>         | 3-20                                                   |

| Table 3-7. Control signal timing                                                                                                                                                                                                                                                                                                                                                       |              |              |                                                        |

| (Vcc = 3.0V, f = 10MHz)                                                                                                                                                                                                                                                                                                                                                                |              | <br>         | 3-23                                                   |

| Table 3-8. Timing condition of On-chip supporting                                                                                                                                                                                                                                                                                                                                      |              |              |                                                        |

| modules $(Vcc = 3.0V, f = 10MHz)$                                                                                                                                                                                                                                                                                                                                                      |              | <br>         | 3-24                                                   |

# 4-Contents

# Introduction to the H8/3003 Emulator

# Introduction

The topics in this chapter include:

- Purpose of the H8/3003 Emulator

- Features of the H8/3003 Emulator

# Purpose of the H8/3003 Emulator

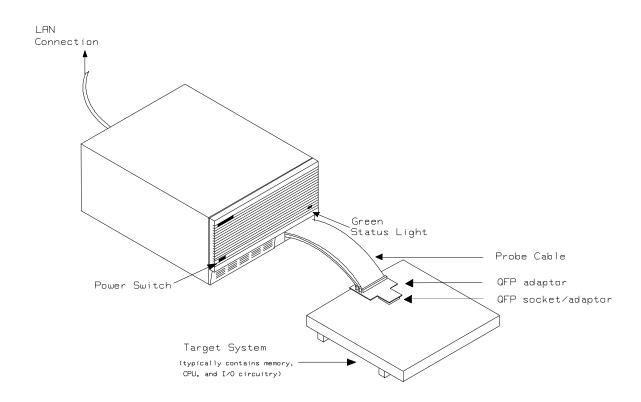

The H8/3003 Emulator is designed to replace the H8/3003 microprocessor in your target system so you can control operation of the microprocessor in your application hardware (usually refer to as the *target system*). The H8/3003 emulator performs just like the H8/3003 microprocessor, but is a device that allows you to control the H8/3003 microprocessor directly. These features allow you to easily debug software before any hardware is available, and ease the task of integrating hardware and software.

Figure 1-1. HP 64784 Emulator for the H8/3003

# 1-2 Introduction to the H8/3003 Emulator

# Features of the H8/3003 Emulator

**Supported Microprocessors**

The HP 64784A H8/3003 emulator supports the microprocessors listed in Table 1-1.

Table 1-1. Supported Microprocessors

|         | Sup         | QFP Adaptor                | PGA Adaptor |                |          |                          |

|---------|-------------|----------------------------|-------------|----------------|----------|--------------------------|

| Туре    | Package     | System<br>Clock<br>Divider | On-chip ROM | Supply Voltage | Board    | Board/<br>QFP probe      |

| H8/3005 | 80pinQFP    |                            |             | 4.75 to 5.25V  |          | HP64784E/                |

|         |             | -                          | -           | 2.7 to 5.25V   | -        | HP64784K*1               |

| H8/3004 | 80pinQFP    |                            |             | 4.75 to 5.25V  |          | HP64784E/                |

|         |             | -                          | -           | 2.7 to 5.25V   | -        | HP64784K*1               |

| H8/3003 | 112 pin QFP |                            |             | 4.75 to 5.25V  |          |                          |

|         |             | 1:2                        | -           | 2.7 to 5.25V   | HP64784C | HP64784E/                |

|         |             |                            |             | 4.75 to 5.25V  |          | HP64784F                 |

|         |             | -                          | -           | 2.7 to 5.25V   |          |                          |

| H8/3002 | 100 pin QFP |                            |             | 4.75 to 5.25V  | HP64784D | HP64784E/                |

|         |             | -                          | -           | 2.7 to 5.25V   |          | HP64784G                 |

| H8/3001 | 80 pin QFP  | -                          | -           | 4.75 to 5.25V  | -        | HP64784E/<br>HP64784J *1 |

**Table 1-1. Supported Microprocessors (Cont'd)**

|         | Sur         | ported M         | icroprocessors | QFP Adaptor           | PGA Adaptor |                     |  |  |

|---------|-------------|------------------|----------------|-----------------------|-------------|---------------------|--|--|

| Type    | Package     | System           | On-chip ROM    | <b>Supply Voltage</b> | Board       | Board/<br>QFP probe |  |  |

|         |             | Clock<br>Divider |                | 2.7 to 5.25V          |             |                     |  |  |

| H8/3032 | 80 pin QFP  |                  |                | 4.75 to 5.25V         |             |                     |  |  |

|         |             |                  | PROM           | 2.7 to 5.25V          |             | HP64784E/           |  |  |

|         |             | -                | 14 1 10014     | 4.75 to 5.25 V        | -           | HP64784H            |  |  |

|         |             |                  | Masked ROM     | 2.7 to 5.25V          |             |                     |  |  |

| H8/3031 | 80 pin QFP  |                  |                | 4.75 to 5.25 V        |             | HP64784E/           |  |  |

|         |             | ı                | -              | 2.7 to 5.25 V         | -           | HP64784H            |  |  |

| H8/3030 | 80 pin QFP  |                  |                | 4.75 to 5.25 V        |             | HP64784E/           |  |  |

|         |             | -                | -              | 2.7 to 5.25 V         | -           | HP64784H            |  |  |

| H8/3042 | 100 pin QFP |                  | DDOM.          | 4.75 to 5.25V         |             |                     |  |  |

|         |             |                  | PROM           | 2.7 to 5.25V          | HP64784D    | HP64784E/           |  |  |

|         |             | -                | M 1 IDOM       | 4.75 to 5.25V         |             | HP64784G            |  |  |

|         |             |                  | Masked ROM     | 2.7 to 5.25V          |             |                     |  |  |

| H8/3041 | 100 pin QFP |                  | Marka I DOM    | 4.75 to 5.25V         | HP64784D    | HP64784E/           |  |  |

|         |             | -                | Masked ROM     | 2.7 to 5.5V           |             | HP64784G            |  |  |

| H8/3040 | 100 pin QFP |                  |                |                       | HP64784D    | HP64784E/           |  |  |

|         |             | -                | Masked ROM     | 2.7 to 5.25V          |             | HP64784G            |  |  |

$<sup>^{*}1</sup>$  When you do in-circuit emulation for H8/3001 with mode 3/4 or H8/3004/5 with mode 3, you must use HP 64784-66509 shipped with HP 64784J/K. Refer to the "In-Circuit Emulation" Chapter in this manual for more details.

## 1-4 Introduction to the H8/3003 Emulator

The H8/3003 emulator is provided without any QFP adaptors and PGA adaptor(HP 64784E) with QFP probe. To emulate each processor with your target system, you need to purchase appropriate QFP adaptor or PGA adaptor with QFP probe listed in Table 1-1. To purchase them, contact your local HP sales representative.

You can buy HP 64797B low voltage adaptor to emulate each processor running with supply voltage from 2.7 up to 5.25V input in your target system. To buy HP 64797B, contact your local HP sales representative.

The list of supported microprocessors in Table 1-1 is not necessarily complete. To determine if your microprocessor is supported or not, contact Hewlett-Packard.

## **Clock Speeds**

You can select whether the emulator will be clocked by the internal clock source or by the external clock source on your target system. When you select a clock input conforming to the specification of Table 1-2.

Refer to the "Configuration the Emulator" Chapter in this manual for more details.

Table 1-2. Clock Speeds

| Table 1-2. Clock Speeds |                     |                                        |                                        |  |  |  |  |  |  |  |

|-------------------------|---------------------|----------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| Clock source            | Chip                | Without 64797B                         | With 64797B                            |  |  |  |  |  |  |  |

| Internal                | H8/3001             | 16MHz                                  | 8MHz                                   |  |  |  |  |  |  |  |

|                         | H8/3002             | (System clock)                         | (System clock)                         |  |  |  |  |  |  |  |

|                         | H8/3003T            | ,                                      | , ,                                    |  |  |  |  |  |  |  |

|                         | H8/3004             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3005             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3030             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3031             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3032             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3040             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3041             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3042             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3003 with system | 8MHz                                   | 8MHz                                   |  |  |  |  |  |  |  |

|                         | clock divider       | (System clock)                         | (System clock)                         |  |  |  |  |  |  |  |

| External                | H8/3001             | From 0.5 up to 16MHz                   | From 0.5 up to 10MHz                   |  |  |  |  |  |  |  |

|                         | H8/3002             | (System clock)                         | (System clock)                         |  |  |  |  |  |  |  |

|                         | H8/3003T            | , ,                                    | , <b>,</b>                             |  |  |  |  |  |  |  |

|                         | H8/3004             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3005             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3030             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3031             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3032             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3040             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3041             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3042             |                                        |                                        |  |  |  |  |  |  |  |

|                         | H8/3003 with system | From 1 up to 24MHz                     | From 1 up to 20MHz                     |  |  |  |  |  |  |  |

| ı                       | clock divider       | (System clock is from 0.5 up to 12MHz) | (System clock is from 0.5 up to 10MHz) |  |  |  |  |  |  |  |

# 1-6 Introduction to the H8/3003 Emulator

# **Emulation memory**

The H8/3003 emulator is used with one of the following Emulation Memory Cards.

- HP 64726A 128K byte Emulation Memory Card

- HP 64727A 512K byte Emulation Memory Card

- HP 64728A 1M byte Emulation Memory Card

- HP 64729A 2M byte Emulation Memory Card

You can define up to 16 memory ranges (at 512 byte boundaries and least 512 byte in length.) The emulator occupies 6K byte, which is used for monitor program and internal RAM of microprocessor mapped as emulation RAM, leaving 122K, 506K, 1018K, 2042K byte of emulation memory which you may use. You can characterize memory range as emulation RAM (eram), emulation ROM (erom), target system RAM (tram), target system ROM (trom), or guarded memory (grd). The emulator generates an error message when accesses are made to guarded memory locations. You can also configure the emulator so that writes to memory defined as ROM cause emulator execution to break out of target program execution.

# **Analysis**

The H8/3003 emulator is used with one of the following analyzers which allows you to trace code execution and processor activity.

- HP 64704A 80-channel Emulation Bus Analyzer

- HP 64703A 64-channel Emulation Bus Analyzer and 16-channel State/Timing Analyzer.

- HP 64794A/C/D Deep Emulation Bus Analyzer

The Emulation Bus Analyzer monitors the emulation processor using an internal analysis bus. The HP 64703A 64-channel Emulation Bus Analyzer and 16-channel State/Timing Analyzer allows you to probe up to 16 different lines in your target system.

#### Registers

You can display or modify the H8/3003 internal register contents. This includes the ability to modify the program counter (PC) value so you can control where the emulator starts a program run.

## **Breakpoints**

You can set the emulator/analyzer interaction so the emulator will break to the monitor program when the analyzer finds a specific state or states, allowing you to perform post-mortem analysis of the program execution. You can also set software breakpoints in your program. This feature is realized by inserting a special instruction into user

Introduction to the H8/3003 Emulator 1-7

program. One of undefined opcodes (5770 hex) is used as software breakpoint instruction. Refer to the "Using Software Breakpoints" section of "Getting Started" chapter for more information.

# **Reset Support**

The emulator can be reset from the emulation system under your control; or your target system can reset the emulation processor.

# **Real Time Operation**

Real-time signifies continuous execution of your program at full rated processor speed without interference from the emulator. (Such interference occurs when the emulator needs to break to the monitor to perform an action you requested, such as displaying target system memory.) Emulator features performed in real time include: running and analyzer tracing. Emulator features not performed in real time include: display or modification of target system memory, load/dump of target memory, display or modification of registers.

# Limitations, Restrictions

**Foreground Monitor** Foreground monitor is not supported for the H8/3003 emulator.

**DMA Support** Direct memory access to the emulation by external DMAC is not

allowed.

Internal RAM of When you emulate H8/3005 processor, you can't use address 0fef10h - 0ff00fh (mode 1) and 0ffef10h - 0fff00fh (mode 3) as internal RAM.

These area are worked as external 8bit 3state area.

Watch Dog Timer in Watch dog timer is suspended count up while the emulator is running

**Background** in background monitor.

Monitor Break at Sleep/Standby Mode When the emulator breaks into the background monitor, sleep or software standby mode is released. Then, PC indicates next address of

"SLEEP" instruction.

**Hardware Standby** Hardware standby mode is not supported for the H8/3003 emulator.

Hardware standby request from target system will give the emulator

reset signal.

Mode

Interrupts in The H8/3003 emulator does not accept any interrupts while in background Cycles background monitor. Such interrupts are suspended while running the

background monitor, and will occur when context is changed to

foreground.

**Reset Output Enable** The RSTOE (Reset output enable bit) is used to determine whether the

H8/3003 processor outputs reset signal when the processor is reset by the watch dog timer. However, the H8/3003 emulator ignores the configuration of the RSTOE, and works as it is configured with the

modify configuration command.

Introduction to the H8/3003 Emulator 1-9

Hewlett-Packard makes no warranty of the problenm caused by the  $\rm H8/3003~Evaluation~chip$  in the emulator.

# **Getting Started**

# Introduction

This chapter will lead you through a basic, step by step tutorial designed to familiarize you with the use of the HP 64700 emulator for the H8/3003 microprocessor. When you have completed this chapter, you will be able to perform these tasks:

- Set up an emulation configuration for out of circuit emulation use

- Map memory

- Transfer a small program into emulation memory

- Use run/stop controls to control operation of your program

- Use memory manipulation features to alter the program's operation

- Use analyzer commands to view the real time execution of your program

- Use software breakpoint feature to stop program execution at specific address

- Search memory for strings or numeric expressions

- Make program coverage measurements

# **Before You Begin**

Before beginning the tutorial presented in this chapter, you must have completed the following tasks:

1. Completed hardware installation of the HP 64700 emulator in the configuration you intend to use for your work:

Standalone configuration

Transparent configuration

Remote configuration

- 2. If you are using the Remote Configuration, you must have completed installation and configuration of a terminal emulator program which will allow your host to act as a terminal connected to the emulator. In addition, you must start the terminal emulator program before you can work the examples in this chapter.

- 3. If you have properly completed steps 1 and 2 above, you should be able to hit <RETURN> (or <ENTER> on some keyboards) and get one of the following command prompts on your terminal screen:

U>

R>

M>

If you do not see one of these command prompts, retrace your steps through the hardware and software installation procedures outlined in the manuals above, verifying all connections and procedural steps. If you are still unable to get a command prompt, refer to the *HP 64700 Support Services Guide*. The guide gives basic troubleshooting procedures. If this fails, call the local HP sales and service office listed in the *Support Services Guide*.

In any case, you **must** have a command prompt on your terminal screen before proceeding with the tutorial.

# A Look at the Sample Program

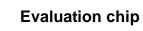

The sample program "COMMAND\_READER" used in this chapter is shown figure 2-1. The program emulates a primitive command interpreter.

#### **Data Declarations**

Msg\_A, Msg\_B and Msg\_I are the messages used by the program to respond to various command inputs.

#### Initialization

The locations of stack and input area(Cmd\_Input) are moved into address registers for use by the program. Next, the CLEAR routine clears the command byte(the first location pointed to by Cmd\_Input - 0ff800 hex). Cmd\_Input contains 00 hex for late use.

#### Scan

This routine continuously reads the byte at location of Cmd\_Input until it is something other than a null character (00 hex); when this occurs, the Exe\_Cmd routine is executed.

#### Exe\_Cmd

Compares the input byte (now something other than a null) to the possible command bytes of "A" (ASCII 41 hex) and "B" (ASCII 42 hex), then jumps to the appropriate set up routine for the command message. If the input byte does not match either of these values, a branch to a set up routine for an error message is executed.

## Cmd\_A, Cmd\_B, Cmd\_I

These routines set up the proper parameters for writing the output message: the number of bytes in the message is moved to the R3L register and the base address of the message in the data area is moved to address register ER4.

#### Write\_Msg

First the base address of the output area is copied to ER5. Then the Clear\_Old routine writes nulls to 32 bytes of the output area (this serves both to initialize the area and to clear old messages written during previous program passes).

Finally, the proper message is written to the output area by the Write\_Loop routine. When done, Write\_Loop jumps back to Clear and the command monitoring process begins again.

Using the various features of the emulator, we will show you how to load this program into emulation memory, execute it, monitor the program's operation with the analyzer, and simulate entry of different commands utilizing the memory access commands provided by the HP 64700 command set.

```

002000

SECTION

Table, DATA, LOCATE=H'2000

002000

Msas

002000 5448495320495320

"THIS IS MESSAGE A"

Msg_A

.SDATA

002000 5448495320495320

002008 4D45535341474520

002010 41

002011 5448495320495320

002019 4D45535341474520

Msg_B

.SDATA

"THIS IS MESSAGE B"

002021 42

002022 494E56414C494420

"INVALID COMMAND"

Msg_I

.SDATA

00202A 434F4D4D414E44

002031

End_Msgs

001000

.SECTION Prog, CODE, LOCATE=H'10:

8

Prog, CODE, LOCATE=H'1000

9

;* Set up the Pointers.;*********

10

*******

11

MOV.L

001000 7A07000FF904

12

#Stack, ER7

MOV.L

001006 7A01000FF800

#Cmd_Input, ER1

;* Clear previous command.

16

Clear MOV.B

00100C F800

#H'00,R0L

00100E 6AA8000FF800

18

MOV.B

ROL,@Cmd_Input

;**************

19

;* Read command input byte. If no command has been

20

;* entered, continue to scan for it.

21

2.2

001014 6A2A000FF800

23

MOV.B

@Cmd_Input,R2L

Scan

00101A AA00

00101C 47F6

CMP.B

#H'00,R2L

25

26

27

;* A command has been entered. Check if it is

28

29

Exe_Cmd

CMP.B

#H'41,R2L

00101E AA41

30

BEQ

{\rm Cmd}\_{\rm A}

001020 5870000A

31

001024 AA42

32

CMP. B

#H'42,R2L

001026 58700010

33

BEO

Cmd B

00102A 58000018

34

35

;* Command A is entered. R3L = the number of bytes

36

;* in message A. R4 = location of the message.

37

/* Jump to the routine which writes the message.

38

39

00102E FB11

001030 7A0400002000

Cmd_A

MOV.B

#Msg_B-Msg_A,R3L

41

MOV.L

#Msg_A,ER4

001036 58000014

42

BRA

Write_Msg

;* Command B is entered.

45

00103A FB11

00103C 7A0400002011

001042 58000008

Cmd_B

MOV.B

#Msg_I-Msg_B,R3L

MOV.L

#Msg_B,ER4

BRA

Write_Msg

```

Figure 2-1. Sample Program Listing

Figure 2-1. Sample Program Listing (Cont'd)

# Using the Help Facility

If you need a quick reference to the Terminal Interface syntax, you can use the built-in help facilities. For example, to display the top level help menu, type:

R> help

```

help - display help information

help <group>

- print help for desired group

print short help for desired groupprint help for desired command

help -s <group>

help <command>

- print this help screen

help

--- VALID <group> NAMES ---

system grammarprocessor specific grammar

gram

proc

- system commands

- emulation commands

emul

hl

- highlevel commands (hp internal use only)

trc

- analyzer trace commands

- all command groups

```

You can type the ? symbol instead of typing help. For example, if you want a list of commands in the emul command group, type:

R> ? emul

```

emul - emulation commands

b....break to monitor cp...copy memory mo...modes

bc...break condition dump..dump memory r...run user code

bp...breakpoints es...emulation status reg..registers

cf...configuration io...input/output rst..reset

cim...copy target image load..load memory rx...run at CMB execute

cmb...CMB interaction m...memory s...step

cov...coverage map...memory mapper ser..search memory

```

To display help information for any command, just type help (or ?) and the command name. For example:

R> help load

```

load - download absolute file into processor memory space

```

```

- download intel hex format

load -i

- download motorola S-record format

load -m

- download extended tek hex format

load -t

load -S

- download sysmbol file

- download hp format (requires transfer protocol)

load -h

load -a

- reserved for internal hp use

- write only to emulation memory

load -e

- write only to target memory

load -u

- data received from the non-command source port

load -o

load -s <str> - send a character string out the other port

- data sent in binary (valid with -h option)

- data sent in hex ascii (valid with -h option)

load -b

load -x

load -q

- quiet mode

load -p

- record ACK/NAK protocol (valid with -imt options)

load -c <file> - data is received from the 64000. file name format is:

<filename>:<userid>:absolute

```

# Initialize the Emulator to a Known State

To initialize the emulator to a known state for this tutorial:

Note

It is especially important that you perform the following step if the emulator is being operated in a standalone mode controlled by only a data terminal. The only program entry available in this mode is through memory modification; consequently, if the emulator is reinitialized, emulation memory will be cleared and a great deal of tedious work could be lost.

- 1. Verify that no one else is using the emulator or will have need of configuration items programmed into the emulator.

- 2. Initialize the emulator by typing the command:

R> init

#### 2-8 Getting Started

# Set Up the Proper Emulation Configuration

# Set Up Emulation Conditions

To set the emulator's configuration values to the proper state for this tutorial, do this:

1. Type:

R> cf

You should see the following configuration items displayed:

cf ba=en cf chip=3042 cf clk=int cf dbc=en cf drst=dis cf mode=7 cf nmi=en cf rrt=dis cf rsp=9 cf tdma=en cf trfsh=en

cf trst=en

**Note**

The individual configuration items won't be explained in this example; refer to Chapter 4 of this manual and the *User's Reference* manual for details.

2. If the configuration items displayed on your screen don't match the ones listed above, here is how to make them agree:

For each configuration item that does not match, type:

R> cf <config\_item>=<value>

For example, if you have the following configuration items displayed (those in bold indicate items different from the list above):

To make these configuration values agree with the desired values, type:

```

R> cf clk=int

R> cf rrt=dis

```

3. Now, you need to set up stack pointer. Type:

```

R> cf rsp=0ff904

```

4. Let's go ahead and set up the proper break conditions. Type:

R> bc

You will see:

```

bc -d bp #disable

bc -e rom #enable

bc -d bnct #disable

bc -d cmbt #disable

bc -d trig1 #disable

bc -d trig2 #disable

```

For each break condition that does not match the one listed, use one of the following commands:

To enable break conditions that are currently disabled, type:

R> bc -e <br/>breakpoint type>

To disable break conditions that are currently enabled, type:

R> bc -d <br/>breakpoint type>

For example, if typing bc gives the following list of break conditions:

#### 2-10 Getting Started

```

bc -d bp #disable

bc -d rom #disable

bc -d bnct #disable

bc -d cmbt #disable

bc -e trig1 #enable

bc -e trig2 #enable

```

(items in bold indicate improper values for this example)

Type the following commands to set the break conditions correctly for this example:

R> bc -e rom

(this enables the write to ROM break)

R> bc -d trig1 trig2

(this disables break on triggers from the analyzer)

# **Mapping Memory**

Depending on the memory board, emulation memory consists of 128K, 512K, 1M or 2M bytes, mappable in 512 byte blocks. The monitor occupies 2K bytes and the emulator maps 4K bytes for internal RAM as emulation RAM automatically, leaving 122K, 506K, 1018K or 2042K bytes of emulation memory which you may use.

The memory mapper allows you to characterize memory locations. It allows you specify whether a certain range of memory is present in the target system or whether you will be using emulation memory for that address range. You can also specify whether the target system memory is ROM or RAM, and you can specify that emulation memory be treated as RAM od ROM.

Type:

R> map 0..0ffff erom

To verify that memory blocks are mapped properly, type:

R> map

#### You will see:

# remaining number of terms : 15

# remaining emulation memory : 6e800h bytes

map 0000000..000ffff erom # term 1

map other tram

Note

You must map internal ROM as emulation memory.

Note

You don't have to map internal RAM, since the emulator maps internal RAM as emulation RAM. And the emulator memory system dose not introduce it in memory mapping display.

Refer to "Memory Mapping" section of "Configuring the Emulator" chapter in this manual for more details.

# Transfer Code into Emulation Memory

# Transferring Code from a Terminal In Standalone Configuration

To transfer code into emulation memory from a data terminal running in standalone mode, you must use the modify memory commands. This is necessary because you have no host computer transfer facilities to automatically download the code for you (as if you would if you were using the transparent configuration or the remote configuration.) To minimize the effects of typing errors, you will modify only one row of memory at a time in this example. Do the following:

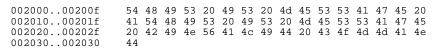

1. Enter the data information for the program by typing the following commands:

R> m 002000..00200f=54,48,49,53,20,49,53,20,4d,45,53,53,41,47,45,20

R> m 002010..00201f=41,54,48,49,53,20,49,53,20,4d,45,53,53,41,47,45

#### 2-12 Getting Started

```

\mathbb{R}> m 002020..00202f=20,42,49,4e,56,41,4c,49,44,20,43,4f,4d,4d,41,4e \mathbb{R}> m 002030=44

```

You could also type the following line instead:

R> m 002000="THIS IS MESSAGE ATHIS IS MESSAGE BINVALID COMMAND"

2. You should now verify that the data area of the program is correct by typing:

R> m 002000..002030

#### You should see:

| 00200000200f | 54 | 48 | 49 | 53 | 20 | 49 | 53 | 20 | 4d | 45 | 53 | 53 | 41 | 47 | 45 | 20 |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00201000201f | 41 | 54 | 48 | 49 | 53 | 20 | 49 | 53 | 20 | 4d | 45 | 53 | 53 | 41 | 47 | 45 |

| 00202000202f | 20 | 42 | 49 | 4e | 56 | 41 | 4c | 49 | 44 | 20 | 43 | 4f | 4d | 4d | 41 | 4e |

| 002030002030 | 44 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

If this is not correct, you can correct the errors by re-entering only the modify memory commands for the particular rows of memory that are wrong.

For example, if row 002000..00200f shows these values:

```

002000..00200f 54 48 49 53 20 20 49 53 20 4d 45 53 53 41 47 45

```

you can correct this row of memory by typing:

```

R> m 002000..00200f=54,48,49,53,20,49,53,20,4d,45,53,53,41,47,45,20

```

Or, you might need to modify only one location, as in the instance where address 00200f equals 22 hex rather than 20 hex. Type:

R> m 00200f=22

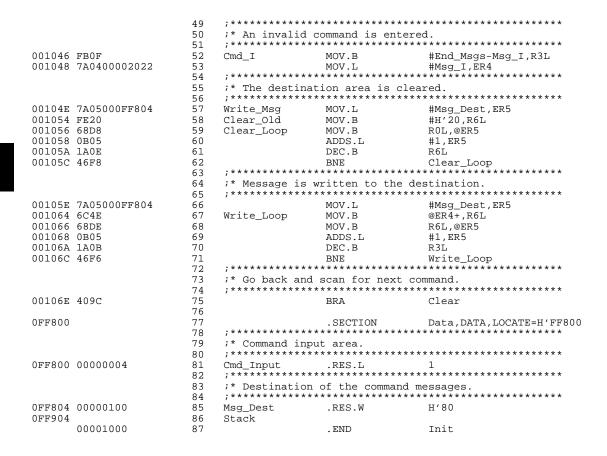

3. Enter the program information by typing the following commands:

(Note the hex letters must be preceded by a digit.)

4. You should now verify that the program area is correct by typing:

R> m 001000..00106f

#### You should see:

If this is not correct, you can correct the errors by re-entering only the modify memory commands for the particular rows of memory that are wrong.

# Transferring Code From A Host, HP 64700 In Transparent Configuration

The method provided in this example assumes that you are running an Assembler/Linkage Editor on an HP 9000/300 computer running the HP-UX operating system. In addition, you must have the HP 64000 **transfer** software running on your host.

If you are not using an Assembler/Linkage Editor, you may be able to adapt the methods below to load your code into the emulator (refer to the *HP 64700 User's Reference* manual for help).

If you are not able to transfer code from your host to the emulator using one of these methods, use the method described previously under "Transferring Code From A Terminal In Standalone Mode", as it will work in all cases. However, transferring code using host transfer facilities is easier and faster than modifying memory locations, especially for large programs.

1. First, you must establish communications with your host computer through the transparent mode link provided in the HP 64700. Type:

#### R> xp -s 02a

This sets the second escape character to "\*".(The first escape character remains at the HP 64700 powerup default of hex 01b, which is the ASCII <ESC>character.) The sequence "<ESC>\*" toggles the transparent mode software within the HP 64700 for the duration of one command (that is, any valid line of HP 64700 commands (not exceed 254 characters) concatenated by semicolons and terminated by a <carriage return>). Refer to the *User's Reference* manual for more information on the xp command.

Enable the transparent mode link by typing:

#### R> xp -e

If you then press <RETURN> a few times, you should see:

This is the login prompt for an HP-UX host system. (Your prompt may differ depending on how your system manager has configured your system.)

login: login: login: 2. Log in to your host system and start up an editor such as "vi". You should now enter the source code for the sample program shown at the beginning of the chapter. When finished, save the program to filename "sampprog.src".

Note

If you need help learning how to log in to your HP-UX host system or use other features of the system, such as editors, refer to the HP-UX Concepts and Tutorials guides and your HP-UX system administrator.

- 3. Assemble and link your code.

- 4. Convert your absolute file generated above into HP format with the following command. This is needed to load the file into the emulator.

- \$ h83cnvhp -x sampprog

An HP format absolute file sampprog.X will be generated.

Now it's time to transfer your code into the emulator. Do the following:

- 1. Disable the transparent mode so that your terminal will talk directly to the emulator. Type:

- \$ <ESC>\* xp -d

The "<ESC>\*" sequence temporarily toggles the transparent mode so that the emulator will accept commands; "xp -d" then fully disables the transparent mode.

2. Load code into the emulator by typing:

```

R> load -hbo

transfer -rtb sampprog.X<ESC>* (NOTE: DO NOT

TYPE CARRIAGE RETURN!)

```

The system will respond:

## R>

**load -hbo** tells the emulator to load code expected in HP binary file format and to expect the data from the other port (the one connected to the host). It then puts you in

communication with the host; you then enter the transfer command to start the HP 64000 transfer utility. Typing "<ESC>\*" tells the system to return to the emulator after transferring the code. The "##" marks returned by the system indicates that the emulator loaded two records from the host.

3. At this point you should examine a portion of memory to verify that your code was loaded correctly.

Type:

R> m 2000..2030

You should see:

If your system does not match, verify 1) that you entered the source code correctly; 2) that you entered the linker parameters correctly.

## Looking at Your Code

Now that you have loaded your code into emulation memory, you can display it in mnemonic format. Type:

R> m -dm 1000..106f

You will see:

```

0001000 -

MOV.L #000ff904,ER7

0001006 -

MOV.L #000ff800,ER1

000100c

MOV.B #00,R0L

MOV.B R0L,@0ff800

000100e

MOV.B @0ff800,R2L

CMP.B #00,R2L

0001014

000101a

BEQ 001014

000101c

000101e

CMP.B #41,R2L

BEQ 00102e

0001020

CMP.B #42,R2L

BEQ 00103a

0001024

0001026

000102a

BRA 001046

MOV.B #11,R3L

MOV.L #00002000,ER4

000102e

0001030

0001036

BRA 00104e

000103a

MOV.B #11,R3L

000103c

MOV.L #00002011, ER4

0001042

BRA 00104e

0001046

MOV.B #0f,R3L

0001048

MOV.L #00002022, ER4

000104e

MOV.L #000ff804,ER5

0001054

MOV.B #20,R6L

0001056

MOV.B ROL,@ER5

0001058

ADDS #1,ER5

000105a

DEC.B R6L

000105c

BNE 001056

MOV.L #000ff804,ER5

MOV.B @ER4+,R6L

000105e

0001064

0001066

MOV.B R6L,@ER5

ADDS #1,ER5

DEC.B R3L

0001068

000106a

000106c

BNE 001064

000106e

BRA 00100c

```

## Familiarize Yourself with the System Prompts

#### **Note**

The following steps are not intended to be complete explanations of each command; the information is only provided to give you some idea of the meanings of the various command prompts you may see and reasons why the prompt changes as you execute various commands.

You should gain some familiarity with the HP 64700 emulator command prompts by doing the following:

1. Ignore the current command prompt. Type:

\*> rst

You will see:

R>

The **rst** command resets the emulation processor and holds it in the reset state. The "R>" prompt indicates that the processor is reset.

2. Type:

R> r 1000

You will see:

U>

The r command runs the processor from address 1000 hex.

3. Type:

U> **b**

You will see:

M>

The **b** command causes the emulation processor to "break" execution of whatever it was doing and begin executing within

**Getting Started 2-19**

the emulation monitor. The "M>" prompt indicates that the emulator is running in the monitor.

Note

If DMA transfer is in progress with BURST transfer mode, **b** command is suspended and occurs after DMA transfer is completed.

## Running the Sample Program

4. Type:

M> r 1000

The emulator changes state from background to foreground and begins running the sample program from location 1000 hex.

Note

The default number base for address and data values within HP 64700 is hexadecimal. Other number bases may be specified. Refer to the Tutorials chapter of this manual or the *HP 64700 User's Reference* manual for further details.

- 5. Let's look at the registers to verify that the address registers were properly initialized with the pointers to the input and output areas. Type:

- U> reg

You will see:

reg pc=001014 ccr=84 er0=00000000 er1=000ff800 er2=00000000 er3=00000000 reg er4=00000000 er5=00000000 er6=00000000 er7=000ff904 sp=000ff904 mdcr=c7

Notice that ER1 contains 0ff800 hex.

2-20 Getting Started

6. Verify that the input area command byte was cleared during initialization.

Type:

U> m -db 0ff800

You will see:

00ff800..00ff800 00

The input byte location was successfully cleared.

7. Now we will use the emulator features to make the program work. Remember that the program writes specific messages to the output area depending on what the input byte location contains. Type:

#### U> m 0ff800=41

This modifies the input byte location to the hex value for an ASCII "A". Now let's check the output area for a message.

U> m 0ff804..0ff823

You will see:

These are the ASCII values for Msg\_A.

Repeat the last two commands twice. The first time, use 42 instead of 41 at location ff800h and note that Msg\_B overwrites Msg\_A. Then try these again, using any number except 00, 41, or 42 and note that the Msg\_I message is written to this area.

## **Stepping Through** the Program

8. You can also direct the emulator processor to execute one instruction or number of instructions. Type:

M> s 1 1000; reg

This command steps 1 instruction from address 1000 hex, and displays registers. You will see:

0001000 - MOV.L #000ff904,ER7

PC =0001006

reg pc=001006 ccr=80 er0=00000000 er1=000ff800 er2=00000000 er3=00000000 reg er4=00000000 er5=00000000 er6=00000000 er7=000ff904 sp=000ff904 mdcr=c7

Notice that PC contains 1006 hex.

9. To step one instruction from present PC, you only need to type s at prompt. Type:

M> s;reg

You will see:

0001006 - MOV.L #000ff800,ER1

PC =000100c

reg pc=00100c ccr=80 er0=00000000 er1=000ff800 er2=00000000 er3=00000000 reg er4=00000000 er5=00000000 er6=00000000 er7=000ff904 sp=000ff904 mdcr=c7

## Tracing Program Execution

### Predefined Trace Labels

Three trace labels are predefined in the H8/3003 emulator. You can view these labels by entering the tlb (trace label) command with no options.

M> tlb

#### Emulation trace labels

tlb addr 16..39

tlb data 0..15

tlb stat 40..57

## Predefined Status Equates

Common values for the H8/3003 status trace signals have been predefined. You can view these predefined equates by entering the equ command with no options.

M> equ

```

### Equates ###

egu byte=0xxxxxx1xxxx1xxxx1xv

equ cpu=0xxxxxx1xxxx11xxxxxy

egu data=0xxxxxx1xxxx1x1xxxxv

equ dma=0xxxxxx1xxxx10xxxxxy

equ fetch=0xxxxxx1x1xx110xx01y

equ fg=0xxx1xxxxxxxxxxxxxx

egu grd=0xxxx011xxxx1xx1xxxy

equ intack=0xxxxxxx0xxxxxxxxxxx

equ io=0xxxxxx1xxxx1xx0xxxy

equ mem=0xxxxxx1xxx1xxx1xxxy

equ read=0xxxxxx1xxxxx1xxxxx1y

equ refresh=0xxxxxx1xxxx01xxxxxy

equ word=0xxxxxx1xxxx1xxxx0xy

equ write=0xxxxxx1xxxx1xxxxx0y

equ wrrom=0xxxx101xxxx1xx1xx0y

```

These equates may be used to specify values for the **stat** trace label when qualifying trace conditions.

### Specifying a Trigger

Now let's use the emulation analyzer to trace execution of the program. Suppose that you would like to start the trace when the analyzer begins writing data to the message output area. You can do this by specifying analyzer trigger upon encountering the address ff804 hex. Furthermore, you might want to store only the data written to the output area. This can be accomplished by modifying what is known as the "analyzer storage specification".

#### Note

For this example, you will be using the analyzer in the easy configuration, which simplifies the process of analyzer measurement setup. The complex configuration allows more powerful measurements, but requires more interaction from you to set up those measurements. For more information on easy and complex analyzer configurations and the analyzer, refer to the *HP 64700 Analyzer User's Guide* and the *User's Reference*.

Now, let's set the trigger specification. Type:

To store only the accesses to the address range ff804 through ff815 hex, type:

```

M> tsto addr=0ff804..0ff815

```

Let's change the data format of the trace display so that you will see the output message writes displayed in ASCII format:

Start the trace by typing:

M> t

You will see:

Emulation trace started

To start the emulation run, type:

Now, you need to have a "command" input to the program so that the program will jump to the output routines (otherwise the trigger will not be found, since the program will never access address ff804 hex). Type:

To display the trace list, type:

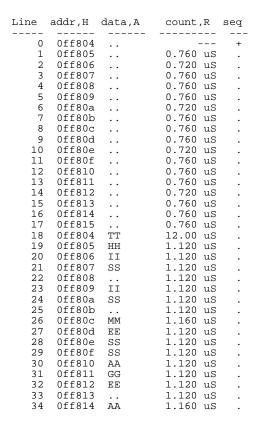

U> tl 0..34

You will see:

| Line                                                                                                                                                       | addr,H                                                                                                                                                                  | data,A                         | count,R                                                                                                                                                                                                                                                                                                                                                                                                                                                  | seq  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | Off804 Off805 Off806 Off807 Off808 Off809 Off800 Off800 Off800 Off806 Off810 Off811 Off812 Off813 Off814 Off815 Off806 Off806 Off807 Off808 Off808 Off808 Off809 Off800 |                                | 0.760 uS<br>0.760 uS<br>1.120 uS | seq+ |

| 19<br>20<br>21<br>22<br>23<br>24                                                                                                                           | 0ff805<br>0ff806<br>0ff807<br>0ff808<br>0ff809<br>0ff80a                                                                                                                | HH<br>II<br>SS<br><br>II<br>SS | 1.120 uS<br>1.120 uS<br>1.120 uS<br>1.120 uS<br>1.120 uS<br>1.120 uS                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 25<br>26                                                                                                                                                   | Off80b<br>Off80c                                                                                                                                                        | <br>MM                         | 1.120 uS<br>1.160 uS                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 32<br>33<br>34                                                                                                                                             | 0ff812<br>0ff813                                                                                                                                                        | EE<br>                         | 1.120 uS<br>1.120 uS                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

If you look at the last lines of the trace listing, you will notice that the analyzer seems to have stored only part of the output message, even though you specified more than the full range needed to store all of the message. The reason for this is that the analyzer has a storage pipeline, which holds states that have been acquired but not yet written to trace memory. To see all of the states, halt the analyzer by typing:

U> th

You will see:

Emulation trace halted

Now display the trace list:

U> tl 0..34

You will see:

As you can see, all of the requested states have been captured by the analyzer.

## Using Software Breakpoints

You can stop program execution at specific address by using **bp** (software breakpoint) command. When you define a software breakpoint to a certain address, the emulator will replace the opcode with one of undefined opcode (5770 hex) as software breakpoint instruction. When the emulator detects the special instruction, user program breaks to the monitor, and the original opcode will be placed at the breakpoint address. A subsequent run or step command will execute from this address.

If the special instruction was not inserted as the result of **bp** command (in other words, it is part of the user program), the "Undefined software breakpoint" message is displayed.

#### Note

You can set software breakpoints only at memory locations which contain instruction opcodes (not operands or data). If a software breakpoint is set at a memory location which is not an instruction opcode, the software breakpoint instruction will never be executed and the break will never occur.

#### **Note**

Because software breakpoints are implemented by replacing opcodes with the software breakpoint instruction, you cannot define software breakpoints in target ROM. You can, however, copy target ROM into emulation memory by **cim** command. (Refer to *HP 64700 Terminal Interface User's Reference* manual.)

### Displaying and Modifying the Break Conditions

Before you can define software breakpoints, you must enable software breakpoints with the **bc** (break conditions) command. To view the default break conditions and change the software breakpoint condition, enter the following commands.

M> bc

bc -d bp #disable

bc -e rom #enable

bc -d bnct #disable

bc -d cmbt #disable

#### M> bc -e bp

## Defining a Software Breakpoint

Now that the software breakpoint is enabled, you can define software breakpoints. Enter the following command to break on the address of the Write\_Msg label.

Run the program and verify that execution broke at the appropriate address.

M> r 1000 U> m 0ff800=41

!ASYNC\_STAT 615! Software break point: 000104e

M> reg

Notice that PC contains 104e.

When a breakpoint is hit, it becomes disabled. You can use the -e option to the bp command to re-enable the software breakpoint.

M> bp

###BREAKPOINT FEATURE IS ENABLED### bp 000104e #disabled

M> bp -e 104e

M> bp

###BREAKPOINT FEATURE IS ENABLED### bp 000104e #enabled

M> r 1000

U> m 0ff800=41

!ASYNC\_STAT 615! Software breakpoint: 000104e

M> bp

###BREAKPOINT FEATURE IS ENABLED###

bp 000104e #disabled

## Searching Memory for Strings or Numeric Expressions

The HP 64700 Emulator provides you with tools that allow you to search memory for data strings or numeric expressions. For example, you might want to know exactly where a string is loaded. To locate the position of the string "THIS IS MESSAGE A" in the sample program. Type:

M> ser 2000..2fff="THIS IS MESSAGE A"

pattern match at address: 0002000

You can also find numeric expressions. For example, you might want to find all of the **CMP.B** instructions in the sample program. Since a **CMP.B** instruction begins with aa hex, you can search for that value by typing:

M> ser -db 10000..106f=0aa

pattern match at address: 000101a

pattern match at address: 000101e

pattern match at address: 0001024

# Making Program Coverage Measurements

In testing your program, you will often want to verify that all possible code segments are executed. With the sample program, we might want to verify that all of the code is executed if a command "A", command "B", and an unrecognized command are input to the program.

To make this measurement, we must first reset the coverage status.

M> cov -r

#### Note

You should **always** reset the coverage status before making a coverage measurement. Any emulator system command which accesses emulation memory will affect the coverage status bit, resulting in measurement errors if the coverage status is not reset.

Now, run the program and input the three commands:

M> r 1000

M> m 0ff800=41

M> m 0ff800=42

M> m 0ff800=43

Make the coverage measurement:

U> cov 1000..106f

percentage of memory accessed: % 100.0

## Trace Analysis Considerations

There are some points you need to attend to in using the emulation analyzer. The following section describes such points.

### How to Specify the Trigger Condition

Suppose that you would like to start the trace when the program begins executing Exe\_Cmd routine.

To initialize the emulation analyzer, type:

U> tinit

To set the trigger condition, type:

U> tg addr=101e

Start the trace and modify memory so that the program will jump to the Exe\_Cmd routine:

U> **t**

U> m 0ff800=41

To display the trace list, type:

#### 2-30 Getting Started

| Line | addr,H | H8/3042 mnemonic,H | count,R  | seq |

|------|--------|--------------------|----------|-----|

|      |        |                    |          |     |

| 0    |        | aa41 fetch mem     |          | +   |

| 1    | 001014 | MOV.B @0ff800,R2L  | 0.120 uS |     |

| 2    | 001016 | 000f fetch mem     | 0.120 uS |     |

| 3    | 001018 | f800 fetch mem     | 0.120 uS |     |

| 4    | 00101a | CMP.B #00,R2L      | 0.120 uS |     |

| 5    | 0ff800 | 00xx read mem byte | 0.120 uS |     |

| 6    | 00101c | BEQ 001014         | 0.120 uS |     |

| 7    | 00101e | aa41 fetch mem     | 0.160 uS |     |

| 8    | 001014 | MOV.B @0ff800,R2L  | 0.120 uS |     |

| 9    | 001016 | 000f fetch mem     | 0.120 uS |     |

| 10   | 001018 | f800 fetch mem     | 0.120 uS |     |

| 11   | 00101a | CMP.B #00,R2L      | 0.120 uS |     |

| 12   | 0ff800 | 00xx read mem byte | 0.120 uS |     |

| 13   | 00101c | BEQ 001014         | 0.120 uS |     |

| 14   | 00101e | aa41 fetch mem     | 0.120 uS |     |

| 15   | 001014 | MOV.B @0ff800,R2L  | 0.160 uS |     |

| 16   | 001016 |                    | 0.120 uS |     |

| 17   |        | f800 fetch mem     | 0.120 uS |     |

| 18   |        | CMP.B #00,R2L      | 0.120 uS | _   |

| 19   | 0ff800 |                    | 0.120 uS |     |

| 20   | 00101c | _                  | 0.120 uS |     |

This is not what we were expecting to see. (We expected to see the program executed Exe\_Cmd routine which starts from 101e hex.) As you can see at the fist line of the trace list, address 101e hex appears on the address bus during the program executing Scan loop. This triggered the emulation analyzer before EXE\_Cmd routine was executed. To avoid mis-trigger by this cause, set the trigger condition to the second instruction of the routine you want to trace. Type:

To change the trigger position so that 10 states appear before the trigger in the trace list, type:

Start the trace again and modify memory:

U> t

U> m 0ff800=41

Now display the trace list:

U> tl -10..10

As you can see, the analyzer captured the execution of Exe\_Cmd routine which starts from line -2 of the trace list.

| Line | addr,H | H8/3042 mnemonic,H    | count,R  | seq |

|------|--------|-----------------------|----------|-----|

| -10  | 00101c | BEQ 001014            | 0.120 uS |     |

| -9   | 00101e | aa41 fetch mem        | 0.120 uS |     |

| -8   | 001014 | MOV.B @0ff800,R2L     | 0.120 uS |     |

| -7   | 001016 | 000f fetch mem        | 0.120 uS |     |

| -6   | 001018 | f800 fetch mem        | 0.120 uS |     |

| -5   | 00101a | CMP.B #00,R2L         | 0.160 uS |     |

| -4   | 0ff800 | 41xx read mem byte    | 0.120 uS |     |

| -3   | 00101c | BEQ 001014            | 0.120 uS |     |

| -2   | 00101e | CMP.B #41,R2L         | 0.120 uS |     |

| -1   | 001014 | 6a2a unused fetch mem | 0.120 uS |     |

| 0    | 001020 | BEQ 00102e            | 0.120 uS | +   |

| 1    | 001022 | 000a fetch mem        | 0.120 uS |     |

| 2    | 00102e | MOV.B #11,R3L         | 0.280 uS |     |

| 3    | 001030 | MOV.L #00002000,ER4   | 0.120 uS |     |

| 4    | 001032 | 0000 fetch mem        | 0.120 uS |     |

| 5    | 001034 | 2000 fetch mem        | 0.120 uS |     |

| 6    | 001036 | BRA 00104e            | 0.120 uS |     |

| 7    | 001038 | 0014 fetch mem        | 0.120 uS |     |

| 8    | 00104e | MOV.L #000ff804,ER5   | 0.240 uS |     |

| 9    | 001050 | 000f fetch mem        | 0.160 uS |     |

| 10   | 001052 | f804 fetch mem        | 0.120 uS |     |

## Store Condition and Disassembling

When you specify store condition with tsto command, disassembling of program execution may not be accurate.

Type:

U> tinit

U> **t**

U> tl 0..20

| Line | addr,H | H8/3042 mnemonic,H | count,R  | seq |

|------|--------|--------------------|----------|-----|

|      | 001016 | 0005 5-1-1-        |          |     |

| 0    |        | 000f fetch mem     | 0 100 0  | +   |

| 1    |        | f800 fetch mem     | 0.120 uS | •   |

| 2    |        | CMP.B #00,R2L      | 0.160 uS | •   |

| 3    | 0ff800 |                    | 0.120 uS |     |

| 4    | 00101c | BEQ 001014         | 0.120 uS |     |

| 5    | 00101e | aa41 fetch mem     | 0.120 uS |     |

| 6    | 001014 | MOV.B @0ff800,R2L  | 0.120 uS |     |