# **HP 64873**

# V-Series Cross Assembler/ Macro Preprocessor

# Reference

HP Part No. 64873-97007 Printed in U.S.A. June 1991

**Edition 3**

# Certification and Warranty

## Certification

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

## Warranty

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its option, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service, Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country. HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### **Limitation of Warranty**

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environment specifications for the product, or improper site preparation or maintenance.

No other warranty is expressed or implied. HP specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### **Exclusive Remedies**

The remedies provided herein are buyer's sole and exclusive remedies. HP shall not be liable for any direct, indirect, special, incidental, or consequential damages, whether based on contract, tort, or any other legal theory.

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office.

## **Notice**

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

© Copyright 1991, Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

UNIX is a registered trademark of UNIX System Laboratories Inc. in the U.S.A. and in other countries.

V20 and V30 are registered trademarks of NEC Corporation.

V25, V33, V35, V40, V50, V53, and V60 are trademarks of NEC Corporation.

Hewlett-Packard Company Logic Systems Division 8245 North Union Boulevard Colorado Springs, CO 80920, U.S.A.

**RESTRICTED RIGHTS LEGEND** Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (C) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227-7013. Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304

# **Printing History**

New editions are complete revisions of the manual. The date on the title page changes only when a new edition is published.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual was issued. Many product updates and fixes do not require manual changes, and manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual revisions.

Edition 1 64873-97001, February 1990 Edition 2 64873-97004, July 1990

Edition 3 64873-97007, June 1991

# **Using This Manual**

Your HP 64873 V-Series Cross Assembler/Linker documentation consists of three manuals:

- 64873 V-Series Cross Assembler/Macro Preprocessor Reference

- 64873 V-Series Cross Linker/Librarian Reference

- A 64873 V-Series Cross Assembler/Linker User's Guide

# The Reference Manuals

The two *Reference* manuals are in the same binder. The *Reference* manuals document the basic features of the HP 64873 Cross Assembler/Linker (assembly language, assembler syntax, directives, macros, assembler controls, program segments, and relocation, linker and librarian commands, and so on).

## The User's Guide

The HP 64873 V-Series Cross Assembler/Linker User's Guide contains information on how to start the HP 64873 product on your host computer. It also gives the command syntax and some short examples to get you started with the product.

## In this Book

This documentation is written for the experienced program developer, and assumes a working knowledge of the V-Series family of microprocessors, and the Intel 8087 or NEC 72291 coprocessors.

Several useful and informative program examples and example fragments have been provided to clarify the references.

This manual is intended as a reference for the features of the HP 64873 Advanced Cross Assembler/Macro Preprocessor. However, this documentation does not describe the microprocessor itself, nor does it

teach you how to write working programs. For such information, refer to the following source:

- NEC 70108(V20) Microprocessor User's Manual.

- NEC 70320 (V25) Microprocessor User's Manual

- NEC 70136 (V33) Microprocessor User's Manual

For additional information call (800) 632-3531.

## **Manual Organization**

This manual is organized in two sections. The first nine chapters of this manual describe the asv20/asv33 assembler. The last four chapters describe the apv20/apv33 macro preprocessor. There are several appendixes that contain information about both the assembler and macro preprocessor including a description of the acvtv20 porting tool. This nonsupported porting tool can help with translation of source files from the HP 64853 dialect to the HP 64873 dialect. Another nonsupported tool is intel2nec, which can assist in the translation of 8086 assembly source to NEC V20 assembly source. The information in this manual consists of the following topics:

#### **Assembler Information:**

- Functional description and list of features.

- Assembly language syntax, character set, symbols (including reserved words), and constants.

- Symbol and expression attributes.

- Alphabetical description of the assembler directives on pages specially formatted for quick reference.

- Thorough discussion of assembler expressions, operands, and a list of the V-Series, Intel 8087, and NEC 72291 instruction mnemonics with accepted operands.

- Description of assembler control statements, including primary and general controls.

■ Description of assembler listings and symbol table listings.

# **Macro Preprocessor Information:**

- Introduction to the macro preprocessor and macro functions.

- Discussion of the elements of macro expressions.

- Description and reference for the pre-defined apv20/apv33 macro functions. How to create user-defined macros and how they are treated by the macro preprocessor.

# Notes

# **Contents**

| 1 | Assembler Introduction      |

|---|-----------------------------|

|   | Introduction                |

|   | Instruction Set             |

|   | Target Microprocessors      |

|   | Assembler Operation         |

|   | File Formats                |

|   | Input File Characteristics  |

|   | Output File Characteristics |

|   | asv20/asv33 Features        |

|   | Macro Preprocessor          |

| 2 | Assembler Syntax            |

|   | Introduction                |

|   | Assembler Character Set     |

|   | Symbols                     |

|   | Symbol Formation            |

|   | Keywords                    |

|   | Instruction Mnemonics       |

|   | Codemacro                   |

|   | Label                       |

|   | Variable                    |

|   | Structure Name              |

|   | Structure Field Name        |

|   | Record Name                 |

|   | Record Field Name           |

|   | Segment Name                |

|   | Group Name                  |

|   | EQU Symbols                 |

|   | Constants                   |

|   | Integer Constant            |

|   | Real Constant               |

|   | Character Constant          |

|   | Delimiters                  |

|   | Assembler Statements        |

Contents-1

|   | General Syntax       2-12         Comment       2-13         Continuation Lines       2-14 |

|---|--------------------------------------------------------------------------------------------|

| 3 | Symbol and Expression Attributes                                                           |

|   | Introduction                                                                               |

|   | TYPE                                                                                       |

|   | BASE                                                                                       |

|   | INDEX       3-3         SEGMENT       3-4                                                  |

|   | SEGMENT RELOCATION                                                                         |

|   | RELOCATION TYPE                                                                            |

|   | SEGMENT ADDRESSABILITY                                                                     |

|   | PS ADDRESSABILITY                                                                          |

| 4 | Assembler Directives                                                                       |

|   | Introduction                                                                               |

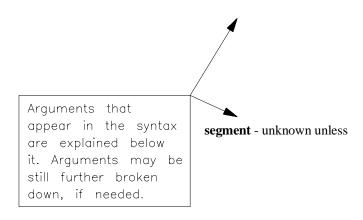

|   | Syntax Conventions                                                                         |

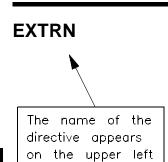

|   | EXTRN                                                                                      |

|   | Segmentation Directives                                                                    |

|   | Program Segmentation                                                                       |

|   | Default Segment - ??SEG                                                                    |

|   | Data Definition Directives                                                                 |

|   | Data Objects                                                                               |

|   | Program Linkage Directives                                                                 |

|   | Program Linkage                                                                            |

|   | ASGNSFR                                                                                    |

|   | ASSUME                                                                                     |

|   | DB, DW, DD, DS, DQ, DL, DT 4-13                                                            |

|   | END                                                                                        |

|   | EQU                                                                                        |

|   | EVEN                                                                                       |

|   | EXTRN                                                                                      |

|   | V33 Considerations                                                                         |

|   | GROUP                                                                                      |

|   | LABEL                                                                                      |

|   | NAME                                                                                       |

|   | ORG4-39                                                                                    |

|   | PROC/ENDP                                                                                  |

|   | PUBLIC 4-43                                                                                |

|   | DVD GE                                |    |

|---|---------------------------------------|----|

|   | PURGE                                 |    |

|   | RECORD                                | _  |

|   | Allocating Record Storage             |    |

|   | SEGMENT/ENDS                          |    |

|   | Multiple Definitions of a Segment 4-5 | _  |

|   | SETIDB                                | 6  |

|   | STRUC/ENDS                            | 8  |

|   | Allocating Structure Storage          | 9  |

| 5 | Expressions                           |    |

|   | Introduction                          | .1 |

|   | Reference Syntax Conventions          |    |

|   | Expression Overview                   |    |

|   | Absolute Expression                   |    |

|   |                                       |    |

|   | Relocatable Expression                |    |

|   | External Expression                   |    |

|   | Expression Operands                   |    |

|   | Numeric Values                        |    |

|   | Memory and Register Expressions       |    |

|   | EQU                                   |    |

|   | Expression Operators Introduction     | 1  |

|   | Arithmetic Operators                  | 1  |

|   | Unary Plus, Unary Minus               | 1  |

|   | Binary Addition, Subtraction          | 2  |

|   | [ ] Square Brackets                   | 3  |

|   | . (Dot operator)                      | 4  |

|   | Multiplication, Division, Modulo 5-1  | 5  |

|   | SHL, SHR                              |    |

|   | HIGH, LOW                             | 7  |

|   | Logical Operators                     |    |

|   | AND, OR, XOR                          |    |

|   | NOT                                   |    |

|   | EQ, NE, LT, LE, GT, GE                |    |

|   | Memory Operators                      |    |

|   | SHORT                                 |    |

|   |                                       |    |

|   |                                       |    |

|   | PTR                                   |    |

|   | Segment or Group Override             |    |

|   | OFFSET                                | _  |

|   | SEG                                   |    |

|   | TVPE 5_2                              | 7  |

|   | LENGTH                                            |

|---|---------------------------------------------------|

|   | SIZE                                              |

|   | Record Operators                                  |

|   | MASK                                              |

|   | WIDTH                                             |

|   | Segment and Group Operators 5-33                  |

|   | SMOFFSET                                          |

|   | GROFFSET                                          |

|   | SMSIZE                                            |

|   | GRSIZE                                            |

|   | Operator Precedence                               |

| 6 | Instructions and Operands                         |

|   | Introduction                                      |

|   | Operand                                           |

|   | Accepted Operands                                 |

|   | Operand Positioning                               |

|   | Immediate Values                                  |

|   | Registers                                         |

|   | Memory Expressions and the MODRM Byte 6-8         |

|   | Segment Addressability and Overrides 6-10         |

|   | Addressability Checking 6-10                      |

|   | Default Segments 6-11                             |

|   | Segment Overrides 6-11                            |

|   | Improper Uses of Segment Overrides 6-12           |

|   | Segment Override Byte 6-12                        |

|   | Overrides and Checking Against ASSUME 6-12        |

|   | Segment Override Byte Generation 6-13             |

|   | The V25 Family of Processors 6-14                 |

|   | The Instruction Set                               |

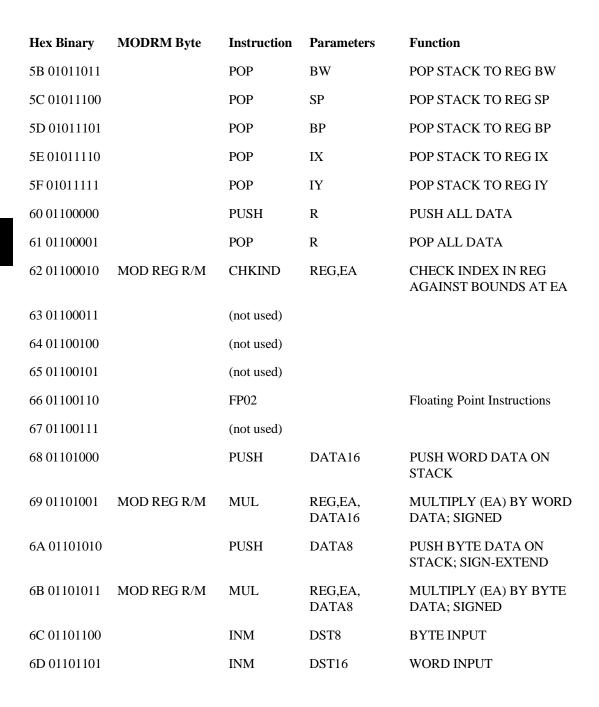

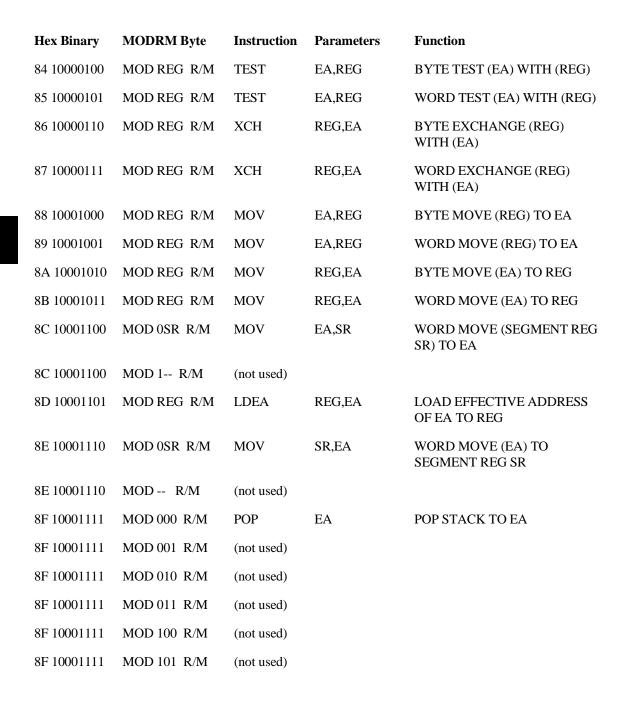

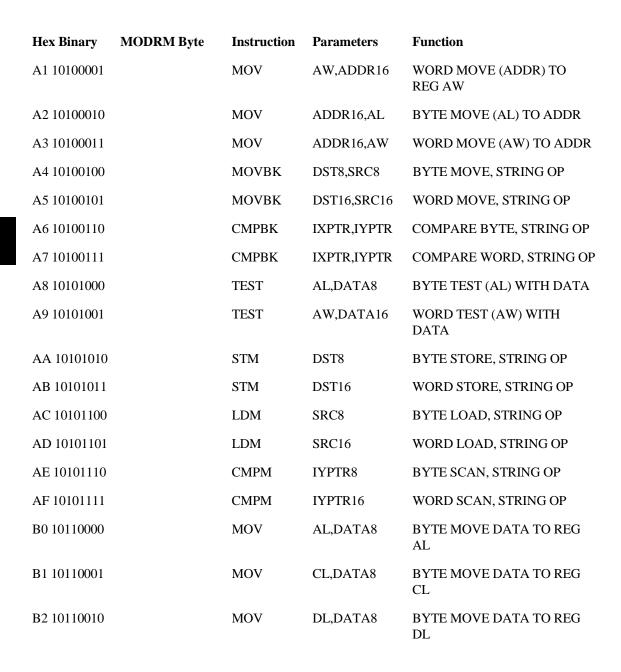

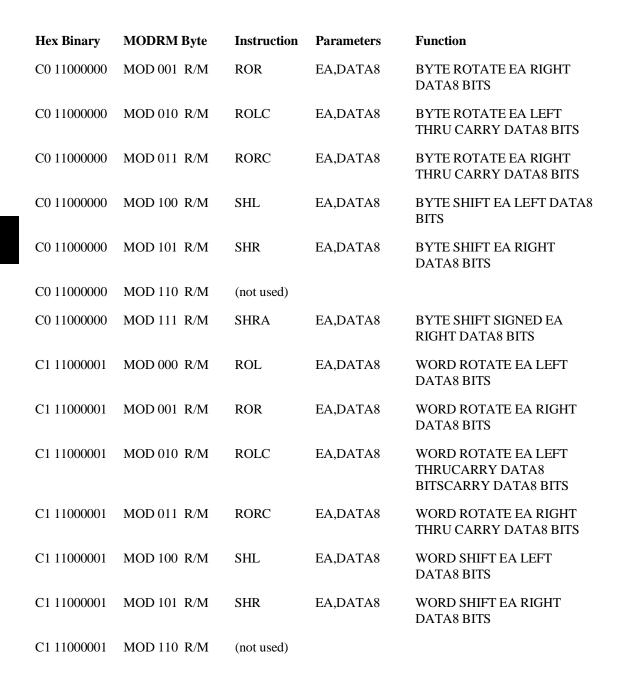

|   | asv20 Assembler Instruction Set 6-23              |

| 7 | Assembler Controls                                |

|   | Introduction                                      |

|   | General Syntax for Assembler Controls             |

|   | Primary and General Controls                      |

|   | Controls on the Command Line                      |

|   | Control Conflicts                                 |

|   | Controls and File Names                           |

|   | Control Abbreviations                             |

|   | Controls and Macro Preprocessor (apv20/apv33) 7-3 |

|   | * \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \           |

| Primary Controls                               | . 7-4 |

|------------------------------------------------|-------|

| [NO]CAPITALS                                   | . 7-4 |

| DATE(string)                                   | . 7-4 |

| [NO]DEBUG                                      |       |

| [NO]ERRORPRINT (filename)                      | . 7-5 |

| EXTERN_CHECK                                   | . 7-5 |

| GROUP_INFO                                     | . 7-5 |

| [NO]HLASSYM                                    | . 7-6 |

| [NO]MACRO(string)                              | . 7-6 |

| MOD087                                         | . 7-6 |

| MOD287                                         | . 7-6 |

| MOD72291                                       | . 7-6 |

| MODV20                                         | . 7-6 |

| MODV25                                         | . 7-7 |

| MODV33                                         |       |

| [NO]OBJECT (filename)                          | . 7-7 |

| OPTIMIZE                                       | . 7-7 |

| PAGELENGTH(n)                                  | . 7-8 |

| PAGEWIDTH(n)                                   | . 7-8 |

| [NO]PAGING                                     | . 7-8 |

| [NO]PRINT(filename)                            |       |

| [NO]SYMBOLS                                    |       |

| [NO]TYPE                                       |       |

| [NO]UNREFERENCED_EXTERNALS                     | . 7-9 |

| WARNING                                        |       |

| WORKFILES( )                                   |       |

| [NO]XREF                                       |       |

| General Controls                               |       |

| EJECT                                          | 7-11  |

| [NO]GEN                                        | 7-11  |

| GENONLY                                        | 7-11  |

| INCLUDE(filename)                              | 7-11  |

| [NO]LIST                                       | 7-12  |

| RESTORE                                        | 7-12  |

| SAVE                                           | 7-13  |

| TITLE(string)                                  | 7-13  |

| Operational Differences in the Different Modes | 7-14  |

| V20 Mode                                       | 7-14  |

| V25 Mode                                       | 7-14  |

| V33 Mode                                       | 7-14  |

| 8087 Mode                                      | 7-14  |

|    | 80287 Mode                                              |

|----|---------------------------------------------------------|

| 8  | <b>Assembler Listing Description</b>                    |

|    | Introduction                                            |

|    | Assembly Listing                                        |

|    | Cross Reference and Symbol Table Format Description 8-5 |

|    | Label                                                   |

|    | Type                                                    |

|    | Value                                                   |

|    | Cross Reference                                         |

| 9  | Codemacros                                              |

|    | Overview                                                |

|    | Referencing Codemacros                                  |

|    | Alphabetical Listing of the Codemacro Directives 9-2    |

|    | Codemacro Directives                                    |

|    | CODEMACRO                                               |

|    | ENDM                                                    |

|    | Codemacro Matching                                      |

|    | The Specmod Field                                       |

|    | Range Specification                                     |

|    | Examples:                                               |

|    | Codemacro Matching Examples 9-14                        |

|    | Expressions in Codemacros                               |

|    | Syntax:                                                 |

|    | Directives within Codemacros                            |

|    | DB, DD, DW                                              |

|    | MODRM                                                   |

|    | Syntax                                                  |

|    | NOSEGFIX                                                |

|    | Record Name Initialization                              |

|    | RELB, RELW                                              |

|    | RFIX, RFIXM, RNFIX, RNFIXM, RWFIX 9-24                  |

|    | SEGFIX                                                  |

| 10 | <b>Macro String Preprocessor Introduction</b>           |

|    | Introduction                                            |

|    | Input Source Characteristics                            |

|    | The Metacharacter '%' And The Call Pattern 10-2         |

|    | Metacharacter Syntax                                    |

|    | Literal Character *                                                                                                                                                                                                            | 10-5                                                                                             |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|    | Input Parsing                                                                                                                                                                                                                  | 10-5                                                                                             |

|    | Output Buffering                                                                                                                                                                                                               | 10-6                                                                                             |

|    | Include Files                                                                                                                                                                                                                  | 10-6                                                                                             |

|    |                                                                                                                                                                                                                                |                                                                                                  |

| 11 | <b>Elements Of Macro Expressions</b>                                                                                                                                                                                           |                                                                                                  |

|    | Introduction                                                                                                                                                                                                                   | 11-1                                                                                             |

|    | Character Set                                                                                                                                                                                                                  | 11-2                                                                                             |

|    | Numbers                                                                                                                                                                                                                        | 11-3                                                                                             |

|    | Symbols                                                                                                                                                                                                                        | 11-3                                                                                             |

|    | Balanced Text String (baltex)                                                                                                                                                                                                  | 11-4                                                                                             |

|    | Expressions and Operators                                                                                                                                                                                                      | 11-4                                                                                             |

|    | HIGH, LOW                                                                                                                                                                                                                      | 11-5                                                                                             |

|    | NOT                                                                                                                                                                                                                            | 11-6                                                                                             |

|    | Add (+), Subtract (—)                                                                                                                                                                                                          | 11-6                                                                                             |

|    | Multiply (*), Divide (/), MOD                                                                                                                                                                                                  | 11-6                                                                                             |

|    | SHL, SHR                                                                                                                                                                                                                       | 11-7                                                                                             |

|    | AND, OR, XOR                                                                                                                                                                                                                   | 11-7                                                                                             |

|    | EQ, LE, LT, GE, GT, NE                                                                                                                                                                                                         | 11-7                                                                                             |

|    |                                                                                                                                                                                                                                |                                                                                                  |

| 12 | Pre-Defined Macro Functions                                                                                                                                                                                                    |                                                                                                  |

|    |                                                                                                                                                                                                                                |                                                                                                  |

|    | Introduction                                                                                                                                                                                                                   | 12-1                                                                                             |

|    | Introduction                                                                                                                                                                                                                   | 12-1<br>12-1                                                                                     |

|    |                                                                                                                                                                                                                                |                                                                                                  |

|    | Pre-Defined Macro Functions                                                                                                                                                                                                    | 12-1                                                                                             |

|    | Pre-Defined Macro Functions                                                                                                                                                                                                    | 12-1<br>12-2                                                                                     |

|    | Pre-Defined Macro Functions                                                                                                                                                                                                    | 12-1<br>12-2<br>12-3                                                                             |

|    | Pre-Defined Macro Functions  %' (Comment Function)                                                                                                                                                                             | 12-1<br>12-2<br>12-3<br>12-5                                                                     |

|    | Pre-Defined Macro Functions                                                                                                                                                                                                    | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-6                                                     |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT                                                                                       | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-6                                                     |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN                                              | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-6<br>12-7                                             |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH                                       | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9                                     |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR                             | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9                                     |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT                     | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-6<br>12-7<br>12-8<br>12-11<br>12-11                   |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT %SET                | 12-1<br>12-3<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-11<br>12-12                   |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT %SET %SUBSTR        | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-11<br>12-12                   |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT %SET %SUBSTR %WHILE | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-11<br>12-12<br>12-13          |

|    | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT %SET %SUBSTR        | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-11<br>12-12<br>12-13          |

| 13 | Pre-Defined Macro Functions %' (Comment Function) %n and %( (Escape and Bracket Functions) %EQS, %NES, %LTS, %LES, %GTS,%GES %EVAL %EXIT %IF (Conditional Assembly Function) %LEN %MATCH %METACHAR %REPEAT %SET %SUBSTR %WHILE | 12-1<br>12-2<br>12-3<br>12-5<br>12-6<br>12-6<br>12-7<br>12-8<br>12-13<br>12-13<br>12-14<br>12-14 |

|   | %DEFINE       13-2         Macro Reference       13-4         What is Output?       13-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Referencing Macro-time Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A | Error Message Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | Error Classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | Warning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | Fatal Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| В | Assembler Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | Syntax Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ~ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C | Macro String Preprocessor Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | Error Codes and Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D | ASCII Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| E | Converting HP 64853 Assembly Language Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| E | Converting HP 64853 Assembly Language Programs  Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | IntroductionE-1acvtv20 IntroductionE-2Assembler DifferencesE-2IFE-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E | IntroductionE-1acvtv20 IntroductionE-2Assembler DifferencesE-2IFE-3EQUE-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E | IntroductionE-acvtv20 IntroductionE-2Assembler DifferencesE-2IFE-3EQUE-3MACROE-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| E | Introduction         E-1           acvtv20 Introduction         E-2           Assembler Differences         E-3           IF         E-3           EQU         E-3           MACRO         E-3           REPT         E-4                                                                                                                                                                                                                                                                                                                                                                 |

| E | Introduction         E-1           acvtv20 Introduction         E-2           Assembler Differences         E-3           IF         E-3           EQU         E-3           MACRO         E-3           REPT         E-4           SET         E-4                                                                                                                                                                                                                                                                                                                                       |

| E | Introduction         E-1           acvtv20 Introduction         E-2           Assembler Differences         E-2           IF         E-3           EQU         E-3           MACRO         E-3           REPT         E-4           SET         E-4           External Declarations         E-4                                                                                                                                                                                                                                                                                           |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction         E-1           acvtv20 Introduction         E-2           Assembler Differences         E-2           IF         E-3           EQU         E-3           MACRO         E-3           REPT         E-4           SET         E-4           External Declarations         E-4           Porting Procedure—Main Files with INCLUDE Files         E-6           acvtv20 Warnings, apv20 Errors, asv20 Errors         E-7           Code Substitution         E-8           BIN, DECIMAL, HEX, OCT         E-10                                                            |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E | Introduction         E-1           acvtv20 Introduction         E-2           Assembler Differences         E-2           IF         E-3           EQU         E-3           MACRO         E-3           REPT         E-4           SET         E-4           External Declarations         E-4           Porting Procedure— Main Files with INCLUDE Files         E-6           acvtv20 Warnings, apv20 Errors, asv20 Errors         E-7           Code Substitution         E-8           BIN, DECIMAL, HEX, OCT         E-10           DECIMAL         E-10           HEX         E-10 |

| E | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| .IF, .GOTO, and .NOP Directives       | E-12 |

|---------------------------------------|------|

| Looping Structures                    | E-13 |

| Numeric, String, and Null Comparisons |      |

|                                       | E-14 |

| Macro Calls                           | E-15 |

| acvtv20(1) Command Syntax             |      |

| Old and New List                      | E-20 |

| ASCII                                 | E-20 |

| ALIGN                                 | E-20 |

| ASSUME                                | E-20 |

| COMN                                  | E-21 |

| DATA                                  |      |

| DBS                                   | E-21 |

| DDS                                   | E-21 |

|                                       | E-21 |

|                                       | E-22 |

| EQU                                   |      |

| EXPAND                                |      |

| EXT                                   | E-22 |

| GLB                                   | E-23 |

| IF (Macro)                            | E-23 |

| INCLUDE Control                       | E-23 |

| LABEL Directive                       | E-23 |

| Label Field                           | E-24 |

| LIST                                  | E-24 |

| MACRO                                 | E-24 |

|                                       | E-25 |

| NAME                                  | E-25 |

| NOLIST                                | E-25 |

| NOWARN                                | E-25 |

| Operator Field                        | E-25 |

| ORG                                   | E-26 |

| PROC                                  | E-27 |

| PROG                                  | E-28 |

| REAL                                  | E-28 |

| Reserved Words                        | E-28 |

| SPC                                   | E-28 |

| SKIP                                  | E-29 |

|                                       | E-29 |

| WARN                                  | E-29 |

| * (Comment)                           | E 20 |

**Contents-9**

|     | INTEL2NEC(1)                               |

|-----|--------------------------------------------|

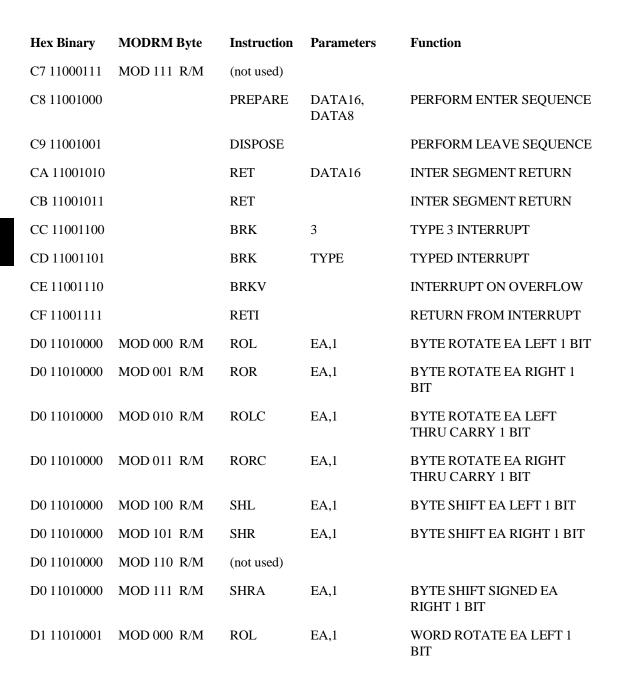

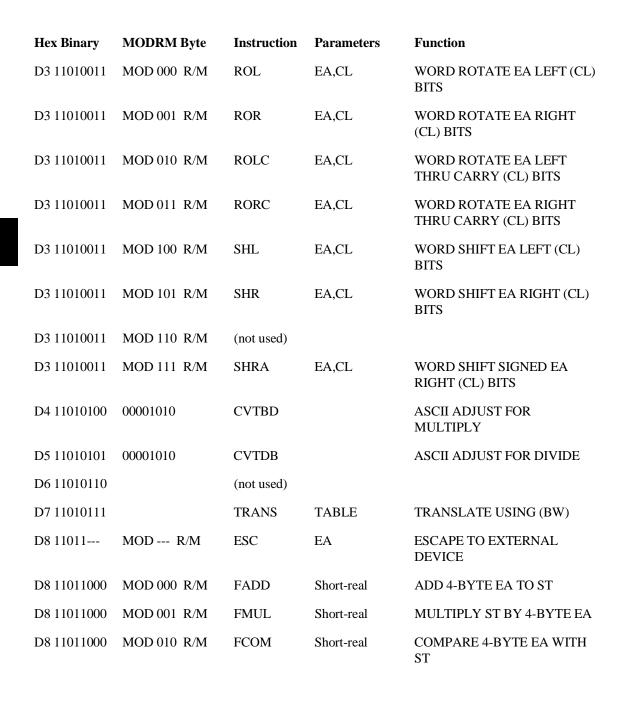

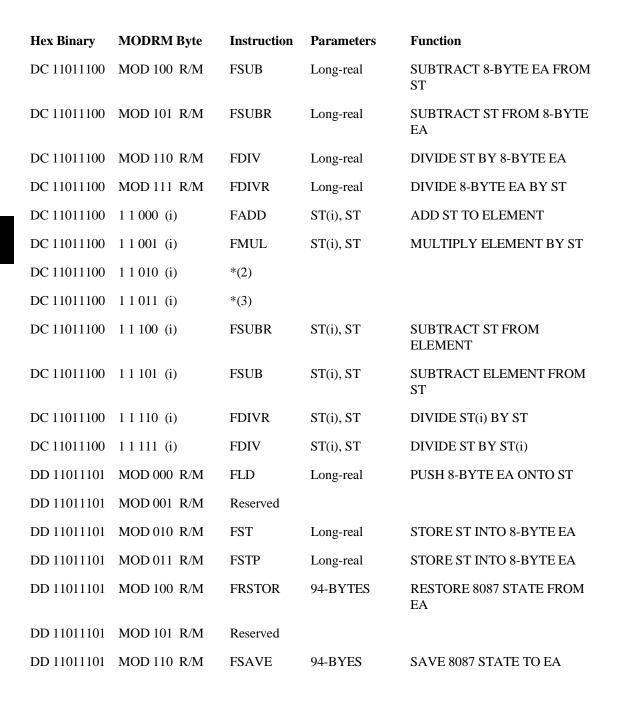

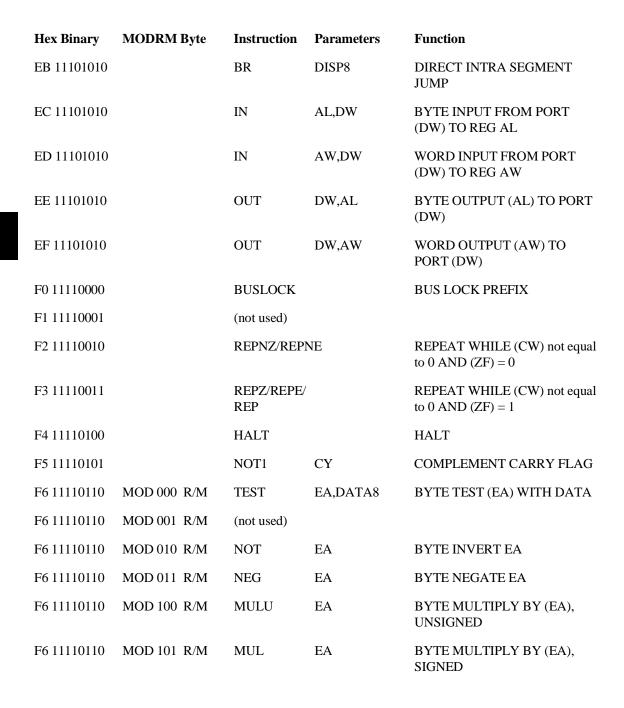

| F   | V-Series Instructions in Hexadecimal Order |

| G   | V-Series Instruction Set Summary FOOTNOTES |

| Inc | lex                                        |

# Illustrations

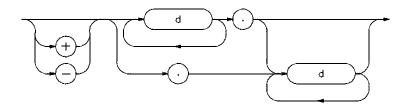

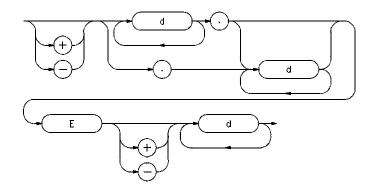

| Figure 2-1. Syntax for Decimal Real Without Exponent | 2-10 |

|------------------------------------------------------|------|

| Figure 2-2. Syntax for Decimal Real with Exponent    |      |

| Figure 4-1. "Partial" Record Definition              |      |

| Figure 4-2. Structure Definition and Allocation      | 4-61 |

| Figure 5-1. SHL Operator                             | 5-16 |

| Figure 6-1. V20/25/33 Registers                      | 6-5  |

| Figure 8-1. Sample Assembler Listing                 | 8-3  |

| Figure 8-2. Cross Reference for Sample Listing       | 8-5  |

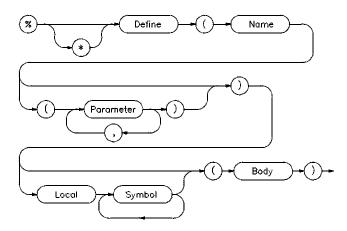

| Figure 13-1. Syntax for User-Defined Macros          | 13-2 |

# **Tables**

| Table 2-1. Assembler Character Set                        |

|-----------------------------------------------------------|

| Table 2-2. asv20/asv33 Keywords and Instructions 2-4      |

| Table 5-1. Binary Plus and Minus Results 5-12             |

| Table 5-2. Operator Precedence                            |

| Table 6-1. RAM Register Bank Structure Definitions 6-15   |

| Table 6-2. RAM and Special Function Register Mapping 6-16 |

| Table 6-3. Operand Codes                                  |

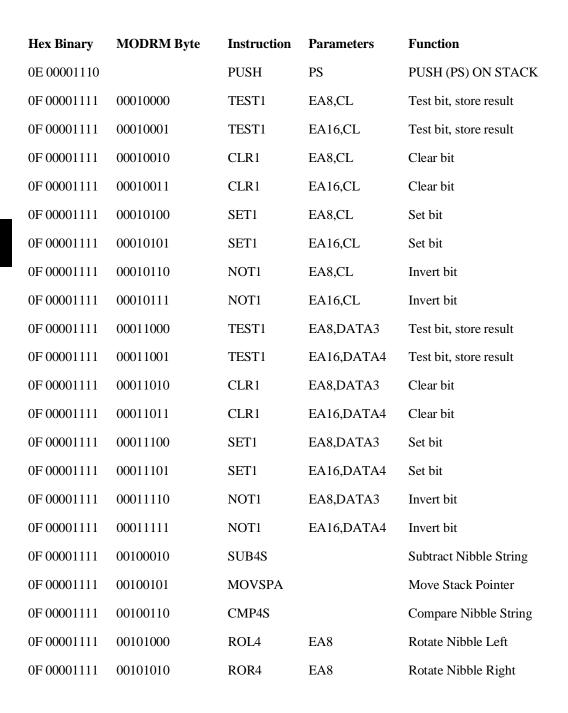

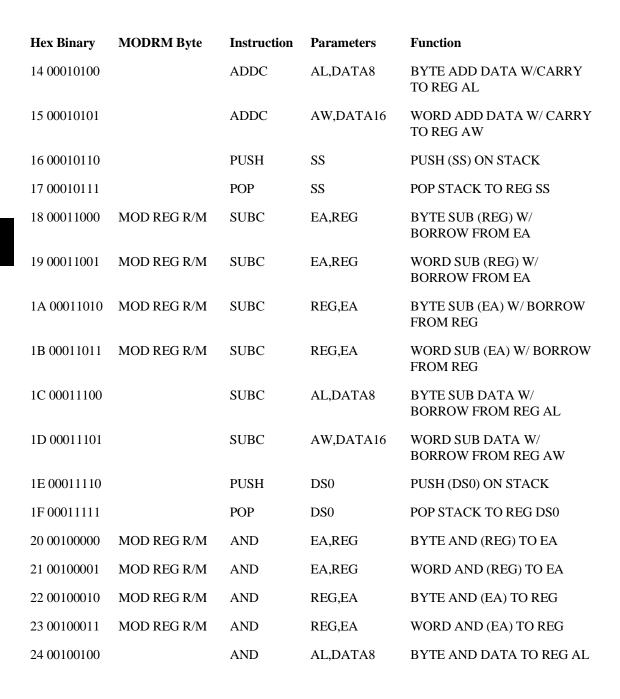

| Table 6-4. Assembler Instruction Set 6-23                 |

| Table 9-1. Codemacro Directives                           |

| Table 9-2. Specmods and Parameter Matches 9-8             |

| Table 9-3. Absolute Number Conversion for Registers 9-12  |

| Table 9-4. Arguments and Actual Parameters 9-14           |

| Table 9-5. Directives within Codemacros 9-17              |

| Table 11-1. Macro Preprocessor Character Set              |

| Table 11-2. Operator Precedence                           |

| Table 12-1. Predefined Macro Functions                    |

| Table D-1. ASCII Codes                                    |

| Table F-1. V-Series and 8087 Instructions F-1             |

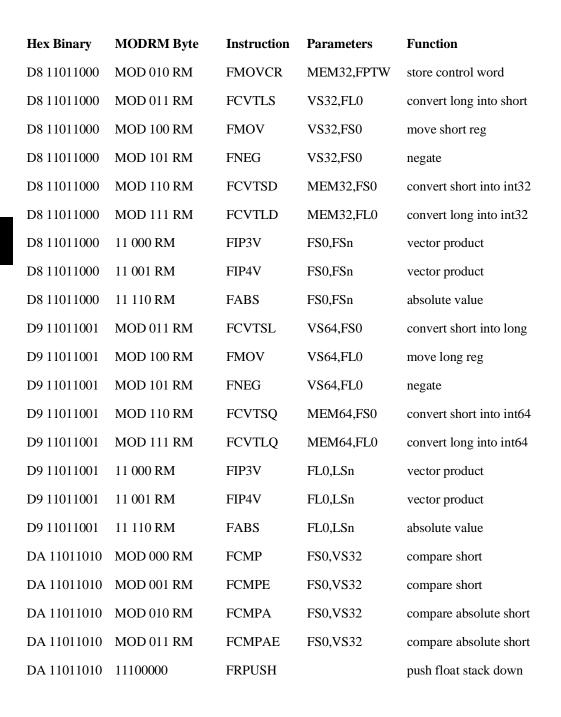

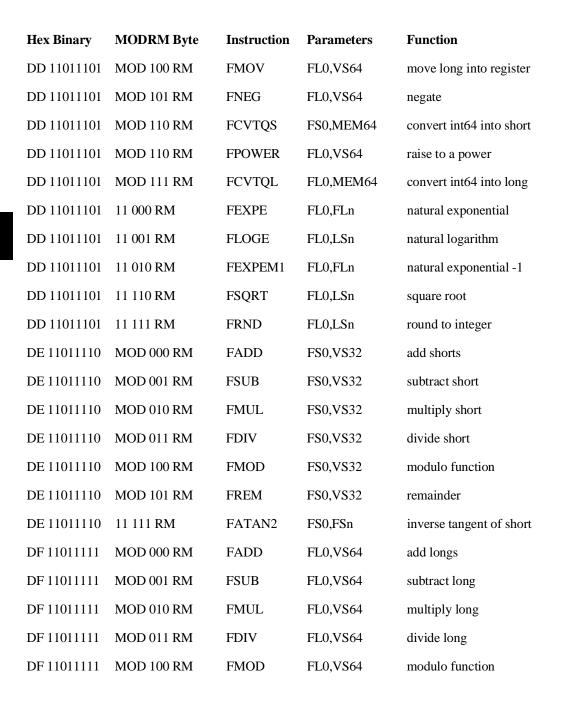

| Table F-2. 72291 Instructions                             |

# **Assembler Introduction**

# Introduction

This chapter introduces the assembler by discussing the instruction set, target microprocessors, input and output file formats, and other similar information about the asv20/asv33 Advanced Cross Assembler. This chapter is primarily a brief overview, but it does highlight some important features of the asv20/asv33 assembler. The asv20 assembler is very similar to the asv33 assembler, but they differ in terms of their default targets.

# **Instruction Set**

The asv20/asv33 assembler supports NEC instruction mnemonics, op codes, and syntax for the target microprocessors and thus is compatible with those used in NEC software and documentation.

The supported instruction set is listed in the chapter titled "Instructions and Operands." For further information about the instruction set, refer to the 70108(V20) Microprocessor User's Manual mentioned in the "Using This Manual" section at the beginning of this manual. References for the V25 and V33 are also noted in that section.

# **Target Microprocessors**

The asv20/asv33 assembler supports the NEC V20, V25, and V33 chip families. The V20 family includes the V20, V30, V40, and V50. The V25 family includes the V25, V35, V25+, and V35+. The V33 family includes the V33 and V53. The asv20 assembler defaults to the V20 and 8087 instruction set, while asv33 defaults to the V33 and 72291 instruction sets.

The asv20/asv33 assembler also translates instructions specific to the Intel 8087 or NEC 72291 floating-point coprocessors for coprocessor execution.

# Assembler Operation

asv20/asv33 is a two pass assembler. On the first pass, labels, variables, and other user-defined symbols are examined and placed in an internal symbol table. Additionally, structure definitions are stored.

On the second pass, asv20/asv33 generates the object code, resolves symbolic addresses, and outputs the object module if the assembly was error free. If it was not error free, then asv20/asv33 displays errors on the output listing device and also a cumulative error count. In addition to the object module, asv20/asv33 can also output an HP 64000 format assembler symbol file for use in analysis tools.

The assembly listing produced during pass two contains information pertaining to the assembled program, including opcodes, assembled data, and the original source statements. Based on command line options, asv20/asv33 may also output a symbol table or cross reference table which gives further information not found in the standard assembly listing. Refer to the chapter titled "Assembler Listing Description" for a more complete explanation of the assembly listing and cross reference or symbol table information.

## **File Formats**

# Input File Characteristics

The source file input for the asv20/asv33 assembler is a text file containing V-Series instructions, assembler directives, and assembler controls. This file can be produced from an editor or the output file from another component of the HP 64873 package, the apv20/apv33 macro preprocessor.

#### 1-2 Assembler Introduction

# Output File Characteristics

#### HP-OMF 86

asv20/asv33 produces a relocatable output object file in HP-OMF 86 format relocatable. HP-OMF 86 format relocatable is a superset of Intel Binary OMF relocatable. HP-OMF 86 format relocatable contains extensions to facilitate code integration and debugging. This format has not been verified to be strictly compatible with Intel Binary OMF relocatable. HP-OMF 86 format relocatable files, therefore, may not work correctly with tools or systems designed to consume Intel Binary OMF relocatable.

### **HP 64000 Assembler Symbol File**

asv20/asv33 can optionally produce an HP 64000 format assembler symbol file. This file is used by analysis tools. The purpose of the assembler symbol file is to preserve the relationship between symbolic names that appeared in the original source file and the memory locations that they referenced.

# asv20/asv33 Features

This final section lists some of the notable features of the asv20/asv33 Advanced Cross Assembler. The asv20/asv33 assembler

- generates code for the complete NEC V20, V25, and V33 instruction set

- supports Intel 8087 and NEC 72291 floating-point coprocessor instructions

**Assembler Introduction 1-3**

- permits repeated definition of the same or of different code, data, and constants segments within a single source file

- has high-level-language-like data structures which permit the definition of structured data types and bit fields

- supports symbolic memory references via symbol names

- allows high degree of control over the assembly process (conditional assembly, structured control, listing and output control) through a flexible set of assembly control statements

- gives detailed, well-documented error messages

- produces extensive program listings that can include symbol table/cross reference information

- has a command line interface tailored to the host operating system

- as part of the HP 64873 V-Series Advanced Cross Assembler/Linker package, is well-integrated with the HP 64906 V-Series C Advanced Cross Compiler

# **Macro Preprocessor**

The HP 64873 V-Series Advanced Cross Assembler/ Linker software package also includes a powerful, string-oriented macro preprocessor. The macro preprocessor adds even more flexibility to the assembler with its features (including support for recursive macros).

#### 1-4 Assembler Introduction

# **Assembler Syntax**

# Introduction

Assembly language, like other programming languages, has a character set, a vocabulary, rules of grammar, and conventions that allow for definition of new words or elements. The rules that describe the language are referred to as the "syntax" of the language. This chapter describes the basic elements of assembler language:

- the character set

- symbols

- constants

- delimiters

These basic elements, in turn, are put together to form assembler statements. This chapter also gives the general syntax of those statements.

Input source lines over 1024 characters in length will be truncated and an error message will be generated.

# Assembler Character Set

The assembler recognizes the characters in Table 2-1. Any other characters, except those in a comment field, generate errors. Many of the special characters have no previously-defined meaning except as character constants. The characters are case sensitive by default. If case sensitivity is turned off, then all lower case alphabetic characters are treated as if they were upper case, unless they appear in quoted strings.

Table 2-1. Assembler Character Set

#### **Alphabetic Characters** ABCDEFGHIJKLMNOPQRSTUVWXYZ abcdefghijklmnopqrstuvwxyz **Numeric Characters** 0 1 2 3 4 5 6 7 8 9 **Special Characters** > greater than \* asterisk blank horizontal tab \* ascci\_ , comma @ commercial at minus sign . period ! exclamation point & ampersand ; semicolon colon = equal sign double quote # sharp double quote question mark % percent underscore back slash right brace caret (uparrow) underscore right bracket left bracket accent grave { left brace vertical bar tilde / slash

# **Symbols**

# **Symbol Formation**

A symbol is a sequence of characters. The first character must be

- A-Z or a-z (alphabetic)

- ? (question mark)

- @ (commercial at sign)

- \_(underscore)

The second and following characters can be any of these characters or the numerals 0-9. Symbols can be up to 255 characters in length, but only the first 31 characters are significant.

Symbols are used to represent arithmetic values, memory addresses, bit arrays (masks), and so on.

#### 2-2 Assembler Syntax

Examples of valid symbols:

```

LAB1

@mask

LOOP_NUM

L234567890123456789012345

;(entire symbol is stored, but only

31

;used for comparison)

```

Examples of invalid symbols:

```

ABORT* ; contains special character

1LAR ; begins with a numeric

PAN N ; embedded blank, symbol is PAN

```

Different symbols represent different kinds of data objects. In general, only a few kinds of symbols are allowed in any particular syntactic construct. Any of the following elements are considered to be symbols.

# **Keywords**

Keywords (also called Reserved Words) are symbols pre-defined by the assembler which you can reference in certain acceptable constructs. Keyword symbols are not user-definable, nor can you create a user-defined symbol with a name that conflicts with a keyword. Keywords include directives and register names, among others. Keywords are not case-sensitive. The full list of assembler keywords appears in the following table. Although the keywords in the table are in upper case, there is no requirement that they appear in upper case in the source code.

Table 2-2. asv20/asv33 Keywords and Instructions

| ??SEG        | BRKEM     | DIR     | FCMPA   | FINCSTP       |

|--------------|-----------|---------|---------|---------------|

| ABS          | BRKV      | DISPOSE | FCMPAE  | FINCSTP       |

| ADD4S        | BRKXA     | DIV     | FCMPE   | FINT          |

| ADD45<br>ADD | BTCLR     | DIVU    | FCMFE   | FINT<br>FIP3V |

|              |           |         |         |               |

| ADDC         | BUSLOCK   | DL      | FCOMP   | FIP4V         |

| ADJ4A        | BV        | DQ      | FCOMPP  | FIST          |

| ADJ4S        | BW        | DS0     | FCOS    | FISTP         |

| ADJBA        | BYTE      | DS1     | FCTW    | FISUB         |

| ADJBS        | BZ        | DS      | FCVTDL  | FISUBR        |

| AH           | CALL      | DT      | FCVTDS  | FL0-FL7       |

| AL           | СН        | DUP     | FCVTLD  | FLD1          |

| AND          | CHKIND    | DW      | FCVTLQ  | FLD           |

| ASGNSFR      | CL        | DWORD   | FCVTLS  | FLDCW         |

| ASSUME       | CLR1      | EI      | FCVTQL  | FLDENV        |

| AT           | CMP4S     | END     | FCVTQS  | FLDL2E        |

| AW           | CMP       | ENDM    | FCVTSD  | FLDL2T        |

| BC           | CMPBK     | ENDP    | FCVTSL  | FLDLG2        |

| BCWZ         | CMPBKB    | ENDS    | FCVTSQ  | FLDLN2        |

| BE           | CMPBKW    | EQ      | FDECSTP | FLDPI         |

| BGE          | CMPM      | EQU     | FDIAG   | FLDZ          |

| BGT          | CMPMB     | ESC     | FDISI   | FLOGE         |

| BH           | CMPMW     | EVEN    | FDIV    | FMOD          |

| BL           | CODEMACRO | EXT     | FDIVP   | FMOV          |

| BLE          | COMMON    | EXTRN   | FDIVR   | FMOVCR        |

| BLT          | CVTBD     | F2XM1   | FDIVRP  | FMOVRT        |

| BN           | CVTBW     | FABS    | FDWORD  | FMUL          |

| BNC          | CVTDB     | FACOS   | FENI    | FMULP         |

| BNE          | CVTWL     | FADD    | FEXPE   | FNCLEX        |

| BNH          | CW        | FADDP   | FEXPEMI | FNDISI        |

| BNL          | CY        | FAR     | FEXPR   | FNEG          |

| BNV          | DB        | FASIN   | FFREE   | FNENI         |

| BNZ          | DBNZ      | FATAN2  | FIADD   | FNINIT        |

| BP           | DBNZE     | FATAN   | FICOM   | FNOP          |

| BPE          | DBNZNE    | FBLD    | FICOMP  | FNSAVE        |

| BPO          | DD        | FBSTP   | FIDIV   | FNSTCW        |

| BR           | DEC       | FCHS    | FIDIVR  | FNSTENV       |

| BRK          | DH        | FCLEX   | FILD    | FNSTSW        |

| BRKCS        | DI        | FCMP    | FIMUL   | FPATAN        |

|              | •         | Z       |         |               |

# 2-4 Assembler Syntax

Table 2-2. asv20/asv33 Keywords and Instructions (Cont'd)

| FPO1    | FXAM     | MOVBKB   | PURGE   | SHL      |

|---------|----------|----------|---------|----------|

| FPO2    | FXCH     | MOVBKW   | PUSH    | SHORT    |

| FPOWER  | FXTRACT  | MOVSPA   | QWORD   | SHR      |

| FPREM   | FYL2X    | MOVSPB   | RECORD  | SHRA     |

| FPTAN   | FYL2XP1  | MUL      | RELB    | SIZE     |

| FPTW    | GE       | MULU     | RELW    | SMOFFSET |

| FQWORD  | GROFFSET | NAME     | REP     | SMSIZE   |

| FR0-FR7 | GROUP    | NE       | REPC    | SP       |

| FREM    | GRSIZE   | NEAR     | REPE    | SS       |

| FRND    | GT       | NEG      | REPNC   | ST       |

| FRNDINT | HALT     | NIL      | REPNE   | STM      |

| FRPOP   | HIGH     | NOP      | REPNZ   | STMB     |

| FRPUSH  | IN       | NOSEGFIX | REPZ    | STMW     |

| FRSTOR  | INC      | NOT1     | RET     | STOP     |

| FS0-FS7 | INM      | NOT      | RETI    | STRUC    |

| FSAVE   | INPAGE   | NOTHING  | RETRBI  | SUB4S    |

| FSCALE  | INS      | OFFSET   | RETXA   | SUB      |

| FSIN    | IX       | OR       | RFIX    | SUBC     |

| FSINCOS | IY       | ORG      | RFIXM   | TBYTE    |

| FSQRT   | LABEL    | OUT      | RNFIX   | TEST1    |

| FST     | LDEA     | OUTM     | RNFIXM  | TEST     |

| FSTCW   | LDM      | PAGE     | ROL4    | THIS     |

| FSTENV  | LDMB     | PARA     | ROL     | TRANS    |

| FSTP    | LDMW     | POLL     | ROLC    | TRANSB   |

| FSTSW   | LE       | POP      | ROR4    | TSKSW    |

| FSTW    | LENGTH   | PREFX    | ROR     | TYPE     |

| FSUB    | LOW      | PREPARE  | RORC    | WIDTH    |

| FSUBP   | LT       | PROC     | RWFIX   | WORD     |

| FSUBR   | MASK     | PROCLEN  | SEG     | XCH      |

| FSUBRP  | MOD      | PS       | SEGFIX  | XOR      |

| FTAN    | MODRM    | PSW      | SEGMENT |          |

| FTST    | MOV      | PTR      | SET1    |          |

| FWAIT   | MOVBK    | PUBLIC   | SETIDB  |          |

|         |          |          |         |          |

|         |          |          |         | _        |

# Instruction Mnemonics

A full set of instruction names (mnemonics) is pre-defined by the assembler. Instruction names can be removed from the symbol table with the PURGE directive and re-defined as something else. If you do this, the original meaning of the instruction is lost. There are six instructions (the operators AND, NOT, OR, SHL, SHR and XOR) that cannot be removed. A full list of the pre-defined instruction mnemonics, including the argument combinations acceptable for each, appears at the end of the chapter titled "Instructions and Operands."

### Codemacro

A codemacro is a user-defined instruction or prefix to an instruction. The output generated from a codemacro can be a new instruction, a mixture of normal instructions, or just about anything that a customer might want (some assemblers define the normal instructions through the use of codemacros). A codemacro can be defined with the same name as an existing instruction or it can have a completely unique name that describes a new operation. Codemacros can be used anywhere that a predefined instruction can be used.

#### Label

A label is a user-defined symbol denoting the address of an instruction. Labels can be referenced only in the BR and CALL instructions and variations thereof. A label can be defined with the PROC directive or with the LABEL directive, but there is a another way to define a label that is used most often.

The most common way of defining a label is to place a name (followed by a colon) before an instruction mnemonic, which defines it as a label. Labels have certain attributes, but a discussion of those aspects of labels is left to the chapter titled "Symbol and Expression Attributes." Example:

THIS IS A LABEL: MOV AW, 2

#### Variable

A variable is a user-defined symbol denoting the address of a location to be used for data storage. Unlike many other assembly languages, asv20/asv33 distinguishes between a label and a variable. They are defined according to syntax and cannot be used interchangeably in expressions or instructions. However, when the LABEL directive is used with the keywords BYTE, WORD, DWORD, FDWORD, QWORD, FQWORD, TBYTE, or with a variable that is a structure name or record name, it defines a variable. When the LABEL directive is used with the type designator NEAR or FAR, it defines a label.

Variables have certain attributes, which are discussed in the chapter titled "Symbol and Expression Attributes."

#### **Structure Name**

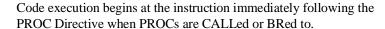

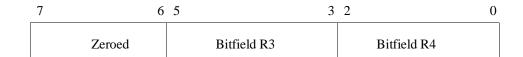

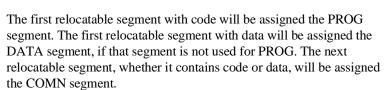

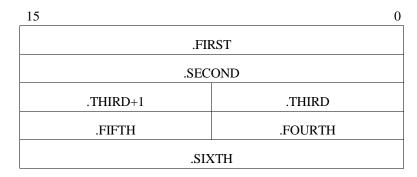

A structure is a user-defined template describing the manner in which a block of storage is to be broken up into elements. A structure template does not have a storage area associated with it which means that a structure name, while it is still a symbol, is not a variable. A structure template name does not have attributes associated with it.