# MICE USER'S GUIDE

# PREFACE

This document provides information on the MICE products from MicroTek International, Inc. Installation and operation instructions are described.

The information presented in this document is believed to be accurate and complete, but no responsibility is assumed for any errors or omissions.

Additional copies of this document or other literature and product information may be obtained from:

#### MicroTek International, Inc.

2-1, Science Road 1 Hsinchu Science-based Industrial Park Hsinchu, Taiwan, 300, R.O.C Telephone: (035) 772155-7 Telex: 32169 MICROTEK

MicroTek Lab., Inc. 17221 South Western Avenue Gardena, California 90247 Telephone: (213) 538-5369 Telex: 696334 BENNY GDNA

#### **Sales Representative Office** GYC, Inc. 100 Clement Street San Francisco, California 94118 Telephone: (415) 751-7150

Printed in U.S.A. July 1982

# CONTENTS

| Chapter 1: Introduction to MICE                |     |     |     | •   |     |   |     |   | 1         |

|------------------------------------------------|-----|-----|-----|-----|-----|---|-----|---|-----------|

| MICE Operating Configurations.                 |     |     |     |     |     |   |     |   | 2         |

| MICE Applications.                             |     |     |     | •   |     |   |     |   | 3         |

| <b>Chapter 2: MICE Installation Procedures</b> |     |     |     | •   |     |   |     |   | 5         |

| MICE Specifications                            |     |     |     |     |     | • |     | • | 5         |

| Communicating with MICE                        |     |     |     |     |     |   |     |   | 6         |

| DTE or DCE.                                    | ••• |     |     | •   |     |   |     |   | 8         |

| Applying Power to MICE                         |     |     |     | •   |     |   |     |   | 10        |

| Interfacing to Target                          |     |     |     | •   |     |   |     |   | $12^{10}$ |

| Chapter 3: MICE Command Language               |     |     |     |     |     |   |     |   |           |

| Command Syntax.                                | ••  | ••  | ••• | •   | ••  | • | ••• | • | 15        |

| Notation and Conventions                       | ••  | ••• | ••  | • • | •   | • | ••• | • | 10        |

| Editing Characters.                            | ••• | ••• | ••• | ••• | •   | • | ••• | • | 10        |

| Operator-Controlled Pauses.                    | • • | ••• | ••  | • • | •   | • | ••• | • | 17        |

| MICE Utility Commands                          | ••• | • • | ••• | ••• | ·   | • | • • | • | 17<br>10  |

| ? –Help Command                                | ••• | ••• | ••• | • • | ••• | • | ••  | • | 10<br>10  |

| ! —Attention Command                           | ••• |     | ••  | ••• | ••• | • | ••  |   | 20<br>13  |

| Memory and Port Contents Commands              |     |     |     |     |     |   |     |   | 20<br>91  |

| M-Memory Display/Change Command                |     |     |     |     |     |   |     |   | 21<br>22  |

| T – Memory Test/Transfer Command               |     |     |     |     |     |   |     |   | 22<br>23  |

| A – Assemble into Memory Command               |     |     |     |     |     | • |     | • | 25<br>25  |

| Z – Disassemble Memory Command.                |     |     |     |     |     |   |     |   | 26        |

| I — Port Input Command                         |     |     |     |     |     |   |     |   | <br>97    |

| O – Port Output Command                        |     |     |     |     |     |   |     |   | 21<br>28  |

| Registers and Control Signals Commands         |     |     |     |     |     |   |     |   | 29        |

| $\mathbf{R}$ – Register Display/Change Command |     |     |     |     |     | • |     | • | 30        |

| J – Program Counter Change Command.            |     |     |     |     |     |   |     |   | 32        |

| D – Disable Control Signal Command             |     |     |     |     |     |   |     |   | 33        |

| E – Enable Control Signal Command.             |     |     |     |     |     |   |     | • | 34        |

| X – Reset Target Processor Command             |     |     |     |     |     |   |     |   | 35        |

| Emulation and Trace Control Commands              |

|---------------------------------------------------|

| C Bogin Emulation Command                         |

| G – Begin Emulation Command                       |

| H – Halt Emulation Command                        |

| C – Cycle Step Command                            |

| S – Instruction Step Command 40                   |

| F – Forward Trace Command                         |

| B – Backward Trace Command                        |

| L - List Trace Command                            |

| Utility Commands Involving a System               |

| : — Download Command (Intel Format)               |

| / – Download Command (Tektronix Format)           |

| U-Upload Command                                  |

|                                                   |

| Appendix A: Summary of MICE Commands55            |

| <b>Appendix B: Hexadecimal-Decimal Conversion</b> |

| Appendix C: ASCII Codes                           |

|                                                   |

| Appendix D: Writing a Driver Program              |

| Appendix E: Controller Card                       |

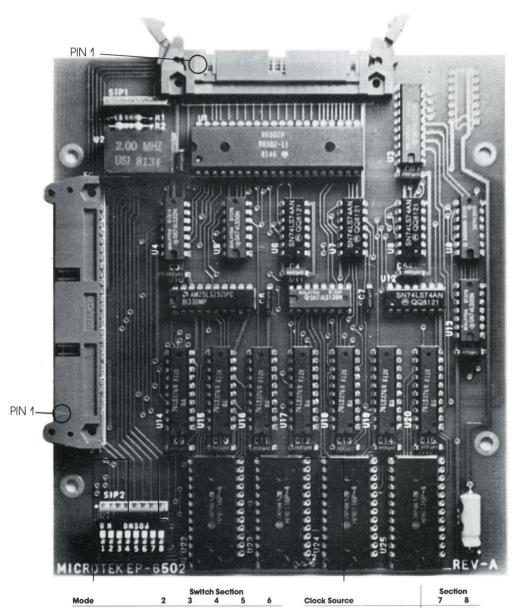

| <b>Appendix F: 6502</b>                           |

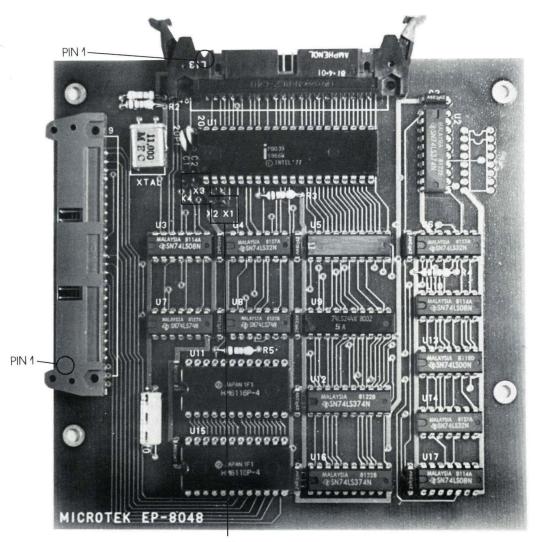

| Appendix G: 8048                                  |

|                                                   |

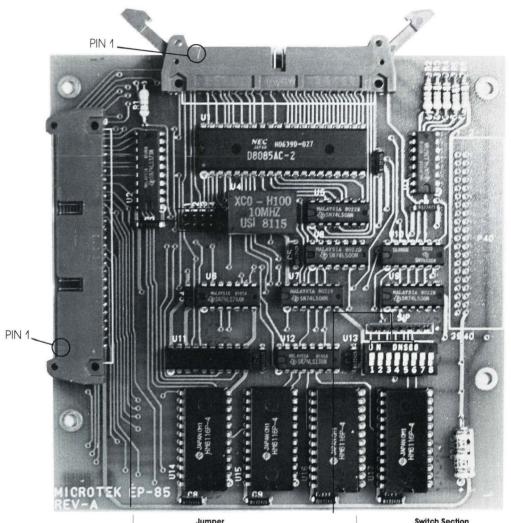

| <b>Appendix H: 8085</b>                           |

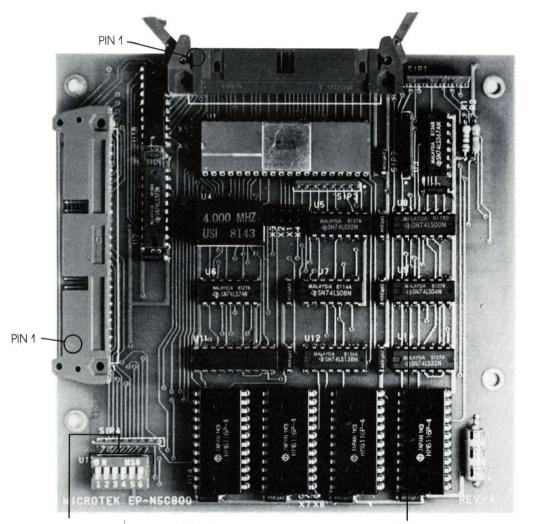

| <b>Appendix I: NSC800</b>                         |

| Appendix $J: Z80/Z80R$                            |

|                                                   |

•

# CHAPTER 1 INTRODUCTION TO MICE

MicroTek's Micro In-Circuit Emulator, MICE, is a low-cost development tool that emulates most of the industry-standard microprocessors and is setting a new standard for universal, high-performance emulation, at an exceptionally low cost-per-function.

Traditionally, microprocessor development has been done on a dedicated system. This computer system would have its complement of peripheral devices and sufficient mass storage to accommodate the user's program and a variety of support software such as editors, debuggers, file management programs, etc. Attached to this system would be a dedicated emulator which allowed the designer to examine the system to assure that all components, both hardware and software, were functioning properly.

More recently, a variety of general purpose computers have been designed for use in microprocessor development. Through the use of cross assemblers and cross compilers, code can be generated for the target system. However, the emulator products are again dedicated to that computer.

With MICE, a third approach to microprocessor development is available; one that uses fewer resources, performs most of the same functions, and yet cost a fraction of its predecessors. Consisting of a control card and a separate personality card for the microprocessor to be emulated, the MICE module is controlled via an RS-232C compatible interface. All software necessary to operate the MICE is contained in EPROMs within the module. The MICE can be operated using only a display terminal or in conjunction with a computer system. Different processors can be emulated by merely changing the personality card and associated EPROMs.

Some of the key features of MICE are:

- Operation at speeds up to the maximum rated frequency of the specified microprocessor.

- Target processor retains its entire memory and I/O spaces.

- Emulation memory which can be mapped into any 8K block of target processor memory.

- Enabling and disabling of hardware control signals to the processor with console commands.

- Single address breakpoint with loop count.

- Forward and backward tracing with 256 cycles of trace memory.

- Single character command set with help command to list all commands and the proper syntax.

- Using a single input command, any port can be sampled up to 256 times at intervals from 1 to 256 milliseconds; and multiple data output with a single port output command.

- Resident assembler and two-pass disassembler which assigns labels to subroutine and branch addresses.

- Built-in memory diagnostics and block memory transfer for the target processor's memory.

- Downloading and uploading of target program between MICE and host computer systems.

Some of the advantages of MICE over the other emulators are:

- **universality** A wide variety of microprocessors can be emulated using this single, low-cost development tool. You can avoid both the inflexibility of dedicated systems and the heavy capital investment required for the general purpose systems.

- **versatility** The emulation of a different processor requires only the changing of a personality card and the control EPROMs. Multiple design projects can be carried out concurrently, and the control card can be reused on different projects.

- **flexibility** With MICE providing its own resident assembler and disassembler, it can be minimally configued with just a display terminal and a power supply. After the target program has been downloaded from the host computer, testing can be done off-line, thereby freeing the computer.

### **MICE** Operating Configurations

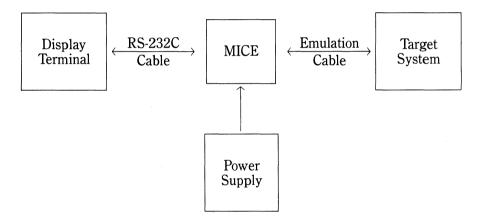

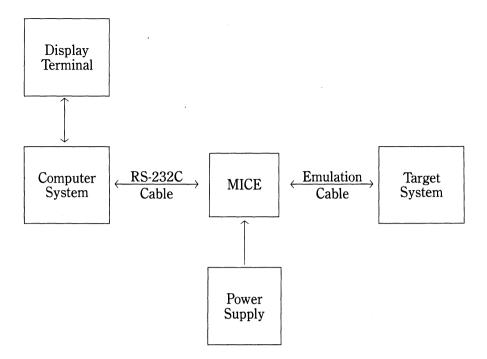

The MICE module can be used in either of two possible configurations. The simplest configuration only requires an RS-232C compatible terminal as the display and command entry device.

If a computer system is used as the controlling device, the configuration is similar to the one above; the computer with its display terminal now replaces the lone terminal.

When a computer system is interfaced to the MICE module, a driver program must be resident in the computer system. Driver programs for various systems have already been written, including

- the Apple computers

- the Intel development systems

- the Digital Equipment mini- and main-frame computers

For an updated list on the computers supported and power supply vendors, contact your local MICE representative.

### **MICE** Applications

Because of its unique design, MICE offers new applications which include:

1. Inexpensive evaluation of new microprocessors is made possible since there is no longer a need to purchase either an evaluation board or an expensive development system.

2. Several designers can now share the use of a single development system, eliminating the difficult problem of allocating a single resource and the expensive need of multiple work-stations. Large programs can be edited, assembled or compiled, and then downloaded using MICE into the target system. Since MICE has its own assembler and disassembler, the programs can then be tested using only a display terminal.

3. In-field or service center testing is ideal. Rather than sending the suspected bad board back to the factory for service, MICE's compact size makes it portable and allows it to be brought to remote sites for diagnosing problems; thus saving time and customer inconvenience. With its RS-232C interface, MICE can be quickly interfaced to any compatible display terminal. Diagnostic programs can be generated using the resident assembler.

4. Personal computers can be upgraded to a development system at a fraction of the typical costs. Driver programs for various computers have already been written, allowing programs assembled or compiled to be downloaded.

# CHAPTER 2 MICE INSTALLATION PROCEDURES

All hardware and software items necessary for operation are contained in the MICE shipping package. The package includes a MICE module, containing a control card and a personality card for the microprocessor being emulated; an emulator cable for connection to the target system; a DC power cable; and a user's guide. After unpacking, check that all the items are complete and undamaged. If any item in the package is damaged or missing, contact your local MICE representative immediately.

### **MICE Specifications**

The MICE module comes in either an aluminum or a plastic case with the following dimensions:

Width -6.89 in. (17.5 cm) Height-2.76 in. (7.0 cm) Depth -9.06 in. (23.0 cm)

and weighs approximately 32 oz (900 g). If the module comes in an aluminum case, its dimensions are a bit smaller; also, be careful where it is placed since aluminum conducts electricity.

The minimum and maximum operating and storage limits for temperature and humidity are:

|                                              |      | rating | storage |        |  |

|----------------------------------------------|------|--------|---------|--------|--|

|                                              | min  | max    | min     | max    |  |

| Temperature in degrees<br>Fahrenheit/Celsius | 32/0 | 122/50 | 14/-10  | 149/65 |  |

| Relative humidity<br>(without condensation)  | 20%  | 80%    | 20%     | 90%    |  |

In order to use MICE, the MICE module requires three power supply voltages; each of which must be regulated to within 5 percent of nominal:

+ 5 VDC at 1.5A (maximum) +12 VDC at 0.2A (maximum) -12 VDC at 0.2A (maximum)

Using the supplied power cable, the mating female connector is to be connected to the pins at the rear of the MICE module with the locking tab pointing up. The power connector pinouts are as follows:

Description + 5 VDC Ground +12 VDC -12 VDC

|         | - Pin                                 |

|---------|---------------------------------------|

|         | 1                                     |

| 1 2 3 4 | $\begin{vmatrix} 2\\ 3 \end{vmatrix}$ |

|         | 4                                     |

5

It is very important to make sure that the correct voltages are connected to the proper pins, otherwise, MICE may suffer severe damages to its circuitry; also, when turning off the power to the MICE module, always wait a few seconds to allow the capacitors to fully discharge before turning on the power again.

### **Communicating with MICE**

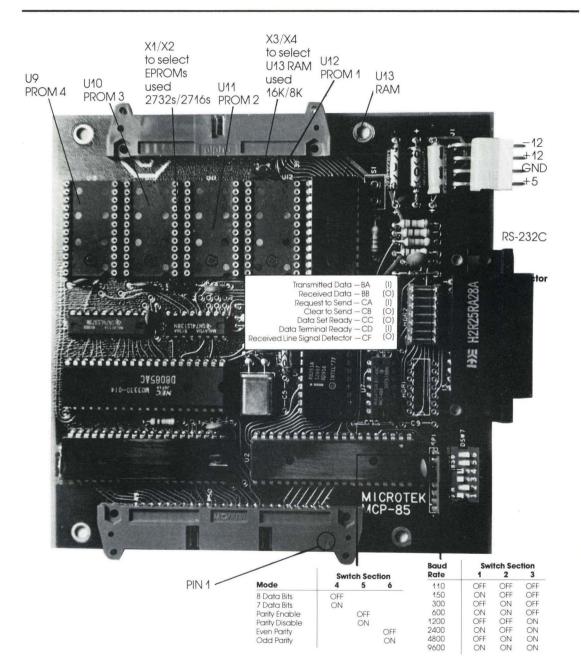

Whether the MICE module is connected to a terminal or to a computer system, the connection between the controlling device and MICE is across a programmable RS-232C compatible interface. To gain access to the controls, the cover to the MICE module must first be removed. Next, carefully lift the top, personality card out to gain access to the bottom, control card. Locate the switch designated as DSW7 on the control card. This switch sets the following power-up and reset modes:

| Switch<br>Section | Description           |

|-------------------|-----------------------|

| 1-3               | Baud Rate             |

| 4                 | 7/8 Data Bits         |

| 5                 | Disable/Enable Parity |

| 6                 | Odd/Even Parity       |

The number of stop bits is permanently set to one; and the communication is full duplex.

MICE modules are shipped from the factory with the switch preset to 2400 baud, seven data bits, and parity enabled with even parity. The switch position for this default selection is shown below.

|                                                          | Switch Section |     |     |    |     |     |

|----------------------------------------------------------|----------------|-----|-----|----|-----|-----|

| Mode                                                     | 1              | 2   | . 3 | 4  | 5   | 6   |

| 2400 Baud<br>7 Data Bits<br>Parity Enable<br>Even Parity | ON             | OFF | ON  | ON | OFF | OFF |

The baud rate is initialized or updated during power-up or reset. Any of 8 different baud rates (110-9600) can be selected. To do this, place sections 1, 2, and 3 of switch DSW7 to the proper positions as shown below.

| Baud | Switch Section |     |     |  |  |

|------|----------------|-----|-----|--|--|

| Rate | 1              | 2   | 3   |  |  |

| 110  | OFF            | OFF | OFF |  |  |

| 150  | ON             | OFF | OFF |  |  |

| 300  | OFF            | ON  | OFF |  |  |

| 600  | ON             | ON  | OFF |  |  |

| 1200 | OFF            | OFF | ON  |  |  |

| 2400 | ON             | OFF | ON  |  |  |

| 4800 | OFF            | ON  | ON  |  |  |

| 9600 | ON             | ON  | ON  |  |  |

The number of data bits and the parity selection are also initialized or updated during a power-up or reset. To change the selection settings, place sections 4, 5, and 6 of the switch to the proper positions as shown below.

|                | Switch Section |     |     |  |

|----------------|----------------|-----|-----|--|

| Mode           | 4              | 5   | 6   |  |

| 8 Data Bits    | OFF            |     |     |  |

| 7 Data Bits    | ON             |     |     |  |

| Parity Enable  |                | OFF |     |  |

| Parity Disable |                | ON  |     |  |

| Even Parity    |                |     | OFF |  |

| Odd Parity     |                |     | ON  |  |

When parity is disabled, the odd/even parity switch section can be set to either position since it is ignored.

### DTE or DCE

Having selected the proper data rate and characteristics, we must now determine whether our controlling device has a data terminal equipment (DTE) interface or a data communication equipment (DCE) interface. Display terminals are usually equipped with DTE interfaces; computer systems are usually equipped with both. If by chance the MICE module is to be interfaced to a modem for remote use, modems are usually equipped with DCE interfaces.

There are three methods for determining the type of interface on the controlling device, listed here in preferential order:

1. Data are transmitted on pin 2 and received on pin 3 of the D-connector for DTE devices; the reverse is true for DCE devices.

2. The voltage on pin 2 with respect to pin 7 of the D-connector is approximately -12 VDC for DTE devices, and on pin 3 for DCE devices.

3. Connect the two devices together. If it works, it must be correct; otherwise, it might be reversed.

The header designated as HDR2 on the control card is used to configure the interface between MICE and the controlling device. The pin definitions on the header are shown below.

#### **D-connector**

#### MICE Interface Logic

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c} -13(I) \\ -12(O) \\ -11(O) \\ -10(I) \end{array} $ | CF – Received Line Signal Detector<br>CD – Data Terminal Ready<br>CC – Data Set Ready<br>CB – Clear to Send<br>CA – Request to Send<br>BB – Received Data |

|------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| pin 45<br>pin 36<br>pin 27                           | – 9(0)                                                                | BB—Received Data<br>BA—Transmitted Data                                                                                                                   |

Pins 1 through 7 on the header are connected to the female D-connector while pins 8 through 14 are connected to the MICE RS-232C interface logic. The symbols "I" and "O" within the parenthesis indicate whether the signals are incoming or outgoing with respect to the logic.

MICE modules are shipped from the factory with the header wired straight across, pins 1-to-14, 2-to-13, etc. In this configuration, MICE is ready for most DTE interfaces; which means that if a display terminal is connected to the MICE module using a straight-wire cable with male D-connectors, the MICE module should respond when power is applied. The display terminal should always be used to check new MICE units to insure that units shipped have not been damaged.

If the controlling device has a DCE interface, the header must be rewired because the incoming signals are now outgoing, and vice versa, on the same pins.

| DTE<br>interface | DCE<br>interface |                                   |

|------------------|------------------|-----------------------------------|

| 8 to 7           | 8 to 6           | (I) Transmitted Data              |

| 9 to 6           | 9 to 7           | (O) Received Data                 |

| 10 to 5          | 10 to 4          | (I) Request to Send               |

| 11 to 4          | 11 to 5          | (O) Clear to Send                 |

| 12 to 3          | 12 to 2          | (O) Data Set Ready                |

| 13 to 2          | 13 to 3          | (I) Data Terminal Ready           |

| 14 to 1          | no connect       | (O) Received Line Signal Detector |

Note that the first six signals are paired, where one is the complement of the other.

Finally, the MICE module requires that both the Request to Send and Data Terminal Ready inputs, pins 10 and 13 respectively on the logic side of the header, to be at +12 VDC before it transmits any data. If the controlling device does not supply the necessary voltage, it may be obtained by not connecting the pins to the designated pins as indicated in the above table, but connecting them to pin 14 (Received Line Signal Detector) of the header which is always at +12 VDC. To accommodate computer systems which are sending commands and data too fast for MICE, the Data Set Ready output, normally at +12 VDC, is pulled low by MICE to -12 VDC; the signal is restored to the +12 VDC when MICE is again ready. To accommodate display terminals with slow carriage-returns or line-feeds, six null characters are always transmitted after a new line is issued.

### **Applying Power to MICE**

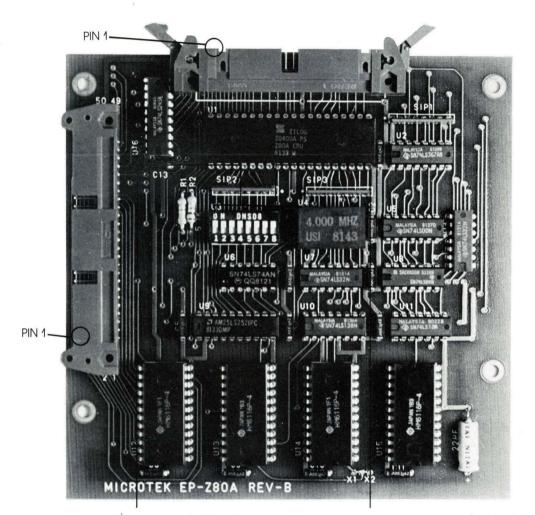

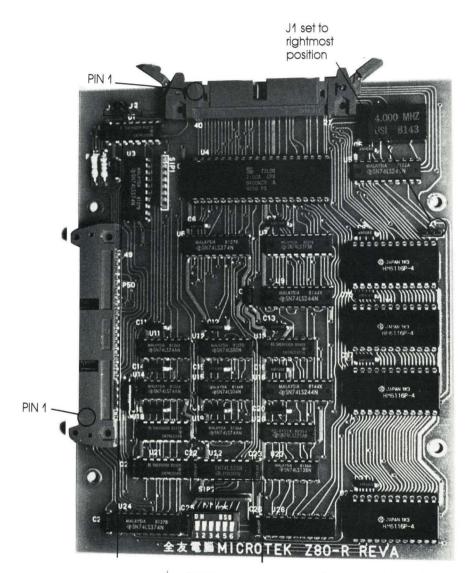

We are now ready to do a preliminary test on our MICE. First, replace the personality card to its original position, reconnecting the ribbon cable between the two boards if it had been removed earlier; the arrows indicate pin 1 and must be aligned when attaching the cable to the connector. Next, connect the RS-232C cable from the controlling device to the female D-connector on the rear of the MICE module. Finally, with the controlling device ready, connect the power cable with the locking tab pointing up, and apply power. Within a few seconds, the start-up message should be displayed.

\*\*\* MICE-type V#. # \*\*\*

>

**type** identifies the target processor being emulated by the personality card.

**#.#** indicates the revision level of the controlling program on the control card.

> is the prompt character indicating that MICE is ready for a command.

During the delay, the RAMs and the EPROMs on the control card are tested. Component failures are listed as detected in the format:

U## – FAILURE

where:

## is the component number on the control card

If there is no response from MICE, here are some things to try:

1. Check the RS-232C cable connection at both ends.

2. Check the power supply connections and voltages.

3. Check that the header has the proper interface.

4. Check that both Request to Send and Data Terminal Ready, pins 10 and 13 respectively on the logic side of the header, are at +12 VDC.

5. Check that the controlling device has the proper voltage level requirements on its RS-232C inputs for transmission and reception.

6. Check that the baud rates of the controlling device and the MICE modules are the same, resetting if necessary. If a message does appear but is garbled, any combination of baud rate, data length, or parity could be incorrectly set.

7. Check the RS-232C cable for incorrectly wired or loose pins.

8. If a computer system is the controlling device, check that the driver progam is running and the RS-232C cable is connected to the correct port and that the port is working.

Remember that the power must be turned off then on again since the configuration switch is only read during a power-up or a reset. It is also important to wait a few seconds before the power is turned on to allow the capacitors to fully discharge.

If the MICE module still does not respond, contact your local MICE representative for further directions.

On the other hand, a proper message displayed means that we are almost done. We must next double check that the number of data bits and the parity have been set correctly. In response to the command prompt character, ">", enter a question mark, "?", immediately followed by a carriage-return. If the data bits and parity are correctly matched, the MICE command summary is listed, otherwise, the error message "WHAT?" is printed. Reset the switch sections as necessary and remember to wait a few seconds before power is turned on again.

Finally, alphabetic characters must be entered in upper-case. Aside from the character "r", which is the command to reset the MICE module, all other lower-case characters are not recognized.

# Interfacing to Target

MICE modules are shipped from the factory configured to run in the stand-alone mode – running without a target system. The mappable emulation memory is enabled and preset to begin from the program memory address 0000H. With the exception of the 8048 family, the personality card has a six or eight section switch; five sections affect the mappable memory as shown below.

|                |     | Swi | itch Sec | tion |     |

|----------------|-----|-----|----------|------|-----|

| Mode           | 2   | 3   | 4        | 5    | 6   |

| 0000H - 1FFFH  | ON  | ON  | ON       |      |     |

| 2000H - 3FFFH  | ON  | ON  | OFF      |      |     |

| 4000H - 5FFFH  | ON  | OFF | ON       |      |     |

| 6000H - 7FFFH  | ON  | OFF | OFF      |      |     |

| 8000H - 9FFFH  | OFF | ON  | ON       |      |     |

| A000H- BFFFH   | OFF | ON  | OFF      |      |     |

| C000H - DFFFH  | OFF | OFF | ON       |      |     |

| E000H - FFFFH  | OFF | OFF | OFF      |      |     |

| Memory Enable  |     |     |          | ON   |     |

| Memory Disable |     |     |          | OFF  |     |

| Write Enable   |     |     |          |      | ON  |

| Write Protect  |     |     |          |      | OFF |

When MICE is used to replace the processor in the target system, the 40-pin ribbon cable is used. With the power off, one end of the cable mates with the 40-pin male connector on the personality card; the arrow indicates pin 1 and must be aligned when attaching the cable. Next, carefully extract the processor from the target system and insert the male plug on the end of the cable into the 40-pin socket; pin numbers are marked on the plug and must be inserted as indicated. A number of jumpers and switch sections on the personality card select the clock source to the processor and other emulation parameters. Since these jumpers and switch settings vary for different types of processors, consult the corresponding guide in the appendices on their meaning. Also consult the appendices if a different personality card is to be installed.

Finally, care must be taken when using the ribbon cable; it is not the same for all processors. If your cable is not identified, mark it yourself so that you can distinguish it from the others. Also, the 40-pin plug that is inserted in place of the target processor has pins which can be easily damaged. If possible, protect those pins by plugging them into a 40-pin socket, using the unit together for insertions and removals. Lastly, the cable and the personality card add additional loads to the target processor and drivers which may cause problems if the target system design is marginal.

# CHAPTER 3 MICE COMMAND LANGUAGE

All MICE products have a common set of commands that are identified by a single character. Regardless of the target processor being emulated, only a different personality card is changed with no time being wasted in learning a new command language.

In this chapter, the commands are described with all the possible options that are available although not all options are applicable to the different types of processors. For the particular processor being emulated, either consult the help (?) command or the corresponding guide in the appendices. The commands described in this chapter are grouped as follows:

MICE Utility Commands

- ? Help Command

- ! Attention Command

- Memory and Port Contents Commands

- M Memory Display/Change Command

- T Memory Test/Transfer Command

- A Assemble into Memory Command

- Z Disassemble Memory Command

- I Port Input Command

- O Port Output Command

- Registers and Control Signals Commands

- R Register Display/Change Command

- J Program Counter Change Command

- D Disable Control Signal Command

- E Enable Control Signal Command

- X Reset Target Processor Command

Emulation and Trace Control Commands

- G Begin Emulation Command

- H Halt Emulation Command

- C Cycle Step Command

- S Instruction Step Command

- F Forward Trace Command

- B Backward Trace Command

- L List Trace Command

Utility Commands Involving a System

- : Download Command

- / Download Command

- U Upload Command

### **Command Syntax**

MICE indicates that it is ready to accept a command line by printing a greater-than character, ">", on a new line. A command may then be entered which must be terminated by a carriage return. The general syntax of MICE commands is:

#### command [parameters] < cr>

where:

**command** is the single character for the command.

**parameters** are one or more variable data supplied with the command. Parameters are alphanumeric; and when a numeric parameter is called for, it must be entered in hexadecimal form.

Where a comma is shown in the syntax, either a comma or a space can be used.

### Notations and Conventions

A set of conventions are used to describe the structure of the commands. The notation and the rules are as follows:

1. An upper-case entry must be entered as shown.

2. A lower-case entry in the description of a command is the class-name for a class of parameters. To create an actual operable command, a particular member of this class must be entered. A class-name never appears in a actual operable command. For example, the lower-case entry:

#### start-address

means that the MICE will only accept a hexadecimal value as an address in the target processor's memory space. The maximum value accepted depends on the target processor being emulated.

3. A required entry is shown without any enclosures, whereas an optional entry is denoted by enclosing in brackets. For example, in the command description

#### G [address]

the command "G" is required; and the brackets around the entry "address" means that its selection is optional in this command. Where brackets are within another set of brackets, the entry enclosed by the inner brackets may only be entered if the items outside those inner brackets have already been entered. For example, in the command description

#### H [address [, count]]

the command "H" is required; and the brackets means that the selection of "address" and ", count" is optional in the command. However, an address must first be entered if a count value is to be specified.

4. Where an entry must be selected from a choice of two or more entries, the choices for the required entry are enclosed in braces with the entries separated by vertical bars. For example,

#### $\{I|T|A\}$

indicates that either "I" or "T" or "A" must be entered.

5. Where a choice exists for an optional entry, the choices are enclosed in brackets with the entries separated by vertical bars. For example,

#### [PIIX]

indicates that either "P" or "I" or "X" may be entered.

6. Where an entry can be optionally repeated, the repeatable entry is enclosed in brackets followed by an ellipsis, "...". For example,

[, qualifier]...

indicates that ", qualifier" can be repeated as many times as required.

7. A decimal number in the text of this manual is without a suffix; whereas, a hexadecimal number has an "H" for a suffix. For example,

#### 1234 1234H

the first value of "1234" is a decimal number, but "1234H" is a hexadecimal number having a decimal value of 4660.

8. In the examples, input normally entered by the user are differentiated from MICE output by being underlined.

## **Editing Characters**

Each character entered on the keyboard is stored in a line editing buffer until the RETURN key is pressed. If too many characters are entered without a RETURN, an error message is printed, and the command is ignored. The line editing buffer can be edited or entirely deleted by using special non-printable editing characters. Control characters are entered by holding down the control key (CONTROL or CTRL) while the character is typed.

| BACKSPACE | deletes the preceding character from the line buffer and from the display. Repeated                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

|           | usage is allowed. Control-H performs the same function. When a hardcopy terminal is used instead of a display screen, RUBOUT should be used. |

|           | terminal is used instead of a display screen, RUBOUT should be used.                                                                         |

- **RUBOUT** deletes the preceding character from the line buffer and echoes the deleted character on the display preceded by a backslash character, "/". Repeated usage is allowed. On some terminals, this key may be labeled as DELETE or just DEL.

- **ESCAPE** ignores the current contents of the line buffer and prompts (">") for a new command on the next line. This key is also used to terminate commands in process and to return to the prompt state. On some terminals, this key may be labeled as ESC; CONTROL-Y performs the same function.

- **CONTROL-R** causes a carriage-return/line-feed, followed by the redisplaying of the current undeleted contents of the line buffer. This is useful to see a clean copy of the command line after RUBOUT has been used.

- **CONTROL-X** ignores the current contents of the line buffer and prompts (">") for a new command on the next line.

### **Operator-Controlled Pauses**

The following control characters can be used to suspend the MICE output, allowing inspection of the display, and then resume the output.

CONTROL-S suspends MICE output.

**CONTROL-Q** resumes MICE output after the CONTROL-S is given.

### **MICE Utility Commands**

These commands allow the user to query MICE for a summary of the commands and syntax that are available for the target under emulation. In addition, the user can query to have displayed the processor type being used.

?

? is the command keyword.

The command summary for the target processor currently emulated is displayed on the terminal. Although the commands are common regardless of the target processor being emulated, some of the parameters may differ for different processors.

During the display, CONTROL-S may be used to stop the display, and CONTROL-Q used to resume the display. ESCAPE or CONTROL-Y may be used to abort the display before the entire summary is displayed.

Example: Display the command summary for the target processor currently being emulated. >?<cr>

>

The notation of the summary does not fully follow the notation and conventions previously described to avoid a lengthy display.

!

! is the command keyword.

The target processor type currently being emulated by the personality card in the MICE module is displayed on the terminal. Up to six characters are used for the identification.

Example: Display the processor type currently being emulated.

>!<u><cr></u> EP8048 >

The response for other processor types supported are:

| (MOS Technology, Inc.):               | EP6502                                                                                |

|---------------------------------------|---------------------------------------------------------------------------------------|

| (Intel Corporation):                  | EP8085                                                                                |

| (National Semiconductor Corporation): | NSC800                                                                                |

| (Zilog Corporation):                  | EP-Z80                                                                                |

| (Zilog Corporation):                  | EPZ80R                                                                                |

|                                       | (Intel Corporation):<br>(National Semiconductor Corporation):<br>(Zilog Corporation): |

### **Memory and Port Contents Commands**

These commands give access to the contents or current values stored in the designated memory locations or input/output ports. The type of memory, maximum amount of memory, and total number of ports differ for the various processors. For the particular processor being emulated, consult the corresponding guide in the appendices.

Commands with no memory type requirements always operate on the target's program memory. Targets with only one type of memory have no distinction between program and data memory.

MICE always checks that the memory type and the memory and port addresses are valid before an operation is performed. References to an invalid type or invalid address result in having an error message being printed and command ended. MICE, however, does not verify that there is memory or anything connect to the port when completing an operation. In these cases, data written are lost, and data read are random.

#### Memory Display/Change Command-M

#### M [type,] start-address [, end-address [, value]]

| M             | is the command keyword (Memory).                                                                                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| type          | is a single alphabetic character indicating the type of memory to be used for pro-<br>cessor with more than one type of memory.       |

| start-address | is the hexadecimal address of the target processor from which to begin the display of memory content.                                 |

| end-address   | is the hexadecimal address of the target processor indicating the last memory location of the range to be either displayed or filled. |

| value         | is the hexadecimal value to be written into the specified memory range.                                                               |

If only the start-address is specified, the content for that memory location is first displayed. MICE then waits for an input from the user. To advance to the next memory address, a line-feed should be entered; the next memory location's content is then displayed, and MICE again waits. Entering a line-feed repeats the entire sequence. If either a carriage-return or an escape is entered, the command is ended. To change the memory content displayed, enter the new hexadecimal value before the line-feed or carriage-return. For target processors with more than one type of memory, the program memory is always selected when the type specification is omitted. To determine whether the target processor being emulated has more than one type of memory, either consult the help (?) command or the corresponding guide in the appendices

Example: Display and change the memory contents from address location 0210H of our 8048 target. The program memory type "P" is assumed.

>M210<cr> 0210 38 <lf> 0211 79 59 < lf>  $0212 \ 0C < cr >$ >

On the other hand, an end-address specification causes the memory contents in the defined memory range to be displayed. The end-address must be greater-than or equal-to the startaddress or an error message is printed and the command ended. The display can be aborted by entering an escape. Again the type specification can be used to indicate the memory type is to be displayed.

Example: Display the program memory contents 0209H to 0217H for our 8048 target processor overlapping the previously altered area:

>MP 209 217 <cr> 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 8D 15 47 92 0C 7F 93 0200 0210 38 59 0C 83 01 28 38 48 >

Finally, a value specified causes that value to be written into the defined range. MICE does not verify the content change; and the command can be aborted by entering an escape although some of the memory locations may be altered. The type specification can be used to indicate the memory type to be changed.

Example: Write the value 28 into the external memory range 0024H to 0053H of our 8048 target processor.

> M, X, 0024, 53 28 < cr> >

22

### Memory Test/Transfer Command-T

| <u>т</u>      | is the command keyword (Test/Transfer).                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| type          | is a single alphabetic character indicating the type of memory to be used for pro-<br>cessor with more than one type of memory.         |

| start-address | is the hexadecimal address of the target processor from which to begin the test<br>or transfer operation.                               |

| end-address   | is the hexadecimal address of the target processor indicating the last memory location of the range to be either tested or transferred. |

| S             | is the alphabetic character indicating that the sum of the contents in the specified range is to be displayed.                          |

| Μ             | is the alphabetic character indicating that a memory test is to be performed for<br>the specified range.                                |

| dest-address  | is the hexadecimal address of the target processor to which the data is to be transferred.                                              |

T [type,] start-address, end-address {SIMIdest-address}

Start-address and end-address defines a range in the target processor's memory whose memory contents are either to be tested or transferred. The end-address must be greater-than or equal-to the start-address or an error message is printed and the command ended. For target processors with more than one type of memory, the program memory is always selected when the type specification is omitted. To determine whether the target processor being emulated has more than one type of memory, either consult the help (?) command or the corresponding guide in the appendices.

If the alphabetic character "S" follows the range specification, the hexadecimal sum of the contents for the indicated range, with carry added back, modulo 256, is displayed.

Because our 8048 does not support this command, these examples assume that one of the other processors is being emulated.

Example: First display the program memory contents for the range 0045H to 004DH, and then perform a sum for the same range.

$> \frac{M 45, 4D < cr>}{00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 0040 39 78 D2 F1 CB 69 03 2C 50 > \frac{T45, 4D S < cr>}{THE CHECKSUM IS 2A >$

On the other hand, an "M" following the range specification causes a memory test to be performed on the indicated range. The upper-byte and lower-byte of the address whose memory is to be tested are exclusive-or'ed and written into the memory for the entire range. The entire range is then verified and the complement value is next written. The entire range is again checked. If the comparison fails in either pass, the test is stopped at the failed address and that address is displayed. The original contents in the memory are destroyed in this test. Testing in progress may also be aborted by entering an escape.

Example: Test the memory range 0024H through 0039H of our target processor.

> <u>T, 024 0039, M <cr></u> RAM OK! >

Finally, a dest-address specification indicates that the memory contents in the defined range is to be transferred into the memory beginning at dest-address. Data are transferred one location at a time from either the starting or the ending address of the range depending on whether there is any overlap.

Example: Transfer the memory contents in the range 0046H through 005FH of our target processor to the memory beginning at 0027H.

> T 46 5F 27 <cr>>

### Assemble into Memory Command-A

#### A start-address

Α

is the command keyword (Assemble).

**start-address** is the hexadecimal address of the target processor's program memory into which MICE begins storing the assembly language program entered.

Rather than entering programs or program changes in machine code using the previously described memory change (M) command, the MICE resident assembler accepts and converts mnemonic inputs into machine code. The converted code is then stored into the target processor's program memory starting from the indicated start-address. The assembler does not recognize symbolic labels; constants and addresses are entered as hexadecimal values. The instruction mnemonics accepted are those that had been adopted by the original manufacturer for the processor being emulated.

After the command keyword and start-address are received, MICE displays the following column headings:

LINE LABEL SOURCE CODE LOC OBJ 0001 \*

where the hexadecimal value of 0001H under the column LINE indicates the line number being entered, and the asterisk, "\*", indicates the new cursor position. MICE then waits for an assembly language line input from the user. The line entered can not cross into the next column, LOC, and must be terminated with either a line-feed or a carriage-return. MICE assembles the line and stores the machine code from the indicated start-address. The first program memory location to be stored is printed under the column LOC, and the data stored under the column OBJ. If a line-feed had been entered, the next line number is printed, and MICE again waits. If a carriage-return had been entered instead, the command is ended with the total number of lines entered reported as a hexadecimal value.

Example: Enter a 5 line 8048 program from 0000H with an error on the third input line.  $>A_0 < cr >$

| LINE           | LABEL     | SOURCE CODE                                               | LOC            | OBJ        |

|----------------|-----------|-----------------------------------------------------------|----------------|------------|

| $0001 \\ 0002$ |           | $\frac{\text{MOV A, #0 < lf >}}{\text{MOV R0, A < lf >}}$ | $0000 \\ 0002$ | 2300<br>A8 |

| 0003           |           | MVO R1, A < lf >                                          | 0002           | Ao         |

| ERROF          | R CODE, T | RY AGAIN!                                                 |                |            |

| 0003           |           | MOV R1, A < lf >                                          | 0003           | A9         |

| 0004           |           | INC A <lf></lf>                                           | 0004           | 17         |

| 0005           |           | JMP 2 < lf >                                              | 0005           | 0402       |

| 0006           |           | <cr></cr>                                                 |                |            |

YOUR TOTAL LINES IS 0005 LINE-ASSEMBLER COMPLETED >

When making program changes into an existing program, it is advisable to check the program around the modifying area using the disassemble memory (Z) command before and after the change. Rechecking the area is important to assure that the new program changes do not affect the surrounding program. The disassemble memory command is described in the following pages.

25

#### Disassemble Memory Command-Z

#### Z start-address [, end address]

| Z             | is the command keyword.                                                                                                                                 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| start-address | is the hexadecimal address of the target processor's program memory from which to begin the display of disassembled memory content.                     |

| end-address   | is the hexadecimal address of the target processor's program memory indicating<br>the last memory location of the range to be disassembled for display. |

If only the start-address is specified, the content for that memory location is disassembled and displayed. More data are read from subsequent locations to complete the instruction if necessary. On the other hand, an end-address specification causes the memory contents in the defined memory range to be disassembled and displayed. The end-address must be greater-than or equal-to the start-address or an error message is printed and the command ended. If an illegal machine code is encountered, the disassembler terminates at the illegal code's address. Entering an escape while MICE is displaying the disassembled data aborts the display.

MICE uses a two-pass disassembler with all branch and subroutine call addresses first identified and converted to labels; only a total of 450 labels are remembered for the disassembly. Depending on the range to be disassembled, there may be a pause before any line is displayed. Thus, to end the command before the display begins, enter and escape.

Example: Disassemble our previously entered 8048 program. Note that the byte following the end-address is also read in order to complete the instruction.

><u>Z05<cr></u>

| LINE                         | LABEL | SOURCE CODE                                  | LOC                                                      | OBJ                    |

|------------------------------|-------|----------------------------------------------|----------------------------------------------------------|------------------------|

| 0001<br>0002<br>0003<br>0004 | B0002 | MOV A, #0<br>MOV R0, A<br>MOV R1, A<br>INC A | $\begin{array}{c} 0000\\ 0002\\ 0003\\ 0004 \end{array}$ | 2300<br>A8<br>A9<br>17 |

| 0005                         |       | JMP 0002                                     | 0005                                                     | 0402                   |

DISASSEMBLY COMPLETED

>

#### Port Input Command-I

#### I port [, count [, duration]]

| Ι        | is the command keyword (Input).                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| port     | is the hexadecimal address of the target processor's input port whose content is to be read and displayed.                                                        |

| count    | is a hexadecimal value from 00H to FFH specifying the number of times the input port is to be read with 00H indicating that it is to be read 256 times.           |

| duration | is a hexadecimal value from 00H to FFH specifying the interval in milliseconds between each read with 00H indicating that the interval is to be 256 milliseconds. |

The input port command has two modes of operation. If neither the count nor the duration is specified, a range of port contents can be read and displayed beginning with the port address indicated.

MICE first reads and displays the contents for the port specified and waits for an input from the user. To advance to the next port, a line-feed should be entered; the next port's content is then read and displayed, and MICE again waits. Entering a line-feed repeats the entire sequence. If either a carriage-return or an escape is entered, the command is ended.

Example: Read and display the contents of ports 4, 5, and 6 of our 8048 target processor.

$> \frac{I4 < cr >}{04 \text{ DC} < lf >} \\ 05 87 < lf >} \\ 06 \text{ FF} < cr >}$

On the other hand, specifying a count with or without a duration specification only operates on the port indicated. MICE first reads the specified input port the number of times indicated; the contents are then displayed. Entering an escape while MICE is displaying the port contents aborts the display.

The duration specification allows the user to select the interval between each read to compensate for data inputs which are time critical; and if no interval is specified, the data are read in 1 millisecond intervals.

Example: Read and display the next 64 (40H) values of port 5 of our 8084 target processor at 10 (0AH) millisecond intervals. The display is aborted before the entire 64 values are listed. > I. 05. 40 A

PORT 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 05 43 23 56 AF 85 9F D7 E3 B6 AB 14 C5 B7 6D 07 16 38 70 01 46 A4 C6 3B 78 93 FF <u><esc></u>

Note that the interval can be up to 256 milliseconds, which is approximately a quarter of a second; if the number of times the port is to be read is also 256, the elapse time before any data is displayed is approximately 65 seconds! Thus, to end the command even before the display begins, enter an escape.

#### Port Output Command-O

#### O port,value-1 [, value-2 [, value-3 [, value-4]]]

| 0                                                                                                  | is the command keyword (Output).                                                                                   |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| U                                                                                                  | is the command key word (Output).                                                                                  |  |

| port                                                                                               | is the hexadecimal address of the target processor's output port to be written.                                    |  |

| value-1                                                                                            | is the hexadecimal value to be written into the specified output port of the target processor.                     |  |

| value-2                                                                                            | is the hexadecimal value of the second value to be written into the specified ouput port of the target processor.  |  |

| value-3                                                                                            | is the hexadecimal value of the third value to be written into the specified output port of the target processor.  |  |

| value-4                                                                                            | is the hexadecimal value of the fourth value to be written into the specified output port of the target processor. |  |

| If only one value is specified, it is written to the output port indicated. If more than one value |                                                                                                                    |  |

is specified (up to a maximum of four), each value is written to the indicated port at 1 millisecond intervals with the first value going out immediately.

Example: Write the value 48H to port 01H of our 8048 target processor.

><u>0148<cr></u>

>

**Example:** Write the values 1, 2, and 3 to port 05H of our 8048 target processor. The value 1 is written immediately followed by the value 2 after 1 millisecond, and the value 3 after another millisecond.

><u>0 05, 1, 2,3<cr></u>

### **Registers and Control Signals Commands**

These commands display and permit the user to change the register contents of the target processor being emulated. Other commands in this group enables or disables some of the control signals going to the processor.

Register mnemonics and register sizes depend on the target being emulated; rarely are they the same for the different types of processors. For target processors with more than one set of registers, some registers may cross over, being in both sets. For more detailed information on the registers of the target being emulated, consult the corresponding guide in the appendices.

The controllable signals available also depend on the target processor being emulated. The possible signals are:

- A-external memory access

- B-bus request and acknowledge

- H-bus hold request and acknowledge

- I -- interrupt request

- N-non-maskable interrupt request

- T-trap request/timer interrupt

The available signal is either enabled or disabled at the input pin on the target processor. Only the sense input to the processor is affected; the circuits which generated the control signal in the target system are unaffected. For the target being emulated, consult the corresponding guide in the appendices on the control signals that are available.

## Register Display/Change Command-R

#### R [bank,] [register]

**R** is the command keyword (Register).

**bank** is one or two characters indicating the group of registers to be used when processors have more than one set of registers.

**register** is a single character indicating the target register whose content is to be displayed.

All register contents are displayed if no specific register is specified. For target processors with more than one set of registers, the currently selected set is always used when the bank selection is omitted. To determine whether the target processor being emulated has more than one set of registers, either consult the help (?) command or the corresponding guide in the appendices.

Example: Display the default (current) set of register contents for our 8048 target processor. > R < cr >

$\begin{array}{c} \underline{\text{CURRENT BANK}} = 0 \\ A & 0 & 1 & 2 & 3 & 4 & 5 & 6 & 7 & T & P & PC \\ BC & 48 & 02 & 67 & 89 & 48 & 00 & 85 & 42 & 00 & 08 & 0003 \\ \end{array}$

Example: Display the main and alternate sets of register contents.

> R . B0< cr>2 Α 0 1 3 4 5 6 7 Т Ρ PC BC 48 02 67 89 48 00 85 42 00 08 0003 > R B1<cr>Α 0 1 2 3 5 Т Ρ PC 4 6 7 28 34 09 AC 5D 76 5A EE 81 00 08 0003 >

If a register is specified, the content for that register is first displayed. MICE then waits for an input from the user. To advance to the next register, a line-feed should be entered; the next register's content is then displayed, and MICE again waits. Entering a line-feed repeats the entire sequence unless the next register displayed is the PC (program counter.) If either a carriagereturn or an escape is entered, the command is ended. If the next register is the PC, the command is also ended. To change the register content for the register displayed, enter the new hexadecimal value before the line-feed or the carriage-return.

Example: Change a few of the register contents of our 8048 target processor.

```

> R < cr >

\overline{\text{CURRENT}} BANK = 0

A 0 1 2 3

5

6

Т

Ρ

PC

4

7

BC 48 02 67 89 48 00 85 42 00 08 0003

> R B0 A<cr>

A \overline{BC < lf >}

0 48 \overline{BC} lf>

1 02 \overline{BB < lf} >

2 67 \overline{02 < lf >}

3 89 17<lf>

4 48 <lf>

5 00 <cr>

> R

<cr>

CURRENT BANK = 0

A 0 1 2 3 4 5 6 7 T P

PC

BC BC BB 02 17 48 00 85 42 00 08 0003

```

To change the program counter (PC), the command J is used and is described in the following command description. Also, some registers may be common to both banks for processors with more than one set of registers. For the particular processor being emulated, consult the corresponding guide in the appendices.

## Program Counter Change Command-J

#### J address

**J** is the command keyword.

**address** is the hexadecimal address of the target processor's program memory location to which the program counter is to be set.

Changing the target processor's program counter causes subsequent emulation to continue from that address in the program memory space.

Example: Change the program counter of our 8048 program from the current address of 0003H to 0002H.

> R < cr > $\overline{\text{CURRENT}}$  BANK = 0 5 6 A 0 1 2 3 4 7 Т Ρ PC BC BC BB 02 17 48 00 85 42 00 08 0003 > J 02 < cr >> R B0 < cr>2 A 0 1 3 5 PC 4 6 7 Т Ρ BC BC BB 02 17 48 00 85 42 00 08 0002 >

# Disable Control Signal Command-D

#### D control-signal

D

is the command keyword (Disable).

**control-signal** is a single alphabetic character

{AIBIHIINIT}

indicating a control signal to the target processor.

A-external memory access

B-bus request and acknowledge

H-bus hold request and acknowledge

I -- interrupt request

N-non-maskable interrupt request

T-trap request/timer interrupt

The control-signal specified is deactivated at the pin on the target processor. This command only affects the sense input to the processor; the circuits which generated the control-signal are unaffected. When resetting the processor using the X command (to be described later), these signals are activated if the MICE emulator is connected to a power-applied target system.

Not all of the control signals are available to a target processor. For the particular processor being emulated, either consult the help (?) command or the corresponding guide in the appendices.

Example: Deactivate the interrupt request control signal to our 8048 target processor, thereby, not processing any interrupts which may occur.

><u>DI<cr></u>

>

## Enable Control Signal Command-E

#### **E** control-signal

| E              | is the command keyword (Enable).                                                                                                                                  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| control-signal | is a single alphabetic character<br>{AIBIHIINIT}                                                                                                                  |

|                | indicating a control signal to the target processor.                                                                                                              |

|                | A-external memory access                                                                                                                                          |

|                | B – bus request and acknowledge                                                                                                                                   |

|                | H – bus hold request and acknowledge                                                                                                                              |

|                | I — interrupt request                                                                                                                                             |

|                | N—non-maskable interrupt request                                                                                                                                  |

|                | T-trap request/timer interrupt                                                                                                                                    |

|                | nal specified is activated at the pin on the target processor. When resetting th<br>the X command (to be described later), these signals are not activated if the |

he e MICE emulator is not connected to a power-applied target system.

Not all of the control signals are available to a target processor. For the particular processor being emulated, either consult the help (?) command or the corresponding guide in the appendices.

Example: Activate the interrupt request control signal to our 8048 target processor, thereby, allowing any interrupts which may occur.

> E I < cr >>

# Reset Target Processor Command-X

#### X [address]

X is the command keyword.

**address** is the hexadecimal address of the target processor's program memory to which the program counter is to be set after the reset.

A signal pulse is generated on the appropriate pin of the target processor under emulation to reset it. The processor's program counter, registers, and flags may be altered depending on the type of processor under emulation. Only the target processor is reset, any other circuits in the target system that are also connected to the same pin are not affected by the reset. In addition, control and interrupt signals to the target processor that are selectively controllable by the disable and enable commands are activated if the MICE emulator is connected to a power-applied target system.

An optional start address can be specified; it sets the target processor's program counter to the specified program memory address.

Example: Reset our 8048 target processor, showing the changes in the program counter, registers, and flags before and after.

> R < cr > $\overline{\text{CURRENT}}$  BANK = 0 A 0 1 2 3 5 Ρ PC 4 6 7 Т BC BC BB 02 17 48 00 85 42 45 08 0002 >X < cr > $> \overline{R B0} < cr>$

A

0

1

2

3

4

5

6

7

T

P

PC

BC

BC

BB

02

17

48

00

85

42

00

C8

0000

>X3<cr> > R B0 < cr >3 Α 0 1 2 PC 45 6 7 ТР BC BC BB 02 17 48 00 85 42 00 C8 0003 >

When targets execute the program halt instructions, the message "PROGRAM HALT!!" is printed. The target processor is disabled; the reset command must be used to enable the target.

# **Emulation and Trace Control Commands**

These commands control the mode of emulation for the target processor. Emulation may be stopped at user defined addresses, instruction-stepped, or cycle-stepped. Additionally, program operation may be recorded either forward from or backward to a user defined trigger address; up to 256 trace steps can be recorded. However, programs running in trace mode execute approximately 2 to 3 orders slower than real time since MICE stops the target processor after each cycle to record the status. Execution is also slower when emulation is to be stopped at a defined address since MICE must stop the target to compare the address after each cycle.

Status information displayed by the commands uses the following column headings:

#### IFADDR ADDRESS DATA STATUS

Where;

IFADDR is the instruction fetch address. ADDRESS is the value on the address bus. DATA is the value on the data bus. STATUS is the type or processor activity

A – interrupt acknowledge

F – program memory fetch

I – port input

O - port output

R – external/data memory read

S — instruction fetch

W-external/data memory write

## Begin Emulation Command-G

#### G [address]

G is the command keyword (Go).

**address** is the hexadecimal address of the target processor's memory from which emulation is to begin.

The target processor's program counter is first set to the address indicated. MICE then starts the real-time emulation of the target processor. If no address is specified, program emulation starts at the current program counter. Aside from the help (?) and the attention (!) commands, entering a new MICE command stops the emulation.

Example: Resume program emulation of our 8048 program, whose current program counter is 0003H, from 0002H.

> R < cr >CURRENT BANK = 0A 0 1 2 3 4 Р PC 5 6 7 T BC BC BB 02 17 48 00 85 42 00 08 0003 >G 02 < cr >> R B0 < cr >A 0 1 2 3 45 6 7 Т Ρ PC 13 13 13 02 17 48 00 85 42 00 08 0004 >

Example: Resume program emulation of our 8048 program from the current program counter of 0004H.

><u>R B0<cr></u> A 0 1 2 3 4 5 6 7 T P PC 13 13 13 02 17 48 00 85 42 00 08 0004 ><u>G<cr></u>

### Halt Emulation Command—H

H [address [, count]]

H is the command keyword (Halt).

**address** is the hexadecimal address of the target processor's memory where emulation is to be stopped.

**count** is a hexadecimal value from 0000H to FFFFH specifying the number of times the indicated address is to be encountered before emulation is stopped with 0000H indicating that emulation is to be stopped at the 65536th occurrence.

Emulation of the target processor is first stopped. If neither the address nor the count is specified, the current status is displayed. On the other hand, an address specification restarts the emulation from the current address until the address in the bus compares with the indicated halt address. MICE then stops the emulation and displays the new status. If the address encountered is in the mid-cycle of an instruction, that instruction is completed for processors that do not support single-cycle operation.

A count may also be specified to indicate the number of times the address is to be encountered before MICE stops the emulation. If no count is specified, the count is one, and the emulation stops at the first occurrence of the address.

Example: Stop the emulation of our 8048 target processor and display its current status.

>H<cr>IFADDR ADDRESS DATA STATUS 0002 0002 A8 S > R B0<cr>Α 2 3 6 ТР 0 1 4 5 7 PC 87 86 86 02 17 48 00 85 42 00 08 0002 >

Example: Restart emulation with the halt address in the middle of an instruction in our 8048 program.

| <b>/</b> п   | 0           |           |     |     |    |    |            |    |     |     |      |

|--------------|-------------|-----------|-----|-----|----|----|------------|----|-----|-----|------|

| IFAI         | DDE         | <u> </u>  | ADI | ORE | SS | DA | <b>ATA</b> | S  | TAT | rus |      |

|              |             |           | 0   | 006 |    |    | 02         |    | F   |     |      |

| 0002         |             |           | •   | 002 |    |    | A8         |    | S   |     |      |

| > <u>R</u> ] | <u>B0 -</u> | <cr></cr> | 2   |     |    |    |            |    |     |     |      |

|              |             |           | 2   |     |    |    |            |    |     |     |      |

| 88           | 87          | 87        | 02  | 17  | 48 | 00 | 85         | 42 | 00  | 08  | 0002 |

| ~            |             |           |     |     |    |    |            |    |     |     |      |

Because our 8048 can not be stopped in mid-cycle, emulation is stopped at the next instruction in the above example.

If the count value is too large or the address has not yet been encountered, entering an escape stops the emulation and ends the command.

Example: Restart emulation and stop at the 34th (22H) occurrence of address 95H, an address which our 8048 program never reaches.

$\begin{array}{c} > \underline{H,95\ 22 < cr >} \\ \underline{<esc>} \\ > \underline{R\ B0 < cr>} \\ A \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ T \ P \ PC \\ BC \ BC \ BB \ 02 \ 17 \ 48 \ 00 \ 85 \ 42 \ 00 \ 08 \ 0003 \\ > \end{array}$

38

С

C is the command keyword (Cycle).

MICE stops the processor and displays the current status of the target and waits for an input from the user. To advance the target processor to the next machine cycle, a line-feed should be entered; the new status is then displayed, and MICE again waits. Entering a line-feed repeats the entire sequence. If either a carriage-return or an escape is entered instead, the single-cycle mode of emulation is ended.

Example: Cycle step our 8048 program. Note that the processor does not begin emulation until the current status is displayed and until a line-feed is entered.

| > R, B0 $<$ cr      |            |                                                   |

|---------------------|------------|---------------------------------------------------|

| A 0 1               | 2 3 4      | 5 6 7 T P PC                                      |

| BC BC BB            | 02 17 48   | 00 85 42 00 08 0003                               |

| > <u>C<cr></cr></u> |            |                                                   |

| IFADDR              | ADDRESS    | DATA STATUS                                       |

| 0003                | 0003       | A9 $S \leq lf >$                                  |

| 0004                | 0004       | $17 S \leq lf >$                                  |

| 0005                | 0005       | 04 S $\leq lf \geq$                               |

|                     | 0006       | 02 F                                              |

| 0002                | 0002       | A8 $S \leq lf >$                                  |

| 0003                | 0003       | A9 $S \leq lf > lf$ |

| 0004                | 0004       | $17  S \overline{\langle cr \rangle}$             |

| >R <cr></cr>        |            |                                                   |

| CURRENT             | A BANK = 0 |                                                   |

| A 0 1               | l 2 3 4    | 567TPPC                                           |

| BD BD BD            | 0 02 17 48 | $00 \ 85 \ 42 \ 00 \ 08 \ 0004$                   |

| >                   |            |                                                   |

In the above example, MICE did not pause at the third cycle because our target processor does not support single-cycle operation. Hence, the entire instruction is executed and status displayed before MICE again waits.

Example: The cycle step mode of emulation can be terminated before a single cycle has advanced by entering either a carriage-return or an escape in response to the first status line.

```

> R B0<cr>

A 0 1 2

3 \ 4 \ 5

6

7 T

Ρ

PC

BD BD BD 02 17 48 00 85 42 00 08 0004

>C < cr >

IFADDR

ADDRESS

DATA

STATUS

0004

0004

17

S < esc >

> RB0< cr>

A 0 1 2

3

4 5 6

7 T P

PC

BD BD BD 02 17 48 00 85 42 00 08 0004

>

```

### Instruction Step Command—S

#### S [count]

**S** is the command keyword (Step).

**count** is a hexadecimal value from 0000H to FFFFH specifying the step interval between the status display with 0000H indicating that the display occurs every 65536 steps.

If no step count is specified, MICE assumes an instruction step count of one. In this mode of operation, MICE first displays the current status of the target and waits for an input from the user. To cause the target processor to execute the next instruction, a line-feed should be entered; the new status is then displayed, and MICE again waits. Entering a line-feed repeats the entire sequence where the new status is displayed after every instruction. If either a carriage-return or an escape is entered instead, the single step mode of emulation ended.

Example: Single step our 8048 program. Note that the processor does not begin emulation until the current status is displayed and until a line-feed is entered.

| >R < cr>            |               | 1-1-5 |    |     |    |                                            |              |      |

|---------------------|---------------|-------|----|-----|----|--------------------------------------------|--------------|------|

| CURRENT             | <b>F BANK</b> | = 0   |    |     |    |                                            |              |      |

| A 0 1               |               |       | 5  |     |    | Т                                          |              | PC   |

| BD BD BI            | 0 02 17       | ′48   | 00 | 85  | 42 | 00                                         | 08           | 0004 |

| > <u>S<cr></cr></u> |               |       |    |     |    |                                            |              |      |

| IFADDR              | ADDR          | ESS   | DA | ATA | S  | TAT                                        | CUS          |      |

| 0004                | 0004          | ł     |    | 17  |    | 5 <u><l< u="">t</l<></u>                   | <u>f&gt;</u> |      |

| 0005                | 0005          | 5     |    | 04  |    | 5 <li< td=""><td>f&gt;</td><td></td></li<> | f>           |      |

| 0002                | 0002          | 2     |    | A8  | Ś  | S < li                                     | f>           |      |

| 0003                | 0003          | 3     |    | A9  | 5  | $S\overline{$                              | f>           |      |

| 0004                | 0004          | ŧ.    |    | 17  |    | $3\overline{<}c$                           | r>           |      |

| >R <cr></cr>        |               |       |    |     |    |                                            |              |      |

| CURRENT             | Γ BANK        | = 0   |    |     |    |                                            |              |      |