# **NEW MICE-II USER'S MANUAL**

# **FOR 8-BIT ZILOG**

# **SERIES MICROPROCESSORS**

- Z80, NSC800, Z8, ZS8 -

# USER'S MANUAL FOR NEW MICE-II

z80 NSC800 z8 zs8

Doc No. 149-000115 2nd Edition January 1989

### DISCLAIMER

© 1989 MICROTEK INTERNATIONAL, INC. All rights reserved.

This manual is subject to change without notice. Nothing herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties.

NEW MICE-II AND THIS MANUAL ARE COVERED BY THE LIMITED WARRANTY SUPPLIED WITH NEW MICE-II AND REPRODUCED IN APPENDIX N OF THIS MANUAL.

Printed in Taiwan, ROC January 1989

#### MICROTEK INTERNATIONAL INC.

6 Industrial Road East 3 Science-Based Industrial Park Hsinchu, Taiwan, 30077, R.O.C.

TEL: (035)772155 TLX: 32169 MICROTEK FAX: (035)772598

#### PREFACE

Microtek International Inc. proudly presents the award winning Micro-In-Circuit-Emulator, NEW MICE-II. You have made an excellent purchase and will soon benefit from the many advance features that Microtek designs into all of its products.

With the detailed instructions provided in this manual, you can rapidly set up and operate your new NEW MICE-II. The information provided in this user's manual is believed accurate and complete, but no responsibility is assumed for any error or omission.

Microtek is dedicated in providing leadership in the microcomputer-based industry. We continue to design new emulators with enhanced features, low cost and always geared toward the microprocessor designer's need. Thank you for choosing Microtek; and may we suggest that you also investigate the many other fine products that Microtek has to offer.

The sale of any Microtek product is subject to all Microtek Terms and Conditions of Sale and Sales Policies, copies of which are available upon request.

Microtek supplies a variety of hi-tech equipment to the microprocessor-based industry. For further information on other Microtek products and/or any other questions regarding this manual, please contact Microtek head-quarters.

# **NEW MICE-II**

# Section

# TABLE OF CONTENTS

|           |       |     |                                      | Page          |

|-----------|-------|-----|--------------------------------------|---------------|

| CHAPTER : |       |     | RAL INTRODUCTION                     | 1-1           |

|           |       |     | Introduction to MICE                 | 1-1           |

|           | 1.    |     | Introduction to NEW MICE-II          | 1-3           |

|           |       |     | 1.2.1 Enhanced Features              | 1-3           |

|           |       |     | 1.2.2 New Breakpoint Processor       | 1-4           |

|           |       |     | 1.2.3 Major Hardware Overview        | 1-5           |

|           |       |     | 1.2.4.Conclusion                     | 1-6           |

|           | 1.    | . 3 | NEW MICE-II Operating Configurations | s1 <b>-</b> 7 |

|           |       |     | 1.3.1 Universal Symbolic Debugger    |               |

|           |       |     | (USD)                                | 1-8           |

|           |       |     | NEW MICE-II Applications             | 1-12          |

|           | 1.    | .5  | NEW MICE-II Definitions              | 1-13          |

| CHAPTER 2 | 2: NI | EW  | MICE-II INSTALLATION PROCEDURES      | 2-1           |

|           |       |     | Setting Up NEW MICE-II               | 2-1           |

|           |       |     | 2.1.1 Opening the NEW MICE-II Case   | 2-1           |

|           |       |     | 2.1.2 Replacing the Personality      |               |

|           |       |     | Board or Emulation CPU               | 2 <b>-</b> 3  |

|           |       |     | 2.1.3 Internal Adjustments           | 2-4           |

|           |       |     | 2.1.4 Connecting the ICE Cable       | 2-4           |

|           |       |     | 2.1.5 Connecting the External Trace  |               |

|           |       |     | Cable                                | 2-8           |

|           |       |     | 2.1.6 Closing the NEW MICE-II Case   | 2-9           |

|           | 2.    | .2  | NEW MICE-II Specifications           | 2-10          |

|           | 2.    | 3   | Communicating with NEW MICE-II       | 2-11          |

|           | 2.    | . 4 | Control Emulation Processor Board    |               |

|           |       |     | (CEP) Setup                          | 2-11          |

|           |       |     | 2.4.1 Interface Parameter Selection  |               |

|           |       |     | 2.4.2 Clock Selection                | 2-13          |

|           |       |     | 2.4.3 Ready Signal Selection (Z80    | _             |

|           |       |     | and NSC800)                          | 2-16          |

|           |       |     | 2.4.4 Bus State Selection (Z80)      | 2-16          |

|            |     | 2.4.5 Vcc Selection (NSC800)        | 2-17 |

|------------|-----|-------------------------------------|------|

|            |     | 2.4.6 ISR Function (Z80)            | 2-18 |

|            | 2.5 | High Performance Universal Emula-   |      |

|            |     | tion Memory (HUEM) Setup            | 2-19 |

|            |     | 2.5.1 U14 and U36: Emulation Memory | -    |

|            |     | Enable/Disable                      | 2-19 |

|            |     | 2.5.2 U28 and U43: Memory Segment   | -    |

|            |     | Selection                           | 2-20 |

|            |     | 2.5.3 Factory Preset                | 2-21 |

|            | 2.6 | Memory Selection for Microcontrol-  |      |

|            |     | lers (Z8 and ZS8)                   | 2-22 |

|            |     | 2.6.1 Memory Selection for NEW      |      |

|            |     | MICE-II Z8                          | 2-22 |

|            |     | 2.6.2 Memory Selection for NEW      |      |

|            |     | MICE-II ZS8                         | 2-26 |

|            |     | RS-232C Cable Connection            | 2-30 |

|            | 2.8 | Applying Power to NEW MICE-II       | 2-33 |

|            |     | 2.8.1 No Response                   | 2-35 |

|            |     | 2.8.2 Failure Device                | 2-36 |

|            | 2.9 | Control Processor Software Reset    |      |

|            |     | Command                             | 2-36 |

|            |     |                                     |      |

| CHAPTER 3: |     | MICE-II COMMAND LANGUAGE            | 3-1  |

|            | 3.1 | Command Syntax                      | 3-3  |

|            | -   | Notations and Conventions           | 3-4  |

|            |     | Editing Characters                  | 3-6  |

|            |     | Control Characters and Delimiters   | 3-7  |

|            | 3.5 | Reference Program for Examples      | 3-8  |

| CHAPTER 4: | NEW | MICE-II UTILITY COMMANDS            | 4-1  |

|            | 4.1 | ? Help Command                      | 4-2  |

|            | 4.2 | ! Attention Command                 | 4-4  |

| CHAPTER 5: | MEMORY       | , PORT AND REGISTER COMMANDS    | 5-1               |

|------------|--------------|---------------------------------|-------------------|

| _          | 5.1 M        | Memory Display/Examine/Modify/  |                   |

|            |              | Fill/Search Command             | 5-3               |

|            |              | 5.1.1 Memory Display            | 5-5               |

|            |              | 5.1.2 Memory Examine/Modify     | 5-6               |

|            |              | 5.1.3 Memory Fill               | 5-7               |

|            |              | 5.1.4 Memory Search             | 5-8               |

|            | 5.2 T        | Memory Checksum/Test/Transfer/  |                   |

|            |              | Compare Command                 | 5-9               |

|            |              | 5.2.1 Memory Checksum           | 5-10              |

|            |              | 5.2.2 Memory Test               | 5-11              |

|            |              | 5.2.3 Memory Transfer           | 5-12              |

|            |              | 5.2.4 Memory Compare            | 5-14              |

|            |              | Line Assembly Command           | 5-16              |

|            | 5.4 Z        | Disassembly Command             | 5 <del>-</del> 20 |

|            | 5.5 I        | Port Input Command              | 5-23              |

|            |              | Port Output Command             | 5-25              |

|            | 5.7 X        | Reset/Initialization Command    | 5-26              |

|            | 5.8 R        | Register Display/Modify Command | 5-28              |

|            |              | 5.8.1 Register Command for NEW  |                   |

|            |              | MICE-II Z80 and NSC800          | 5-28              |

|            |              | 5.8.2 Register Command for NEW  |                   |

|            |              | MICE-II Z8                      | 5-30              |

|            |              | 5.8.3 Register Command for NEW  |                   |

|            |              | MICE-II ZS8                     | 5 <b>-</b> 33     |

|            | 5.9 <b>J</b> | Jump/Branch Command             | 5-38              |

| CHAPTER 6: | CONTRO       | OL SIGNAL COMMANDS              | 6-1               |

| <b></b>    | 6.1 E        | Enable/Display Control Signal   |                   |

|            | J            | Command                         | 6 <b>-</b> 3      |

|            | 6.2 D        | Disable/Display Control Signal  | 9                 |

|            |              | Command                         | 6-4               |

| CHAPTER | 7: |              | ATION AND TRACE CONTROL                      |      |

|---------|----|--------------|----------------------------------------------|------|

|         |    | COMM         |                                              | 7-1  |

|         |    | 7.1          | G Go/Execution Command                       | 7-4  |

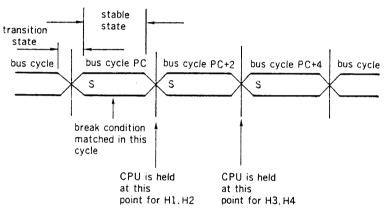

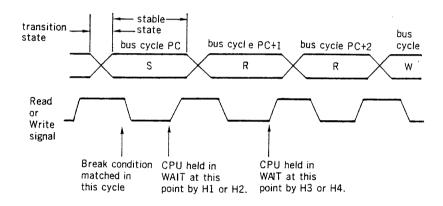

|         |    | 1.2          | H Halt/Breakpoint Set Command                | 7-5  |

|         |    |              | 7.2.1 Halt                                   | 7-6  |

|         |    |              | 7.2.2 Set Breakpoint                         | 7-6  |

|         |    |              | 7.2.3 Display Breakpoint                     | 7-8  |

|         |    |              | 7.2.4 Clear Breakpoint                       | 7-9  |

|         |    | 7.3          | F Forward Trace Command                      | 7-10 |

|         |    | 7.4          | B Backward Trace Command                     | 7-1  |

|         |    | 7.5          | L List/Display Trace Buffer                  | •    |

|         |    |              | Command                                      | 7-1  |

| CHAPTER | 8- | STEP         | PED EMULATION COMMANDS                       | 0 1  |

|         | •  | 8 1          | C Single Cycle, Step Command                 | 8-1  |

|         |    | 8 2          | S Instruction Step Command                   | 8-2  |

|         |    | 0.2          | 8.2.1 Instruction Step                       | 8-4  |

|         |    |              | 8.2.2 Instruction Step in                    | 8-5  |

|         |    |              | Mnemonic Form                                | 0 (  |

|         |    |              |                                              | 8-6  |

|         |    |              | 8.2.3 Instruction Step with                  | 0 (  |

|         |    |              | Register Content                             | 8-6  |

|         |    |              | 8.2.4 Instruction Step with Count            | 0 0  |

|         |    |              |                                              | 8-9  |

|         |    |              | 8.2.5 Instruction Step with                  | 0 4  |

|         |    | 834          | Cycle Status<br>Application Note for Stepped | 8-10 |

|         |    | 0.5 <i>I</i> | Emulation Commands                           | 8-13 |

|         |    |              |                                              | 0 1. |

| CHAPTER | 9: | UTILI        | ITY COMMANDS INVOLVING A SYSTEM              | 9-1  |

|         |    | 9.1:         | Download Command (Intel Format)              | 9-2  |

|         |    | 9.2 /        | / Download Command (Tektronix                | ,    |

|         |    |              | Format)                                      | 9-6  |

|         |    | 9.3 t        | J Upload Command                             | á-a  |

# APPENDICES

| A:         | Summary of NEW MICE-II Commands             | A-1 |

|------------|---------------------------------------------|-----|

| в:         | Hexadecimal-Decimal Conversion              | B-1 |

| C:         | ASCII Code Lists and Definitions            | C-1 |

| D:         | Writing a Driver Program                    | D-1 |

| <b>E</b> : | NEW MICE Driver Programs                    | E-1 |

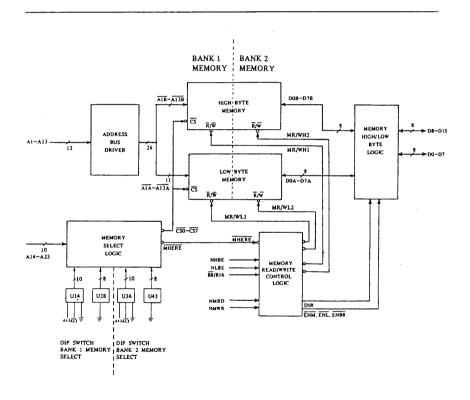

| F:         | High Performance Universal Emulation Memory |     |

|            | Board (HUEM)                                | F-1 |

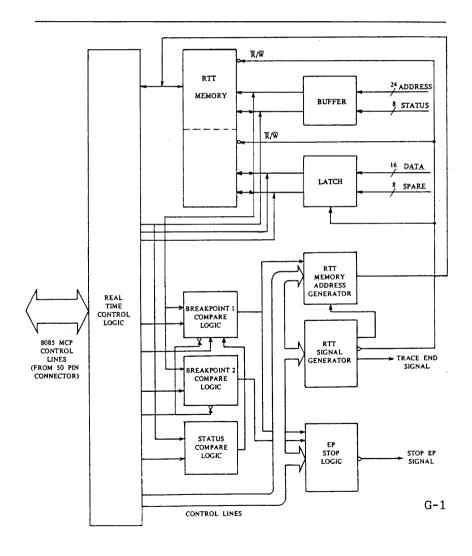

| G:         | Real-time Trace Board (RTT)                 | G-1 |

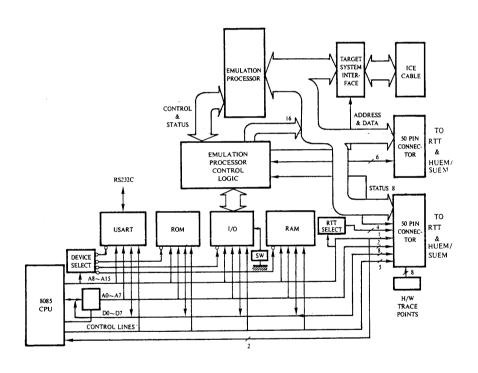

| Н:         | Control Emulation Processor Board (CEP)     | H-1 |

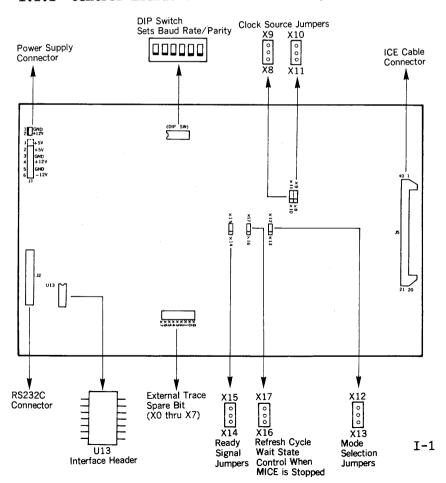

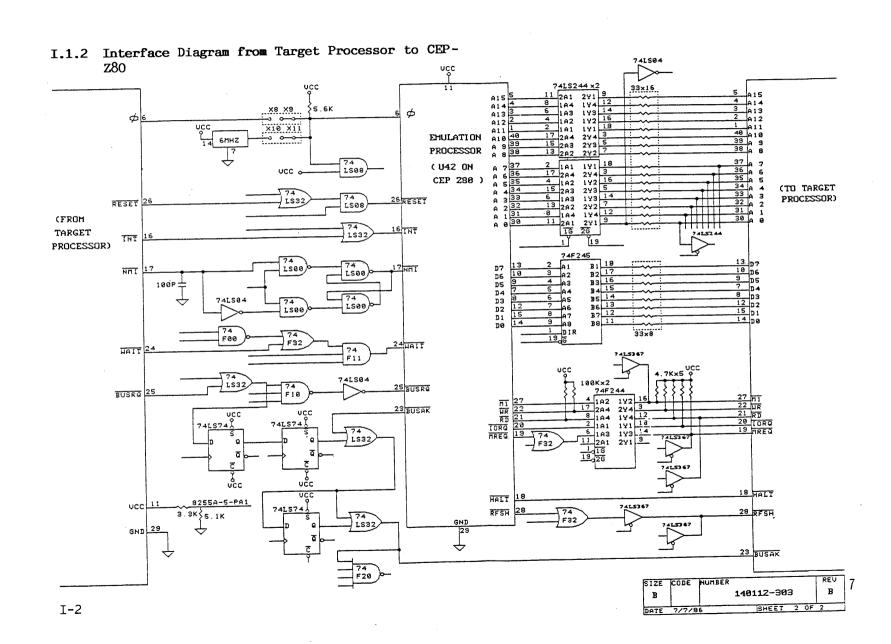

| I:         | Z80                                         | I-1 |

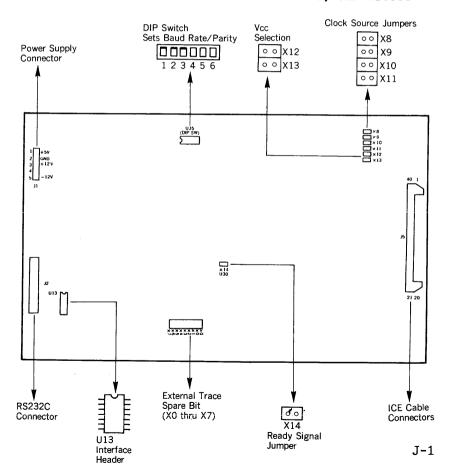

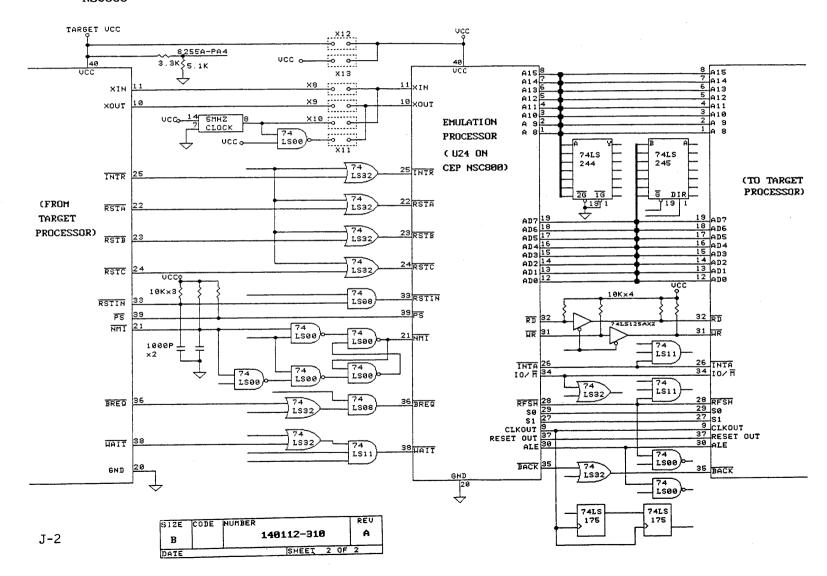

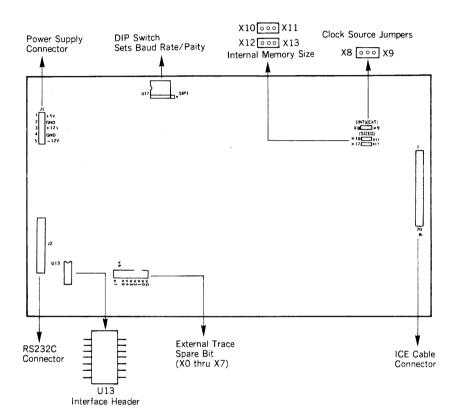

| J:         | NSC800                                      | J-1 |

| K:         | Z8                                          | K-1 |

| L:         | ZS8                                         | L-1 |

| M:         | Error Messages                              | M-1 |

|            | Warranty and Service                        | N-1 |

# MICE International Distributors

#### CHAPTER 1

#### GENERAL INTRODUCTION

### 1.1 Introduction To MICE

Microtek's versatile Micro-In-Circuit-Emulator (MICE) is a low-cost development tool that emulates most industry-standard microprocessors. It has set new standards for universal, high-performance emulation, at an exceptionally low cost-per-function.

Traditionally, microprocessor development was done on dedicated systems. The computer system had its complement of peripheral devices and sufficient mass storage to accommodate user programs, data, etc. A dedicated emulator was attached to the system to assist the designer in ensuring that both hardware and software were functioning properly.

Recently, a variety of general purpose computers have been designed for use in microprocessor development. Through the use of cross assemblers, code can be generated for the target system. However, these emulators are still dedicated to the particular computer.

With MICE, a third and more practical approach to microprocessor development is now available; one that uses fewer resources, performs most of the same functions, yet costs only a fraction compared with its predecessors. The MICE module is controlled via an RS-232C compatible interface. All software required to operate the MICE module are contained in EPROMs within the module. MICE can be operated by using a display

terminal only or in conjunction with a computer system. Different processors can be emulated by merely changing the personality card and associated EPROMs.

# Some key features of MICE are:

- \* Operation at speeds up to the maximum rated frequency of the specified microprocessor.

- \* Target processor retains its entire memory and I/O space.

- \* Enabling and disabling of hardware control signals to the processor with console commands.

- \* Resident assembler and two-pass disassembler which assigns labels to subroutine and branch addresses.

- \* Built-in memory diagnostics and block memory transfer for target processor memory.

- \* Downloading and uploading of target program between MICE and host computer system.

- \* Help command that lists all commands along with the proper syntax.

#### 1.2 Introduction to NEW MICE-II

# 1.2.1 Enhanced Features

NEW MICE-II is an enhanced member of the MICE family. Aside from retaining the original MICE features, NEW MICE-II has substantially been upgraded to include the following new features:

- \* High Performance Universal Emulation Memory (HUEM) with memory size selectable at 64K or 128K bytes (2 independent 64K settings) of static RAM for 8-bit NEW MICE-II models (user must specify if required for microcontroller versions).

- \* Super Universal Emulation Memory (SUEM) with memory size 256K bytes of static RAM for 8 bit NEW MICE-II models.

- \* 8/256 Kbytes block enable/disable capability for HUEM/SUEM.

- \* User-qualified trigger to specify start or end of tracing for source code and machine statuses. Up to 2048 cycles and 40 channels of signals may be recorded for program debug.

- \* Supports up to 8 hardware trace points for program debug.

- \* Real-time forward and backward trace for up to 2048 machine cycles.

- \* Two real-time breakpoints.

- \* Supports disassembly for both Instruction Step and List Trace commands.

- \* With built-in power supply and cooling fan.

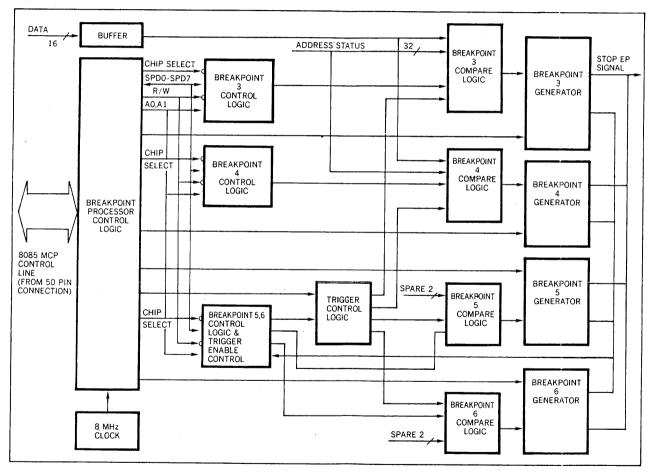

### 1.2.2 Breakpoint Processor

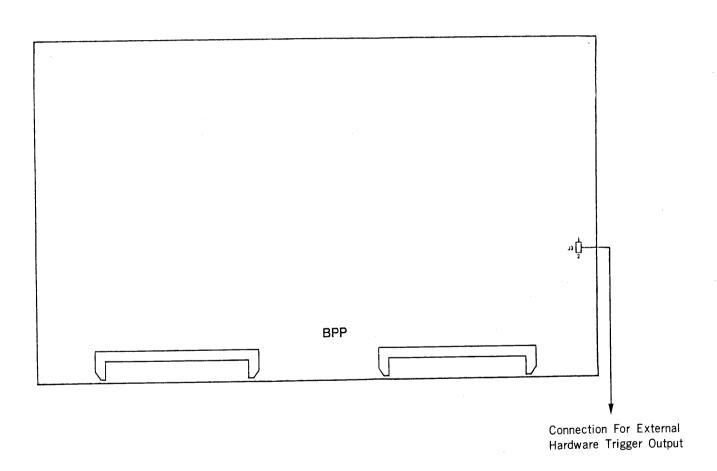

NEW MICE-II may also be equipped with the new Breakpoint Processor (BPP) board at user's option. The board allows the NEW MICE-II to provide more advanced features as summarized below:

- \* Sophisticated breakpoint logic, with up to 120 new breakpoint constructs.

- \* Flexible trigger constructs that can define single events, multiple activities or external hardware signals.

- \* Two data breakpoints and two external hardware breakpoints.

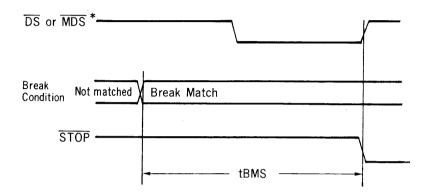

- \* Breakpoint interval timer that displays the interval between initial trigger and emulation stops.

# 1.2.3 Major Hardware Overview

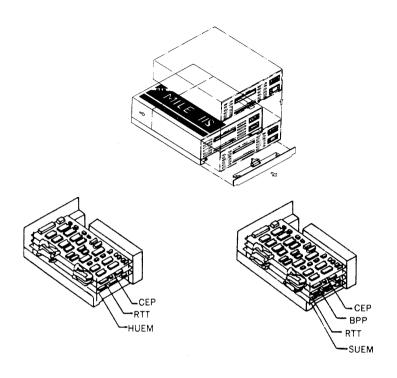

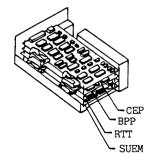

NEW MICE-II is a low-cost powerful emulation instrument basically equipped with the following boards:

# Control Emulation Processor (CEP)

- also called personality board

Real-time Trace (RTT)

High Performance Universal Emulation Memory (HUEM) or Super Universal Emulation Memory (SUEM)

- also called memory board

# BreakPoint Processor (BPP)

Remember that the CEP board can be interchanged to form any other NEW MICE-II. If more emulation memory is needed, additional HUEM boards may be added. And where more powerful emulation breakpoint or triggering capability is required, the BPP board is available.

#### 1.2.4 Conclusion

At half the cost of competitive units, NEW MICE-II provides features not available with other emulators. Some of the advantages of NEW MICE-II over other emulators are:

universality A wide variety of microprocessors can be emulated using this single development tool, thus avoiding both the inflexibility of dedicated systems and the heavy capital investment required for general purpose systems.

versatility Emulation of a different processor only requires changing the personality board.

Multiple design projects can be carried out concurrently, and the CEP board can be reused for different projects.

flexibility With NEW MICE-II providing its own resident assembler and disassembler, it can be minimally configured with just a display terminal and power supply. After the target program has been downloaded from the host computer, testing can be done off-line, thereby freeing the computer.

### 1.3 NEW MICE-II Operating Configurations

NEW MICE-II can be used in several configurations. The simplest configuration requires only an RS-232C compatible terminal as the display console and command entry device. A computer system can also be configured as the controlling device.

| CRT      | RS-232C | NEW MICE-II | Emulation | Target |

|----------|---------|-------------|-----------|--------|

| or Host  | Cable   |             | Cable     | System |

| Computer |         |             |           |        |

# Figure 1-1 Configuring NEW MICE-II With an RS-232C Compatible Terminal or Host Computer

When a computer system is interfaced with NEW MICE-II, a driver program must be resident in the system. Driver programs and symbolic translator drivers are available for various systems. (See Appendix E for a detailed listing.)

Microtek has access to various sources of driver programs and other software tools. For updated information contact your local Microtek representative.

# 1.3.1 Universal Symbolic Debugger (USD)

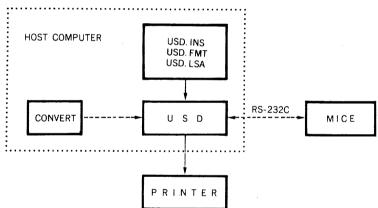

The USD (Universal Symbolic Debugger), is a sophisticated software package designed specifically to enhance the debugging and other capabilities of Microtek's MICE series of emulators. USD acts an interface between the MICE user, MICE, and the host computer system, to make the optimum use of the resources available on each. It enhances the range of development, emulation, analysis and debugging features of MICE to a new dimension and providing MICE users with a high quality and broad range of support to suit their various engineering applications.

- \* Universal

- \* Enhanced symbol processing capability

- \* File management

- \* Command file

- \* Logic state analysis

- \* Software performance analysis

- \* Sophisticated utility commands

- \* Fully supports object files, and MICE's

#### \* Universal

Almost all popular cross-assembler/cross-compiler formats, such as 2500AD, IAR, intel 0MF51/85/86, and MRI format symbol tables are accepted. MICE command for all type MICE are fully transparent.

# \* Enhanced symbolic processing capability

Symbol table file can be: loaded/listed/saved; symbols can also be created/deleted. Any address can be qualified to check for symbol equivalence.

# \* File management

Hex file can be down loaded to emulation/user memory, and data in memory can be uploaded to host computer. All MICE and USD commands can be logged as a macro command file; all debug commands as well as the command output can be logged as an output file. The logged output file is especially useful in detailed checking of sophisticated debug session.

#### \* Command file

Unlimited command lines can be edited in a command file. 10 replaceable parameters are permitted; conditional subcommands and loop block capability are provided.

# \* Logic state analysis

Trace buffer data, such as address bus, data bus, control, and spare signals can all be displayed in waveform.

# \* Software performance analysis

# Module entry histogram:

Display the number of calls for specified program addresses, along with a bar graph showing the percentage of processor activity for each address.

# Execution interval histogram:

Display the number of times a program routine executes within different timing frames, along with a bar graph showing the percentage of processor activity for each range.

# \* Sophisticated utility commands

Help for USD commands

Window facility is provided: foreground and background

windows

Up to 16 command lines can be retained

DOS commands access

# \* Fully supports object files, and MICE's

Firmware version supported (for the firmware and higher version).

#### For NEW MICE-II

| <b>z</b> 80 | V3.1 | & | later |

|-------------|------|---|-------|

| NSC800      | V3.2 | & | later |

| <b>z</b> 8  | V3.1 | & | later |

| zs8         | V3.0 | & | later |

# \* Host computers supported

IBM PC/XT/AT (MS-DOS 2.0)

NEC 9801 (MS-DOS 3.0)

SUN MICRO WORKSTATION (UNIX 2.0)

VAX/VMS 4.1

uVAX/ULTRIX

# 1.4 NEW MICE-II Applications

Because of its unique design, NEW MICE-II offers new applications which include:

- Inexpensive evaluation of new microprocessors without purchasing a special evaluation board or expensive development system.

- 2. Several designers can share the use of a single development system, eliminating the difficult problem of allocating a single resource and the need for multiple work-stations. Large programs can be edited, assembled or compiled, and then downloaded to the target system. Since NEW MICE-II has its own assembler and disassembler, the programs can then be tested using only a display terminal.

- 3. NEW MICE-II's compact size, light weight, and rugged construction makes it an ideal field service instrument. Easily transported and set up in remote locations, NEW MICE-II can reduce downtime, provide on the spot diagnosis and resolution of field problems, avoiding customer inconvenience and expensive service delays. With its RS-232C interface, NEW MICE-II can be quickly interfaced with any compatible display terminal. Diagnostic programs can be generated using the resident assembler.

- 4. Personal computers can be upgraded to development systems at a fraction of the typical costs. Driver programs for various computers have already been written, allowing programs assembled or compiled to be downloaded.

#### 1.5 NEW MICE-II Definitions

#### MICE

is a patented trade name for Microtek emulators and stands for Micro-In-Circuit-Emulator.

#### ICE cable

is an In-Circuit-Emulator cable that joins NEW MICE-II to the target.

#### NEW MICE-IIH

is a conventional MICE emulator module consisting of three interconnected printed circuit boards. These boards are:

- 1. Control Emulation Processor (CEP) board.

- 2. Real-time Trace (RTT) board.

- 3. High Performance Emulation Memory (HUEM) board.

#### NEW MICE-IIS

is a conventional MICE emulator module consisting of four interconnected printed circuit boards. These boards are:

- Control Emulation Processor (CEP) board.

- 2. Real-time Trace (RTT) board.

- 3. Super Universal Emulation Memory (SUEM) board.

- 4. Breakpoint Processor (BPP) Board.

#### CHAPTER 2

# NEW MICE-II INSTALLATION PROCEDURES

NEW MICE-II comes from the factory preset and completely assembled. The NEW MICE-II module consists of three printed circuit boards: Control Emulation Processor board (CEP), Real-time Trace board (RTT) and High Performance Universal Emulation Memory board (HUEM). ICE cables are also included which must be connected between NEW MICE-II and the target system.

### 2.1 Setting Up NEW MICE-II

Detailed instructions for setting up the NEW MICE-II module are as follows:

# 2.1.1 Opening the NEW MICE-II Case

NEW MICE-II is contained in a two piece high impact metal case. To open the case, hold the lower portion of the vertical end (rear) firmly with both hands and with your thumbs slide the top half forward about one half inch. This will separate the top from the bottom half.

NEW MICE-IIH NEW Figure 2-1

Opening The NEW MICE-II Case

NEW MICE-IIS

2-2

# 2.1.2 Replacing the Personality Board (CEP) or Emulation CPU

1. To install a personality board in place of the current card, the cover of the NEW MICE-II case must first be removed. With power off, carefully remove the top personality card (CEP) from the NEW MICE-II module by disconnecting the two ribbon cable connectors which join the CEP board to the RTT board below, and then removing the six locking screws and six brass spacers.

Install the new personality board into the module by refastening the brass spacers and locking screws to hold the replacement card permanently in position. Then reconnect the two ribbon cable connectors from the RTT board below to the CEP board; the arrows indicating pin 1 must be aligned.

2. Only one CPU is supplied with NEW MICE-II per the customer's specification. To emulate the other processor, replace the CPU as indicated below:

| NEW MICE-II | CPU                | Location |

|-------------|--------------------|----------|

| * Z80       | Z80/Z80A/Z80B/Z80H | U36      |

| NSC800      | NSC800             | U24      |

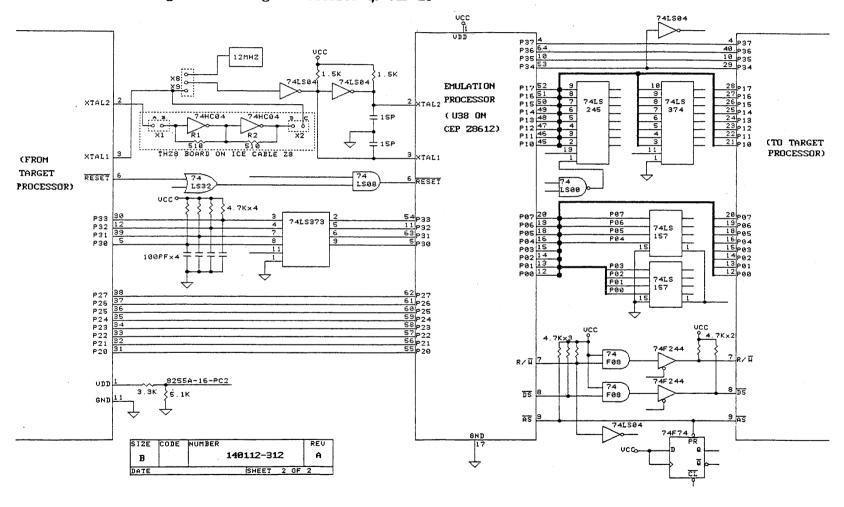

| z8          | z8612              | U38      |

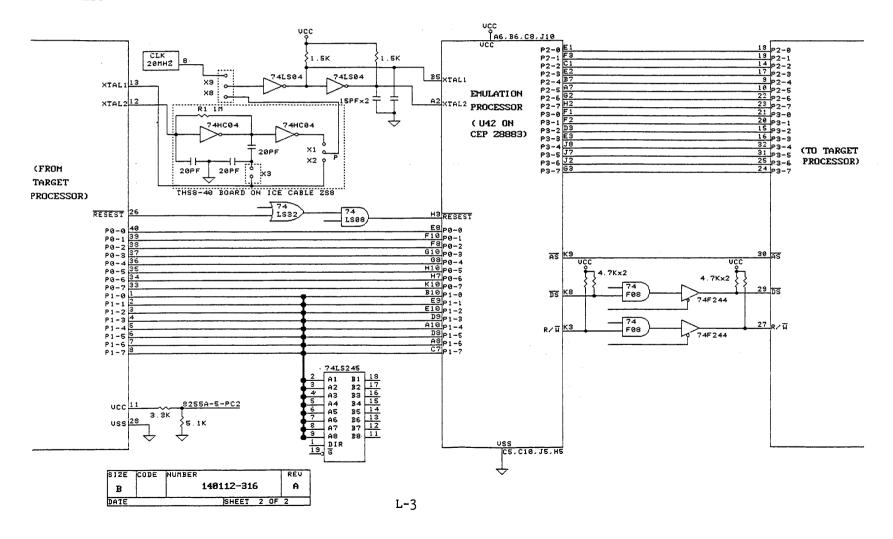

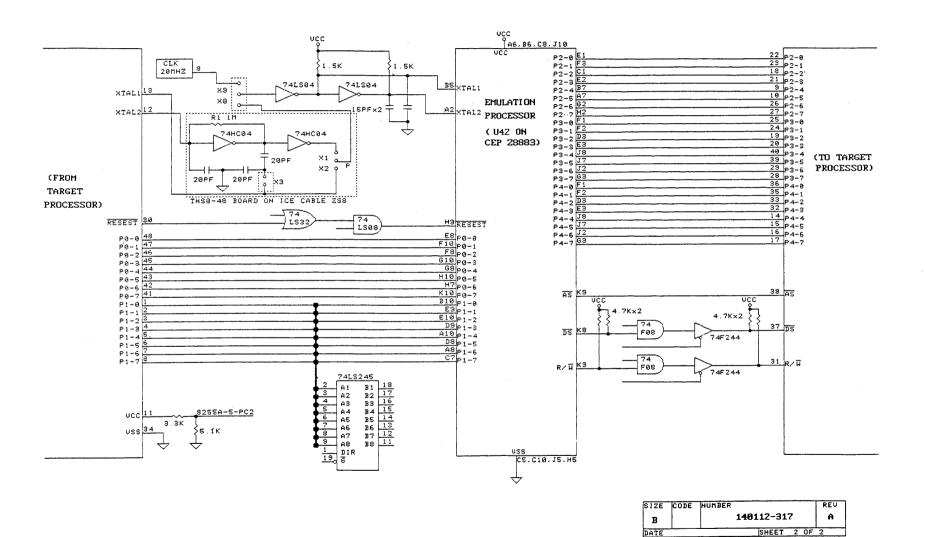

| zs8         | z8883              | U42      |

<sup>\*</sup> CPU alteration applicable to Z80 only.

# 2.1.3 Internal Adjustments

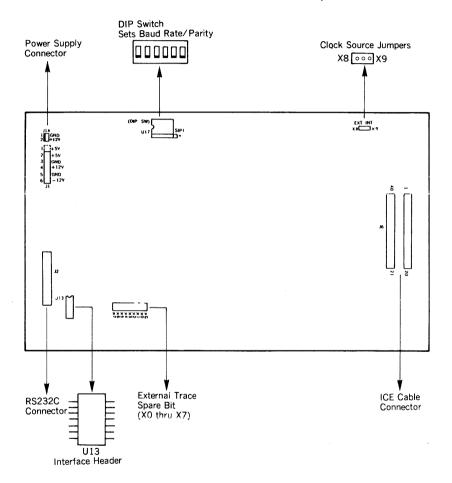

Access to all adjustment switches is possible with the NEW MICE-II cover removed. The DIP switch on the personality board is readily accessed from the top; and the three DIP switches for memory board selection are located in the opening at the end of the NEW MICE-II case, which results when the cover is removed. Preset instructions are explained in the following sections of this chapter.

# 2.1.4 Connecting the ICE Cable

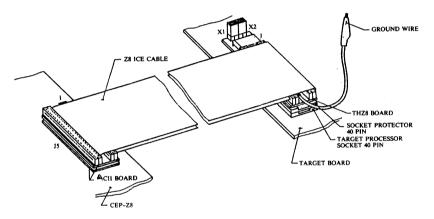

#### 1. Z80

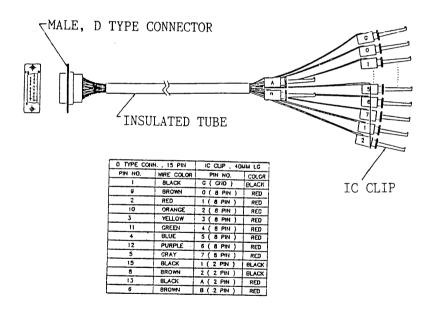

The ICE (In-Circuit-Emulator) cable assembly consists of one flat-wire cable with a 40-pin connector at one end and an IC header at the other end. To install the ICE cable after setup has been completed, remove the cover to NEW MICE-II, and attach the 40-pin connector at position J5 on the CEP board. Thread the IC header end through the rectangular opening in the NEW MICE-II case and slide the cover shut (section 2.1.6). Then attach the end with the IC header to the 40-pin target processor socket on the target board. Note that the ICE cable cannot be interchanged with other NEW MICE-II models.

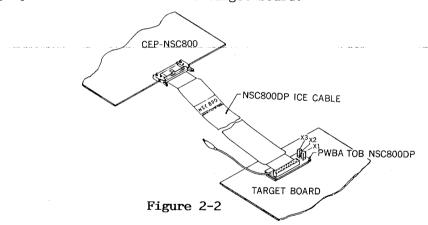

#### 2. NSC800

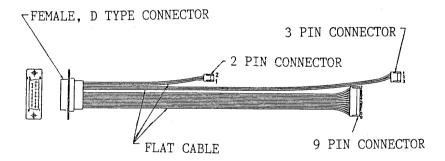

The ICE cable assembly (Figure 2-2) consists of an IC header at the Target Connected Board (TCB-NSC800DP). To install the ICE cable after setup has been completed, remove the cover of the NEW MICE-II, thread the connector end through the rectangular opening in the NEW MICE-II case, attach the 40-pin connetor on the CEP board and slide the cover shut. At the target end of the cable, remove the protective padding from the bottom of the IC header. Gently insert the header into the appropriate CPU socket on the target board.

# 3. z8

The ICE cable assembly (Figure 2-3) consists of two flat-wire cables with dual 40-pin connectors at one end (CHZ8) and a single 40-pin connector at the other end (THZ8). To install the ICE cable after setup has been completed, remove the NEW MICE-II cover and attach the end with dual 40-pin connectors at position J5 on the CEP board. Thread the IC header end through the

rectangular opening in the NEW MICE-II case and slide the cover shut (section 2.1.6). Then attach the end with a single 40-pin connector to the 40-pin target processor socket on the target board. (Note that the ICE cable cannot be interchanged with other NEW MICE-II models.)

Figure 2-3

# 4. zs8

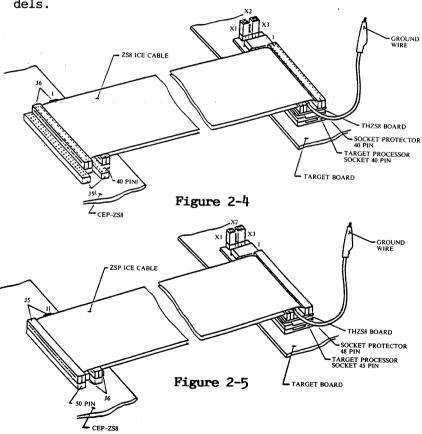

Two different ICE cables are used for 40 and 48 pin target CPUs. The ICE cable assembly for a 40-pin target CPU (Figure 2-4) consists of two flat-wire cables with dual 40-pin connectors at one end and a single 40-pin connector at the other end (THZS8-40). The ICE cable assembly for a 48-pin target CPU (Figure 2-5) consists of two flat-wire cables with dual 50-pin connectors at one end and a single 48-pin connector at the other end (THZS8-48).

To install the ICE cable after setup has been com-

pleted, remove the NEW MICE-II cover and attach the end with dual 40/50 pin connectors at position J6/J5 on the CEP board. Thread the IC header end through the rectangular opening in the NEW MICE-II case and slide the cover shut (section 2.1.6). Then attach the end with a single 40/48 pin connector to the 40/48 pin target processor socket on the target board. Note that the ICE cable cannot be interchanged with other NEW MICE-II models.

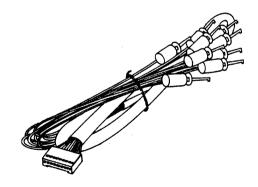

#### 2.1.5 Connecting the External Trace Cable

The external trace cable shown below is used for recording external signals during trace operations. To monitor any external activity not automatically recorded by trace commands, the input cable must be connected from the trace point connector on the CEP board to the target. This connector consists of a 9 post stick header on the CEP board designated XO-X7 from right to left, plus XG for ground.

The monitored signals are called spare bits and support concurrent trace with the address, data and status bus. Any of these bits can be monitored by trace commands to display hardware status (in the SPARE column) by executing List, Cycle Step and Instruction Step commands; where "1" represents a high (or floating) signal and "0" indicates a low signal.

Figure 2-6 Signal Monitor Cable

## 2.1.6 Closing the NEW MICE-II Case

To close the cover, set it over the base leaving a 1/2 inch gap. Holding the base firmly in the front, use your thumbs to push the cover the remaining distance. This will force the locking tabs into position and firmly attach the top to the base.

#### 2.2 NEW MICE-II Specifications

Mechanical specifications for NEW MICE-II are:

| Width  | 26.0 cm | (10.24 in.) |

|--------|---------|-------------|

| Height | 12.7 cm | (5.00 in.)  |

| Length | 33.0 cm | (13.00 in.) |

| Weight | 5.0 kg  | (11.00 lb.) |

The minimum and maximum operation and storage limits for temperature and humidity are:

Operating Temperature: 0°~50°C(32°~122°F) Storage Temperature: -10°~65°C(14°~149°F) Relative Humidity: 20 ~80%

NEW MICE-II equips one built-in power supply.

Power Consumption: AC100-120V~: 1.3A MAX AC200-240V~: 0.65A MAX

47-63HZ

Voltage requirements: AC100-120V~ or

AC200-240V~ Factory-set

## 2.3 Communicating with NEW MICE-II

Whether NEW MICE-II is connected to a terminal or to a computer system, the connection between the controlling device and NEW MICE-II is across a programmable RS-232C compatible interface.

## 2.4 Control Emulation Processor Board (CEP) Setup

Other NEW MICE-II emulators can be formed simply by replacing the personality (CEP) board. If a change of personality boards is required, or modification to the factory preset conditions is necessary, the adjustment options are described in the following sections.

## 2.4.1 Interface Parameter Selection

On the CEP board locate the six position DIP switch (NSC800 - U35 and all others - U17). This switch sets the following communication modes which are only examined by the control processor during power-up and reset.

| Switch Selection | Description           |

|------------------|-----------------------|

| S1-S2-S3         | Baud Rate             |

| S4               | 7/8 Data Bits         |

| S.5              | Disable/Enable Parity |

| S6               | Odd/Even Parity       |

The number of stop bits is permanently set at two; and communication is full duplex. Each data frame consists of 1 start bit, 2 stop bits, 7/8 data bits and 1 parity bit if parity is enabled.

The transmission rate can be specified from 150-19200 baud by setting S1-S2-S3 of the DIP switch as follows:

| Baud  | Switch Section |     |     |   |  |  |

|-------|----------------|-----|-----|---|--|--|

| Rate  | S1             | S2  | S3  |   |  |  |

| 150   | ON             | OFF | OFF |   |  |  |

| 300   | OFF            | ON  | OFF |   |  |  |

| 600   | ON             | ON  | OFF |   |  |  |

| 1200  | OFF            | OFF | ON  |   |  |  |

| 2400  | ON             | OFF | ON  |   |  |  |

| 4800  | OFF            | ON  | ON  |   |  |  |

| 9600  | ON             | ON  | ON  |   |  |  |

| 19200 | OFF            | OFF | OFF | * |  |  |

\* This setting is only effective for the following (or later) firmware versions: V3.0 - ZS8, V3.1 - Z80/Z8 and V3.2 - NSC800. For all previous versions, this switch setting indicates 110 baud.

The number of data bits and parity can be specified by setting S4, S5 and S6 of the DIP switch as follows:

|                | Swite | h Sec | tion      |

|----------------|-------|-------|-----------|

| Mode           | S4    | S5    | <b>S6</b> |

| 8 Data Bits    | OFF   |       |           |

| 7 Data Bits    | ON    |       |           |

| Parity Enable  |       | OFF   |           |

| Parity Disable |       | ON    |           |

| Even Parity    |       |       | OFF       |

| Odd Parity     |       |       | ON        |

NEW MICE-II personality boards are shipped from the factory preset to 9600 baud, 8 data bits, and none parity. Switch position for this default selection is as follows:

| Mode                       | Switch Position |    |    |         |        |           |

|----------------------------|-----------------|----|----|---------|--------|-----------|

|                            | · S1            | S2 | S3 | S4      | S5     | <u>s6</u> |

| 0(00 P 1                   | on<br>L         | ON | ON | OFF<br> | ON<br> | ON<br>    |

| 9600 Baud _<br>8 Data Bits |                 |    |    |         |        |           |

| Parity Disable             |                 |    |    |         |        |           |

| Odd Parity                 |                 |    |    |         |        |           |

Default setting

When parity is disabled, the odd/even parity switch (S6) section can be set to either position since it is ignored.

#### 2.4.2 Clock Selection

#### 1. For NEW MICE-II Z80

NEW MICE-II Z80 supports the Z80 dynamic RAM refresh function and is available in the following versions:

Z80 - 2.5MHz clock oscillator Z80A - 4MHz clock oscillator Z80B - 6MHz clock oscillator Z80H - 8MHz clock oscillator

The target's clock, the on-board clock, or the on-board clock with an option to support the target can be selected by placing jumpers on the personality board as follows:

|        | x8 | Х9 | X10 | X11 |

|--------|----|----|-----|-----|

| EXT    | C  | 0  | 0   | C . |

| INT    | 0  | С  | С   | 0   |

| INT>   |    |    |     |     |

| TARGET | С  | 0  | С   | 0   |

C: Close O: Open

Internal/External Clock Selection

#### 2. For NEW MICE-II NSC800

The target's clock or the on-board 5 MHz clock can be selected by placing jumpers on the personality board as follows:

|           |    |    | TCB-NSC800DP Adapter |     |    |    |    |

|-----------|----|----|----------------------|-----|----|----|----|

|           |    |    |                      |     | ¥  | *  | ₩  |

|           | 8X | Х9 | X10                  | X11 | X1 | X2 | х3 |

| INT       | 0  | 0  | C                    | 0   | 0  | 0  | 0  |

| EXT       |    |    |                      |     |    |    |    |

| TTL CLOCK | С  | C  | 0                    | 0   | 0  | С  | 0  |

| EXT       |    |    |                      |     |    |    |    |

| CRYSTAL   | C  | C  | 0                    | 0   | С  | 0  | C  |

Internal/External Clock Selection

C: Close

0: Open

#### 3. For NEW MICE-II Z8

The target's clock or the on-board 12MHz clock can be selected by placing jumpers on the personality board as follows:

THZ8\* Adapter

|           | X8 | Х9 | X1 | X2 | Х3 |

|-----------|----|----|----|----|----|

| INT       | С  | 0  | 0  | 0  | 0  |

| EXT       |    |    |    |    |    |

| TTL CLOCK | 0  | С  | 0  | C  | 0  |

| EXT       |    |    |    |    |    |

| CRYSTAL   | 0  | C  | C  | 0  | С  |

C: Close 0: Open

#### 4. Clock Selection for NEW MICE-II ZS8

The target's clock or the on-board 20MHz clock can be selected by placing jumpers on the personality board as follows:

|           |    | THZS8* |     |        |    |    |  |

|-----------|----|--------|-----|--------|----|----|--|

|           |    |        | . 1 | Adapte | r  |    |  |

|           | x8 | х9     | X1  | X2     | Х3 | _  |  |

| INT       | С  | .0     | 0   | 0      | 0  |    |  |

| EXT       |    |        |     |        |    |    |  |

| TTL CLOCK | 0  | C      | 0   | C      | 0  |    |  |

| EXT       |    |        |     |        |    | C: |  |

| CRYSTAL   | 0  | С      | C   | 0      | С  | 0: |  |

|           |    |        |     | ~      | -  |    |  |

0pen Internal/External Clock Selection

Close

Internal/External Clock Selection

<sup>\*</sup>The THZ8 Adapter is located on the target side of the ICE cable.

<sup>\*</sup> The THZS8 Adapter is located on the target side of the ICE cable.

## 2.4.3 Ready Signal Selection (Z80 and NSC800)

#### 1. For NEW MICE-II Z80

The target ready signal, or on-board ready signal (when memory is located in SUEM/HUEM) can be selected by placing jumpers on the personality board as follows:

|          | X14 | X15 |          |

|----------|-----|-----|----------|

| TARGET   | 0   | С   | C: Close |

| ON-BOARD | С   | 0   | 0: Open  |

#### 2. For NEW MICE-II NSC800

The target ready signal can be selected by removing the jumper at X14; or if MICE emulation memory is selected, the on-board ready signal can be used by connecting a jumper at X14.

## 2.4.4 Bus State Selection (Z80)

NEW MICE-II Z80 permits the CPU to be stopped at either WAIT or BUSAK state. Stopped at WAIT state, the two refresh signals RFSH, MREQ will be lost but the CPU will stop in the middle of the machine cycle. Therefore, the messages displayed have not yet been executed. Under this condition, the DATA BUS, ADDRESS BUS and STATUS signals are still active and can be read. This simplifies hardware debug. Stopped at BUSAK state, refresh is still supported to the target; and the CPU will stop at the end of the machine cycle where the messages displayed have already been executed. Selection is shown below:

X12 X13

| WAIT  | C | 0 | C: Close |

|-------|---|---|----------|

| BUSAK | 0 | C | 0: Open  |

WAIT/BUSAK Mode Selection

## 2.4.5 Vcc Selection (NSC800)

The NSC800 Vcc on the target can be selected by removing the jumper at X12; or the on-board Vcc can be used by placing a jumper at X13.

|                    |     | X12 | X13 |           |

|--------------------|-----|-----|-----|-----------|

| Γ                  | INT | 0   | С   | C: Close  |

| Γ                  | EXT | С   | 0   | 0: Open   |

| Internal /External |     |     | Vcc | Salaction |

## 2.4.6 ISR Function (Z80)

CEP-Z80 revision M supports ISR (Interrupt Service Routine) function in emulation memory. Mini-jumper X24 is used to enable/disable ISR.

| X24 | ON  | ISR disable | (default) |

|-----|-----|-------------|-----------|

|     | OFF | ISR enable  |           |

## Application Notes

When applying ISR function, if RETI instruction is placed in MICE emulation memory, take limitations below:

- In the target, data buffer is not allowed between CPU and I/O devices.

- 2. Target memory location must not overlap with MICE emulation memory.

- 3. Before setting X24 to OFF, be sure to connect X19.

It is not able to implement ISR function by reworking previous version CEP L1 or earlier versions. ISR function only applies to firmware V2.1 and later.

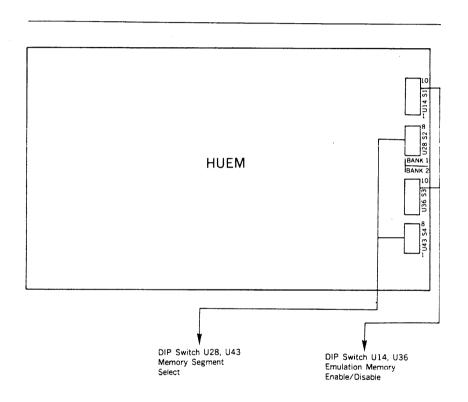

# 2.5 High Performance Universal Emulation Memory Board (HUEM) Setup

There are four DIP switches located at the front of the HUEM board (bottom board in the NEW MICE-II module); U14/U28 (enabled for both the standard 64K byte version and the optional 128K byte version) and U36/U43 (enabled only for the optional 128K byte version). The individual keys on the switches are designated S1 through S8 or S10. (Refer to the placement chart on Appendix F for the board location of these switches.)

There are two separate 64K memory banks in the HUEM. U14 and U28 set bank 1; and U36 and U43 set bank 2. Note that bank 2 is only populated for the optional 128K byte version.

The DIP switches setup are explained in the following paragraphs.

## 2.5.1 U14 and U36: Emulation Memory Enable/Disable

The user can select any memory block of 8K bytes to disable or enable depending on the amount of emulation memory needed. Set individual keys ON for enable and OFF for disable.

Position S9 and S10 are used as follows:

| Mode           | S9  | S10 |

|----------------|-----|-----|

| Write Enable   | ON  |     |

| Write Protect  | OFF |     |

| Memory Enable  |     | OFF |

| Memory Disable |     | ON  |

## 2.5.2 U28 and U43: Memory Segment Select

Memory segments may be selected within 16M bytes by setting U28 and U43 as follows:

| Segment | Start Address | S1  | S2  | S3 | <b>S</b> 4 | S5 | <b>S6</b> | S7 | S8 |

|---------|---------------|-----|-----|----|------------|----|-----------|----|----|

| OK      | ОН            | ON  | ON  | ON | ON         | ON | ON        | ON | ON |

| 64K     | 10000Н        | OFF | ON  | ON | ON         | ON | ON        | ON | ON |

| 128K    | 20000Н        | ON  | OFF | ON | ON         | ON | ON        | ON | ON |

| "       | **            |     |     |    | **         |    |           |    |    |

| 16320к  | FF0000H       |     |     | Α  | "<br>11 0  | FF |           |    |    |

Note: If bank 1 and bank 2 have the same start address (i.e. U28 and U43 have the same key setting), HUEM will select bank 1 only and disregard the U43 key setting for bank 2.

## 2.5.3 Factory Preset

HUEM is preset at the factory with the following switch positions (0-128K bytes):

In this configuration all blocks (64K byte  $\mathbf{x}$  2) of emulation memory are enabled and write enabled.

All U28 keys are in the ON position. In this configuration, the bank 1 memory segment start address is 0000H.

Only S1 is OFF. In this configuration, the bank 2 memory segment start address is 10000H.

Setting U14, U28, U36 and U43 completes setup of the HUEM board.

## 2.6 Memory Selection for Microcontrollers (Z8 and ZS8)

## 2.6.1 Memory Selection for NEW MICE-II Z8

1. The Z8 family of processors has three types of memory: internal program memory (P), external program memory (P), and external data memory (X). P and X serve as optional qualifiers for M/T commands, with program memory (P) as the default value. Note that if qualifier X is used to address internal program memory, an error message will display:

#### "LOCATION ERROR!"

| CPU                        | Ad                  | Addressable         |                  |             |

|----------------------------|---------------------|---------------------|------------------|-------------|

|                            | Internal<br>Program | External<br>Program | External<br>Data | 1/0         |

| Z8611/Z8613                | 000H-FFFH           | 1000H-FFFFH         | 1000H-FFFFH      | Ports PO-P3 |

| Z8601/Z8603/Z8671<br>Z8681 | 000H-7FFH           |                     | 800H-FFFFH       | Ports PO-P3 |

| 28682*                     | none                | 000H-FFFFH          | 000H-FFFFH       | Ports PO-P3 |

| 70007-                     | none                | 800H-FFFFH          | 800H-FFFFH       | Ports PO-P3 |

<sup>\*000</sup>H-7FFH is not addressable.

- 2. Internal program memory (4K bytes) is located in emulation memory on the CEP board (6264 RAM at U51).

- 3. If program memory is larger than 4K bytes or external data memory is used, then a SUEM/HUEM board must be used for emulation memory. To select SUEM/HUEM, set control register PO1M (F8H) with the R command, or with the user's program, to define Port 0 in address mode (PO=ADDR) and Port 1 in address/data mode (P1=A/D); i.e. set D7; D4 & D1=1 and D3=0 in register PO1M (RF8=1XX10X1X).

Example: Set RF8=96H to specify -

a) P00-P07=A8-A15

- b) P10-P17=AD0-AD7

- c) internal stack pointer

- d) normal external memory timing

- 4. However, if memory space is segregated, then input the EX command (Chapter 6), and logically select program memory and data memory using Data Memory select output. Define Port3-pin4 for Data Memory output, by setting control register P3M (F7H) with the R command, or with the user's program, to P34=DM. External segregated emulation memory is located in SUEM/HUEM, with program memory at 1000H-FFFFH and data memory at 11000H-1FFFFH.

Example: If the program memory range is 0 3FFFH and data memory range is 1000H 1FFFH, then set emulation memory as indicated below for SUEM or HUEM.

<u>SUEM</u> Set these two parameters regardless of the option selected -

- \* emulation memory block enable/disable

- \* memory offset address to OH

- a) Emulate program memory only by setting -

- \* memory segment to OH

\* starting address to OH

- b) Or emulate data memory only by setting -

- \* memory segment to 10000H

HUEM Enable all emulation memory by setting

\* U14 and U36 S1-S9 ON and S10 OFF

Emulate program memory in bank 1 by setting

\* memory segment to OH (U28 S1-8 all ON)

Emulate data memory in bank 2 by setting

\* memory segment to 10000H (U43 S1 OFF, all others ON)

5. HUEM can cover the entire emulation memory range required for external program and external data memory (max 120K bytes).

Because the offset address cannot be defined for HUEM, the first 4K bytes of both memory banks are disabled. For information on HUEM switch settings refer to section 2.5.

| Emulation Memory Selection |               |                                                                   |                |  |  |  |  |  |

|----------------------------|---------------|-------------------------------------------------------------------|----------------|--|--|--|--|--|

| Required Memory            |               | >4K bytes                                                         |                |  |  |  |  |  |

| Size                       | <4K bytes     |                                                                   |                |  |  |  |  |  |

| Emulation                  |               | Segregated                                                        | Combined       |  |  |  |  |  |

| Memory Location            |               | (set EX, & P34=DM)                                                | (set DX)       |  |  |  |  |  |

| SUEM                       | Not needed    | Use for program<br>or data memory<br>(max 120K bytes)             | Max 60K bytes  |  |  |  |  |  |

| HUEM                       | Not needed    | Use for program<br>or data memory,<br>or both<br>(max 120K bytes) | Max 60K bytes  |  |  |  |  |  |

| CEP U51(6264)*             | Used as inter | rnal program memory                                               | (Max 4K bytes) |  |  |  |  |  |

- \*If program memory (0-4K) is located in target ROM, either read the data into the host computer and then download it to MICE emulation memory, or place the target ROM (if a 2732 or 2764) on the CEP-Z8 at U51.

- a) If HUEM is selected and memory is combined, then both program and data memory must be located in the same memory bank (HUEM has two separate 64K byte memory banks) with the memory segment set to OH (U37/U43 S1-8 all ON). Because the first 4K bytes (in each memory bank) are always disabled (OK-4K internal program memory is located on the CEP-Z8), the maximum addressable memory on HUEM is 60K bytes.

However, if memory is segregated, then program memory should be located in one memory bank and data memory in the other bank. The maximum addressable memory on HUEM is then 120K bytes.

- b) When using SUEM, up to 120K bytes of external memory can be defined. The start address for 120K bytes of emulation memory can be specified anywhere within the available emulation memory (refer to SUEM section).

- c) The first 4K bytes are always internal program memory. Remember that the 2K to 4K bytes of external program memory downloaded to the CEP-Z8 for the Z8601, Z8603, Z8671 and Z8682 is addressed as internal memory.

## 2.6.2 Memory Selection for NEW MICE-II ZS8

1. The Super-8 family of processors has three types of memory: internal program memory (P), external program memory (P), and external data memory (X). P and X serve as optional qualifiers for M/T commands, with program memory (P) as the default value.

| CPU         | Add         | Addressable I/O |             |                 |

|-------------|-------------|-----------------|-------------|-----------------|

|             | Internal    | External        | External    |                 |

|             | Program     | Program         | Data        |                 |

| Z8811/Z8813 | 0000H-OFFFH | 1000H-FFFFH     | 0000H-FFFFH | Ports PO-P3     |

| Z8821/Z8823 | 0000H-1FFFH | 2000H-FFFFH     | 0000H-FFFFH | Ports PO-P3     |

| Z8831/Z8833 | 0000H-3FFFH | 4000H-FFFFH     | 0000H-FFFFH | Ports PO-P3     |

| Z8810/Z8812 | 0000H-OFFFH | 1000H-FFFFH     | 0000H-FFFFH | Ports PO-P4     |

| Z8820/Z8822 | 0000H-1FFFH | 2000H-FFFFH     | 0000H-FFFFH | Ports PO-P4     |

| Z8830/Z8832 | 0000H-3FFFH | 4000H-FFFFH     | 0000H-FFFFH | Ports PO-P4     |

| 7.8801      | none        | 0000H-FFFFH     | 0000H-FFFFH | Ports P2-P3(P0) |

| 7.8800      | none        | 0000H-FFFFH     | 0000H-FFFFH | Ports P2-P4(P0) |

The Z8800 and Z8801 microprocessors can use port P0 for addressable I/0 or external memory, where the address range is selectable at 0000H-0FFFH or 0000H-FFFFH depending on address pin definition.

2. Internal program memory (0/4/8/16 Kbytes) is located in emulation memory on the CEP board (two 6264 RAMs at U52 and U53). The size of the internal memory to be emulated is selected by placing jumpers on the personality board as follows.

| Internal Memory | Jumper Setting |     |     |     |  |  |

|-----------------|----------------|-----|-----|-----|--|--|

| Size            | X10            | X11 | X12 | X13 |  |  |

| none (ROMless)  | С              | 0   | С   | 0   |  |  |

| 4K              | 0              | C   | 0   | С   |  |  |

| 8K              | С              | 0   | 0   | С   |  |  |

| 16K             | 0              | С   | С   | 0   |  |  |

C: Close

O: Open

Size of Internal Program Memory

3. If the user's program is larger than internal program memory or external data memory is used, then a SUEM/HUEM board must be used for emulation memory. To select SUEM/HUEM, set mode register POM (FOH, BANKO) and PM (F1H, BANKO) with the R command, or with the user's program, to define Port O in address mode (PO=ADDR) and Port 1 in address/data mode (P1=A/D); i.e. set D7-D0=1 in register POM (RSOFO=FF), and D5=1 in register PM (RSOF1=20).

Example: Set RSOFO=FF and RSOF1=20 to specify -

- a) P00-P07=A8-A15

- b) P10-P17=AD0-AD7

- 4. However, if memory space is segregated, then input the EX command (Chapter 6), and logically select program memory and data memory using Data Memory select output. Define Port3-pin5 for Data Memory output, by setting mode register PM (F1H, BANKO) with the R command, or with the user's program, to P35=DM. External segregated emulation memory is located in SUEM/HUEM, with program memory at OOOOH-FFFFH and data memory at 11000H-1FFFFH.

Example: If the external program memory range is 4000H-BFFFH and data memory range is 1000H-8FFFH, then set emulation memory as indicated below for SUEM or HUEM.

- SUEM a) Emulate program memory only by setting -

- \* memory segment to OH

- \* starting address to 4000H

- b) Or emulate data memory only by setting -

- \* memory segment to 10000H

- \* starting address to 1000H

HUEM

Enable all emulation memory by setting \* U14 and U36 S1-S9 ON and S10 OFF

Emulate program memory in bank 1 by setting \* memory segment to OH (U28S1-8 all ON)

Emulate data memory in bank 2 by setting \* memory segment to 10000H (U43 S1 OFF, all others ON)

5. SUEM/HUEM can cover the entire emulation memory range required for external program and external data memory (max 128K bytes).

Because internal program memory is located on the CEP board at U52/U53, do not set the address for SUEM within the internal memory range. However, the offset address cannot be defined for HUEM. Therefore, the first 0/4/8/16 Kbytes of the memory bank containing program memory are disabled when emulation memory is segregated, and the first 0/4/8/16 Kbytes of both memory banks are disabled when emulation memory is combined. For information on HUEM switch settings refer to section 2.5.

Emulation Memory Selection Required Memory >0/4/8/16 Kbytes\* 0.<4/8/16 Kbytes\* (Microcomputer) Size Emulation (Microcontroller) Segregated Combined (set EX, & P35=DM) (set DX) Max 64K bytes Memory Location Use for program SUEM Not required or data memory (max 128K bytes) Use for program HUFM Not required Max 64K bytes or data memory, or both (max 128K bytes) CEP U52/53(6264x2)\*\* Used as internal program memory (Max 16K bytes)

- \* Depends on the target processor under emulation.

- \*\* If internal program memory is located in target ROM, either read the data into the host computer and then download it to MICE emulation memory, or place the target ROM (if a 2764) on the CEP-ZS8 at U52 or U53.

- a) If HUEM is selected and memory is combined, then both program and data memory must be located in the same memory bank (HUEM has two separate 64K byte memory banks) with the memory segment set to OH (U37/U43 S1-8 all ON). Because the internal memory range is always disabled (0/4/8/16 Kbytes internal program memory is located on the CEP-ZS8), the maximum addressable memory on HUEM is 64 Kbytes.

However, if memory is segregated, then program memory should be located in one memory bank and data memory in the other bank. The maximum addressable memory on HUEM is then 128K bytes.

b) When using SUEM, up to 128K bytes of external memory can be defined. The start address can be specified anywhere within the available emulation memory (SUEM section).

#### 2.7 RS-232C Cable Connection

After selecting the proper data rate and transmission characteristics, next determine whether the controlling device has a data terminal equipment (DTE) interface or a data communication equipment (DCE) interface, with or without handshaking. Display terminals are usually equipped with DTE interface; computer systems usually have both.

There are several methods for determining the type of interface on the controlling device. The first method is by simple trial and error. If this fails, procedures two and three listed below can be used to determine the interface type. (It must be known beforehand whether or not handshaking is selected as a software option for the controlling device, as it cannot be easily detected by examining hardware signals.) Subsequent instructions detail how to accomplish interface header rewiring if required.

- Try connecting the two devices together. If the response is correct, the interfaces match and no further adjustment is required. If the interconnect does not work, a mismatch exists and indicates that a connection change is necessary.

- 2. Data are transmitted on pin 2 and received on pin 3 of the D-connector for DTE devices; the reverse is true for DCE devices.

- 3. When not transmitting, the voltage (with respect to pin 7 [ground] of the D-connector) is -12 VDC on pin 2 for DTE devices and -12 VDC on pin 3 for DCE devices.

The header designated as U13 on the CEP board is used to configure the interface between NEW MICE-II and the controlling device. NEW MICE-II are shipped from the factory with a straight-wired header for DTE with hand-shaking.

Pins 1-7 on the interface header are connected to the female D-connector (J2) while pins 8-14 are connected to the NEW MICE-II, RS-232C interface logic. Pin definitions on the header are shown below:

| RS-232C Signals         | D-connector | Header | MICE Logic Side                       |

|-------------------------|-------------|--------|---------------------------------------|

|                         | (female)    |        | •                                     |

| CF-Data Carrier Detecto | r pin 8     | 1 14   | +12 <u>VDC</u>                        |

| CD-Data Terminal Ready  | pin 20      | 2 13   | → <b>&gt;</b> o*- <u>DSR</u> of 8251A |

| CC-Data Set Ready       | pin 6       | 3 12   | <u>→</u>                              |

| CB-Clear To Send        | pin 5       | 4 11   | o <b>√</b> <u>RTS</u> of 8251A        |

| CA-Request To Send      | pin 4       | 5 10   | —— ⊳oCTS of 8251A                     |

| BB-Received Data        | pin 3       | 6 9—   | o <b>&lt;</b> TxD of 8251A            |

| BA-Transmitted Data     | pin 2       | 7 8    | —— <b>○</b> oRxD of 8251A             |

<sup>\*</sup>RS-232C interface gate for 1488 or 1489 depending on signal Input or Output.

The wiring configuration for all three header types is shown below. Note that if the controlling device has a DCE interface, incoming signals are now outgoing, and vice versa, on the same pins. By removing the cover to the header, the interface type used by MICE can be determined according the following wiring configuration.

DTE with DCE with DTE without DCE without handshaking handshaking handshaking handshaking handshaking

|     | ٦     |      | _  | 1  | _   | ٦    | T |     |     |             |                       |

|-----|-------|------|----|----|-----|------|---|-----|-----|-------------|-----------------------|

| 1 - | - 1   | 14 1 | -  | 14 | 1   | - 14 | 1 | -1  | 14  | (from MICE) | Data Carrier Detector |

| 2 - | - 1   | 13 2 | V  | 13 | 2   | 13   | 2 | . ] | 13  | (to MICE)   | Data Terminal Ready   |

| 3 - | - 1   | 12 3 | ٨  | 12 | 3 ' | 12   | 3 | L   | 1.2 | (from MICE) | Data Set Ready        |

| 4 - | -   1 | 11 4 | V  | 11 | 4   | . 11 | 4 | ١,  | 11  | (from MICE) | Clear to Send         |

| 5 - | -   1 | 10 5 | Λ  | 10 | 5 ' | 10   | 5 | l   | 10  | (to MICE)   | Request to Send       |

| 6 - | -   9 | 6    | VΙ | 9  | 6 - | . 9  | 6 | V   | 9   | (from MICE) | Received Data         |

| 7 - | ع ا   | 3 7  | Λ  | 8  | 7 - | - 8  | 7 | М   | 8   | (to MICE)   | Transmitted Data      |

| L_  | _!    | Į    |    |    |     | _    | L |     |     |             |                       |

When wired for DTE, connect NEW MICE-II using a straight-wire cable with male D-connectors; for other header types, the cable must be rewired accordingly. If a display terminal is connected after making the proper connections, NEW MICE-II should respond when power is applied. (A display terminal should always be used to check new NEW MICE-II units to ensure that they are properly functioning.)

Finally, NEW MICE-II requires that both Request to Send and Data Terminal Ready inputs, pins 10 and 13 respectively on the logic side of the header, be at +12 VDC before it transmits any data. If the controlling device does not supply the necessary voltage, it can be obtained by reconnecting pins 10 and 13 directly to pin 14 (Received Line Signal Detector) of header U13 which is always at +12 VDC.

To accommodate computer systems which are sending commands and data too fast for NEW MICE-II, the Data Set Ready output, normally at +12 VDC, is pulled low by NEW MICE-II to -12 VDC. The signal is restored to +12 VDC when NEW MICE-II is again ready. Also, to accommodate display terminals with slow carriage-returns or line-feeds, six null characters are always transmitted after a carriage-return is issued.

#### 2.8 Applying Power to NEW MICE-II

Connect the RS-232C cable from the controlling device to the female D-connector at the rear of NEW MICE-II. (The recommended power-on sequence is to first apply power to the target and then to NEW MICE-II; and to use the opposite sequence when powering off.) With the controlling device ready, connect the power cable with the locking tab pointing up, and apply power. Within a few seconds, the following start-up message should display:

```

***MICE-II-type V#.#**

>

```

type identifies target processor being emulated by the personality card.

- #. # indicates version number of controlling program on personality card.

- is the prompt character indicating that NEW MICE-II is ready for a command.

In response to the command prompt character ">" enter a question mark "?", immediately followed by a carriage

return. If the data bits and parity are correctly matched, the NEW MICE-II command summary is listed; otherwise, the error message "WHAT?" is printed. Reset the switch section where necessary and remember to wait a few seconds before power is turned on again.

Notes 1. If target VCC is not provided when NEW MICE-II is powered up, the following message will display:

Z80 - NO TARGET VCC; NMI, INTR, RESET, BUSRQ DISABLED!

NSC800 - NO TARGET VCC; NMI, INTR, BREQ DISABLED!

Z8 - NO TARGET VCC; IRQ, RESET DISABLED, MEMORY COMBINED!

ZS8 - NO TARGET VCC; RESET DISABLED, MEMORY COMBINED!

2. The CPU is automatically reset after power-up, software reset command "r" (section 2.9) or MICE Reset command X (section 5.7). If the target system has any peripheral devices or slave processors which must be synchronized with a CPU reset, then the reset must be performed on the target side. A target reset signal will also reset the emulation CPU. However, the reset control signal for MICE must be enabled (section 6.2) for the Z80/Z8/ZS8, otherwise the target reset signal cannot reset the emulation CPU.

Note that a synchronized reset may be performed by either MICE or the target system for the NSC800, since this processor supports a RESET output signal when the reset line for peripheral devices or slave processors on the target side is connected to reset pin-37.

#### 2.8.1 No Response

If there is no response from NEW MICE-II, check the following items:

- 1. Check the RS-232C cable connection at both ends.

- 2. Check the power supply connections and voltages.

- 3. Check that the header has the proper interface.

- 4. Check that both Request to Send and Data Terminal Ready, pins 10 and 13 on the header are at +12 VDC.

- 5. Check that the controlling device has the proper voltage level requirements on its RS-232C inputs for transmission and reception.

- 6. Check that the baud rates of the controlling device and NEW MICE-II are the same, resetting if necessary. If a message does appear but is garbled, any combination of the baud rate, data length or parity could be incorrectly set.

- 7. Check the RS-232C cable for incorrectly wired or loose pins.

- 8. If a computer system is the controlling device, check that the driver program is running and the RS-232C cable is connected to the correct port and that the port is working.

Note: When changing the communication configuration switch, note that it is only read during a power-up or reset. After turning the power off, wait a few seconds before the power is turned on again to allow the capacitors to fully discharge.

If the problem still cannot be found, contact your local Microtek representative for further assistance.

#### 2.8.2 Failure Device

During the delay prior to the start-up message the RAMs and EPROMs on the CEP board are tested. If any component failures exist, they are listed as detected in the following format: "U## - FAILURE", where ## is the component number on the personality board.

## 2.9 Control Processor Software Reset Command

The character "r" is the command to reset NEW MICE-II. Remember that except for this command all alphabetic characters must be entered in upper-case; no other lower-case characters are recognized.

#### CHAPTER 3

#### NEW MICE-II COMMAND LANGUAGE

All NEW MICE-II products have a common set of commands identified by a single or double character regardless of the processor being emulated. No additional time or effort is required to learn a new command language when the target processor changes.

These commands are described in the following chapters along with a variety of available options, though not all options are applicable for the different types of processors. For the specific processor being emulated, consult the Help "?" command. The commands described in the following chapters are grouped as follows:

#### NEW MICE-II Utility Commands

- ? Help Command

- ! Attention Command

#### Memory, Port and Register Commands

- M Memory Display/Examine/Modify/Fill/Search Command

- T Memory Checksum/Test/Transfer/Compare Command

- A Line Assembly Command

- Z Disassembly Command

- I Port Input Command

- O Port Output Command

- R Register Display/Modify Command

- J Jump/Branch Command

- X Reset/Initialization Command

#### Control Signal Commands

- D Disable/Display Control Signal Command

- E Enable/Display Control Signal Command

#### Emulation and Trace Control Commands

- G Go/Execution Command

- H Halt/Breakpoint Set Command

- F Forward Trace Command

- B Backward Trace Command

- L List Trace Buffer Command

#### Stepped Emulation Commands

- C Single Cycle, Step Command

- S Instruction Step Command

## Utility Commands Involving a System

- : Download Command (Intel Format)

- / Download Command (Tektronix Format)

- U Upload Command

#### 3.1 Command Syntax

NEW MICE-II indicates that it is ready to accept a command line by printing a greater-than character ">" on a new line. A command may then be entered and must be terminated by a carriage-return (CR). The general syntax of NEW MICE-II commands is:

## command [parameters] (CR)

where: command is the command representation.

> parameters are one or more variable data supplied with the command. Parameters are alphanumeric; when a numeric parameter is called for, it must be

entered in hexadecimal.

Where a space is shown in the syntax, either a space or comma can be used. A <CR> must be used to terminate a command input line. In most cases line feed (LF) or <CR>> have the same effect, except where otherwise noted. Note that brackets [ ] and braces { } are used for describing command syntax only, and are not used in command input.

#### 3.2 Notations and Conventions

A set of conventions is used to describe the structure of commands. The notations and rules are as follows:

- 1. An upper-case entry must be input.

- 2. A lower-case entry in the description of a command is the class-name for a parameter. A particular value for this class must be entered. A classname never appears in an actual operable command. For example, the lower-case entry - "start-address" means that NEW MICE-II will only accept a hexadecimal value as an address in the target processor's memory space.

- 3. A required entry is shown without any enclosures; whereas an optional entry is denoted by enclosing it in brackets. For example, in the command description "G[address]", the command "G" is required, and the brackets around the entry "address" means that it is optional in this command.

Where brackets are within another set of brackets, the entry enclosed by the inner brackets may only be entered if the items outside those inner brackets are first entered. For example, in the command description - "I port[ count[ time]]", th is required; and the brackets mean tha tion of "count" and "time" is optional mand. However, a "count" must first be en "time" value is to be specified.

- 4. Where an entry must be selected from a choice of two or more, the choices for the required entry are enclosed in braces and separated by vertical bars. For example "{S|M|a3[V]}" indicates that either "S", "M" or "a3" must be entered.

- 5. Where a choice exists for an optional entry, the choices are enclosed in brackets and separated by vertical bars. For example, "[I|H|T]" indicates that either "I", "H" or "T" may be entered.

- 6. "Addx" is a hex address with a wildcard byte pair of "XX" or "XXXX", or a wildcard nibble of "X" [only for the third digit (e.g. X23) for 8048]; where X indicates that the digits are "don't care". For example "12XX" means all addresses between 1200H and 12FFH.

- 7. Commands A/C/S/I/R all use carriage-return  $\langle CR \rangle$  or line-feed  $\langle LF \rangle$  to display the next line.

- 8. In the Memory Modify (M) command, use a <CR> to advance to the next location and a <LF> to return to the previous location.

- 9. Entries underlined in command examples indicate user input.

#### 3.3 Editing Characters

Each character entered on the keyboard is stored in a line editing buffer until  $\langle \text{CR} \rangle$  is entered. If more than 80 characters are entered without inputting a  $\langle \text{CR} \rangle$ , an error message is printed, and the command is ignored.

The line editing buffer can be edited or entirely deleted by using special non-printable editing characters. Control characters are entered by holding down the control key (CTRL) while the character is typed. Control character input is expressed with the control command enclosed in () brackets.

BACKSPACE deletes the preceding character from the line buffer and from the display. Repeated usage is allowed. <CTRL-H> performs the same function. When a hardcopy terminal is used instead of a display screen, RUBOUT should be used.

RUBOUT deletes the preceding character from the line buffer and echoes the deleted character on the display, preceded by a backslash character. Repeated usage is allowed. On some terminals, this key may be labeled as DELETE or DEL.

ignores the current contents of the line buffer and prompts ">" for a new command on the next line. This key is also used to terminate commands in process and to return to the prompt state. ESCAPE is also expressed as <ESC>. On some terminals, this key may be labeled ESC. <CTRL-Y> performs the

same function.

- <CTRL-R> causes a <CR> or <LF>, followed by a redisplaying of the current undeleted contents

in the line buffer. This is useful to see a

clean copy of the command line after RUBOUT

has been used.

- ignores the current contents of the line

buffer and shifts the cursor to the first

position of the next line, awaiting input of

new data.

#### 3.4 Control Characters and Delimiters

The following control characters have special meaning for all NEW MICE-II firmware:

⟨CTRL-J⟩: is the same as ⟨LF⟩.

⟨CTRL-M⟩: is the same as ⟨CR⟩.

<CTRL-S>: stops data transmission from NEW MICE-II.<CTRL-Q>: continues data transmission from NEW MICE-II.

⟨CTRL-Y⟩: is the same as ⟨ESC⟩.

# 3.5 Reference Program for Examples

The following sample program for a Z80 target is used as the basis for most of the examples listed in this user's manual. It includes commonly used instructions for performing various bus cycles.

| LOC<br>0000<br>0003<br>0006 | OBJ<br>310020<br>CD0001<br>DD210030 | LINE<br>0001<br>0002<br>0003 | LABEL<br>B0000 | SOURCE<br>LD'<br>CALL<br>LD | E CODE<br>SP,2000<br>0100<br>IX,3000 |

|-----------------------------|-------------------------------------|------------------------------|----------------|-----------------------------|--------------------------------------|

| 000A                        | 110010                              | 0004                         |                | LD                          | DE,1000                              |

| OOOD                        | 1A                                  | 0005                         | BOOOD          | LD                          | A, (DE)                              |

| 000E                        | DD7700                              | 0006                         |                | LD                          | (IX+00),A                            |

| 0011                        | DD23                                | 0007                         |                | INC                         | ΪΧ                                   |

| 0013                        | 13                                  | 8000                         |                | INC                         | DE                                   |

| 0014                        | 7B                                  | 0009                         |                | LD                          | A,E                                  |

| 0015                        | FEOF                                | 0010                         |                | CP                          | OF                                   |

| 0017                        | C20D00                              | 0011                         |                | JP                          | NZ,000D                              |

| 001A                        | C30000                              | 0012                         |                | JP                          | 0000                                 |

| 0100                        | 110010                              | 0001                         |                | LD                          | DE,1000                              |

| 0103                        | 3E20                                | 0002                         | B0103          | LD                          | A,20                                 |

| 0105                        | 12                                  | 0003                         |                | LD                          | (DE),A                               |

| 0106                        | 7B                                  | 0004                         |                | LD                          | A,E                                  |

| 0107                        | 13                                  | 0005                         |                | INC                         | DE                                   |

| 0108                        | FĘOF                                | 0006                         |                | CP                          | OF                                   |