# MAINTENANCE MANUAL

NPC 764

LOGIC ANALYSIS SYSTEM

201 Fourier Avenue Fremont, California 94539 Telephone: (415) 490-8300 TWX: 910-381-7030

### SAFETY PRECAUTIONS

The notations shown in the box below are used in this manual to draw the attention of the user to particular items within the text. Personnel hazards (WARNING) exist as noted in the specific operations described in this manual. Equipment damage potential (CAUTION) exists in the following cases: Mechanical damage as noted in specific operations described in this manual. Electrical damage when power cord is connected and/or power is applied as noted in specific procedures within this manual.

# WARNING

A WARNING NOTATION IS USED TO DESCRIBE AN OPERATING OR MAINTENANCE PROCE-DURE, PRACTICE, CONDITION OR STATEMENT, WHICH, IF NOT STRICTLY OBSERVED, COULD RESULT IN INJURY TO, OR DEATH OF PERSONNEL.

A CAUTION NOTATION IS USED TO DESCRIBE AN OPERATING OR MAINTENANCE PROCEDURE, PRACTICE, CONDITION OR STATEMENT, WHICH, IF NOT STRICTLY OBSERVED, COULD RESULT IN DAMAGE TO, OR DESTRUCTION OF EQUIPMENT OR LOSS OF EQUIPMENT EFFECTIVENESS.

### NOTE

A NOTE IS USED TO DESCRIBE AN ESSENTIAL OPERATING OR MAINTENANCE PROCEDURE, CONDITION OR STATEMENT WHICH MUST BE HIGHLIGHTED.

### TABLE OF CONTENTS

| Sect                         | ion                                               | Page                                      | Section                                                |                                               |  |  |

|------------------------------|---------------------------------------------------|-------------------------------------------|--------------------------------------------------------|-----------------------------------------------|--|--|

| 1.                           | INTRODUCTION                                      |                                           | V. CRT DISPLAY MODULE                                  |                                               |  |  |

| 1.1<br>1.2<br>1.3<br>1.4     | Manual Contents                                   | • 1-2<br>• 1-2                            | 5.1 Introduction                                       | 5-1                                           |  |  |

| 11.                          | SELF TESTS                                        |                                           | 6.1 Introduction                                       |                                               |  |  |

| 2.2<br>2.2.<br>2.2.          | Introduction                                      | • 2-1<br>• 2-1<br>• 2-2                   | 6.2 Functional Description                             | 6-1<br>6-1<br>6-2                             |  |  |

| 2.3.                         | Analyzer Test Card                                |                                           | •                                                      |                                               |  |  |

| 2.3.                         | 2 Test Card Description                           | . 2-3                                     | VII. STATE CONTROL BOARD                               |                                               |  |  |

| 2.3.<br>2.3.<br>2.3.<br>2.3. | 4 Basic State Tests                               | • 2-4<br>• 2-6<br>• 2-6<br>• 2-8<br>• 2-8 | 7.1 Introduction                                       | 7-1<br>7-1<br>7-2<br>7-3<br>7-3               |  |  |

| 111.                         | CHASSIS, MOTHERBOARD,<br>POWER SUPPLY, DISK DRIVE |                                           | 7.2.5 Post-Trigger Counter 7.2.6 Restart Generator     | 7-5                                           |  |  |

| 3.1<br>3.2                   | Introduction                                      |                                           | and Parts List                                         | 7-7                                           |  |  |

| 3.3                          | Motherboard Functional Description                | . 3-4                                     | VIII. STATE MEMORY BOARD                               |                                               |  |  |

|                              | •                                                 | . 3-6<br>. 3-8<br>. 3-9<br>.3-10<br>.3-11 | 8.1 Introduction                                       | 8-1<br>8-1<br>8-3<br>8-3<br>8-4<br>8-4<br>8-5 |  |  |

| 17.                          | KEYBOARD AND FRONT PANEL                          |                                           | 8.3 Board A, Board B and Board C. 8.3.1 Qualifier Bits | 8-7                                           |  |  |

| 4.1                          | Keyboard Functional Description                   | . 4-1                                     | 8.3.2 Signal CLKQUALIN                                 | 8-7                                           |  |  |

| 4.2                          | Removal and Disassembly                           |                                           | 8.3.4 Signal BSELECT                                   |                                               |  |  |

### TABLE OF CONTENTS (Contid)

| Sect                                        | ion Pag                                                                                | e Section Pa                                    | age                      |

|---------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------|

| 8.4                                         | Schematic, Board Layout Parts List 8-                                                  | 11.5 Signature Analyzer Functional  Bescription |                          |

| IX.                                         | TIMING CONTROL BOARD                                                                   | ally rails List                                 | ر ج ا                    |

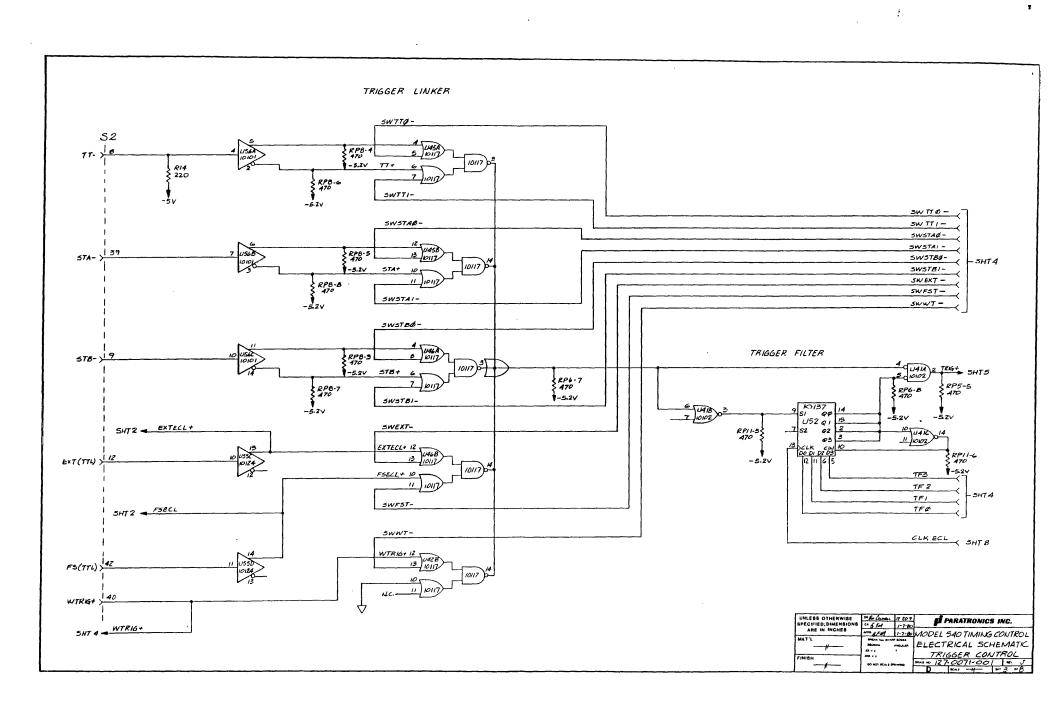

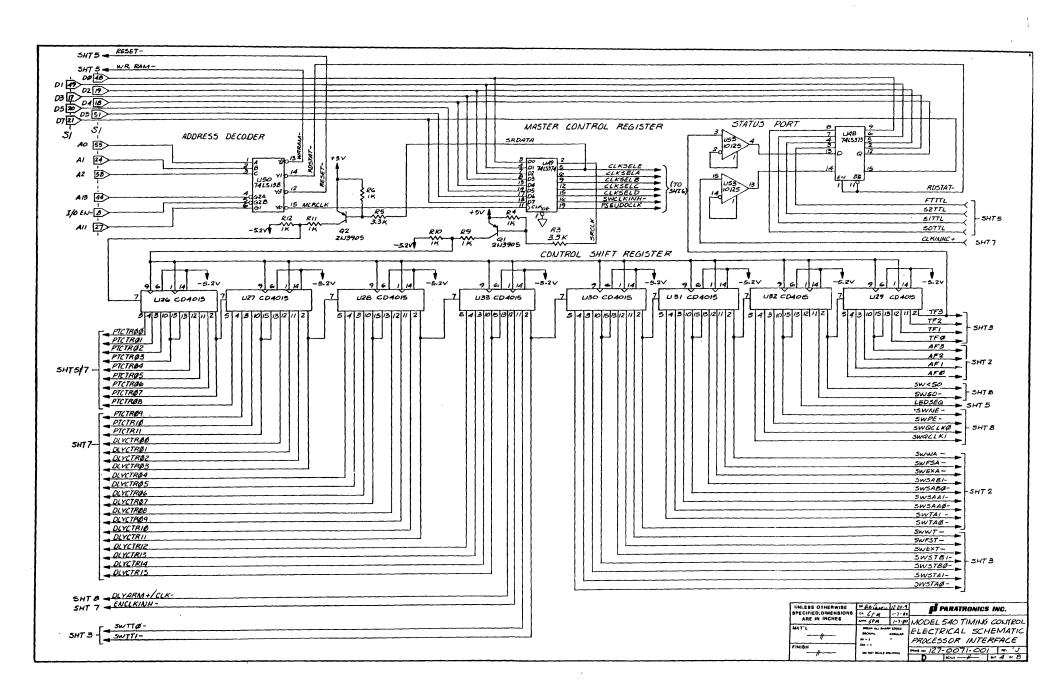

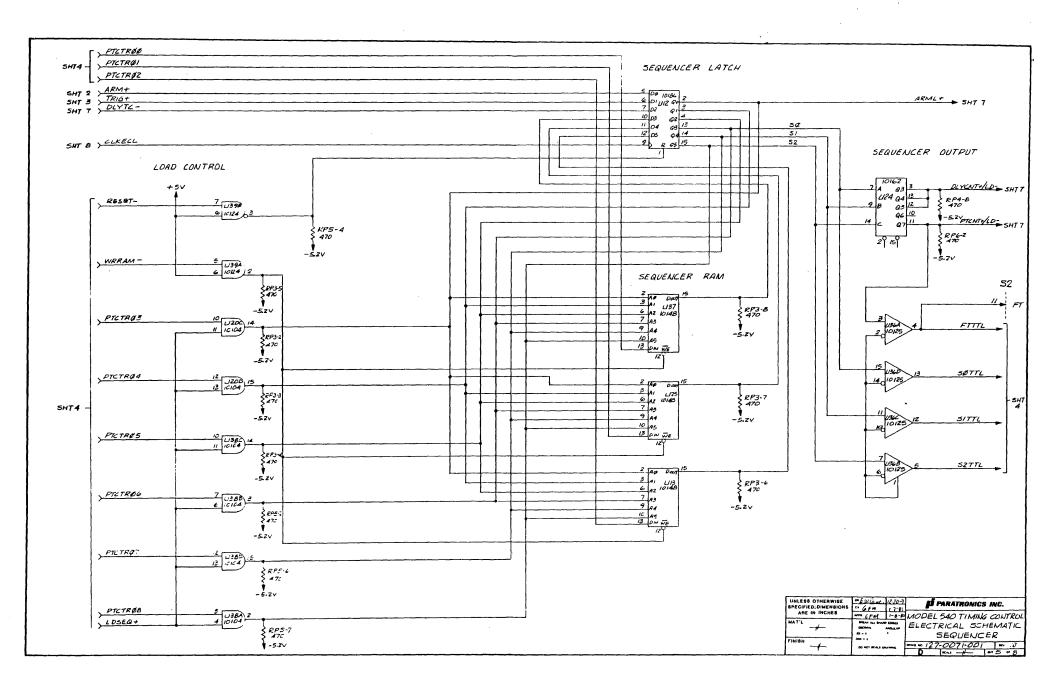

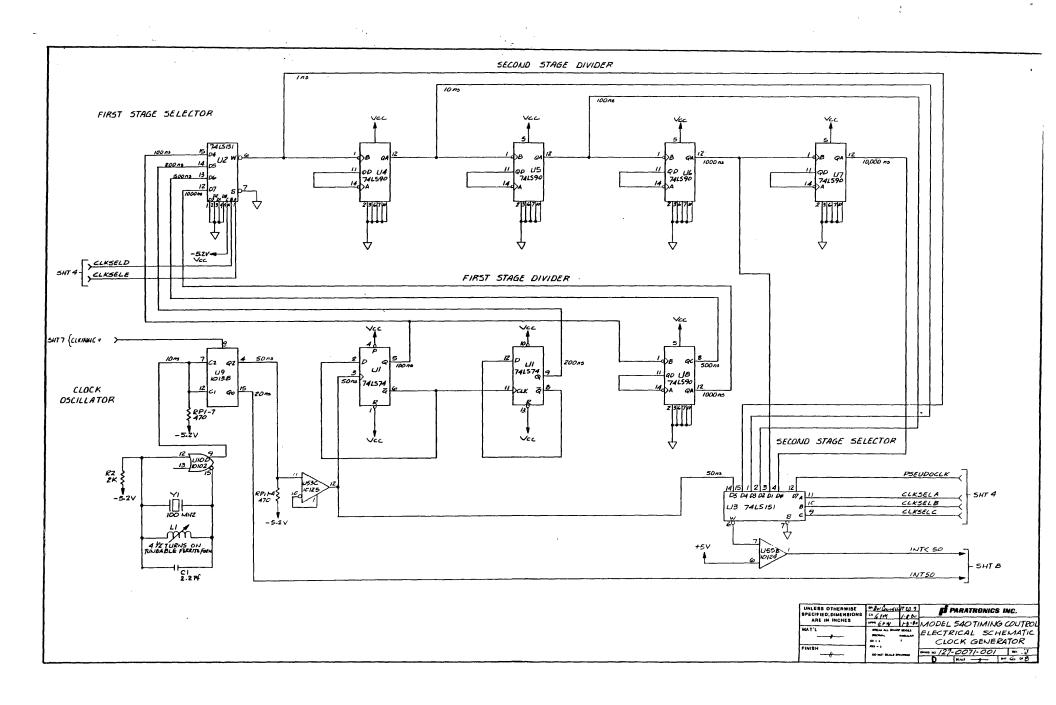

| 9.2<br>9.2.<br>9.2.<br>9.2.<br>9.2.<br>9.2. | 2 Clock Generator 9-<br>3 Clock Control 9-<br>4 Trigger Control 9-<br>5 Arm Control 9- | 1 12.1 Introduction                             | 2-1<br>2-2<br>3-1<br>3-1 |

|                                             |                                                                                        | 13.4 Schematics, Board Layouts and Parts List   |                          |

| 10.1                                        | Introduction                                                                           | 1 14.1 Introduction                             |                          |

| 10.2<br>10.2<br>10.2                        | .1 Processor Interface                                                                 | 14.3 Model 80 Probe                             | 4-2<br>4-2<br>4-2<br>4-3 |

| XI.                                         | COUNTER-TIMER/SIGNATURE ANALYZER                                                       | XV. MOTHERBOARD CONNECTIONS                     |                          |

| 11.2<br>11.3                                | Introduction                                                                           | •1                                              | 5-1                      |

| 11.4                                        | Counter-Timer Functional  - Description                                                | 2 16.0 Introduction                             | 16-1                     |

### LIST OF TABLES

| Table | e Page                                               | Table | Page |

|-------|------------------------------------------------------|-------|------|

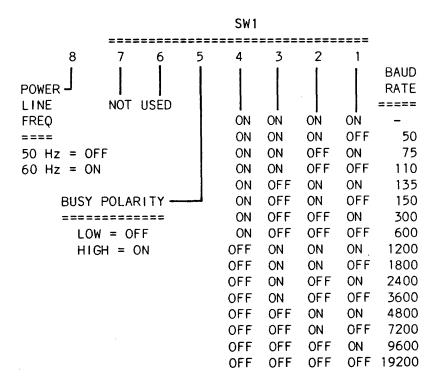

|       | IEEE-488 Signal Flow 6-3 DIP Switch 1 Selections 6-3 |       | 13-3 |

|       | Power Source Requirements 3-4                        |       | 13-3 |

### LIST OF ILLUSTRATIONS

| Figur      | re Page                       | Figure                                 | Page                   |

|------------|-------------------------------|----------------------------------------|------------------------|

| 1-1        | NPC-764 Simplified Block      | 3-2 Rear Panel and Voltage Select Card | 7 7                    |

| 2-1        | Diagram                       | 3-3 Circuit Board Locations .          |                        |

| 2-1<br>2-2 | Connector Jumper 2-1          |                                        |                        |

|            | Screen                        | 11, 7                                  |                        |

| 2-3        | Screen                        |                                        |                        |

| 2-4        | Screen                        | 4-2 Keyboard with Bezel Removed        |                        |

| 2-5        | Screen                        | 5-1 CRT Module Cover Removal .         |                        |

| 2-6        | Screen 2-3                    | 5-2 CRT Adjustments                    |                        |

| 2-7        | Logic Analyzer Test Card 2-3  | 6-1 Dip Switch Location                | 6-4                    |

| 2-8        | Configuration Menu 2-5        | 7-1 State Control Board Block          |                        |

| 2-9        | Channel State Screen 2-5      | Diagram                                | 7-0                    |

|            | Hexademical Format Screen 2-6 | 8-1 State Memory Board Block           |                        |

|            | Difference Menu Screen 2-7    | Diagram                                |                        |

|            | Binary Differnce Screen 2-7   | 9-1 Timing Control Board Block         |                        |

|            | First Difference Word 2-9     | Diagram                                | 9-1                    |

|            | Search Word 2-9               | 10-1 Timing Memory Board Block         |                        |

| 2-15       | Difference Menu Screen2-10    | Diagram                                | 10-1                   |

| 2-16       | Channel Timing Menu 2-10      | 10-2 Clock Generator Timing            |                        |

| 2-17       | Timing Diagram Display2-11    | Diagram                                | 10-6                   |

| 2-18       | Timing Display at             | 10-3 Data Comparator Expanded          | ٠٠٠ . الله الله        |

|            | Location 500                  | Schematic                              | . 10-10                |

| 2-19       | Timing Dislay and Menu 2-13   | 10-4 Data Comparator Timing            | 9 <b>1</b> 11150       |

|            | Clock Timing Samples 2-15     | Diagram                                | • 10 <sup>2</sup> 10 ′ |

|            | Correlation Display 2-15      | 11-1 CTSA Block Diagram                | 11-1                   |

|            | Correlation Display 2-16      | 11-2 Signature Analyzer                |                        |

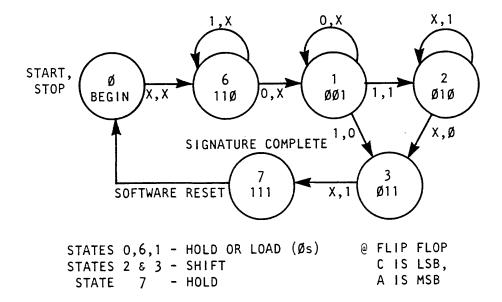

|            | State Menu                    | Sequencer State Diagram                | 11-3                   |

| 3-1        | NPC 764 Logic Analysis        | 13-1 Potentiometer and Dip             |                        |

|            | System                        | Switch Location                        | 13-2                   |

# **INTRODUCTION**

# SECTION 1: INTRODUCTION

|     |                           | PAGE |

|-----|---------------------------|------|

| 1.1 | Manual Contents           | 1-1  |

| 1.2 | NPC-764 Operation         | 1-2  |

| 1.3 | Block Diagram Description | 1-2  |

| 1.4 | Detailed Operation        | 1-3  |

# SECTION I

### 1.1 MANUAL CONTENTS

This manual contains technical information useful for the maintenance and repair of the Nicolet Paratronics Corporation NPC 764 Logic Analyzer. Each section of this manual contains the pertinent schematics, technical description and parts list. The manual is arranged as follows:

Section I - Introduction

Includes a general description of the NPC 764 including principles of operation, block diagram description, and performance characteristics. A brief description of the performance checks is also given.

Section II - Self Tests

Description of automatic and keyboard selftests. In addition, a step-by-step illustration of self-tests performed with the Logic Analyzer Test Card is provided.

Section III - Chassis

Mainframe, power supply, PCB arrangement and motherboard layout.

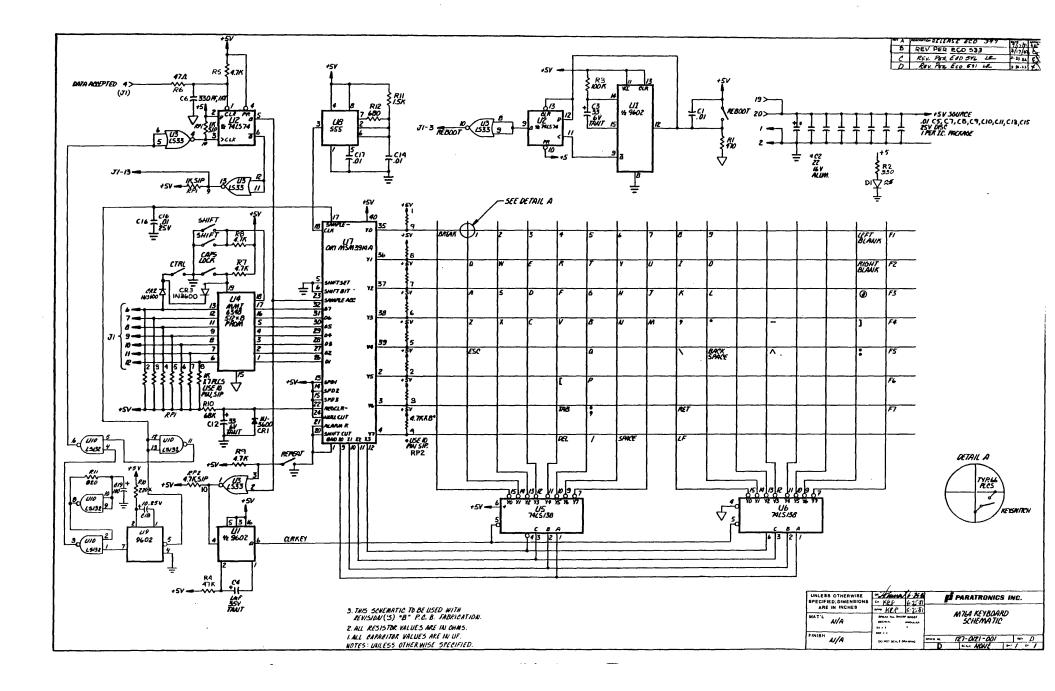

Section IV - Keyboard

Description of keyboard, operation and circuitry.

Section V - Display Module

Maintenance details of the Display module contained in the NPC 764.

Section VI - Processor/Video

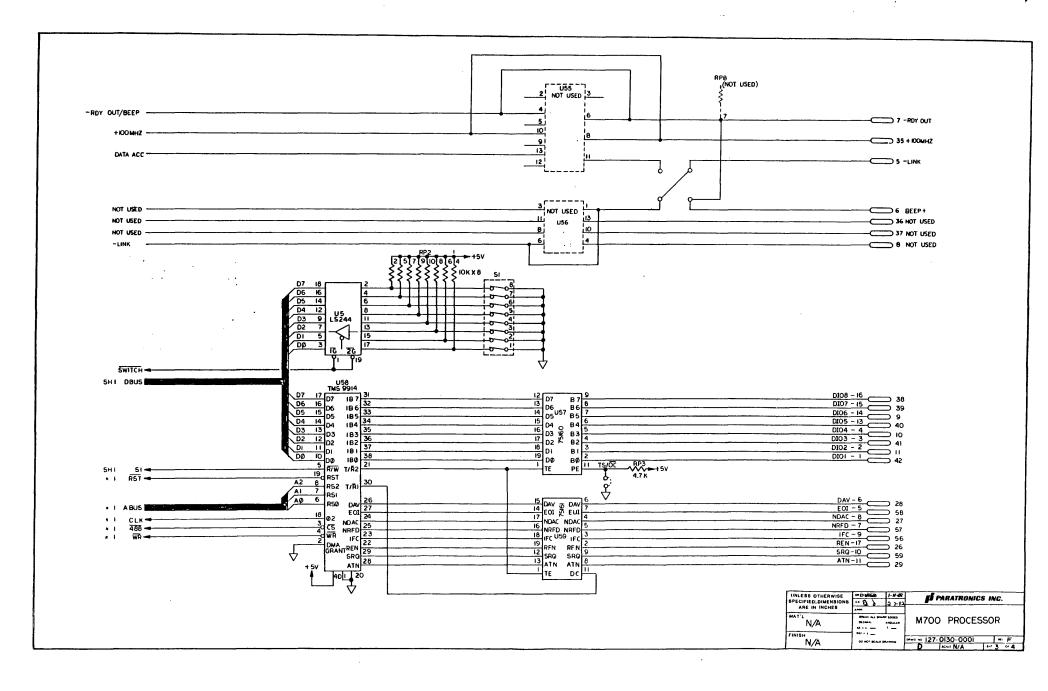

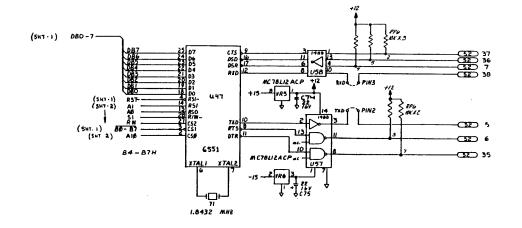

Microprocessor, memory, video display circuitry, and IEEE-488 interface details including a block diagram.

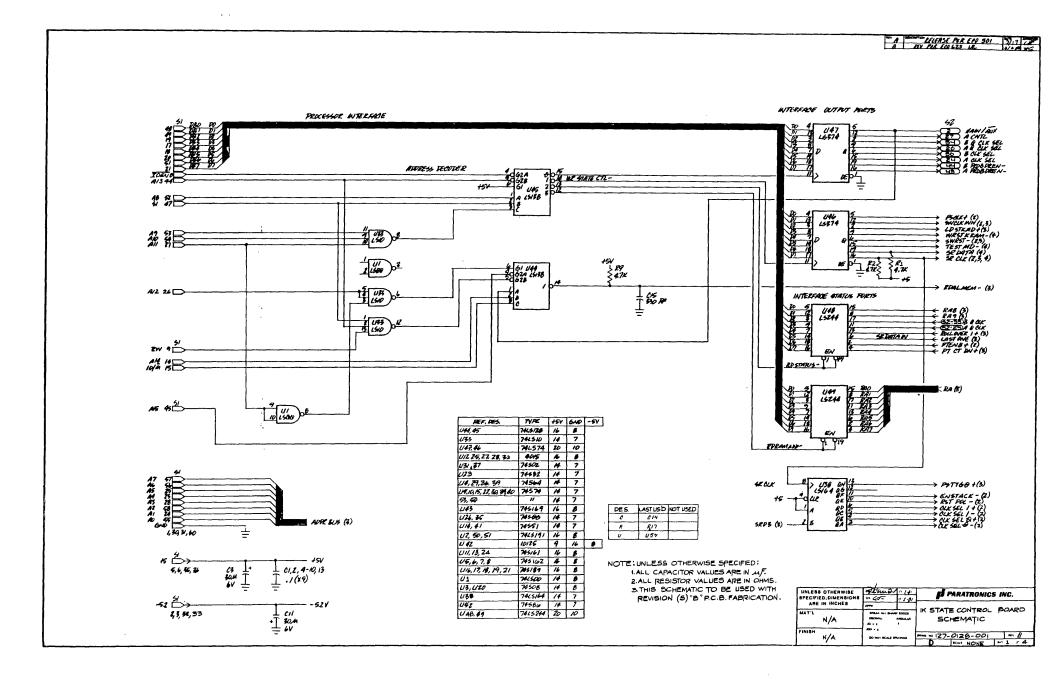

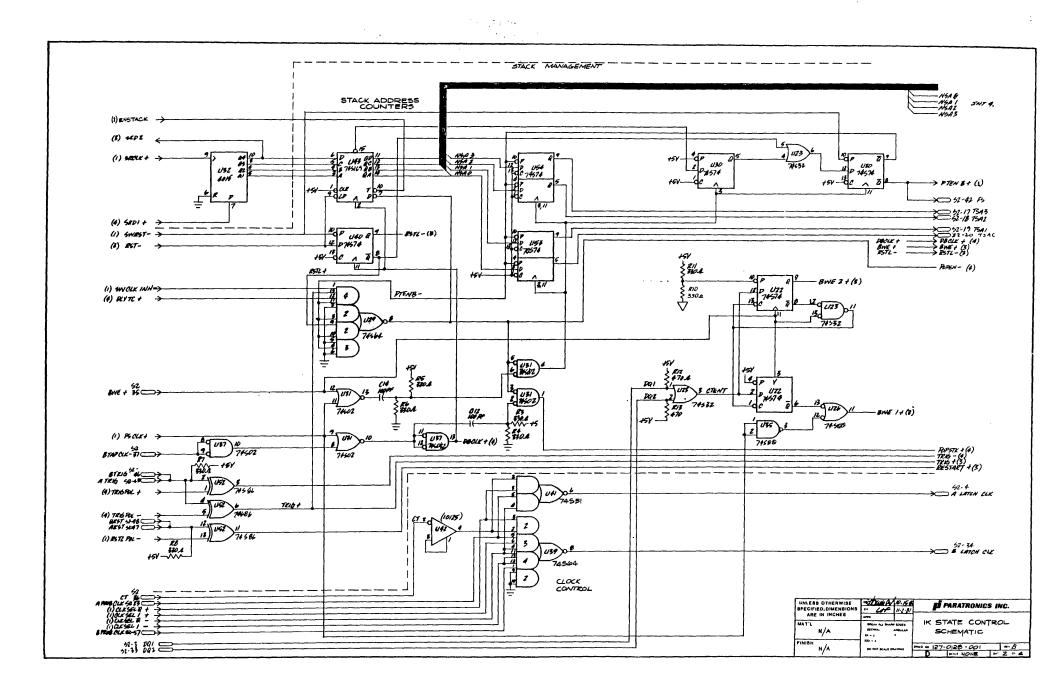

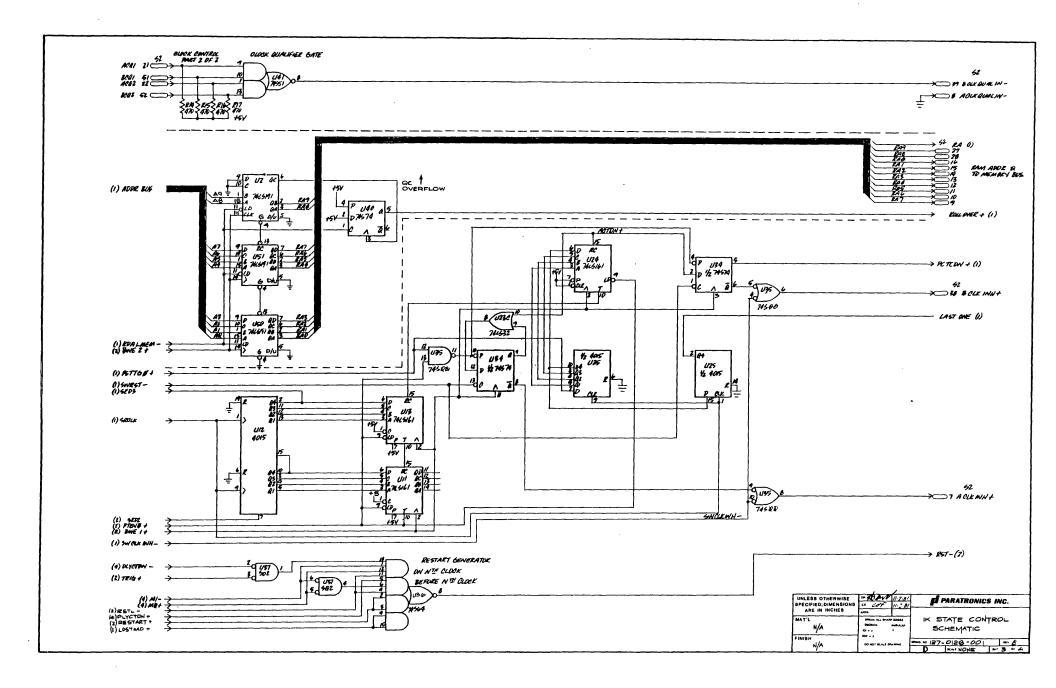

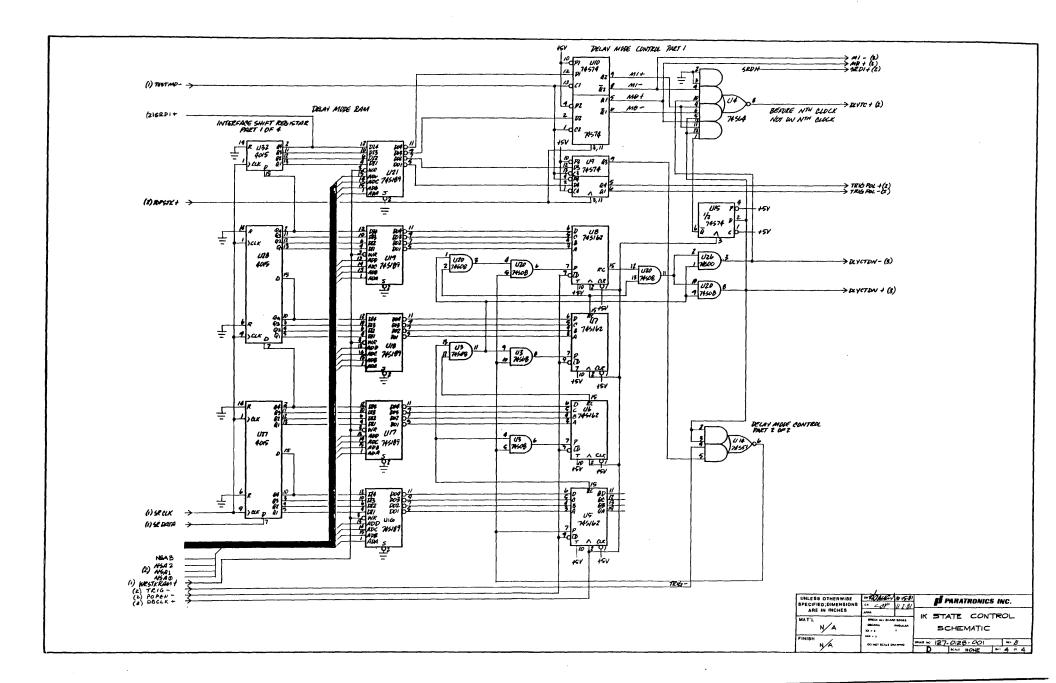

Section VII - State Control Board

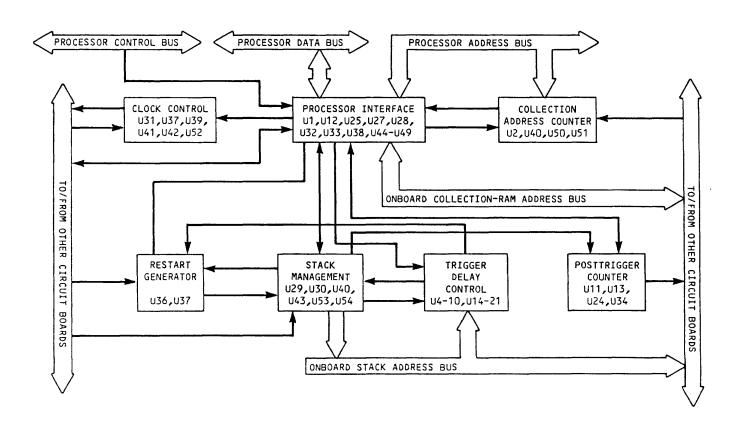

Block diagram, schematic and theory of operation for the state analyzer control.

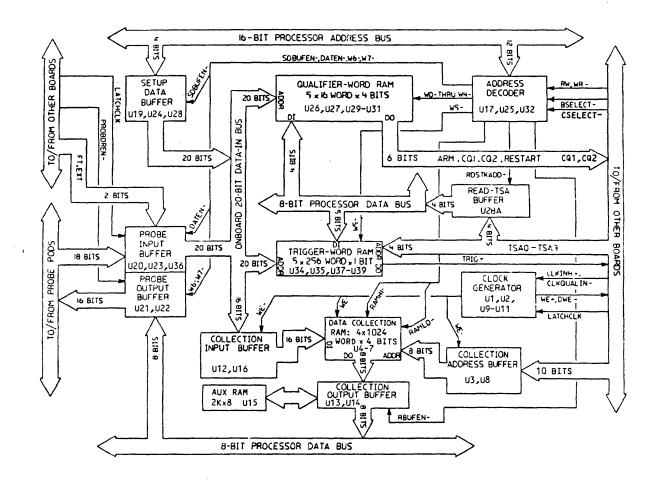

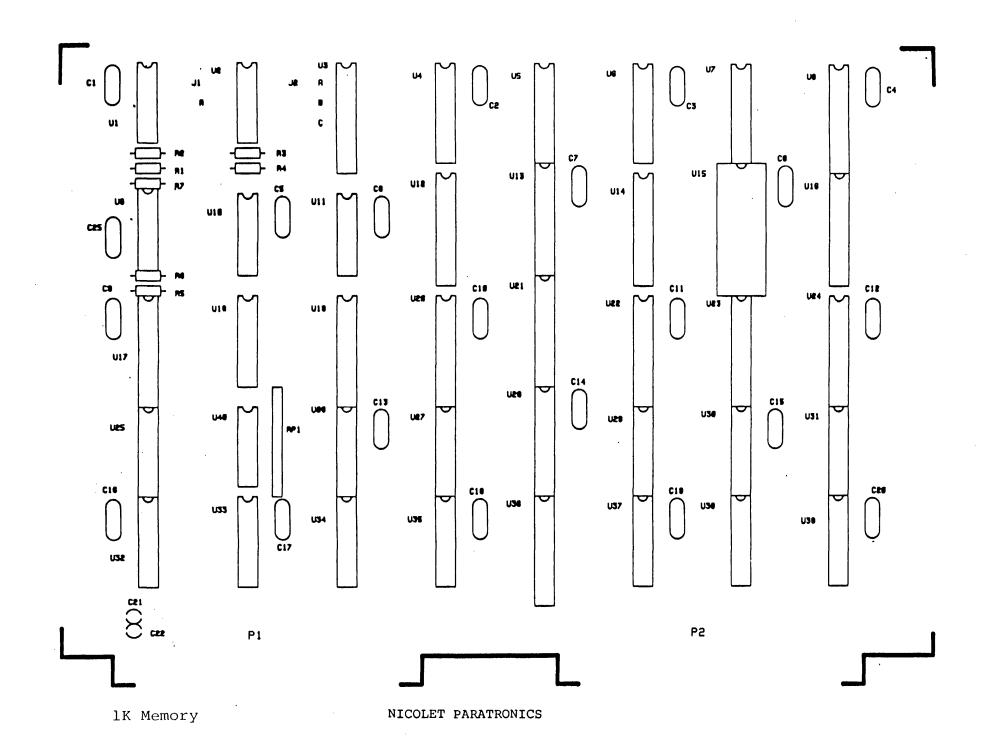

Section VIII - State Memory Boards

Block diagram, schematic and theory of operation for the State Memory Board.

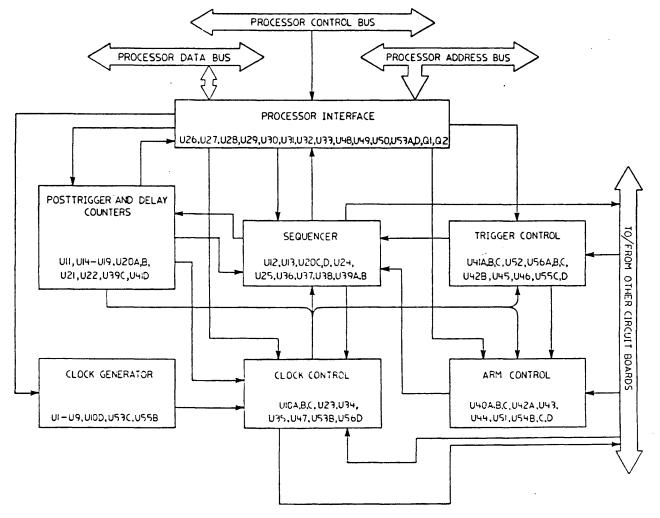

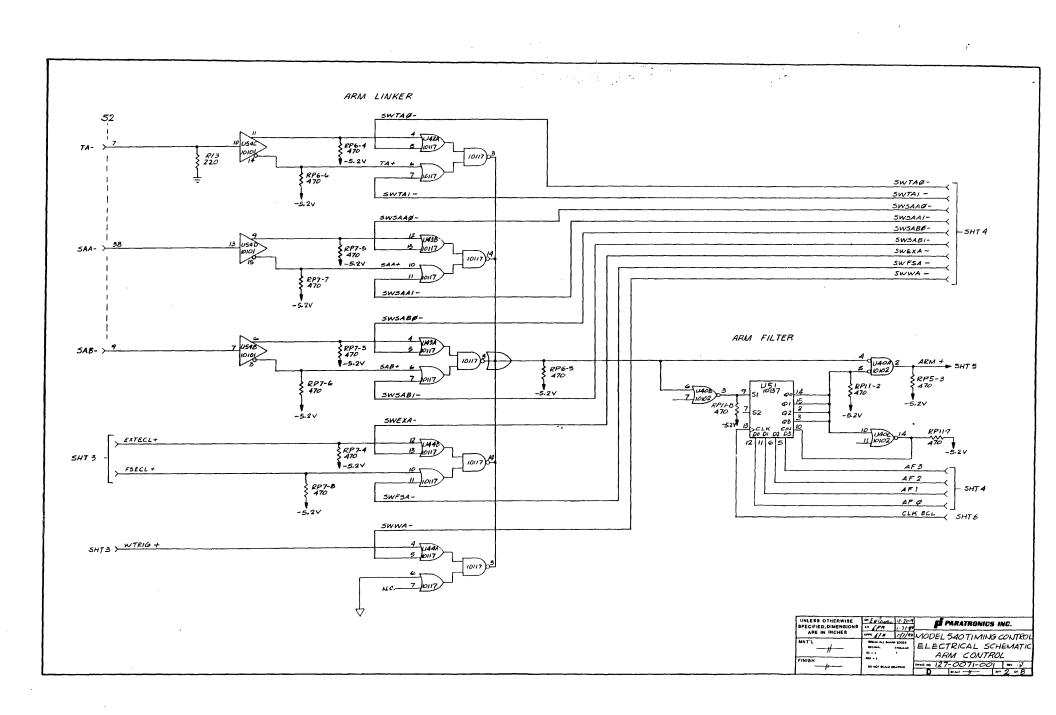

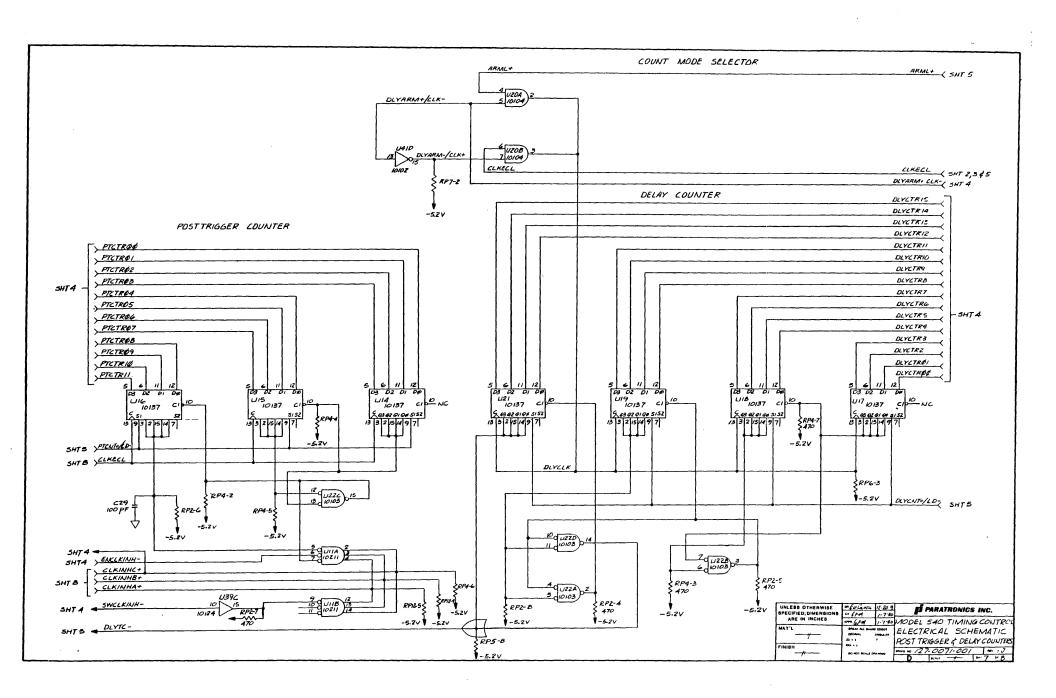

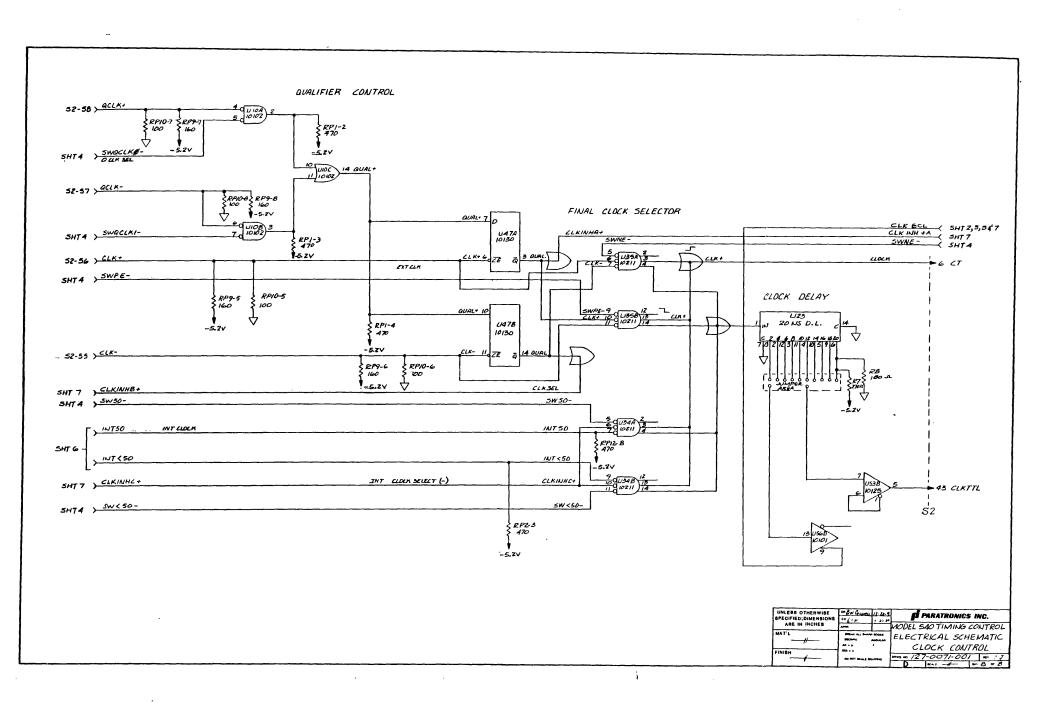

Section IX - Timing Control Board

Block diagram, schematics and theory of operation for the Timing Control Board.

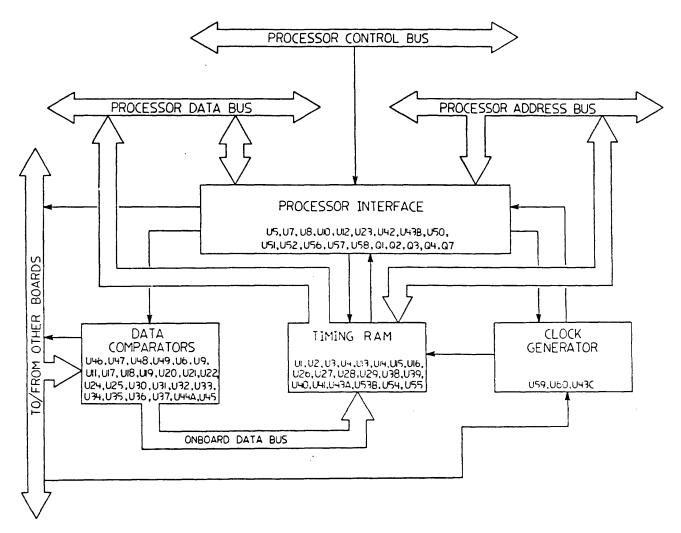

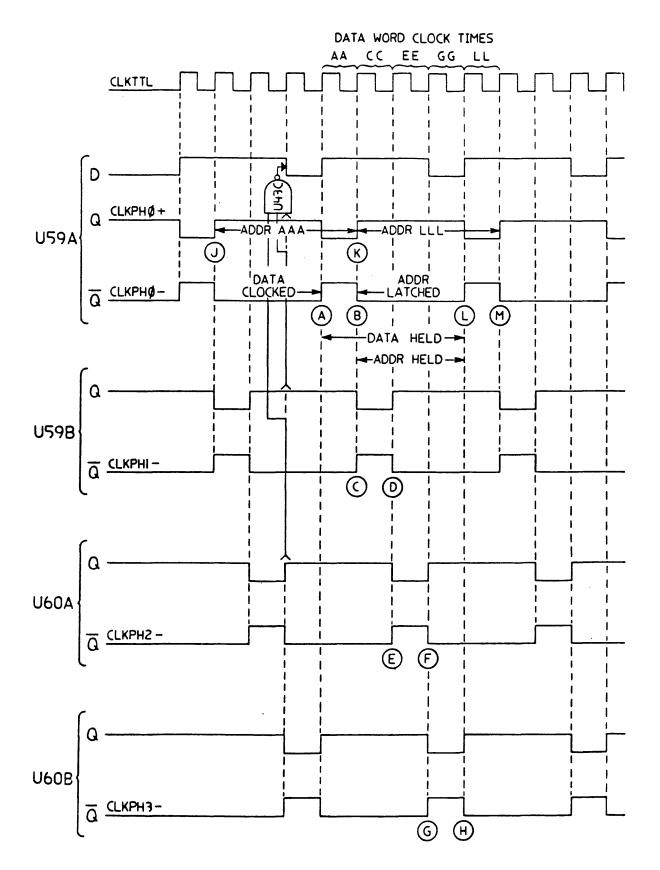

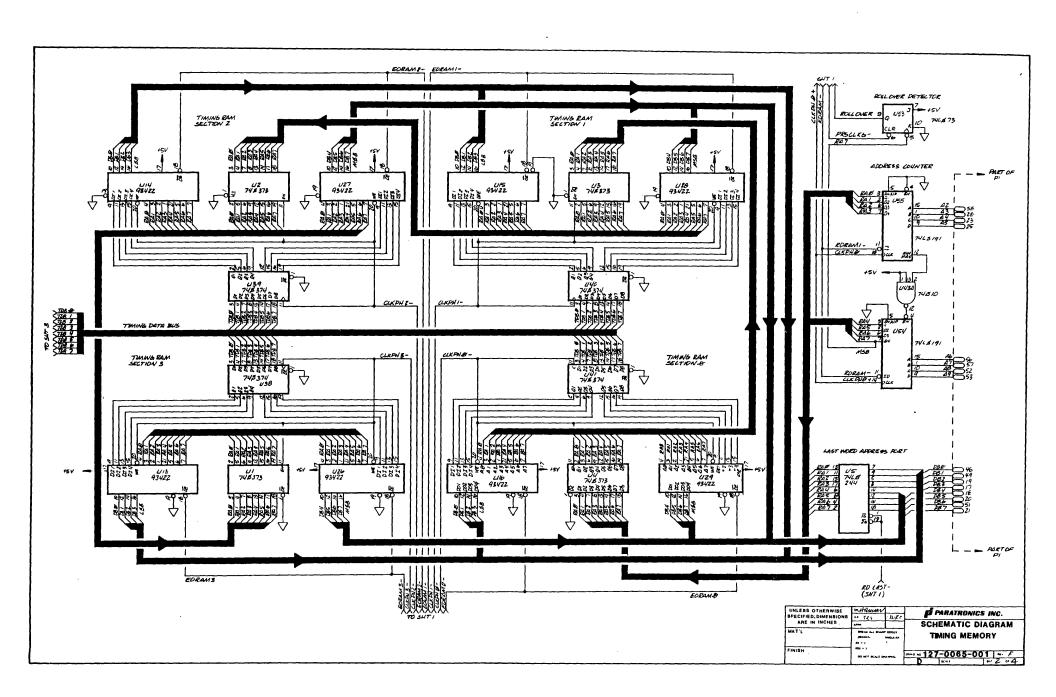

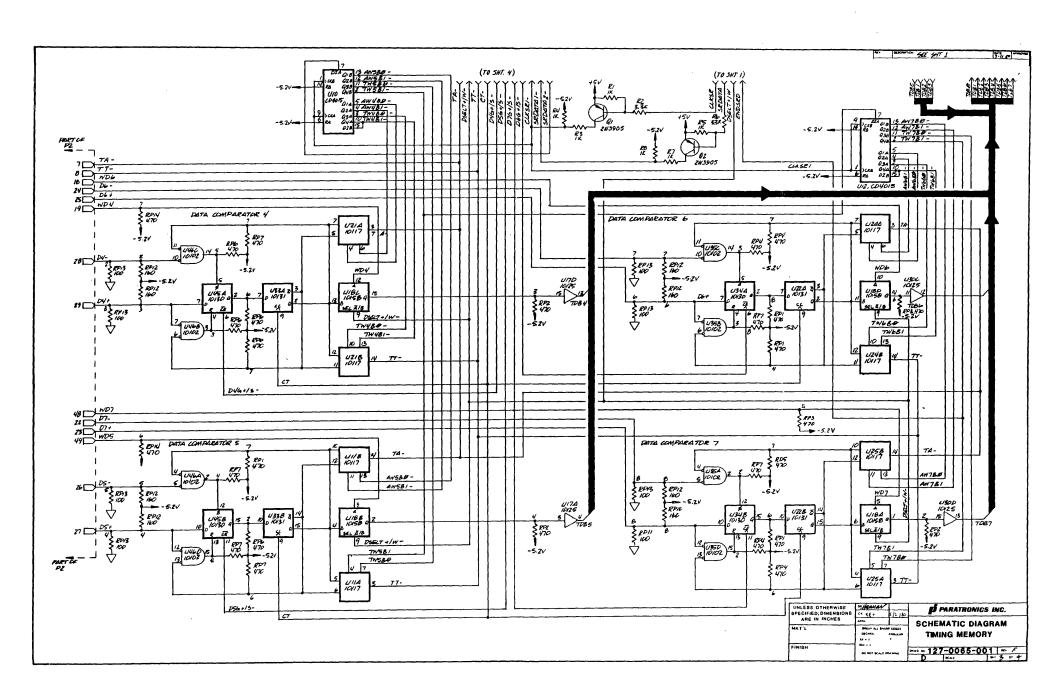

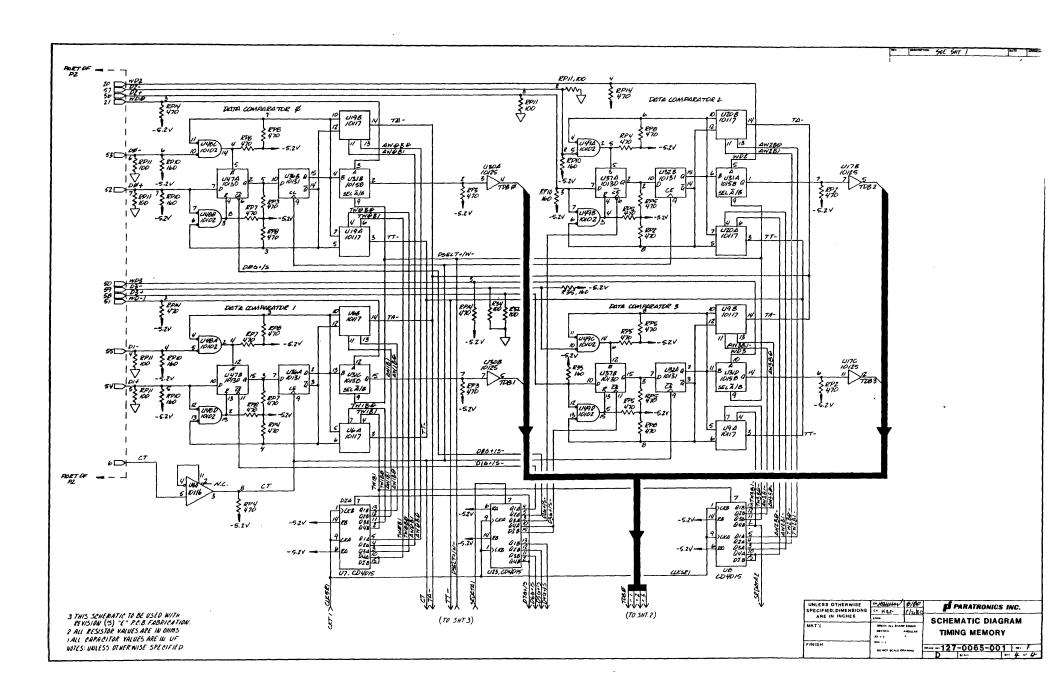

Section X - Timing Memory Boards

Block diagram, schematics and theory of operation for the two Timing Memory Boards.

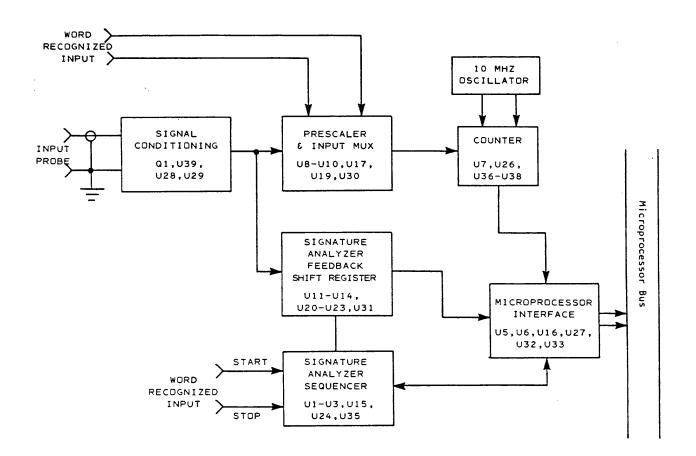

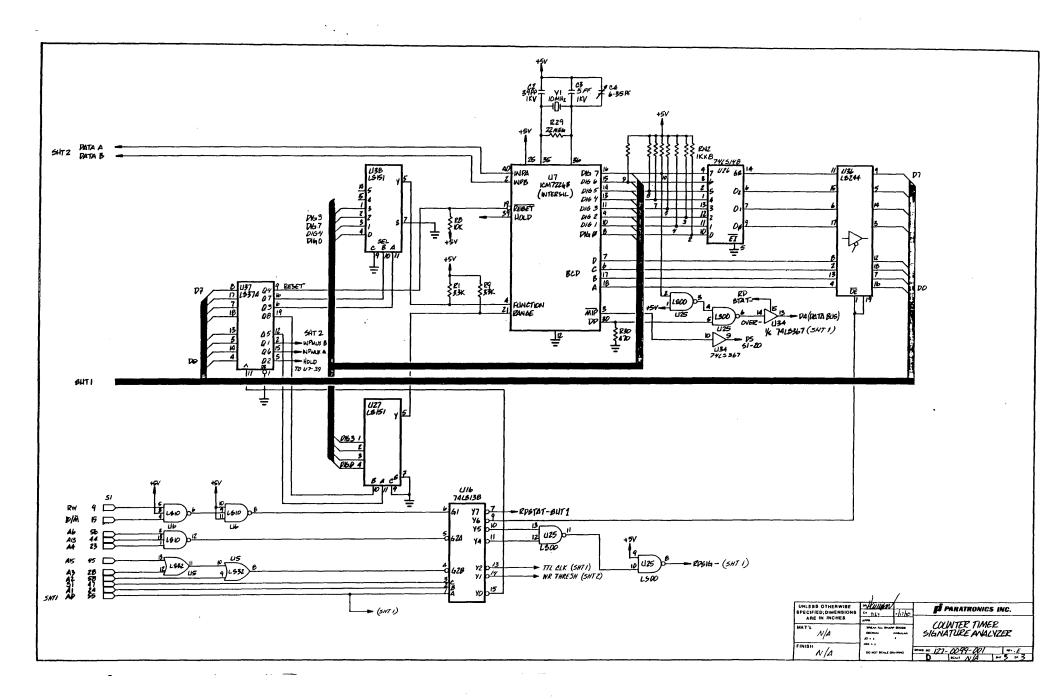

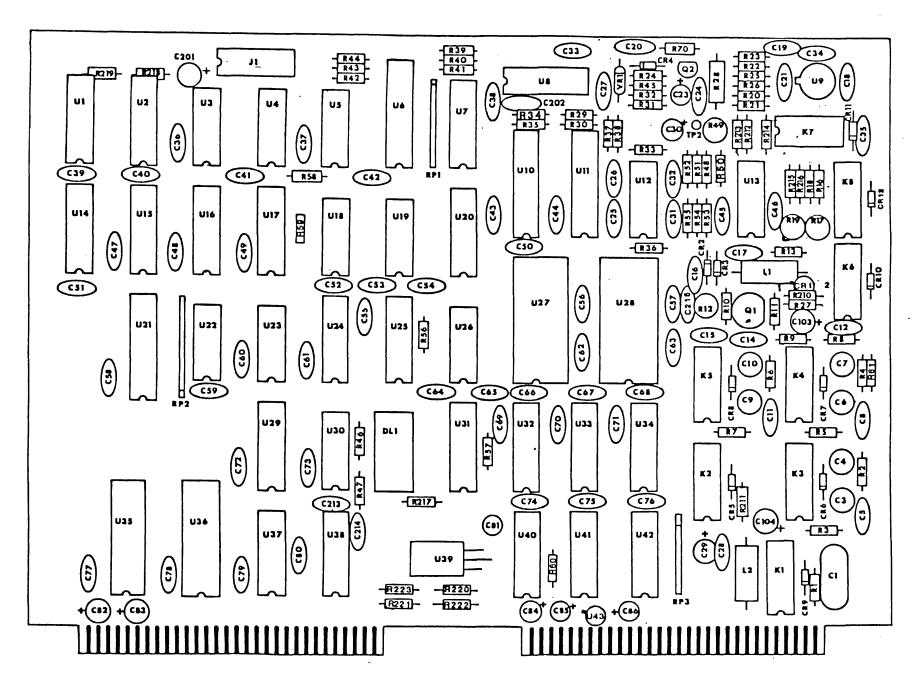

Section XI - CT/SA Board

Description of the optional Counter-Timer and Signature Analyzer Plug-in Board.

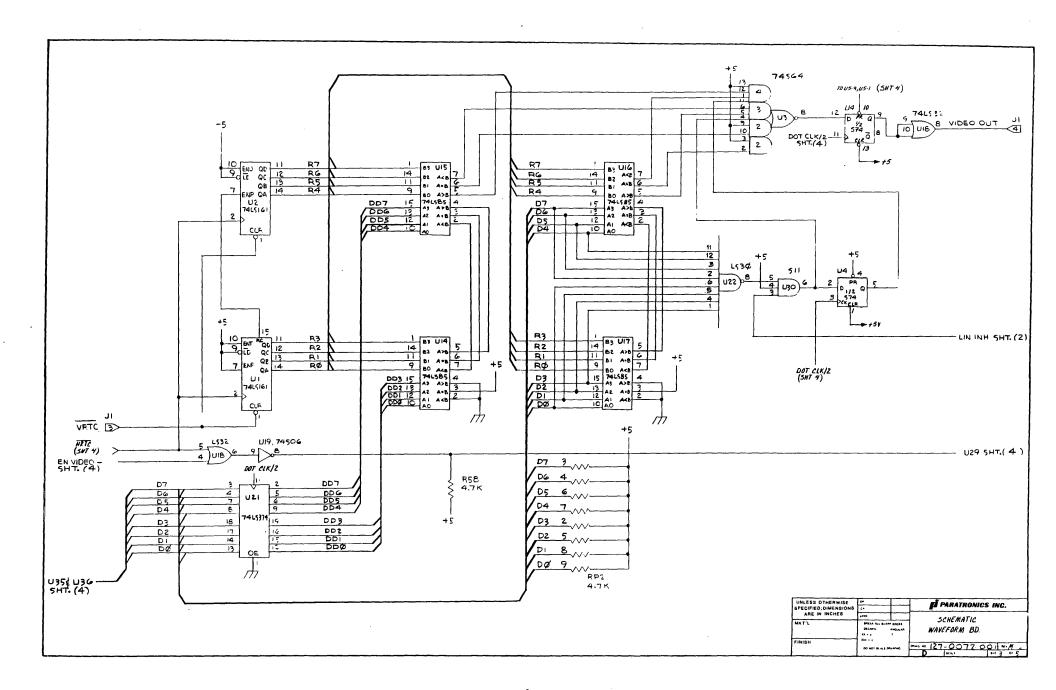

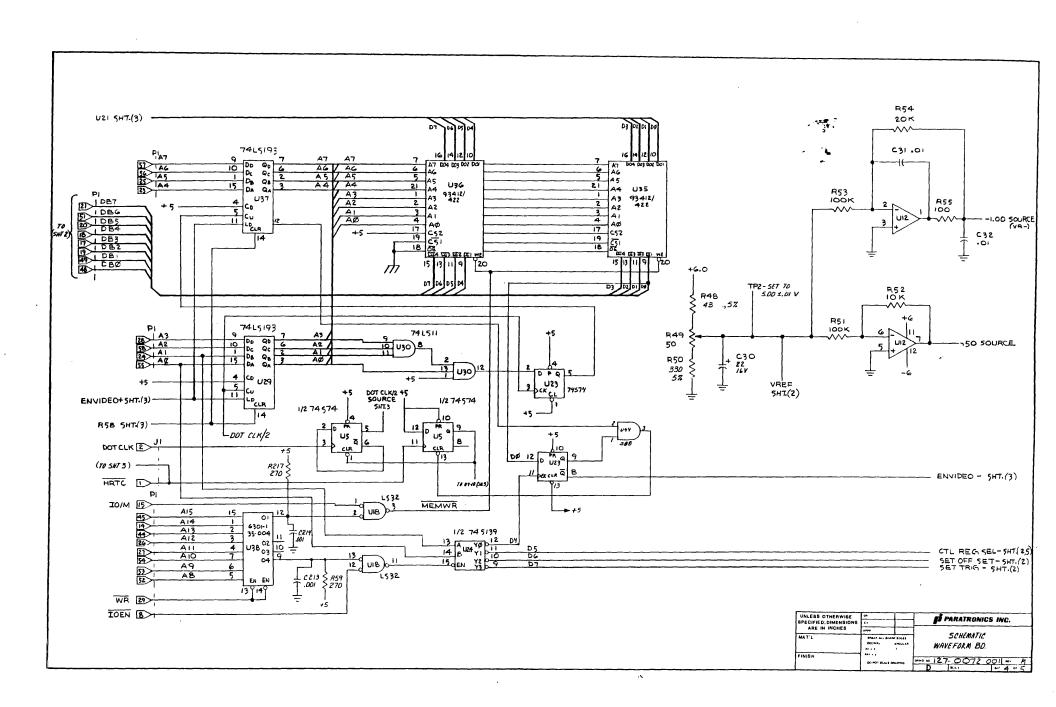

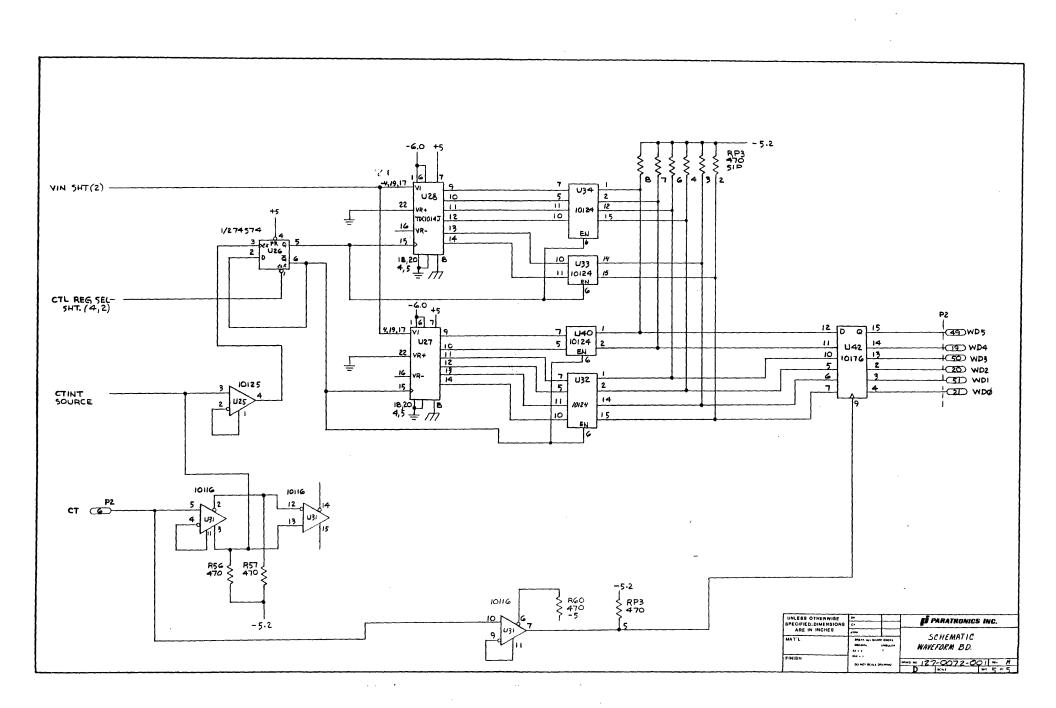

Section XII - Waveform Board

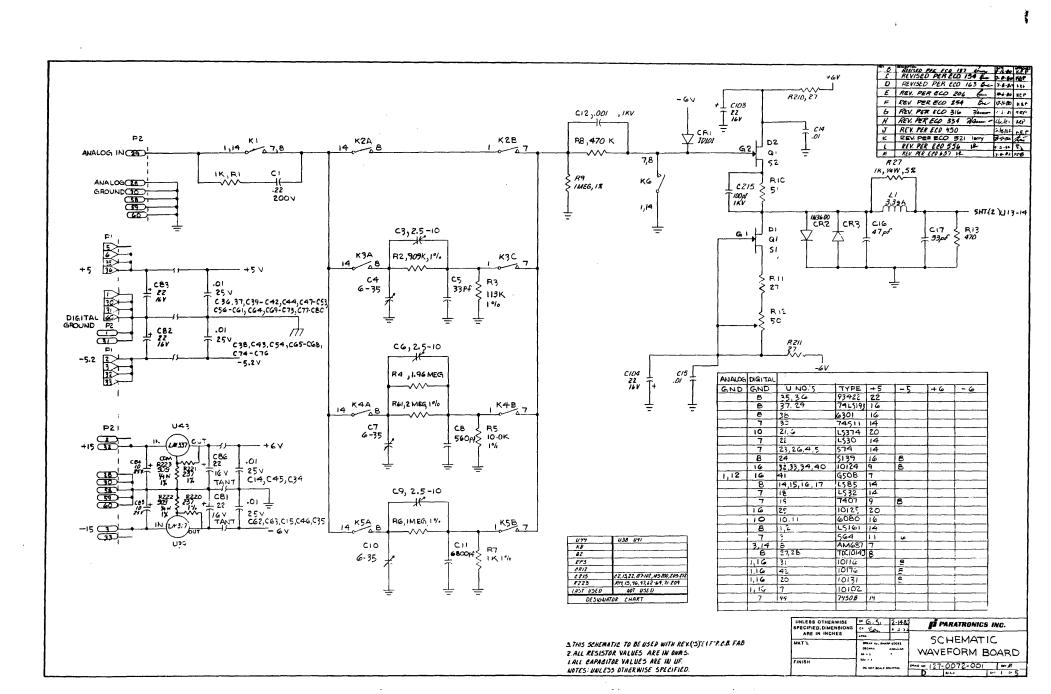

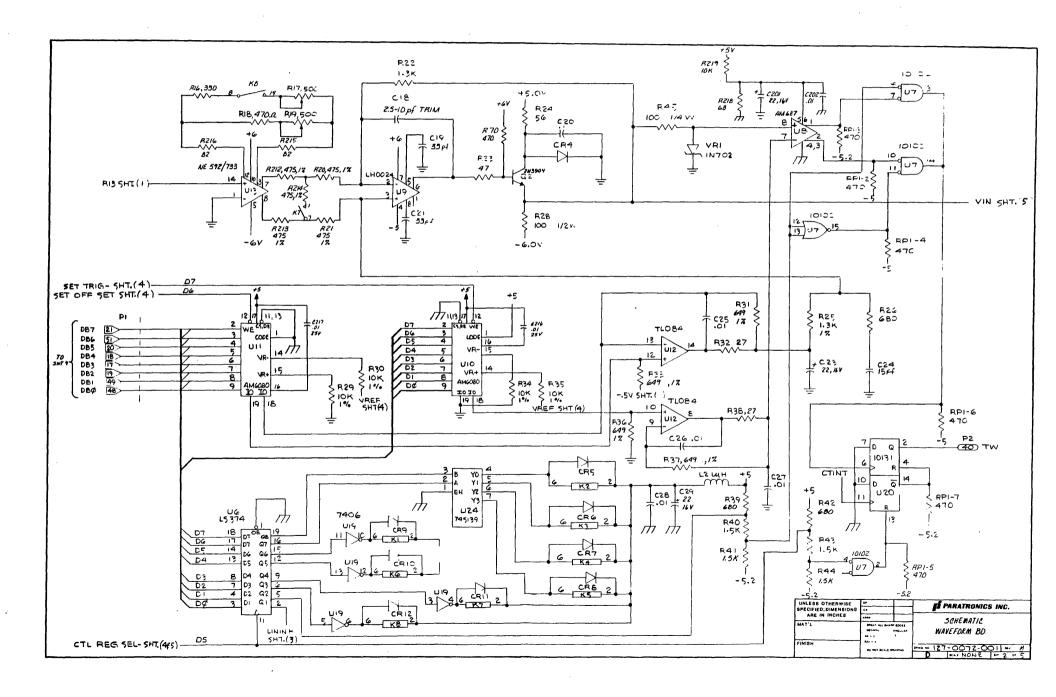

Schematic and theory of operation for the optional Waveform Board.

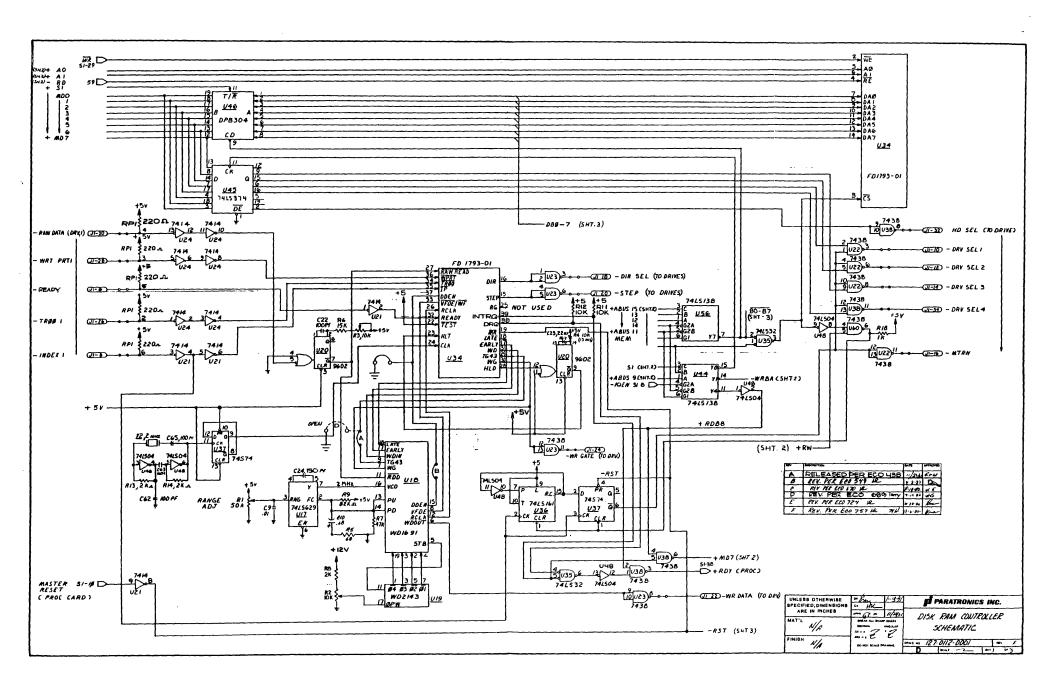

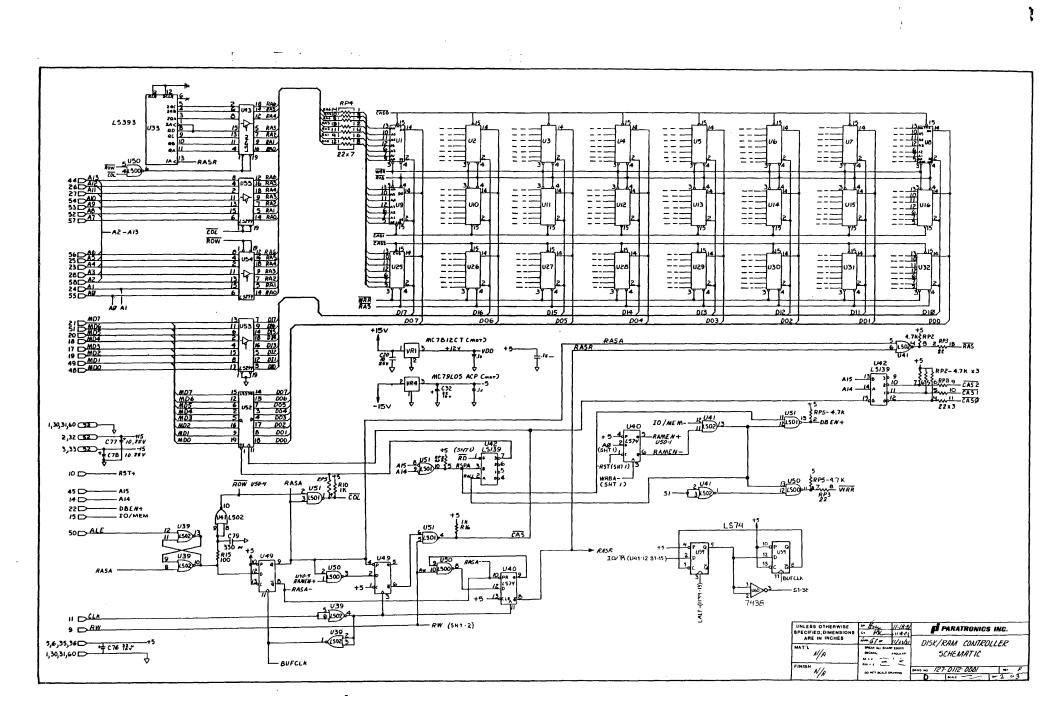

Section XIII - Disk Drive, Controller, Dynamic RAM

Description, operation and circuitry of the Disk Drive/Controller/Dynamic RAM.

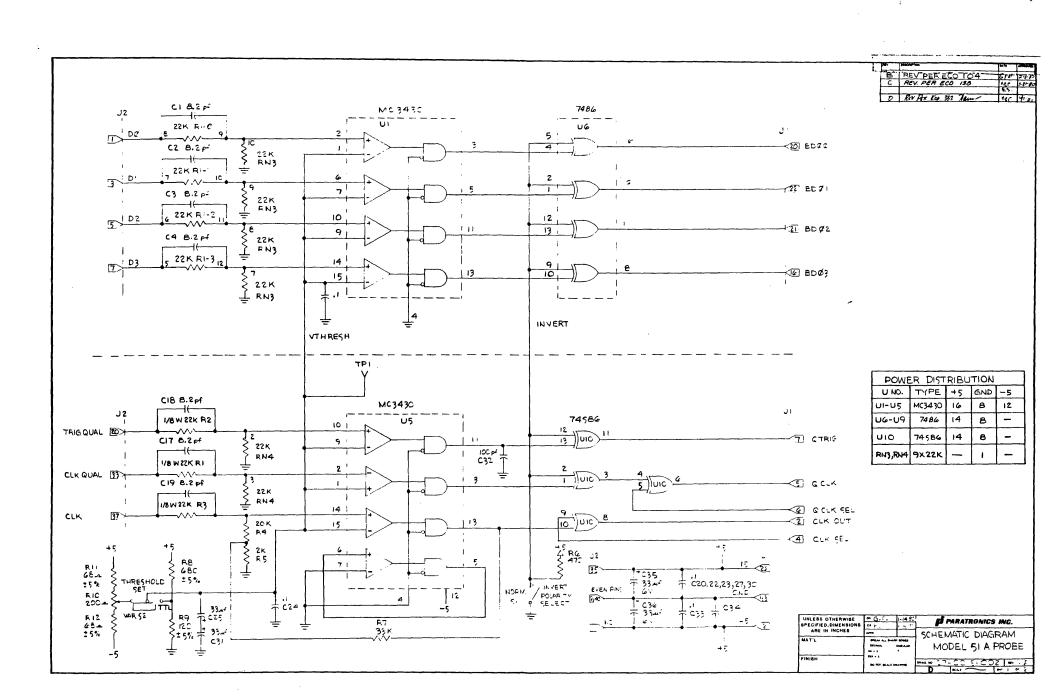

Section XIV - Input Probes

Describes the three probes used with the NPC 764. The Model 80 probe is used to apply input signals to the timing analyzer. The Model 90 probe is used for CT/SA readings of external signals and to apply input signals to the CT/SA Board or Waveform Board. The Model 51A probe is used to apply signals to the state section.

Section XV - Signal/Connection Tables

Contains complete wiring and pin assignments for the NPC 764 in tabular form.

Section XVI - Glossary

A glossary of terms used in this manual and logic analysis in general.

### 1.2 NPC 764 OPERATION

Instrument operation is covered in detail in the NPC 764 Operator's Manual shipped with each unit. Additional copies are available from Nicolet Paratronics.

The Operator's Manual contains several sections that may be useful from a maintenance point of view. These sections should be reviewed for a greater understanding of the product operation. The sections on KEYBOARD, MENUS AND DISPLAYS and REFERENCE should be particularly helpful. The section on REFERENCE contains solutions to many common operating problems.

In general, the maintenance information in this manual can be used without reference to the operating information in the Operator's Manual.

### 1.3 BLOCK DIAGRAM DESCRIPTION

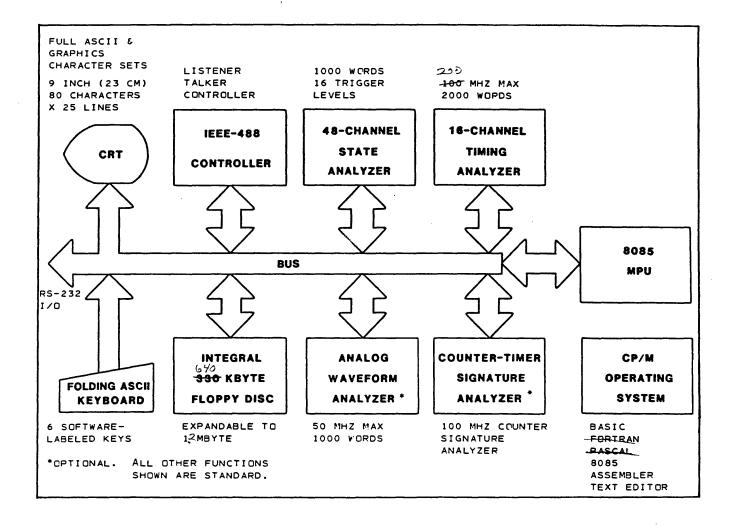

Refer to Figure 1-1. The NPC 764 is interconnected by a 60-wire system bus that forms an I/O path for all the functional modules.

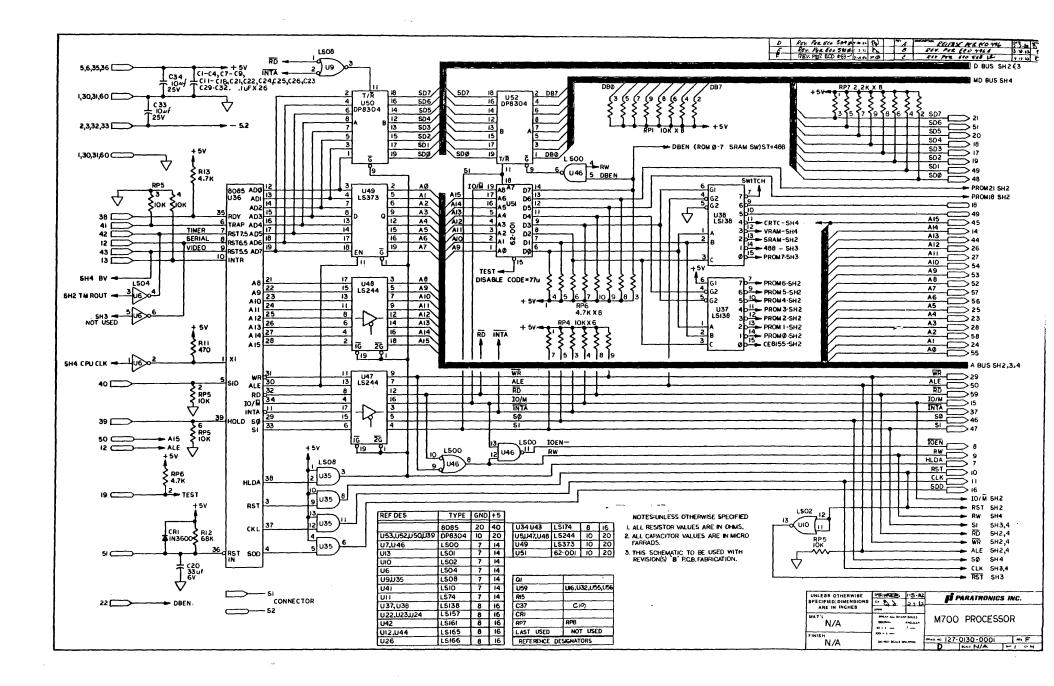

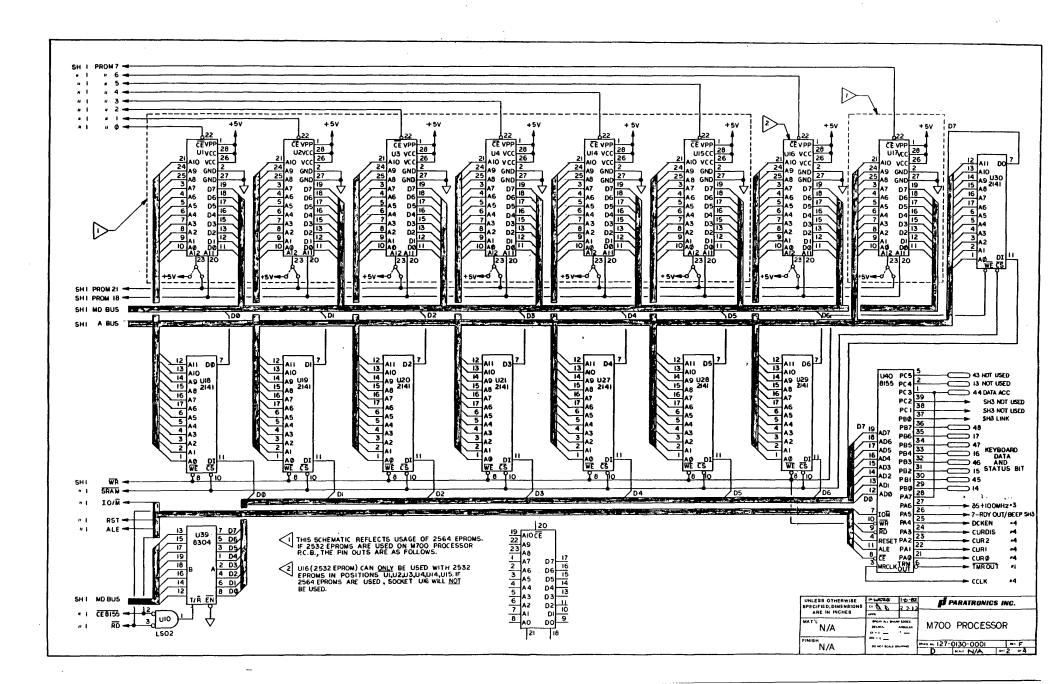

The CPU incorporates an Intel 8085 micro-processor that utilizes up to 48K bytes of ROM, and 48K bytes of RAM. The processor controls system operation including data collection, keyboard scanning, display and interfacing.

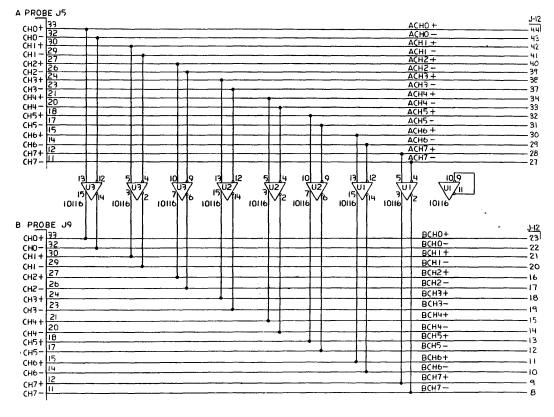

The State Input circuitry consists of Model 51A probes connected to State Memories A, B and C. Data is latched into these memories at rates up to 12.5 MHz. The data is continuously examined by the state control trigger detectors. When the data meets user-selected trigger conditions, it causes a Main Memory data collection.

Timing Input data from two Model 80 probes is fed to data comparators on Timing Memory Boards A and B. The data is sent from the probes in 16-bit parallel data streams. Data is continuously latched into these comparators. The data is sent from the comparators to the Main Memory, at userselected clock rates up to 100 MHz. The comparators continuously compare the incoming data with arm and trigger words entered from the keyboard at set-up time. When arm and trigger conditions are met, a snapshot of 1000 words of current data is locked into the Main Memory. This snapshot subsequently may be displayed and examined. The 1000-word snapshot also can be divided between pre-trigger and posttrigger words as selected from the keyboard at set-up time.

The Main Memory retains the last data entered until a new set of data is loaded. The new set of data is loaded using the COLLECT (soft) key. Also, the contents of the Main Memory can be transferred to the Auxiliary Memory. There it may be retained for comparison with subsequent Main Memory data collection. The contents of either the Main or Auxiliary Memory can be displayed under keyboard control.

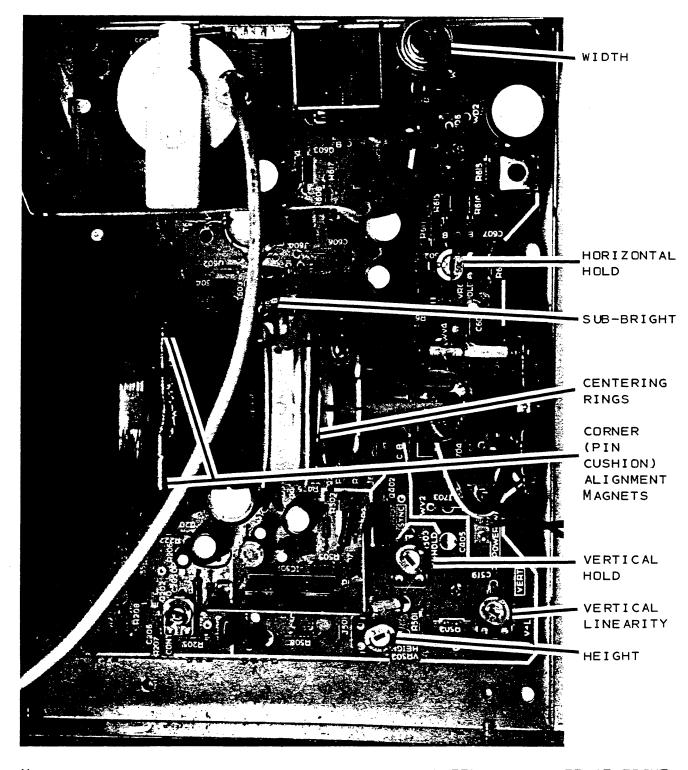

The CRT Display is a raster scan unit with a 9-inch (23 cm) diagonal screen. The driving circuitry resides on the CPU board. A composite video output on the rear panel of the NPC 764 allows use of a large-screen monitor if desired.

The Keyboard provides user access to the NPC 764 parameter/ measurement set, menus, display formats, trigger modes and interfaces. The keys are a combination of direct entry, menu selection and software-defined "soft" keys.

An RS-232 Interface is provided as standard on the NPC 764. This interface permits output of display-formatted data to a printer or other peripheral. The NPC 764 also is provided as standard with an instrument-bus IEEE-488 Interface. That allows the NPC 764 to be talker, listener or controller.

Optional measurement features are added to the NPC 764 by adding the CT/SA (Counter-Timer/Signature Analyzer) PCB to the unit.

The Waveform Analyzer board can optionally be included in the NPC 764 to obtain added analog measurement capabilities.

Mnemonic Disassembly accessories are available for a variety of microprocessors. Disassembly operates by loading programs from disk and collecting data using dedicated probes.

### 1.4 DETAILED OPERATION

The NPC 764 analyzer collects data under specified conditions and stores the data in memory for detailed examination.

To start data collection, the user presses COLLECT (soft key) on the keyboard. When the trigger conditions are met, data collection is automatically stopped by the analyzer. Alternately, selection may be made for data collection to continue after the trigger event. The user must specify the amount of post-trigger data to be collected. Once data collection has stopped, the data can be displayed in various formats for convenient analysis.

Figure 1-1 NPC-764 Simplified Block Diagram

### SECTION 2: SELF TESTS

|     |         |             |                                         | PAGE         |

|-----|---------|-------------|-----------------------------------------|--------------|

| 2.1 | Introdu | uction      | • • • • • • • • • • • • • • • • • • • • | 2-1          |

| 2.2 | Automa  | tic Self To | est                                     | 2-1          |

|     | 2.2.1   | Processo    | r Test                                  | 2-1          |

|     | 2.2.2   | System D    | isk Self-Tests                          | 2-2          |

| 2.3 | Basic 1 | Γests With  | the Logic Analyzer Test Card            | 2-2          |

|     | 2.3.1   | Prelimina   | ary Tests                               | 2-3          |

|     | 2.3.2   | Test Card   | d Description                           | 2-3          |

|     | 2.3.3   | Set-Up .    |                                         | 2-4          |

|     | 2.3.4   | Basic Sta   | ate Tests                               | 2-4          |

|     |         | 2.3.4.1     | Saving Data                             | 2-6          |

|     |         | 2.3.4.2     | Hold ≠ Mode                             | 2-6          |

|     |         | 2.3.4.3     | Difference Mode                         | 2-8          |

|     |         | 2.3.4.4     | Search Word Mode                        | 2 <b>-</b> 8 |

|     | 2.3.5   | Basic Tir   | ning Test                               | 2-8          |

### SECTION II SELF TESTS

#### 2.1 INTRODUCTION

The NPC 764 provides three types of selftests that can be useful in assessing the condition of the instrument. First, an automatic self-test is performed every time power is turned on. Second, there are self-tests that can be performed with the Logic Analyzer Test Card, NPC part number 143-0046-002. Third, there are self-tests that can be performed using a system disk.

### 2.2 AUTOMATIC SELF TEST

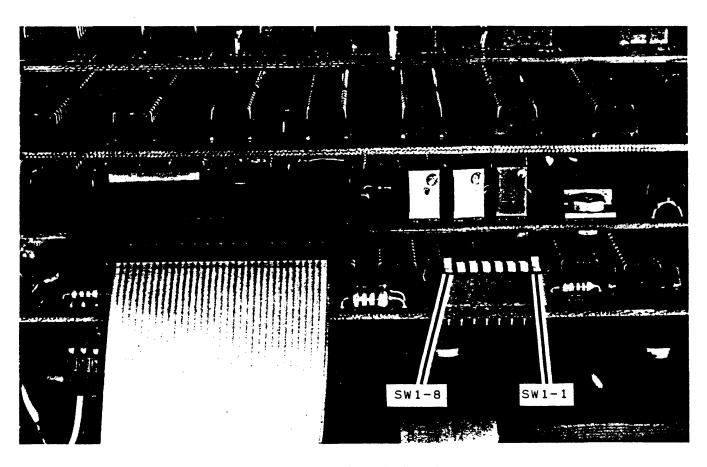

The automatic self-test is performed during the first two seconds each time power is applied to the analyzer. This test goes through a set of performance checks of the NPC 764 memories and other subsystems. The test reads the setting of the power-line frequency selector switch, S1-1, on the Processor Board. The CRT vertical SYNC frequency is set to a matching 50 or 60 Hz. Although this self-test does not provide a 100% check, it offers a high confidence level that the analyzer is operating properly.

Successful completion of the test is an-

nounced by a short beep followed by a display of the Configuration Menu. If the test is not successful, there will be no beep.

#### 2.2.1 PROCESSOR TEST

The 764 system software contains a test that automatically checks the processor board. To run this test proceed as follows:

- a. Turn the 764 OFF.

- b. Short pins 2 and 3 of the RS-232 connector, located on the back panel of the unit. (See Figure 2-1).

Figure 2-1 Connector Jumper

- c. Turn the 764 on.

- d. Press the BREAK key.

- e. Verify that the display appears as shown in Figure 2-2.

NORMAL HALFLIGHT BLINK THE THE OVERLINE

MODEL 188 PROJESSOR BOARD FUNCTIONAL TEST PROGRAM VI. 1 81/05/22

Figure 2-2 Screen

To abort the test hold down the RESET key for three seconds and press the ESCape key.

### 2.2.2 SYSTEM DISK SELF-TESTS

Each CP/M system disk contains three tests. They are as follows: The RAM test, the keyboard test and the disk drive test. To run any of these tests, insert a system disk into drive A and press the ESCape key. The CRT display will then look like Figure 2-3.

### MICOLET-PARATRONICS 70000 48K CPM 2.2 OF 9-3-81

4>

Figure 2-3 Screen

To run the RAM test type RAMTEST <return>.

This test writes a walking I's pattern into the dynamic RAM, reads the data back and indicates any errors. The test runs continuously, and takes about 20 minutes for

each pass. The total number of errors and the number of test runs is indicated on the screen. See Figure 2-4. To abort the test, press the RESET key. To reboot, press the ESCape key.

### ### 48K D'ANGMIC ROM TEST PROGRAM G8/17/81 WALKING I'S TEST: 1'S ADDR: 8898

TESTING ADDRESS: ---- EXPECTED: -- READ: -TUTAL FAILURES: 8

PASSES COMPLETED: 8

Figure 2-4 Screen

To run the keyboard test type KYBDTEST <return>. Observe the keyboard display on the CRT. See Figure 2-5.

To test the keyboard strike each key displayed on the screen once. As each key is struck, it will disappear from the screen.

### DISK TEST

To test a drive, boot up the CP/M system disk by pressing ESCape (if not already booted up). Enter DSK5TEST <return> on the keyboard. Refer to Figure 2-6. You will then be asked to select a drive to be tested. If you have only one drive, enter the letter "A". The 764 will respond with the question "How many retrys?" Enter a number between zero and nine. You will then be asked for a full track seek. If you enter "Y". the read/write head will restore to track 0 after each track is read. If you enter "N", each track will be read consecutively. After selecting "Y" or "N", strike RETURN to start the test. The test will take between five and ten minutes to complete depending on the parameters you have selected.

# 2.3 BASIC TESTS WITH THE LOGIC ANALYZER TEST CARD

NPC Logic Analyzer Test Card, Part Number 143-0046-002, provides a comprehensive functionals test of the NPC 764 Logic Analysis system. A suitable procedure is given in the following paragraphs. All

F1 F2 F3 F4 F5 F6 LABELS

ESC 1 2 3 4 5 6 7 8 9 8 - = "BS BK

TAB querty uia p C ! LF DEL

as d f g h j k I; ' (RETURN

S1 z x c v b n m , . / S2

SPACE

UNLOCK CAPS LOCK KEY

PRESS EACH KEY ON KEYBOARD. ALL KEY LAKELS SHOULD DISSAPPEAR

Figure 2-5 Screen

### MICOLET-PARATRONICS 7888 48K CPM 2.2 OF 9-3-81

### A)DSK5TEST

TARBELL DISK DIAGNOSTIC STANDARD VERSION 1.8 77 TRACKS 16 SECTORS

SELECT DRIVE. (A/B/C/D) A HOW MANY RETRYS? (B-9) B SELECT STEP RATE. (S/M/F) FULL TRACK SEEK? (Y/N) N TO START TEST TYPE RETURN.

0888 READ ERRORS DETECTED.

REPEAT TEST? (YAVC=CONTINUOUS) C

Figure 2-6 Screen steps necessary for a comprehensive evaluation are presented. This procedure assumes the user has some familiarity with the operation of the NPC 764. If necessary, refer to the Operator's Manual.

### 2.3.1 PRELIMINARY TESTS

Perform the following tests to confirm operation at the most primitive level.

- a. Disconnect the power cord from the analyzer. The power fuse and voltage cord must be visually inspected to verify correct installation for the current application. Refer to the discussion of the Mains Module in the Chassis section for more information. Reconnect the power cord.

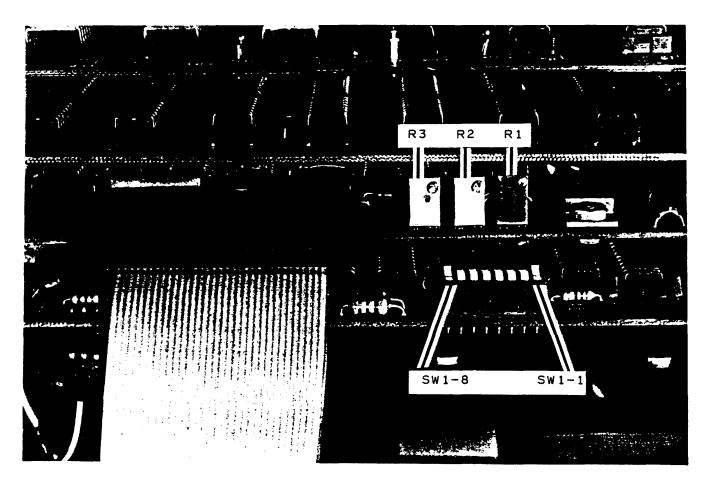

- b. Check the setting of SW1-1 on the Processor Board. The video vertical sync frequency is set to match the power mains frequency. ON = 60 Hz, OFF = 50 Hz.

### 2.3.2 TEST CARD DESCRIPTION

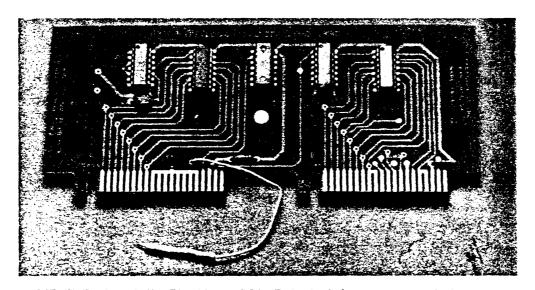

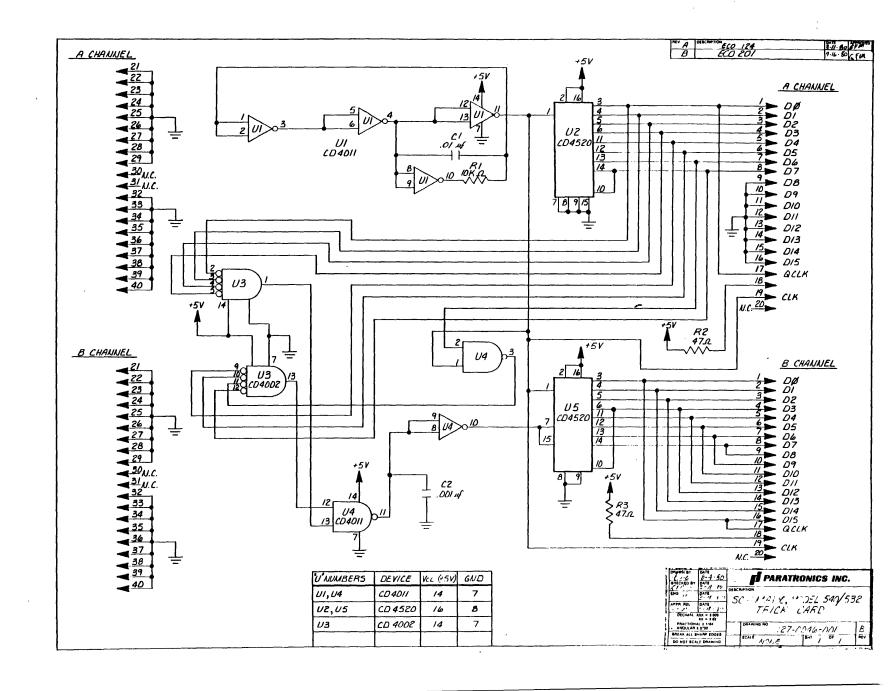

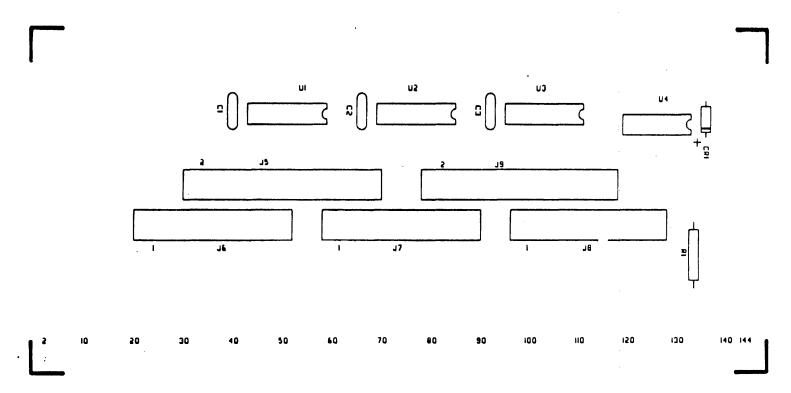

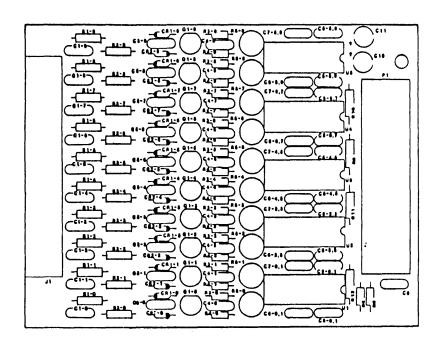

The Logic Analyzer Test Card consists of two 8-bit CMOS counters (A and B), a clock, and simple decoding logic. Refer to Figure 2-7 and schematic #127-0046-001 at the end

TEST CARD

CHASSIS CONNECTORS FOR PROBES

Figure 2-7 Logic Analyzer Test Card and Probe Connectors

of this section. Each CMOS counter normally counts from  $(00)_{\rm HEX}$  to  $({\rm FF})_{\rm HEX}$ . When the A counter reaches  $(40)_{\rm HEX}$ , the decode logic resets the B counter to  $(00)_{\rm HEX}$ .

The A channel connector is wired with the eight least significant bits corresponding directly to the output of the A counter. The eight most significant bits are tied to ground. Thus, the A channel provides a 16-bit word to the analyzer that sequences from  $(0000)_{\rm HFX}$  to  $(00{\rm FF})_{\rm HFX}$ .

The B channel connector is wired so that the 16 output bits toggle nonsequentially. A typical binary count sequence at the B channel connector is as follows:

| COUNT | BINARY   | PATTERN* | HEX PA | TTERN |

|-------|----------|----------|--------|-------|

| ===== | =======  | =======  | =====  | ===== |

| 0     | 00000000 | 00000000 | 00     | 00    |

| 1     | 10000000 | 00000001 | 80     | 01    |

| 2     | 01000000 | 00000010 | 40     | 02    |

| 3     | 11000000 | 00000011 | CO     | 03    |

| •     | •        | •        | • •    |       |

| •     | •        | •        | • •    |       |

| •     | •        | . •      | • •    |       |

| 15    | 11110000 | 00001111 | F0     | 0F    |

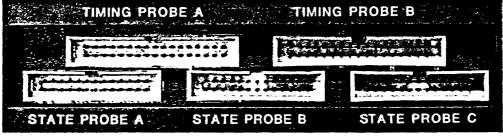

Note the difference in pin-outs between the 16-channel state probes and the 8-channel timing probes. Due to the difference, this exact pattern will be displayed on the NPC 764 only when using the state probe.

Power to the test card is supplied by the +5 V output at either probe connector.

The A counter is generally used as a signal source for the A state or timing probe. The B counter output feeds the B state or timing probe. The third 16-channel state probe (C) is not normally connected to the test card.

### 2.3.3 SET-UP

Before using the test card, proceed as follows:

a. Connect the A and B state probe cables to the NPC 764. LEAVE THE C PROBE UNCONNECTED.

- b. Connect the A probe to the left-hand connector of the test card and the B probe to the right-hand connector. Set both probes for TRUE and TTL operation.

- c. Turn the NPC 764 power switch ON and wait for the self-test beep and Configuration Menu. Refer to Figure 2-8.

### 2.3.4 BASIC STATE TESTS

To test the basic state analysis capabilities of the NPC 764 do the following:

- a. Select a menu.

- b. Enter in a trigger word.

- c. Press the COLLECT(F6) key.

Captured data can be then formatted in a variety of ways.

The six soft function keys are labeled F1 to F6 from left to right. They are identified by labels on the bottom line of the CRT. These labels differ from menu to menu, as selected with the SEL DOWN or SEL UP keys.

Examples using these keys are given below:

- a. To select the 48-CHANNEL STATE mode, press the STATE(F1) key to call the state menu illustrated in Figure 2-9.

- b. The 48-channel state menu should be set up with the default values in all fields except the trigger word field. Advance the blinking cursor to the trigger stack field, level 0, with the NEXT(F2) key. Press the H key to format this field for a hexadecimal trigger word. Now enter the following trigger word: 0040. Observe the field at the lower right of the CRT. Other formats can be selected from this field using the indicated keys.

- c. Press COLLECT(F6) to take a data collection beginning at 0040. Then

# NE NICHET PARATRONICS 764 CONFIGURATION VER 4.0

- 48 CHNL STATE

2 - 16 CHIL TIMING

3 - 48 CHNL STATE/16 CHNL TIMING

4 - 8 CHAL TIMING (109MHZ 2000 WORD)

5 - 48 CHNL STATE/8 CHNL TIMING

6 - 8 CHAL TIMING GLITCH

7 - 48 CHNL STATE/8 CHNL SLITCH

8 - WAVEFORK RECORDER

9 - 48 CHNL STATE MAYEFORM

10 - COUNTER/TIMER

11 - SIGNATURE ANALYZER

12 - PI 78 SERIAL PROBE TRANSMIT

ESC - DISK OPERATING SYSTEM

BREAK - PROCESSOR SELF-TEST

I - I/O CONFIGURATION MENU

STATE

SEL DOWN

SEL UP COLLECT

Figure 2-8 Configuration Menu

48 CHANNEL STATE MENU

FORMAT: ANAGAGA ARGAGAGA GRAGAGAG ARGAGAGA ARGAGAGA ARGAGAGA

A HEX

CLK SEL: A PRB: J B PRB: A C PRB: A QUALIFIERS: -AABBCD EL

CLK GUAL: OFF CR CFF

PRE-TRIS MEMORY (0-999): 800 WCRDS

RESTART: OFF

TRIGGER:

**99 48 XX XX XX XX -XXXXXX XX** 8

END

H - HEX

0 - OCTAL

Z - DEC

N - BINARY

Y - ASCII

U - USER

31 - DATA DISPLAY

PREVIOUS

NEXT

CONF16

COLLECT

Figure 2-9 48 Channel State Screen

press the LABELS key. Reformat the display in octal, decimal, binary and ASCII by pressing the O, Z, N, and Y keys in turn. Press the H key for the hexadecimal format. Refer to Figure 2-10.

d. Scroll the display up and down by holding the SCRL UP(F2) key, then the SCRL DOWN(F1) key. Locate the end of the data collection (word +999) by pressing the LOCATE(F3) key then the E key. Then locate word +101 by pressing LOCATE(F3) followed by +101. Finish with the trigger word at the top of the CRT by pressing the LOCATE(F3) and T keys.

### 2.3.4.1 Saving Data

To test the SAVE mode, press the LABELS key in the top row. Perform the SAVE function by pressing the S key. This action causes the entire data collection, the test codes (SIG), and the menu parameters to be stored in the NPC 764 auxiliary RAM memory. Press

the MEMSEL(M) key to cause the auxiliary memory to be displayed. Press M again to return the main memory to the screen.

### 2.3.4.2 HOLD≠ MODE

The HOLD≠ mode is used to detect and isolate intermittent faults. Press the # key (SHIFT and 3) to activate the HOLD≠ mode. Note that the flashing status messages indicate the analyzer is automatically collecting and comparing main and auxiliary data.

Hold the shorting wire on pad 5 on the right-hand side (B side) of the test card. Note that the flashing status message now reads HOLDING, and data are displayed. Remove the shorting wire from pad 5.

Press the M key to compare main and auxiliary test codes. Notice that one of the main memory test codes differs from the corresponding auxiliary memory test code. This indicates that somewhere in the new data collection, one or more bits differ

Figure 2-10 Hexademical Format Screen

```

祖堂

+827

000 091 216 027 255 255

+828 890 092 856 828 255 255

+029 000 093 184 029 255 255

+030 000 094 120 030 255 255

SIG: C1E7 +031 989 995 248 831 255 255

79E7 +032 806 096 008 008 255 255

DBD3 +033 900 997 128 001 255 255

969 898 964 962 255 255

+034

HOLD# MODE +035 808 899 192 003 255 255

+336 898 199 832 984 255 255

+337 000 101 160 005 255 255

DIFFERENCE +333 008 102 096 066 255 255

+369 000 103 224 007 255 255

+343 808 184 816 888 255 255

+341 898 185 144 989 255 255

+342 | 000 106 000 010 255 255

±343 808 107 208 011 255 255

÷344 000 108 048 012 255 255

+345 898 109 176 913 255 255

+346 898 118 112 014 255 255

```

### LABELS

| SCRL DAN   | SCR  | LUP       | LOCATE   | SR                    | CAM K    | CONFIG    | COLLECT  |

|------------|------|-----------|----------|-----------------------|----------|-----------|----------|

|            | Figu | re 2-1    | l Diff   | erence                | Menu S   | Screen    |          |

| MAIN       | +827 | 90060008  | 91911911 | 11011200              | 80611011 | 111111111 | 11111111 |

|            | +928 | 60969696  | 01011190 | 99111999              | 00611160 | 111111111 | 11111111 |

| LOC:       | +829 | 99989999  | 01611101 | 19111969              | 00011101 | 111:1111  | 11111111 |

|            | +838 | 69999669  | 01011110 | 01111000              | 00011110 | 11111111  | 11111111 |

| SEG: C1E7  | +831 | 69696969  | 01011111 | 11111860              | 000:1111 | 11111111  | 11111111 |

| ?9₹7       | +032 | 98999368  | 81199988 | 9 <del>839</del> 3988 | 2030393  | 11111111  | 11111111 |

| D8D3       | +633 | 58998988  | 01188881 | 10000000              | 10000099 | 11111111  | 11111111 |

|            | +934 | 8888888   | 01166819 | 81888988              | 88000018 | 11111111  | 11111111 |

|            | +635 | 68666668  | 81169611 | 11000000              | 88868811 | 11111111  | 11111111 |

|            | -03E | 9999999   | 91199108 | 89899189              | 90900100 | 111111111 | 11111111 |

|            | -637 | 89888689  | 01100101 | 10100000              | 90999191 | 11111111  | 11111111 |

| DIFFERENCE | -038 | 90000000  | 91100110 | 81100000              | 80909118 | 11111111  | 11111111 |

|            | -039 | 96966668  | 81160111 | 11109099              | 88889111 | 11111111  | 11111111 |

|            | -040 | 9888888   | 81101698 | 66919000              | 90801080 | 11111111  | 11111111 |

|            | -041 | 00000000  | 81181881 | 18016000              | 80801001 | 11111111  | 11111111 |

|            | -842 | 909090998 | 91181916 | 81819000              | 90601919 | 111111111 | 11111111 |

|            | -0:3 | 90000000  | 91101011 | 11818888              | 80801011 | 11111111  | 11111111 |

|            | -614 | 86999668  | 81101106 | 60116006              | 00001190 | 11111111  | 11111111 |

|            | -816 |           |          |                       |          | 11111111  |          |

|            | -846 |           |          |                       |          | 11111111  |          |

LABELS

SCRL DAN SCRL UP LOCATE SRCH HRD CONFIG COLLECT

Figure 2-12 Binary Difference Screen

between the main and auxiliary memories. Now return to the main memory.

### 2.3.4.3 Difference Mode

The DIFFERENCE mode is used for rapid identification of differences between and previously-saved auxiliary memory data and main memory.

Press the / key to activate the DIFFERENCE mode. This key toggles the DIFFERENCE mode so that repeated keystrokes turn it on and off. In this mode, only data words that differ between the main and auxiliary memories are displayed at full-intensity. Data words that match are displayed at half-intensity. Press the SCRL UP(F2) key to find the first difference word. (Simultaneously press the REPEAT key if desired). Refer to Figure 2-11.

Press the N key to view the difference in binary. Then press M and REPEAT to locate the specific bits responsible for the differences. Refer to Figure 2-12.

Return to the main memory and press the H key. Press LOCATE(F3) followed by D to place the first difference word at the top of the screen. This is an alternative and faster way of locating the first difference word. Now press LOCATE followed by S to find the next group of half-intensified words that are the same. Press the SCRL DWN key once to verify this. Refer to Figure 2-13.

Press LOCATE followed by T to place the trigger word at the top of the CRT. Then press the / key to disable the DIFFERENCE mode.

### 2.3.4.4 Search Word Mode

The SEARCH WORD mode allows you to locate any particular bit pattern within a data collection. You specify the word to search for and then the direction of search.

Press the SRCH WRD(F4) key to obtain the menu shown in Figure 2-14.

In the example, 009E is used as the word to be found in the data collection. (NOTE: This word occurs only once in the data memory). Key in 0-0-9-E (the rest of the field are X's - DON'T CARE). Press S2 to display the data again, then press K to search the data for 009E. Refer to Figure 2-15.

### 2.3.5 BASIC TIMING TEST

To test the basic timing analysis capabilities of the NPC 764 do the following:

- a. Select the menu.

- b. Choose a sampling clock and a trigger point.

- c. Press the COLLECT(F6) key.

Before starting this test, disconnect the M51A state probes from the test card. Connect the two A and B Model 80 Timing Probes to the NPC 764. Then connect these probes to the test card A and B outputs, respectively. The state probes may be left connected to the NPC 764. Proceed as follows:

- a. Press the F5 key to return to the Configuration List.

- b. To select the 16-CHANNEL TIMING mode, press the SEL DOWN(F4) key. Call the menu with the TIMING(F1) key.

- c. Use the PREVIOUS(F1) or NEXT(F2) key to step to the CLOCK field, if necessary. An external clock with a rising edge is selected by pressing P. Use the NEXT(F2) key to step to the TRIGGER field. Specify a trigger word of 0-0-0-0-0-0-0-0 1-0-0-1-1-0-0-0. Use the NEXT key to step down to the PRETRIGGER field. Set this field to 00%. Leave all other menu entries set at the default value as shown in Figure 2-16.

```

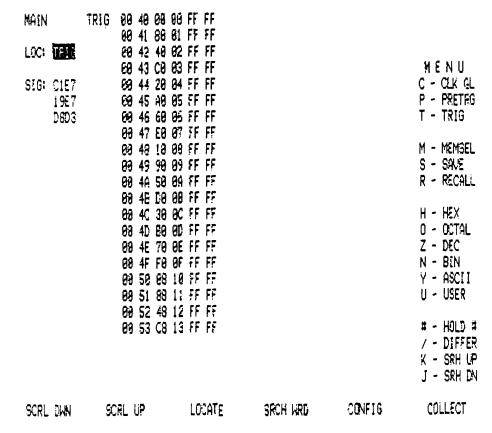

MAIN

+864 98 88 82 48 FF FF

+865 08 81 82 41 FF FF

LOC: ### +065 08 82 42 42 FF FF

±067 80 83 C2 43 FF FF

SIG: CIE? +068 90 84 22 44 FF FF

79E7 +069 80 85 A2 45 FF FF

DBD3 +879 90 86 62 46 FF FF

+071 90 87 E2 47 F5 5F

+072 00 88 12 48 FF FF

+073 80 89 92 49 FF FF

+874 88 8A 52 4A FF FF

DIFFERENCE +075 00 88 D2 48 FF FF

+076 00 80 32 40 FF FF

+977 00 80 82 4D FF FF

+078 00 8E 72 4E FF FF

+079 00 8F F2 4F FF FF

+880 80 90 0A 50 FF FF

+081 00 91 8A 51 FF FF

+082 00 92 4A 52 FF FF

+083 00 93 CA 53 FF FF

```

LABELS

SCRL DAN 9CRL UP LOCATE SRCH WRD CONFIG COLLECT

Figure 2-13 First Difference Word

FURMET: AGRAGADA GAGAGADA AGRAGADA AGRAGADA AGRAGADA ARAGADADA A HEX

SEARCH WORD:

889EXXXXXXXX

H - HEX

U - OCTAL

Z - DEC

N - BINARY

Y - ASCII

S2 - DATA DISPLAY

U - USER

PREVIOUS NEXT SELECT DEFAULT CONFIG COLLECT

Figure 2-14 Search Word

```

MAIN

+094 00 9E 7A 5E FF FF

+895 00 9F FA 5F FF FF

LOC:

+896 88 A8 82 48 FF FF

+097 88 A1 82 41 FF FF

SIG: CIE7 +099 88 A2 42 42 FF FF

79E7 +099 88 A3 C2 43 FF FF

D8D3 +100 88 A4 22 44 FF FF

+181 88 A5 A2 45 FF FF

+182 88 A6 62 46 FF FF

+163 98 A7 E2 47 FF FF

+184

00 A8 12 48 FF FF

DIFFERENCE +185 88 A9 92 49 FF FF

+186 88 AA 52 4A FF FF

+187 88 A8 D2 48 FF FF

+168 88 AC 32 4C FF FF

+169 86 AD B2 4D FF FF

+119 88 AE 72 4E FF FF

88 AF F2 4F FF FF

+111

+112 80 80 8A 50 FF FF

+113 96 BI 8A 51 FF FF

```

LABELS

SCRL DAN SCRL UP LOCATE SRCH WRD CONFIG COLLECT

> Figure 2-15 Difference Menu Screen 16 CHAL TEMENG/STATE MENU

EXT I CLOOK CLK GUAL: X

TRIGGER WHEN:

TRIG OCCURS ) 8888 CLOCKS AFTER FIRST ARM CHAL NO. A76543218 B76543218 FILTER LINKAGE

ARM (B, I,X):

XXXXXXXX XXXXXXXX OFF NOVE

TRIS (9,1,X):

00000000 10011000 OFF NONE

INPUT MODE (S.L): PRE-TRIGGER (0-9): BOX

SSSSSSSS SSSSSSSS

DISPLAY ORDER (0-7.X):

BBBBBBB AAAAAA 76543218 76543218

DISPLAY POLARITY (+,-): +++++++ THRESHOLD:

A PROBE 8 PROBE

HYSTERESIS (-6.40 - +6.350)+1.69 +1.60 ON

SI - STATE DISPLAY 52 - TIMING DISPLAY

PREVIOUS NEXT

CONFIG

COLLECT

Figure 2-16 16 Channel Timing Menu

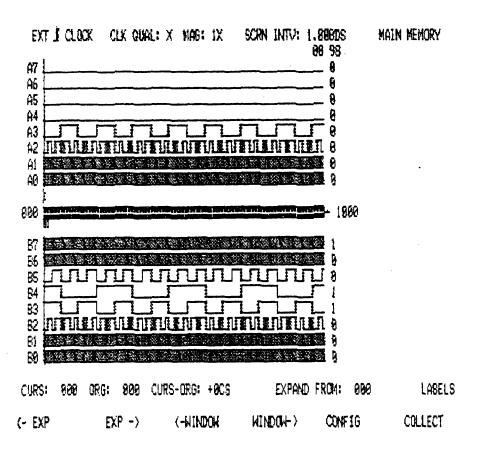

- d. Press COLLECT(F6) key. When a data capture is complete, the screen fills with the timing diagram display. Refer to Figure 2-17.

- e. The inverse video graticule represents the entire 1000 samples in the memory. See Figure 2-17. Observe the 00 indicator at the left end of the graticule is intensified. This indicates the 00% pre-trigger value set in previously. With 00% pre-trigger, the first word in the data collection (word 000) is the trigger word. The cursor reads the binary and hexadecimal values of each location in the data memory where the cursor is placed. Thus, the trigger word at cursor location 000 should be (0098) HEX. In Figure 2-

- 17, this trigger word appears at the upper right-hand corner of the CRT.

- f. Figure 2-17 also shows the 16 timing channels and the corresponding binary values at cursor location 000. The four most significant A channels (A7-A4) are at ground as described previously. The cross-hatched areas on certain channels indicate that data in the memory are occurring too close together. The current X1 magnification factor is unable to resolve this visually.

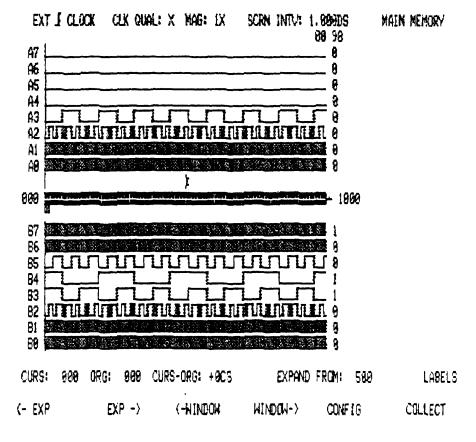

- g. Sweep the expansion symbol, E, to wards the middle of the CRT by pressing F2 and REPEAT. Stop the symbol at location 500 as indicated by the EXPAND FROM: readout in the

Figure 2-17 Timing Diagram Display

lower right-hand portion of the CRT. Refer to Figure 2-18.

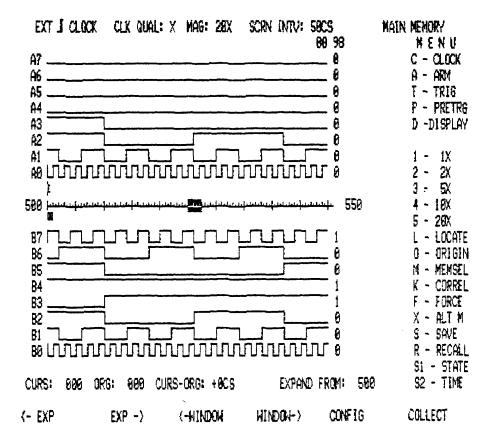

- Next press the LABELS key. Try magnification factors between 2X to 20X using the 2 to 5 numeric keys as indicated in the LABEL MENU. After higher magnification keys are pressed, the inverse video indicator at the bottom of the screen reduces proportionately in size. This indicator shows the location and amount of timing data currently being displayed relative to the entire 1000-word data collection. At 20X magnification, note that the inverse video indicator is only 5% of the original (1X) size. The screen now displays timing data between memory locations 500 and 550. Re-

- fer to Figure 2-19. Finish by setting the magnification at 10%.

- i. View other segments of the memory by pressing the WINDOW(F3) or the WINDOW (F4) keys and the REPEAT key simultaneously. Return to a data window of 500 to 550 as shown in Figure 2-19. Also return the expansion symbol to the left-hand side of the CRT.

- j. To quickly move the cursor from 000 to the left side of the screen interval, press the L (LOCATE CURSOR) key. This is indicated in the LABELS menu. Bring the cursor to the center of the CRT by pressing the SPACE BAR and the REPEAT keys simultaneously. Overshoot can be

Figure 2-18 Timing Display at Location 500

lower right-hand portion of the CRT. Refer to Figure 2-18.

- Next press the LABELS key. Try magnification factors between 2X to 20X using the 2 to 5 numeric keys as indicated in the LABEL MENU. After higher magnification keys are pressed, the inverse video indicator at the bottom of the screen reduces proportionately in size. This indicator shows the location and amount of timing data currently being displayed relative to the entire 1000-word data collection. At 20X magnification, note that the inverse video indicator is only 5% of the original (1X) size. The screen now displays timing data between memory locations 500 and 550. Refer to Figure 2-19. Finish by setting the magnification at 10X.

- i. View other segments of the memory by pressing the WINDOW(F3) or the

- WINDOW (F4) keys and the REPEAT key simultaneously. Return to a data window of 500 to 550 as shown in Figure 2-19. Also return the expansion symbol to the left-hand side of the CRT.

- j. To quickly move the cursor from 000 to the left side of the screen interval, press the L (LOCATE CURSOR) key. This is indicated in the LABELS menu. Bring the cursor to the center of the CRT by pressing the SPACE BAR and the REPEAT keys simultaneously. Overshoot can be remedied by pressing the BACKSPACE key.

- k. In this step we will measure the relative time between the edges in two channels. Visually select an edge (rising or falling) in channel A2 and another edge (later in time) in channel B6. Step the cursor so that it aligns with the selected

Figure 2-19 Timing Display and Menu

- edge in Channel A2. Note the value of the cursor position indicator at the lower left of the screen. Now press the letter 0 to reset the origin from 000 to the current cursor location. The CURS-ORG indicator should now read +OCS. where CS stands for clock samples. When an internal clock is being used, the indicator reads in units of time. Next, step the cursor to the selected edge on channel B6. The CURS-ORG indicator will now directly read the time (in clock samples) between these two edges. Figure 2-20 demonstrates one sample using this measurement procedure.

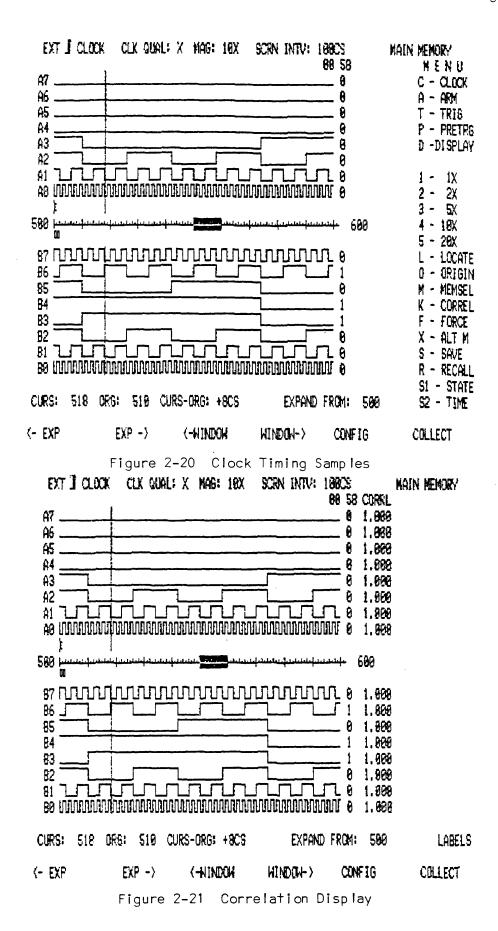

- Press the COLLECT key to take a new data collection. Then press the SAVE(S) key and observe the flashing SAVED message. To compare main and auxiliary data press K(CORREL) key. Note that a correlation factor of 1.000 is displayed at the right of each channel. This factor indicates that the 1000 bits in each main memory channel compares with the 1000 bits in the corresponding auxiliary memory channel. Comparisions are done on a bit-forbit basis. Refer to Figure 2-21. Thus, if a correlation factor of .995 were displayed, it would indicate that 5 bits out of 1000 were different.

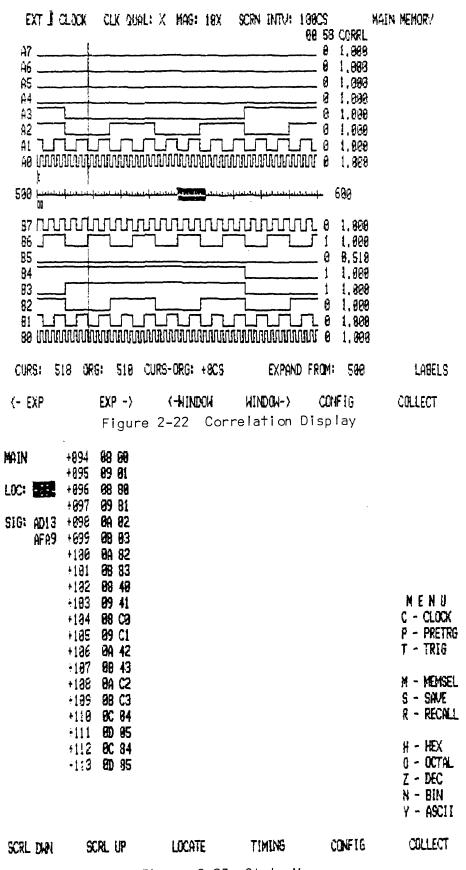

- m. Now short out the pad labeled 5 on the B side of the test card. While holding the short in place, press COLLECT. Now remove the short. To see which channel was affected by the short, again press K. Note that the correlation factor for channel B5 is significantly lower than 1.000. The other channels still have correlation factors of 1.000. This results from the use in this example of an external, synchronous clock from the test card. If the internal, asynchronous clock were used, the correlation factors of the other channels would probably never be exactly 1.000. This is due to normal sampling uncertainties.

- n. In order to view the actual effect of the short on channel B5, press the X(ALT MEMORY) key. As shown in Figure 2-22, channel B5 should cycle between a 1 and a 0. Return to the main memory by pressing M. Also return to a 1X magnification by pressing the 1 key.

To view the timing data in a state format, press \$1. The state data can be displayed in HEX, OCTAL, DECIMAL, BINARY or ASCII. Refer to Figure 2-23. Press the LABELS key to display the menu of formats available in this mode. Return to the timing diagram display by pressing \$1 again.

Figure 2-23 State Menu

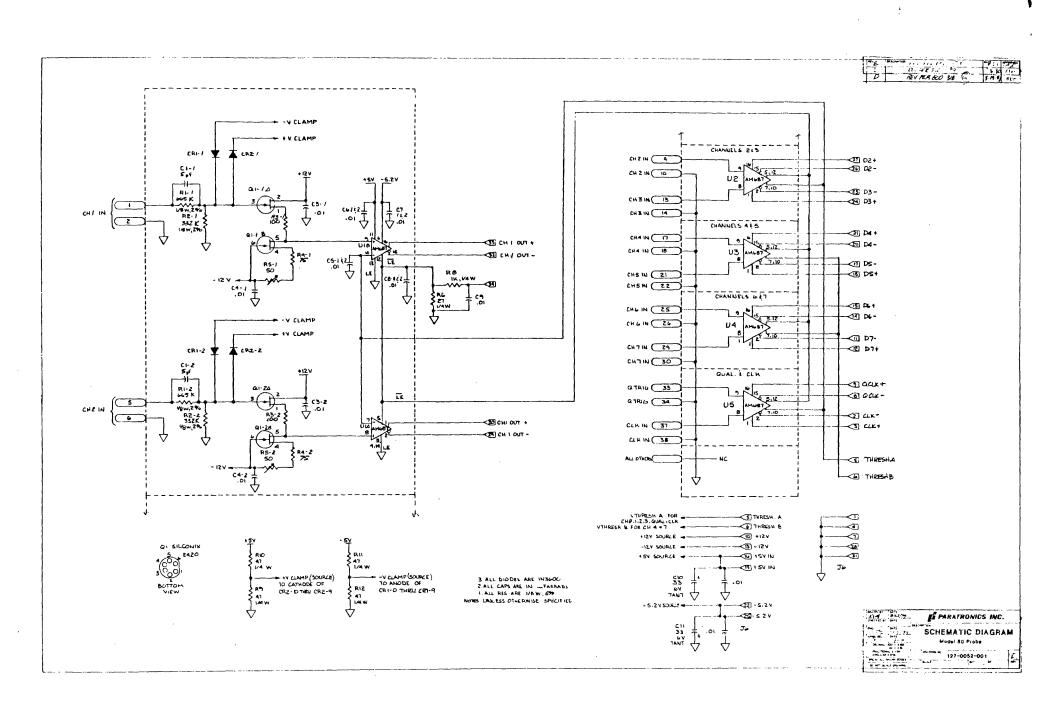

PARENT LIFE CRUSS FOR TITE 143-0045-0062

PESC- IPTION LUGIC ANALYZER DEMO CAPO ENGR JRA4 281 0 ..

BATCH DIY 1 ITEM TYPE 1 LOW LEVEL 03 EFF°C 12/08/H2 UNIT MEAS FA PLANNER

| MSR<br>FF |              | COMPUNENT & CRUSS NEF. | OESCRIPTION & COMMENT               | ENGINEERING<br>DRAWING NUMMER | JUANTITY<br>PEP |      | T F M | OPT<br>NER | FIRST<br>CP SEO | LT | EFFECTIVE CATES |

|-----------|--------------|------------------------|-------------------------------------|-------------------------------|-----------------|------|-------|------------|-----------------|----|-----------------|

|           | do           | 110-0005-0031          | 47 UPM 1/4W 5% CH PES<br>92 - R3    |                               | 0000            | E A  | 4C    |            |                 |    | 2/25/90         |

|           | 7)6          | 110-0005-0037          | 100 JHM 1/4W 5% CF RFS              |                               | 1.000           | £ A  | 40    |            |                 |    |                 |

|           | 75           | 113-0005-0087          | 10K 2H7 1/4W 5% CF RES <sub>1</sub> |                               | 1.000           |      |       |            |                 |    |                 |

|           | () ប         | 111-3304-0066          | -01 UF 25V CO CAP                   |                               | 1.000           | F A  | 4C    |            |                 |    |                 |

|           | ിഠ           | 111-6006-0650          | • 001 UF 50V CD CAP                 |                               | 1.000           | i: V | 4 C   |            |                 |    | 2/25/90         |

|           | .)4          | 113-0023-0001          | 1.C. 094520<br>U2 U5                |                               | 2.000           | E A  | 40    |            |                 |    | 2/25/90         |

|           | 74           | 113-0039-0001          | 1.C. C04011<br>U1 U4                |                               | 2.000           | FΑ   | 40    |            |                 |    | 2/25/BU         |

|           | ) +          | 113-0046-0001          | 1.C. 014002                         |                               | 1.000           | f A  | 40    |            |                 |    | 2/25/90         |

|           | 15           | 117-0115-0001          | BUMPER RUBBER STEM 322-2            |                               | 4.000           | FΑ   | 4C    |            |                 |    | 2/25/8G         |

|           | 57           | 117-0002-0001          | SHEINK TUBE, 1/3 WHITE              |                               | 1.000           |      | 4C    |            |                 |    | €/24/80         |

|           | 1) 4         | 114-0055-0032          | #25 NWG STRANDED WIRE BLK 4.5       |                               | 1.000           | FA   | 4 C   |            |                 |    | 1/15/81         |

|           | ) · <b>+</b> | 126-0046-0001          | LUDIC ANALYZER DEMO CARD PCB        | ECO 160 RFV 2                 | 1.000           | FΑ   | 4C    |            |                 |    | 2/25/80         |

|           | ) 4          | 127-3046-0001          | DEMO CARD PCH SCHEMATIC             |                               | •000            | FΛ   | 0     |            |                 |    | 2/10/92         |

# CHASSIS, MOTHERBOARD, POWER SUPPLY, DISK DRIVE

# SECTION 3: CHASSIS, MOTHERBOARD, POWER SUPPLY, DISK DRIVE

|     |                                           | PAGE                      |

|-----|-------------------------------------------|---------------------------|

| 3.1 | Introduction                              | 3-1                       |

| 3.2 | Chassis Description                       | 3-1                       |

| 3.3 | Motherboard Functional Description        | 3-4                       |

| 3.4 | Power Supply Functional Description       | 3-6                       |

|     | 3.4.1 Test Set-Up                         | 3-6<br>3-8<br>3-9<br>3-10 |

| 3.5 | Disk Drive Removal                        | 3-11                      |

| 3.6 | Schematics, Board Layouts and Parts Lists | 3-11                      |

## SECTION III CHASSIS, MOTHERBOARD, POWER SUPPLY AND DISK DRIVE

#### 3.1 INTRODUCTION

Refer to the schematic diagrams, board layouts, interconnection diagram, and the parts lists located at the end of this section. Tables of connector pins versus signals names for all motherboard connectors are provided in the SIGNAL AND INTERCONNECTION TABLES section. An alphabetical list of all interboard signals is included. The GLOSSARY offers explanations for acronyms or terms that may be unfamiliar.

### 3.2 CHASSIS FUNCTIONAL DESCRIPTION

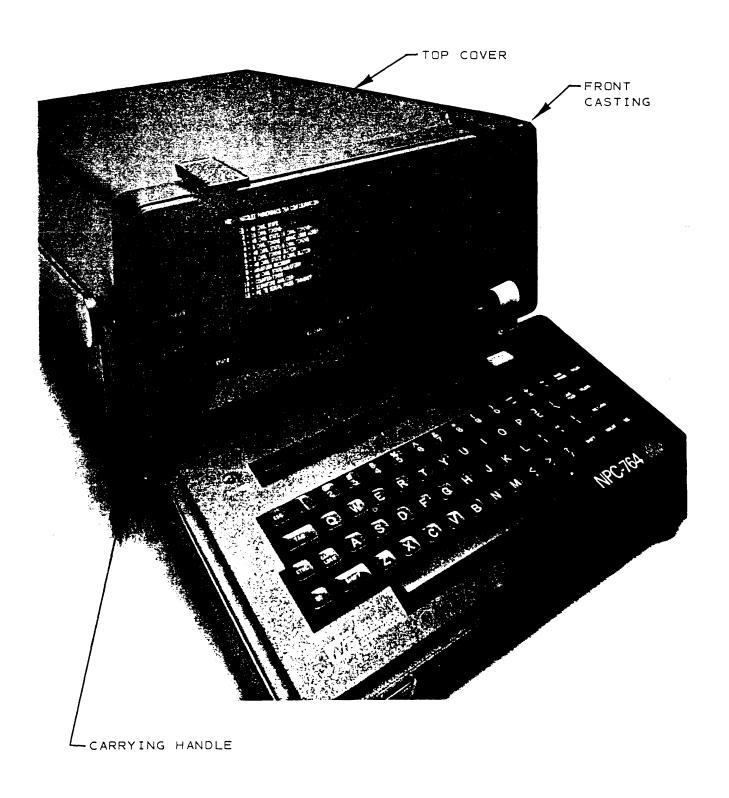

The chassis provides the supporting structure for the Front Bezel, the Display Module, the Card Cage Assembly, the Rear Panel and Power Supply. The top cover, a part of the chassis, gives complete protection to the internal components and adds structural strength to the complete assembly.

The units that will be discussed as part of the chassis group are the following: The chassis, the cover, the carrying handle, the Mains Module, the auxiliary power transformer, the cooling fan, and the interconnecting wiring.

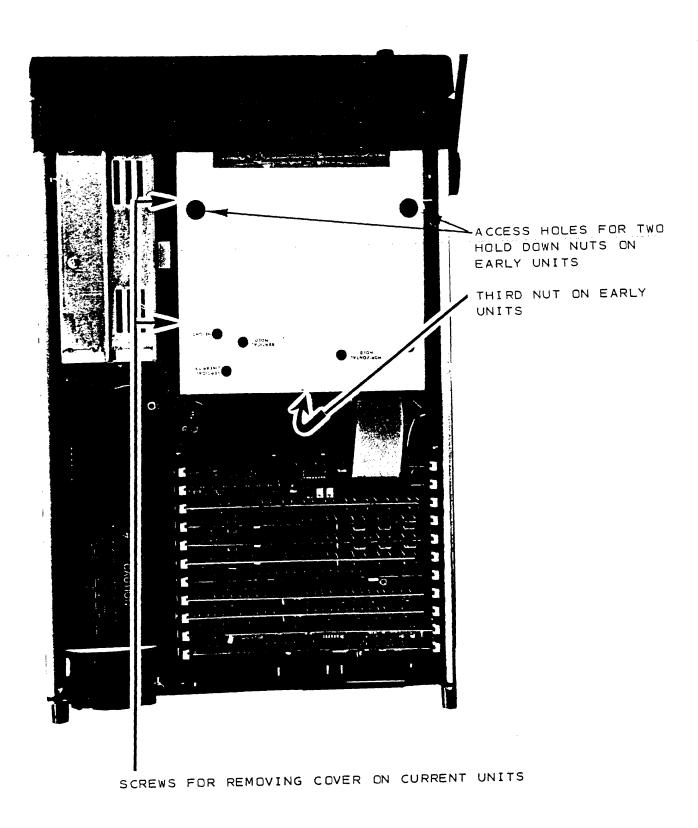

Refer to Figure 3-1. The Chassis consists of an aluminum bottom pan that mounts the front casting, rear panel, and extrusion rails. The front casting is joined to the rear panel by the longitudinal extrusion rails. The rails accept the side edges of the cover and bottom pan. There is a large rectangular hole in the front casting through which the CRT screen is viewed. A plastic face plate is attached directly to the CRT tube. The face plate protects the CRT and is lightly tinted to enhance the contrast of the display.

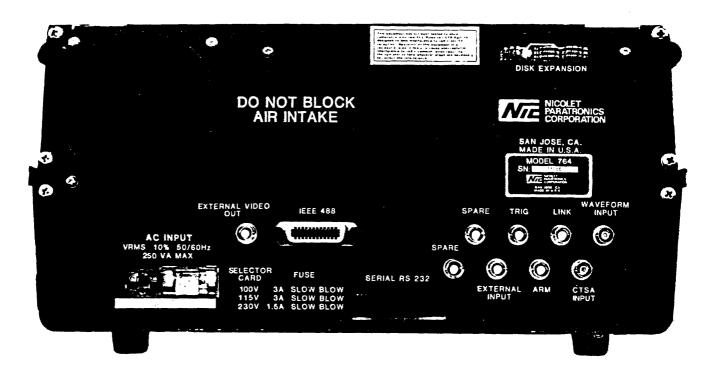

The shielded Display Module is mounted to the bottom pan by three threaded studs set

into the bottom pan. The Card Cage Assembly is mounted to the bottom pan by three screws through the bottom pan. The cooling fan fastens to the rear panel by three screws through the rear panel. The auxiliary power transformer fastens to the rear panel by nuts on two threaded studs set into the rear panel. The Mains Module mounts into a rectangular hole in the rear panel with snap-in fasteners. The BNC connectors, Serial and GPIB connectors mount onto the card cage and project through openings in the rear panel.

DISCONNECT THE A-C POWER CORD AT THE BACK OF THE CHASSIS BEFORE REMOVING THE COVER. THE DISPLAY MODULE CONTAINS A VERY HIGH VOLTAGE OF 9 KV THAT CAN BE LETHAL. EXTREME CAUTION MUST BE USED WHENEVER POWER IS APPLIED TO THE NPC 764 WITH THE COVER REMOVED.

The cover folds around the top and half way down the sides of the instrument. It fits into grooves in the extrusion rails. Clips that fit under the front casting secure the front of the cover. The cover is held in place at the rear by two quarter-turn fasteners that mate into fittings in a flange on the rear panel.

The carrying handle attaches to the extrusion rails. When the analyzer is in use, the handle can be folded underneath to act as a stand. This props up the front of the instrument so the keyboard is at a convenient height.

The Mains Module is mounted in a rectangular cutout in the rear panel. It is held in place by snap-in fasteners attached to the sides of the module. Refer to the chassis wiring diagram.

Figure 1-1 MPC 754 Logic Analysis System

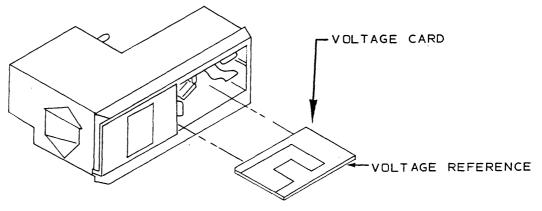

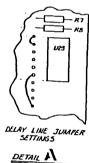

A Voltage PCB in the Mains Module allows selection of the power mains voltage for the instrument. The sliding cover for this Voltage PCB can be opened only when the power cord is unplugged from the module.

Voltage designators are etched in copper near the edges of the Voltage PCB. The voltage designator programmed by the PCB is visible on the rear edge when the board is in place. Refer to Figure 3-2.

SELECT:

100 V NOMINAL

115 V NOMINAL

230 V NOMINAL

AS APPROPRIATE

NOTE: THE CARD MUST BE DRIENTED SO THAT THE SELECTED VOLTAGE CAN BE READ WITH THE CARD INSTALLED.

Figure 3-2 Rear Panel and Voltage Select Card

BEFORE APPLYING POWER TO THE NPC 764, MAKE CERTAIN THAT THE PROGRAMMED MAINS VOLTAGE CORRESPONDS TO THE VOLTAGE BEING USED. OTHERWISE, SERIOUS DAMAGE TO THE INTERNAL POWER SUPPLY MAY RESULT.

To change the voltage programmed, remove the PCB, change the orientation, and reinsert it. The voltages available for selection are shown in Table 3-1.

The power-mains fuse is located on the Mains Module just above the Voltage PCB. The rating of the fuse depends on the voltage programmed. The required fuse ratings are included in Table 3-1.

Table 3-1 Power Source Requirements

| Selector | Operable | Fuse                                    |

|----------|----------|-----------------------------------------|

| Card     | Range, V | Req'd                                   |

| =======  | ======   | ======================================= |

| 100 V    | 90-110   | 3 AMP Slow Blow                         |

| 115 V    | 105-125  | 3 AMP Slow Blow                         |

| 230 V    | 210-250  | 1.5 AMP Slow Blow                       |

The auxiliary transformer is mounted on two threaded studs set into the rear panel just above the Mains Module. The primary of this transformer acts as an autotransformer. It supplies a nominal 115 VAC to the fan motor regardless of the programmed mains voltage. The secondary supplies 17 VAC to the Power Supply for an auxiliary supply circuit, also independent of the mains voltage.

The cooling fan is mounted in a 4-inch round, air-intake hole in the rear panel. This hole is covered by a replaceable air filter. The fan motor is supplied with 115 VAC power from the auxiliary transformer. There are air vent slots in the cover for air exhaust. The fan draws air in through the rear panel air filter and exhausts it from

these vents. This air flow lowers operating temperatures within the cabinet to safe levels. The air filter can be removed by loosening the three screws holding the filter retaining clips. The filter should be cleaned by washing in soapy water monthly (more often in dirty environments).

IF THE FAN IS NOT FUNCTIONING, OR IF THE AIR FILTER IS DIRTY OR OTHERWISE OBSTRUCTED, DO NOT OPERATE THE NPC 764. DOING SO MAY RESULT IN SERIOUS DAMAGE TO COMPONENTS THROUGHOUT THE INSTRUMENT.

The interconnecting wiring is shown in the wiring diagram at the end of this section. All interconnections to the Display Module, Card Cage assembly, Front Panel, and Power Supply are made through connectors. Any of these units can be removed without unsoldering wires.

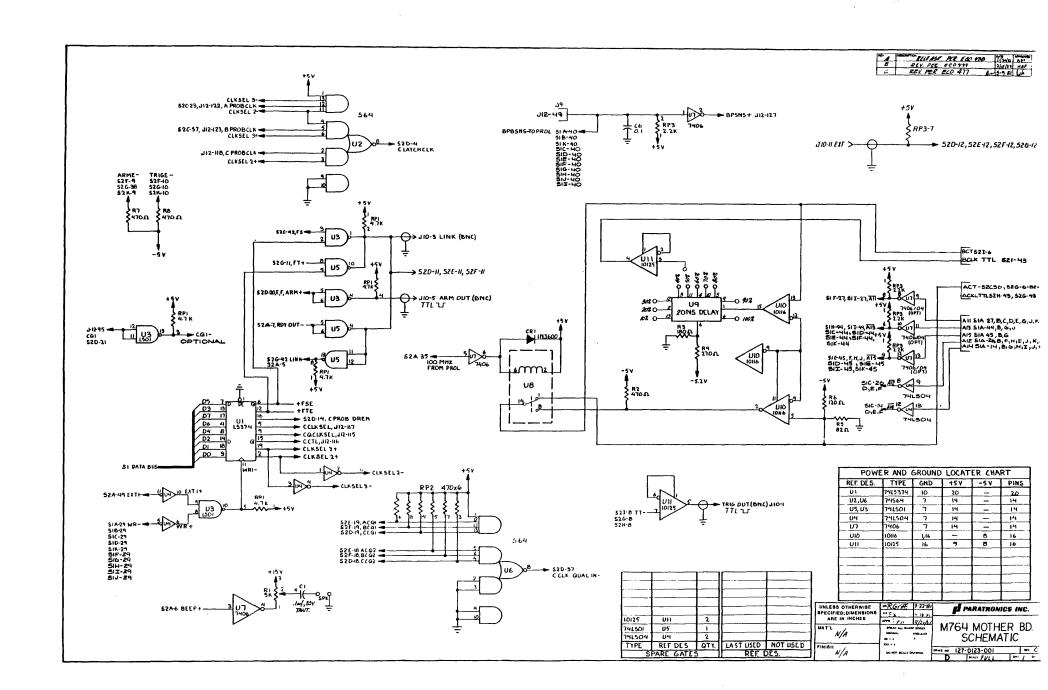

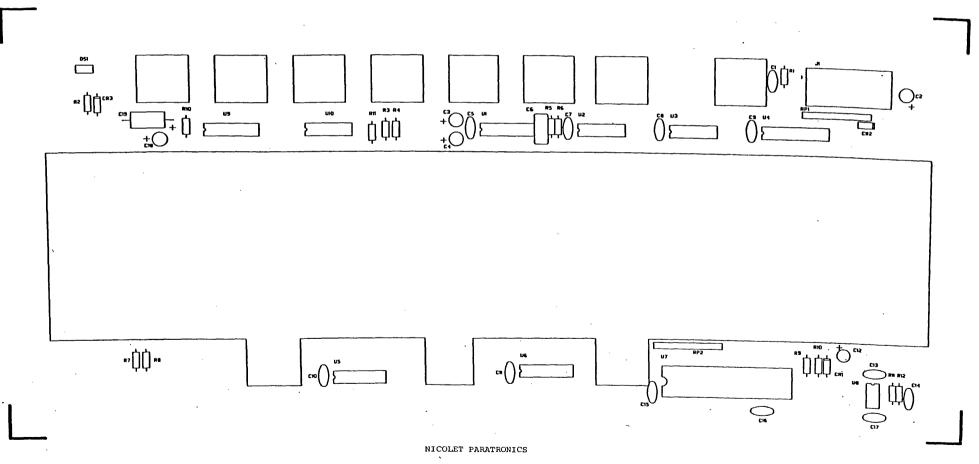

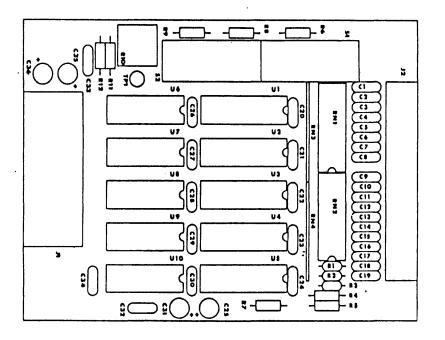

### 3.3 MOTHERBOARD FUNCTIONAL DESCRIPTION

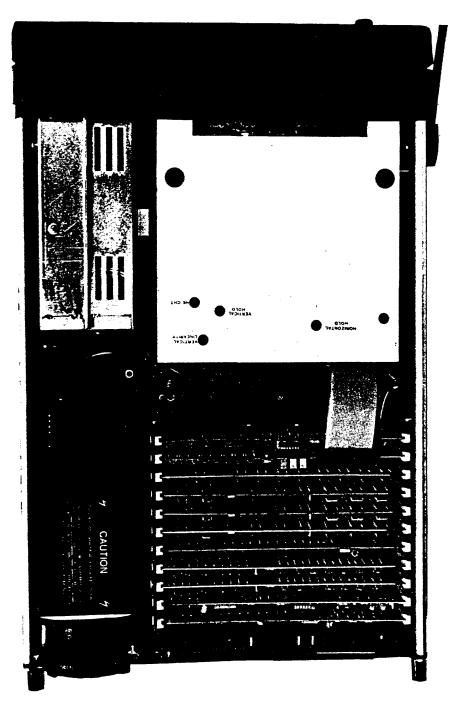

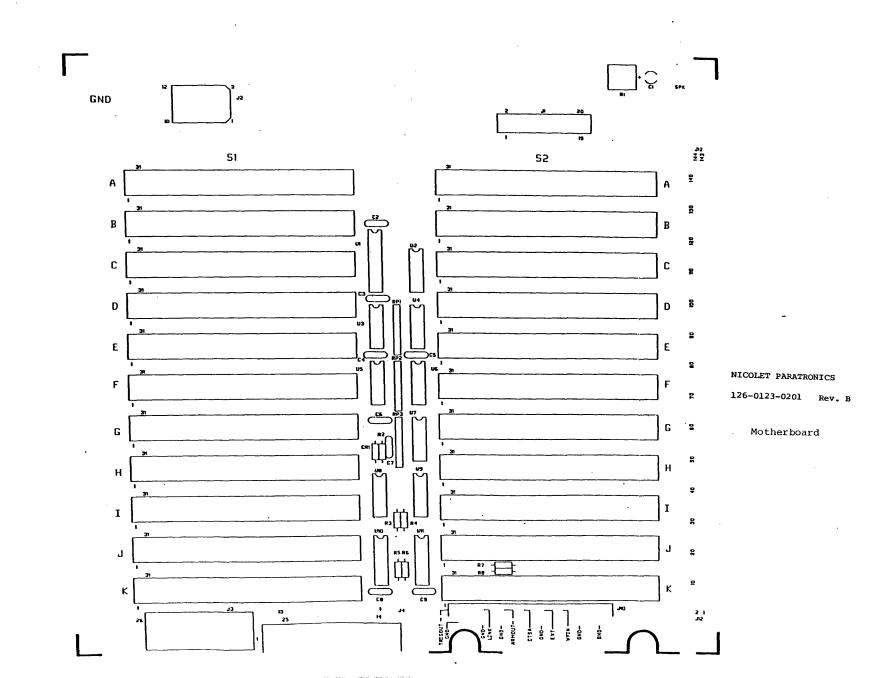

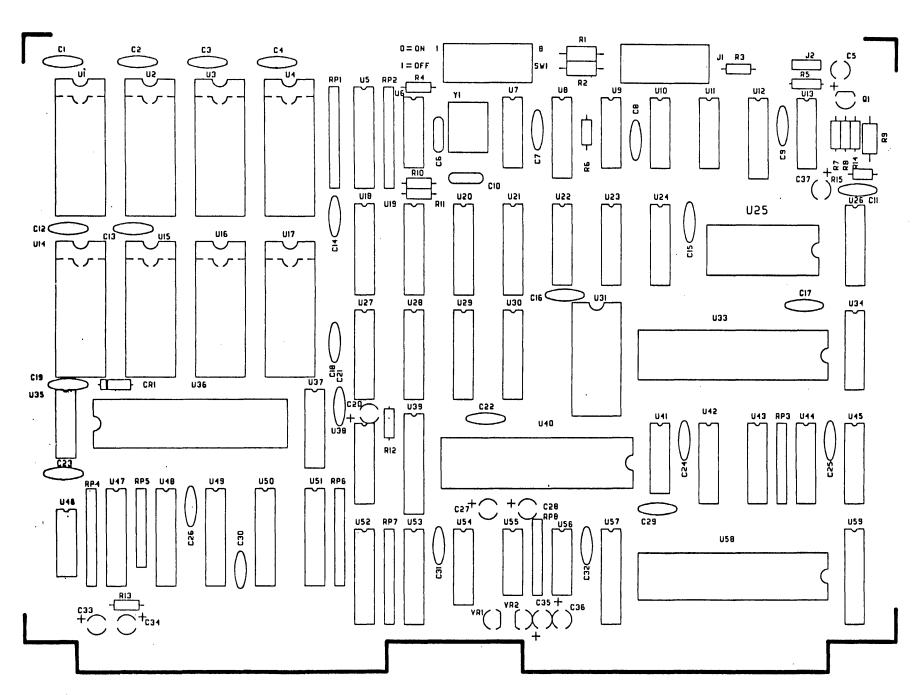

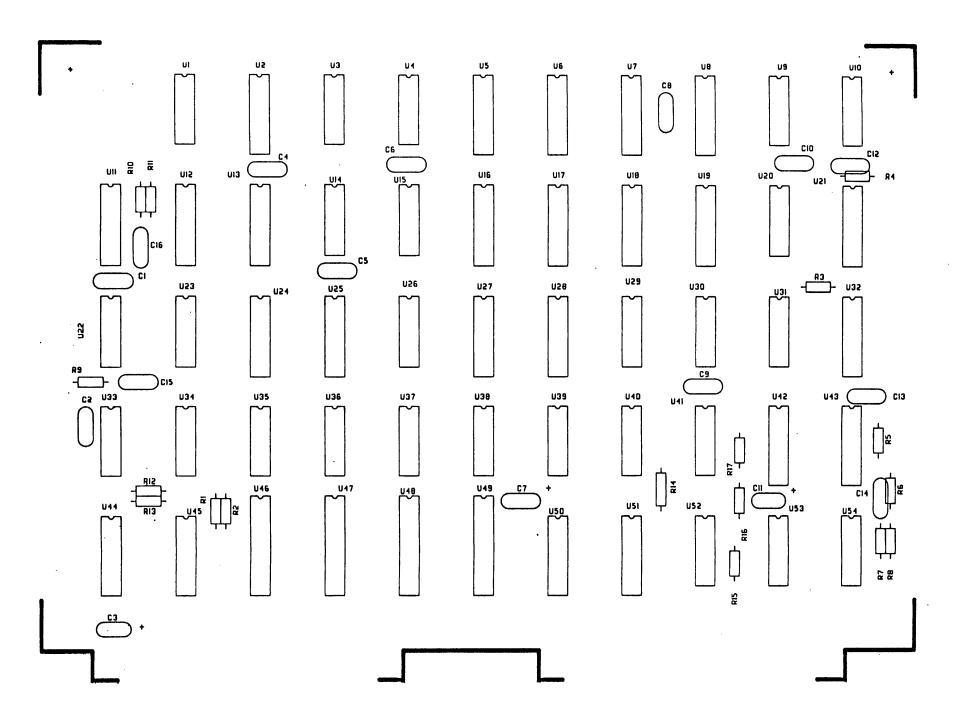

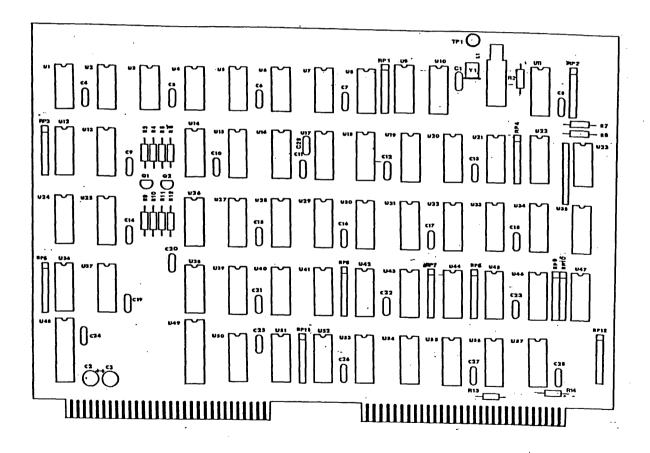

A Motherboard in the NPC 764 contains sockets, card guides and supporting structure for the individual PC boards. Refer to Motherboard schematic #127-0123-001 and the board layout drawing #126-0123-001. The Motherboard contains sockets, card guides and interconnections for 11 circuit boards. The slot assignments for individual PC boards are fixed and boards are keyed to interface only into the correct slots. Refer to Figure 3-3.

DO NOT ATTEMPT TO FORCE A PCB INTO AN INCORRECT SLOT OR DAMAGE TO THE CONNECTOR OR PCB MAY RESULT.

| SLOT   | CIRCUIT BOARD                           |

|--------|-----------------------------------------|

| ====   | ======================================= |

| F RON1 |                                         |

| A      | Processor                               |

| В      | RAM DISK                                |

| С      | State Control                           |

| D      | State Memory-C (LSB)                    |

| Ε      | State Memory-A (MSB)                    |

| F      | State Memory-B                          |

| G      | Timing Control                          |

| Н      | Timing Memory-A                         |

| I      | Timing Memory-B                         |

| J      | Waveform                                |

| K      | Counter-Timer/SA                        |

|        |                                         |

The location and part numbers of the boards are listed below:

| SLOT  | CIRCUIT BOARD                           | PART NUMBER  |

|-------|-----------------------------------------|--------------|

| ====  | ======================================= | =========    |

| FRONT | Γ                                       |              |

| Α     | Processor                               | 143-0130-001 |

| В     | RAM DISK                                | 143-0112-001 |

| С     | State Control                           | 143-0128-001 |

| D     | State Memory-C (LSB)                    | 143-0127-001 |

| E     | State Memory-A (MSB)                    | 143-0127-001 |

| F     | State Memory-B                          | 143-0127-001 |

| G     | Timing Control                          | 143-0071-001 |

| H     | Timing Memory-A                         | 143-0065-003 |

| !     | Timing Memory-B                         | 143-0065-004 |

| J     | Waveform                                | 143-0072-001 |

| K     | Counter-Timer/SA                        | 143-0099-001 |

| REAR  |                                         |              |

Note that the three State Memory boards are identical and may be interchanged. The two timing Memory boards contain different decoded PROMs U52. The PROM marked 113-4035-14 is required for the A Timing Memory board in slot H. The PROM marked 113-4035-15 is required for the B Timing memory board in slot I.

The Clock Qualifier Gate (U6) and the Clock Multiplexer (U2), both part of State Control, are contained on the Motherboard. These circuits are described in the STATE CONTROL BOARD section. Additional circuitry (U1, U3, U5, U7) interfaces the link control signals and provides additional clock selection control. Components U4, U7, U8, U9, 10 and U11 are shown on the board layout drawing. The circuitry is shown on the Motherboard schematic. The signals that must be sent to the Keyboard are fed to connector S2. This connector mates with P2 via a flat ribbon cable connected to the Keyboard.

The PC Board sockets are interconnected as described in the SIGNAL AND INTERCONNECTION TABLES section. Some inversion of address lines to S1 is done so that electrically identical boards (Memory) can occupy unique address spaces.

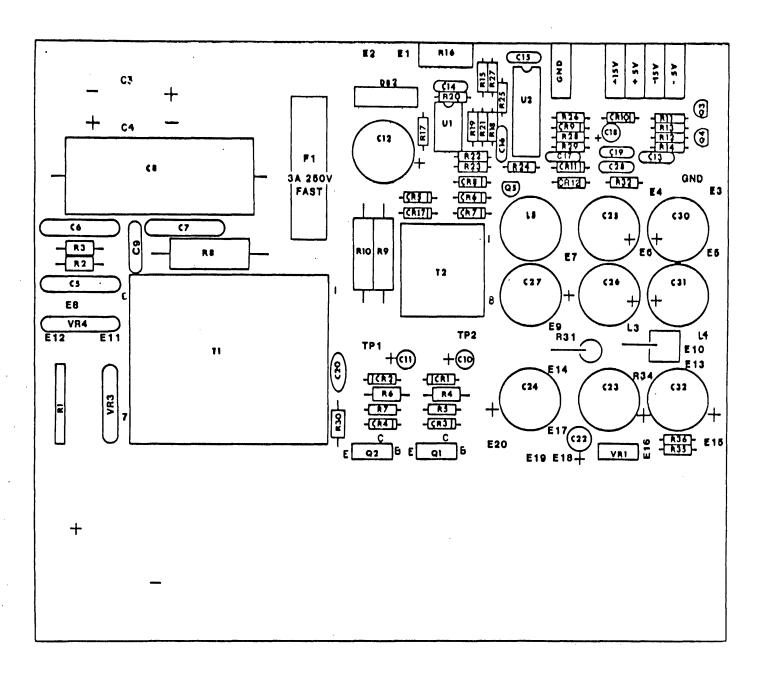

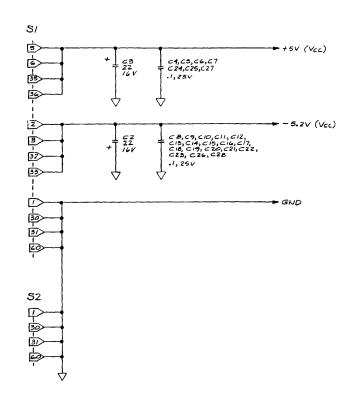

### 3.4 POWER SUPPLY FUNCTIONAL DESCRIPTION

The Power Supply is mounted to the bottom pan of the instrument and is enclosed in a protective housing. The Power Supply is a pulse-width modulated, half-bridge, 25 KHz switching circuit operating directly off the a-c power line. It supplies +/-5 V and +/-15 V to the Keyboard and Card Cage, +12 V to the Display Module and +5 V or +12 V to the disk drive. Also, it provides very effective overvoltage and overcurrent protection for both the Power Supply itself and the circuits that it supplies.

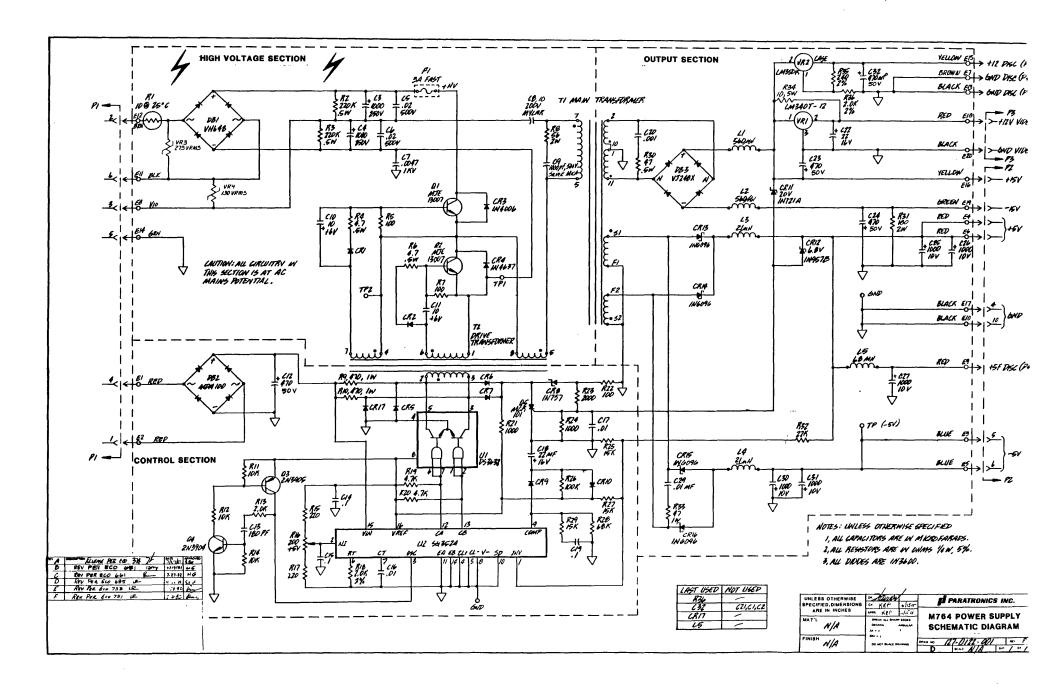

Refer to schematic #127-0122-001. The major functional units of the Power Supply circuit are the High Voltage Section, Control Section and Output Section. These units are discussed further in the following subsections. Refer to assembly drawing 143-0122-001 for major component location, disassembly and assembly information. Assembly drawing 126-0122-201 depicts the PC Board component locations.

## WARNING

THIS POWER SUPPLY CIRCUIT IS CONNECTED DIRECTLY TO THE A-C MAINS WITH NO INTERVENING ISOLATION TRANSFORMER. WHEN POWER IS APPLIED, LETHAL VOLTAGES ARE PRESENT. ONLY QUALIFIED SERVICE PERSONNEL FAMILIAR WITH LINE-OPERATED SWITCHING POWER SUPPLIES SHOULD UNDERTAKE SERVICE OF THIS SUPPLY, AND THEN ONLY WITH THE ISOLATING TEST SET-UP DESCRIBED BELOW. FAILURE TO OBSERVE THESE PRECAUTIONS MAY RESULT IN SERIOUS INJURY OR DEATH.

### 3.4.1 TEST SET-UP

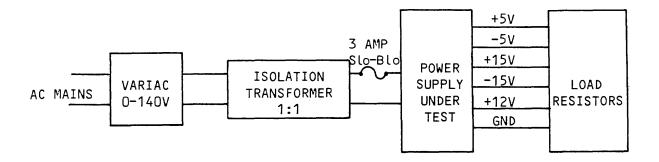

The a-c input power is fed directly from the mains to rectifier circuit DB1 without an intervening isolation transformer. Therefore, it is essential that an isolation transformer be incorporated in the test set-up as shown in Figure 3-4.

# WARNING

MEASUREMENTS OR TESTS UNDERTAKEN WITHOUT THE USE OF AN ISOLATION TRANSFORMER MAY RESULT IN SERIOUS INJURY OR DEATH TO PERSONNEL.

To gain access to the Power Supply, proceed as follows:

### NOTE

READ THE ENTIRE PROCEDURE ONCE BEFORE STARTING.

- a. Disconnect the power cord. Wait three minutes after the power is turned off to allow the capacitors to fully discharge.

- b. Remove the top cover by loosening the two quarter-turn fasteners at the rear of the cover and slide cover back.

- c. Remove the two nuts holding down the power supply cover. These are located between the power supply cover and disk drive bracket. Be careful not to damage the ground straps connected to the grounding stud.

- d. Turn the unit over to expose the bottom cover. Then remove the two screws near the rear that hold down the power supply cover. The cover may now be removed, exposing the supply.

To remove the supply proceed as follows:

- a. Unplug the power cords connecting the power supply to the disk drive, CRT and main Motherboard.

- b. Remove the six screws mounting the power supply heatsink to the bottom pan. These may be accessed from the bottom.

- c. The supply is now free and may be lifted up. Complete removal is accomplished by unplugging the six-conductor a-c plug.

Figure 3-4 Power Supply Test Set-Up

DO NOT RISK DAMAGE TO VALUABLE CIRCUIT BOARDS BY USING THE ANALYZER AS A TEST LOAD FOR THE SAKE OF CONVENIENCE.

USE RESISTORS AS DESCRIBED IN THE FOLLOWING PARAGRAPH. NOTE THAT NO LOAD IS NEEDED ON THE +12 V SUPPLIES UNLESS THEY ARE SPECIFICALLY UNDER INVESTIGATION.

To load the power supply outputs, proceed as follows:

a. Obtain a mating connector for P12 (see parts list). Make an adapter to connect the load resistors between the outputs and ground returns. Load resistance values are shown below:

### MINIMUM LOADING

| OUTPUT | CURRENT | RESISTANCE | RATING  |

|--------|---------|------------|---------|

| ====== | ======  | =========  | =====   |

| +5 V   | 5 A     | 1 ohm      | 25 W    |

| -5 V   | 5 A     | 1 ohm      | 25 W    |

| +12 V  |         | (no load r | needed) |

| +15 V  | 200 mA  | 75 ohms    | 5 W     |

| -15 V  | 200 mA  | 75 ohms    | 5 W     |

b. Bring power to the Power Supply by connecting the Mains Module through an isolation transformer to the power mains.

### 3.4.2 HIGH VOLTAGE SECTION

The High Voltage Section consists of the following: DB1, a VH 648 bridge rectifier; Q1 and Q2, Motorola MJE13007 power switching transistors; CR1,2, 1N3600 diodes; CR3,4, 1N4637 diodes; transformers T1 and T2; thermistor R1; and various resistors and capacitors.

This circuitry converts a nominal 100, 110 or 220 VAC, 50-60 Hz mains voltage to a

center-tapped nominal +/-162 d-c voltage. This d-c voltage is converted to a fixed-frequency, pulse-width modulated, a-c voltage across T1. The conversion is performed by the action of Q1, Q2, T2 and the control section. The output voltages of T1 are a nominal 5 and 15 VAC RMS at a nominal frequency of 25 KHz.

Input from the power mains is sent directly to the rectifier DB1 with no intervening isolation transformer. Consequently, all components within the High Voltage Section are at mains potential! PLEASE SEE PRECEDING WARNINGS AND CAUTIONS! A Mains Module contains a Voltage PCB that is used to select the a-c mains voltage that will be used to power the analyzer. This was described previously under CHASSIS. The three selection options are 100, 110 and 230 VAC.

If a mains voltage of 230 VAC is selected, it is applied across input pins P1-2 and P1-6. DB1 acts as a full-wave bridge rectifier and produces a nominal 325 V. This d-c voltage is filtered by filter capacitors C3 and C4 connected in series. The junction of C3 and C4 is a center tap of the 325 V. This provides +/-162 V for the switching circuit and transformer T1. R3 and R4 stabilize the center tap and act as bleeders. C5 and C6 are for EMI reduction. Fuse F1, a 3 A Fast-Blow type, provides circuit board protection in case Q1 or Q2 shorts out. Any failure of Q1 or Q2 will happen faster than the fuse can blow.

If a mains voltage of 100 or 110 VAC is selected, it is applied across input pins P1-2 and P1-3. With this connection, DB1 acts as a full-wave doubler rectifier. DB1 produces a nominal 325 V across series-connected C3 and C4 as before.

By means of transformer T2, the Control Section turns transistor Q1 ON and OFF in alternation with Q2. The cycle time is a nominal 40 microseconds. NOTE that Q1 and Q2 are never both ON at the same time. This alternately applies +162 and -162 V across the primary of transformer T1. The resulting a-c voltages across the secondaries of T1 are rectified and averaged in

the Output Section. The longer Q1 and Q2 are ON during each cycle, the higher the d-c output voltages from the Output Section. The width of the ON-pulse thus provides a means of voltage control. This is used by the Control Section for voltage regulation.

Capacitor C8 blocks any d-c bias that might otherwise result from a mismatch between Q1 and Q2. Components R8 and C9 reduce ringing and transient spikes. CR1, R4, C10 and CR2, R6, C11 speed up the turnoff times for Q1 and Q2.

#### 3.4.3 CONTROL SECTION

The Control Section consists of U1, a National DS3632 dual peripheral driver; U2, a Silicon General SG3524 regulating pulsewidth modulator; Q4, a 2N3904 transistor; Q3, a 2N3905 transistor; Q5, a Motorola MCR101 SCR; CR5-7,9,10,17,all 1N3600 diodes; CR8, a 1N588 Zener diode; and DB2, an MDA100 bridge rectifier.

This circuit provides drive pulses through transformer T2 that switch Q1 and Q2 ON and OFF. It controls the width of these drive pulses in response to voltage feedback from the Output Section. The circuit provides good voltage regulation of the output voltages. Also, it detects any overcurrent condition and reacts by shutting down the Power Supply.

The nucleus of the Control Section is the circuit U2. It is powered by a nominal +20 V from the bridge rectifier DB2. DB2 is fed, via P1-1 and P1-4, with a nominal 17 VAC at 50-60 Hz from a small transformer, T3. T3 is mounted on the rear panel, refer to Chassis wiring diagram. Circuit U2 produces drive pulses at outputs CA and CB (pins 12 and 13). These are used, via U1 and transformer T2, to turn Q1 and Q2 ON and OFF. The repetition rate of the pulses is established by an oscillator in U2. The frequency is set by the values of R18 and C16 at pins 6 and 7 to a nominal 50 KHz. There are two U2 drive pulses for one cycle of the Q1-Q2 switching circuit. This sets the switching frequency of the power supply to a nominal 25 KHz.

The drive pulses from U2 acts as follows. When CA is low and CB is high, U1 output 5 is turned OFF and output 3 is turned ON. The +20 V applied through R9 drives a current through winding 2-3 of T2. The current is driven in the direction making the dot end of the winding positive. This current in 2-3 induces voltages in windings 7-4 and 6-1, making their respective dot ends positive. The connections to these windings are such that Q2 is turned ON and Q1 remains OFF. The base of Q1 is driven even further negative.

The -162 V applied to Q2 drives current through T1 7-5 and T2 8-5 in the direction making the dot end of 8-5 positive. This regenerative action reinforces the base drive to Q2. Transformer T2 acts as a current transformer. Thus, the base drive current to Q2 is proportional to the T1 primary current through T2 8-5. The current ratio is such that Q2 is assured of being fully ON and out of the linear region.

Q2 is turned OFF again by the blanking pulse within U2 that brings CA high with CB. This turns U1 outputs 3, 5 ON, short circuiting T2 2-3 and turning OFF Q2 drive current at T2 6-1. This short circuit condition lasts for the duration of the blanking pulse, a nominal three microseconds. During this time Q2 and Q1 are both forced to remain OFF. This ensures that Q1 cannot be turned ON until Q2 is OFF. The turn-on time of these transistors is shorter than the turnoff time. Without a long enough blanking pulse, it would be possible for Q1 to turn ON while Q2 was still ON. For example, under conditions of low mains voltage and a compensating maximum pulse width for the switching circuit. This would put a short circuit across the + 162 V supply and cause component damage.

The next half of the 20 KHz switching cycle starts with the leading edge of the blanking pulse. Any drive pulse that would turn Q1 ON is inhibited within U2 for the duration of the blanking pulse. At the end of the blanking pulse, the voltage regulation circuitry in U2 is again in control. That circuitry determines when to start the Q1 drive pulse, and CB is brought low. This

turns U1 output 3 OFF and drives current through 2-3 of T2. The current is driven in the direction to turn Q1 ON and hold Q2 OFF. The rest of the action is analogous to that of the first half cycle.

Inputs to the U2 voltage regulation circuit are V+, pin 2, and V-, pin 1. The V+ input is supplied with a nominal +2.5 V reference voltage. The reference voltage is obtained, via R15, R17 and potentiometer R16, from regulated +5 V of U2, pin 16. Pin 16 output is also used as a source of +5 V power for other parts of the circuit.

The V- input is supplied with a nominal +2.5 V of negative feedback, via R32, R27 and R25. This is derived from the regulated +5 V output of the power supply. R28, R29 and C19 provide gain control and phase lag to the feedback amplifier. Lead compensation for the +5 V feedback signal is provided by C28.

If the feedback voltage at V- exceeds the reference voltage at V+, U2 acts to reduce the drive pulse width. This reduces the output voltages of the power supply. If the feedback voltage at V- falls below the reference at V+, the action is the opposite. This regulating action does not appreciably affect the 25 KHz switching frequency, only the ON times of Q1 and Q2.

The variable resistor R16 is adjusted so that the Power Supply output voltage at the +5 V test point is +5.1 V +0.05 V. This adjustment should be made with both Power Supply output plugs connected to the analyzer, all circuit boards in place, and after the analyzer has had power applied for a period of 10 minutes.

As mentioned previously, the U2 clock frequency is set to a nominal 50 KHz by R18 and C16. The clock signal is a short-duty-cycle pulse that is also used as the blanking pulse. The pulse width is approximately 0.5 microseconds, which is not enough for the blanking pulse in this application.

The output of the clock oscillator circuit is made available at pin 3. The Q3-Q4 circuit connected to this pin is used to

stretch the clock/blanking pulse to a nominal three microseconds. This provides blanking protection for Q1 and Q2.

The SCR Q5, Zener diode CR8, and diodes CR6 and CR7 constitute an overcurrent shutdown circuit that functions as follows. A component of the voltage across winding 2-3 of T2 is proportional to the current in winding 8-5. Normally the voltage across winding 2-3 results in less than 7.5 V at the cathode of CR8 via CR6 or CR7. If the rated current in winding 8-5 is exceeded, the voltage at CR8 cathode will exceed 7.5 V and CR8 will conduct.

When CR8 conducts, SCR Q5 is triggered and shorts both sides of winding 2-3 to ground through CR6 and CR7. This holds both Q1 and Q2 OFF, shutting down the power supply indefinitely until the power is turned OFF. When power is turned ON, the supply will function normally if the cause of the shutdown has been removed.

Diodes CR17 and CR5 serve to clip any ringing voltages that appear at winding 2-3 of T2.

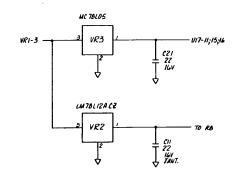

### 3.4.4 OUTPUT SECTION

The Output Section consists of VR1, an LM340T-12 +12 V series regulator; VR2, an LM350K +12 V regulator; DB3, a Varo VJ248X bridge rectifier, CR13 through CR17, all 1N6096 rectifiers; CR12, a 1N9578 6.8V Zener diode; and CR11, a 1N721A 20 V Zener diode.

This section contains rectifier and filter circuits for the four major output voltages of +5, -5, +15 and -15 volts. These circuits are fed with 25 KHz pulse-width modulated power from secondary windings on switching transformer T1.

Also contained in this section is the low-power series regulator, VR1, that provides +12 V for the Display Module. A second regulator, VR2, provides +12 V for the disk drive circuitry. Both low-power regulators are fed from the +15 V supply. The current ratings for these supply voltages are as follows:

| VOLTA          | GE   | MAXIMUM CURRENT                         |

|----------------|------|-----------------------------------------|

| =====          | ==   | ======================================= |

| +5             |      | 20.0 A                                  |

| <del>-</del> 5 |      | 12.0 A                                  |

| +15            |      | 1.0 A                                   |

| -15            |      | 1.0 A                                   |

| +12            | CRT  | 1.5 A                                   |

| +12            | DISK | 3.0 A                                   |

| +5             | DISK | 1.0 A                                   |

|                |      |                                         |

DB3 acts as a full-wave bridge rectifier for both the +15 and -15 V supplies. It is fed from secondary windings, 11-10-12, on the switching transformer T1. L1-C23 and L2-C24 act as pulse-averaging and ripple filters for the +15 V and -15 V supplies, respectively. R31 is a bleeder for the -15 V supply. R30 and C20 suppress transient ringing in the secondary.

Series regulator VR1 drops part of the  $\pm 15$  V output to  $\pm 12$  V for the Display Module. C19 provides additional filtering and decoupling for the  $\pm 12$  V.

The two diodes CR13 and CR14 are rectifiers for the +5 V supply. They are each fed from the center tapped secondary windings, on switching transformer T1. The cathodes of the diodes are connected to the L3-C25-C26 pulse-averaging and ripple filter. R33 and C29 suppress transient ringing in the 5 V secondaries.

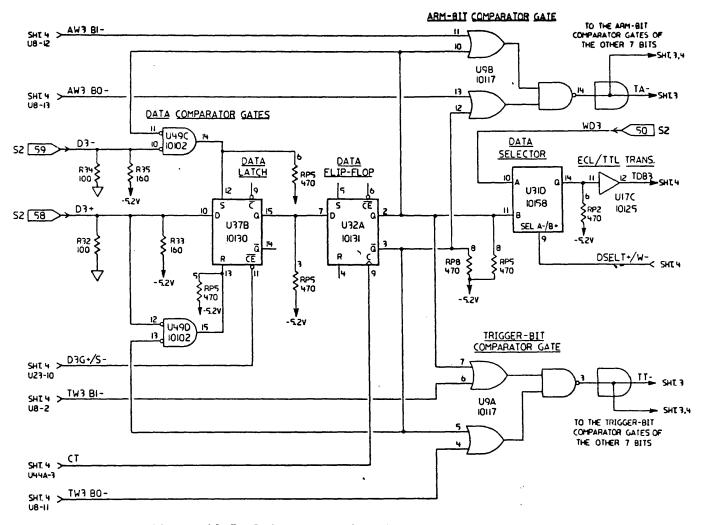

The -5 V output circuit is the same as the +5 V except for the differences to accommodate opposite polarity.