DP11-A synchronous line interface manual

DEC-11-HDPAA-C-D

DP11-A synchronous line interface manual

digital equipment corporation · maynard. massachusetts

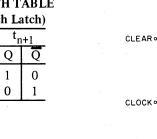

1st Edition August 1971

2nd Printing (Rev) February 1972

3rd Printing (Rev) November 1972

4th Printing February 1973

5th Printing September 1973

6th Printing November 1974

# Copyright © 1971, 1972, 1973, 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard Massachusetts:

| DEC    |           |

|--------|-----------|

| FLIP C | HIP       |

| DIGITA | <b>\L</b> |

and the state of the second second

PDP FOCAL COMPUTER LAB

# CONTENTS

| CHAPTER 1  | GENERAL DESCRIPTION                                       |     |

|------------|-----------------------------------------------------------|-----|

| 1.1        | INTRODUCTION                                              | 1-1 |

| 1.2        | FUNCTIONAL DESCRIPTION                                    | 1-1 |

| 1.2.1      | DP11 Modem Devices                                        | 1-2 |

| 1.2.2      | DP11 Modem Interface                                      | 1-2 |

| 1.3        | SPECIFICATIONS                                            | 1-5 |

| 1.3.1      | Physical Description                                      | 1-5 |

| 1.3.2      | Environmental, Interface, Modem, and Power Specifications | 1-7 |

| 1.4        | RELATED DOCUMENTS                                         | 1-8 |

| CHAPTER 2  | DP11 INSTALLATION PLANNING                                |     |

| 2.1        | INTRODUCTION                                              | 2-1 |

| 2.2        | CONFIGURATIONS                                            | 2-1 |

| 2.3        | CABLING AND TERMINATIONS                                  | 2-2 |

| 2.4        | ADDRESS AND PRIORITY ASSIGNMENTS                          | 2-3 |

| 2.5        | POWER CONNECTIONS                                         | 2-3 |

| 2.6        | INSTALLATION TESTING                                      | 2-4 |

| 2.0        |                                                           |     |

| CHAPTER 3  | OPERATIONAL PROGRAMMING                                   |     |

| 3.1        | INTRODUCTION                                              | 3-1 |

| 3.2        | DEVICE REGISTERS                                          | 3-1 |

| 3.2.1      | Receiver Control and Status Register (RCSR)               | 3-1 |

| 3.2.2      | Receiver Buffer Register (RBUF)                           | 3-2 |

| 3.2.3      | Sync Register (Sync)                                      | 3-3 |

| 3.2.4      | Transmitter Control and Status Register (TCSR)            | 3-3 |

| 3.2.5      | Transmitter Buffer Register (TBUF)                        | 3-5 |

| 3.3        | ADDRESS UTILIZATION                                       | 3-5 |

| 3.4        | BUS REQUEST PRIORITY AND INTERRUPT VECTORS                | 3-6 |

| CHAPTER 4  | DETAILED DESCRIPTION                                      |     |

| 4.1        | INTRODUCTION                                              | 4-1 |

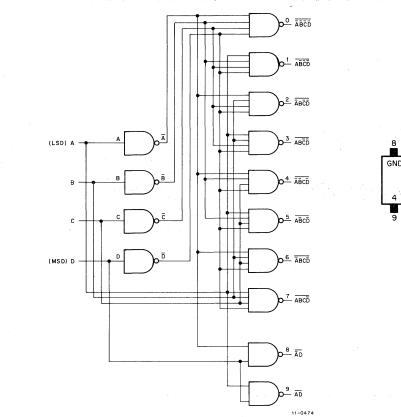

| 4.1        | SELECTION LOGIC                                           | 4-2 |

| 4.2.1      | Address Selector Module                                   | 4-2 |

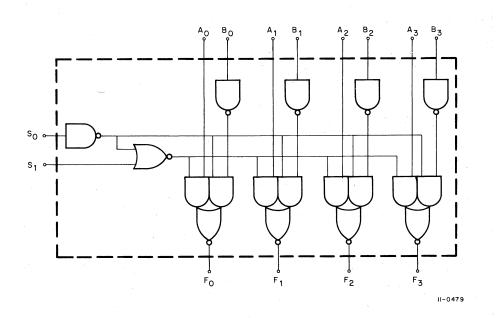

| 4.2.2      | Gating Logic                                              | 4-2 |

| 4.2.3      | Bus Drivers and Receivers                                 | 4-3 |

| 4.3        | INTERRUPT CONTROL                                         | 4-3 |

| 4.3        | CLOCK LOGIC                                               | 4-4 |

| 4.4<br>4.5 | CONVERTER LOGIC                                           | 4-4 |

| 4.6        | INITIALIZATION LOGIC                                      | 4-4 |

| 4.7        | RECEIVER OPERATION                                        | 4-5 |

| 4.7.1      | Character Length and Sync Character Control               | 4-5 |

| 4.7.1      | Sync Character Detection and Receiver Synchronization     | 4-6 |

| 4.7.2      | Receiver Character Transfer                               | 4-7 |

| 4.7.5      | TRANSMITTER OPERATION                                     | 4-8 |

| 4.8.1      | Transmitter Initiation                                    | 4-8 |

| 4.8.2      | Character Length Control                                  | 4-8 |

| 4.8.2      | Transmitter Transfer                                      | 4-9 |

| 7.0.5      | Transmitter Transier                                      | . , |

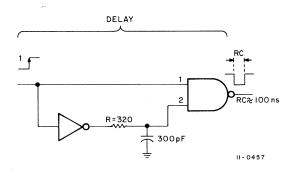

#### 4.8.4 **IDLE SYNC Control** 4.8.5 Half-Duplex Operation 4.9 MAINTENANCE MODE **CHAPTER 5 MAINTENANCE** 5.1 **INTRODUCTION** 5.2 INTERNAL LOOP TEST 5.3 EXTERNAL LOOP TEST APPENDIX A DP11 OPTION SPECIFICATIONS **RS-232-C ELECTRICAL SPECIFICATIONS** A.1 A.2 EIA RS-232-C INTERFACE PIN ASSIGNMENTS A.3 EIA (RS-232-C) TO EQUIVALENT CCITT A.4 CURRENT MODE ELECTRICAL SPECIFICATIONS APPENDIX B PULSE DELAY CIRCUIT

**CONTENTS** (Cont)

Page

4-10

4-10

4-11

5-1

5-1

5-1

A-1

A-1

A-2

A-3

| B.1 | PULSE DELAY CIRCUIT |  |  | <b>B-</b> ] |

|-----|---------------------|--|--|-------------|

|     |                     |  |  |             |

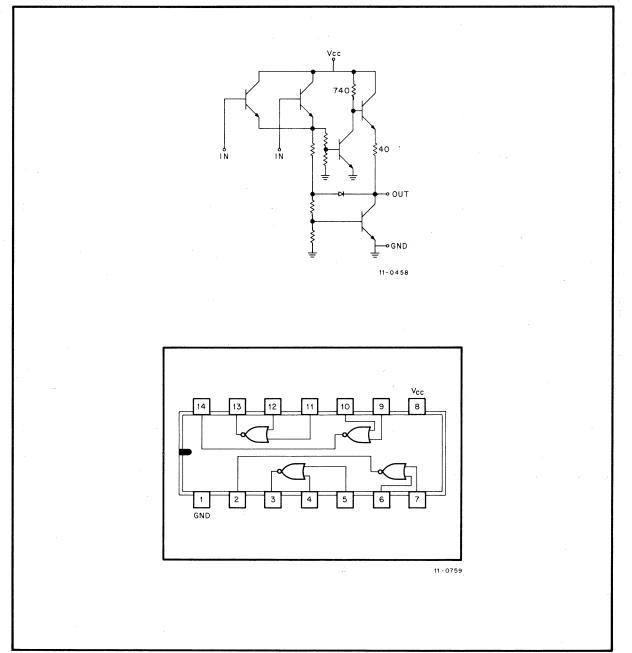

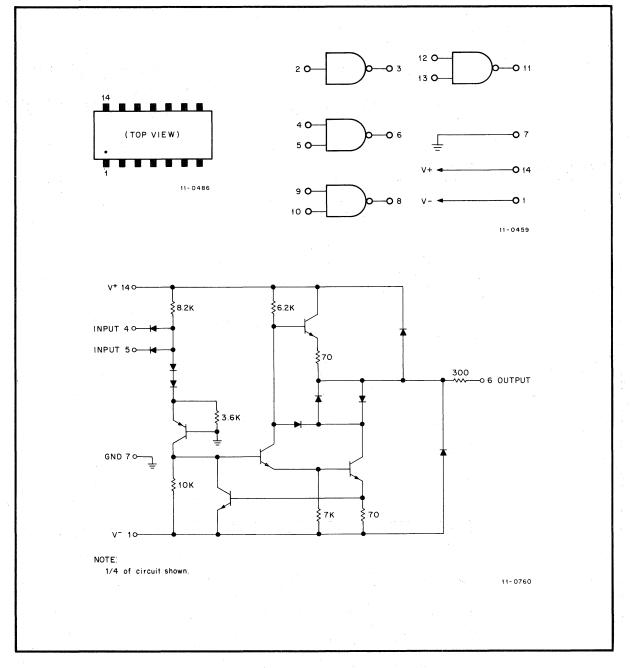

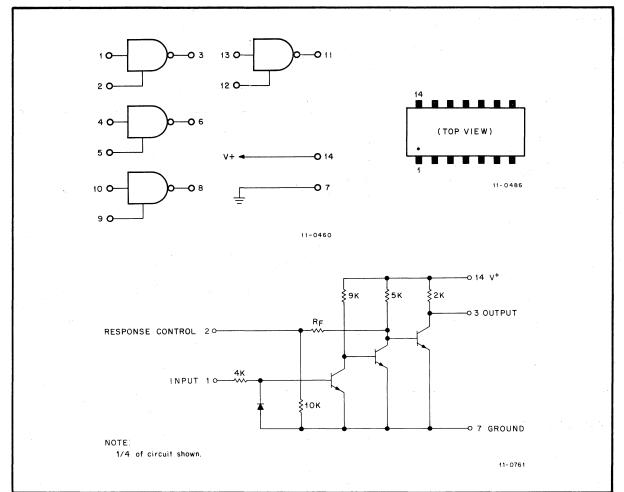

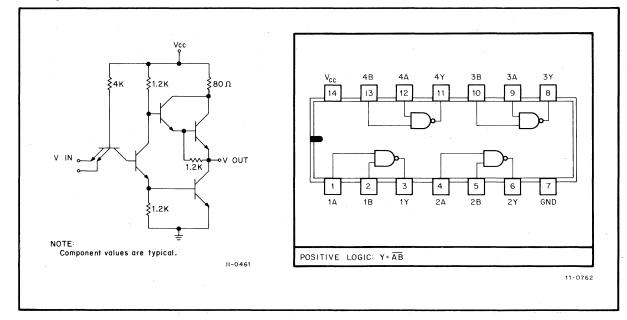

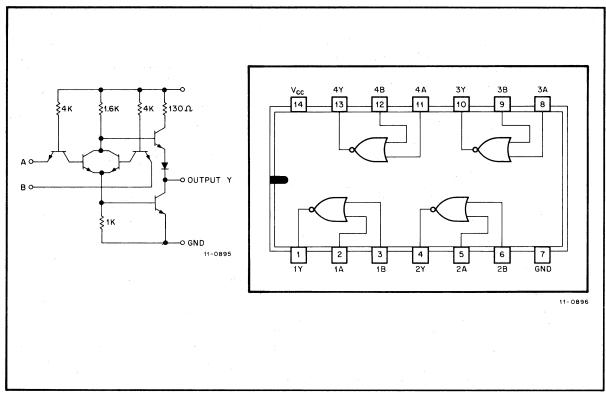

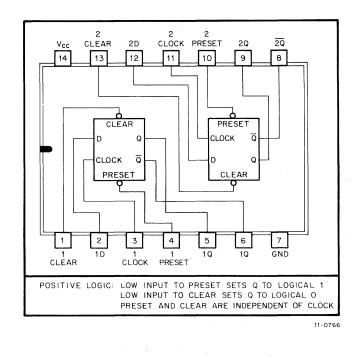

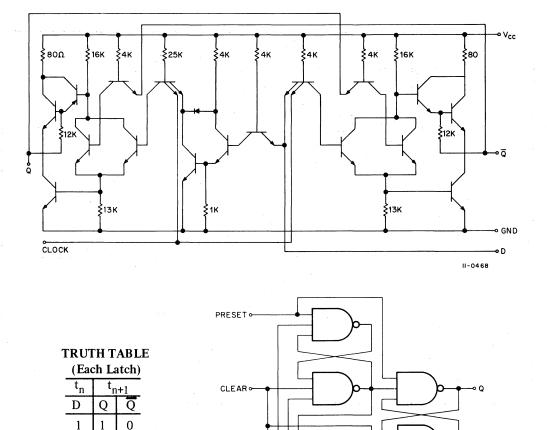

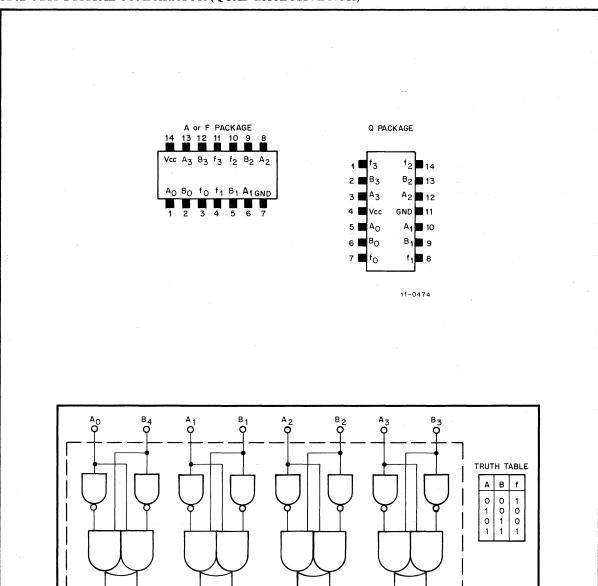

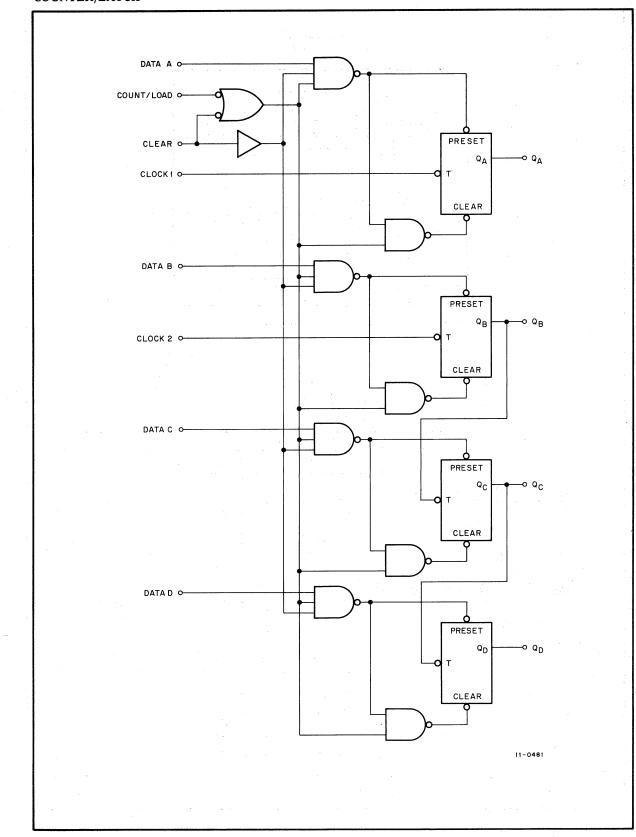

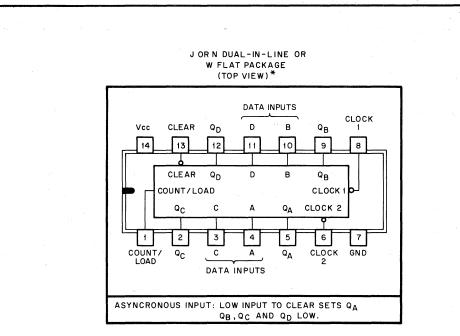

# APPENDIX C DP11 INTEGRATED CIRCUITS

# ILLUSTRATIONS

| Figure No. | Title                                         | Page |

|------------|-----------------------------------------------|------|

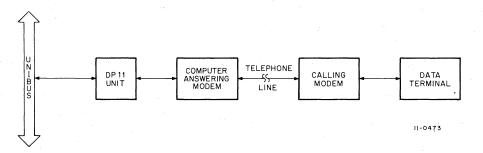

| 1-1        | Synchronous Data Communication Block Diagram  | 1-2  |

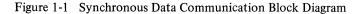

| 1-2        | DP11 Synchronous Line Interface Block Diagram | 1-3  |

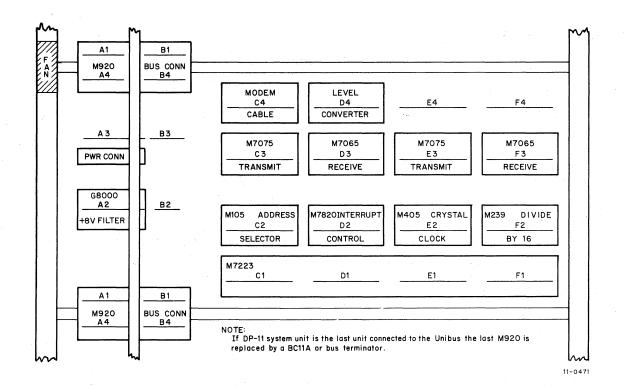

| 1-3        | DP11 System Unit Layout                       | 1-6  |

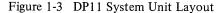

| 2-1        | Modem Configurations                          | 2-2  |

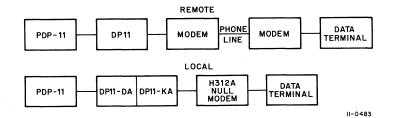

| 2-2        | Interface Configurations for Two Computers    | 2-2  |

| 5-1        | Test Connector Configuration                  | 5-2  |

| B-1        | Pulse Delay Circuit                           | B-1  |

#### TABLES

| Table No. | Title                                    | Page |

|-----------|------------------------------------------|------|

| 1-1       | Related Documents                        | 1-8  |

| 2-1       | DP11 Options                             | 2-1  |

| 2-2       | Data and Control Leads                   | 2-3  |

| 4-1       | Gating and Select Line Signal Generation | 4-3  |

| 5-1       | Test Connector Configuration             | 5-2  |

# FOREWORD

This manual provides the user with the thoery of operation and logic diagrams necessary to understand and maintain the DP11-A Synchronous Line Interface (hereafter referred to as DP11). The level of discussion assumes that the user is familiar with basic digital computer theory and basic PDP-11 operation.

Although signals and data are transferred between the DP11 and the PDP-11 Unibus, this manual does not cover operating of the Unibus. A detailed description of the Unibus is presented in the PDP-11 Peripherals and Interfacing Handbook.

The DP11 is an interface control between the PDP-11 and the Bell 201, 301, and 303 modems, or any equivalent modems. However, this manual does not describe the operation of the Bell units. For a detailed description of the Bell 200 and 300 series modems, the user is referred to their respective *Bell System Communications Technical Reference Manuals*.

A copy of this manual is supplied with each DP11. Throughout the text of this manual, engineering drawings are referenced; a reduced set of engineering drawings is provided in a separate document (also supplied with the equipment) entitled *DP11 Synchronous Communication Interface Engineering Drawings*. This document reflects the updated drawings for the DP11 at the time the equipment is shipped and is to be used in conjunction with this manual.

This manual is divided into five chapters:

- *a.* general description

- b. installation planning

- c. operational programming

- *d.* detailed description

- e. maintenance

# CHAPTER 1 GENERAL DESCRIPTION

### **1.1 INTRODUCTION**

The DP11 provides a double-buffered, program-interrupt interface between a PDP-11 and a serial synchronous line. With this interface, the PDP-11 can be used in remote batch and remote concentrator applications; the PDP-11 can also be used as a front end synchronous line controller to handle remote and local synchronous terminals. The PDP-11 Unibus functions as a multiplexer for adding multiple synchronous lines to the PDP-11.

For additional flexibility, the DP11 interface handles a wide variety of terminals and line disciplines (i.e., line control procedures and error control techniques). A programmer can vary the Sync character, data character size, and modem control leads of the DP11. Automatic Sync character stripping and automatic idling are also program selectable. While idling, the DP11 transmits the contents of the Sync buffer instead of transmitting the contents of the data buffer.

The DP11 interface provides individual interrupt vectors and hardware interrupt priority assignments for the transmitter and receiver. Interrupt priority is jumper selectable, which, when coupled with the automatic transmit idle capability, enables dynamic system adjustment to peak message activity. For example, the programmer can temporarily ignore the transmitter if receiver activity is high.

The basic DP11 system unit, which requires the same mounting space as a single PDP-11 system unit, consists of a pre-wired assembly and a fixed set of modules. Some of the optional equipments are: level converters; modem cables for various modems (e.g., EIA RS-232-C for Bell 201, or equivalent modems); the internal crystal clocking source; and character expansion to 12 bits maximum (8 bits are standard). The basic module set is listed below:

- 1 M7075 Transmit Module

- 1 M7065 Receive Module

- 1 M7223 Control Module

- 1 G8000 +8V Filter Network

- 1 M105 Address Selector Module

- 1 M7820 Interrupt Control Module

- 1 BR5 DEC #5408778 Jumper

#### **1.2 FUNCTIONAL DESCRIPTION**

The DP11 is a serial synchronous line interface that is capable of program-controlled, full- or half-duplex operation with a serial modem device. The DP11 interface provides serial-to-parallel and parallel-to-serial data conversion, level conversion, and modem control. In addition, the DP11 has three programmable character lengths: 6,

1-1

7, or 8 bits. The character length can be extended to 10, 11, or 12 bits, all optional. The DP11 is program selectable for Sync code and Sync character stripping and is also capable of data transfer line speeds of up to 50,000 baud. The unit is interface-compatible to Bell 201, 301, and 303, or equivalent modems. The DP11 Control provides an auto-answering capability in addition to the features described above.

#### 1.2.1 DP11 Modem Devices

The DP11 interface is compatible with Bell 201, 301, or 303 data set modem devices; detailed information on these units is contained in their respective *Bell System Data Communications Technical Reference Manuals*, supplied with the equipment. However, it is important to describe the modem *handshaking* sequence in relation to the DP11. For purposes of this description, the Bell 201-A Type Modem is used as an example (for procedures that apply to other modems, consult the appropriate reference manual). The handshaking sequence sets up the computer, the DP11, and the modem for data communications. Handshaking is accomplished through call and acknowledge signals between these three units. To set up a data communications channel, the DP11 transmitter status register.

Thus, to establish a data communication channel, the modem at the computer is called by another remote modem (see Figure 1-1), and a RING signal from that modem is sent to the DP11. The RING signal initiates an interrupt to the computer, if Interrupt Enable (Status Interrupt) is set. The software determines that the interrupt was caused by a RING signal and, through a service routine in the software, issues a TERMINAL READY signal. This TERMINAL READY signal causes the data set to answer the call; a CARRIER signal is then sent to the caller. The caller acknowledges the CARRIER signal with its own CARRIER signal, which causes the modems to latch into the data mode. Through this sequence, a data channel is established between the caller and the computer, and the DP11 is now ready to receive or transmit data. The only prerequisites for the handshaking sequence are: the software service routines must be in use, and the Interrupt Enable (Status Interrupt) must be set in the DP11 logic.

#### 1.2.2 DP11 Modem Interface

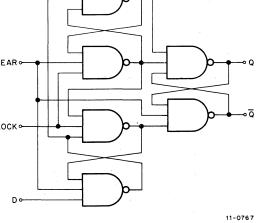

The DP11 is a fully character-buffered synchronous serial line interface that translates serial and parallel data (see Figure 1-2). Output characters are transferred in parallel from the computer to a buffer register; from the buffer register, the characters are serially shifted to the communication line. Input characters from the modem are shifted into a shift register, transferred to a buffer register, and then made available to the PDP-11 on an interrupt basis. Both the transmitter and receiver are double-buffered; as a result, a full character time is allowed in which to service transmitter and receiver interrupts. The clocking necessary to serialize the data is normally provided by the associated high-speed synchronous modem. However, the internal clocking option can be used for local terminals when no external clocking is available.

Figure 1-2 DP11 Synchronous Line Interface Block Diagram

Essentially, the DP11 performs two major functions:

- *a.* it receives data from the modem in serial form and transfers the data to the computer in parallel form.

- b. it converts parallel data from the computer to serial data and transmits it to the remote terminal near the modem.

When the handshaking procedure has established a data channel between a modem and the computer, the DP11 in Receiver operation must be synchronized with the transmitting data terminal. Synchronization is accomplished through the established Sync Character Code. Because the Sync Character Code and the character size are programmable, the programmer must load them into the Sync Register and Receiver Status Register (refer to Chapter 3) prior to synchronization. When the DP11 has the Sync Character Code and character size, it is able to scan the incoming bit stream until it finds two sequential Sync characters. When two sequential Sync characters are found, the Receive Active Flag is set and synchronization is achieved.

The standard Sync characters are as follows:

- a. 8-bit ASCII is 026, (00010110 binary bit stream)

- b. 8-bit IBM BISYNC is 32<sub>16</sub> (00110010 binary bit stream)

- c. and EBCDIC is  $062_8$ .

When synchronization is achieved, serial data can be received continuously (no start or stop bits are needed). The first character following two or more Sync characters causes an interrupt if the RECEIVE INTERRUPT is enabled (if STRIP SYNC is set, an interrupt occurs at the first data character). This interrupt occurs each time a data character is received by the DP11, and it is one of two DP11 independent interrupt request levels and vectors.

The other interrupt request is for the transmitter and DP11 status. A receive interrupt request is generated as the receive character is transferred into the receive buffer. If the program does not remove the receive character from the buffer before the next character is transferred, a DATA OVERRUN ERROR bit is set in the DP11 Status Register. If the STATUS INTERRUPT ENABLE bit is set, this error condition causes a DP11 status interrupt request.

When receiving data, the DP11 operates in one of two modes:

- a. All Sync characters are stripped automatically from the incoming data stream, if the RECEIVE ACTIVE bit is set and the STRIP SYNC bit is set.

- b. Sync characters are treated as normal data and cause an interrupt request when transferred, if the RECEIVE ACTIVE bit *is set* and the STRIP SYNC bit *is not* set.

Incoming characters to the Receiver logic appear right-justified in the receive data buffer. The first bit received from each character appears as the right-most bit in the receive buffer. The parity of this bit can be tested by the programmer.

The transmitter of the DP11 synchronizes identically to the receiver. When synchronization is achieved, serial data can be transmitted to a modem. The transmitter operates in one of two modes:

- a. When the IDLE SYNC bit *is not* set, the transmitter must be refreshed in approximately one character time (i.e., 1/baud × number of bits per character 1/2 second), or the DP11 stops transmitting (i.e., holds the TRANSMITTED DATA line to the modem in the binary one-mark position). This also sets the REQUEST TO SEND line to the modem to OFF.

- b. When the IDLE SYNC bit is set, the logic will transmit from the Sync buffer if the programmer does not refresh the transmitter in approximately one character time (i.e.,  $1/baud \times number$  of bits per character -1/2 second).

The transmitter, as indicated previously, has a separate INTERRUPT ENABLE control bit from the receiver. When the transmitter interrupt is enabled, an interrupt request is generated each time the leading edge of a data character is presented to the modem synchronous line. In the idle mode, transmission from the Sync buffer does not cause an interrupt. Only the transmission of data characters can cause an interrupt.

With the buffer loaded on IDLE SYNC asserted, the SEND REQUEST (modem control) lead asserts when data is ready for transmission. The first data bit is presented to the modem on the first transition of the clock following the assertion of the CLEAR TO SEND lead. Additionally, provided that the HALF-DUPLEX bit is set, the assertion of SEND REQUEST inhibits the Receiver logic, which prevents the transmitter from causing a Receive "A" interrupt. When terminating the transmitter operation (i.e., the transmit buffer is empty and IDLE SYNC clear), SEND REQUEST is negated on the second positive transition of the transmit clock, after the last data bit has been delivered to the modem.

In addition to the signals transmitted between the modem and the DP11 during the handshaking sequence, other control signals and data are transmitted between these units through the modem control leads, provided to interface the DP11 to the Bell 201, 301, 303 or equivalent modems. These leads allow the DP11 to be used in *switched* or *dedicated* full- or half-duplex configurations. The DP11 status interrupts have a separate interrupt enable bit but share the bus request level and interrupt vector address with the transmitter. In relation to the modems, if STATUS INTERRUPT is enabled (same as INTERRUPT ENABLE of the handshaking sequence), a CARRIER FLAG, DATA OVERRUN, or RING will generate interrupt requests. The control leads are fail-safe (i.e., they appear OFF if the modem loses power). For the actual control lead designations of the cable interface between the Bell 201, 301, and 303 modems and the DP11, refer to Chapter 2.

#### **1.3 SPECIFICATIONS**

The DP11 specifications are grouped into five general categories:

- a. physical description

- b. environmental limits

- c. operational interface characteristics

- d. modem compatibility

- e. power requirements

#### 1.3.1 Physical Description

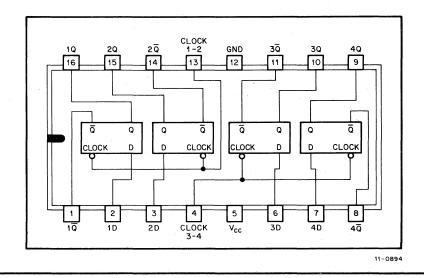

One DP11 Synchronous Line Interface unit occupies (see Figure 1-3) one PDP-11 System unit within the PDP-11 System mounting box. The DP11 interface unit (including all options) consists of:

- a. a PDP-11 System unit,

- b. two M7075 Transmit Modules,

- c. two M7065 Receive Modules,

- d. M7223 Control Module,

- e. M105 Address Selector Module,

- f. M7820 Interrupt Control Module,

- g. G8000 +8V Filter,

- h. M920 Unibus Connector,

- *i.* M405 Crystal Clock,

- j. M239 Counter Module,

- k. Level Converter Module (depending on the modems interfaced),

- 1. Modem Cable Connector Module (depending on the modems interfaced), and

- *m*. DP11 Power Connections.

The level converter and cable connector options are described in the configuration option section of Chapter 2. Figure 1-3 illustrates the module layout for a general DP11 System. The cable options with the cable connection module are listed in the cable requirement section of Chapter 2.

#### NOTE

If the DP11 system unit is the last unit connected to the PDP-11 Unibus, then the last M920 Module is replaced by a BC11A or M930 Bus Terminator.

Strip Sync: The Receiver has the programmable feature of stripping incoming Sync characters from the data stream.

Idle Mode: This programmable feature transmits the contents of Sync Register if the program fails to refresh the transmit buffer.

Order of Bit Transmission: Low-order bit first.

Program Response Time:

Receive:  $1/baud \times bits$  per character seconds.

Transmit:  $1/\text{baud} \times \text{bits per character} - 1/2$  second.

Parity: Parity check bit provided on incoming characters.

Program Interrupt: Conditions are Receive Done, Transmit Done, and Status (CARRIER FLAG, RECEIVE OVERRUN, and RING). There are two independently selectable Bus Request (BR) priorities: one for Receive Done, and the other for Transmit Done and Status.

Data and Modem Control Signals:Most leads of the Bell 201, 301, and 303 modems are brought into the unit.All leads are EIA RS-232-C and CCITT-compatible for the 201 modem.All leads for the 300 series modems are current mode, as defined in the<br/>appropriate reference manual.

Bus Load: One line unit (DP11) represents one unit load to the PDP-11 Unibus. The Unibus provides 20 unit loads. To add more than 20 unit loads, a bus extender (DB11-A) must be used.

Physical Connection: For 201 modems, a 25-ft cable with RS-232-C compatible, 25-pin male connector (BC01R-25) is used. For 300 series modems, a 25-ft coaxial cable is used with appropriate connectors for the 301 and 303 modems, respectively (BC01T-25 and BC01Y-25).

### 1.3.2 Environmental, Interface, Modem, and Power Specifications

The environmental limits, operational interface characteristics, modem capabilities, and power requirements are as follows:

# **Environmental Limits**

Temperature: 10°C to 50°C Humidity: 20% to 90% non-condensing

#### **Operational Interface Characteristics**

Operating Transfer Mode:

Modem: Full- or half-duplex, selected under software control.

PDP-11: Interrupt mode for parallel data and status.

Maximum Data Rates: At EIA/CCITT/10,000 baud (for 200 series modems). Current mode is program limited (300 series modems) to 50,000 baud.

Data Format: Character size is variable under program control to 6, 7, or 8 bits (additional 10, 11 or 12 bits optional).

Clocking: Synchronous clock from the external modem, (Internal clock optional).

Sync Character: Identifiable Sync character is programmable.

Sync Detection: Two successive Sync characters are required to activate the DP11 Receiver. The DP11 has no other character recognition feature.

#### Modem Compatibility (Typical)

| Туре      | <b>Communications Channel</b>                       | Speed (Baud) |

|-----------|-----------------------------------------------------|--------------|

| Bell 201A | (Direct Distance Dialing Network - Type 3002 (C2))  | 2,000        |

| Bell 201B | (Leased Line Only – Type 3002 (C2))                 | 2,400        |

| Bell 301B | (Leased Line Only – Group (12 Voiceband Line))      | 40,800       |

| Bell 303B | (Leased Line Only – Half Group (6 Voiceband Lines)) | 19,200       |

| Bell 303C | (Leased Line Only – Group (12 Voiceband Lines))     | 50,000       |

#### Power Requirements

Current Drawn (maximum):

|         | +5V: 0.77A @ 3.85W or 13.2 BTU/hr                                                                            |  |

|---------|--------------------------------------------------------------------------------------------------------------|--|

| DP11-KA | +5V: 0.18A @ 0.9W or 3.08 BTU/hr                                                                             |  |

| ******  | +5V: 2.56A @ 12.8W or 43.8 BTU/hr<br>-15V: 0.07A @ 1.05W or 3.59 BTU/hr<br>+8V: 0.04A @ 0.32W or 1.09 BTU/hr |  |

| DP11-DA | -15V: 0.07A @ 1.05W or 3.59 BTU/hr                                                                           |  |

|         | +8V: 0.04A @ 0.32W or 1.09 BTU/hr                                                                            |  |

# 1.4 RELATED DOCUMENTS

A list of documents pertaining to the DP11 as a peripheral interface for the PDP-11 computer is provided in Table 1-1.

| Table 1-1         Related Documents            |                |                                                                                                                                                                                                                                             |  |

|------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Title                                          | Number         | Description                                                                                                                                                                                                                                 |  |

| GENERAL                                        |                |                                                                                                                                                                                                                                             |  |

| PDP-11/20/15/R20<br>Processor Handbook         | 112.01071.1855 | Discussion of overall system, addressing<br>modes, and basic instruction set from a pro-<br>gramming point of view. Some interface<br>and installation data.                                                                                |  |

| Instruction List                               | None           | Pocket-size list of instructions. List group<br>names, functions, codes, and bit assignments<br>Includes ASCII codes and the bootstrap<br>loader.                                                                                           |  |

| Logic Handbook                                 | DEC, 1970      | Presents functions and specifications of the<br>M-Series logic modules and accessories used<br>in PDP-11 interfacing. Includes other types<br>of logic produced by DEC but not used<br>with the PDP-11.                                     |  |

| HARDWARE                                       |                |                                                                                                                                                                                                                                             |  |

| PDP-11 Peripherals and<br>Interfacing Handbook | 112.01071.1854 | Used in conjunction with this manual.<br>Provides detailed theory, flow, and logic<br>descriptions of Unibus and external device<br>logic. Discusses methods of interface con-<br>struction and provides examples of typical<br>interfaces. |  |

| PDP-11 Conventions                             | DEC-11-HR6A-D  | <ul> <li>a. General Maintenance</li> <li>b. Logic Symbology</li> <li>c. Drawing Set Explanation</li> <li>d. Processor Signals</li> <li>e. Product Identification Code</li> <li>f. Glossary</li> <li>g. Abbreviations</li> </ul>             |  |

| SOFTWARE                                       |                |                                                                                                                                                                                                                                             |  |

| Paper-Tape Software Programming<br>Handbook    | DEC-11-GGPA-D  | Detailed discussion of the PDP-11 software<br>system used to load, dump, edit, assemble<br>and debug PDP-11 programs. Also included<br>is a discussion of input/output programming<br>and the floating-point and math package.              |  |

1-8

ť

# Table 1-1 (Cont)Related Documents

| Title                                                                         | Number | Description                                                                                                 |  |

|-------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------|--|

| DATA SETS                                                                     |        |                                                                                                             |  |

| Bell System Data Communications<br>Data Set 201 Technical Reference<br>Manual | None   | Data Set Interface specifications. Data Set description and options including interface signals and timing. |  |

| Bell System Data Communications<br>Data Set 301 Technical Reference<br>Manual | None   | Data Set Interface specifications. Data Set description and options including interface signals and timing. |  |

| Bell System Data Communications<br>Data Set 303 Technical Reference<br>Manual | None   | Data Set Interface specifications. Data Set description and options including interface signals and timing. |  |

# CHAPTER 2 DP11 INSTALLATION PLANNING

# 2.1 INTRODUCTION

This chapter contains the information necessary to install and operate DP11. All necessary power and interface connections, priority and address assignments, and optional system configurations are also included in this chapter.

# 2.2 CONFIGURATIONS

Table 2-1 lists the available DP11 options, their prerequisites, and a brief description.

| DEC No. | Prerequisite                        | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DP11-DA | PDP-11                              | Full/half duplex synchronous line module set. Double buffered, 6, 7, or 8-bit characters. EIA/CCITT termination suitable for direct use with 201 modems. Includes 25-ft modem cable.                                                                                                                                                                                                                    |  |

| DP11-DB | PDP-11                              | Same as above except suitable for direct use with 301 modems. Includes 25-ft modem cable.                                                                                                                                                                                                                                                                                                               |  |

| DP11-DC | PDP-11                              | Same as above except suitable for direct use with 303 modems. Includes 25-ft modem cable.                                                                                                                                                                                                                                                                                                               |  |

| DP11-CA | DP11-DA<br>DP11-DB<br>DP11-DC       | Allows the DP11 to handle 10, 11, or 12 bits per character, in addi-<br>tion to the standard 6, 7, and 8 bits per character. Jumper "D4" on<br>M7065 Module must be removed at F03.                                                                                                                                                                                                                     |  |

| DP11-KA | DP11-DA or<br>DP11-DB or<br>DP11-DC | Internal Clock. Clocking source to be used for direct connection of DP11 to local synchronous terminal or a local synchronous computer interface (without modems). For following baud rates: 2400, 4800, 9600, 19.2K and 40.8K, baud rate must be specified.                                                                                                                                            |  |

| H312A   | DP11-DA                             | Synchronous/asynchronous null modem jumper box. Allows direct<br>connection of a PDP-11 to any peripheral with a modem type inter-<br>face that conforms to EIA RS-232-C and CCITT specifications. Also<br>allows direct serial synchronous computer to computer data transfers<br>between two PDP-11s. Each PDP-11 must have a DP11-DA and a<br>DP11-KA. The maximum separation must not exceed 50 ft. |  |

Table 2-1 DP11 Options

The basic DP11 consists of the module layout for a particular option (refer to Chapter 1). However, the DP11 can connect a variety of terminals or synchronous lines to the PDP-11 System, either remotely or locally. These possible configurations are shown in Figure 2-1. The DP11 is ideally suited for interfacing the PDP-11 to high-speed synchronous lines for remote batch, remote data collection, and remote concentration applications.

Figure 2-1 Modem Configurations

Multiple DP11s enable a PDP-11 System to be used as a synchronous line concentrator or front-end synchronous controller to a larger computer. In these cases, the PDP-11 Unibus acts as a multiplexer for the synchronous lines of the various DP11s. The DP11 can also connect two PDP-11s or a PDP-11 and a larger computer (e.g., the IBM 360). These connections can be either remote or local. Two possible configurations are shown in Figure 2-2.

Figure 2-2 Interface Configurations for Two Computers

#### 2.3 CABLING AND TERMINATIONS

The DP11 provides an interface to the PDP-11 Unibus and the synchronous modem interface. The DP11 presents one unit load to the Unibus and meets all Unibus electrical specifications. Also, the DP11 provides data and control leads compatible with modem types 201A, 201B, 301 and 303 modems, or equivalent. The 201 series interfacing conforms to EIA CCITT specifications; the 300 series interfaces are current mode. Table 2-2 shows all the data and control leads utilized for both the standard type modems and the DP11. Unless otherwise specified, the 201 levels are bipolar; the 301 and 303 levels are current mode. The control and data leads are interfaced to the DP11 through the cable modules listed below:

| Modem      | Cable            | Connector                    |  |

|------------|------------------|------------------------------|--|

| 200 series | BC01R-25 (25 ft) | DP25P Cannon or Cinch 25-pin |  |

| 303 series | BC01W-25 (25 ft) | Burndy                       |  |

#### NOTE

These components are supplied with the particular configuration delivered.

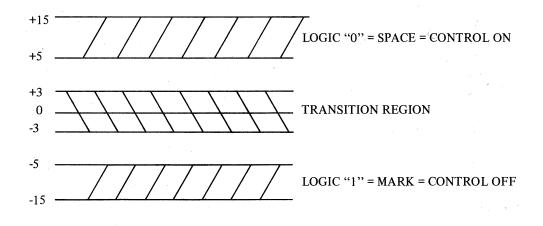

For the 200 series modems, a EIA/CCITT Level Converter (RS-232-C) Module is needed from the DF11-A series (M594). The 300 series level conversion is provided by the DF11-G Current Mode Level Converter. Electrical specifications for both RS-232-C and current mode interfacing are given in Appendix A. The RS-232-C Interface Pin Assignments and Equivalent CCITT for each data and control lead are also included in Appendix A.

| DP11A Interface        | Model 301                           | Model 303                           | Model 201             |

|------------------------|-------------------------------------|-------------------------------------|-----------------------|

| Send Data              | Send Data                           | Send Data                           | Send Data             |

| Received Data          | Received Data                       | Received Data                       | Received Data         |

| Send Request           | Send Request                        | Send Request                        | Send Request          |

| Clear to Send          | Clear to Send                       | Clear to Send                       | Clear to Send         |

| Interlock/Data Set Rdy | Interlock                           | Data Set Rdy                        | Interlock             |

| Carrier/AGC            | Carrier on-off                      | AGC Lock                            | Carrier on-off        |

| Serial Clock Transmit  | Serial Clock Transmit               | Serial Clock Transmit               | Serial Clock Transmit |

| Serial Clock Rcve      | Serial Clock Rcve                   | Serial Clock Rcve                   | Serial Clock Rcve     |

| Terminal Rdy           |                                     | Data Terminal Rdy*                  | Remote Control        |

| Ring                   |                                     | Ring Indicator*                     | Ring Indicator 1      |

| External Timing        | Serial Clock Transmit<br>(external) | Serial Clock Transmit<br>(external) | External Timing       |

Table 2-2Data and Control Leads

## 2.4 ADDRESS AND PRIORITY ASSIGNMENTS

The DP11 is addressed through the M105 Address Selector Module; the DP11 interrupt vector is determined by the M7820 Interrupt Control Module. Each DP11 unit uses a different set of vector addresses. These addresses are pre-assigned and are listed in Paragraph 3.4. The priority assignment is determined by the jumper connections that plug into the M7223 Module. The normally supplied priority for the DP11 is Bus Request Line 5 (BR5). The Bus Request levels for transmit and receive are independently selected; however, the user can assign another priority level. The respective BR level connectors with part numbers are as follows:

| BR Level         | Part No. |

|------------------|----------|

| BR4 (priority 4) | 5408776  |

| BR5 (priority 5) | 5408778  |

| BR6 (priority 6) | 5408780  |

| BR7 (priority 7) | 5408782  |

#### 2.5 POWER CONNECTIONS

The PDP-11 System or BA11 Mounting Box provide the power connections to the DP11 (see Figure 1-3). Because the DP11 occupies a typical PDP-11 System unit, it receives power from the PDP-11. These power connections are discussed in detail in the *PDP-11 Peripherals and Interfacing Handbook*.

# 2.6 INSTALLATION TESTING

Installation testing is performed to ensure that the DP11 has been properly installed and is completely operational. Installation testing is accomplished by running the diagnostic supplied with the DP11 (MainDEC-11-D8DA). This program is contained on the diagnostic tape supplied with the DP11. Instructions for running the diagnostic are included with the program tape (refer to Chapter 5).

# CHAPTER 3 OPERATIONAL PROGRAMMING

# 3.1 INTRODUCTION

The software-related aspects of the DP11 hardware operation are discussed in this chapter. Descriptions of the addressable hardware registers, addressing utilization, Bus Request priorities and interrupt vectors, synchronous timing considerations, and data format are also included.

### **3.2 DEVICE REGISTERS**

The following paragraphs provide the register address assignments, definitions of each register bit, and bit map diagrams for each of the six device registers of the DP11.

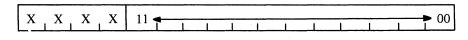

# 3.2.1 Receiver Control and Status Register (RCSR)

| Address: | 774XX0 |

|----------|--------|

|----------|--------|

| •   | 1                 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |    |   |   |     |    |          |    |          |                                                           |

|-----|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----|---|---|-----|----|----------|----|----------|-----------------------------------------------------------|

|     |                   | 12 11          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>→</b> 08 07 | 06 | X | X | 03  | 02 | 01       | 00 |          |                                                           |

| Bit | Bit Designat      | tion Descripti |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |    |   |   | ion | on |          |    |          |                                                           |

| 00  | STRIP SYNC        | the in         | If set, all Sync characters following Receive Active are stripped from<br>the incoming serial data. This bit is Read/Write and cleared by                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |    |   |   |     |    |          |    |          |                                                           |

|     |                   |                | Initia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | lize.          |    |   |   |     |    |          |    |          |                                                           |

| 01  | HALF DUPL         | EX             | K If set, Request to Send On inhibits the Receive logic. This bit is F Write and cleared by Initialize.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |    |   |   |     |    |          |    | is Read/ |                                                           |

| 02  | MAINTENAN<br>MODE | JCE            | CE Maintenance Mode provides an internal data loop that connects the<br>transmitter output to the Receiver input. Additionally, the Clear<br>Send lead is simulated by the hardware. This mode of operation p<br>vides its own clock, which handles data at approximately 3000 bat<br>Maintenance Mode, coupled with the Read and/or Write Status bit<br>exercises approximately 85% of the DP11's logic. This is excluding<br>the EIA converters, modem cable, modem status, and the interrup<br>caused by the modem status. This bit is Read/Write and is cleared<br>by Initialize. |                |    |   |   |     |    |          |    |          | ear to<br>on pro-<br>) baud.<br>s bit,<br>uding<br>rrupts |

| 03  | MISC RECEI        | VE             | Miscellaneous Receive is provided to monitor any nonstandard<br>status required by the user. Changes can be implemented by C<br>Special Systems or by the user. Production units will be wired<br>ondary Receive (i.e., 202D). This bit is Read Only.                                                                                                                                                                                                                                                                                                                                 |                |    |   |   |     |    | Computer |    |          |                                                           |

| Not Used<br>NTR EN<br>RX DONE)          | when the Recei                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                         | when the Recei                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| , e e e e e e e e e e e e e e e e e e e | •                                                                                                                                                                                                                                                                                                                                        | The Receive Done Interrupt Enable allows an "A" interrupt to occur<br>when the Receive Done Flag is set. This bit is Read/Write and is<br>cleared by Initialize.                                                                                                                                                                                |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RECEIVE DONE<br>FLAG<br>RX DONE)        | The Receive Done Flag indicates that the receive buffer contains an assembled character. If the program does not respond to this flag in 1/baud x bits per character, the Receive Overflow Flag will be set causing a "B" interrupt. This bit is Read/Write and is cleared by Initialize and by gating the receive buffer to the Unibus. |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                         | Selects 6, 7, 8, 1                                                                                                                                                                                                                                                                                                                       | 10,1                                                                                                                                                                                                                                                                                                                                            | 1 or 1                                                                                                                                                                                                                                  | 2 bits per character as follows:                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| CHARACTER                               | Da                                                                                                                                                                                                                                                                                                                                       | ta B                                                                                                                                                                                                                                                                                                                                            | its                                                                                                                                                                                                                                     | Select                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                         | 10                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                         | 0                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                       | 8 bits per character                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                         | 0                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                       | 7 bits per character                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                         | 0                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                       | 6 bits per character                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                         | 0                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                       | Not used                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                         | 1                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                       | 12 bits per character                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                         | 1                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                       | 11 bits per character                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                         | . 1                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                       | 10 bits per character                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                         | 1                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                       | Not used                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                         | Sync characters ize. The M7065                                                                                                                                                                                                                                                                                                           | . Th<br>mo                                                                                                                                                                                                                                                                                                                                      | is bit i<br>dule p                                                                                                                                                                                                                      | the hardware recognizes <i>two</i> consecutive<br>is Read/Write Zero and is cleared by Initial-<br>rovides jumpers for operation with one<br>ode of operation is not software supported.                                                           |  |  |  |  |  |  |  |

|                                         | Character Parity (VRC) indicates the parity of the last character as-<br>sembled and contained in the receive buffer. A 1 indicates odd char-<br>acter parity; a 0 indicates even parity. This bit is changed at the same<br>time the Receive Done Flag is set. This bit is Read Only and is cleared<br>by Initialize.                   |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| lot Used                                | Not Applicable                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                         | RX DONE)<br>BITS PER<br>CHARACTER<br>RECEIVE<br>ACTIVE<br>CHARACTER<br>ARITY<br>Not Used                                                                                                                                                                                                                                                 | Causing a "B" in<br>Initialize and by<br>SITS PER Selects 6, 7, 8, 1<br>THARACTER Da<br>10<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>RECEIVE Receive Active is<br>ACTIVE Sync characters<br>ize. The M7065<br>Sync character,<br>CHARACTER Character Parity<br>sembled and con<br>acter parity; a 0<br>time the Receive<br>by Initialize. | causing a "B" intern<br>Initialize and by gatiBITS PER<br>CHARACTERSelects 6, 7, 8, 10, 1<br>Data B10900000001011111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111< | Causing a "B" interrupt. T<br>Initialize and by gating theBITS PER<br>CHARACTERSelects 6, 7, 8, 10, 11 or 1<br>Data Bits09800000101011011011101110111011101110111111111111111111111111111111111111111111111111111111111111111111111111111111111111 |  |  |  |  |  |  |  |

Bit

Description

.00

00-11

Provides a 12-bit Data Buffer Register for each character received from the modem and sent to the DP11.

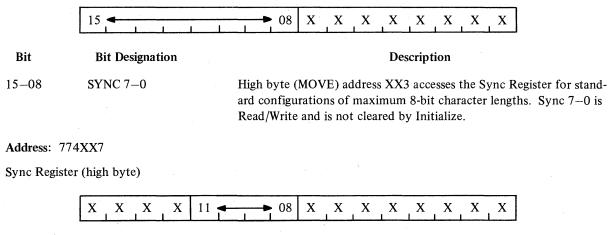

# 3.2.3 Sync Register (Sync)

### Address: 774XX3

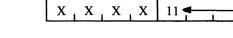

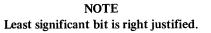

Sync Register (high byte)

| Bit Bit Designation |            | Description                                                                                                                                                                                          |  |  |  |  |  |

|---------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 11-08               | SYNC 11-08 | High byte (MOVE) address XX7 accesses the additional Sync Register<br>for expanded configurations to maximum 12-bit character lengths.<br>Sync 11-08 is Read/Write and is not cleared by Initialize. |  |  |  |  |  |

# 3.2.4 Transmitter Control and Status Register (TCSR)

| Address: 7 | 74XX4 |

|------------|-------|

|------------|-------|

|     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14     | 13     | 12  | 11 | 10     | 09             | Χ               | 07                         | 06             | 05           | 04            | 03             | X             | 01             | 00              |         |                                       |        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----|----|--------|----------------|-----------------|----------------------------|----------------|--------------|---------------|----------------|---------------|----------------|-----------------|---------|---------------------------------------|--------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |        |     |    |        |                |                 |                            |                |              |               |                |               |                |                 |         |                                       |        |

| Bit | Bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t Desi | ignati | ion |    |        |                |                 |                            |                |              | Des           | cript          | ion           |                |                 |         |                                       |        |

| 00  | TE                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RMIN   | AL F   | RDY |    | n<br>t | nunic<br>he es | ation<br>tablis | chan<br>hed c              | nel.<br>all. A | Auto<br>Auto | Dial<br>answe | and a<br>er: a | manu<br>llows | al cal<br>hand | l orig<br>shaki | ination | to the c<br>main<br>esponse<br>llize. | ntains |

| 01  | 01 IDLE SYNC Allows transmission from the Sync Buffer. TRANSMIT DONE is set<br>(if enabled) as the first bit of each data character is presented to the<br>line. If the IDLE SYNC bit is set when the transmitter is inactive, the<br>logic will raise Request to Send and begin transmitting from the Sync<br>Register. Once active, the Transmits Shift Register will be loaded for<br>the Sync Register if the program has <i>not</i> responded to Transmit Done |        |        |     |    |        |                |                 | he<br>, the<br>ync<br>from |                |              |               |                |               |                |                 |         |                                       |        |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |        |     |    |        |                |                 |                            |                |              |               |                |               |                |                 |         | his bit i                             |        |

# NOTE IDLE does not cause TRANSMIT DONE.

Read/Write and is cleared by Initialize.

| Bit | Bit Designation                    | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-----|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|