EK-1184A-TM-PR1

MEM-VMJA

# PRELIMINARY

# PDP-11/84

# SYSTEM INSTALLATION AND TECHNICAL REFERENCE MANUAL

「兼代育」

3

,

# PRELIMINARY PDP-11/84 SYSTEM INSTALLATION AND TECHNICAL REFERENCE MANUAL

Prepared by Educational Services af Digital Equipment Corporation

First Edition, May 1985

© Digital Equipment Corporation 1985.

All Rights Reserved.

Printed in U.S.A.

;

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The manuscript for this book was created on a Digital Word Processing System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital ~ | Micro/PDP-11 | RSX            |

|-----------|--------------|----------------|

| DEC       | MicroVAX     | RT             |

| DECmate   | PDP          | UNIBUS         |

| DECUS     | P/OS         | VAX            |

| DECwriter | Professional | VAXcluster     |

| DIBOL     | Q-Bus        | VMS            |

| LSI-11    | Rainbow      | VT             |

| MASSBUS   | RSTS         | Work Processor |

## TABLE OF CONTENTS

## CHAPTER 1 SYSTEM INTRODUCTION

| 1.1 INTRODUCTION                       |        | •     | • | 1-1  |

|----------------------------------------|--------|-------|---|------|

| 1.2 SYSTEM COMPONENTS AND VARIATIONS   | •      | •     | • | 1-2  |

| 1.2.1 KDJ11-BF Processor Module .      | • •    | •     | • | 1-5  |

| 1.2.2 KTJ11-B UNIBUS Adapter ModulE    | • •    | •     | • | 1-6  |

| 1.2.3 MSV11-JB/JC Memory Module .      |        | •     | • | 1-6  |

| 1.2.4 UNIBUS Terminator                |        | •     | • | 1-6  |

| 1.2.5 Monitor and Distribution Module  | • •    | •     | • | 1-6  |

| 1.2.6 Minimum Load Module              | • •    | •     | • | 1-6  |

| 1.2.7 Power Supply                     | • •    | •     | • | 1-6  |

| 1.2.8 Console Serial Line Board .      | •      | •     | • | 1-7  |

| 1.2.9 Backplane Assembly               |        | •     | • | 1-7  |

| 1.2.10 Front Panel Assembly            | •      | • •   | • | 1-8  |

| 1.2.11 Cabinet Power Controller .      | • •    | •     | • | 1-8  |

| 1.2.12 Cabinet Blower Unit             |        | • •   | • | 1-8  |

| 1.2.13 Box Cooling Fans                |        |       |   | 1-8  |

| 1.2.14 Additional Expansion and Memory | • Opti | lons. | • | 1-8  |

| 1.3 SYSTEM SPECIFICATIONS              | •      | •     | • | 1-9  |

| 1.4 RELATED DOCUMENTS                  | •      | • •   | • | 1-14 |

## CHAPTER 2 SITE PREPARATION AND INSTALLATION

.

| 2.1   | SITE PR  | EPARATI | ON .  |          | •     | •    | •    | •    | •    | •    | •  | 2-1  |

|-------|----------|---------|-------|----------|-------|------|------|------|------|------|----|------|

| 2.1.1 | Cabine   | et Site | Pre   | para     | atio  | n    | •    | •    | •    | •    | •  | 2-1  |

|       | Box S    |         |       |          |       | •    | •    | •    | •    | •    | •  | 2-2  |

|       | SHIPPING |         |       |          |       | •    | •    | •    | •    | •    | •  | 2-4  |

|       | UNPACKI  |         |       |          |       | -    | •    |      | •    | •    | •  | 2-5  |

|       | Cabine   |         |       |          |       |      |      |      |      | •    | •  | 2-5  |

|       | Box U    |         |       |          |       | •    | •    | •    | •    | •    | •  | 2-5  |

|       | SYSTEM 2 | INSTALL | ATIC  | DN .     | •     | •    | •    | •    | •    | •    | •  | 2-5  |

| 2.4.1 |          | et Mech |       |          |       |      |      | •    | •    | •    |    | 2-6  |

|       | Box M    |         |       |          |       |      |      |      |      | •    |    | 2-6  |

| 2.4.3 | Conso    | le Seri | al I  | line     | Hoo   |      |      |      |      |      |    | 2-8  |

|       | Cabine   |         |       |          |       |      | •    | •    | •    | •    |    | 2-9  |

| 2.4.5 | Box S    | witch S | Setti | ngs      | •     | •    | •    | •    | •    | •    | •  | 2-11 |

|       | Cabin    |         |       |          |       |      |      |      |      | •    |    | 2-13 |

| 2.4.7 |          | ower Ho | okup  | <b>)</b> | •     | •    | •    | •    | •    | •    | •  | 2-13 |

| 2.5   |          | CONTROL | S AN  | ID IN    | NDIC. | ATOR | S    | •    | •    | •    | •  | 2-14 |

| 2.5.1 |          | Panel.  |       |          |       |      |      |      |      |      | •  | 2-14 |

| 2.5.2 | Conso    | le Seri | al L  | ine      | Dis   | trib | utio | n Bo | ard  | •    | •  | 2-17 |

| 2.5.3 |          | l Commu | inica | ation    | ns P  | ort  | •    | •    | •    | •    | •  | 2-17 |

| 2.5.4 | Baud 1   | Rate Se | lect  | Swi      | itch  | •    |      | •    | •    | •    | •  | 2-17 |

| 2.6   |          | HARDWAH | RE CC | DNFIC    | GURA  | TION | •    | •    | •    | •    | •  | 2-18 |

| 2.6.1 | KDJ11.   | -BF Mod | ule   | Conf     | Eigu  | rati | on   | •    | •    | •    | •  | 2-19 |

| 2.6.2 | KTJ11-   | -B Modu | le C  | Conf     | igur  | atio | n    | •    | •    | •    | •  | 2-19 |

| 2.6.3 |          | or and  |       |          |       |      |      | Con  | fiau | rati | on | 2-20 |

|       |          |         |       |          |       |      |      |      | 5.   |      |    |      |

PAGE

| 2.6.4 | MSV11-JB/JC Module Configuration      | • | • | • | 2-20 |

|-------|---------------------------------------|---|---|---|------|

| 2.6.5 | Minimum Load Module                   | • | • | • | 2-23 |

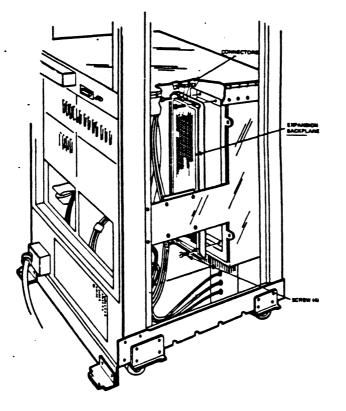

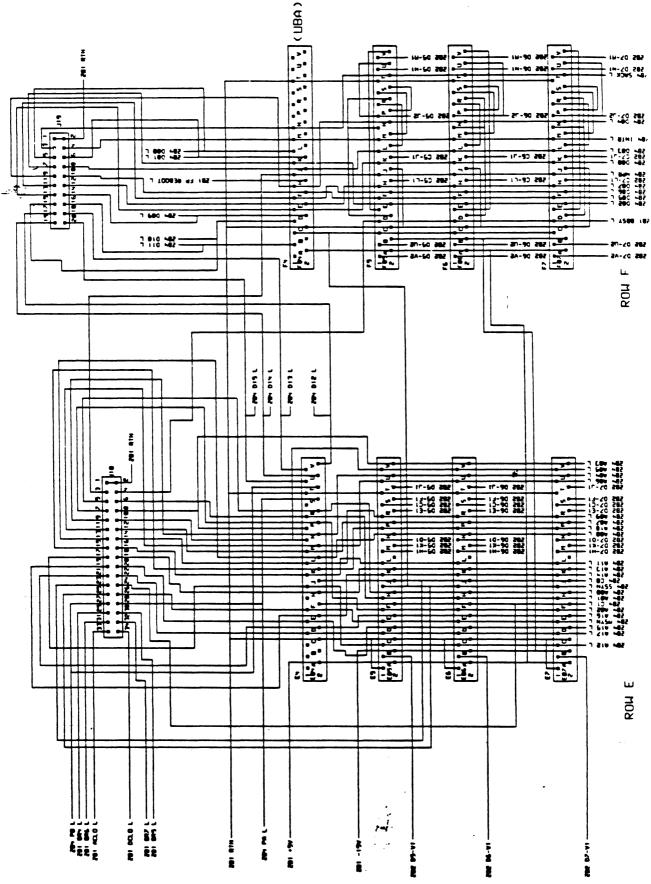

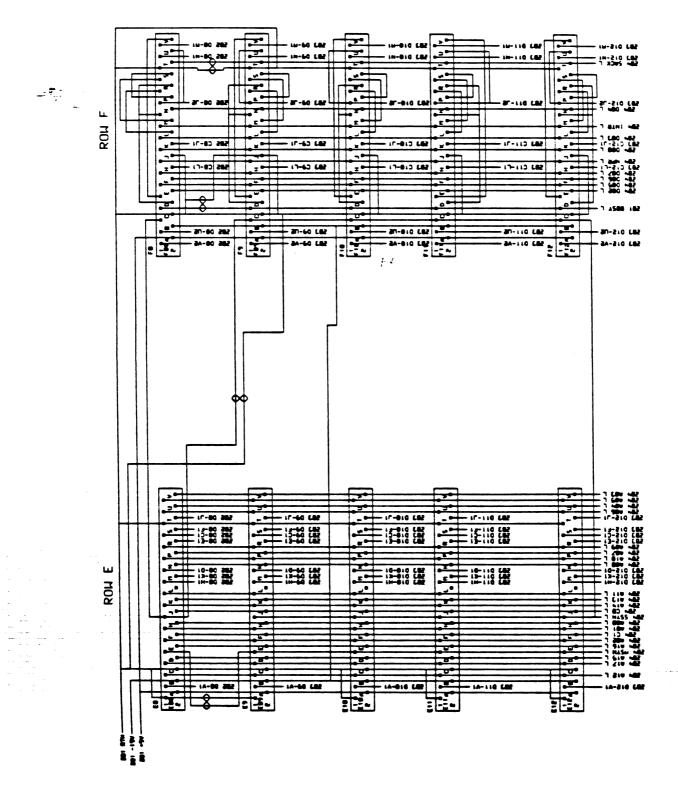

| 2.7   | EXPANSION BACKPLANE INSTALLATION .    | • | • | • | 2-24 |

| 2.7.1 | Expansion Backplane Installation      | • | • | • | 2-25 |

| 2.7.2 | NPG and BG Jumper Lead Routing .      | • | • | • | 2-27 |

| 2.7.3 | Backplane Power Connections           | • | • | • | 2-28 |

| 2.7.4 | SPC Backplane Locations               | • | • | • | 2-31 |

| 2.8   | SPC MODULE INSTALLATION               | • | • | • | 2-31 |

| 2.8.1 | Cabinet SPC Cable Routing             | • | • | • | 2-32 |

| 2.8.2 | Box SPC Cable Routing                 | • | • | • | 2-33 |

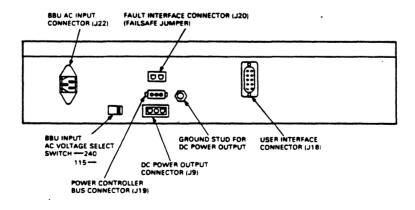

| 2.9   | CABINET BATTERY UP UNIT INSTALLATION  | • | • | • | 2-34 |

| 2.10  | BOX BATTERY BACK UP UNIT INSTALLATION | • | • | • | 3-37 |

CHAPTER 3 FUNCTIONAL DESCRIPTION

| 3.1            |                                                          | • | •    | •   | 3-1          |

|----------------|----------------------------------------------------------|---|------|-----|--------------|

| 3.2            | PMI BUS DESCRIPTION                                      | • | •    | •   | 3-2          |

| 3.2.1          | PMI BUS Acquisition                                      | • | •    | •   | 3-7          |

| 3.2.2          | DMA Requests                                             | • | •    | •   | 3-8          |

| 3.2.3          | PMI BUS Acquisition                                      | • | •    | •   | 3-11         |

| 3.2.4          | PMI Data Transfer Address Cycle .                        |   |      |     | 3-14         |

|                | PMI Data Transfer Protocol                               | - | •    |     | 3-15         |

|                | PMI Data In Cycles (DATI) and (DATIP                     | ) | -    |     | 3-15         |

|                | PMI Block Mode Data In Cycles .                          |   |      |     | 3-17         |

| 3.2.8          |                                                          | • | •    |     | 3-18         |

| 3.3            |                                                          | • | •    |     | 3-19         |

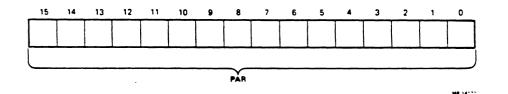

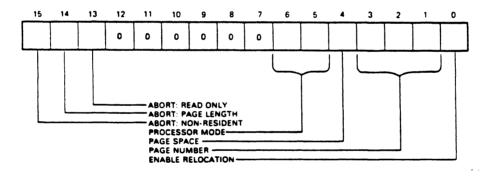

| 3.3.1          |                                                          | • | •    |     | 3-21         |

|                | - J                                                      | • | •    |     | 3-21         |

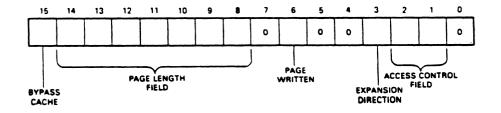

| 3.3.2<br>3.3.3 |                                                          | • | •    | •   | 2-22         |

|                | · · · ·                                                  | • | •    | •   | 3-23         |

| 3.3.4          |                                                          | • | •    | •   | 3-25         |

| 3.3.5          | Memory Management Register 2                             | • | •    | •   | 3-25         |

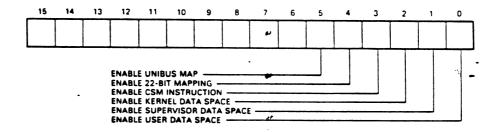

| 3.3.6          | Memory Management Register 3.                            | • | •    | •   | 3-25         |

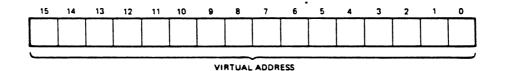

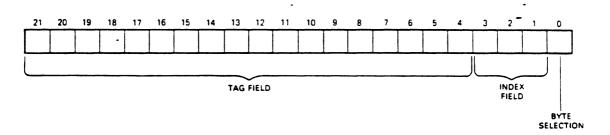

| 3.3.7          | Physical Address Construction                            | • | •    | •   | 3-26<br>3-27 |

| 3.3.8          | Memory Relocation                                        | • | •    | .•. | 3-21         |

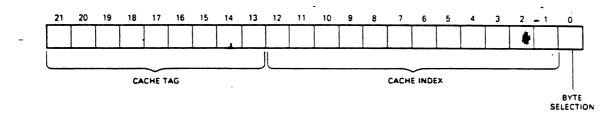

| 3.4            | KDJII-BF CACHE                                           | • | •    | •   | 3-27         |

| 3.4.1          | KDJ11-BF Cache Operations                                | • | •    | •   | 3-29         |

| 3.4.2          | KDJ11-BF Cache Operations<br>KDJ11-BF Cache Organization | • | •    |     | 3-29         |

| 3.4.3          | Cache Control Register                                   | • | •    |     | 3-32         |

| 3.4.4          | Memory System Error Register .                           | • | •    |     | 3-35         |

| 3.4.5          |                                                          | • | •    |     | 3-38         |

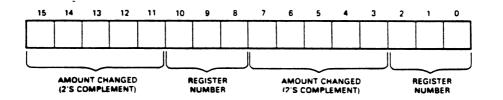

| 3.5            | ADDITIONAL CPU REGISTER DESCRIPTIONS                     | • | •    |     | 3-38         |

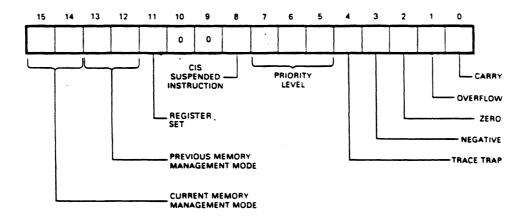

| 3.5.1          | Processor Status Word                                    | • | •    | •   | 3-39         |

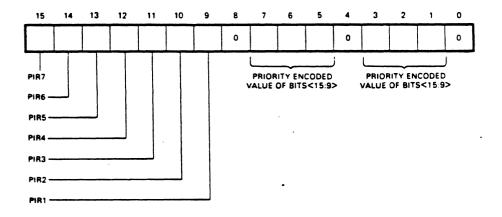

| 3.5.2          | Program Interrupt Request Register                       | • | •    |     | 3-40         |

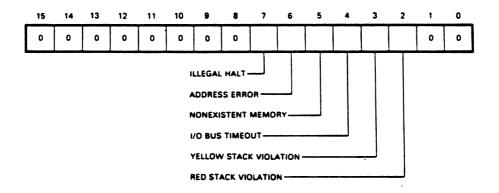

| 3.5.3          | CPU Error Register                                       | • | •    | •   | 3-41         |

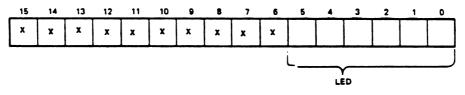

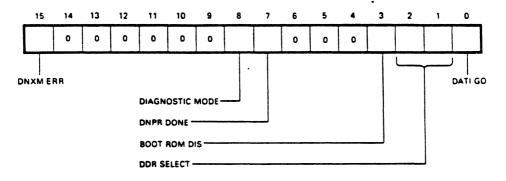

| 3.5.4          | Configuration and Display Register                       | • | •    | •   | 3-42         |

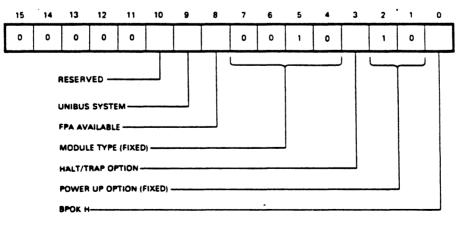

| 3.5.5          | Maintenance Register                                     | • | •    | •   | 3-44         |

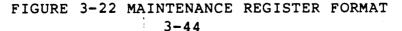

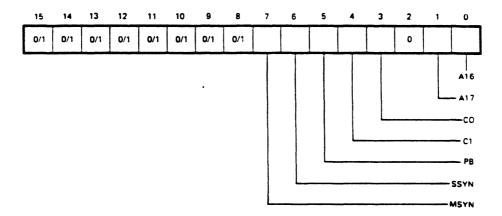

| 3.5.6          |                                                          |   | aist | er  | 3-46         |

| 3.5.7          | Page Control Register                                    |   | •    | •   | 3-49         |

| 3.5.8          |                                                          |   | •    | •   | 3-50         |

| 3.6            | STACK LIMIT PROTECTION                                   | • | •    | •   | 3-52         |

|                | KERNEL PROTECTION                                        | • | •    | •   | 3-52         |

| 3.8            | TRAP AND INTERRUPT SERVICE PRIORITIES                    | • | •    | •   | 3-53         |

|                |                                                          |   |      |     |              |

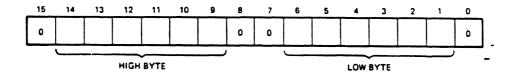

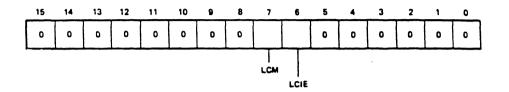

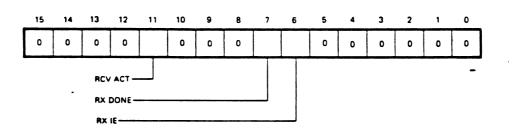

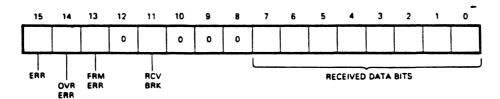

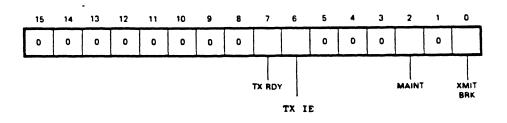

| 3.9.1Receiver Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.9 CONSOLE SERIAL LINE UNIT                  | • | • | 3-54 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|---|------|

| 3.9.3Transmitter Receiver Status Register3-573.9.4Transmitter Data Buffer Register3-583.9.5Break Response3-583.10KERNEL/SUPERVISOR/USER MODE DESCRIPTIONS3-593.11PMG COUNTER3.12KTJ11-BF CACHE OPERATIONS <t< td=""><td>3.9.1 Receiver Status Register</td><td>•</td><td>•</td><td>3-54</td></t<>                                                                                                                                                                                                                   | 3.9.1 Receiver Status Register                | • | • | 3-54 |

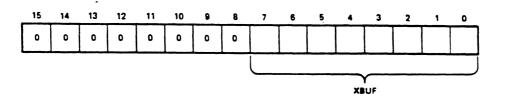

| 3.9.4Transmitter Data Buffer Register3.9.5Break Response3.10KERNEL/SUPERVISOR/USER MODE DESCRIPTIONS3.11PMG COUNTER3.12KTJ11-BF CACHE OPERATIONS3.12.1KTJ11-B Cache Organization3.12.2DMA Cache Enable/Disable3.12.4DMA Cache Write Operations3.13UNIBUS MAPPING3.13.1UNIBUS Mapping Registers3.13.3Memory Configuration Register3.14DIAGNOSTIC AND CONFIGURATION REGISTERS3.14.1Diagnostic Controller Status Register3.14.3Diagnostic DATI NPR Cycles                                                              | 3.9.2 Receiver Data Buffer                    | • | • | 3-56 |

| 3.9.5Break Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.9.3 Transmitter Receiver Status Register.   | • | • | 3-57 |

| 3.10KERNEL/SUPERVISOR/USER MODE DESCRIPTIONS3-593.11PMG COUNTER3-593.12KTJ11-BF CACHE OPERATIONS3-603.12.1KTJ11-B Cache Organization3-613.12.2DMA Cache Enable/Disable3-623.12.3DMA Cache Write Operations3-633.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-713.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.3Diagnostic DATI NPR Cycles3-79   | 3.9.4 Transmitter Data Buffer Register        | • | • | 3-58 |

| 3.11PMG COUNTER<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.9.5 Break Response                          | • | • | 3-58 |

| 3.12KTJ11-BF CACHE OPERATIONS3-603.12.1KTJ11-B Cache Organization3-613.12.2DMA Cache Enable/Disable3-623.12.3DMA Cache Write Operations3-633.12.4DMA Cache Read Operations3-633.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-713.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.3Diagnostic Data Register3-773.14.3Diagnostic DATI NPR Cycles3-79 | 3.10 KERNEL/SUPERVISOR/USER MODE DESCRIPTIONS | • | • | 3-59 |

| 3.12.1KTJ11-B Cache Organization3-613.12.2DMA Cache Enable/Disable.3-623.12.3DMA Cache Write Operations3-633.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers.3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-713.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.3Diagnostic Data Register.3-773.14.3Diagnostic DATI NPR Cycles3-79                                                                  | 3.11 PMG COUNTER                              | • | • | 3-59 |

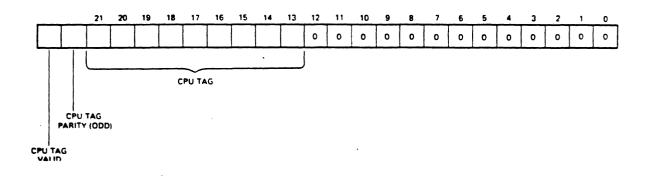

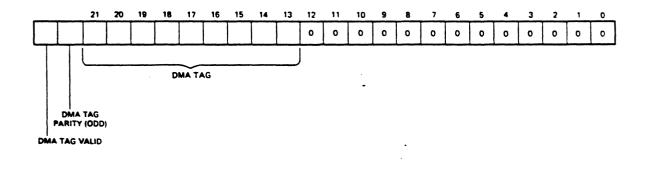

| 3.12.2DMA Cache Enable/Disable.3-623.12.3DMA Cache Write Operations3-633.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers.3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-673.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.3Diagnostic Data Register3-773.14.3Diagnostic DATI NPR Cycles3-79                                                                                                       | 3.12 KTJ11-BF CACHE OPERATIONS                | • | • | 3-60 |

| 3.12.3DMA Cache Write Operations3-633.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-673.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.2Diagnostic Data Register3-773.14.3Diagnostic DATI NPR Cycles3-79                                                                                                                                           | 3.12.1 KTJ11-B Cache Organization             | • | • | 3-61 |

| 3.12.4DMA Cache Read Operations3-633.13UNIBUS MAPPING3-643.13.1UNIBUS Mapping Registers3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-713.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.2Diagnostic Data Register3-773.14.3Diagnostic DATI NPR Cycles3-79                                                                                                                                                                               | 3.12.2 DMA Cache Enable/Disable               | • | • |      |

| 3.13UNIBUS MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.12.3 DMA Cache Write Operations             | • | • |      |

| 3.13.1UNIBUS Mapping Registers.3-653.13.2Optional UNIBUS Memory3-673.13.3Memory Configuration Register3-713.14DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1Diagnostic Controller Status Register3-763.14.2Diagnostic Data Register3-773.14.3Diagnostic DATI NPR Cycles3-79                                                                                                                                                                                                                                       | 3.12.4 DMA Cache Read Operations              | • | • |      |

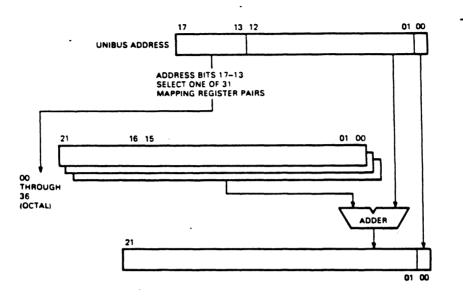

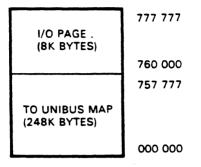

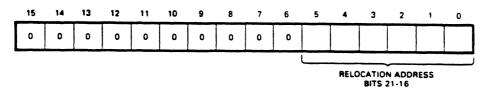

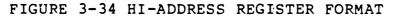

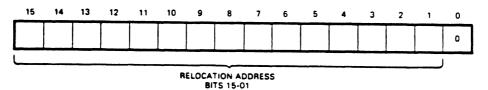

| 3.13.2 Optional UNIBUS Memory3-673.13.3 Memory Configuration Register3-713.14 DIAGNOSTIC AND CONFIGURATION REGISTERS3-763.14.1 Diagnostic Controller Status Register3-763.14.2 Diagnostic Data Register3-773.14.3 Diagnostic DATI NPR Cycles3-79                                                                                                                                                                                                                                                                    |                                               | • | • | 3-64 |

| 3.13.3Memory Configuration Register<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.13.1 UNIBUS Mapping Registers               | • | • | 3-65 |

| 3.14DIAGNOSTIC AND CONFIGURATION REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.13.2 Optional UNIBUS Memory                 | • | • | 3-67 |

| 3.14.1Diagnostic Controller Status Register <td< td=""><td>3.13.3 Memory Configuration Register</td><td>•</td><td>•</td><td>3-71</td></td<>                                                                                                                                                                                                                                                                                                                                                                         | 3.13.3 Memory Configuration Register          | • | • | 3-71 |

| 3.14.2 Diagnostic Data Register <td< td=""><td>3.14 DIAGNOSTIC AND CONFIGURATION REGISTERS</td><td>•</td><td>•</td><td>3-76</td></td<>                                                                                                                                                                                                                                                                                                                                                                              | 3.14 DIAGNOSTIC AND CONFIGURATION REGISTERS   | • | • | 3-76 |

| 3.14.3 Diagnostic DATI NPR Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.14.1 Diagnostic Controller Status Register  | • | • | 3-76 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.14.2 Diagnostic Data Register               | • | • | 3-77 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               | • | • | 3-79 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               | • | • | 3-79 |

CHAPTER 4 BOOTSTRAP AND DIAGNOSTIC ROM PROGRAMMING

| 4.1 INTRODUCTION .      | •     | •     | •     | •   | • | • | • | • | 4-1  |

|-------------------------|-------|-------|-------|-----|---|---|---|---|------|

| 4.2 DIALOG MODE COMMAN  | ID DE | ESCRI | [PTIC | ONS | • | • | • | • | 4-3  |

| 4.2.1 Help Command      | •     | •     | •     | •   | • | • | • | • | 4-6  |

| 4.2.2 Boot Command      | •     | •     | •     | •   | • | • | • | • | 4-7  |

| 4.2.3 List Command      |       | •     |       |     |   | • | • | • | 4-9  |

| 4.2.4 Setup Command     | •     | •     | •     | •   | • | • | • | • | 4-11 |

| 4.2.5 Map Command .     | •     | •     | •     | •   | • | • | • | • | 4-11 |

| 4.2.6 Test Command      | •     |       |       | •   | • | • | • | • | 4-13 |

| 4.3 SETUP MODE COMMANE  | DES   | SCRII | PTIO  | NS  | • | • | • | • | 4-14 |

| 4.3.1 Setup Command 1   | •     | •     | •     | •   | • | • | • | • | 4-16 |

| 4.3.2 Setup Command 2   | •     | •     | •     | •   | • | • | • | • | 4-16 |

| 4.3.3 Setup Command 3   | •     | •     | •     | •   | • | • | • | • | 4-23 |

| 4.3.4 Setup Command 4   | •     | •     | •     | •   | • | • | • | • | 4-26 |

| 4.3.5 Setup Command 5   |       |       | •     | •   | • | • | • | • | 4-29 |

| 4.3.6 Setup Command 6   | •     | •     | •     | •   | • | • | • | • | 4-29 |

| 4.3.7 Setup Command 7   | •     | •     | •     | •   | • | • | • | • | 4-30 |

| 4.3.8 Setup Command 8   | •     | •     | •     | •   | • | • | • | • | 4-30 |

| 4.3.9 Setup Command 9   | •     | •     | •     | •   | • | • | • | • | 4-31 |

| 4.3.10 Setup Command 10 | )     | •     | •     | •   | • | • | • | • | 4-32 |

| 4.3.11 Setup Command 11 |       |       |       | •   |   |   |   | • | 4-33 |

| 4.3.12 Setup Command 12 | 2     | •     | •     | •   | • | • | • | • | 4-33 |

| 4.3.13 Setup Command 13 | }     | •     | •     | •   | • | • | • | • | 4-34 |

| 4.3.14 Setup Command 14 | 1     | •     |       | •   | • | • | • | • | 4-36 |

| 4.3.15 Setup Command 15 |       | •     | •     | •   | • | • | • | • | 4-37 |

| 4.4 DIAGNOSTIC ERROR M  |       | AGES  | •     | •   | • |   |   | • | 4-40 |

| 4.5 BOOTSTRAP PROGRAMS  |       | -     |       | -   | - | - | - |   | 4-40 |

| 4.5.1 Bootstrap List    |       | •     |       | -   | • | • | • | • | 4-42 |

| <b></b>                 | -     | •     | -     | -   | • | • | • | • |      |

|                         |       |       |       |     |   |   |   |   |      |

.

| 4.5.2 | EEPROM Format                            | •    | •    | • | 4-44 |

|-------|------------------------------------------|------|------|---|------|

| 4.5.3 | General Rules For EEPROM User Boots      | •    | •    | • | 4-46 |

| 4.6   | BOOT ROM FACILITY (M9312 compatible)     | •    | •    | • | 4-48 |

| 4.6.1 | Boot ROM Installation                    | •    | •    | ± | 4-49 |

| 4.6.2 | ROM Addresses                            | •    | •    | • | 4-49 |

| 4.6.3 | ROM Formats                              | •    | •    | • | 4-49 |

| 4.6.4 | Single ROM Programs                      | •    | •    | • | 4-50 |

| 4.6.5 | Multiple ROM Programs                    | •    | •    | • | 4-50 |

| 4.6.6 | Program Headers                          | •    | •    | • | 4-50 |

| 4.6.7 | ROM Data Organization                    |      |      |   | 4-52 |

| 4.7   | J11 MICRO ODT                            | •    | •    | • | 4-52 |

| 4.7.1 |                                          | •    | •    | • | 4-54 |

| 4.7.2 | <cr> (ASCII 015) Carriage Return</cr>    | •    | •    | • | 4-54 |

| 4.7.3 | <lf> (ASCII 012) Line Feed</lf>          |      |      |   | 4-54 |

| 4.7.4 | \$ (ASCII 122) Internal Register Des:    | igna | ator | • | 4-55 |

| 4.7.5 | G (ASCII 107) GO                         | •    | •    | • | 4-55 |

| 4.7.6 | P (ASCII 120) Proceed                    | •    | •    | • | 4-56 |

| 4.7.7 | <b>^</b> S (Control-Shift-S) Binary Dump | •    | •    | • | 4-57 |

CHAPTER 5 SYSTEM MAINTENANCE

| 5.1    | INTRODUCTION                               | •    | •   | 5-1  |

|--------|--------------------------------------------|------|-----|------|

| 5.2    | DIAGNOSTIC TYPES                           | •    | •   | 5-1  |

| 5.3    | CONSOLE TERMINAL ERROR MESSAGE FORMAT .    | •    | •   | 5-2  |

| 5.3.1  | Console Error Message Description .        | •    | •   | 5-3  |

| 5.3.2  | Unexpected Trap and MMU Error Code Descr   | ipti | ons | 5-12 |

| 5.3.3  |                                            | -    | •   | 5-13 |

| 5.4    | SYSTEM TROUBLESHOOTING AIDS                | •    | •   | 5-15 |

| 5.4.1  | Front Panel                                | •    | •   | 5-15 |

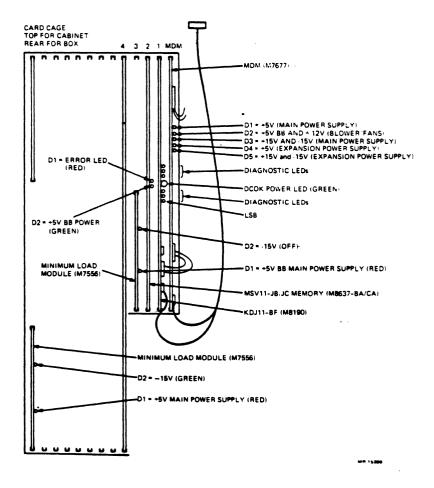

| 5.4.2  | MDM Module                                 | •    | •   | 5-16 |

| 5.4.3  | KDJ11-BF CPU Module                        | •    | •   | 5-19 |

| 5.4.4  | MSV11-JB/JC Memory Module                  | •    | •   | 5-19 |

| 5.4.5  | KTJ11-B UBA Module                         | •    | •   | 5-22 |

|        | Mimimum Load Module                        | •    | •   | 5-23 |

|        | FIELD REPLACEABLE UNITS                    | •    | •   | 5-24 |

| 5.6    | MODULE REPLACEMENT/REMOVAL                 | •    | •   | 5-25 |

| 5.7    | POWER SUPPLY REMOVAL/REPLACEMENT           | •    |     | 5-26 |

| 5.7.1  | Cabinet Power Supply Removal/Replacement   | _    | •   | 5-26 |

| 5.7.2  | Box Power Supply Removal/Replacement       | •    | •   | 5-28 |

| 5.8    | CABINET BLOWER REMOVAL/REPLACEMENT .       | •    | •   | 5-30 |

|        | BOX FAN REMOVAL/REPLACEMENT                | •    | •   | 5-31 |

| 5.10   | FRONT PANEL REMOVAL/REPLACEMENT            | •    | •   | 5-32 |

| 5.10.  | l Cabinet Front Panel Removal/Replacement  | •    |     | 5-32 |

| 5.10.2 | 2 Box Front Panel Removal/Replacement .    | •    | •   | 5-33 |

| 5.11   | CIRCUIT BREAKER REMOVAL/REPLACEMENT .      | •    | •   | 5-34 |

| 5.11.  | l Cabinet Circuit Breaker Removal/Replacem | nent | •   | 5-34 |

| 5.11.  | 2 Box Circuit Breaker Removal/Replacement  | •    | •   | 5-35 |

| 5.12   | CABINET POWER CONTROLLER REMOVAL/REPLACEME | INT  | •   | 5-36 |

| 5.13   | SLU INTERFACE ASSEMBLY REMOVAL/REPLACEMENT | 7    | •   | 5-37 |

| 5.13.  | l Cabinet SLU Assembly Removal/Replacement | :    | •   | 5-37 |

| 5.13.  |                                            | •    | •   | 5-39 |

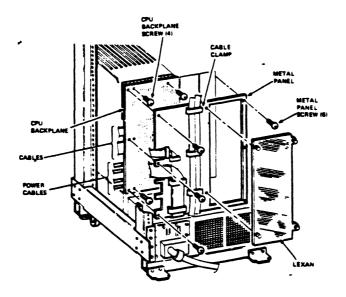

| 5.14   | CPU BACKPLANE REMOVAL/REPLACEMENT          | •    | •   | 5-39 |

|        | l Cabinet Backplane Removal                | •    | •   | 5-40 |

|        |                                            |      |     |      |

. •

#### CHAPTER 1

#### SYSTEM INTRODUCTION

#### 1.1 INTRODUCTION

The A Series PDP-11/84 (PDP-11/84-A) is a high performance computer containing a J11 microprocessor with floating point accelerator (FPA). The processor executes the PDP-11 instruction set. The system operates on Digital Equipment Corporation's 18-bit UNIBUS with a 22-bit memory addressing capabiltiy.

The system is available in two configurations:

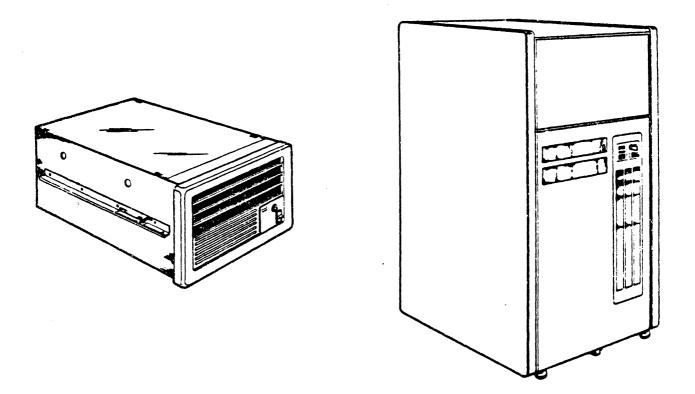

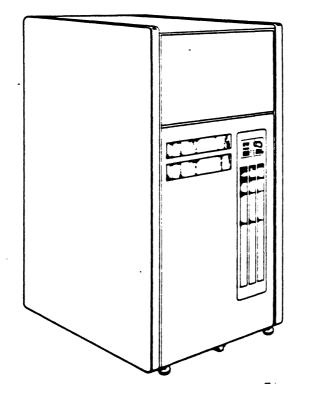

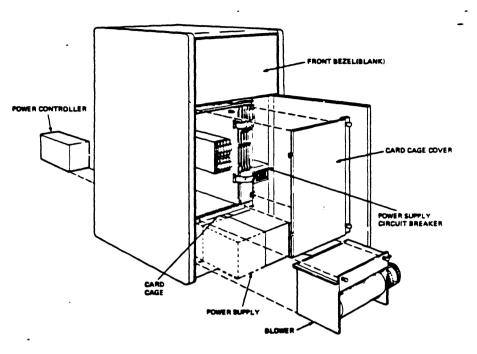

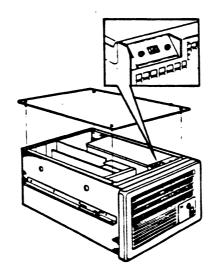

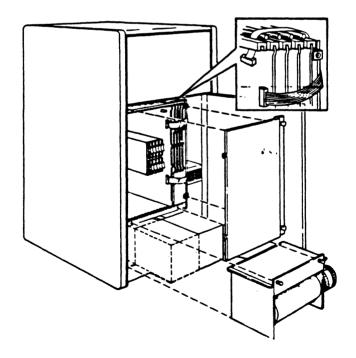

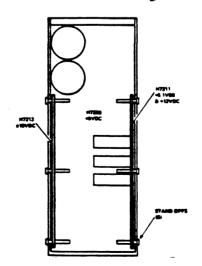

- a. PDP-11X84: a kernel system configuration packaged in a 41-inch cabinet. (See Figure 1-1.) The top portion of the cabinet provides a 10.5-inch enclosure for installing peripherals.

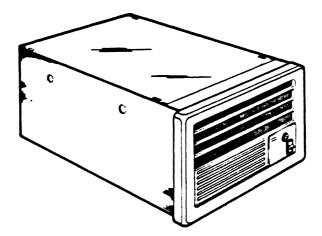

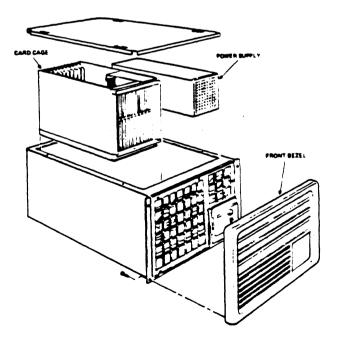

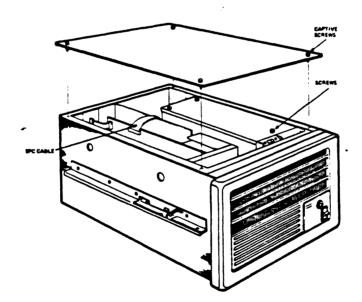

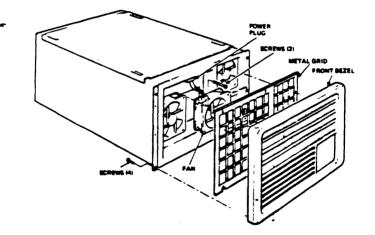

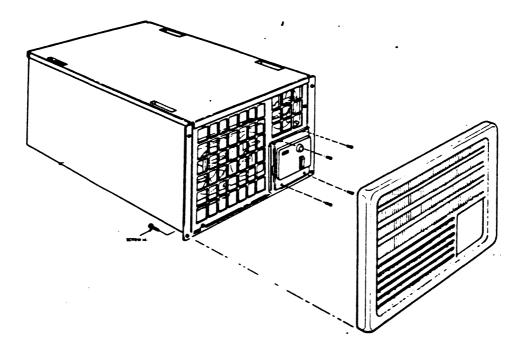

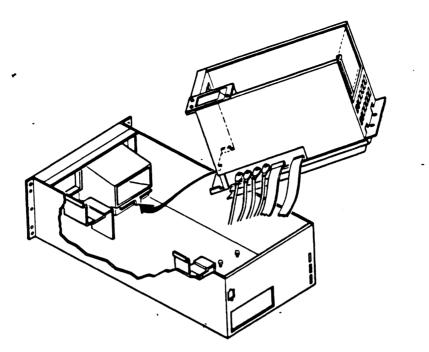

- b. PDP-11/84: an expansion box kernel system configuration packaged in a 10.5-inch rackmountable enclosure. (See Figure 1-2.)

NOTE

The "PDP-11/84" system designation as used in this manual implies that the context applies to both cabinet and box configurations.

FIGURE 1-1 PDP-11X84 CABINET PRODUCT

FIGURE 1-2 PDP-11/84 BOX PRODUCT

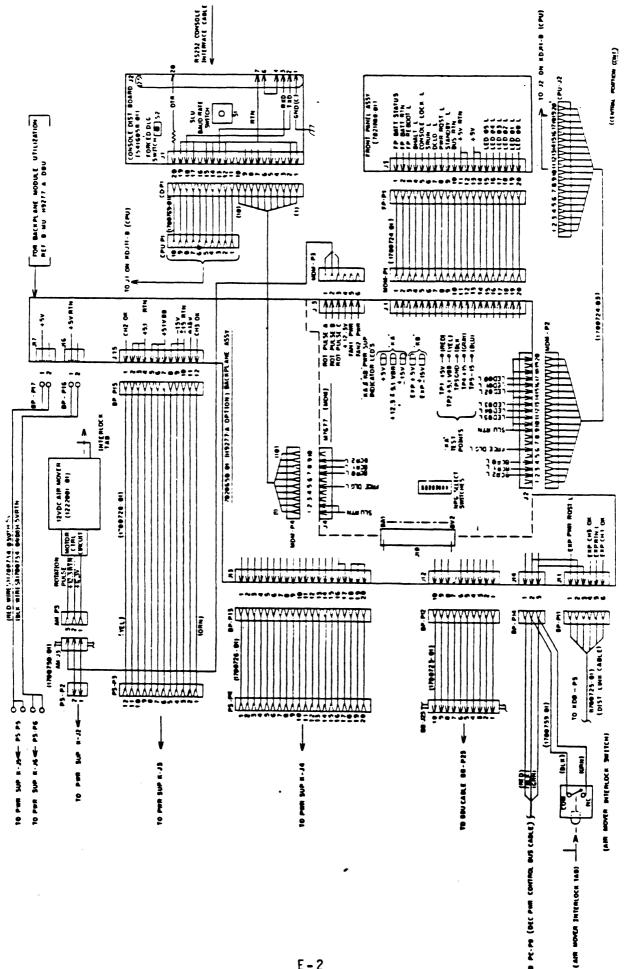

#### 1.2 SYSTEM COMPONENTS AND VARIATIONS

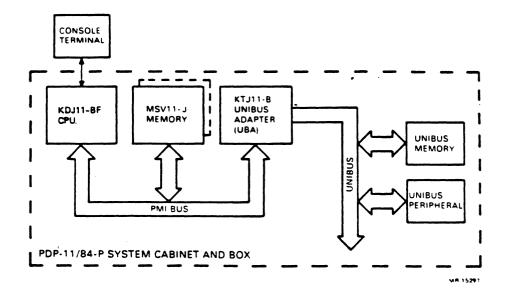

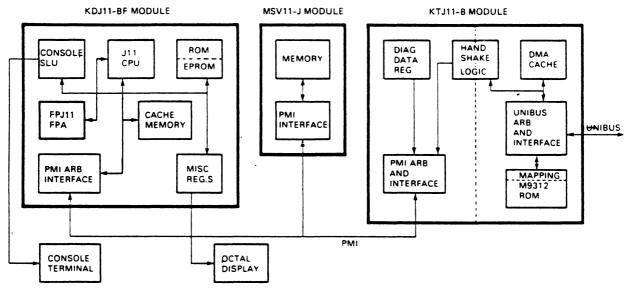

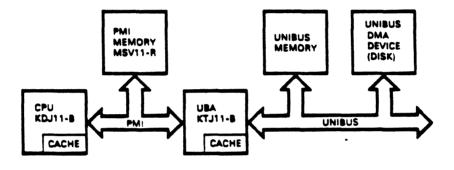

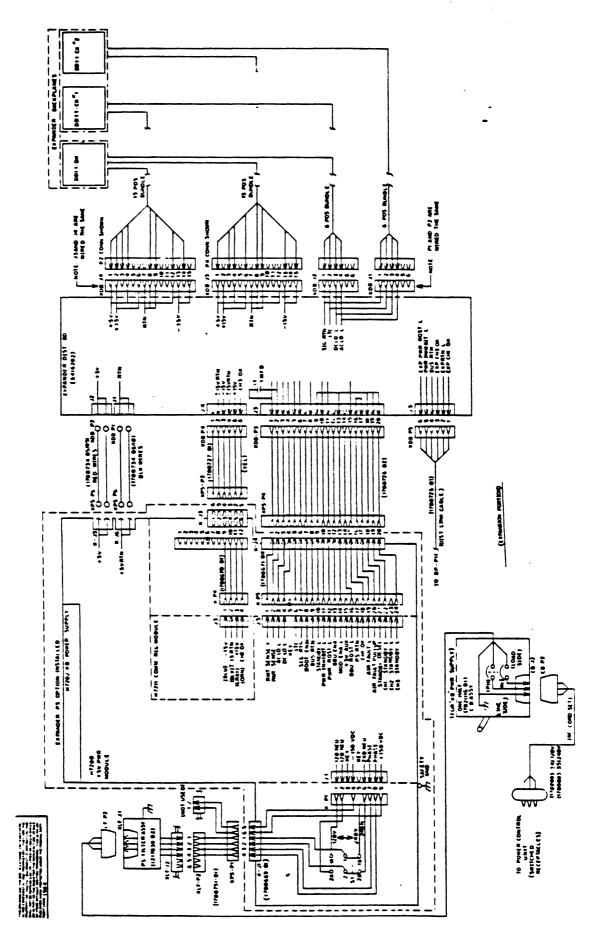

The system block diagram for the cabinet and box product is shown in Figure 1-3. The kernel system consists of:

- 1. A KDJ11-BF processor module (CPU),

- An MSV11-JB 1 Mb ECC memory module(s), or an MSV11-JC 2 MB ECC memory module(s),

- 3. A KTJ11-B UNIBUS Adapter Module (UBA),

- 4. A Monitor and Distribution module (MDM), and

- 5. One or more Minimum Load Modules (MLM).

The modules communicate through the high-speed Private Memory Interconnect (PMI) bus using 22-bit address/16-bit data lines.

A console port supporting the EIA RS-232 communication standard enables a console terminal to be connected into the KDJ11-B processor module.

The KTJ11-B UBA interfaces to the PMI bus and the UNIBUS. The UBA module supports all address/data communications between the processor memory and all UNIBUS periherals (options). In addition, the UBA serves as a terminator for the CPU end of the UNIBUS.

FIGURE 1-3 PDP-11/84 SIMPLIFIED BLOCK DIAGRAM

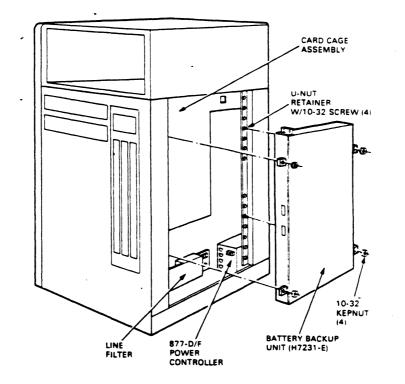

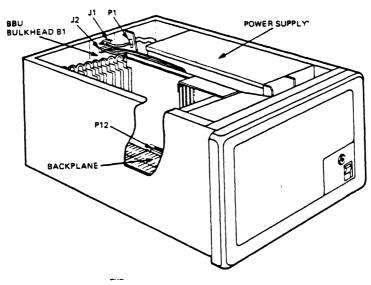

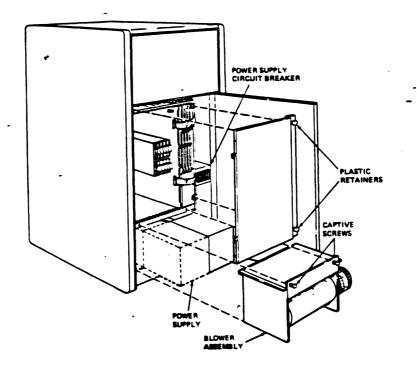

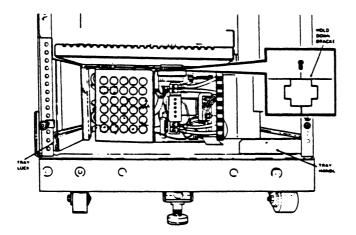

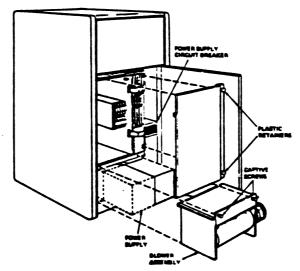

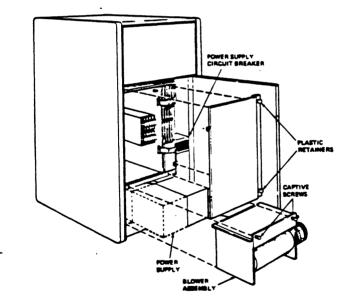

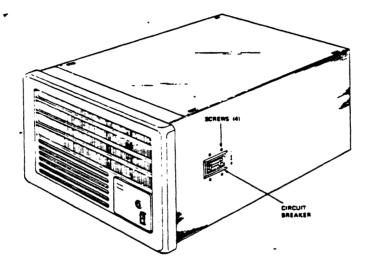

The basic cabinet and box components are shown in Figures 1-4 and 1-5. The following subsections briefly describe the basic system components.

# FIGURE 1-4 BASIC CABINET HARDWARE COMPONENTS

FIGURE 1-5 BASIC BOX HARDWARE COMPONENTS

1-4

Table 1-1 specifies the system variations.

TABLE 1-1 A-SERIES PRODUCT VARIATIONS VARIATION DESCRIPTION \_\_\_\_\_\_ KDJ11-BF, MSV11-JB 1 MB 11/84-AA 10.5-inch Box, 120 Vac KDJ11-BF, MSV11-JB 1 MB 11/84-AB 10.5-inch Box, 240 Vac Same as -AA except MSV11-JC 2 MB 11/84-BA Same as -AB except MSV11-JC 2 MB 11/84-BB 11X84-AA KDJ11-BF, MVS11-JB (JD) 1 MB 40-inch cabinet, 120 Vac 11X84-AB KDJ11-BF, MSV11-JB (JD) 1 MB 40-inch cabinet, 240 Vac Same as -AA except MSV11-JC 2 MB 11X84-BA 11X84-BB Same as -AB except MSV11-JC 2 MB

#### 1.2.1 KDJ11-BF Processor Module

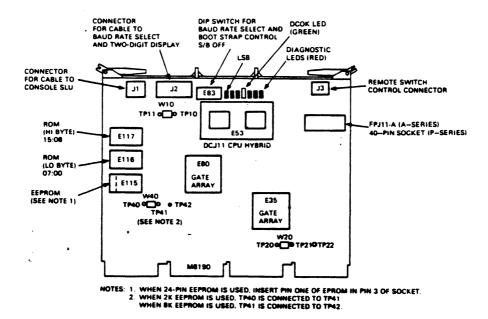

The KDJll-BF (M8190-AE) is a quad-height CPU module having the complete functionality of a PDP-ll processor. The KTJll-B UNIBUS Adapter Module allows the CPU to interface with Digital's UNIBUS.

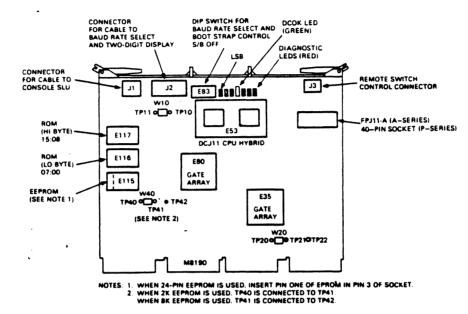

The module features a: Jll microprocessor, FPA, 22-bit memory management, 8KB cache memory, programmable line frequency clock, console serial line unit, an alterable configuration EEPROM, and boot and diagnostic ROMs.

In addition the KDJll-BF has six red LED's for displaying diagnostic information during power-up and bootstrapping. A single green LED indicates dc power to the module.

#### 1.2.2 KTJ11-B UNIBUS Adapter Module

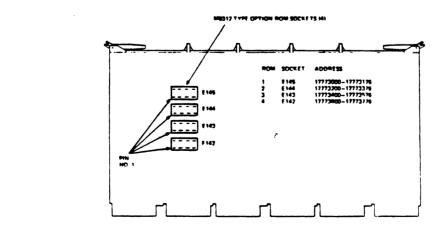

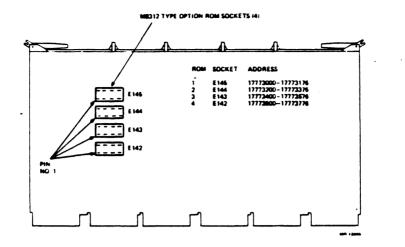

The KTJ11-B UNIBUS Adapter (M8191) is a hex-height module that interfaces with the KDJ11-BF processor and memory through the PMI. The module contains: the PMI adapter logic, UNIBUS mapping, and four M9312 compatible boot ROM sockets.

#### 1.2.3 MSV11-JB/JC Memory Module

The quad-height memory module uses 256K dynamic RAMs, and is available in two versions:

- 1. MSV11-JB (M8637-B) with a 1MB capacity

- 2. MSV11-JC (M8637-C) with a 2MB capacity

The modules provide error correction logic, and supports write byte/word, double-word read, and block mode read operations over the PMI bus. A red LED indicates the occurance of an uncorrectable error; a green LED indicates the presence of 5 Vdc power.

#### 1.2.4 UNIBUS Terminator

The UNIBUS Terminator (M9302) is a resistive network with a characteristic impedance of 120 ohms. The module terminates one end of the UNIBUS and provides the SACK turnaround feature.

#### 1.2.5 Monitor and Distribution Module

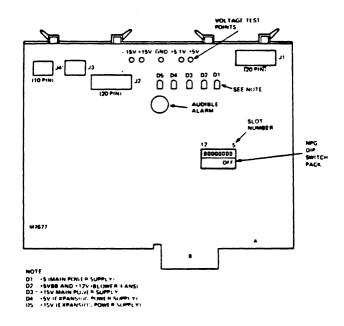

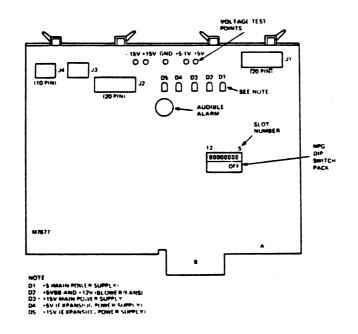

The Monitor and Distribution Module (MDM) is a guad-height module (M7677) and includes: power supply voltage indicators, voltage test points, fan/blower rotation monitor and nonprocessor grant (NPG) jumper selection switches.

#### 1.2.6 Mimimum Load Module

The double-height Minimum Load Modules (MLM) provide a minimum load for the -15 Vdc and +5 VBB power supply regulators. Each module includes two power supply LEDs, one for each regulator.

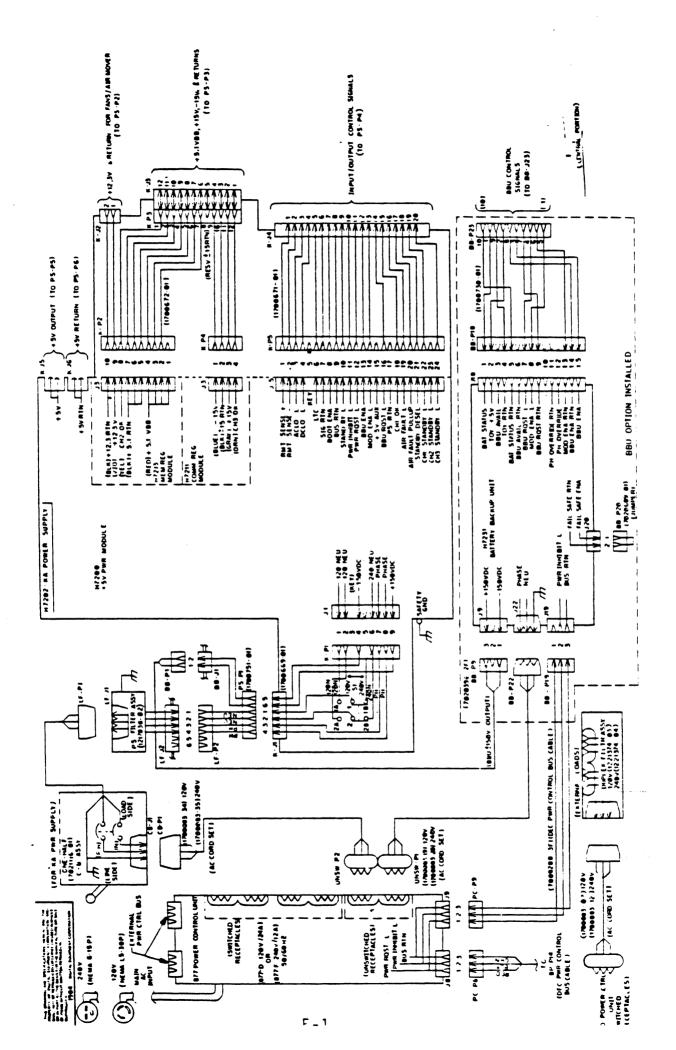

#### 1.2.7 Power Supply

Dc system power is provided by two power supplies: H7202-KA and H7202-KB.

The H7202-KA power supply provides: 60 A at +5 Vdc, 2A at +15 Vdc, +3 A at -15 Vdc. It also provides 3 A at +12 Vdc for fans/blower and up to 15 A at +5 Vdc to the PMI memory. There are 272 watts available for the user when one memory module is used, and 252 watts available when with two memory modules are used. The power supply provides overvoltage and over- heating protection. A switch allows the user to select either 120 Vac or 240 Vac primary power operation.

The H7202-KB power supply provides power for additional (i.e., expansion) backplanes. Similar to the H7202-KA, it can be operated at 120 or 240 Vac, and features overvoltage and overheating protection. The power supply - which connects to the 877-D/F - provides the following power: 32 A at +5 Vdc, 2 A at +15 Vdc, and 3 A at -15 Vdc

#### 1.2.8 Console Serial Line Board

The console serial line board (54-16058-) provides: an EIA RS232-C I/O port for communication with the KDJ11-B, a ten-position rotary switch for selecting the console I/O port baud rate, and a two-position position switch for selecting a restart mode.

#### 1.2.9 Backplane Assembly

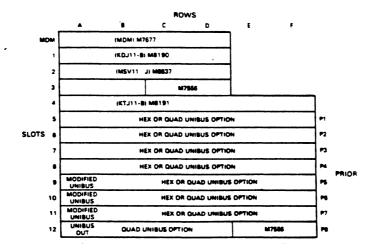

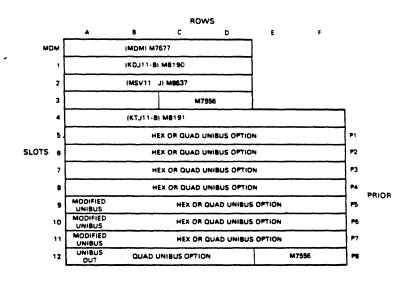

As shown in Figure 1-6, the backplane assembly (70-20650-01) is a 13-module slot backplane. Module slots MDM through 4 are dedicated to the system kernel. Slots 5 through 11 support hexor quad-height Small Peripheral Controllers (SPCs). Slot 12 supports only quad-height UNIBUS option modules. Backplane NPG jumper functions, for slots 5 through 12 are implemented in a DIP switch located on the MDM module.

FIGURE 1-6 BACKPLANE ASSEMBLY

#### 1.2.10 Front Panel Assembly

The front panel assembly (70-21888-01) includes switches and indicators for status display and operator control of the system. A keyed rotory switch selects one of four power states, and a toggle switch selects system halt or restart modes. In addition, three LEDs display the system status, and a two-digit octal LED displays diagnostic error status.

#### 1.2.11 Cabinet Power Controller

The cabinet contains either an 877-D power controller for 120 Vac operation, or an 877-F controller for 240 Vac operation. The unit controls all AC power entering the cabinet. It provides primary power for all the power supplies, and the two AC outlets located in the top peripheral enclosure.

#### 1.2.12 Cabinet Blower Unit

The cabinet is cooled by a blower unit (12-22001-01) mounted below the card cage. Air is drawn through the top front of the cabinet, forced through the card cage by a plenum, through the power supply, and out through the rear of the cabinet.

The blower is capable of cooling the optional expansion kit power supply and an optional UNIBUS backplane. The card cage cover must be installed during operation to insure proper module cooling.

#### 1.2.13 Box Cooling Fans

The box product is cooled by three fans mounted behind the front bezel. The fans draw air through the front bezel and a plenum directs the air horizontally through the card cage and power supply, and out the rear of the box.

#### 1.2.14 Additional Expansion and Memory Options

The system supports the following options:

- a. H7231-E, Cabinet Battery Back Up Unit (requires M7677-YA)

- b. H7231-F, Box Battery Back Up Unit (requires M7677-YA)

- c. DDll-CK, 4-slot Backplane (PDP-11X84)

- d. DD11-DK, 9-slot Backplane (PDP-11X84)

#### **1.3 SYSTEM SPECIFICATIONS**

The following tables list the PDP-11/84 system specifications. Table 1-2 through Table 1-4 list the cabinet specifications; Table 1-5 through Table 1-7 list the box specifications. Supported peripheral device specifications are contained in the user's guide associated with that device.

TABLE 1-2 CABINET ENVIRONMENTAL SPECIFICATIONS

| Characteristic                             | Description                                                                                                            |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Temperature:<br>Operating                  | l0 deg C to 40 deg C<br>(50 deg F to 104 deg F)                                                                        |

| Nonoperating<br>(storage)                  | -40 deg C to 66 deg C<br>(-40 deg F to 151 deg F)                                                                      |

| Humidity:<br>Operating                     | 10% to 90% with max wet bulb temp.<br>28 deg C (82 deg F) and a min dew<br>point 2 deg C (36 deg F) non<br>condensing. |

| Vibration                                  |                                                                                                                        |

| Operating                                  | 5 to 22 Hz:0.01 in DA; 22 to 500 Hz<br>0.25 Gpk. Sweep rate of 1.0<br>octave/min. All three axis.                      |

| Nonoperating<br>(packed for<br>shipment)   | Vertical Axis Random Vibration: 0.687<br>Grms overall from 10 to 200 Hz;<br>duration: 1 hr each axis.                  |

| Altitude:                                  | _                                                                                                                      |

| Operating                                  | 0 to 2.4 km (8000 ft)                                                                                                  |

| Nonoperating                               | 9.1 km (30000 ft)                                                                                                      |

| Maximum operating<br>with altitude         | maximum operating (40 deg C) should<br>be reduced 1.8 deg C/ 1000m<br>(1 deg F/ 1000 ft) above sea level               |

| Shock:                                     | (I deg r/ 1000 It) above sea level                                                                                     |

| Operating                                  | 10 Gpk for 10 ms (+3 ms), 1/2 sine wave, vertical axis only                                                            |

| Nonoperating<br>(packaged for<br>shipment) | Flat drop from a 6 in height, three<br>drops total (vertical direction only)                                           |

•

| Characteristic     | Description                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------|

| Overall dimensions | 105.7 cm high X 53.9 cm wide X<br>76.2 cm long (41.64 in high X<br>21.25 in wide X 30 in long) |

| Weight:            |                                                                                                |

| Unpacked           | 150.5 kg (331 lb)                                                                              |

| Packed             | 182.2 kg (401 1b)                                                                              |

|                    |                                                                                                |

TABLE 1-3 CABINET MECHANICAL SPECIFICATIONS

·

## TABLE 1-4 CABINET ELECTRICAL SPECIFICATIONS

| Characteristics                    | Description                                                                |

|------------------------------------|----------------------------------------------------------------------------|

| 120 Vac operation:<br>Line voltage | 93 - 132 Vrms, single-phase, two-wire<br>and ground (120 Vrms nominal)     |

| Frequency                          | 47.5-63 Hz                                                                 |

| Current (ac)                       | 13.5 A (rms) max at 120 Vac                                                |

| Power factor                       | Greater than 0.60 at full output load and low input voltage (93)           |

| Start Up Current                   | 100 A, 0.16 usec duration                                                  |

| Inrush current                     | 160 A (peak) max at 120 Vac, 0.16 usec duration                            |

| Power                              | 2880 V-A max*                                                              |

| BTU                                | 3519                                                                       |

| 240 Vac operation:<br>Line voltage | 186 - 264 Vrms, single-phase,<br>two-wire and ground (240 Vrms<br>nominal) |

| Frequency                          | 47.5-63 Hz                                                                 |

| Current (ac)                       | 6.7 A (rms) max at 240 Vac                                                 |

TABLE 1-4 (Cont)

| Power factor     | Greater than 0.60 at full output load and low input voltage (186 Vac) |

|------------------|-----------------------------------------------------------------------|

| Start Up Current | 50 A, 0.16 usec duration                                              |

| Inrush current   | <pre>160 A (peak) max at 240 Vac, 0.16 usec duration</pre>            |

| Power            | 2880 V-A max*                                                         |

| BTU              | 3519                                                                  |

Noise Transient: (both line voltages)

| High-energy     | lKV peak spike containing not more |

|-----------------|------------------------------------|

| transients      | than 0.2 W of energy per spike     |

| Conducted noise | CW-10 KHz to 30 MHz 3 Vrms         |

Conducted noise CW-10 KHz to 30 MHz, 3 Vrms

\* Including mass storage devices

--

#### TABLE 1-5 BOX ENVIRONMENTAL SPECIFICATIONS

| * * * * * * * * * * * * * * * * * * |                                                                                                                        |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Characteristic                      | Description                                                                                                            |

|                                     |                                                                                                                        |

| Temperature:                        |                                                                                                                        |

| Operating                           | 5 deg C to 50 deg C<br>(41 deg F to 122 deg F)                                                                         |

| Nonoperating<br>(storage)           | -40 deg C to 66 deg C<br>(-40 deg F to 151 deg F)                                                                      |

| Humidity:                           |                                                                                                                        |

| Operating                           | 10% to 95% with max wet bulb temp.<br>32 deg C (82 deg F) and a min dew<br>point 2 deg C (36 deg F) non<br>condensing. |

|                                     |                                                                                                                        |

SYSTEM INTRODUCTION

TABLE 1-5 (Cont)

| Vibration:                               |                                                                                                          |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Operating .                              | 5 to 30 Hz: 0.01 in DA; 30 to 500 Hz<br>0.5 Gpk. Sweep rate of 1.0<br>octave/min. All three axes.        |

| Nonoperating<br>(packed for<br>shipment) | Vertical Axis Random Vibration: 0.68<br>Grms overall from 10 to 200 Hz;<br>duration: 1 hr each.          |

| Altitude:                                |                                                                                                          |

| Operating                                | 0 to 2.4 km (8000 ft)                                                                                    |

| Nonoperating                             | 9.1 km (30000 ft)                                                                                        |

| Shock:                                   |                                                                                                          |

| Operating                                | <pre>10 Gpk for 10 ms (+3 ms), 1/2 sine wave, vertical axis only</pre>                                   |

| Nonoperating                             | Flat drop from a 6 in height, three<br>drops total (vertical direction only                              |

| Maximum<br>operating with<br>altitude    | Maximum operating (40 deg C) should<br>be reduced 1.8 deg C/ 1000m<br>(1 deg F/ 1000 ft) above sea level |

TABLE 1-6 BOX MECHANICAL SPECIFICATIONS

.

| Characteristic     | Description                                                                            |

|--------------------|----------------------------------------------------------------------------------------|

| Mechanical:        |                                                                                        |

| Overall dimensions | 47 cm wide X 67.5 cm long X<br>26 cm high (19 in wide X 27 in<br>long X 10.44 in high) |

| Weight:            |                                                                                        |

| Unpacked           | 42.75 kg (95 lb)                                                                       |

| Packed             | 59 kg (130 lb)                                                                         |

|                    | 1-12                                                                                   |

.

| Characteristic     | Description                                                                |

|--------------------|----------------------------------------------------------------------------|

| 120 Vac operation: |                                                                            |

| Line voltage       | 90 - 132 Vrms, single-phase, two-wire<br>and ground (120 Vrms nominal)     |

| Frequency          | 47.5 - 63 Hz                                                               |

| Current (ac)       | 8.0 A (rms) max at 120 Vac                                                 |

| Power factor       | Greater than 0.60 at full output load<br>and 120 Vac nominal input voltage |

| Start Up Current   | 50 A, 0.16 usec duration                                                   |

| Inrush current     | 80 A (peak) max at 120 Vac, 0.16 usec duration                             |

| Power              | 650 W MAX                                                                  |

| BTU                | 2218                                                                       |

| 240 Vac operation: |                                                                            |

| Line voltage       | 180 - 264 Vrms, single-phase,<br>two-wire and ground (240 Vrms<br>nominal) |

| Frequency          | 47.5 - 63 Hz                                                               |

| Current (ac)       | 5.0 A (rms) max at 240 Vac                                                 |

| Power factor       | Greater than 0.60 at full output load<br>and 240 Vac nominal input voltage |

| Start Up Current   | 50 A, 0.16 usec duration                                                   |

| Inrush current     | 80 A (peak) max at 240 Vac, 0.16 usec duration                             |

| Power              | 650W MAX                                                                   |

| BTU                | 2218                                                                       |

|                    |                                                                            |

### TABLE 1-7 BOX ELECTRICAL SPECIFICATIONS

•

TABLE 1-7 (Cont)

# ------

| Noise transient:<br>(both line voltages | )                                                                        | - |

|-----------------------------------------|--------------------------------------------------------------------------|---|

| High-energy<br>transients               | l KV peak spike containing<br>not more than 0.2 W of<br>energy per spike |   |

| Conducted noise                         | CW-10KHz to 30 MHz, 3Vrms                                                |   |

## 1.4 RELATED DOCUMENTS

Table 1-8 lists the related PDP-11/84 related documents.

| ORDER NUMBER         |

|----------------------|

|                      |

| EB-17525-20          |

| EK-1184A-TM          |

| EK-PDP84-IN          |

| t                    |

| MP-02199<br>MP-02198 |

| MF-02190             |

| EK-KDJ1B-UG          |

| EK-MSVlJ-UG          |

| EJ-01387-92          |

| EK-DCJ11-UG          |

| EB-26085-41/         |

|                      |

TABLE 1-8 PDP-11/84 RELATED DOCUMENTS

.

\_

Printed copies of the above listed documents may be ordered from:

Digital Equipment Corporation

444 Whitney Street

Northboro, Massachusetts 01532

ATTN: Printing and Circulation Services (NR2/M15)

Customer Services Section

-

#### CHAPTER 2

. . . . . .

#### SITE PREPARATION AND INSTALLATION

This chapter describes how to prepare your site, unpack and install the system, and verify its operational readiness.

2.1 SITE PREPARATION

In order to use a PDP-11/84 system; the space requirement, environmental operating limits and the electrical power, available at the site, should be part of the site preparation. The specifications are listed in the following subsections.

2.1.1 Cabinet Site Preparation Specifications

Physical Space Requirements:

| Width  | 53.25 cm (21.2 in) |

|--------|--------------------|

| Height | 105 cm (41.6 in)   |

| Depth  | 75 cm (31.5 in)    |

| Weight | 150 kg (331 lb)    |

Environmental Operating Limits:

- a. Operating Temperature: 10 deg C to 40 deg C ( 50 deg F to 104 deg F)

- b. Relative Humidity: 10% to 90% with max wet bulb temp. 28 deg C (82 deg F) and min dew point 2 deg C (36 deg F) non-condensing

- c. Storage Temperature: -40 deg C to 66 deg C (-40 deg F to 151 deg F)

2-1

d. Temperature Derating with Altitude: maximum allowable operating temperature should be reduced by 1.8 deg C per every 1000 m the system is operated above sea level. (1 deg F per 1000 ft)

AC Electrical Power Requirement:

Depending on the site line voltage, two power controllers are available:

877-D Power Controller: Voltage - 120 Vac Nominal (93 to 132 Vrms)

Frequency - 47.5 to 63 HZ

877-F Power Controller: Voltage - 240 Vac Nominal (186 to 264 Vrms)

Frequency - 47.5 to 63 HZ

#### NOTE

A dedicated circuit from the power source is recommended for each system. This circuit should provide an isolated ground path between the receptacle an the power source. The power system should be stable and free form electrical noise.

Do not connect any equipment such as air conditioners, office copiers, or coffee pots, on the same circuit with the system.

The user must supply the following AC electrical power and receptacle(s).

NEMA AC Electrical Receptacle Required:

a. for 120V service: NEMA L5-30R (rated @ 30 A).

b. for 240V service: NEMA 6-15R (rated @ 15 A).

The power cord provided is approximately 14 feet long, with either a NEMA L5-30P, or a 6-15P plug attached.

2.1.2 Box Site Preparation Specifications

#### SITE PREPARATION AND INSTALLATION

Physical Space Requirements:

Width 47.5 cm (19.0 in) Height 26 cm (10.4 in) Depth 67.5 cm (27.0 in) Weight 43 kg (95 lb)

Environmental Operating Limits:

a. Operating Temperature: 5 deg C to 50 deg C (41 deg F to 122 deg F)

.

- b. Relative Humidity: 10% to 95% with max wet bulb temp. 32 deg C (90 deg F) and minimum dew point 2 deg C (36 deg F) non condensing

- c. Storage Temperature: -40 deg C to 66 deg C (-40 deg F to 151 deg F)

- d. Temperature Derating with Altitude: maximum allowable operating temperature should be reduced by 1.8 deg C per every 1000 m the system is operated above sea level. (1 deg F per 1000 ft)

- AC Electrical Power Requirement:

Voltage - 120 Vac Nominal (90 to 132 Vrms)

Frequency - 47.5 to 63 HZ

Voltage - 240 Vac Nominal (180 to 264 Vrms)

Frequency - 47.5 to 63 HZ

NEMA AC Electrical Receptacle Requirement:

NOTE

When switching the power supply input voltage from the 120 Vac (shipped configuration) to the 240 Vac operation, the power cord must also be changed.

1. 120 Vac service: NEMA 5-15R (rated @ 15A)

#### SITE PRERARATION AND INSTALLATION

2. 240 Vac service: NEMA 6-15R (rated @ 15A)

The power cord provided is 75 inches long, with either a NEMA 5-15 P, or a 6-15 P plug attached. If an isolated ground is provided, prefix NEMA receptacle numbers with "IG".

#### 2.2 SHIPPING SPECIFICATIONS

This section provides AS SHIPPED information. Products (BOX and CABINET are shipped in reinforced cardboard containers as shown in Figures 2-1 and 2-2.

Box Container:

Width: 57.5 cm (23 in) Height: 50.8 cm (20 in) Length: 77.5 cm (31 in) Weight: 56 kg (125 lb)

Cabinet Container:

| Width:  | 86 cm (34 in)  |   |

|---------|----------------|---|

| Height: | 139 cm (55 in) |   |

| Length  | 107 cm (42 in) |   |

| Weight  | 182 kg (401 lb | ) |

FIGURE 2-2 CABINET SHIPPING CONTAINER

#### SITE PRERARATION AND INSTALLATION

#### 2.3 UNPACKING INSTRUCTIONS

Read the following steps prior to unpacking the cabinet or box product.

2.3.1 Cabinet Unpacking

The unpacking instructions are located inside the shipping container. To open the shipping container complete the following steps.

#### IMPORTANT

Read warning labels on outside of container.

- 1. Cut and remove plastic strapping.

- 2. Remove top cover.

- 3. Follow directions packed inside

2.3.2 Box Unpacking

The unpacking instructions are located inside the shipping container. To open the shipping container complete the following steps.

#### IMPORTANT

Read warning labels on outside of container

- 1. Cut and remove plastic strapping.

- 2. Carefully cut sealing tape.

- 3. Open folded top of container.

- 4. Follow directions packed inside.

#### 2.4 SYSTEM INSTALLATION

To install a cabinet or box read the appropriate subsection and follow the procedures. The procedures do not cover optional device installation. Option installation is covered in the manual supplied with the device.

#### 2.4.1 Cabinet Mechanical Installation

To install the cabinet complete the following procedure.

- 1. Complete the unpacking instructions located inside the shipping container.

- 2. After rolling the cabinet down the ramps, position the cabinet on a level surface in the operational area.

- 3. Reverse step 6 of the unpacking instructions and lower the four leveling feet. Each foot is lowered until the wheel near the foot is raised approximately 1/8- to 1/4-inch above the floor surface.

- 4. Level the cabinet.

- 5. Raise each top nut and tighten it against the cabinet frame while holding the bottom leveling foot hex nut.

This completes the mechanical installation procedure.

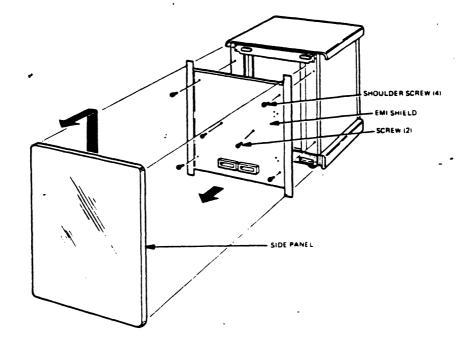

2.4.2 Box Mechanical Installation

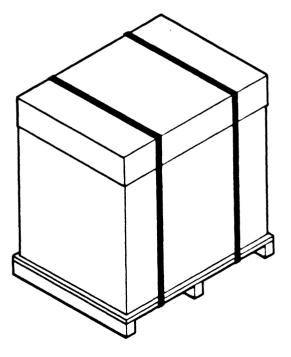

To install a box in an ANSI/EIA standard 19-inch rack, complete the following procedure.

- 1. Locate and check hardware in the box shipping container.

- Mount the chassis slide bracket by aligning the rack frame holes with the slide bracket. Secure the bracket to the frame with a nut bracket and three no.10 screws (no star washers). Tighten the screws. (See Figure 2-3.)

- 3. Mount the three other chassis slide brackets to the rack frame as in step 1.

#### SITE PRERARATION AND INSTALLATION

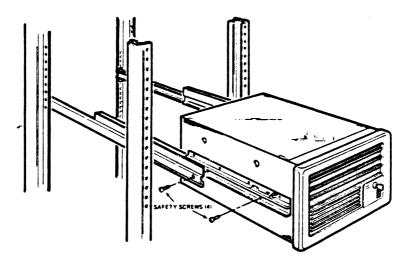

FIGURE 2-3 MOUNTING CHASSIS SLIDE AND RESTRAINT BRACKET

- 4. Mount the restraint bracket to the rack frame by aligning the bracket holes with the rack frame holes, starting two holes above the mounted chassis slide bracket. Thread and tighten three no.10 screws into the nut bars to secure the bracket.

- 5. Align the right chassis slide (front) clearance hole with the center hole of the mounted chassis slide bracket. Thread a no.10 screws (with star washer) to secure the chassis slide to the bracket. Do not tighten.

- 6. Align the two rear holes on the chassis slide with the mounted bracket. Thread two no.10 screws (with star washers) securing the chassis slide rear to the rear chassis slide bracket. Tighten the two screws.

- 7. Tighten the front screw securing the front end of the chassis slide assembly to the front mounted chassis slide bracket.

- Secure the left chassis slide assembly to the left front and rear mounted chassis slide brackets by repeating steps

4 through 6.

- 9. Extend the stabilizer bar (if present) before placing the box on the slide assemblies.

- 10. Fully extend both chassis slide assemblies forward: Lower the box assembly onto the slide assemblies, aligning the chassis slide slot with the tab on the box rail.

FIGURE 2-4 SECURING BOX INTO CHASSIS SLIDE ASSEMBLY

- 11. Secure the box to the chassis slides by aligning the front clearance hole with the threaded box hole. Thread a no.8 screw and tighten.

- 12. Slide the box rearward aligning the rear chassis slide clearance hole with the threaded box bole. Thread a no.8 screw and tighten.

- 13. Slide the box to the rear and secure it to the rack frame by threading two, no.8 phillips screws to the restraint bracket located on the box rear panel. Tighten the screws.

This completes the installation of the box in an ANSI/EIA standard 19-inch rack.

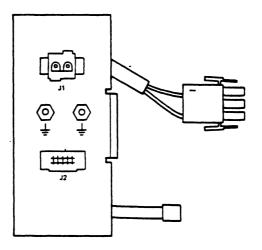

2.4.3 Console Serial Line Hookup

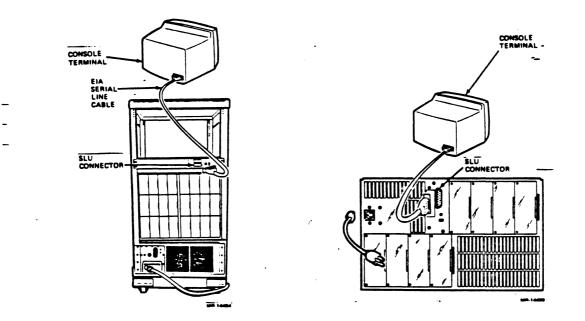

Install the console serial line as shown in Figure 2-5.

2-8

#### SITE PRERARATION AND INSTALLATION

FIGURE 2-5 SERIAL LINE HOOKUP

2.4.4 Cabinet Switches Settings

The following switch settings are required for the cabinet product.

NOTE

Switch settings must be verified before power is applied to the system.

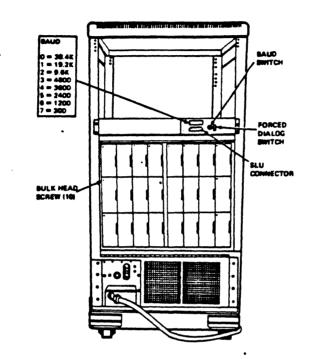

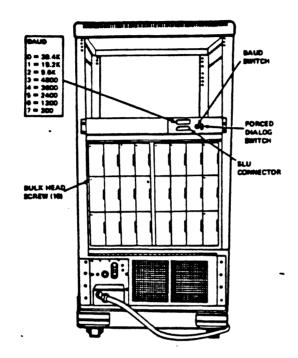

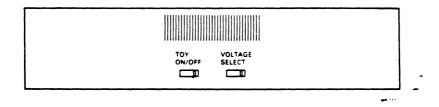

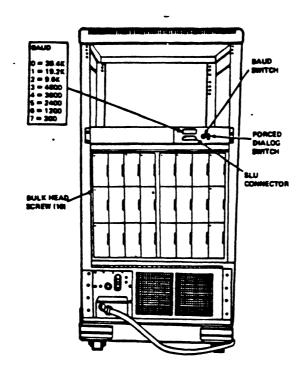

- 1. Set the Forced Dialogue switch to OFF (0).

- 2. Set the baud rate of the console terminal.

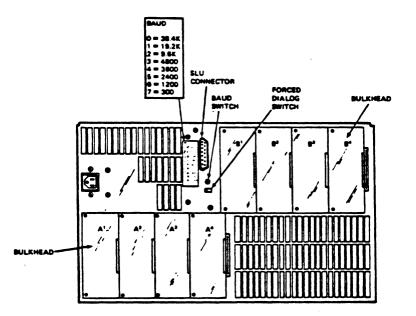

- 3. Set the Baud Rate switch to match the baud rate of the console terminal. (see Figure 2-6.)

- 4. Assure that the AC power outlet matches the power controller AC input power requirement. Model 877-D is for 120 Vac operation and 877-F is for 240 Vac operation. The model number is printed on a label located on the power controller.

#### SITE PRERARATION AND INSTALLATION

NOTE

When the power controller is turned off the AC power circuit breaker is inoperable.

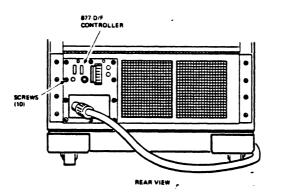

FIGURE 2-6 CABINET REARVIEW

- 5. Turn the power controller breaker switch to the off (0) position. See Figure 2-6.

- 6. Set the front panel keylock switch to OFF. (See Figure 2-11.)

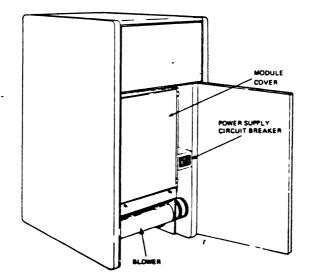

- 7. Open the front door, turn both power supply circuit breakers to OFF (0). (See Figure 2-7.)

- 8. Assure that the expansion power supply breaker is OFF (0) if the expansion backplane is in use.

This completes the cabinet switch set up.

FIGURE 2-7 CABINET FRONTVIEW

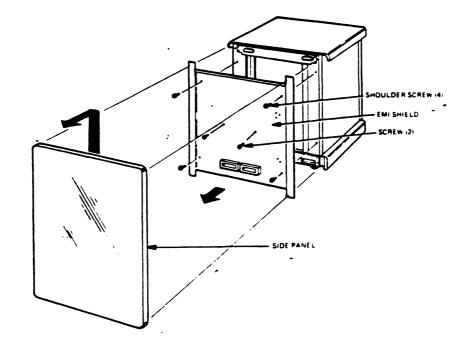

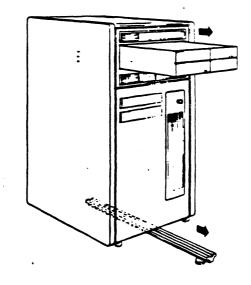

#### 2.4.5 Box Switch Settings

The following switch settings are required for the box product.

- 1. Slide the box forward to the mechanical stop.

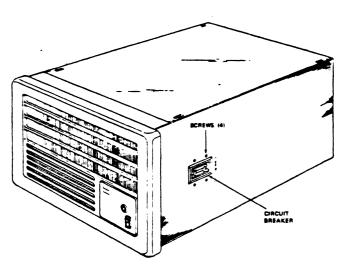

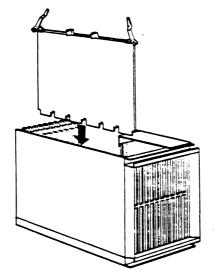

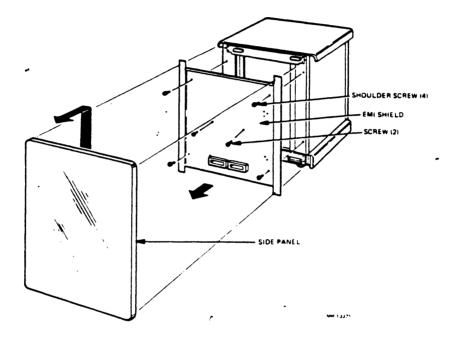

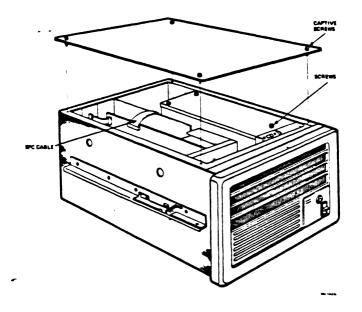

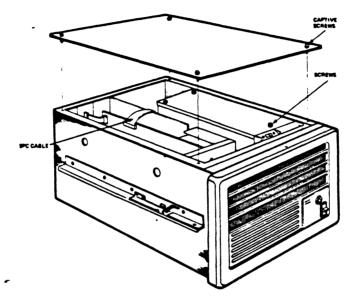

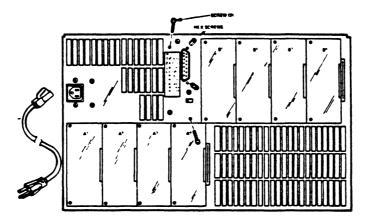

- Remove the four top cover screws and lift the cover off. (See Figure 2-8.)

- 3. Set the power supply input AC voltage switch, located on the power supply front, to match the AC power outlet voltage. (See Figure 2-8.)

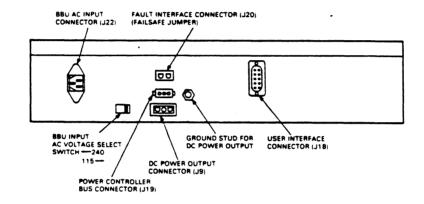

FIGURE 2-8 BOX POWER SUPPLY INPUT SELECT SWITCH

- 4. Reinstall the top cover.

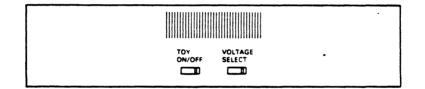

- 5. Set the Forced Dialogue switch to OFF (0).

- 6. Set the baud rate of the console terminal.

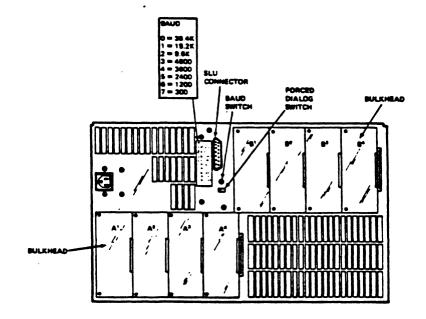

- 7. Set the Baud Rate switch to match the baud rate for the console terminal. See Figure 2-9.

FIGURE 2-9 BOX REARVIEW

8. Set the front panel keylock switch to OFF.

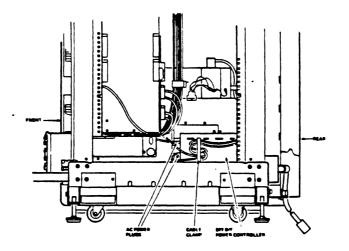

9. Turn the circuit breaker to OFF (0). See Figure 2-10. This completes the box switch set up.

FIGURE 2-10 BOX FRONT VIEW

#### 2.4.6 Cabinet Power Hookup

Complete the following procedure.

#### CAUTION

Assure that the wall outlet voltage matches the line voltage selected for operation.

Assure that all system switch settings are as specified in subsection 2.4.4.

- 1. Plug the AC power cord into the AC power outlet.

- 2. Turn the power controller circuit breaker to ON (1). See Figure 2-6.

- 3. Open the front door and turn the main power supply circuit breaker to ON (0). See Figure 2-7.

This completes the cabinet AC electrical hook up.

2.4.7 Box Power Hookup

Complete the following procedure.

#### CAUTION

Assure that the wall outlet voltage matches the line voltage selected for operation.

Assure that all system switch settings are as specified in subsection 2.4.5.

- 1. Plug the female end of the AC power cord into the receptacle mounted on the rear of the box. See Figure 2-9.

- 2. Plug the male end of the AC power cord into the AC power outlet.

- 3. Remove the restraint bracket at the rear of the box.

- 4. Slide the box out approximately 6 inches and turn the circuit breaker to ON (1). See Figure 2-10.

- 5. Slide the box back into the rack and replace the restraint bracket

This completes the box electrical hook up.

#### 2.5 SYSTEM CONTROLS AND INDICATORS

The following subsections describe the system controls and indicators. The functions described are for normal operating conditions. If a problem occurs during normal operation refer to Chapter 5, System Maintenance.

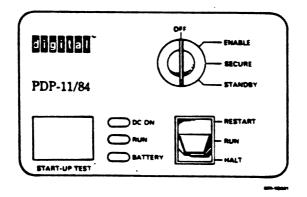

#### 2.5.1 Front Panel

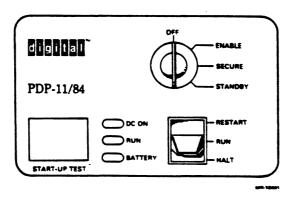

The front panel consists of a keylock power switch, RESTART/RUN/ HALT Switch, a Start-up Test LED display, and POWER and RUN indicators. Figure 2-11 shows the front panel controls and indicators.

FIGURE 2-11 FRONT PANEL CONTROLS AND INDICATORS

The Keylock Switch is a four position rotary switch used to select ONE of four power states. Table 2-1 lists and describes each of the power switch selections.

TABLE 2-1 KEYLOCK POSITION DESCRIPTIONS

POSITION FUNCTION

- OFF Power supplies are turned off. DC power to the logic and blower/fan assembly is off. However, AC power into the power supplies is present.

- ENABLE The ON position. Power supply voltages are present to the logic and blower/fan assembly.

- SECURE Same as the ENABLE position except that the console terminal Halt-On-Break feature and the HALT/RUN/RESTART switch are disabled.

- STANDBY Power is supplied to the PMI memory, blower/fans but other voltages are turned off.

The HALT/RUN/RESTART switch functions are enabled only when the keylock switch is in the ENABLED position. Table 2-2 lists the switch positions and their functions.

#### TABLE 2-2 HALT/RUN/RESTART SWITCH

## POSITION FUNCTION

- HALT The CPU program is stopped and the incremented content of the program counter is displayed on the console terminal. The CPU enters Jll Micro-ODT.

- RUN Entering RUN from RESTART enables CPU operations to run. Entering from HALT causes the processor to remain in micro-ODT awaiting a command from the console terminal.

- RESTART This momentary switch position initiates processor execution of bootstrap program instructions located in the boot ROM according to the set up configuration in the EEPROM. For modifying EEPROM configurations see the EEPROM section in this chapter.

Three LEDs are located on the front panel. Table 2-3 describes the LED status and functions.

#### TABLE 2-3 FRONT PANEL INDICATORS

LED STATUS FUNCTION

- RUN ON The Jll processor is fetching and executing instructions. This is the normal condition.

- OFF The processor is halted or waiting for an interrupt. When the processor is in Micro-ODT the RUN indicator blinks for each console keystroke. The RUN LED also turns off during extended DMA activity.

- DC ON ON DC power is available to the logic and all voltages are within specified levels.

- OFF DC voltages are not available to the logic or voltages are present but not within tolerances.

- BATTERY ON Battery is present and charged to 80% or greater capacity.

- Slow Blink Battery is at less than 80% capacity and is (1 Hz) charging.

- Fast Blink The ac power has failed; the battery is dis-(10 Hz) charging, but the memory content remains valid.

- OFF Battery is either fully discharged or not present in the system. Memory content will not be preserved if ac power fails.

The two-digit Start-up Test LED display provides the start-up diagnostic error codes. The codes are described in Chapter 5, System Maintenance.

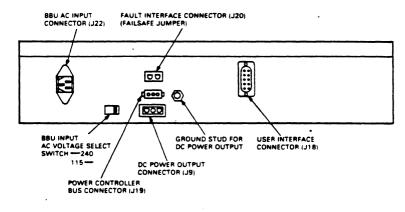

#### 2.5.2 Console Serial Line Distribution Board

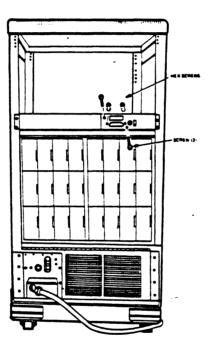

The console serial line distribution board (SLU) is mounted to the inside back panel of both products. The SLU includes a serial communications port connector, a baud rate select switch and a Forced Dialogue mode switch. The SLU mounting position for the cabinet and box are shown in Figures 2-12 and 2-9.

FIGURE 2-12 CABINET BACKPANEL VIEW

#### 2.5.3 Serial Communications Port

A serial line connector is located on the back panel. Figures 2-12 and 2-9 show the physical location of the connector. It provides an EIA RS232-C, RS449 compliant full duplex communications link between the CPU and console terminal. Note that 20 ma applications are not supported.

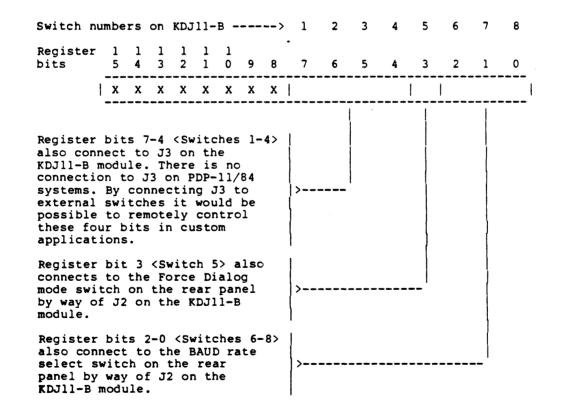

#### 2.5.4 Baud Rate Select Switch

The baud rate switch enables the operator to set the operating baud rate between the console terminal and system. The baud rate is set for one of eight possible baud rates. Table 2-4 lists the switch positions and their corresponding baud rates.

| SWITCH<br>POSITION | BAUD RATE |

|--------------------|-----------|

| 0                  | 38400     |

| 1                  | 19200     |

| 2                  | 9600      |

| 3                  | 4800      |

| 4                  | 2400      |

| 5                  | 1200      |

| 6                  | 600       |

| 7                  | 300       |

|                    |           |

TABLE 2-4 BAUD RATE SWITCH DESCRIPTIONS

#### 2.6 SYSTEM HARDWARE CONFIGURATION

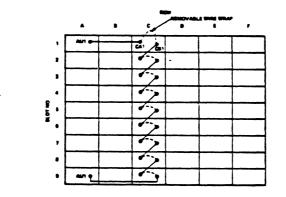

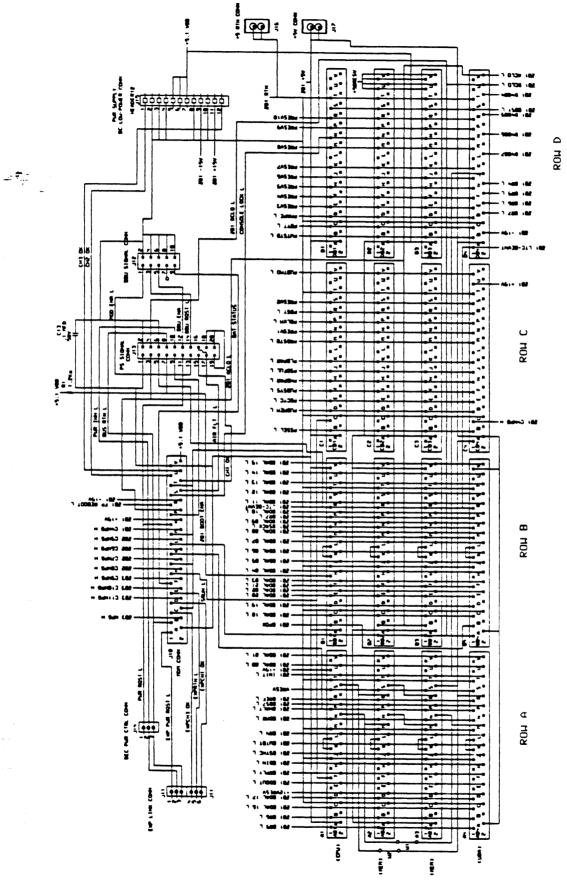

Figure 2-13 shows the location of the modules within the system backplane. Slot MDM is dedicated to the Monitor and Distribution module (M7677). Slots 1 through 4 comprise the system kernel. Slots 5 through 12 support most UNIBUS compatible small peripheral controllers (SPC). The following subsection describe configuration details for the kernel.

FIGURE 2-13 H9277-A BACKPLANE MODULE LOCATIONS

#### 2.6.1 KDJ11-BF Module Configuration

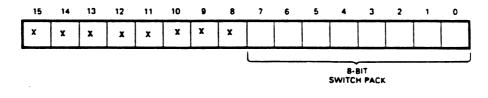

The KDJll-BF module has three jumper groupings and one DIP switch pack for hardware configuration. The jumpers should be installed as shown in the Figure 2-14. The DIP switches should be set to OFF.

FIGURE 2-14 KDJ11-B JUMPER AND DIP SWITCH LOCATION

#### 2.6.2 KTJ11-B Module Configuration

\_

-

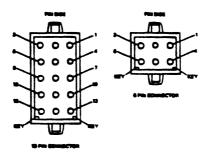

The UBA module does not have any hardware jumpers or switches for configuration. It has four sockets for the addition of M9312 compatible user ROMs. See Figure 2-15 for the ROM socket locations.

The M9312 compatible user ROMs are installed with pin one of the chip toward the left edge of the component side of the module.

FIGURE 2-15 KTJ11-B ROM SOCKET LOCATIONS

2-19

#### 2.6.3 Monitor and Distribution Module Configuration

The quad-height Monitor and Distribution Module (MDM) has an eight switch DIP pack. The eight switches correspond to backplane slots 5 through 12 and are wired to the UNIBUS Non Processor Grant (NPG) line. This eliminates the wire wrapping of backplane pins for non DMA SPCs. For non DMA SPCs the switch is turned ON (toward module handles). For UNIBUS DMA devices the switch is turned OFF.

An audible alarm is mounted on the module and sounds when a failure of a box fan or the cabinet blower occurs. See Figure 2-17 for the switch location and numbering.

FIGURE 2-16 MDM DIP SWITCH LOCATION

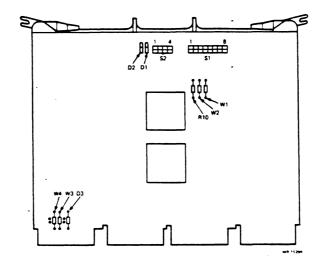

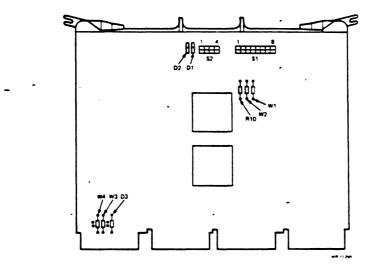

2.6.4 MSV11-JB/JC Memory Module Configuration

The guad-height memory module provides:

- a. A red LED to indicate uncorrectable errors

- b. A green LED to indicate the presence of +5 VBB

- c. Two switch packs for starting and CSR address selection

- d. Four factory-set jumpers.

See Figure 2-17 for LED, switch pack, and jumper layout.

FIGURE 2-17 MSV11-JB/JC LED/SWITCH PACK/JUMPER LAYOUT

The starting address is configured using switch pack Sl, switches 1 - 8 Table 2-5 lists the switch settings, starting addresses and decimal number.

| TABLE 2-5 MSV11-JX STARTING ADDRES | TABLE | 2-5 | MSV11-JX | STARTING | ADDRESS |

|------------------------------------|-------|-----|----------|----------|---------|

|------------------------------------|-------|-----|----------|----------|---------|

| SWITCH SETTING*<br>1 2 3 4 5 6 7 8 | STARTING<br>ADDRESS<br>(Octal) | DECIMAL<br>Kwords | DECIMAL<br>Kbytes |

|------------------------------------|--------------------------------|-------------------|-------------------|

| 0 0 0 0 0 0 0 0                    | 00000000                       | 0                 | 0                 |

| 0 1 0 0 0 0 0 0                    | 04000000                       | 512               | 1024              |

| 1 0 0 0 0 0 0 0                    | 1000000                        | 1024              | 2048              |

| 1 1 0 0 0 0 0 0                    | 14000000                       | 1536              | 3072              |

|                                    |                                |                   |                   |

\* 1 = Switch on 0 = Switch off

The CSR address is configured using switch pack S2, switches 1 - 4. The base address is 17772100. Each successive address is the base plus 2. Table 2-6 lists all sixteen possible CSR addresses.

.

TABLE 2-6 MSV11-JB/JC CSR ADDRESS SELECTIONS

-

.

| S2 | SI | ETI | CING | . CSR           |

|----|----|-----|------|-----------------|

| 1  | 2  | 3   | 4    | ADDRESS (OCTAL) |

| 0  | 0  | 0   | 0    | 17772100        |

| 0  | 0  | 0   | 1    | 17772102        |

| 0  | 0  | 1   | 0    | 17772104        |

| 0  | 0  | 1   | 1    | 17772106        |

| 0  | 1  | 0   | 0    | 17772110        |

| 0  | 1  | 0   | 1    | 17772112        |

| 0  | 1  | 1   | 0    | 17772114        |

| 0  | 1  | 1   | 1    | 17772116        |

| 1  | 0  | 0   | 0    | 17772120        |

| 1  | 0  | 0   | 1    | 17772122        |

| 1  | 0  | 1   | C    | 17772124        |

| 1  | 0  | 1   | 1.   | 17772126        |

| 1  | 1  | 0   | 0    | 17772130        |

| 1  | 1  | 0   | 1    | 17772132        |

| 1  | 1  | 1   | 0    | 17772134        |

| 1  | 1  | 1   | 1    | 17772136        |

|    |    |     |      |                 |

The jumper configurations for the lMB (MSV11-JB) and 2MB (MSV11-JC) memory modules are different. Assure that the factory-set jumpers are as specified in Table 2-7.

TABLE 2-7 MSV11-JB/JC JUMPER CONFIGURATIONS

| MODULE   | JUMPER(S) | POSITION | DESCRIPTION             |

|----------|-----------|----------|-------------------------|

| MSV11-JB |           |          |                         |

|          | Wl        | OUT      | 256K Dynamic RAMs       |

|          | W2        | IN       | Half-populated module   |

|          | W3,W4     | Vertical | Reserved for future use |

| MSV11-JC |           |          |                         |

|          | Wl        | OUT      | 256K Dynamic Rams       |

|          | W2        | OUT      | Fully populated module  |

|          | W3,W4     | Vertical | Reserved for future use |

|          |           |          |                         |

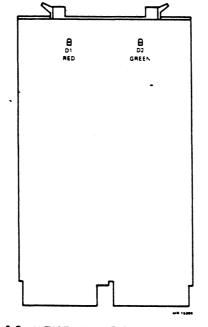

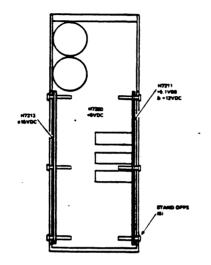

#### 2.6.5 Minimum Load Module

The MLM modules are used to provide minimum power supply regulator loads under the following conditions:

- a. An MLM is inserted in CPU backplane slot 3 (rows C and D) to ensure a minimum current drain of 2 A from the +5 VBB regulator.

- b. An MLM is inserted in CPU backplane slot 12 (rows E and F) to ensure a mimimum current drain of 1 A from the -15 Vdc regulator.

- c. If an expansion backplane (DDll-CK or DDll-DK) is installed, an MLM is inserted in the last slot of the backplane (rows E and F) to ensure a mimimum current drain of 1 A from the -15 Vdc regulator.

#### NOTE

An MLM is not required in the last backplane slot (CPU or expansion) if the installed options draw the minimum 1 A of -15 V.

When not required, the Load Modules must be removed from the backplane.

As shown in Figure 2-18, the MLM has two LEDs to indicate the presence of +5 VBB and -15 Vdc.

FIGURE 2-18 MINIMUM LOAD MODULE LAYOUT

2-23

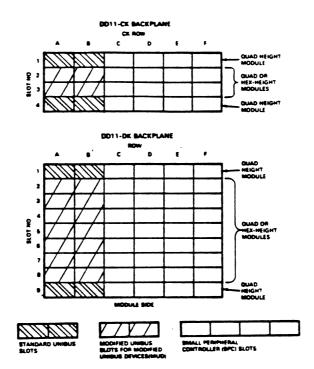

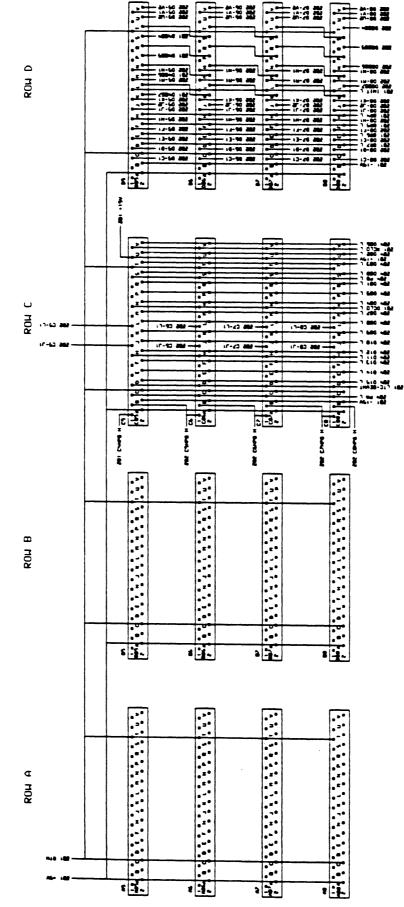

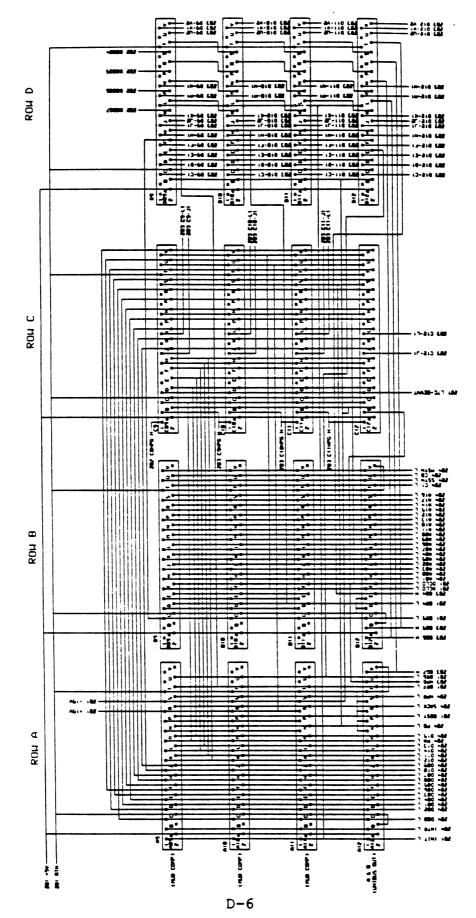

#### 2.7 EXPANSION BACKPLANE INSTALLATION

Two types of expansion backplanes are available for installation in the cabinet. They are:

- 1. DD11-CK 4-slot backplane

- 2. DDll-DK 9-slot backplane

Both backplanes are shown in Figure 2-19.

FIGURE 2-19 EXPANSION BACKPLANE SLOT ASSIGNMENTS

The standard UNIBUS connectors contain all the UNIBUS connections. Rows A and B of slot l are the beginning of the UNIBUS DD11-CK and DD11-DK and should be occupied by the BC11-A UNIBUS in cable.