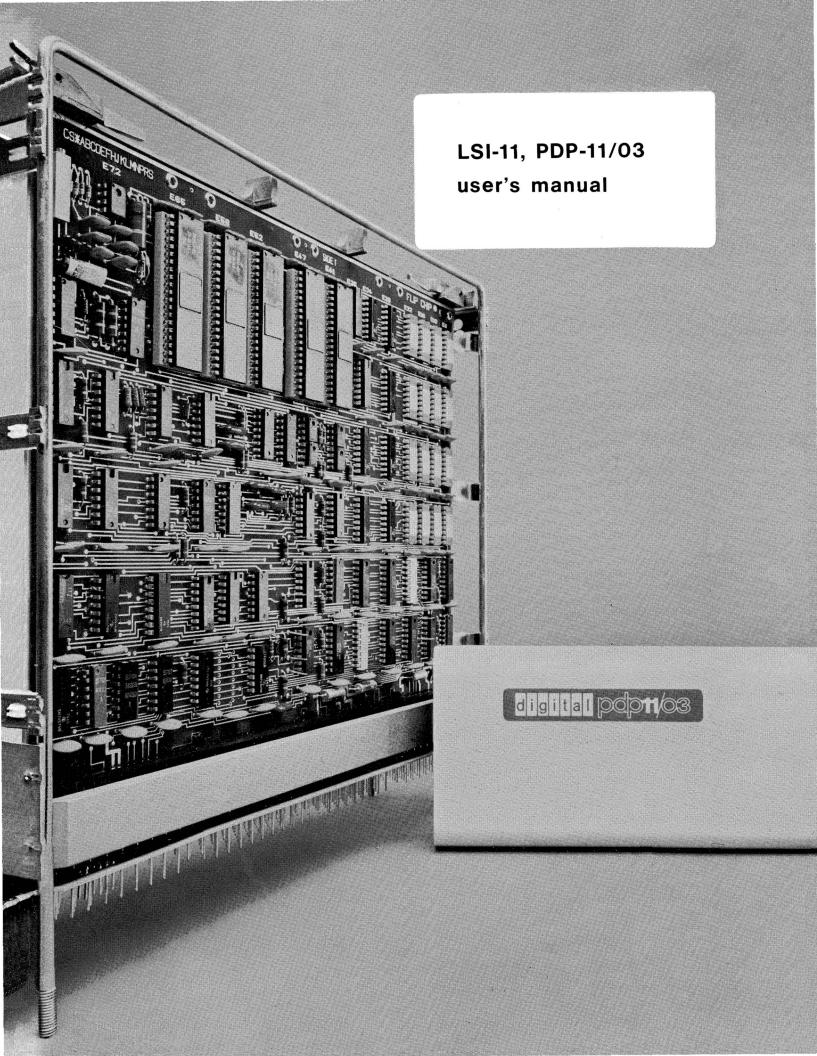

LSI-11, PDP-11/03 user's manual

digital equipment corporation • maynard, massachusetts

1st Edition, September 1975 2nd Printing (Rev), November 1975 3rd Printing (Rev), May 1976

#### Copyright © 1975, 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

#### CONTENTS

| CHARTER 1 INTRODUCTION                              |       |

|-----------------------------------------------------|-------|

| CHAPTER 1 INTRODUCTION                              |       |

| 1.1 GENERAL                                         | . 1-1 |

| 1.2 SCOPE                                           | 1-1   |

| 1.3 REFERENCES                                      | . 1-1 |

| CHAPTER 2 LSI-11 SYSTEM OVERVIEW                    |       |

| 2.1 GENERAL                                         | 2-1   |

| 2.2 SYSTEM CONFIGURATIONS                           | 2-1   |

| 2.3 LSI-11 MICROCOMPUTER                            | 2-1   |

| 2.4 I/O BUS CONCEPT                                 | 2-2   |

| 2.5 MEMORY OPTIONS                                  | 2-3   |

| 2.6 PERIPHERAL INTERFACE OPTIONS                    | 2-3   |

| 2.7 BACKPLANE, POWER SUPPLY, AND HARDWARE OPTIONS   | 2-3   |

| 2.8 POWER REQUIREMENTS                              | 2-4   |

| 2.9 GENERAL SPECIFICATIONS                          | 2-4   |

| CHAPTER 3 THE LSI-11 BUS                            |       |

| 3.1 CHOOSING AN I/O TRANSFER TYPE                   | 3-1   |

| 3.2 DEVICE PRIORITY                                 | 3-1   |

| 3.3 MODULE CONTACT FINGER IDENTIFICATION            | 3-2   |

| 3.4 BUS SIGNALS                                     | 3-4   |

| 3.5 BUS CYCLES                                      | 3-7   |

| 3.5.1 General                                       | 3-7   |

| 3.5.2 Input Operations                              | 3-7   |

| 3.5.3 Output Operations                             | 3-8   |

| 3.6 DMA OPERATIONS                                  | 3-11  |

| 3.7 INTERRUPTS                                      |       |

| 3.8 BUS INITIALIZATION                              | 3-12  |

| 3.9 POWER-UP/POWER-DOWN SEQUENCE                    | 3-12  |

| 3.10 HALT MODE                                      |       |

| 3.11 MEMORY REFRESH                                 | 3-13  |

| 3.12 BUS SPECIFICATIONS                             | 3-14  |

| 3.13 BUS CONFIGURATIONS                             | 3-14  |

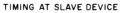

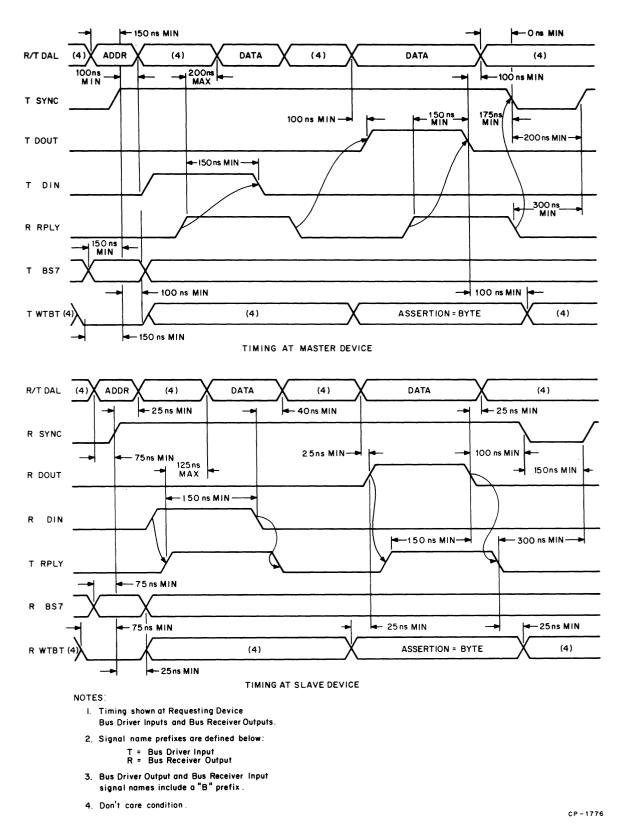

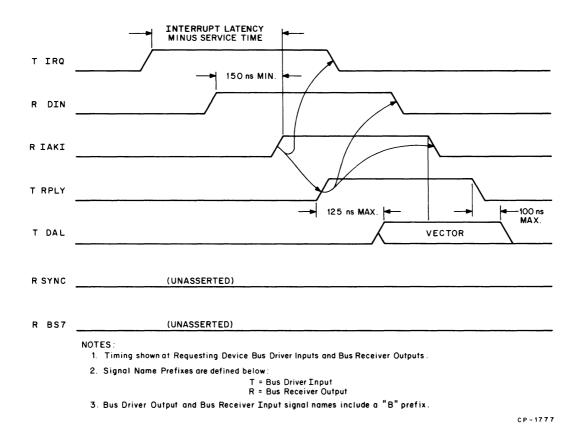

| 3.14 BUS SIGNAL TIMING                              | 3-15  |

| CHAPTER 4 LSI-11 MODULE DESCRIPTIONS                |       |

| 4.1 GENERAL                                         | 4-1   |

| 4.2 KD11-F MICROCOMPUTER                            | 4-2   |

| 4.2.1 General                                       | 4-2   |

| 4.2.2 Basic Microcomputer Functions                 | 4-3   |

| 4.2.2.1 Microprocessor Chip Set                     |       |

| 4.2.2.2 Clock Pulse Generator                       |       |

| 4.2.2.3 Bus Interface and Data/Address Distribution |       |

| 4.2.2.4 Bus I/O Control Signal Logic                |       |

| 4.2.2.5 Bank 7 Decoder                              |       |

| 4.2.2.6 Interrupt Control and Reset Logic           |       |

| 4.2.2.7 Special Control Functions                   |       |

| 4.2.2.8 Bus Arbitration Logic                       |       |

|          |                                                     | Page |

|----------|-----------------------------------------------------|------|

| 4.2.3    | KD11-F Resident Memory                              | 4-13 |

| 4.2.4    | DC-DC Power Inverter                                |      |

| 4.3      | MMV11-A 4K BY 16-BIT CORE MEMORY                    |      |

| 4.3.1    | General                                             |      |

| 4.3.2    | Functional Description                              |      |

| 4.3.2.1  | Introduction                                        |      |

| 4.3.2.2  | Core Addressing                                     |      |

| 4.3.2.3  | Read/Write Data Path                                |      |

| 4.3.2.4  | Timing and Control                                  |      |

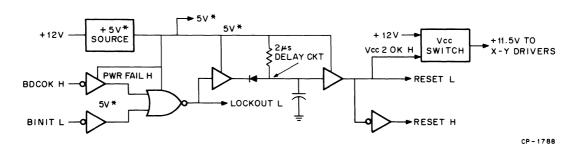

| 4.3.2.5  | DC Protection and Vcc Switch                        |      |

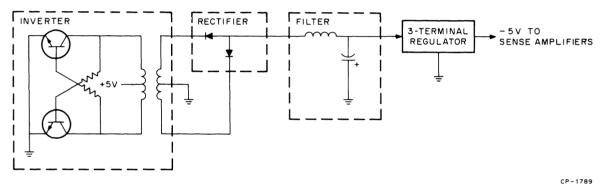

| 4.3.2.6  | DC-DC Inverter                                      |      |

| 4.4      | MRV11-A 4K BY 16-BIT READ-ONLY MEMORY               |      |

| 4.4.1    | General                                             |      |

| 4.4.2    | Functional Description                              |      |

| 4.4.2.1  | General                                             |      |

| 4.4.2.2  | Addressing                                          |      |

| 4.4.2.3  | Data Read Operation                                 |      |

| 4.5      | MS11-B 4K BY 16-BIT SEMICONDUCTOR READ/WRITE MEMORY |      |

| 4.5.1    | General                                             |      |

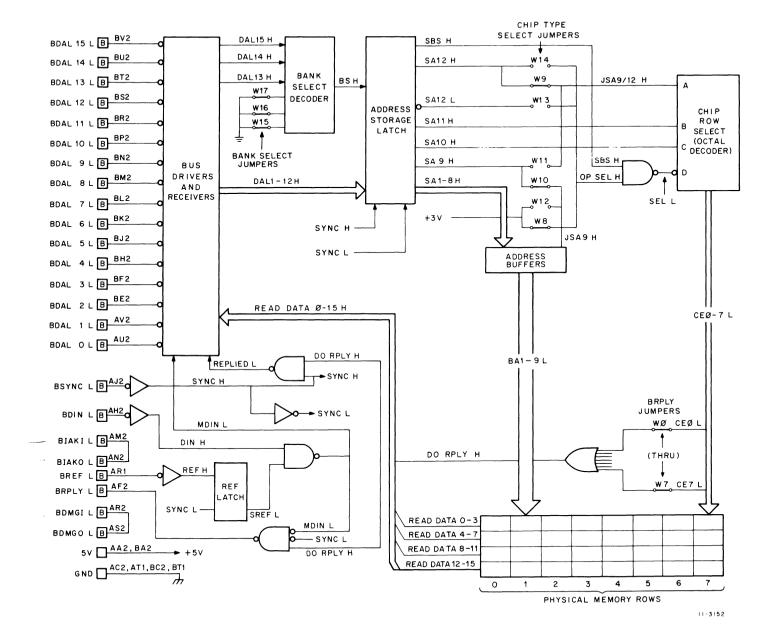

| 4.5.2    | Functional Description                              |      |

| 4.6      | This section was deleted                            |      |

| 4.7      | DLV11 SERIAL LINE UNIT                              | 4-29 |

| 4.7.1    | General                                             |      |

| 4.7.2    | Functional Description                              |      |

| 4.7.2.1  | General                                             |      |

| 4.7.2.2  | UAR/T Operation                                     |      |

| 4.7.2.3  | Baud Rate Generator                                 |      |

| 4.7.2.4  | Bus Drivers and Receivers                           |      |

| 4.7.2.5  | Address Decoding                                    |      |

| 4.7.2.6  | Function Decoding and Control                       |      |

| 4.7.2.7  | Interface Control Logic                             |      |

| 4.7.2.8  | CSR Selection and Gating                            | 4-34 |

| 4.7.2.9  | Break Logic                                         |      |

| 4.7.2.10 | Reader Run Logic                                    | 4-34 |

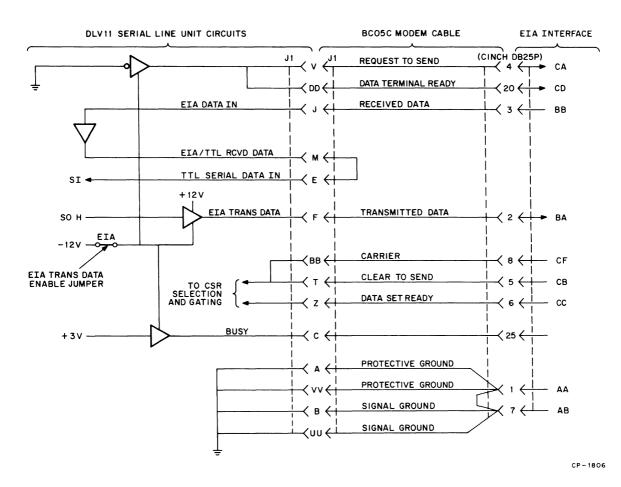

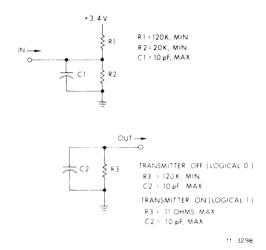

| 4.7.2.11 | EIA Interface Circuits                              | 4-34 |

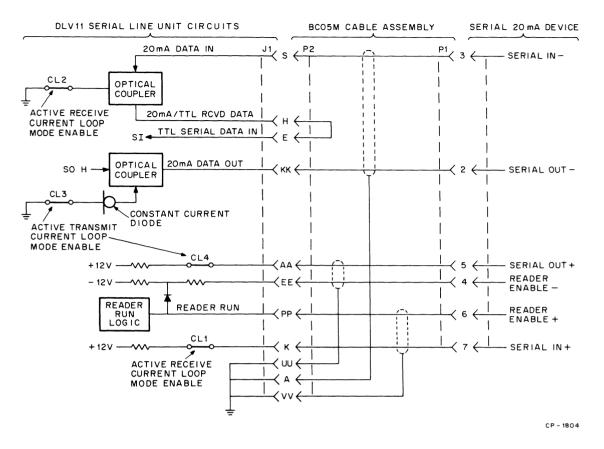

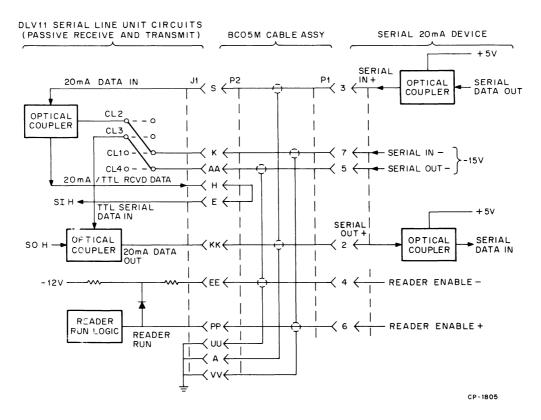

| 4.7.2.12 | 20 mA Loop Current Interface                        | 4-35 |

| 4.7.2.13 | -12 V Inverter                                      | 4-35 |

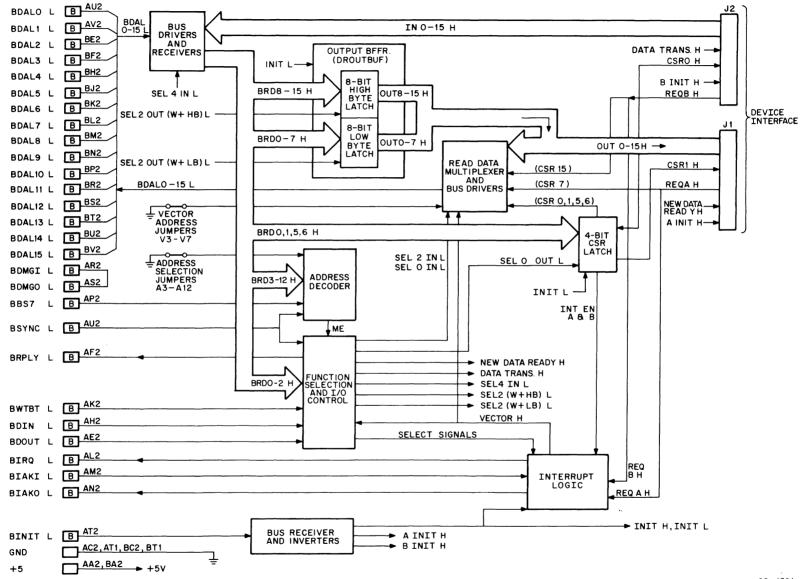

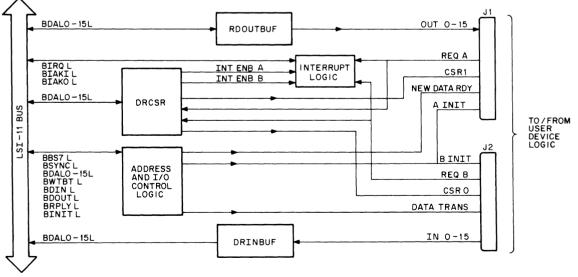

| 4.8      | DRV11 PARALLEL LINE UNIT                            | 4-35 |

| 4.8.1    | General                                             | 4-35 |

| 4.8.2    | Functional Description                              | 4-35 |

| 4.8.2.1  | General                                             | 4-35 |

| 4.8.2.2  | Addressing                                          | 4-35 |

| 4.8.2.3  | Function Selection                                  |      |

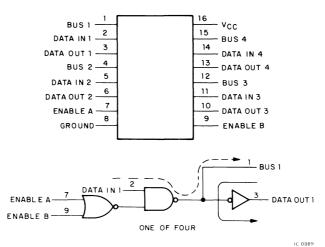

| 4.8.2.4  | Read Data Multiplexer                               |      |

| 4.8.2.5  | DRCSR Functions                                     |      |

| 4.8.2.6  | DRINBUF Input Data Transfer                         | 4-38 |

| 4.8.2.7  | DROUTBUF Output Data Transfer                       | 4-38 |

|            | F                                           | Page       |

|------------|---------------------------------------------|------------|

| 4.8.2.8    | Interrupts                                  | -38        |

| 4.8.2.9    | Maintenance Mode                            | -39        |

| 4.8.2.10   | Initialization                              | -39        |

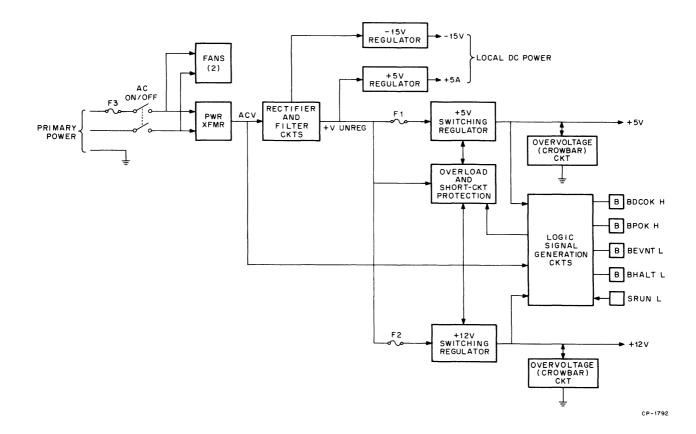

| 4.9        | H780 POWER SUPPLY                           | -39        |

| 4.9.1      | General                                     | -39        |

| 4.9.2      | Specifications                              | -40        |

| 4.9.3      | Functional Description                      | -40        |

| 4.9.3.1    | General                                     | -40        |

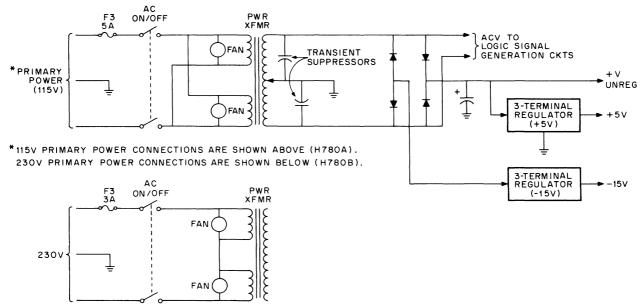

| 4.9.3.2    | Unregulated Voltage and Local Power         | -40        |

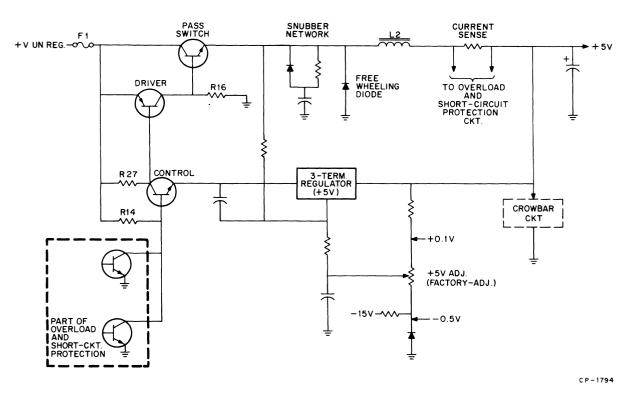

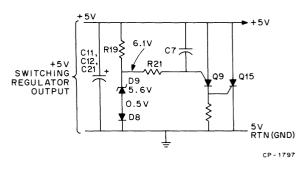

| 4.9.3.3    | Basic Regulator Circuit                     | -42        |

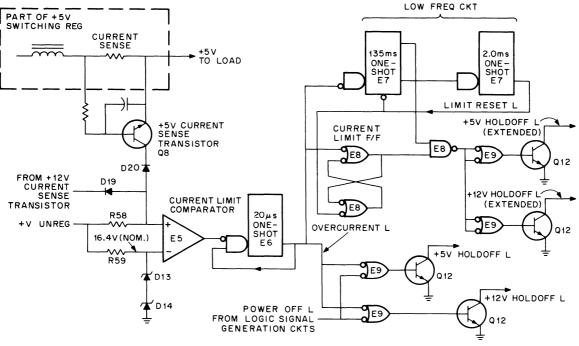

| 4.9.3.4    | Overload and Short-Circuit Protection       |            |

| 4.9.3.5    | Crowbar Circuits                            | -44        |

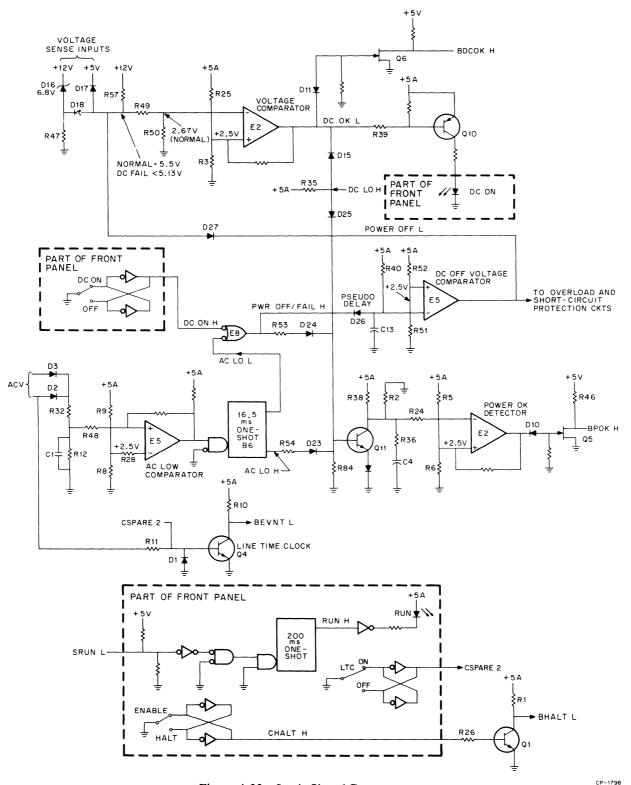

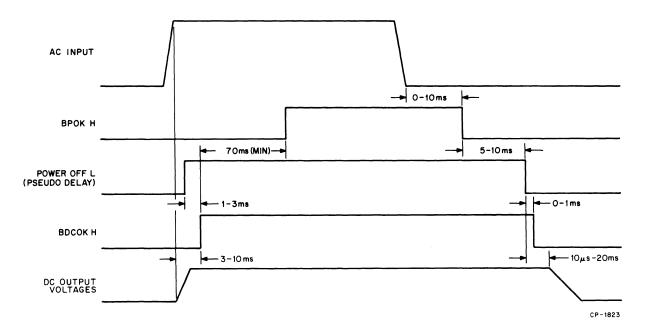

| 4.9.3.6    | Logic Signal Generation                     | -44        |

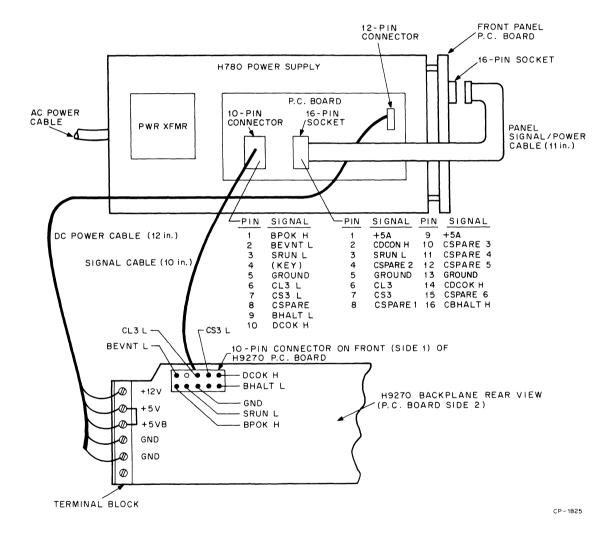

| 4.9.4      | H780 Connections                            | -48        |

| CHAPTER 5  | USING KD11-F and KD11-J PROCESSORS          |            |

| 5.1        |                                             | 5-1        |

| 5.2        |                                             | 5-1        |

| 5.2.1      |                                             | 5-1<br>5-1 |

| 5.2.2      |                                             | 5-1<br>5-1 |

| 5.2.3      | •                                           | 5-1<br>5-2 |

| 5.2.4      | · · ·                                       | 5-2<br>5-2 |

| 5.2.5      | Power-Up Mode Selection                     | 5-2<br>5-3 |

| 5.3        | Resident Memory 4K Address Selection        | 5-3<br>5-4 |

| 5.3<br>5.4 | USING THE LSI-11 MICROCOMPUTER              | 5-4<br>5-4 |

| 5.4.1      | General                                     | 5-4<br>5-4 |

| 5.4.2      | Interrupt and Trap Priority                 | 5-4        |

| 5.4.3      |                                             | 5-4<br>5-4 |

| 5.5        |                                             | 5-4        |

| CHAPTER 6  | LSI-11 INTERFACE MODULES                    |            |

| 6.1        | GENERAL                                     | 61         |

| 6.2        |                                             | 6-1        |

| 6.2.1      |                                             | 6-1        |

| 6.2.2      | General                                     | 6-1        |

| 6.2.2.1    |                                             | 6-1<br>6-1 |

| 6.2.2.2    |                                             | 6-1        |

| 6.2.2.3    | Addressing                                  | 6-3        |

| 6.2.2.4    | Vectors                                     |            |

| 6.2.2.5    | UAR/T Operation                             | 6-3        |

| 6.2.2.6    | Baud Rate Selection                         | 6-3        |

| 6.2.2.7    |                                             | 6-3        |

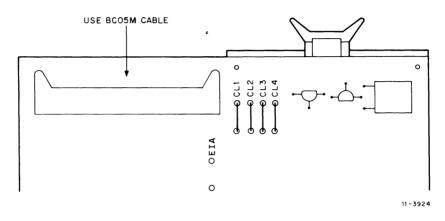

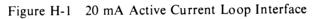

| 6.2.2.8    | 20 mA Current Loop Interface                | 6-3        |

|            | Framing Error Halt                          | 6-4        |

| 6.2.3      | Installation                                | 6-4        |

| 6.2.4      | Interfacing with 20 mA Current Loop Devices | 6-4        |

| 6.2.5      | Interfacing with EIA-Compatible Devices     | 6-5        |

| 6.2.6      | Programming                                 | 6-5        |

| 6.2.6.1    | Addressing                                  | 6-5        |

-

|           | Page                                                              | ! |

|-----------|-------------------------------------------------------------------|---|

| 6.2.6.2   | Interrupt Vectors                                                 |   |

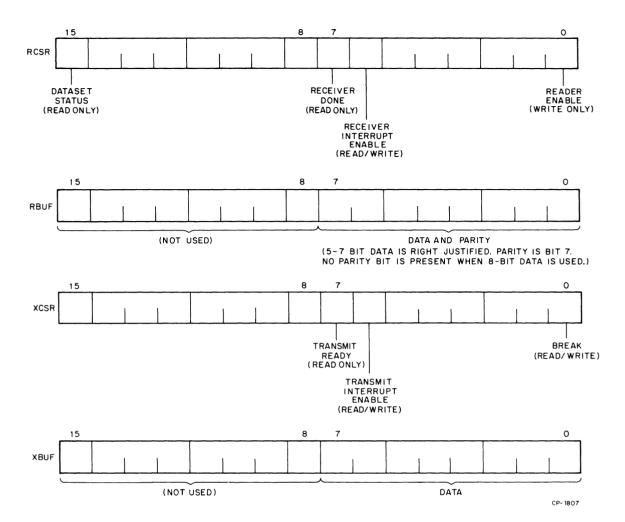

| 6.2.6.3   | Word Formats                                                      | , |

| 6.2.7     | Console Device                                                    | , |

| 6.3       | DRV11 PARALLEL LINE UNIT                                          | , |

| 6.3.1     | General                                                           | , |

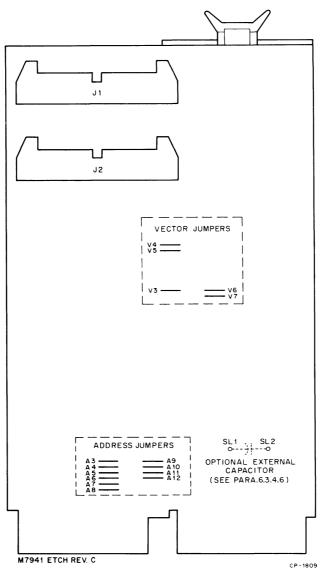

| 6.3.2     | Jumper-Selected Addressing and Vectors                            | , |

| 6.3.2.1   | Locations                                                         | ļ |

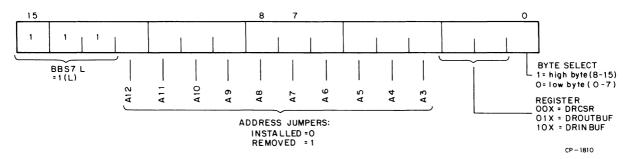

| 6.3.2.2   | Addressing                                                        |   |

| 6.3.2.3   | Vectors                                                           | ) |

| 6.3.3     | Installation                                                      |   |

| 6.3.4     | Interfacing to the User's Device                                  |   |

| 6.3.4.1   | General                                                           |   |

| 6.3.4.2   | Output Data Interface                                             |   |

| 6.3.4.3   | Input Data Interface                                              |   |

| 6.3.4.4   | Request Flags                                                     |   |

| 6.3.4.5   | Initialization                                                    |   |

| 6.3.4.6   | NEW DATA READY and DATA TRANSMITTED Pulse Width Modification 6-13 |   |

| 6.3.4.7   | BC08R Maintenance Cable                                           |   |

| 6.3.5     | Programming                                                       |   |

| 6.3.5.1   | Addressing                                                        |   |

| 6.3.5.2   | Interrupt Vectors                                                 |   |

| 6.3.5.3   | Word Formats                                                      |   |

| 0.3.3.3   |                                                                   | • |

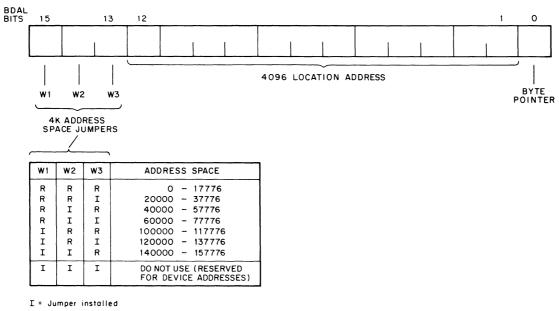

| CHAPTER 7 | USING MSV11-B READ/WRITE MEMORY MODULES                           |   |

| 7.1       | GENERAL                                                           |   |

| 7.2       | MSV11-B JUMPERS                                                   |   |

| 7.2.1     | Addressing                                                        | į |

| 7.2.2     | Reply to Refresh                                                  | l |

| 7.3       | MSV11-B BUS RESTRICTION                                           |   |

| 1.5       |                                                                   |   |

| CHAPTER 8 | USING MMV11-A CORE MEMORY                                         |   |

| 8.1       | GENERAL                                                           | Į |

| 8.2       | SWITCH-SELECTED ADDRESSING 8-1                                    | l |

| 8.2.1     | General                                                           |   |

| 8.3       | BUS RESTRICTIONS                                                  |   |

|           |                                                                   |   |

| CHAPTER 9 | USING MRV11-A READ-ONLY MEMORY                                    |   |

| 9.1       | GENERAL                                                           | 1 |

| 9.2       | JUMPER-SELECTED ADDRESSING AND CHIP TYPE                          |   |

| 9.2.1     | General                                                           |   |

| 9.2.2     | Chip Type Selection                                               |   |

| 9.2.3     | Addressing and Reply                                              |   |

| 9.3       | PROGRAMMING PROM AND ROM CHIPS                                    |   |

| 9.4       | PROGRAMMING RESTRICTIONS                                          |   |

| 9.5       | TIMING AND BUS RESTRICTION                                        | - |

|           |                                                                   |   |

| CHAPTER 10 | USER-DESIGNED INTERFACES                     |

|------------|----------------------------------------------|

| 10.1       | GENERAL                                      |

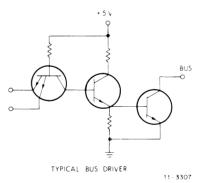

| 10.2       | BUS RECEIVER AND DRIVER CIRCUITS             |

| 10.3       | PROGRAMMED INTERFACE                         |

| 10.4       | INTERRUPT LOGIC                              |

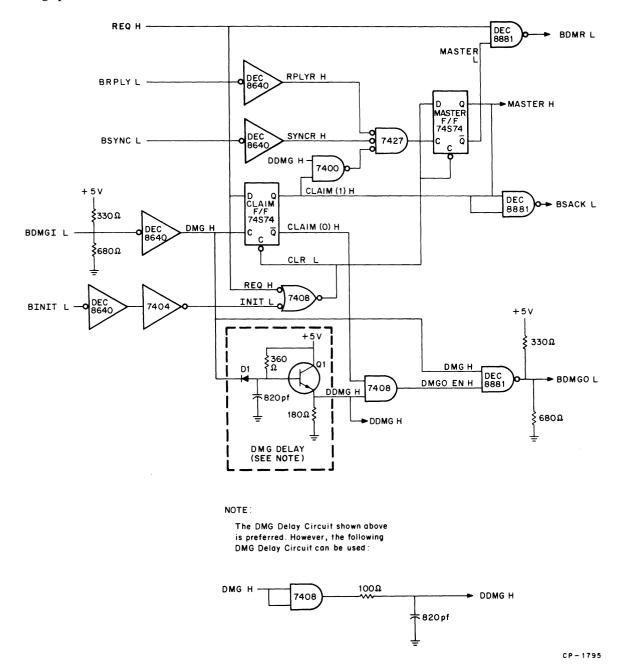

| 10.5       | DMA INTERFACE LOGIC                          |

|            |                                              |

| CHAPTER 11 | SYSTEM CONFIGURATION AND INSTALLATION        |

| 11.1       | GENERAL                                      |

| 11.2       | CONFIGURATION CHECKLIST                      |

| 11.3       | DEVICE PRIORITY                              |

| 11.3.1     | General                                      |

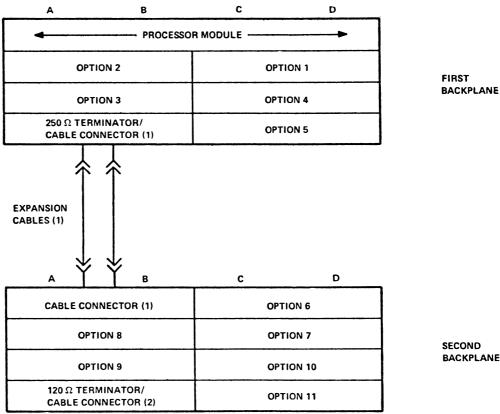

| 11.3.2     | Priority Selection Using the H9270 Backplane |

| 11.3.3     | H9270 Backplane/MMV11-A Configuration        |

| 11.4       | MODULE INSERTION AND REMOVAL                 |

| 11.5       | I/O CABLING                                  |

| 11.6       | PDP-11/03 INSTALLATION PROCEDURE             |

| 11.6.1     | Packaging and Mounting                       |

| 11.6.2     | Power Requirements                           |

| 11.6.3     | Environmental Requirements                   |

| 11.7       | LSI-11 SYSTEM INSTALLATION                   |

| 11.7.1     | General                                      |

| 11.7.2     | Mounting the H9270 Backplane                 |

| 11.7.3     | DC Power Connections                         |

| 11.7.3.1   | Voltage and Current Requirements             |

| 11.7.3.2   | H9270 Backplane Power Connections            |

| 11.7.4     | H9270 Backplane Ground Connection            |

| 11.7.5     | Environmental Requirements                   |

| 11.7.6     | Externally Generated Bus Signals             |

| 11.7.6.1   | General                                      |

| 11.7.6.2   | BDCOK H and BPOK H                           |

| 11.7.6.3   | BEVNT L Signal                               |

| 11.7.6.4   | BHALT L Signal                               |

| 11.8       | SYSTEM OPERATION                             |

| 11.8.1     | General                                      |

| 11.8.2     | PDP-11/03 Power-On                           |

| 11.8.3     | LSI-11 Power-On                              |

| 11.8.4     | ASCII Character Console Printout Program     |

| 11.9       | PAPER TAPE SYSTEM OPERATION                  |

| 11.9.1     | General                                      |

| 11.9.2     | References                                   |

| 11.9.3     | Loading the Absolute Loader                  |

| 11.9.4     | Loading Program Tapes                        |

| 11.9.4.1   | General                                      |

| 11.9.4.2   | Normal Loading Procedure                     |

| 11.9.4.3   | Relocated Loading Procedure                  |

| 11.9.4.4   | Self-Starting Programs                       |

| 11.9.5     | Program Starting and Execution               |

|            |                                              |

#### Page

| 11.10     | RT-11 SYSTEM OPERATION                          |

|-----------|-------------------------------------------------|

| 11.10.1   | General                                         |

| 11.10.2   | Using the RX01                                  |

| 11.10.3   | RXV11 Bootstrap 11-16                           |

| 11.10.3.1 | General                                         |

| 11.10.3.2 | Booting the System Using the REV11-A or REV11-C |

| 11.10.3.3 | Booting the System Via the Console Device       |

| 11.10.4   | Using the <b>RT</b> -11                         |

- CHAPTER 12 PERIPHERALS

- APPENDIX A MEMORY MAP

- APPENDIX B LSI-11 BUS PIN ASSIGNMENTS

- APPENDIX C 7-BIT ASCII CODE

- APPENDIX D SUMMARY OF LSI-11 INSTRUCTIONS

- APPENDIX E H9270 BACKPLANE CONFIGURATIONS

- APPENDIX F BUS INTERFACE I.C. PINS

- APPENDIX G LSI-11 BUS ACCESSORY OPTIONS INSTALLATION AND OPERATION

- APPENDIX H DLV11 I/O JUMPER CONFIGURATIONS

#### ILLUSTRATIONS

| Figure No.  | Title                                                 | Page  |

|-------------|-------------------------------------------------------|-------|

| 3-1         | Module Contact Finger Identification                  | . 3-2 |

| 3-2         | Quad Module Contact Finger Identification             |       |

| 3-3         | LSI-11, PDP-11/03 Backplane Module Pin Identification |       |

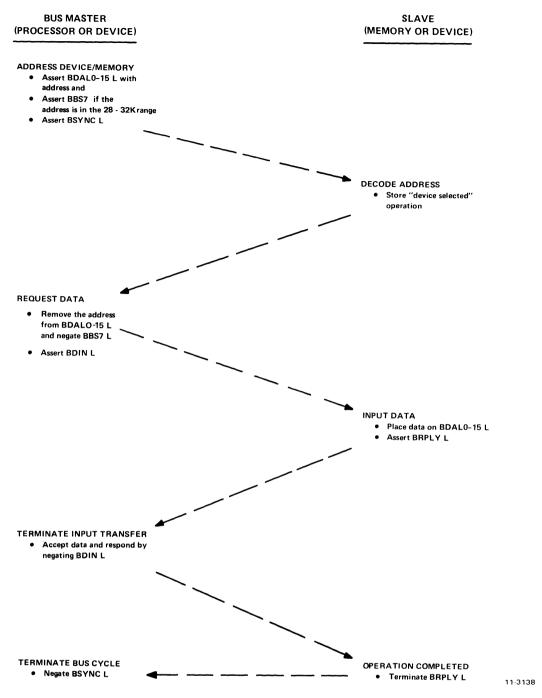

| 3-4         | DATI Bus Cycle                                        |       |

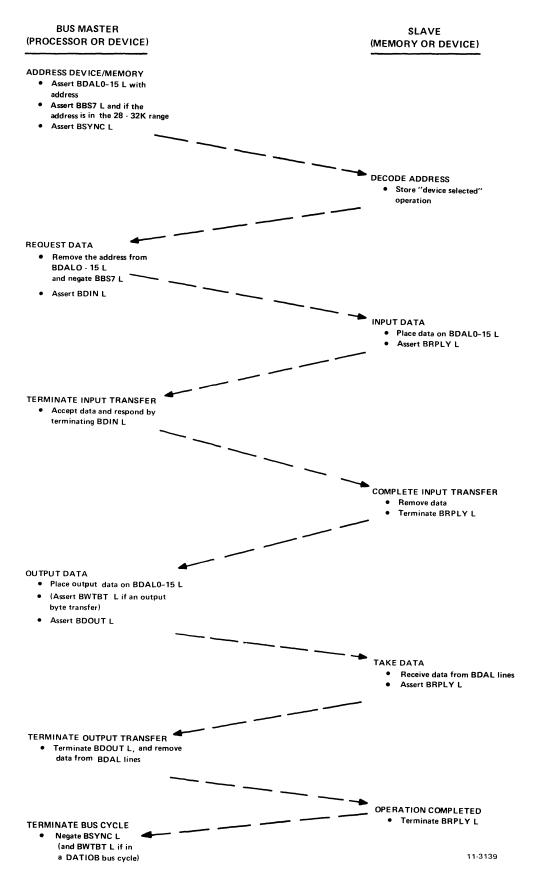

| 3-5         | DATIO or DATIOB Bus Cycle                             |       |

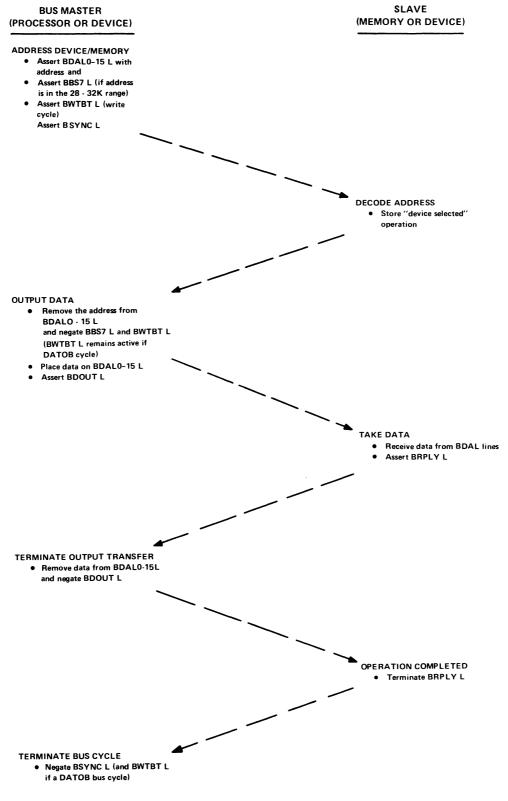

| 3-6         | DATO or DATOB Bus Cycle                               |       |

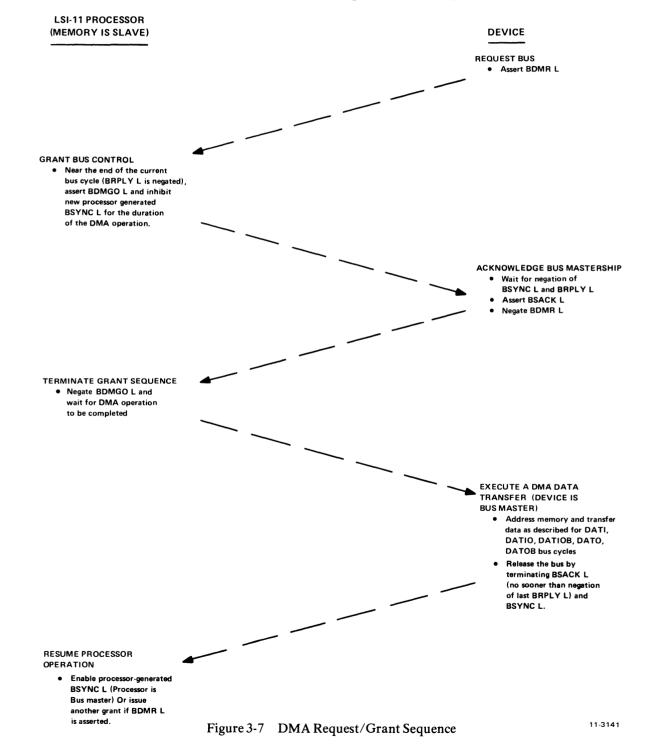

| 3-7         | DMA Request/Grant Sequence                            |       |

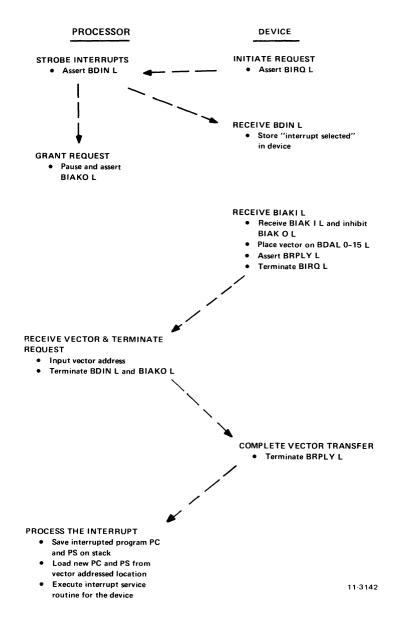

| 3-8         | Interrupt Request/Acknowledge Sequence                |       |

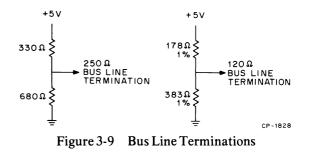

| 3-9         | Bus Line Terminations                                 |       |

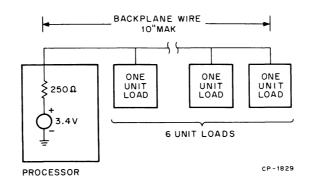

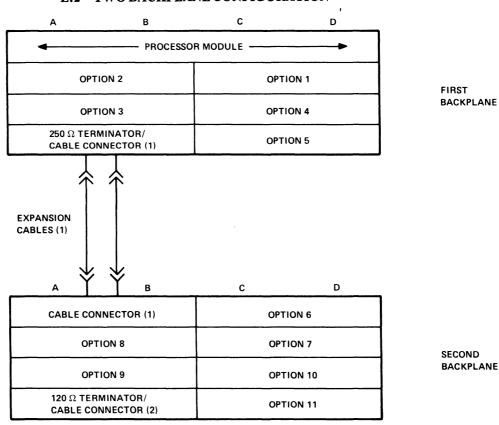

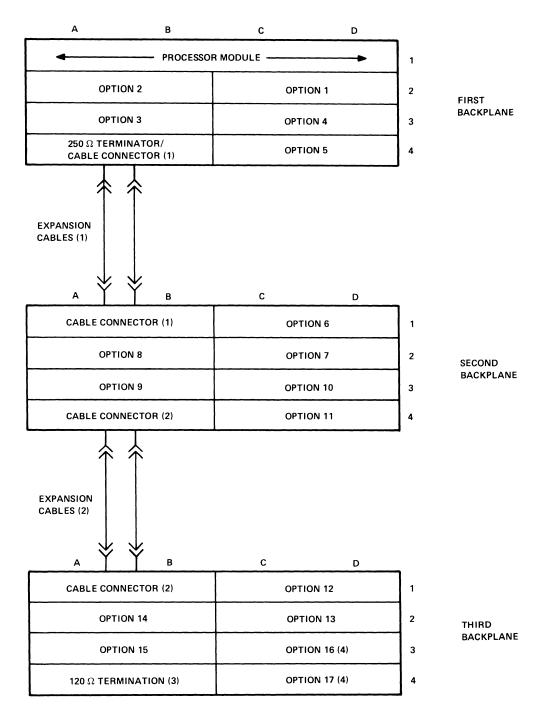

| 3-10        | Minimum Configurations                                |       |

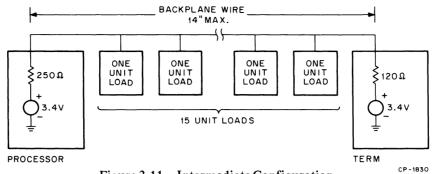

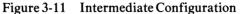

| 3-11        | Intermediate Configuration                            |       |

| 3-12        | Maximum Configuration                                 |       |

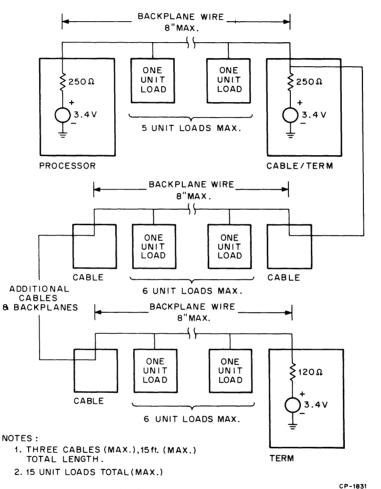

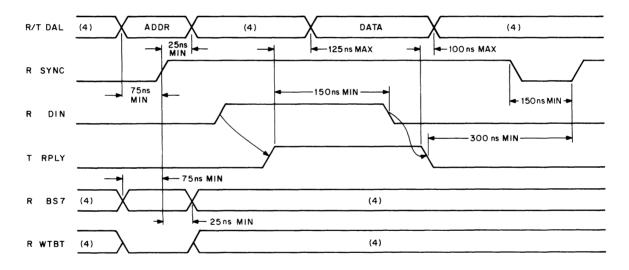

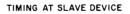

| 3-13        | DATI Bus Cycle Timing                                 |       |

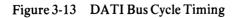

| 3-14        | DATO or DATOB Bus Cycle Timing                        |       |

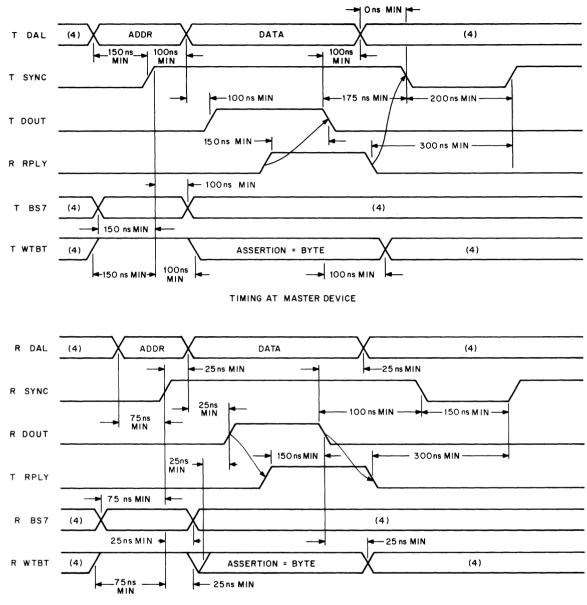

| 3-15        | DATIO Bus Cycle Timing                                |       |

| 3-16        | Interrupt Transaction Timing                          |       |

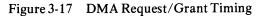

| 3-17        | DMA Request/Grant Timing                              |       |

| 3-18        |                                                       |       |

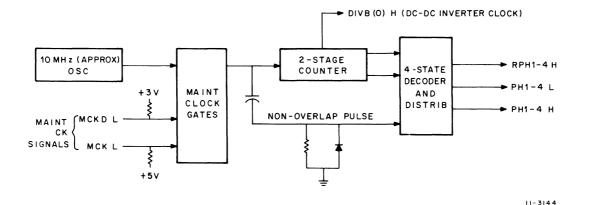

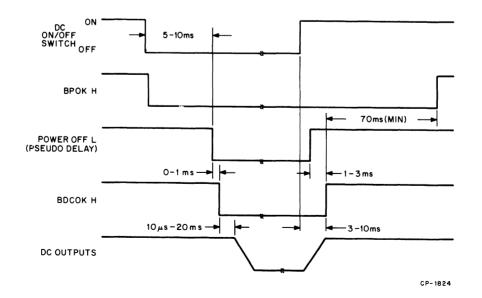

| 3-18<br>4-1 | Power-Up/Power-Down Timing                            |       |

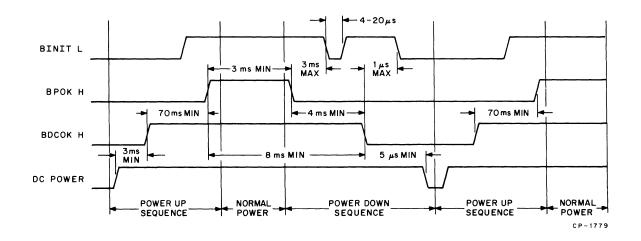

| 4-1         | KD11-F Microcomputer Logic Block Diagram              |       |

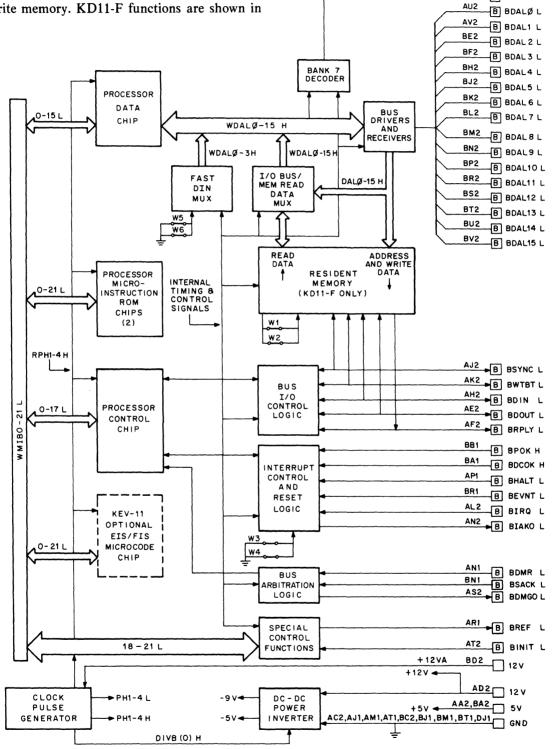

| 4-2<br>4-3  | Clock Pulse Generator                                 |       |

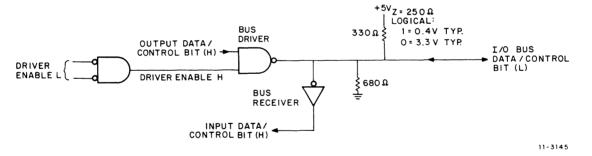

| 4-3<br>4-4  | LSI-11 Bus Loading and Driver/Receiver Interface      |       |

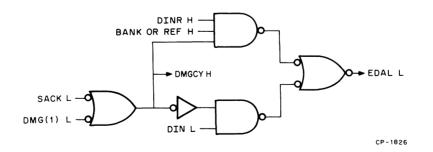

| • •         | EDAL L Logic                                          |       |

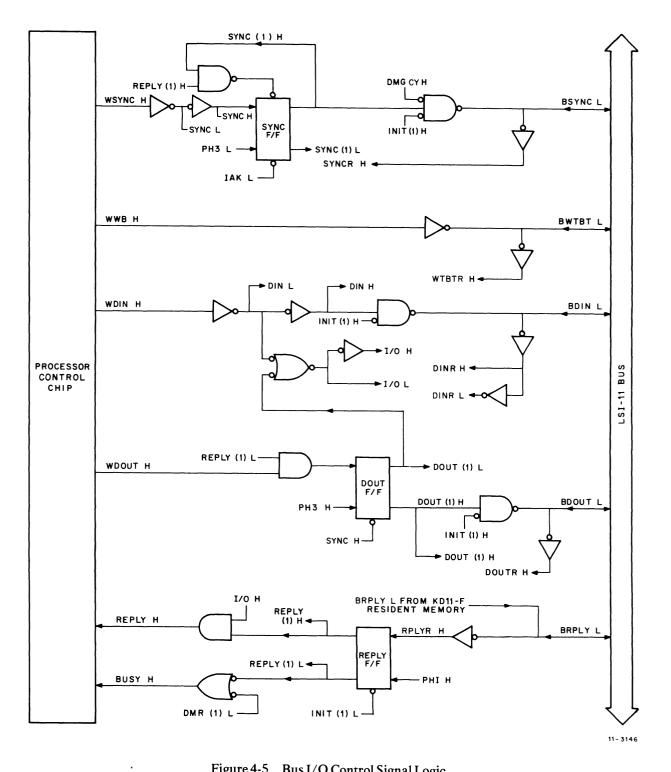

| 4-5         | Bus I/O Control Signal Logic                          |       |

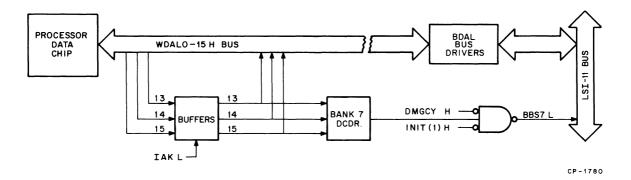

| 4-6         | Bank 7 Decoder                                        |       |

| 4-7         | Interrupt Control and Reset Logic                     |       |

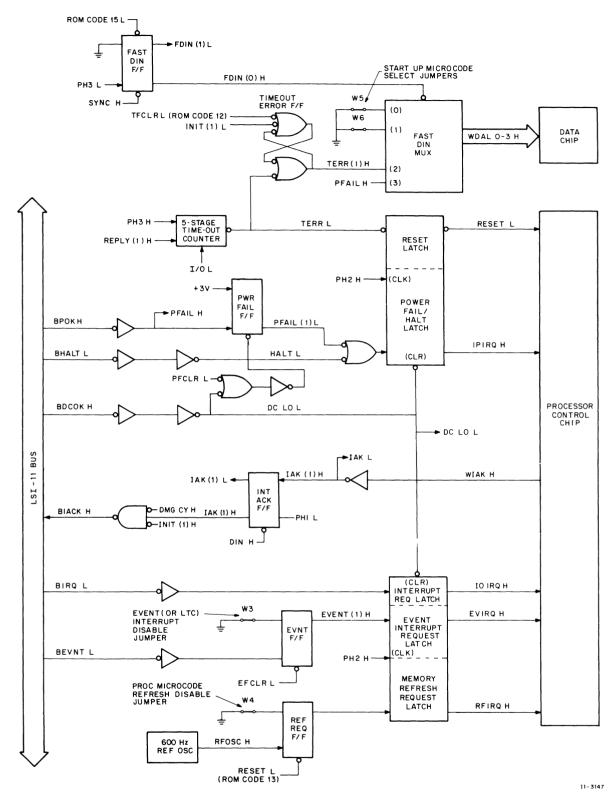

| 4-8         | Special Control Functions                             |       |

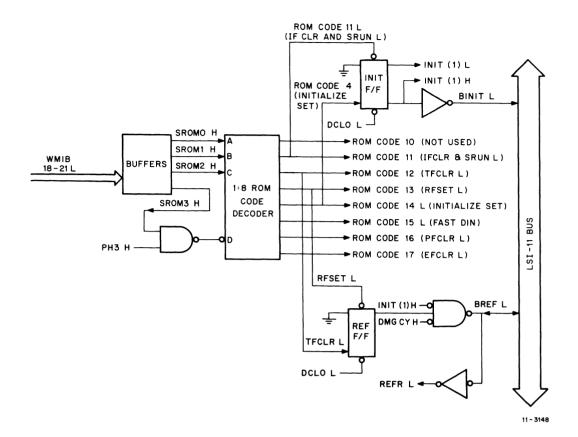

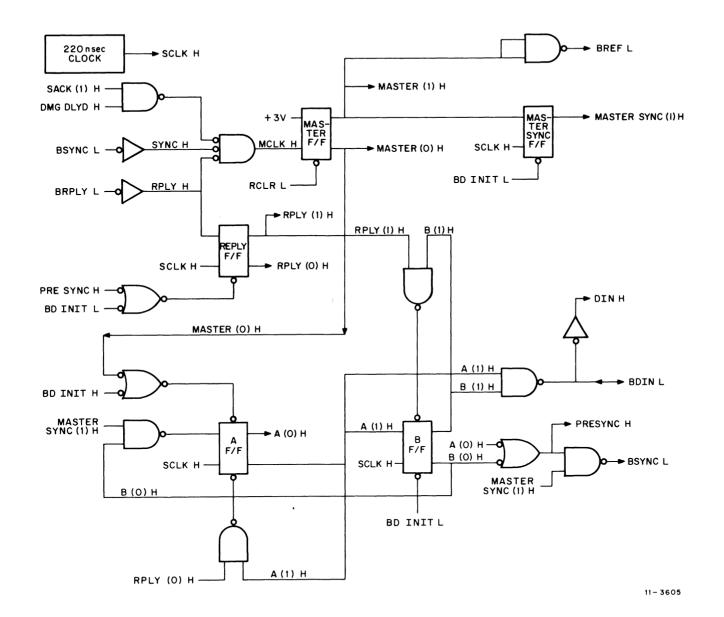

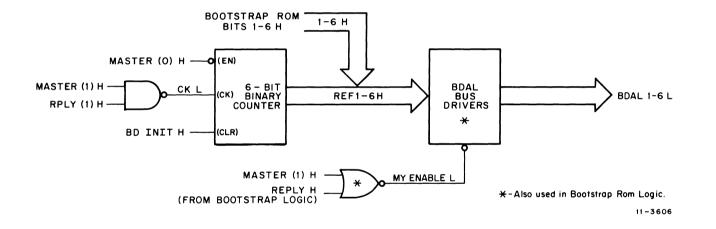

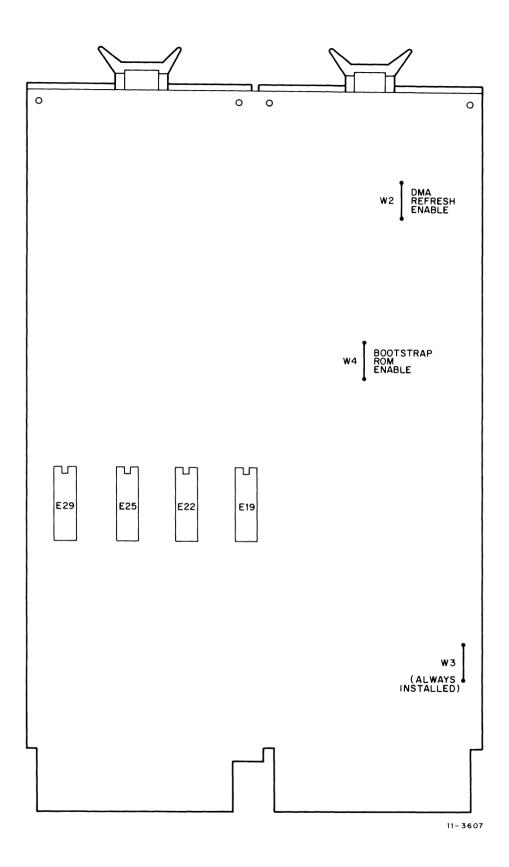

| 4-9         | Bus Arbitration Logic                                 |       |

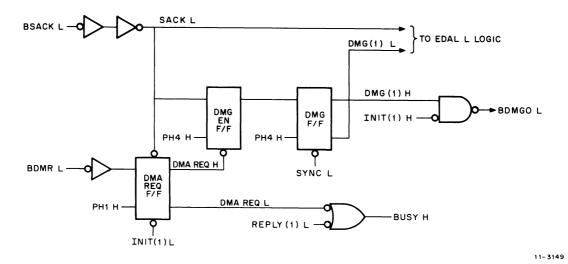

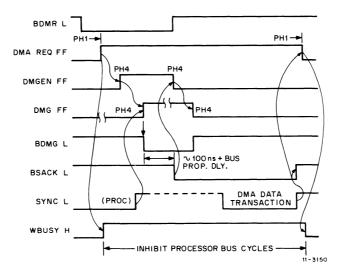

| 4-10        | DMA Grant Sequence                                    |       |

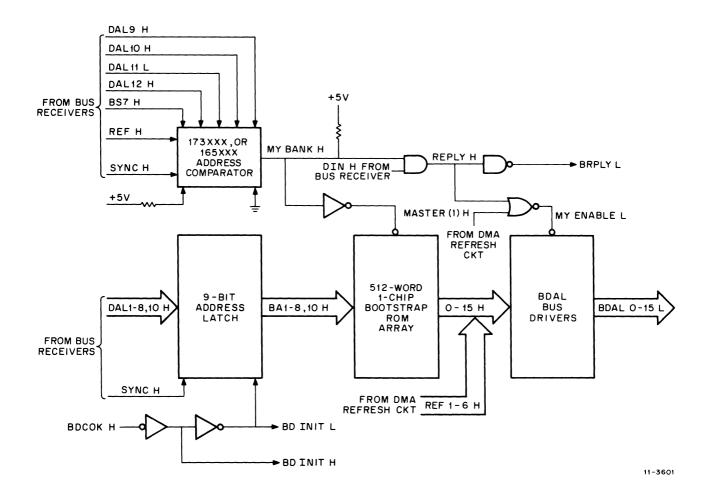

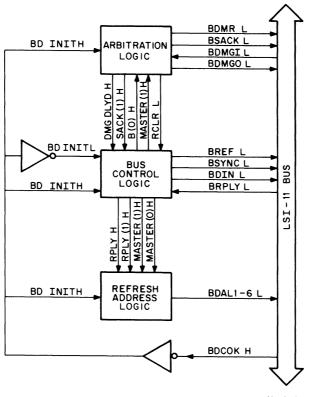

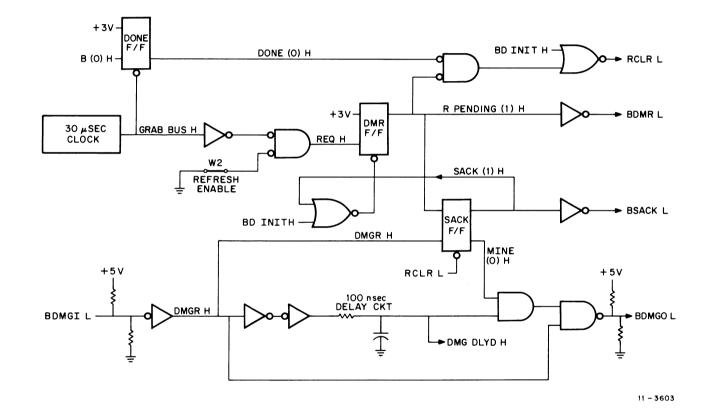

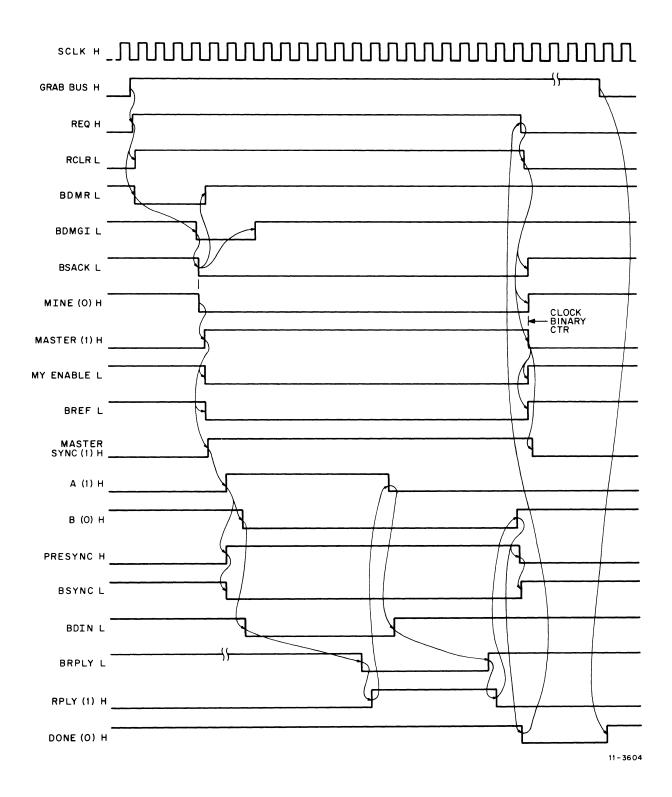

| 4-11        | KD11-F Resident Memory                                |       |

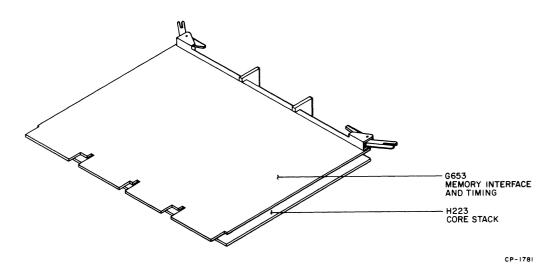

| 4-12        | MMV11-A Core Memory Option                            |       |

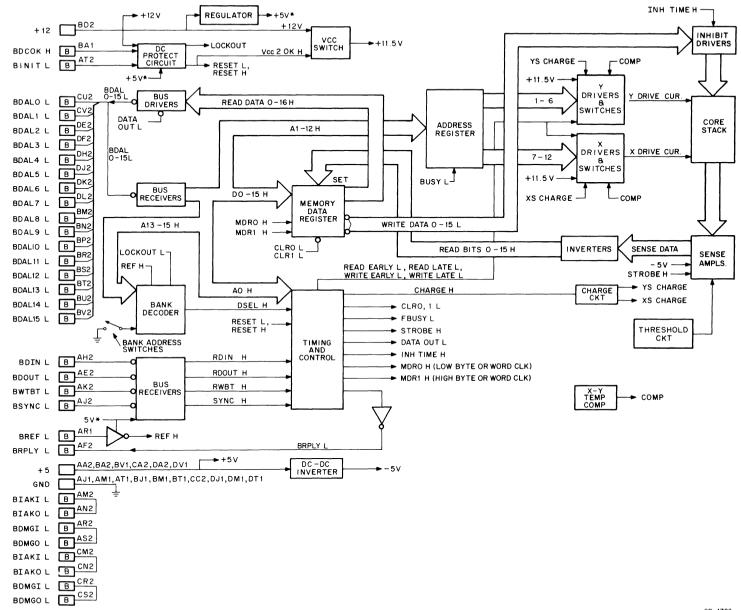

| 4-13        | MMV11-A Logic Block Diagram                           |       |

| 4-14        | MMV11-A Core Addressing                               |       |

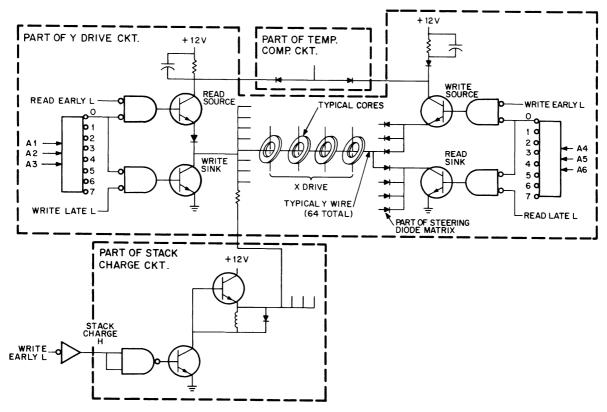

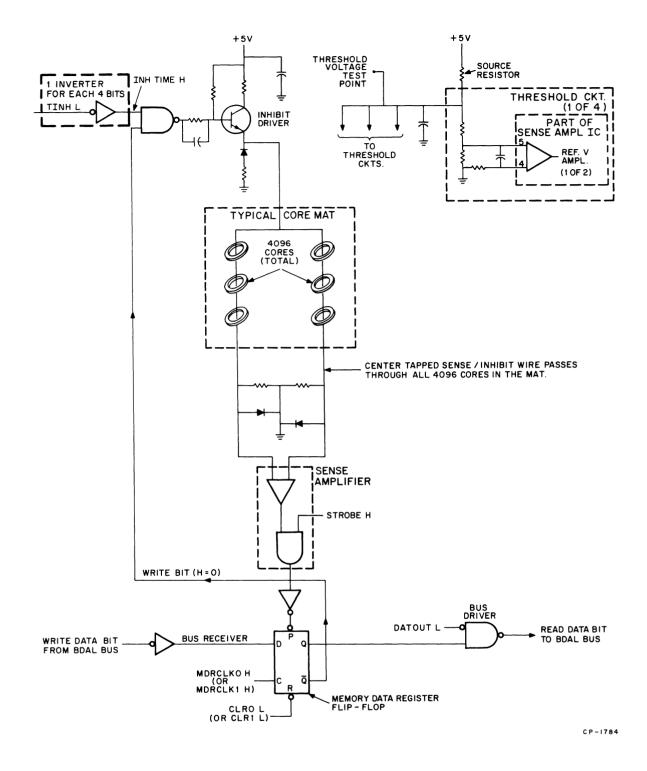

| 4-15        | MMV11-A Read/Write Bit Data Path                      |       |

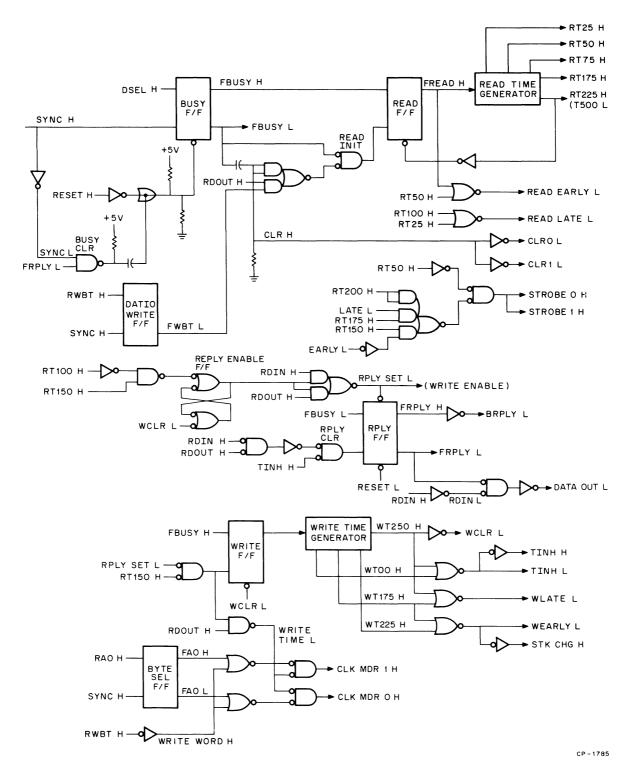

| 4-16        | MMV11-A Timing and Control Circuits                   |       |

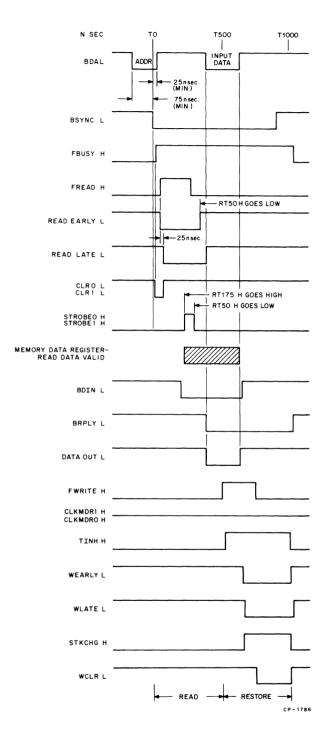

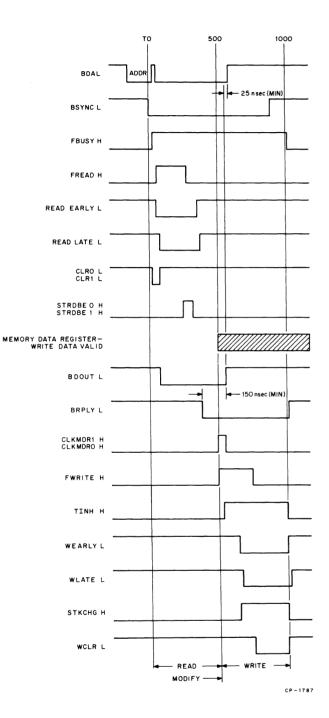

| 4-17        | Read-Restore Memory Cycle Timing                      |       |

| 4-18        | Read-Modify-Write Memory Cycle Timing                 |       |

| 4-19        | DC Protection and Vcc Switch Circuits                 |       |

| 4-20        | DC-DC Inverter Circuit                                |       |

| 4-21        | MRV11-A Logic Block Diagram                           | 4-25  |

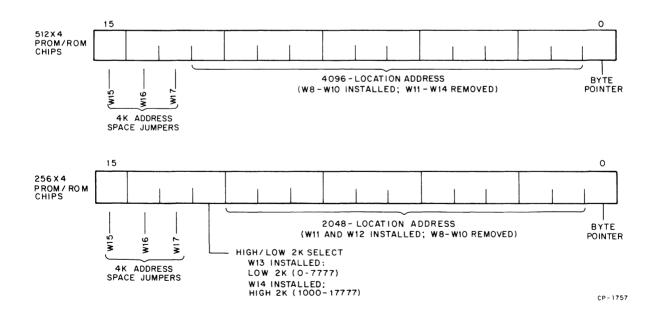

| 4-22        | 512 by 4-Bit Chip-Jumper Configuration                | 4-26  |

| 4-23        | 256 by 4-Bit Chip-Jumper Configuration                | 4-27  |

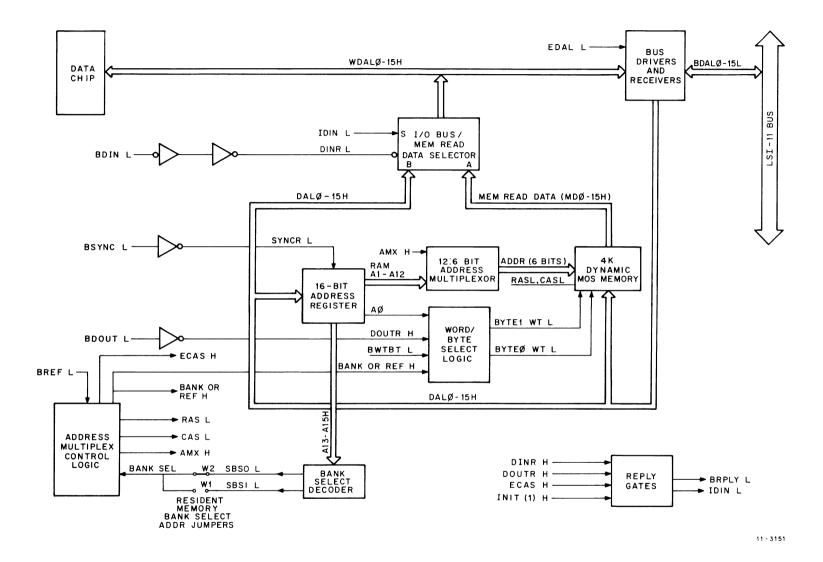

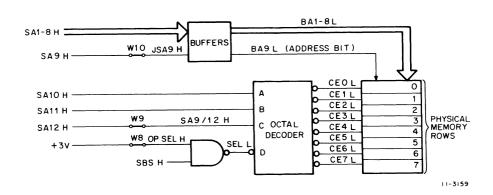

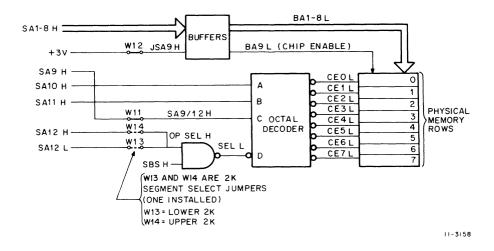

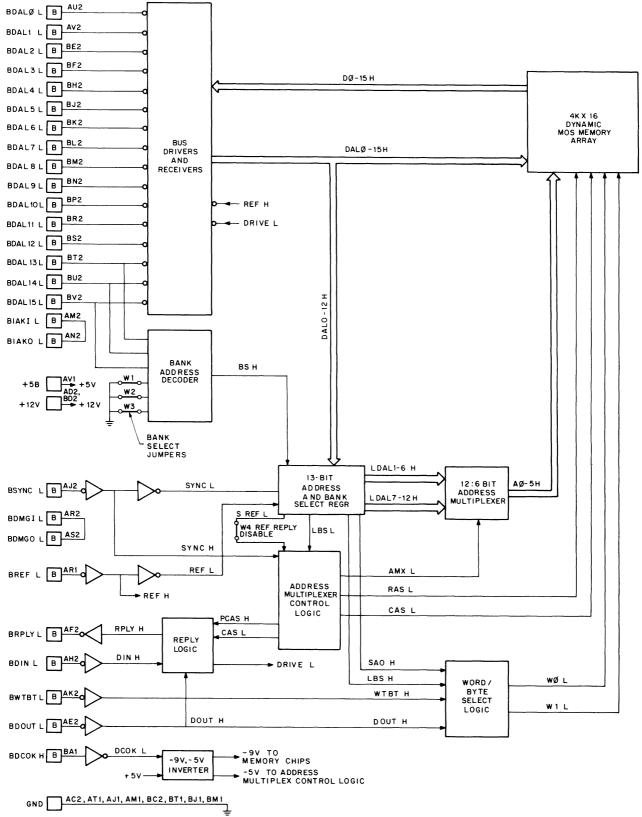

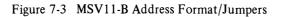

| 4-24        | MSV11-B Logic Block Diagram                           | 4-28  |

| 4-25        | This figure was deleted                               |       |

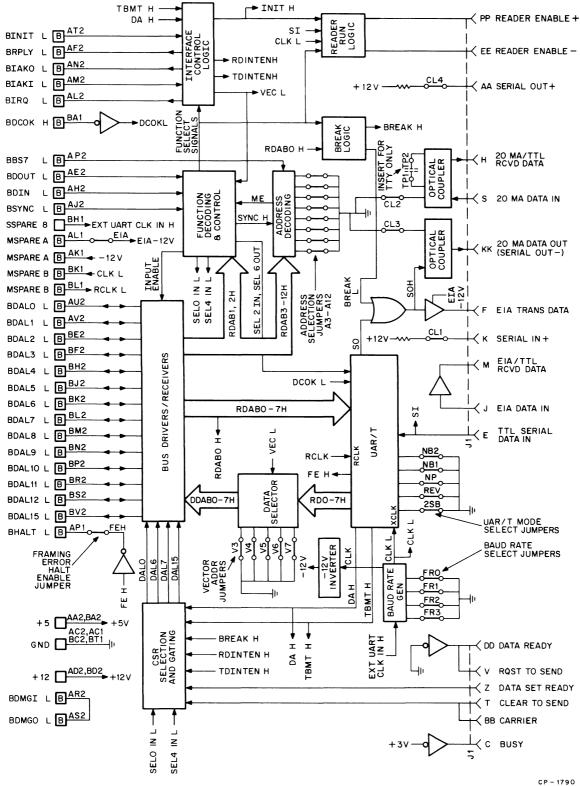

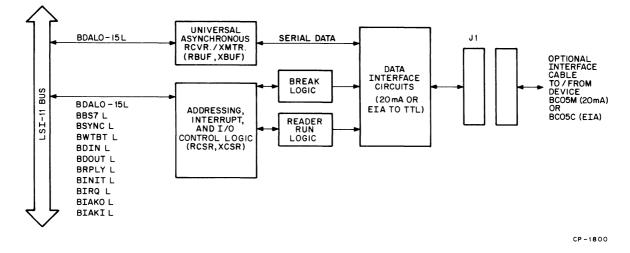

| 4-26        | DLV11 Logic Block Diagram                             | 4-33  |

| 4-27        | DRV11 Logic Block Diagram                             | 4-36  |

| 4-28        | H780 Power Supply Block Diagram                       |       |

| 4-29        | Unregulated Voltage and Local DC Power                |       |

| 4-30        | Basic Regulator Circuit                               |       |

| 4-31        | Overload and Short-Circuit Protection                 |       |

#### **ILLUSTRATIONS** (Cont)

#### Title

Figure No.

-

.

| 4-32 | Crowbar Circuit                                                         |   |

|------|-------------------------------------------------------------------------|---|

| 4-33 | Logic Signal Generation                                                 |   |

| 4-34 | Power-Up/Power-Down Sequence                                            |   |

| 4-35 | DC ON/OFF Circuit Timing                                                |   |

| 4-36 | H780 Connections                                                        |   |

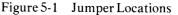

| 5-1  | Jumper Locations                                                        |   |

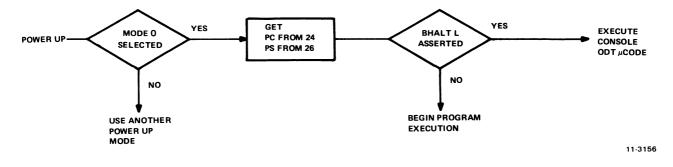

| 5-2  | Mode 0 Power-Up Sequence         5-3                                    |   |

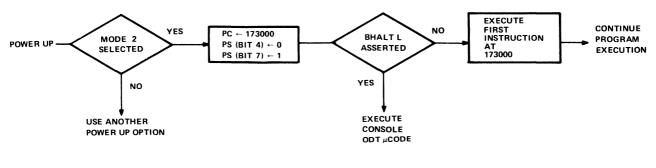

| 5-3  | Mode 2 Power-Up Sequence 5-3                                            |   |

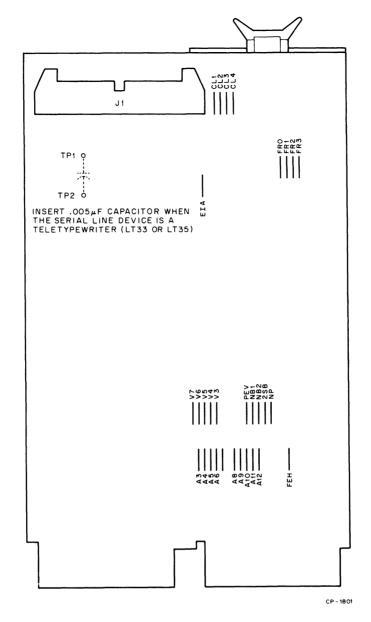

| 6-1  | DLV11 Serial Line Unit                                                  |   |

| 6-2  | DLV11 Jumper Locations                                                  |   |

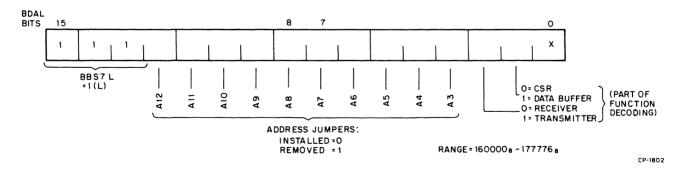

| 6-3  | DLV11 Addresses                                                         |   |

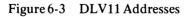

| 6-4  | DLV11 Interrupt Vectors                                                 |   |

| 6-5  | Active 20 mA Current Loop Interface                                     |   |

| 6-6  | Passive 20 mA Loop Jumper Configuration                                 |   |

| 6-7  | EIA Interface                                                           |   |

| 6-8  | DLV11 Word Formats                                                      |   |

| 6-9  | DRV11 Parallel Line Unit                                                |   |

| 6-10 | DRV11 Jumper Locations                                                  |   |

| 6-11 | DRV11 Device Address                                                    |   |

| 6-12 | DRV11 Vector Address                                                    |   |

| 6-13 | J1 or J2 Connector Pin Locations                                        |   |

| 6-14 | DRV11 Word Formats                                                      |   |

| 7-1  | MSV11-B 4K by 16-Bit Read/Write Memory                                  |   |

| 7-2  | MSV11-B Jumper Locations                                                |   |

| 7-3  | MSV11-B Address Format/Jumpers                                          |   |

| 8-1  | MMV11-A 4K by 16-Bit Core Memory 8-1                                    |   |

| 8-2  | Bank Address Switch Locations 8-2                                       |   |

| 8-3  | MMV11-A Addressing                                                      |   |

| 9-1  | MRV11-A Read-Only Memory                                                |   |

| 9-2  | MRV11-A Jumper Locations                                                |   |

| 9-3  | MRV11-A Address Word Formats                                            |   |

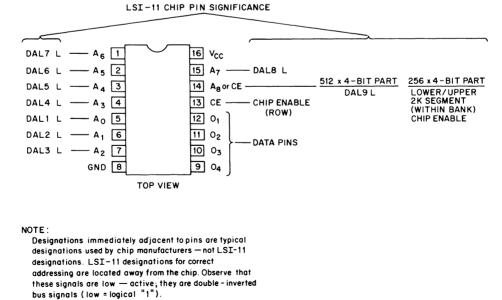

| 9-4  | PROM/ROM Chip Pin Addressing                                            |   |

| 10-1 | Bus Driver and Receiver Equivalent Circuits                             |   |

| 10-2 | Typical Bus Driver Circuit                                              |   |

| 10-3 | Programmed I/O Interface                                                |   |

| 10-4 | Dual Interrupt Interface                                                |   |

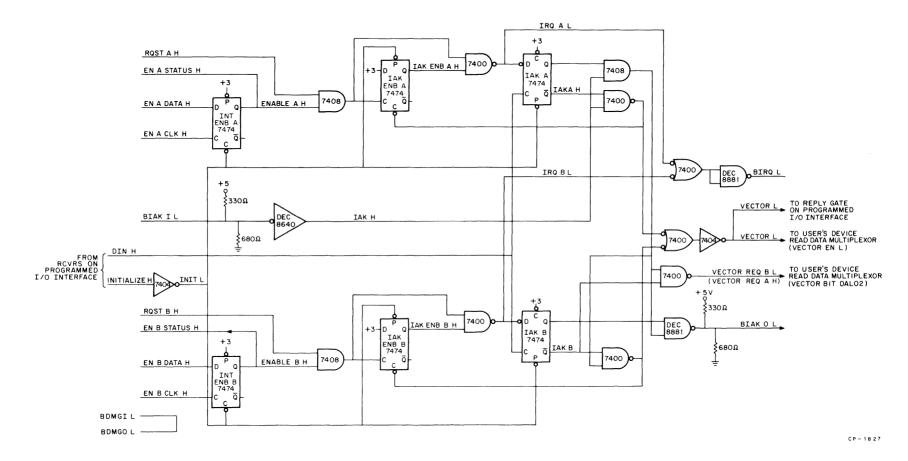

| 10-5 | DMA Arbitration Logic                                                   |   |

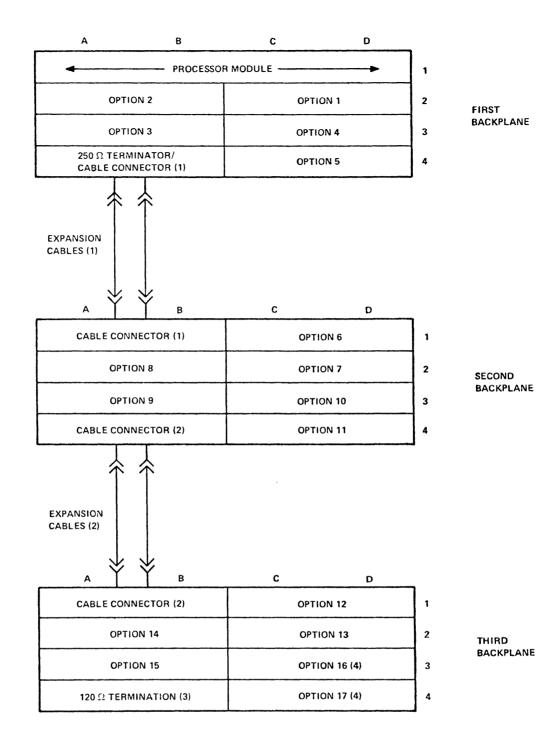

| 11-1 | Typical Configuration LSI-11 Backplane – Processor and Option Locations |   |

| 11-2 | H9270 Backplane/MMV11-A Core                                            |   |

| 11-3 | Module Installation in the H9270 Backplane                              |   |

| 11-5 | H9270 Backplane                                                         |   |

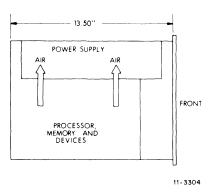

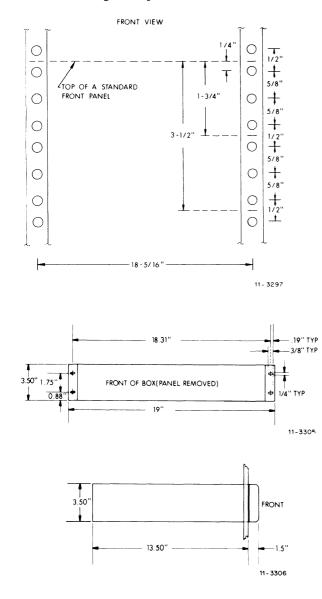

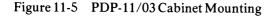

| 11-5 | PDP-11/03 Cabinet Mounting                                              |   |

| 11-5 | H9270 Backplane Mounting                                                |   |

| 11-7 | H9270 Side Mounting                                                     |   |

| 11-7 | H9270 Rear Mounting                                                     |   |

| 11-8 | H9270 Top and Bottom Mounting                                           |   |

| 11-2 |                                                                         | 1 |

#### **ILLUSTRATIONS** (Cont)

#### Title

Page

| 11-10 | H9270 Backplane Terminal Block                              |

|-------|-------------------------------------------------------------|

| 11-11 | H9270 Backplane Ground Wire DELETED 11-8                    |

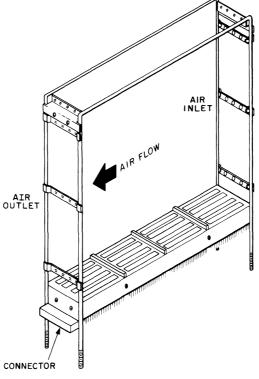

| 11-12 | H9270 Backplane Air Flow                                    |

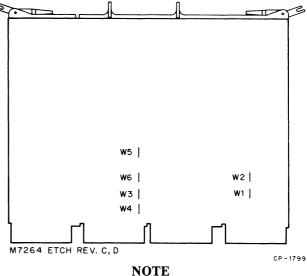

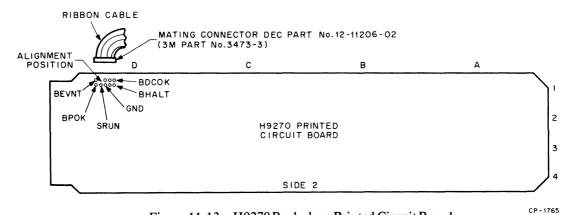

| 11-13 | H9270 Backplane Printed Circuit Board                       |

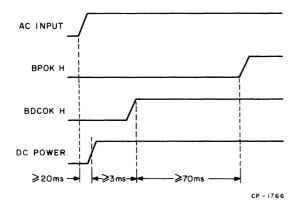

| 11-14 | Power-Up Sequence                                           |

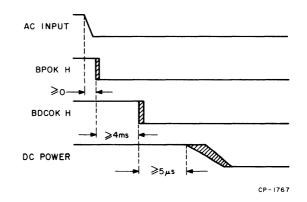

| 11-15 | Power-Down Sequence                                         |

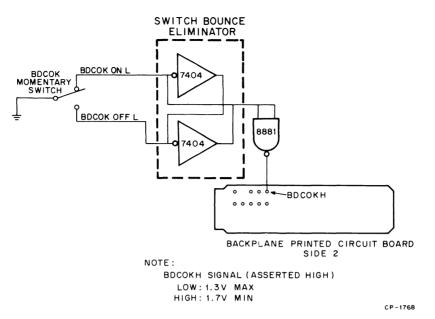

| 11-16 | BDCOK H Signal Routing Diagram                              |

| 11-17 | BEVNT L Signal                                              |

| 11-18 | Sample Console Printout                                     |

| 12-1  | Direct 20 mA Current Loop Interface                         |

| 12-2  | Telephone Line Interface Via Data Sets                      |

| 12-3  | Telephone Line Interface Via Acoustic Couplers         12-1 |

|       |                                                             |

#### TABLES

Title

#### Table No.

Figure No.

| 2.4   |

|-------|

|       |

|       |

|       |

|       |

|       |

|       |

|       |

| 5-2   |

|       |

|       |

|       |

|       |

|       |

|       |

| 9-1   |

| 9-4   |

|       |

|       |

|       |

|       |

| tions |

|       |

|       |

| : t   |

-

### CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

This manual contains technical data that will enable LSI-11 and PDP-11/03 microcomputer users to interface and use LSI-11 system components effectively. Before reading the detailed technical content of this manual, the user should become familiar with the basic characteristics of the LSI-11 processor, as described in the LSI-11, PDP-11/03 Processor Handbook.

#### **1.2 SCOPE**

This manual contains hardware descriptions and information for using LSI-11 system modules, including system configuration, installation, and interfacing. The manual is organized as follows:

| Chapter 1 | Introduction                                                                |

|-----------|-----------------------------------------------------------------------------|

| Chapter 2 | LSI-11 and PDP-11/03 System Overview                                        |

| Chapter 3 | LSI-11 Bus                                                                  |

| Chapter 4 | LSI-11 Module Descriptions<br>(including functional theory of<br>operation) |

| Chapters 5—9 | Use of the Various LSI-11<br>Modules (including jumper<br>configurations, interfacing,<br>and programming information)                     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 10   | User-Designed Interfaces                                                                                                                   |

| Chapter 11   | System Configuration and In-<br>stallation                                                                                                 |

| Chapter 12   | Peripherals (including the basic<br>devices available and the re-<br>quired LSI-11 interface mod-<br>ule, and cables required for<br>each) |

In addition, quick reference information is included in appendixes. This information includes a memory map, LSI-11 bus pin assignments, the 7-bit ASCII code, and a summary of LSI-11 instructions.

#### **1.3 REFERENCES**

The LSI-11, PDP-11/03 Processor Handbook is a required reference manual for using LSI-11 system components. In addition, standard hardware and interface components are listed and described in the Hardware/ Accessories Catalog and the Logic Handbook. -

#### 2.1 GENERAL

All LSI-11 and PDP-11/03 systems are configured by selecting various LSI-11 module options which can be installed in a backplane. Although individual system requirements (in which the LSI-11 system functions as a controller and/or data processor) may vary greatly in each application, LSI-11's modular concept allows for efficient use of the microcomputer in a compact, cost-effective, flexible system design. The PDP-11/03 is a packaged LSI-11 system, including a processor, 4K memory, enclosure, H9270 backplane, and H780 power supply.

In general, all LSI-11 and PDP-11/03 systems include the KD11-F or KD11-J microcomputer. The KD11-F is a single 8.5 by 10 inch module that contains the LSI-11 microprocessor and a 4K by 16-bit semiconductor read/write memory. The KD11-J uses the same microcomputer module as the KD11-F; however, it is supplied with the MMV11-A 4K by 16-bit core memory instead of the semiconductor memory. Either type of basic LSI-11 or PDP-11/03 system can be expanded by adding various memory and peripheral device interface options.

#### 2.2 SYSTEM CONFIGURATIONS

LSI-11 systems can be configured using one of three general approaches:

- 1. *Modules only:* The user purchases only the basic module(s).

- 2. *Modules and backplane:* The user purchases an LSI-11 subsystem that is easily mounted in a larger system.

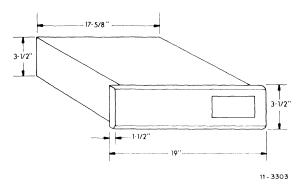

- 3. LSI-11 system in a box: The user purchases a PDP-11/03 system. It includes the KD11-F or KD11-J processor and 4K memory, a DLV11 serial line unit, an H9270 backplane, and an H780 power supply installed in a rack-mountable enclosure.

### CHAPTER 2 LSI-11 SYSTEM OVERVIEW

Systems are configured using the basic modules described in the following paragraphs.

#### 2.3 LSI-11 MICROCOMPUTER

This paragraph focuses on the KD11-F (processor and 4K semiconductor memory), which is the basic LSI-11 microcomputer. The KD11-J has all of the basic features of the KD11-F, except for the semiconductor memory; the MMV11-A core memory is included as a separate module.

Each KD11-F features:

- A low-cost, powerful processor for integration into any small- or medium-sized computer system.

- Direct addressing of 32K 16-bit words or 64K 8-bit bytes (K = 1024).

- Efficient processing of 8-bit characters without the need to rotate, swap, or mask.

- Asynchronous operation that allows system components to run at their highest possible speed; replacement with faster devices means faster operation without other hardware or software changes.

- A modular component design that provides ease and flexibility in configuring systems.

- Hardware memory stack for handling structured data, subroutines, and interrupts.

- Direct memory access for high data rate devices inherent in the bus architecture.

- Eight general-purpose registers that are available for data storage, pointers, and accumulators. Two are dedicated: SP and PC.

- A bus structure that provides positiondependent priority as peripheral device interfaces are connected to the I/O bus.

- Fast interrupt response without device polling.

- A powerful and convenient set of programming instructions.

- A jumper-selected power-up mode that enables restart through a power-up vector, console Octal Debugging Technique (ODT) microcode subset, or a bootstrap program.

- On-board 4K RAM

- An ODT microprogram that controls all manual entry/display functions previously performed by a control panel through a serial ASCII device (optional) which is capable of transmitting and receiving ODT commands and data.

- Compact size (only 8.5 by 10 in.).

#### 2.4 I/O BUS CONCEPT

The LSI-11 I/O bus is simple, fast, and easy to use as an interface between the LSI-11 microcomputer, memory, and peripheral interface modules. It comprises 17 control lines and a 16-line data/address bus. All modules connected to this bus receive the same interface signals.

Address/data and control lines are open-collector lines which are asserted low. The microcomputer module is capable of driving six device locations along the bus. Peripheral interface or memory modules can be installed in any location along this bus.

Both address and data words (or bytes) are time multiplexed over 16 bus lines. For example, during a programmed data transfer, the LSI-11 microcomputer first asserts an address on the bus for a fixed time. After the address time has been completed, the processor performs either an input or output data transfer; the actual data transfer is asynchronous and requires a response from the addressed device. Bus synchronization and control signals provide this function.

Control signal lines include two daisy-chained grant signals which provide a priority-structured I/O system. The highest priority device is the module electrically closest to the KD11-F (or KD11-J) module. Higher priority devices pass a grant signal to lower priority devices only when not requesting service. (Memory options or devices which do not use these signals must connect the chain.)

The KD11-F contains a memory address register and 4K bank address decoder for its resident memory, which can be assigned to bank 0 or bank 1. Bank 7 is also decoded when addresses ranging from 160000 to

177777 are placed on the bus. These addresses are normally used for addressing nonmemory devices, thus eliminating the need for bank address decoding on peripheral device interface modules.

The bus provides a vectored interrupt capability for any interface device. Hence, device polling is not required in interrupt processing routines. This results in a considerable savings in processing time when many devices requiring interrupt service are interfaced along the bus. When a device receives an interrupt grant (acknowledge), the KD11-F inputs the device's interrupt vector. The vector points to two addresses which contain a new processor status word and the starting address of the interrupt service routine for the device.

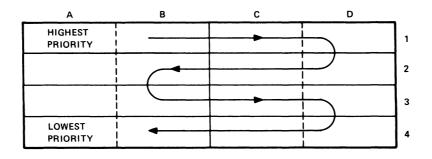

One bus signal line functions as an external event interrupt input to the KD11-F module. This signal line can be connected to a frequency source, such as a line frequency, and used as a line time clock (LTC) interrupt. A jumper on the KD11-F module enables or inhibits this function. When enabled, the device connected to this line has the highest interrupt priority external to the processor. Interrupt vector  $100_8$  is reserved for this function, and an interrupt request via the BEVNT line causes new PC and PS words to be loaded from locations  $100_8$  and  $102_8$ .

Memory refresh of dynamic MOS read/write memory is accomplished by bus signals. Refresh operation is controlled by either the processor module microcode or a user-supplied intelligent DMA device.

The processor can be placed in the Halt mode by asserting one bus signal. This allows peripheral devices or a separate switch to invoke console ODT microcode operation.

Power-up/power-down sequencing is controlled by two bus signals. One signal, when in its true state, implies that primary power is normal. The second signal is in its true state when sufficient dc power is available (and voltages are normal) for normal system logic operation. These signals are produced by circuits contained in the H780 power supply (PDP-11/03 only) or by the user's system (circuits external to the LSI-11 system components).

Direct memory access (DMA) operation is controlled by three bus signals. Logic on the processor module, which is normally bus master, arbitrates DMA requests and grants bus mastership to the highest priority device requesting the bus. Priority is position-dependent through the use of a daisy-chained DMA grant signal.

#### 2.5 MEMORY OPTIONS

Memory options are available for expanding memory to 28K. The basic LSI-11 microcomputer is supplied with read/write memory. KD11-F's memory consists of a 4K dynamic MOS array which is physically located on the processor module. KD11-J's memory is a 4K magnetic core array contained on a separate module; the processor module supplied with the KD11-J contains no semiconductor memory components.

Optional memory modules include:

MRV11-AA — 4K by 16-bit programmable readonly memory on an 8.5 by 5 inch module. Requires one device location on the I/O bus. Can be configured using either 256 by 4-bit or 512 by 4bit field programmable or masked ROMs for a maximum capacity of 2048 or 4096 16-bit words.

MMV11-A — 4K by 16-bit core memory on an 8.5 by 10 by 0.9 inch module. Requires two device locations on the I/O bus when installed in the backplane (preferred location slots A4-D4). This allows a daughterboard (part of the MMV-11-A) to extend slightly beyond the backplane without using additional device locations. If not installed in this location, the MMV11-A requires four device locations because of the additional module thickness (0.9 inch instead of 0.5 inch for all other modules).

MSV11-B - 4K by 16-bit dynamic MOS read/ write memory on an 8.5 by 5 inch module. Requires one device location on the I/O bus. Refresh is automatically performed by the KD11-F processor microcode or by an external device.

#### 2.6 PERIPHERAL INTERFACE OPTIONS

Two basic interface modules are used for serial and parallel programmed I/O transfer between the LSI-11 bus and peripheral devices. The DLV11 is a serial line unit used for serial 5- to 8-bit data transfers between a device and the bus. It interfaces either EIA-compatible or 20 mA current loop devices to the bus using optional cables which select the type of serial interface desired. The cables are completely connector- and pincompatible with available modems, DECwriter, DECscope, and teletypewriter options. The DRV11 is a general-purpose parallel line unit interface which is capable of 16-bit input and 16-bit output parallel transfers to/from user devices. Both interface units contain all required control/status registers, interrupt control logic, and bus interface logic. The user can easily assign unique device and vector addresses for each device by changing the jumpers on each interface module.

Peripheral interface options include:

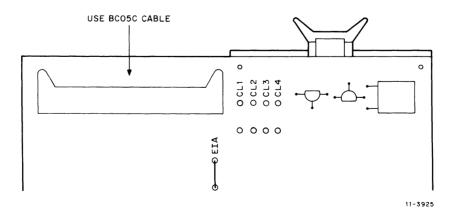

DLV11 — Serial line unit interface on an 8.5 by 5 inch module. Requires one device location on the bus. Jumpers select crystal-controlled baud rates (50—9600 baud) and serial word format, including number of stop bits, number of data bits, and even, odd, or no parity bit. Optional interface cables include the BC05M, which connects the DLV11 to 20 mA current loop peripheral devices, and the BC05C, which connects the DLV11 to EIA-compatible devices (modems) via a Cinch DB-25P connector.

DRV11 — General-purpose parallel line unit interface on an 8.5 by 5 inch module. Requires one device location on the bus. Two 40-pin connectors are included on the module for user interface application. One is the 16-bit input and the other is the 16-bit output. Optional interface cables are described in the Hardware/Accessories Catalog.

# 2.7 BACKPLANE, POWER SUPPLY, AND HARDWARE OPTIONS

Backplane, power supply, and hardware options provide a convenient means for configuring the LSI-11 system. An LSI-11 system usually requires an interconnection scheme. The H9270 backplane assembly is the most convenient to use. It is prewired for the LSI-11 I/O bus pinning and can accept one KD11-F microcomputer and up to six LSI-11 interface or memory modules. It includes a card guide assembly which provides mechanical stability for the modules. Power and ground are applied to the backplane via a screwterminal block.

Power can be obtained from the system in which the LSI-11 subsystem is installed, or the H780 (115 or 230 Vac input) power supply (included in PDP-11/03 systems) can be used. The power supply provides the required regulated voltages for all LSI-11 modules connected to the backplane. In addition, it generates the necessary bus signals to initiate the KD11-F or KD11-J power-up or power-fail processor sequence. Hardware options include standard hardware accessories listed in DIGITAL's Hardware/Accessories Catalog.

#### 2.8 POWER REQUIREMENTS

The power requirements for LSI-11 system modules are given in Table 2-1.

| Designation       | $+5V \pm 5\%$ |      | $+12V \pm 3\%$ |        |

|-------------------|---------------|------|----------------|--------|

| Designation       | Тур           | Max  | Тур            | Max    |

| KD11-F            | 1.8A          | 2.4A | 0.8A           | 1.6A   |

| KD11-J            | 6.4A          | 9.0A | 1.2A           | 1.5A   |

| DLV11             | 1.0A          | 1.6A | 180 mA         | 250 mA |

| DRV11             | 0.9A          | 1.6A |                |        |

| MRV11-AA (with-   |               |      |                |        |

| out memory chips) | 0.4A          | 0.6A |                |        |

| MRV11 (with 4K    |               |      |                |        |

| memory chips)     | 2.8A          | 4.1A |                |        |

| MSV11-B           | 0.6A          | 1.2A | 0.3A           | 0.7A   |

| MMV11-A (standby) | 3.0A          |      | 0.2A           |        |

| MMV11-A           |               |      |                |        |

| (operating)       | 7.0A          |      | 0.6A           |        |

Table 2-1

LSI-11 Modules Power Requirements

The input power requirements for PDP-11/03 systems are:

#### PDP-11/03-AA or -BA

100-127 Vac (115 Vac nominal),  $50 \pm 1$  Hz or  $60 \pm 1$  Hz, single phase, 400 W maximum (including options) (190 W typical)

#### PDP-11/03-AB or -BB

200-254 Vac (230 Vac nominal),  $50 \pm 1$  Hz or  $60 \pm 1$  Hz, single phase, 400 W maximum (including options) (190 W typical)

#### 2.9 GENERAL SPECIFICATIONS

#### Dimensions (in.)

KD11-F

$10.5\times8.50\times0.5$

#### MSV11-B

5×8.50×0.5

MRV11-AA 5×8.50×0.5

MMV11-A

10×8.50×0.9

#### DLV11

5×8.50×0.5 DRV11

5×8.50×0.5

#### Electrical

Input Logic Levels TTL Logical Low: 0.8 Vdc max TTL Logical High: 2.0 Vdc min

- Output Logic Levels TTL Logical Low: 0.4 Vdc max TTL Logical High: 2.4 Vdc min

- Bus Receivers Logical Low: 1.3 Vdc max,-10µA max at 0V Logical High: 1.7 Vdc min, 80µA max at 2.5V

#### **Bus Drivers**

Logical Low: 0.8 Vdc max at 70 mA Logical High:  $25\mu$ A max at 3.5V

#### Environmental

Ambient Temperature, *PDP-11/03 System:* Operating: 5° to 40° C

Ambient Temperature, LSI-11 modules: Operating:  $5^{\circ}$  to  $50^{\circ}$  C ( $41^{\circ}$  to  $122^{\circ}$  F) Nonoperating:  $-40^{\circ}$  to  $66^{\circ}$  C ( $-40^{\circ}$  to  $+ 150^{\circ}$  F) Derate at  $6^{\circ}$ C/1000 ft. above 8000 ft.

#### Humidity

10 to 90 percent, noncondensing

#### Air Flow

200 linear ft./minute min. (modules only)

### CHAPTER 3 THE LSI-11 BUS

#### 3.1 CHOOSING AN I/O TRANSFER TYPE

Before interfacing the processor with any peripheral device, the designer must determine the type of I/O transfer that would be best suited for the application: programmed I/O transfers, DMA, or interrupt-driven transfers.

Programmed I/O transfers are executed by single- or double-operand instructions. The instruction can be used to input or output a 16-bit data word or an 8-bit byte. By including the device's address as the effective source or destination address, the user selects the input or output operation. In many instances, the programmer inputs a byte from the device's control/status register (CSR) to determine that the device has input data ready or that it is ready to accept the processor's output data.

DMA transfers are the fastest method of transferring data between memory and a device. They can occur between processor bus cycles and do not alter processor status in any way. Addressing, controlling the size of the data block (number of word or byte transfers in the operation), and type of transfer are under the control of the requesting device. The processor does not modify data being moved in the DMA mode. Thus, blocks of data can be moved at memory speeds via the DMA transfer mode. The processor sets up these conditions before the DMA transfer is executed.

Interrupts allow the processor to continue a programmed operation (sometimes called a background program) without waiting for a device to become ready to transfer data. When the device does become ready, it interrupts the processor's background program execution and causes execution of a device interrupt service routine. After the device's service routine has been executed, the background program is restored and program execution resumes at the point where it was interrupted.

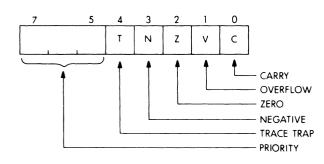

#### **3.2 DEVICE PRIORITY**

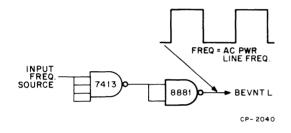

Each device has an I/O priority based on its distance from the processor. When two or more devices request interrupt service, the device electrically closer to the microcomputer will receive the interrupt grant (acknowledge). The microcomputer can be inhibited from issuing more grants by setting the processor's priority to 4 in the PS word. Bit 7 in the new PS word should be a 1. If further interrupts are to be serviced, the processor's priority should be 0, and bit 7 in the new PS word should be a 0. Consequently, interrupts can be nested to any level. Factors to consider when assigning device priorities are:

- 1. Device Operating Speed Data from a fast device is available for only a short period; highest priorities are usually assigned to fast devices to prevent loss of data and to prevent the bus from being tied up by slower devices.

- 2. Ease of Data Recovery If data from a device is lost, recovery may be automatic, may require manual intervention, or may be impossible to recover; highest priorities are assigned to devices whose data cannot be recovered.

- 3. Service Requirements Some devices cannot function without help from the processor, while DMA devices can operate independently and require only minimal processor intervention; devices requiring continual help from the processor for servicing are assigned to lowest priorities to prevent tying up the processor.

Both address and data are multiplexed onto the 16 BDAL lines. In addition, individual control signals sequence programmed I/O operations, direct memory access (DMA), and processor interrupts. Any bus-

compatible module can be inserted into any bus location and still receive interface signals; however, the module's priority, which is position-dependent along the bus, will change.

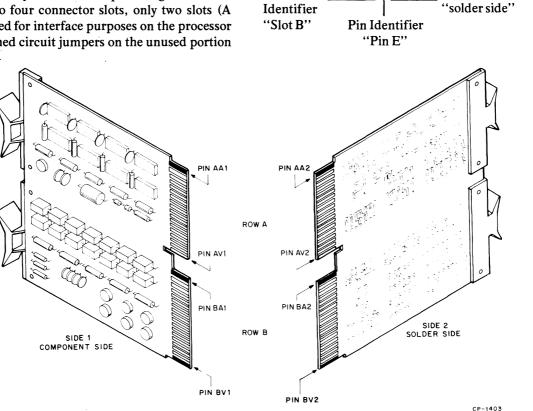

# 3.3 MODULE CONTACT FINGER IDENTIFICATION

DIGITAL plug-in (FLIP CHIP) modules, including LSI-11 modules, all use the same contact finger (pin) identification system. The LSI-11 I/O bus is based on the use of double-height modules. These modules plug into a two-slot bus connector, each containing 36 lines per slot (18 each on component and solder sides of the circuit board). Although the LSI-11 processor module and core memory module are quad-height modules that plug into four connector slots, only two slots (A and B) are used for interface purposes on the processor module. Etched circuit jumpers on the unused portion of the module maintain continuity of grant signals BIAKI L to BIAKO L and BDMGI L to BDMGO L. These daisy-chained signals are described later.

Slots, shown as ROW A and ROW B in Figure 3-1, include a numeric identifier for the side of the module. The component side is designated side "1" and the solder side is designated side "2." Letters ranging from A through V (excluding G, I, O, and Q) identify a particular pin on a side of a slot. Hence, a typical pin is designated as:

Module Side Identifier

BE2

Slot (Row)

Figure 3-1 Module Contact Finger Identification

Note that the positioning notch between the two rows of pins mates with a protrusion on the connector block for correct module positioning.

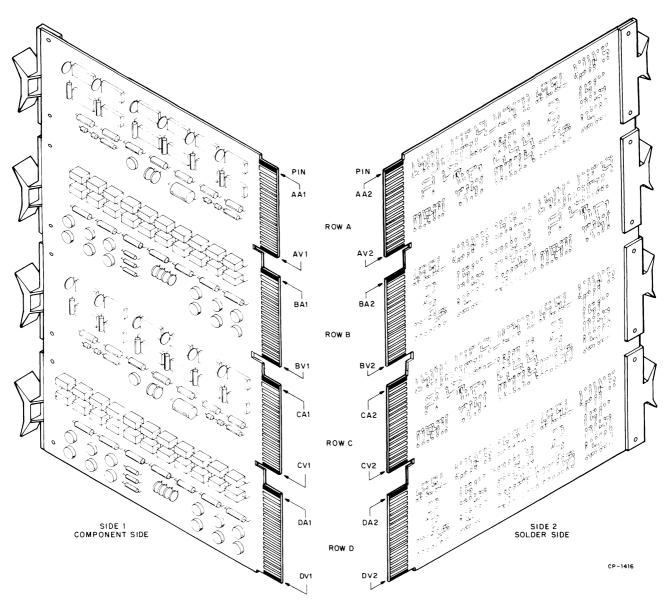

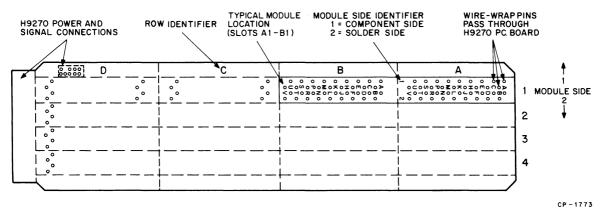

Quad-height modules are similarly pin numbered. They are identified in Figure 3-2. Individual connector pins, viewed from the underside (wiring side) of a backplane, are identified as shown in Figure 3-3. Only the pins for one bus location (two slots) are shown in detail. This pattern of pins is repeated eight times on the H9270 backplane, allowing the user to install one LSI-11 microcomputer module (four slots) and up to six additional two-slot modules.

Figure 3-2 Quad Module Contact Finger Identification

Figure 3-3 LSI-11, PDP-11/03 Backplane Module Pin Identification

#### 3.4 BUS SIGNALS

8 m

H9270 backplane pin assignments are listed and described in Table 3-1. Only slots A and B are listed. However, they are identical to slots C and D,

respectively. Applicable bus cycle timing and specifications are discussed in Paragraphs 3.12, 3.13, and 3.14.

| Bus<br>Pin        | Mnemonic                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AA1<br>AB1        | BSPARE1<br>BSPARE2            | Bus Spare (Not Assigned. Reserved for DIGITAL use.)                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AC1<br>AD1        | BAD16<br>BAD17                | Extended address bits (not implemented)                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| AE1<br>AF1<br>AH1 | SSPARE1<br>SSPARE2<br>SSPARE3 | Special Spare (Not assigned, not bused. Available for user interconnections.)                                                                                                                                                                                                                                                                                                                                                                            |  |

| AJ1               | GND                           | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AK1<br>AL1        | MSPAREA<br>MSPAREA            | Maintenance Spare — Normally connected on the backplane at each optio location (not bused connection).                                                                                                                                                                                                                                                                                                                                                   |  |

| AM1               | GND                           | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AN1               | BDMR L                        | Direct Memory Access (DMA) Request — A device asserts this signal to reque<br>bus mastership. The processor arbitrates bus mastership between itself and a<br>DMA devices on the bus. If the processor is not bus master (it has completed<br>bus cycle and BSYNC L is not being asserted by the processor), it grants but<br>mastership to the requesting device by asserting BDMGO L. The device r<br>sponds by negating BDMR L and asserting BSACK L. |  |

| AP1               | BHALTL                        | Processor Halt — When BHALT L is asserted, the processor responds by haltin<br>normal program execution. External interrupts are ignored but memory refre-<br>interrupts (enabled if W4 on the processor module is removed) and DMA r<br>quest/grant sequences are enabled. When in the halt state, the processor ex-<br>cutes the ODT microcode and the console device operation is invoked.                                                            |  |

| AR1               | BREFL                         | Memory Refresh — Asserted by a processor microcode-generated refresh i<br>terrupt sequence (when enabled) or by an external device. This signal forces<br>dynamic MOS memory units to be activated for each BSYNC L/BDIN L b<br>transaction.                                                                                                                                                                                                             |  |

|                   |                               | CAUTION<br>The user must avoid using multiple DMA data transfers [Burst or<br>"hog" mode] during a processor-generated refresh operation so that<br>a complete refresh cycle can occur once every 1.6 ms.                                                                                                                                                                                                                                                |  |

| AS1               | PSPARE3                       | Spare (Not assigned. Customer usage not recommended.)                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| AT1               | GND                           | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| AU1               | PSPARE1                       | Spare (Not assigned. Customer usage not recommended.)                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| AV1               | +5B                           | +5 V Battery Power — Secondary $+5$ V power connection. Battery power ca<br>be used with certain devices.                                                                                                                                                                                                                                                                                                                                                |  |

| BA1               | BDCOK H                       | DC Power OK — Power supply-generated signal that is asserted when there sufficient dc voltage available to sustain reliable system operation.                                                                                                                                                                                                                                                                                                            |  |

# Table 3-1Backplane Pin Assignments

#### Table 3-1 (Cont.) Backplane Pin Assignments

| Bus<br>Pin                      | Mnemonic                                            | Description                                                                                                                                                                                                                                                                                                                      |  |

|---------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BB1                             | ВРОК Н                                              | Power OK — Asserted by the power supply when primary power is normal.<br>When negated during processor operation, a power fail trap sequence is ini-<br>tiated.                                                                                                                                                                  |  |

| BC1<br>BD1<br>BE1<br>BF1<br>BH1 | SSPARE4<br>SSPARE5<br>SSPARE6<br>SSPARE7<br>SSPARE8 | Special Spare (Not assigned, not bused. Available for user interconnections.)                                                                                                                                                                                                                                                    |  |

| BJ1                             | GND                                                 | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                     |  |

| BK1<br>BL1                      | MSPAREB<br>MSPAREB                                  | Maintenance Spare — Normally connected on the backplane at each option location (not a bused connection).                                                                                                                                                                                                                        |  |

| BM1                             | GND                                                 | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                     |  |

| BN1                             | BSACK L                                             | This signal is asserted by a DMA device in response to the processor's BDMGO L signal, indicating that the DMA device is bus master.                                                                                                                                                                                             |  |

| BP1                             | BSPARE6                                             | Bus Spare (Not assigned. Reserved for DIGITAL use.)                                                                                                                                                                                                                                                                              |  |

| BR1                             | <b>BEVNT L</b>                                      | External Event Interrupt Request — When asserted, the processor responds (if PS bit 7 is 0) by entering a service routine via vector address $100_8$ . A typical use of this signal is a line time clock interrupt.                                                                                                              |  |

| BS1                             | PSPARE4                                             | Spare (Not assigned. Customer usage not recommended.)                                                                                                                                                                                                                                                                            |  |

| BT1                             | GND                                                 | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                     |  |

| BU1                             | PSPARE2                                             | Spare (Not assigned. Customer usage not recommended.)                                                                                                                                                                                                                                                                            |  |

| BV1                             | +5                                                  | +5 V Power — $+5$ Vdc system power.                                                                                                                                                                                                                                                                                              |  |

| AA2                             | +5                                                  | +5 V Power — Normal $+5$ Vdc system power.                                                                                                                                                                                                                                                                                       |  |

| AB2                             | -12                                                 | -12 V Power — -12 Vdc (optional) power for devices requiring this voltage.                                                                                                                                                                                                                                                       |  |

|                                 |                                                     | NOTE                                                                                                                                                                                                                                                                                                                             |  |

|                                 |                                                     | LSI-11 modules which require negative voltages contain an in-<br>verter circuit (on each module) which generates the required volt-<br>age(s); hence, -12 V power is not required with DIGITAL-supplied<br>options.                                                                                                              |  |

| AC2                             | GND                                                 | Ground — System signal ground and dc return.                                                                                                                                                                                                                                                                                     |  |

| AD2                             | +12                                                 | +12 V Power — $+12$ Vdc system power.                                                                                                                                                                                                                                                                                            |  |

| AE2                             | BDOU'T L                                            | Data Output — BDOUT, when asserted, implies that valid data is available on BDAL0—15 L and that an output transfer, with respect to the bus master device, is taking place. BDOUT L is deskewed with respect to data on the bus. The slave device responding to the BDOUT L signal must assert BRPLY L to complete the transfer. |  |

| AF2                             | BRPLY L                                             | Reply — BRPLY L is asserted in response to BDIN L or BDOUT L and during IAK transactions. It is generated by a slave device to indicate that it has input data available on the BDAL bus or that it has accepted output data from the bus.                                                                                       |  |

# Table 3-1 (Cont ) Backplane Pin Assignments

| Bus<br>Pin | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AH2        | <b>BDIN L</b>      | <ol> <li>Data Input — BDIN L is used for two types of bus operations:</li> <li>When asserted during BSYNC L time, BDIN L implies an input transfer with respect to the current bus master, and requires a response (BRPLY L). BDIN L is asserted when the master device is ready to accept data from a slave device.</li> <li>When asserted without BSYNC L, it indicates that an interrupt operation is occurring.</li> <li>The master device must deskew input data from BRPLY L.</li> </ol>                                                                                                                                                                                |

| AJ2        | BSYNC L            | Synchronize — BSYNC L is asserted by the bus master device to indicate that it has placed an address on BDAL0—15 L. The transfer is in process until BSYNC L is negated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AK2        | BWTBTL             | <ol> <li>Write/Byte — BWTBT L is used in two ways to control a bus cycle:</li> <li>It is asserted during the leading edge of BSYNC L to indicate that an output sequence is to follow (DATO or DATOB), rather than an input sequence.</li> <li>It is asserted during BDOUT L, in a DATOB bus cycle, for byte addressing.</li> </ol>                                                                                                                                                                                                                                                                                                                                           |

| AL2        | BIRQ L             | Interrupt Request — A device asserts this signal when its Interrupt Enable and<br>Interrupt Request flip-flops are set. This signal informs the processor that a<br>device has data to input to the processor or it is ready to accept output data. If<br>the processor's PS word bit 7 is 0, the processor responds by acknowledging the<br>request by asserting BDIN L and BIAKO L.                                                                                                                                                                                                                                                                                         |

| AM2<br>AN2 | BIAKI L<br>BIAKO L | Interrupt Acknowledge Input and Interrupt Acknowledge Output — This is<br>an interrupt acknowledge signal which is generated by the processor in response<br>to an interrupt request (BIRQ L). The processor asserts BIAKO L, which is<br>routed to the BIAKI L pin of the first device on the bus. If it is requesting an in-<br>terrupt, it will inhibit passing BIAKO L. If it is not asserting BIRQ L, the device<br>will pass BIAKI L to the next (lower priority) device via its BIAKO L pin and the<br>lower priority device's BIAKI L pin.                                                                                                                            |

| AP2        | BBS7L              | Bank 7 Select — The bus master asserts BBS7 L when an address in the upper 4K bank (address in the 28-32K range) is placed on the bus. BSYNC L is then asserted and BBS7 L remains active for the duration of the addressing portion of the bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                                        |

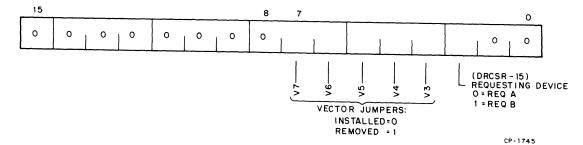

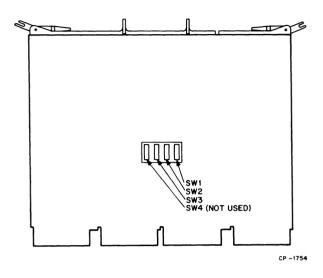

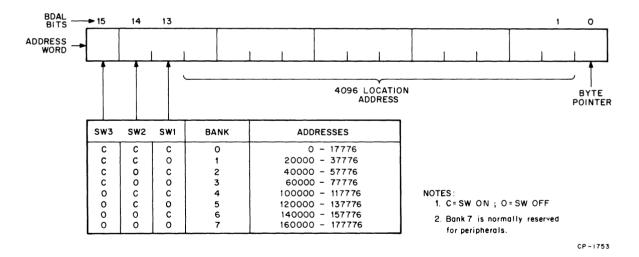

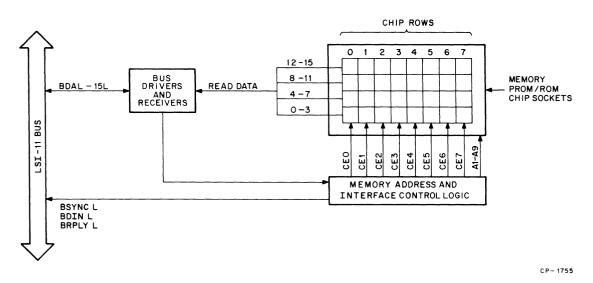

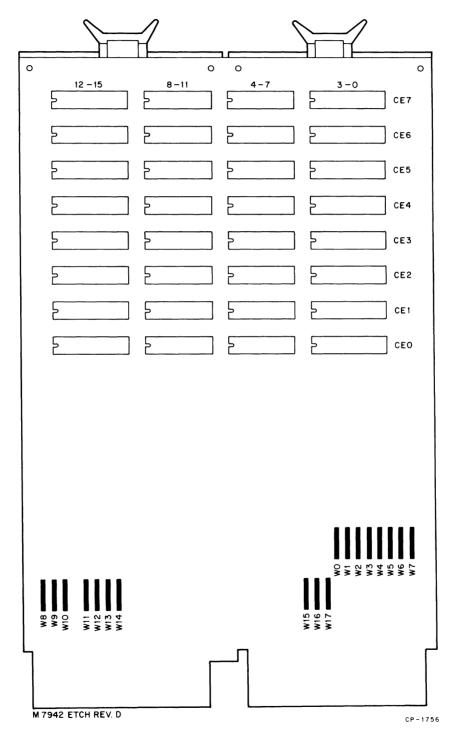

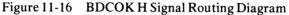

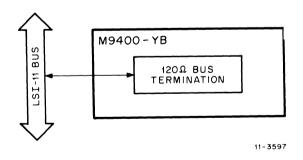

| AR2<br>AS2 | BDMGI L<br>BDMGO L | DMA Grant-Input and DMA Grant-Output — This is the processor-generated daisy-chained signal which grants bus mastership to the highest priority DMA device along the bus. The processor generates BDMGO L, which is routed to the BDMGI L pin of the first device on the bus. If it is requesting the bus, it will inhibit passing BDMGO L. If it is not requesting the bus, it will pass the BDMGI L signal to the next (lower priority) device via its BDMGO L pin. The device asserting BDMR L is the device requesting the bus, and it responds to the BDMGI L signal by negating BDMR, asserting BSACK L, assuming bus mastership, and executing the required bus cycle. |