# Page 4

#### (Continued)

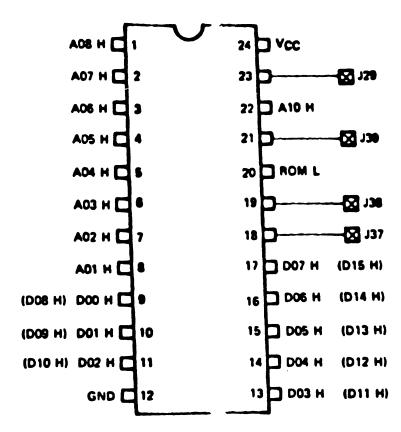

ROM memory configuration continued - refer to Figure 2

J29, J15 - pin 23 - ROM address bit 9

J39,J33 - pin 21 - ground

J39,J34 - pin 21 - +3V

J39,J35 - pin 21 - ROM address bit 12

J39,J40 - pin 21 - +5V

J38,J33 - pin 19 - ground

J38, J34 - pin 19 - +3V

J38, J36 - pin 19 - ROM address bit 11

J37,J33 - pin 18 - ground

J37, J34 - pin 18 - +3V

J37, J35 - pin 18 - ROM address bit 12

# 4. Crystal Clock Option

- To connect 60Hz clock to BEVENT, wire-wrap J3 to J4.

## 5. Factory Configuration

| Jl serial li | ne /       |                |         |                 |

|--------------|------------|----------------|---------|-----------------|

| J23,J18      | address    | 176500 💚       | J45,J50 | 38.4K baud      |

| J24,J19      | 5          | and the second |         |                 |

| J53,J57      | 2 vector 3 | 100            |         |                 |

| J54,J52      | \$         |                |         |                 |

| J2 serial li | ne         |                |         |                 |

| J28,J19      | 7          |                | J46,J4B | 9600 baud       |

| J26,J15      | address    | 177560         |         |                 |

| J25,J14      | 7          |                | J6,J7   | HALT on BREAK   |

| J27,J13      | )          |                |         | (framing error) |

| J56,J51      | 7 vector   | 50             |         |                 |

| J54,J55      | 7          |                |         |                 |

- Both serial lines have the following characteristics:

8 data bits, no parity, one stop bit J59,J61 J61,J62 J62,J64 J59,J66 J60,J63 J63,J65

- RAM is addressed at Bank \$

J30,J31 J32,J33 J31,J32

- ROM is addressed for TU58 bootstrap

J37,J38

J21,J22

J34,J37

J33,J39

J29,J15

- Clock to BEVENT is disabled.

## 3. ROM Memory Enable

- Address Response

|                    | Wire-Wr |         |         |

|--------------------|---------|---------|---------|

| Bank Ø             |         | J10,J11 | J29,J15 |

| Bank 1             | J20,J21 | J 9,J11 | J29,J15 |

| Bootstrap Window   | J22,J21 |         |         |

| (173000 or 773000) |         |         | ·       |

If using the MXV11-A2 bootstrap ROMs:

|      |      | Wire-Wrap Pa  | irs    |

|------|------|---------------|--------|

| Disk | Boot | J22,J21 / J16 | ,J29 : |

| TU58 | Boot | J22,J21 J15   | , 329  |

- To disable ROM memory: wire-wrap pair J21,J8

- Configuring module for user ROMs

note: user must consult ROM vendor's spec. to determine the correct level

for pins

#### NOTE:

DATA OUT PINS SHOWN IN F. RENTHESES REFER TO THE HIGH BYTE SOCKET XE67. DATA OUT PINS DOO H THROUGH DO? H REFER TO THE LOW BYTE SOCKET XE57.

MA 2367

# (Continued)

Note on Wire-Wrapping:

Do not wrap more than two wires per post. Daisy-chain the wire-wraps to connect multiple pins.

# - Baud Rate Selection

wire-wrap the appropriate pair: 6 PRINTER (ONSOL IJ J2 150 baud J45,J41 J46,J41 J45,J43 300 J46,J43 J46,J42 1200 J45,J42 J45,J44 2400 J46,J44 4800 J45,J47 J46,J47 9600 J45,J48 J46,J48 19.2 K J45,J49 J46,J49 38.4 K J45,J50 J46,J50

- Transmit/Receive Characteristics

wire-wrap the appropriate pair:

|                         | J J L   | <b>J</b> 2 |

|-------------------------|---------|------------|

| 8 data bits/no parity** | J62,J66 | J59,J66    |

| 7 data bits/parity      | J62.J65 | J59,J65    |

| two stop bits           | J63,J66 | J60,J66    |

| one stop bit            | J63,J65 | J60,J65    |

| even parity*            | J64,J66 | J61,J66    |

| odd parity*             | J64,J65 | J61,J65    |

- \* if 7 data/parity option is selected

- odd or even parity must be selected, though ignored i.e., the parity wirewrap pins can't be left floating

- Console Operation J2

wire-wrap pair:

boot on framing error (break) J6,J5 halt on framing error (break) J6,J7

#### 2. RAM Memory

- Starting address selection; wire wrap the three pairs which correspond to the desired baud rate.

| Starting Address | Bank | Wire    | Wrap Pairs | <u>B_</u> |

|------------------|------|---------|------------|-----------|

| 1000000          | 0    | J32,J33 | J31,J33    | J30,J33   |

| 020000           | 1    | J32,J33 | J31,J33    | J30,J34   |

| 040000           | 2    | J32,J33 | J31,J34    | J30,J33   |

| 060000           | 3    | J32,J33 | J31,J34    | J30,J34   |

| 100000           | 4    | J32,J34 | J31,J33    | J30,J33   |

| 120000           | 5    | J32,J34 | J31,J33    | J30,J34   |

| 140000           | 6    | J32,J34 | J31,J34    | J30,J33   |

| 160000           | 7    | J32,J34 | J31,J34    | J30,J34   |

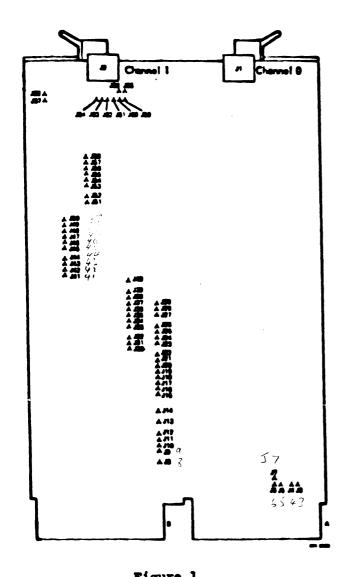

# MXVII-AA, AC Configuration Guide (M8047)

Figure 1

- To disable the serial ports

| channel   | wire wrap                   |

|-----------|-----------------------------|

| <b>J1</b> | J8 to J23 or J24            |

| <b>J2</b> | J8 to J25, J26, J27, or J28 |

# 1. Serial I/O ports J1, J2

- only J2 may be used as the console

| - Address Selection   | on - <u>J1</u> |

|-----------------------|----------------|

| address bit           |                |

| decoded as:           |                |

| bit $3 \rightarrow 1$ | J24, J12       |

| $\rightarrow g$       | J24, J19       |

| bit $4 \rightarrow 1$ | J23, J13       |

| $\rightarrow g$       | J23, J18       |

| - | Address | Se?           | Selection - J2 |              |          |  |

|---|---------|---------------|----------------|--------------|----------|--|

|   | bit 3   | 1 -           | 1              | J28,         | _<br>J12 |  |

|   |         | -             | ø              | J28,         | J19      |  |

|   | bit (   | 1 ->          | 1              | <i>3</i> 27, | J13      |  |

|   |         | $\rightarrow$ | g              | J27,         | J18      |  |

|   | bit !   | <b>5</b> →    | 1              | J25,         | J14      |  |

|   |         | <b>→</b>      | ø              | J25,         |          |  |

|   | bit 9   | • →           | 1              | J26,         | J15      |  |

|   |         | ذ_            |                | 726          |          |  |

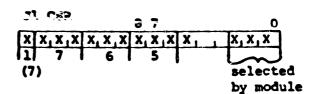

| JZ | CSR       |           |       |     |     |        |    |

|----|-----------|-----------|-------|-----|-----|--------|----|

| Б  |           |           | 8 7   |     |     | 0      |    |

| X  | $X_1X_1X$ | $x_1 x_1$ | X,X,X | 1.1 | XX  | X      |    |

| 1  | 7         |           | 5     |     |     | ]      |    |

| (7 | )         | •         | •     | •   |     | ~      | _  |

| •  | •         |           |       |     | se: | lected | 3  |

|    |           |           |       |     | by  | modu   | le |

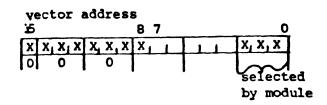

### - Vector Address Selection

Note - Vectors for both I/O ports must be determined before the vector jumpers can be wire wrapped.

wire-wrap the appropriate pair:

|       | n = #   | J1 = 1  | J1 = F  | 51 = 1  |

|-------|---------|---------|---------|---------|

|       | J2 = #  | J2 = ¶  | J2 - 1  | J2 = 1  |

| bit 3 | J53,J57 | J53,J51 | J53,J52 | J53,J58 |

| bit 4 | J54,J57 | J54,J51 | J54,J52 | J54,J58 |

| bit 5 | J55,J57 | J55,J51 | J55,J52 | J55,J58 |

| bits  | J56,J57 | J56,J51 | J56,J52 | J56,J58 |

| 6 6 7 |         | _       |         |         |