# Intel® 82802AB/82802AC Firmware Hub (FWH)

**Datasheet**

**November 2000**

Document Number: 290658-004

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 82802AB/AC Firmware Hub (FWH) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 1999-2001

# Contents

| 1. | Archite | ectural Overview                                                           | 9  |

|----|---------|----------------------------------------------------------------------------|----|

|    | 1.1.    | Interface Overview                                                         | g  |

|    |         | 1.1.1. Intel Firmware Hub Interface                                        | 10 |

|    |         | 1.1.2. Address/Address-Multiplexed Interface                               |    |

|    | 1.2.    | Nonvolatile Flash Memory Core                                              |    |

| 2. | Pinout  | Configurations                                                             | 13 |

|    | 2.1.    | Pin Descriptions                                                           |    |

| 3. | Interfa | ce Operation Description                                                   | 17 |

|    | 3.1.    | Read 17                                                                    |    |

|    | 3.1.    | Write 17                                                                   |    |

|    |         |                                                                            | 47 |

|    | 3.3.    | Output Disable                                                             | 17 |

|    | 3.4.    | Reset 17                                                                   |    |

|    | 3.5.    | Operational Effects of Hardware Write-Protect Pins TBL# and WP#            | 18 |

| 4. | Functi  | onal Descriptions                                                          | 19 |

|    | 4.1.    | Read Array Command                                                         | 21 |

|    | 4.2.    | Read Identifier Codes Command                                              | 21 |

|    | 4.3.    | Read Status Register Command                                               | 21 |

|    | 4.4.    | Clear Status Register Command                                              | 21 |

|    | 4.5.    | Block Erase Command                                                        |    |

|    | 4.6.    | Program Command                                                            |    |

|    | 4.7.    | Block Erase Suspend Command                                                |    |

|    | 4.8.    | Program Suspend Comand                                                     |    |

|    | 4.9.    | Register Based Locking, General-Purpose Input, and Random Number Generator | 0  |

|    | Regist  | · · · · · · · · · · · · · · · · · · ·                                      |    |

|    | J       | 4.9.1. T_BLOCK_LK and T_MINUSxx_LK — Block-Locking Registers               | 25 |

|    |         | 4.9.2. General-Purpose Input Register                                      |    |

|    |         | 4.9.2.1. GPI_REG — General-Purpose Input Register                          |    |

|    |         | 4.9.3. Random Number Generator Registers                                   |    |

|    |         | 4.9.3.1. RNG Hardware Status Register                                      |    |

|    |         | 4.9.3.2. RNG Data Status Register                                          |    |

|    | 4.40    | 4.9.3.3. RNG Data Register                                                 |    |

|    | 4.10.   | Using the Random Number Generator                                          |    |

|    | 4.11.   | Detecting and Initializing the RNG Device                                  |    |

|    |         | 4.11.1. Detecting the RNG Device                                           |    |

|    |         | 4.11.2. Initializing the RNG Device                                        |    |

|    |         | 4.11.4. Mapping FWH Devices onto Memory Map                                |    |

|    |         | 4.11.5. Paging FWH Devices for Greater Than 4 MB of FWH Memory             |    |

|    |         | 4.11.6. Programming Multiple FWH Devices                                   |    |

|    | 4.12.   | CUI Automation Flowcharts                                                  |    |

| _  |         |                                                                            |    |

| 5. |         | cal Specifications                                                         |    |

|    | 5.1.    | Absolute Maximum Ratings                                                   | 33 |

| 5.2. | Operating Condit             | ions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.2.3. Intel F               | FWH Interface AC Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.2.3.1.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.2.3.2.                     | Signal Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.3. | Block Programm               | ing Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4. |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.4.1.1.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.4.1.2.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.4.1.3.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.4.1.4.                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.4.1.5.                     | Response To Invalid Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.4.1.6.                     | Abort Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.4.1.7.                     | Intel FWH Cycle Timing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.5. | RNG Parameters               | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PRO  | M Programming Spe            | ecifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.1. |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.2  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0.2. |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | •                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3. |                              | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

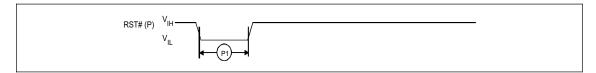

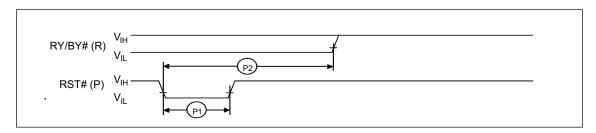

|      | 6.4.2. AC W                  | aveforms for Reset Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

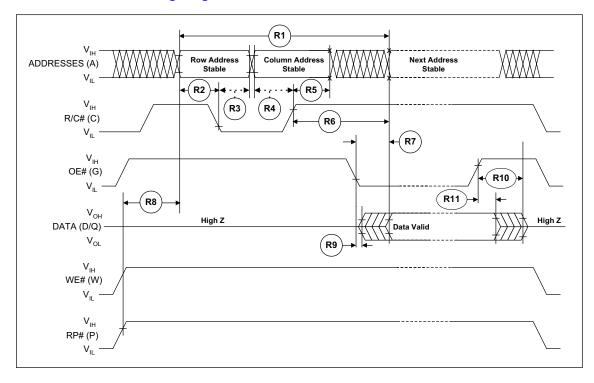

|      | 6.4.3. A/A N                 | Mux Read-Only Operations (1,3)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

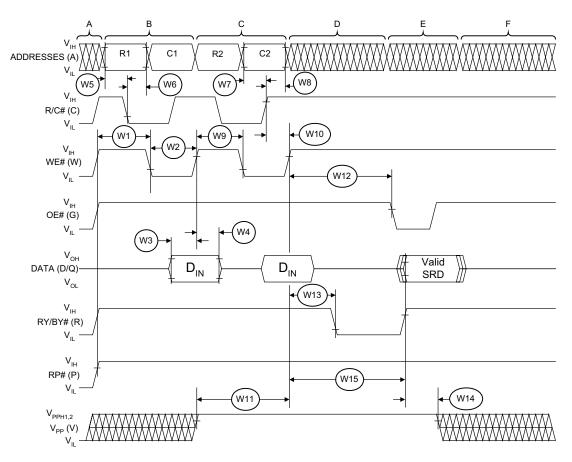

|      | 6.4.4. A/A N                 | 1ux Write Operations (1,2)                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.3.<br>5.4.<br>5.5.<br>PROI | 5.2.1. Interface 5.2.2. Interface 5.2.2. Interface 5.2.3. Intel Face 5.2.3.1. 5.2.3.2.  5.3. Block Programm 5.4. Intel Firmware His 5.4.1. Intel Face 5.4.1.1. 5.4.1.2. 5.4.1.3. 5.4.1.4. 5.4.1.5. 5.4.1.6. 5.4.1.7.  5.5. RNG Parameters PROM Programming Special Programming Special Programming ("A 6.2. Bus Operation 6.2.1. Output 6.2.2. Row/G 6.2.3. Read 6.2.4. Read 6.2.4. Read 6.2.5. Write 6.3. Command Defini 6.4. Electrical Charace 6.4.1. Reser 6.4.2. AC W 6.4.3. A/A M | 5.2.1. Interface DC Input/Output Specifications. 5.2.2. Interface AC Input/Output Specifications. 5.2.3. Intel FWH Interface AC Timing Specifications. 5.2.3.1. Clock Specification. 5.2.3.2. Signal Timing Parameters. 5.3. Block Programming Times 5.4. Intel Firmware Hub Interface. 5.4.1.1. Read Cycle Sequence. 5.4.1.2. Single-Byte Read Waveforms. 5.4.1.3. Write Cycle Sequence. 5.4.1.4. Write Waveforms. 5.4.1.5. Response To Invalid Fields. 5.4.1.6. Abort Operations. 5.4.1.7. Intel FWH Cycle Timing Information. 5.5. RNG Parameters.  PROM Programming Specifications. 6.1. Programming ("A/A Mux") Mode Operation. 6.2.1. Output Disable/Enable. 6.2.2. Row/Column Addresses. 6.2.3. Read Operation. 6.2.4. Read Identifier Codes Operation. 6.2.5. Write Operation. 6.2.6. Command Definitions. 6.4.1. Reset Operations. 6.4.2. AC Waveforms for Reset Operations. 6.4.3. A/A Mux Read-Only Operations. 6.4.3. A/A Mux Read-Only Operations. 6.4.3. A/A Mux Read-Only Operations. |

# **Figures**

| Figure 1.  | Simplified Block Diagram                                    | 8  |

|------------|-------------------------------------------------------------|----|

| Figure 2.  | Device Memory Map with Intel FWH Hardware Lock Architecture |    |

| Figure 3.  | Intel FWH Boot-Configuration System Memory Map              |    |

| Figure 4.  | 32-Lead PLCC Intel Firmware Hub Pinout                      |    |

| Figure 5.  | 40-Lead TSOP Intel Firmware Hub Pinout                      | 13 |

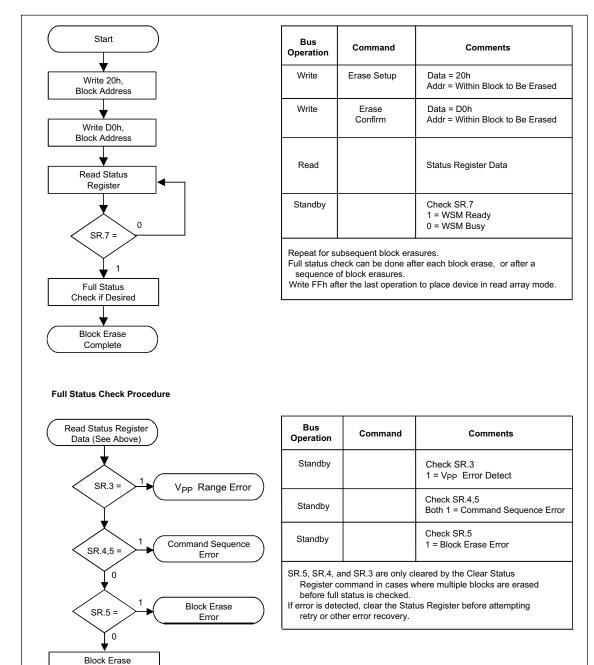

| Figure 6.  | Automated Block Erase Flowchart                             | 31 |

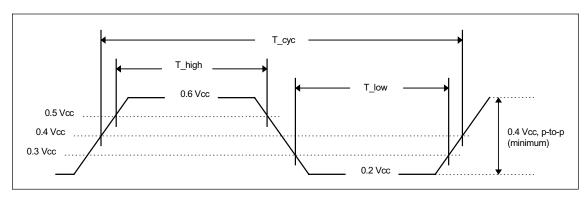

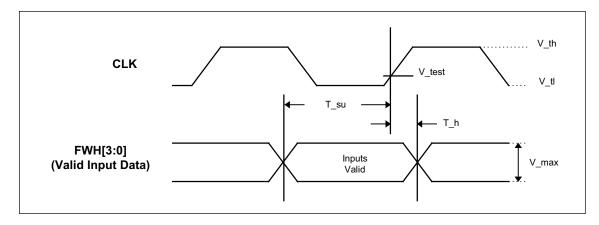

| Figure 7.  | Clock Waveform                                              |    |

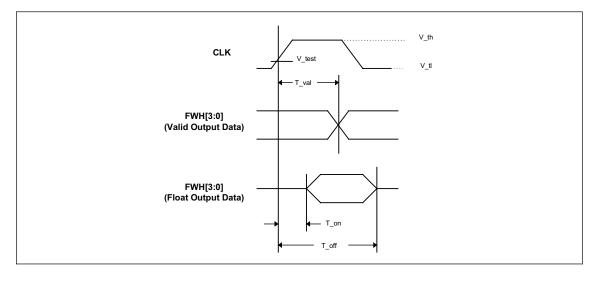

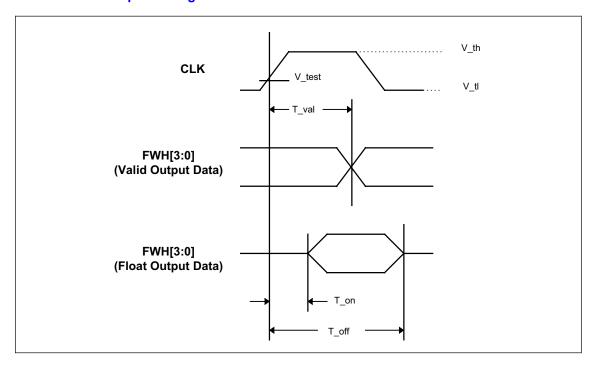

| Figure 8.  | Output Timing Parameters                                    | 38 |

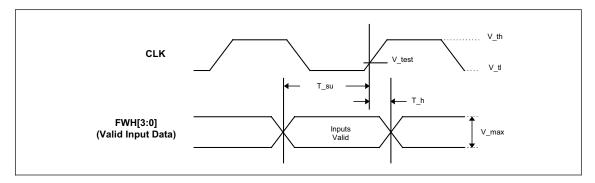

| Figure 9.  | Input Timing Parameters                                     | 39 |

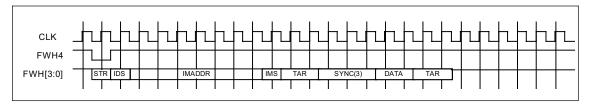

| Figure 10. | FWH Single-Byte Read Waveforms                              |    |

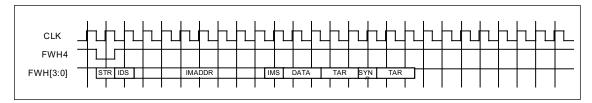

| Figure 11. | Write Waveforms                                             | 43 |

| Figure 12. | Intel FWH Output Timing Parameters                          |    |

| Figure 13. | Intel FWH Input Timing Parameters                           |    |

| Figure 14. | A/A Mux Read Timing Diagram                                 |    |

| Figure 15. | A/A Mux Write Timing Diagram                                |    |

|            |                                                             |    |

# **Tables**

| Table 1.  | Pin Descriptions                                   | 14 |

|-----------|----------------------------------------------------|----|

| Table 2.  | Command Definitions                                |    |

| Table 3.  | Status Register Definition                         | 20 |

| Table 4.  | Identifier Codes                                   |    |

| Table 5.  | Intel Firmware Hub Register Configuration Map      | 24 |

| Table 6.  | Register-Based Locking Value Definitions           | 25 |

| Table 7.  | Temperature and VCC                                |    |

| Table 8.  | Intel FWH Interface DC Input/Output Specifications | 34 |

| Table 9.  | Power Supply Specifications — All Interfaces       | 35 |

| Table 10. | Intel FWH Interface AC Input/Output Specifications | 36 |

| Table 11. | Clock Specification                                | 37 |

| Table 12. | Signal Timing Parameters                           | 38 |

| Table 13. | Interface Measurement Condition Parameters         |    |

| Table 14. | AC Waveform for Reset Operation                    | 39 |

| Table 15. | Programming Times                                  |    |

| Table 16. | FWH Read Cycle                                     | 41 |

| Table 17. | FWH Write Cycle                                    |    |

| Table 18. | Signal Timing Parameters                           | 44 |

| Table 19. | RNG Timing Characteristics                         | 45 |

| Table 20. | RNG Statistical Characteristics                    |    |

| Table 21. | Bus Operations                                     | 48 |

# **Revision History**

| Rev. | Draft/Changes                                                        | Date          |

|------|----------------------------------------------------------------------|---------------|

| -001 | Initial Release                                                      | April 1999    |

| -002 | Added Chapter 6                                                      | May 1999      |

|      | Updated programmer vendor/service provider information.              |               |

| -003 | Changed V <sub>IH</sub> min. spec to reflect actual value.           | May 2000      |

|      | Updated programmer vendor/service provider information.              |               |

|      | Clarification of part numbering.                                     |               |

|      | Spec now includes all known issues from all densities/lithographies. |               |

|      | Included FWH memory cycle and RNG information.                       |               |

| -004 | Removed All references to multi-byte read cycles                     | November 2000 |

|      | Added DC Characteristics for A/A Mux mode                            |               |

# Intel<sup>®</sup> 82802AB/AC Firmware Hub (FWH)

#### **Product Features**

- Intel platform compatability

- Enables security-enhanced platform infrastructure; facilitates option to remove ISA.

- Firmware hub hardware interface mode

- 5-Signal communication interface supporting byte-at-a-time reads and writes

- Register-based read and write protection for each code/data storage block

- Hardware write protect pins for the top boot block and the remaining code/data storage blocks

- 5 Additional GPIs for platform design flexibility

- Contains a hardware Random Number Generator (RNG) for enhancing platform security

- Integrated Command User Interface (CUI) for requesting access to locking, programming, and erasing options. The CUI also handles requests for data residing in status, ID, and block-lock registers.

- Operates with 33-MHz PCI clock and 3.3 V I/O.

- Industry-standard packages (40L TSOP or 32L PLCC)

- Two configurable interfaces

- Firmware hub interface for platform operation

- Address/Address-Multiplexed (A/A Mux) interface for programming during manufacturing

- 4 or 8 Mbits of flash memory for platform code/data nonvolatile storage

- Symmetrically blocked, 64-KB memory sections

- Available in 8-Mbit (Intel® 82802AC) and 4-Mbit (Intel® 82802AB) densities

- Automated byte program and block erase via an integrated Write State Machine (WSM)

- Address/Address-Multiplexed (A/A Mux) interface/mode

- —11-Pin multiplexed address and 8-pin data I/O interface

- Supports fast on-board or out-of-system programming for manufacturing

- Case temprature operating range

- Power supply specifications

- Vcc:  $3.3 \text{ V} \pm 0.3 \text{ V}$

- Vpp: 3.3 V and 12 V for fast programming, (80 hours maximum)

The Intel® 82802 (FWH) firmware hub may contain design defects or errors known as errata that may cause the products to deviate from published specifications. Current characterized errata are available upon request.

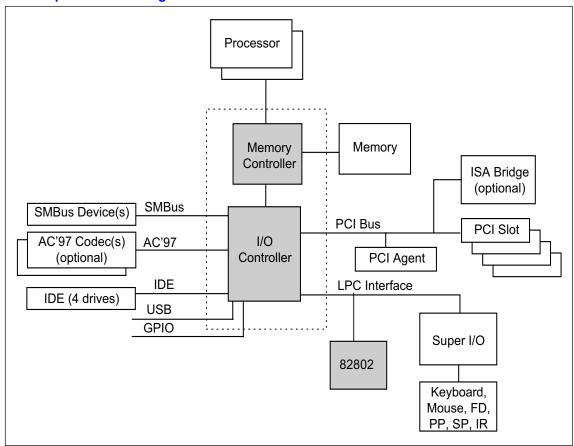

Figure 1. Simplified Block Diagram

# 1. Architectural Overview

The Intel® 82802 Firmware Hub (FWH) discrete component is compatible with several Intel chipset platforms and a variety of applications. The device operates under the LPC/FWH interface/protocol. The hardware features of this device include a Random Number Generator (RNG), five General-Purpose Inputs (GPIs), register-based block locking, and hardware-based locking. This combination of logic features and non-volatile memory enables better protection for the storage and update of platform code and data, adds platform flexibility through additional GPIs, and allows for quicker introduction of new security/manageability features into current and future platforms. The platform RNG, accessed through the Intel® Security Driver and third-party software, enables security features for the PC platform. See the product features listed previously for a list of more key features that the Intel FWH provides.

#### 1.1. Interface Overview

This device is equipped with two hardware interfaces. The state of the device's "IC" (InterfaceConfiguration) pin determines which interface is in use. The interface mode must be selected prior topower-up or before return from reset (RST# or INIT# low-to-high transition). The Intel FWH interface isdesigned to work with the Intel family of I/O Controller Hubs (ICH) during platform operation. The A/A Mux interface is designed as a programming interface for OEMs, for use during motherboard manufacturing or component pre-programming. The A/A Mux interface is not intended for use during regular personal computer operation. Such a configuration would cause the expected (Intel FWH) interface to be disabled, and the system boot sequence would fail upon power-up.

An internal Command User Interface (CUI) serves as the internal control center for the nonvolatilememory core in either of the two device interfaces (Intel FWH or A/A Mux). A single valid commandsequence written to the CUI initiates an automated sequence of internal events to complete various tasks. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase and program operations.

Driving RST# or INIT# low resets the device, which resets the block-lock registers to their default (write-locked) condition and clears the status register. A reset time (tPHQV A/A Mux) is required from RST# or INIT# switching high until outputs are valid. Likewise, the device has a wake time (tPHRH A/A Mux) from RST# or INIT# high until writes to the CUI are recognized. A reset latency will occur if a reset procedure is performed during a programming or erase operation. Resetting the component will put the component back into read-array mode.

**Note:** There is no chip enable (like CE#) in either interface. Stand-by current control in the Inel FWH interface is enabled automatically, if the Intel FWH4 is high and the device is not working to complete a requested activity.

#### 1.1.1. Intel Firmware Hub Interface

The Intel Firmware Hub (Intel FWH) interface consists primarily of a 5-signal communication interface used to control the operation of the device in a system environment. The buffers for this interface were designed to be PCI compliant. To ensure the effective delivery of security and manageability features, the Intel FWH interface is the only way access the full feature set of the device. The Intel FWH interface is equipped to operate at 33 MHz, synchronous with the PCI bus.

#### 1.1.2. Address/Address-Multiplexed Interface

The A/A Mux refers to the multiplexed row and column addresses in this interface. This approach is required so that the device can be tested and programmed quickly with automated test equipment (ATE) or off-board PROM programmers in the OEM's manufacturing flow. This interface also allows the device to have an efficient programming interface with potentially large future densities, while still fitting into a 32-pin package. Only basic reads, programming, and erasure of the nonvolatile memory blocks can be performed through the A/A Mux interface. In this mode, the Intel FWH features, security features, and registers are unavailable. A row/column (R/C#) pin determines which set of addresses (rows or columns) is latched. See the A/A Mux pin description table for more information.

# 1.2. Nonvolatile Flash Memory Core

The primary feature of the Intel FWH component is a nonvolatile memory core based on Intel<sup>®</sup> Flash Technology. This high-performance memory array is arranged in eight (4-Mbit device) or sixteen (8-Mbit device) 64-KB blocks.

Intel® Flash Technology enables fast factory programming and low-power designs. Specifically designed for 3-V systems, this component supports read operations at 3.3 V  $V_{CC}$  and block erase and program operations at 3.3 V and 12 V  $V_{PP}$ . The 12 V  $V_{PP}$  option yields the fastest program performance, which will increase factory throughput, but is not recommended for standard in-system FWH operation in the platform, due to an **80-hr limit for 12 V** on the  $V_{PP}$  pin over the lifetime of the device, whether or not programming is taking place. With the 3.3-V  $V_{PP}$  option (recommended for in-system operation),  $V_{CC}$  and  $V_{PP}$  may be tied together for a simple, low-power 3-V design. In addition to the voltage flexibility, the dedicated  $V_{PP}$  pin provides complete data protection when  $V_{PP} \le V_{PPLK}$ . Internal  $V_{PP}$  detection circuitry automatically configures the device for block erase and program operations. While current for 12-V programming will be drawn from  $V_{PP}$ , 3.3-V programming solutions should design their board such that  $V_{PP}$  draws from the same supply as  $V_{CC}$ , and should assume that full programming current may be drawn from either pin.

0FFFF 64-Kbyte Block 15 } TBL# (8 Mb) 0F0000 0EFFFF 64-Kbyte Block 14 0E0000 0DFFFF 64-Kbyte Block 13 0D0000 0CFFFF 64-Kbyte Block 12 64-Kbyte Block 11 64-Kbyte Block 10 64-Kbyte Block 9 090000 08FFFF WP# (8 Mb) 64-Kbyte Block 8 080000 07FFFF Blocks 0-14 64-Kbyte Block 7 }TBL# (4 Mb) 070000 06FFFF 64-Kbyte Block 6 060000 05FFFF 050000 04FFFF 040000 03FFFF 030000 02FFFF 020000 01FFFF 010000 00FFFF 64-Kbyte Block 5 64-Kbyte Block 4 WP# (4 Mb) 64-Kbyte Block 3 64-Kbyte Block 2 64-Kbyte Block 1 64-Kbyte Block 0 000000 mem\_map\_lock

Figure 2. Device Memory Map with Intel FWH Hardware Lock Architecture

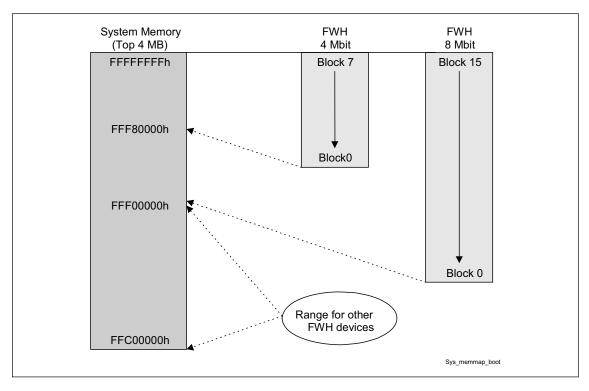

Figure 3. Intel FWH Boot-Configuration System Memory Map

This page is intentionally left blank.

# 2. Pinout Configurations

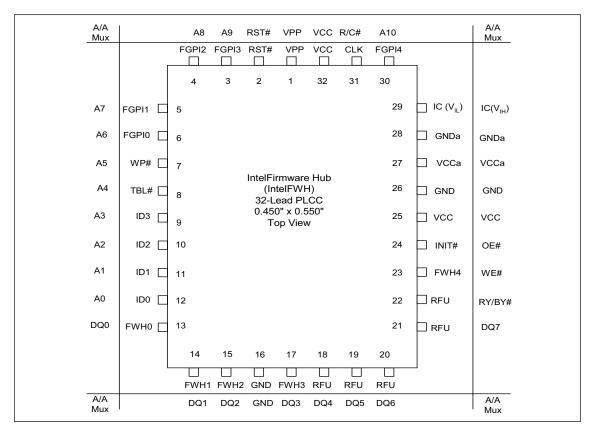

Figure 4. 32-Lead PLCC Intel Firmware Hub Pinout

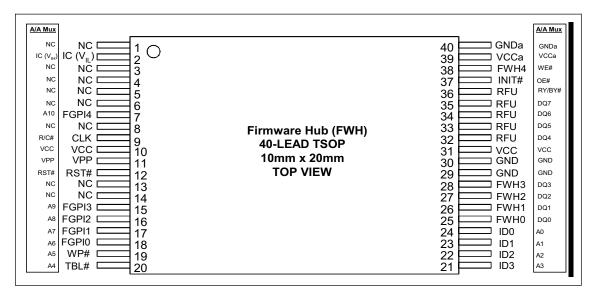

Figure 5. 40-Lead TSOP Intel Firmware Hub Pinout

# 2.1. Pin Descriptions

The pin descriptions table details the usage of each device pin. Most pins have dual functionality, with functions in both the Intel Firmware Hub and A/A Mux interfaces. The A/A Mux functionality for pins is shown *bold italic* in the description box for that pin. All pins are designed to be compliant with VCC + 0.3 V max. unless otherwise noted.

Table 1. Pin Descriptions

| Symbol   | Туре     | Int          | erface  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------|----------|--------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |          | Intel<br>FWH | A/A Mux |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| IC       | I        | X            | х       | Interface Configuration Pin. This pin determines which interface is used to communicate with the device. When it is held low, the Intel FWH interface is enabled. When it is held High, the A/A Mux interface is enabled. This pin must be set at power-up or before return from reset, and must not be changed during device operation. This pin is pulled down with an internal resistor of between 20 and 100 k $\Omega$ . When the IC is High (A/A Mux mode), this pin will exhibit a leakage current of approximately 200 $\mu$ A. This pin may be floated, which will select the Intel FWH mode. |  |  |

| RST#     | ı        | х            | X       | Interface Reset. Valid for both A/A Mux and Intel FWH interface operation. When driven low, RST# inhibits write operations to provide data protection during power transitions, resets internal automation, and tri-states pins FWH[3:0] (in Intel FWH interface mode). RST#-high enables normal operation. When exiting from reset, the device defaults to read array mode.                                                                                                                                                                                                                           |  |  |

| INIT#    | I        | x            |         | Processor Reset. This is a second reset pin for in-system use. This pin is internally combined with the RST# pin. If this pin or RST# is driven low, identical operation is exhibited. This signal is designed to be connected to the chipset INIT signal (Max. voltage depends on the processor. Do <b>not</b> use 3.3 V).                                                                                                                                                                                                                                                                            |  |  |

| 0114     |          |              |         | A/A Mux = OE#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| CLK      | <b> </b> | X            |         | <b>33-MHz Clock for</b> Intel <b>FWH Interface.</b> This input is the same as that for the PCI clock and adheres to the PCI specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|          |          |              |         | A/A Mux = R/C#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| FWH[3:0] | I/O      | Х            |         | Intel FWH I/Os. I/O communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|          |          |              |         | A/A Mux = DQ[3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| FWH4     | I        | Х            |         | Intel FWH Input. Input communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|          |          |              |         | A/A Mux = WE#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Symbol    | Туре | Int          | erface  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------|------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|